# THEORY, SYNTHESIS AND IMPLEMENTATION OF CURRENT-MODE CMOS PIECEWISE-LINEAR CIRCUITS USING MARGIN PROPAGATION

By

Ming Gu

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

**Electrical Engineering**

2012

#### **ABSTRACT**

# THEORY, SYNTHESIS AND IMPLEMENTATION OF CURRENT-MODE CMOS PIECEWISE-LINEAR CIRCUITS USING MARGIN PROPAGATION

#### By

#### Ming Gu

Achieving high energy-efficiency is a key requirement for many emerging smart sensors and portable computing systems. While digital signal processing (DSP) has been the de-facto technique for implementing ultra-low power systems, analog signal processing (ASP) provides an attractive and alternate approach that can not only achieve high energy efficiency but also high computational density. Conventional ASP techniques are based on a top-down design approach, where proven mathematical principles and related algorithms are mapped and emulated using computational primitives inherent in the device physics. An example being the translinear principle, which is the state-of-the-art ASP technique, that uses the exponential current-to-voltage characteristics for designing ultra-low-power analog processors. However, elegant formulations could result from a bottom-up approach where device and bias independent computational primitives (e.g. current and charge conservation principles) are used for designing "approximate" analog signal processors. The hypothesis of this proposal is that many signal processing algorithms exhibit an inherent calibration ability due to which their performance remains unaffected by the use of "approximate" analog computing techniques.

In this research, we investigate the theory, synthesis and implementation of high performance analog processors using a novel piecewise-linear (PWL) approximation algorithm called margin propagation (MP). MP principle utilizes only basic conservation laws of physical quantities (current, charge, mass, energy) for computing and therefore is scalable across devices (silicon, MEMS, microfluidics). However, there are additional advantages of MP-based processors when imple-

mented using CMOS current-mode circuits, which includes: 1) bias-scalability and robust to variations in environmental conditions (e.g. temperature); and 2) improved dynamic range and faster convergence as compared to the translinear implementations. We verify our hypothesis using two ASP applications: (a) design of high-performance analog low-density parity check (LDPC) decoders for applications in sensor networks; and (b) design of ultra-low-power analog support vector machines (SVM) for smart sensors. Our results demonstrate that an algorithmic framework for designing margin propagation (MP) based LDPC decoders can be used to trade-off its BER performance with its energy efficiency, making the design attractive for applications with adaptive energy-BER constraints. We have verified this trade-off using an analog current-mode implementation of an MP-based (32,8) LDPC decoder. Measured results from prototypes fabricated in a 0.5  $\mu$ m CMOS process show that the BER performance of the MP-based decoder outperforms a benchmark state-of-the-art min-sum decoder at SNR levels greater than 3.5 dB and can achieve energy efficiencies greater than 100pJ/bit at a throughput of 12.8 Mbps.

In the second part of this study, MP principle is used for designing an energy-scalable SVM whose power and speed requirements can be configured dynamically without any degradation in performance. We have verified the energy-scaling property using a current-mode implementation of an SVM operating with 8 dimensional feature vectors and 18 support vectors. The prototype fabricated in a  $0.5~\mu m$  CMOS process has integrated an array of floating gate transistors that serve as storage for up to 740 SVM parameters as well as novel circuits that have been designed for interfacing with an external digital processor. These include a novel current-input current-output logarithmic amplifier circuit that can achieve a dynamic range of 120dB while consuming nanowatts of power and a novel varactor based temperature compensated floating-gate memory that demonstrates a superior programming range than other competitors.

#### ACKNOWLEDGMENT

I am deeply grateful to Dr. Shantanu Chakrabartty for his advice during my Ph.D studies. I owe my successful transition from control theory to analog integrated circuit design to his guidance, encouragement, support, and constant assurance. As an academic advisor, he was always approachable and ready to help in every possible way to make sure I was always at ease while working on my research. I wish him well for all his future endeavors and would be happy to cooperate with him in the future.

Many thanks to Dr. Hayder Radha, Dr. Tongtong Li and Dr. Jonathan I. Hall for being on my Ph.D committee, for their feedbacks, suggestions, and continual interest in my progress. Thanks to Dr. Hayder Radha for helping me in our collaborated project and the instructions on information theory. Thanks to Dr. Tongtong Li and Dr. Jonathan I. Hall in helping me in communication theory and error-correcting coding.

I would like to thank my lab mates Ravi Krishna Shaga, Tao Feng, Pikul Sarkar and Thamira Hindo. I really enjoy the opportunities to work with them and have a good time with them during my graduate studies.

I am grateful to my friends Rui Lin, Xiaoqin Tang, Lei Zhang, Kiran Misra, Hao Wen and Yun Li for their friendship, support, and motivation.

My special thanks go to my husband, Dr. Wei Wang, for his support during my graduate studies. His love, support, and encouragement have carried me to where I am today. We met, got to know each other, fell in love and got married at MSU. The time we spent together at MSU pursuing our Ph.Ds is the best part in our lives. I would dedicate this dissertation to my parents, and grandparents for their support all the time.

## LIST OF TABLES

| Table 1.1 | Power dissipation of major components for a 0.6 $\mu$ m mixed-signal CMOS              |     |

|-----------|----------------------------------------------------------------------------------------|-----|

|           | image sensor [1]                                                                       | 4   |

| Table 1.2 | Milestones in TASP                                                                     | 8   |

| Table 3.1 | Operands of MP units in Fig 3.4                                                        | 44  |

| Table 4.1 | Operations in ordinary and logarithmic arithmetic in digital implemented LNS processor | 47  |

| Table 5.1 | Threshold comparison for AWGN channel under margin propagation and                     | 02  |

| Table 5.2 | Specifications of the MP-based analog LDPC decoder                                     | 93  |

| Table 5.3 | CMOS Digital (top 4) and Analog (bottom 6) Decoders                                    | 121 |

| Table 6.1 | Specifications of the current-input current-output CMOS logarithmic am- |     |

|-----------|-------------------------------------------------------------------------|-----|

|           | plifier                                                                 | 150 |

| Table 6.2 | Comparison of performance                                               | 156 |

| Table 6.3 | Specification of the fabricated prototype                               | 156 |

## LIST OF FIGURES

| Figure 1.1 | Illustration of the tradeoffs in (a)DSP and (b)CADSP systems [2, 3]. For                                                                       |    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | interpretation of the references to color in this and all other figures, the                                                                   |    |

|            | reader is referred to the electronic version of this dissertation                                                                              | 3  |

|            |                                                                                                                                                |    |

| Figure 1.2 | Power consumption comparison for DSP [4, 5] and ASP [6, 7]                                                                                     | 4  |

|            |                                                                                                                                                |    |

| Figure 1.3 | Basic CMOS circuits for (a) digital half adder based on NAND and NOT                                                                           |    |

|            | gates; (b) digital multiplier based on (a); (c) analog adder; (d) analog                                                                       |    |

|            | multiplier (Gilbert cell)                                                                                                                      | 5  |

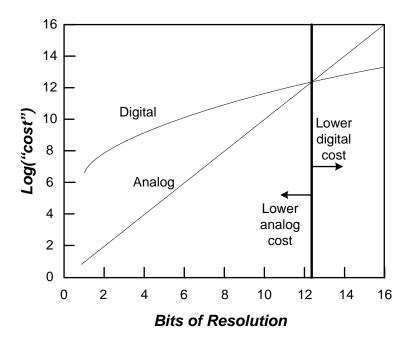

| Figure 1.4 | Resolution versus "cost" on using ASP or DSP [2]                                                                                               | 7  |

|            |                                                                                                                                                |    |

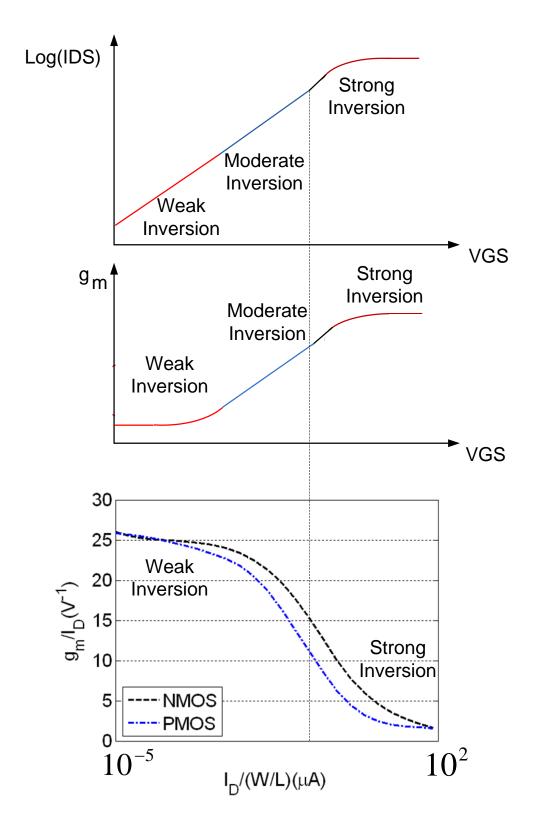

| Figure 1.5 | $log(I_{\hbox{\it D}})$ versus $V_{\hbox{\it GS}},~g_m$ versus $V_{\hbox{\it GS}},$ and $g_m/I_{\hbox{\it D}}$ versus $I_{\hbox{\it D}}/(W/L)$ |    |

|            | curves for various operation regions [8]                                                                                                       | 16 |

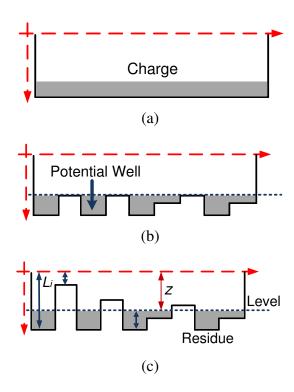

| Figure 1.6  | illustration of the proposed concept for designing scalable analog com-   |     |

|-------------|---------------------------------------------------------------------------|-----|

|             | putational systems. The depth of potential wells can be controlled by an  |     |

|             | external voltage source. At equilibrium the charge re-distributes amongst |     |

|             | potential wells to satisfy charge conservation laws                       | 17  |

|             |                                                                           |     |

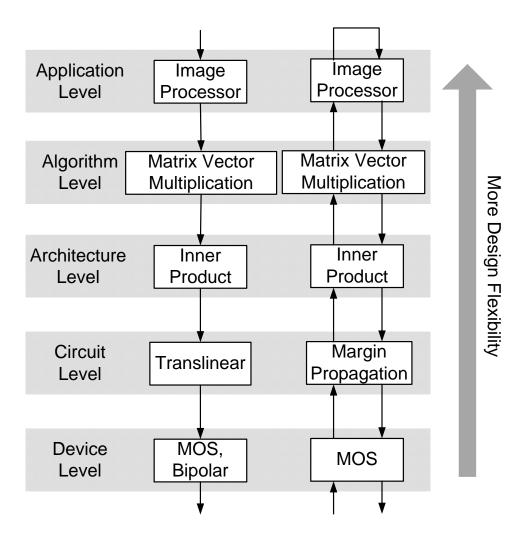

| Figure 1.7  | Top-down design procedure for conventional TASP and the bottom-up         |     |

|             | procedure we propose.                                                     | 18  |

|             |                                                                           |     |

|             |                                                                           | 4.0 |

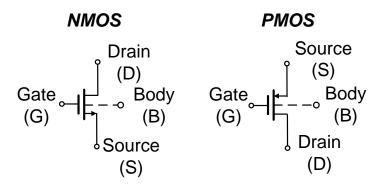

| Figure 2.1  | MOS symbols                                                               | 19  |

|             |                                                                           |     |

| Figure 2.2  | An alternating translinear loop of NMOS transistors. Here the number      |     |

|             | of clockwise facing transistors in junction is the same as the number of  |     |

|             | counterclockwise facing transistors                                       | 22  |

|             |                                                                           |     |

| Figure 2.3  | A voltage-in-current-out winner-take-all circuit                          | 27  |

|             |                                                                           |     |

| Figure 2.4  | A multiple-input translinear element (MITE)                               | 27  |

| 1 iguic 2.4 | A marapie-input transmical element (wirth).                               | 21  |

|             |                                                                           |     |

| Figure 2.5  | Principle of dynamic translinear circuits                                 | 28  |

|             |                                                                           |     |

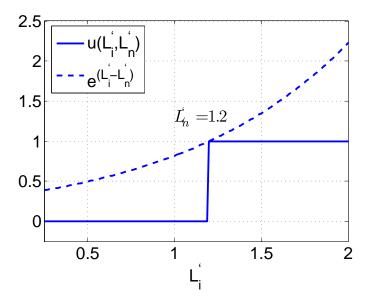

| Figure 3.1  | Illustration of reverse water-filling procedure                           | 32  |

| Figure 3.2            | Scaling property of margin propagation                                                                                                         | 33       |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 3.3            | The curve of $e^{(L_i^{\prime}-L_n^{\prime})}$ and its PWL approximation curve of $u(L_i^{\prime},L_n^{\prime})$                               | 42       |

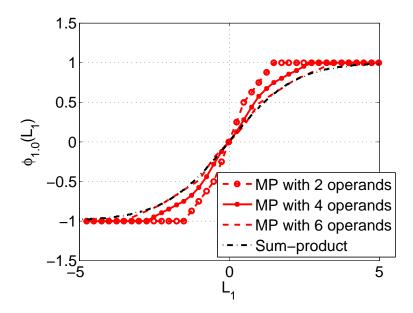

| Figure 3.4            | PWL approximation effect of MP algorithm                                                                                                       | 45       |

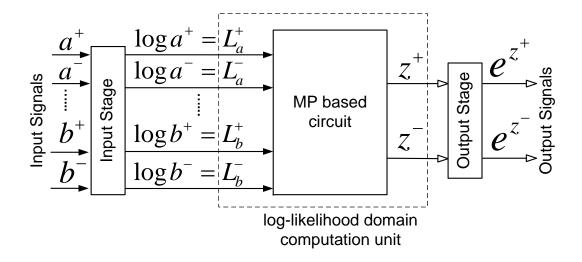

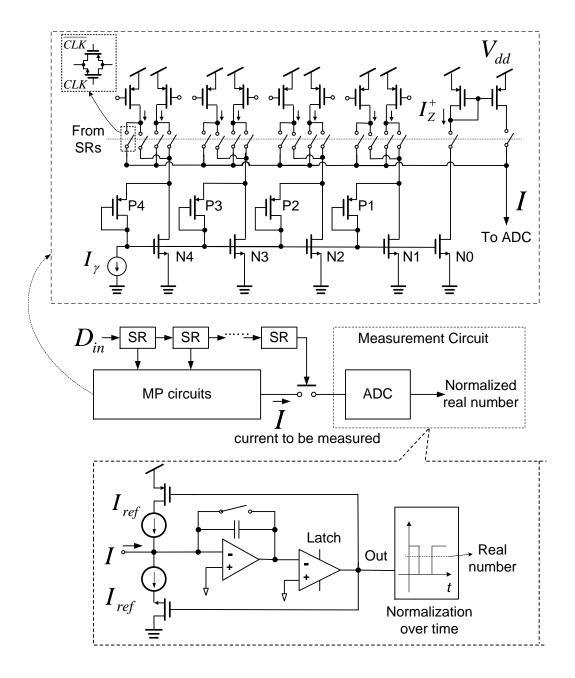

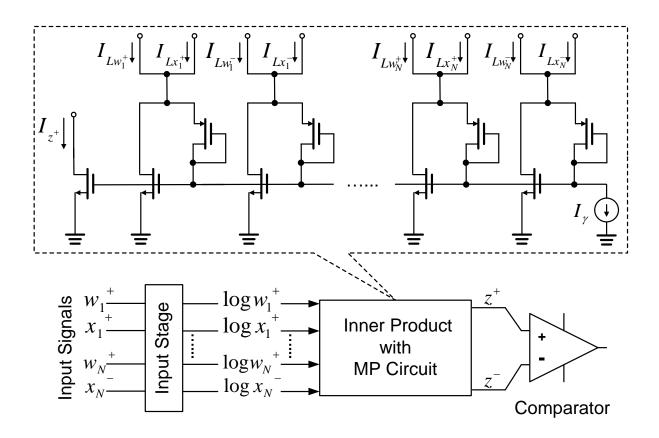

| Figure 4.1            | Top architecture of the computation unit                                                                                                       | 50       |

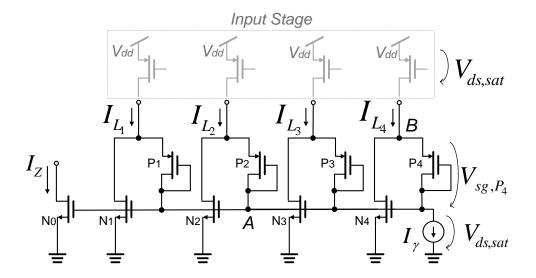

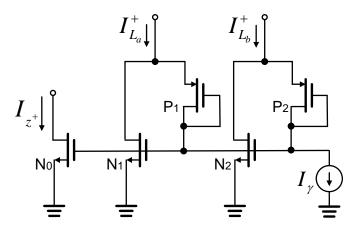

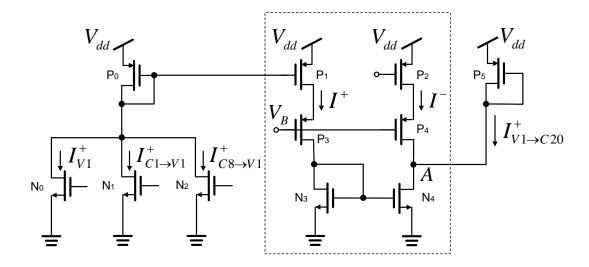

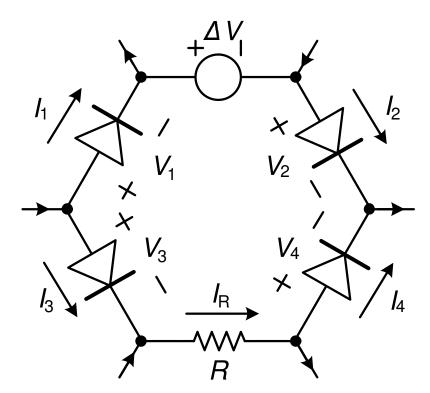

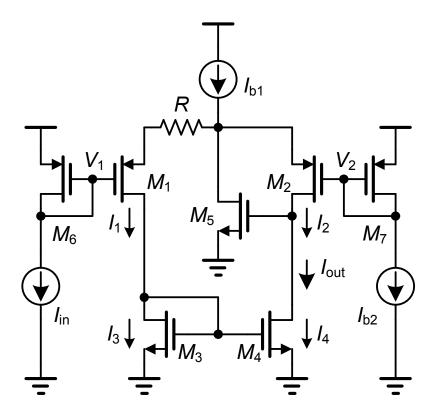

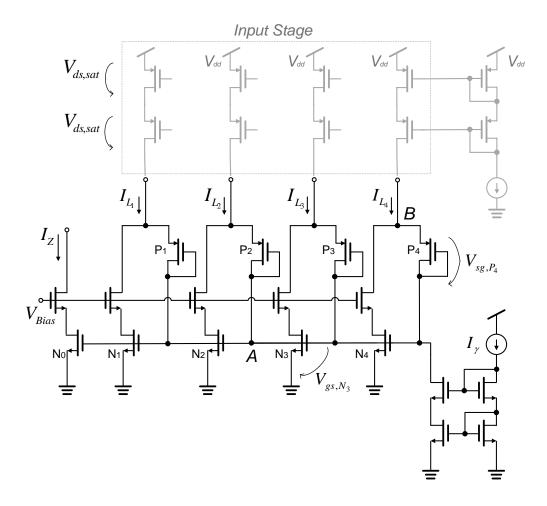

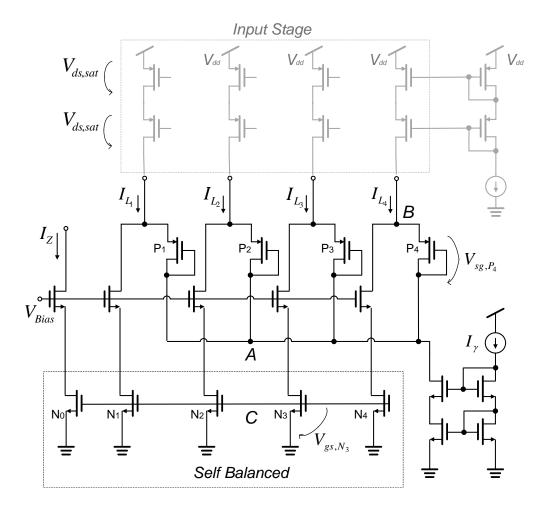

| Figure 4.2            | CMOS implementation of the core MP circuit                                                                                                     | 52       |

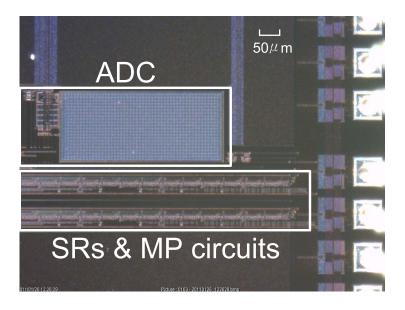

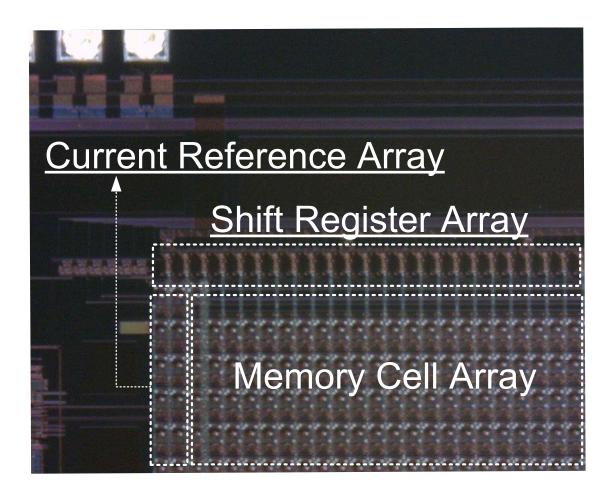

| Figure 4.3            | Die micrograph of the chip                                                                                                                     | 52       |

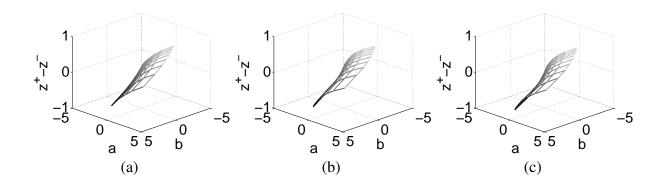

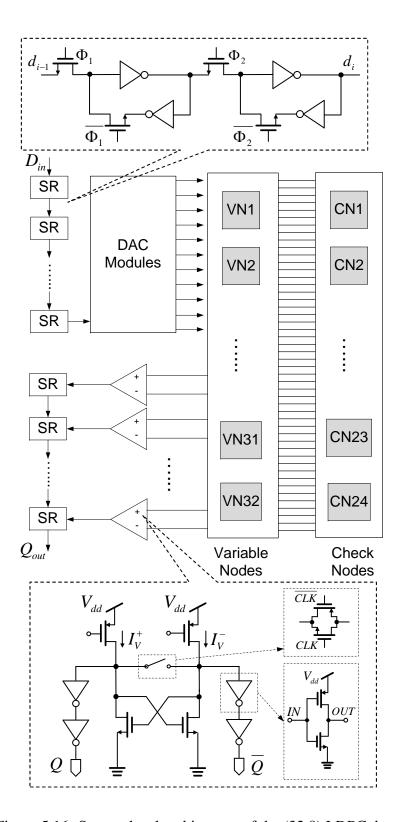

| Figure 4.4 Figure 4.5 | System architecture of the chip                                                                                                                |          |

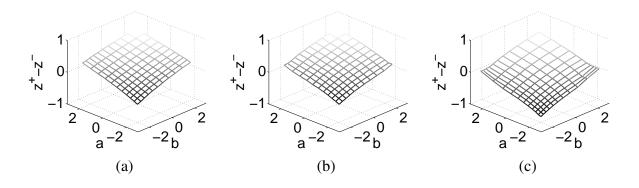

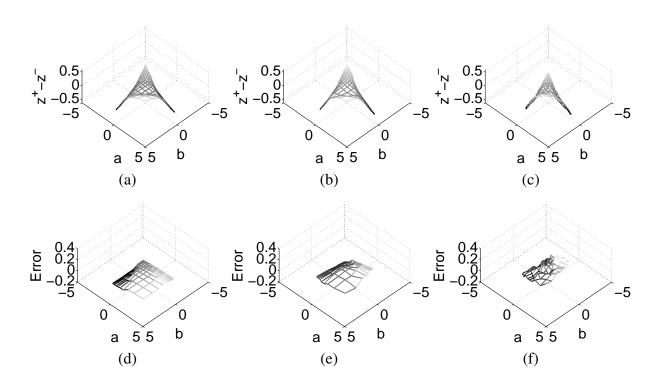

| Figure 4.6            | Addition: $z^+-z^-$ computed according to (a) the original log-sum-exp function; (b) MP approximations (simulation); and (c) MP circuits (mea- |          |

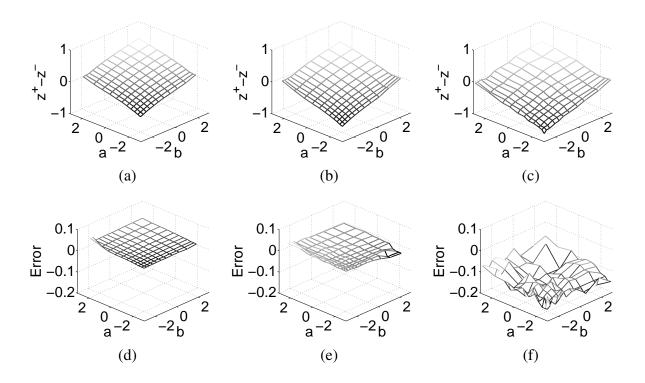

| Figure 4.7            | Surement)                                                                                                                                      | 56<br>57 |

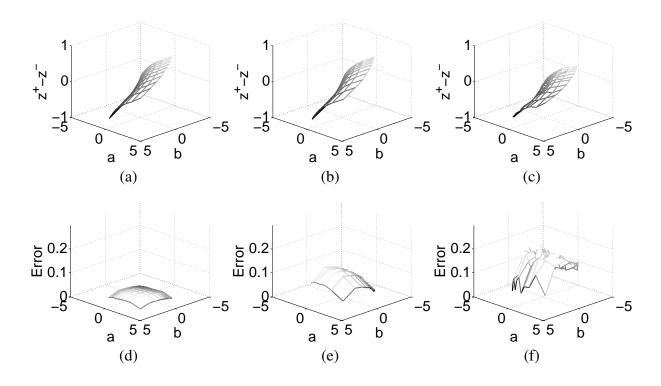

| Figure 4.8  | Subtraction: $z^+ - z^-$ computed by (a) original functions; (b) MP ap-      |    |

|-------------|------------------------------------------------------------------------------|----|

|             | proximations (simulation); and (c) MP circuits (measurement)                 | 59 |

| Figure 4.9  | Subtraction: measurement results for $z^+ - z^-$ with transistors biased in  |    |

|             | (a)strong inversion; (b)moderate inversion; (c)weak inversion; and (d)-(f)   |    |

|             | show respective approximation errors                                         | 59 |

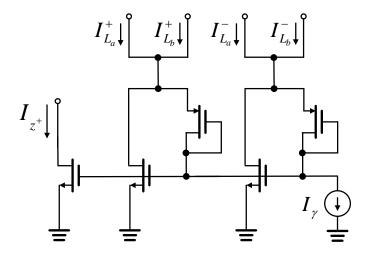

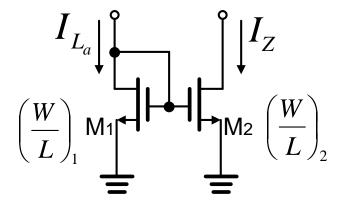

| Figure 4.10 | MP circuit for implementing four quadrant operand multiplication             | 61 |

|             |                                                                              |    |

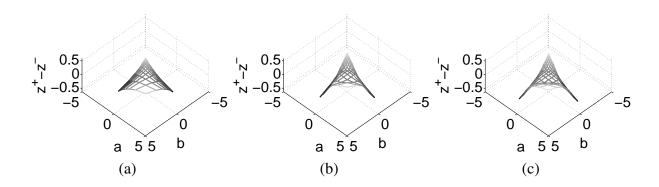

| Figure 4.11 | Multiplication: $z^+ - z^-$ computed according to the (a) original function; |    |

|             | (b) MP approximations (simulation); and (c) MP circuits (measurement).       | 61 |

| Figure 4.12 | Multiplication: measurement results for $z^+ - z^-$ with transistors biased  |    |

|             | in (a)strong inversion; (b)moderate inversion; (c)weak inversion; and (d)-   |    |

|             | (f) the respective approximation errors                                      | 62 |

| Figure 4.13 | A current mirror implementing the power function in logarithmic domain.      | 65 |

| Figure 4.14 | Power: $z^+ - z^-$ computed according to the log-sum-exp function, the       |    |

|             | MP approximation simulation and the MP circuit measurement                   | 66 |

| Figure 4.15 | Noise model for MP circuit in Fig. 4.2                                       | 66 |

| Figure 4.16 | System architecture and circuit diagram of the MP-based pattern classifier.  | 73 |

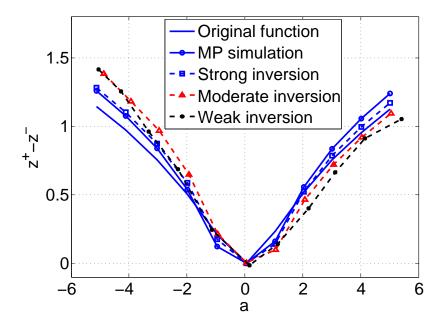

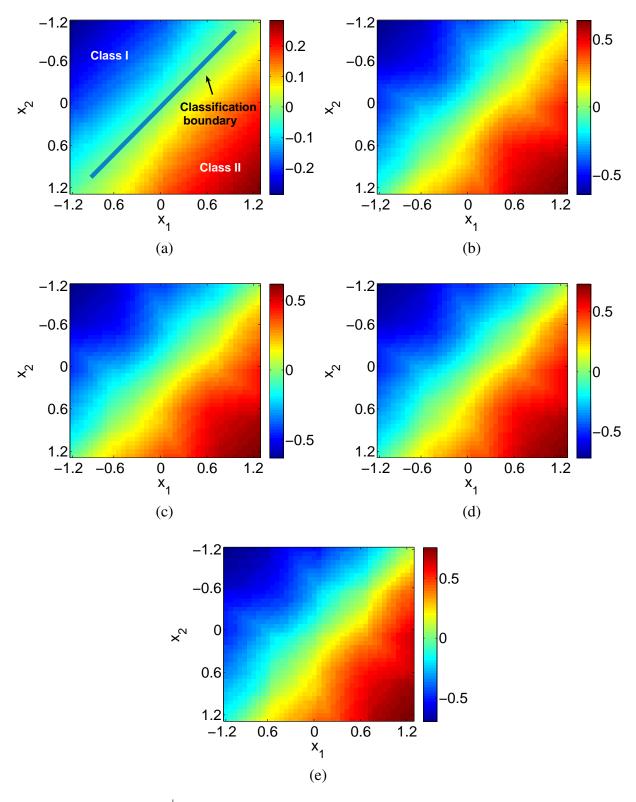

| Figure 4.17 | Classifier: $z^+ - z^-$ simulated by (a) log-sum-exp function (simulation); |    |

|-------------|-----------------------------------------------------------------------------|----|

|             | (b) MP approximation (simulation); and measured $z^+ - z^-$ when the        |    |

|             | transistors are biased in (c)strong inversion (measurement); (d)moderate    |    |

|             | inversion (measurement); (e)weak inversion (measurement)                    | 75 |

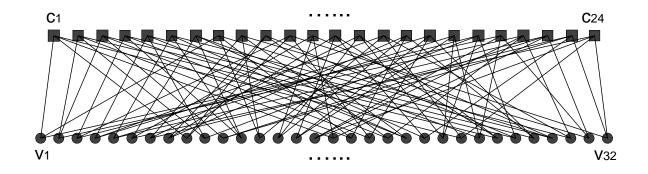

| Figure 5.1  | Factor graph corresponding to a 32-bit $(3,4)$ LDPC code $\ldots \ldots$    | 78 |

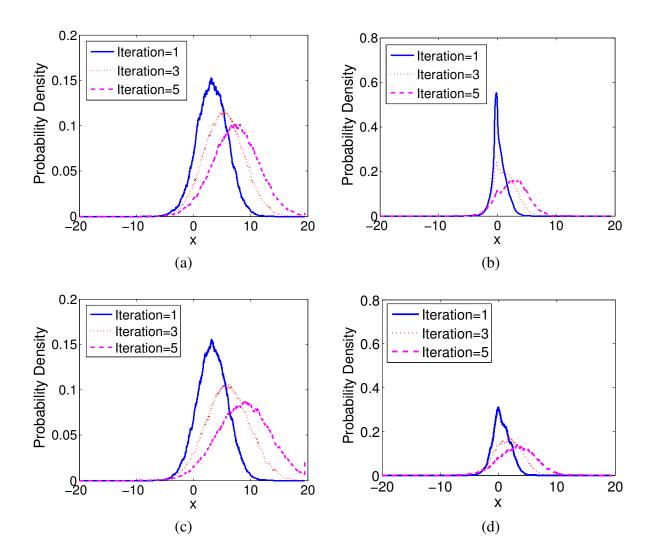

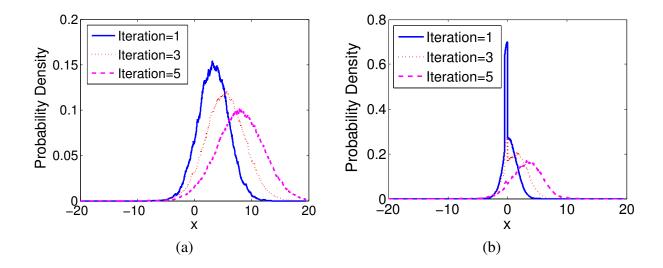

| Figure 5.2  | A (3,6) LDPC message PDF evolution for: (a) sum-product variable to         |    |

|             | check messages; (b) sum-product check to variable messages; (c) min-        |    |

|             | sum variable to check messages; (d) min-sum check to variable messages;     | 80 |

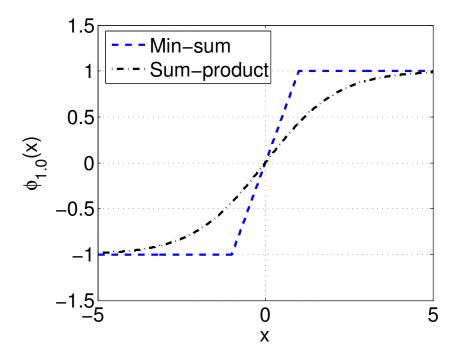

| Figure 5.3  | Comparison of pair-wise decoding functions for sum-product and min-         |    |

|             | sum LDPC decoding algorithms                                                | 85 |

| Figure 5.4  | Comparison of pair-wise decoding function for sum-product, min-sum          |    |

| Tiguic 3.4  | and margin propagation decoding algorithms                                  | 87 |

|             | and margin propagation decoding argorithms                                  | 07 |

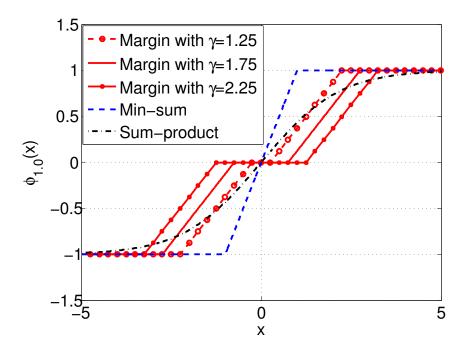

| Figure 5.5  | Comparison of 3D LDPC check function for (a) sum-product (b) min-           |    |

|             | sum and (c) margin propagation with $\gamma$ =1.75                          | 88 |

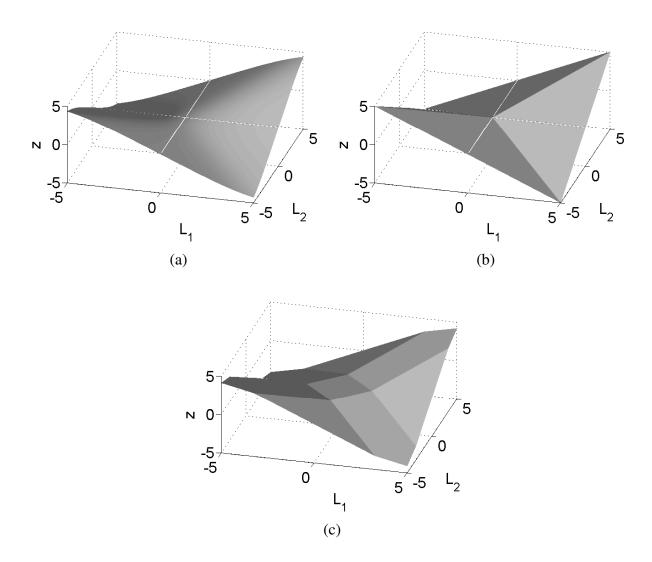

| Figure 5.6  | Possible solutions $z$ for $M(\ell_1,\ell_2)$                               | 89 |

|             |                                                                             |    |

| Figure 5.7  | A (3,6) LDPC message PDF evolution for: (a) margin propagation vari-        |    |

|             | able to check messages; (b) margin propagation check to variable messages;  | 93 |

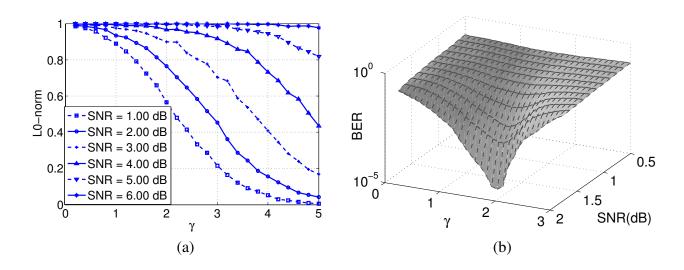

| Figure 5.8  | : (a)Effect of hyper-parameter $\gamma$ on the $L_0$ norm of the check to variable |     |

|-------------|------------------------------------------------------------------------------------|-----|

|             | messages(for different AWGN channel conditions) (b)Effect of hyper-                |     |

|             | tuning parameter $\gamma$ on BER performance (for different AWGN channel           |     |

|             | conditions)                                                                        | 97  |

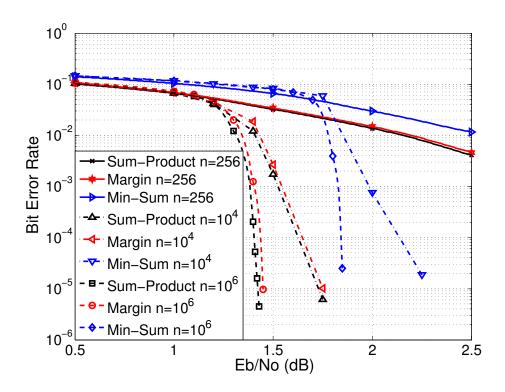

| Figure 5.9  | The comparison of BER for LDPC decoders based on different algo-                   |     |

|             | rithms achieved by (3,6)-regular LDPC code of length 256, $10^4$ , and $10^6$ ;    |     |

|             | note the maximum iteration number is set to 20                                     | 100 |

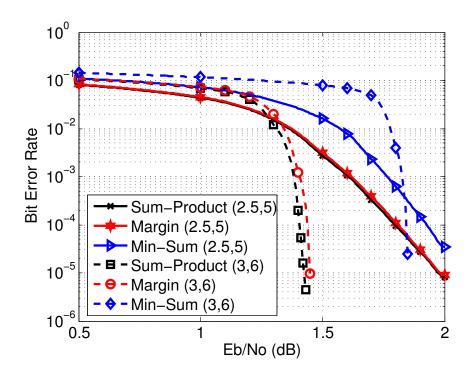

| Eigure 5 10 | The communican of DED for LDDC deceders based on different also                    |     |

| Figure 5.10 | The comparison of BER for LDPC decoders based on different algo-                   |     |

|             | rithms achieved by length $10^6$ (3,6)-regular LDPC code and (2.5,5) ir-           |     |

|             | regular LDPC code; note the maximum iteration number is set to 20                  | 101 |

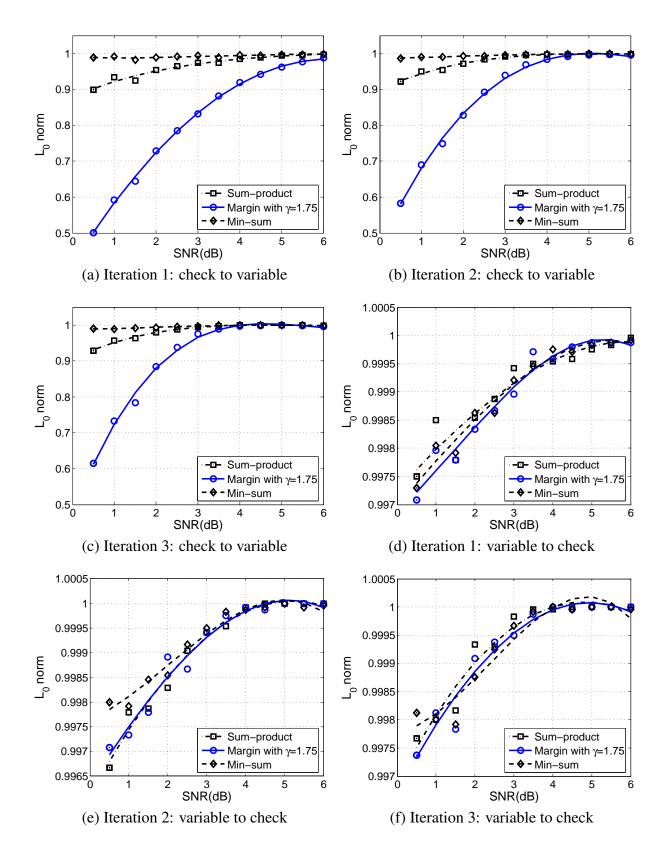

| Figure 5.11 | : $L_0$ norm comparison of sum-product, min-sum and margin propagation             |     |

|             | for iterations 1,2,3 for check to variable messages: (a),(b),(c) and variable      |     |

|             | to check messages: (d),(e),(f)                                                     | 103 |

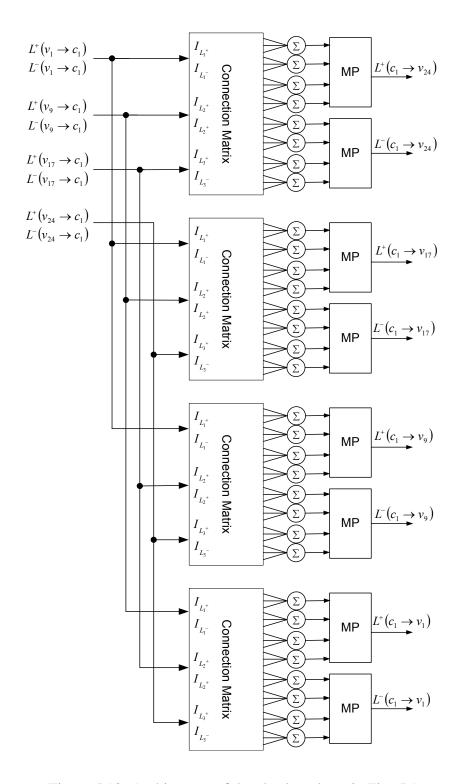

| Figure 5.12 | Architecture of the check node $c_1$ in Fig. 5.1                                   | 106 |

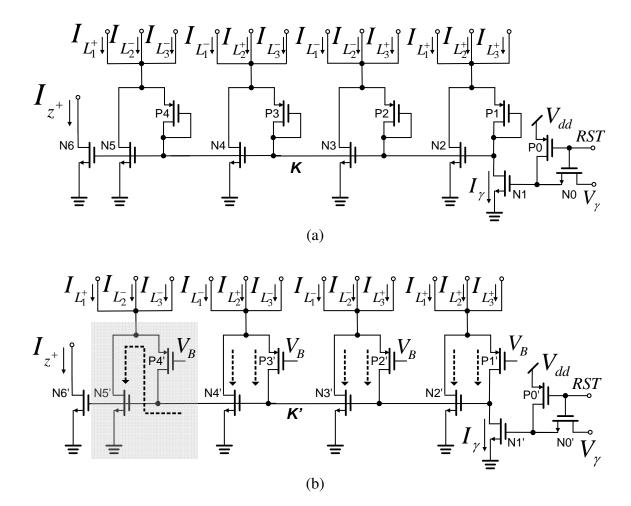

| Figure 5.13 | (a) Circuits for implementing the check node module using the MP al-               |     |

| riguic 3.13 | gorithm:(a) design used in this paper; and (b) an alternate low-voltage            |     |

|             |                                                                                    | 107 |

|             | circuit                                                                            | 107 |

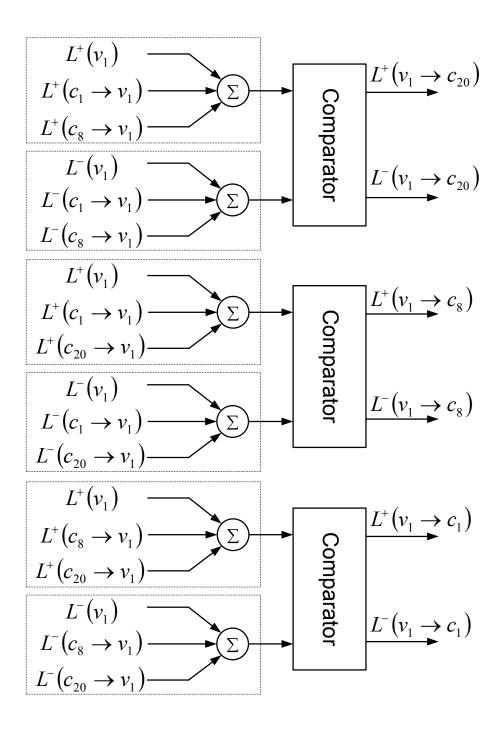

| Figure 5.14 | Architecture of variable node $v_1$ in Fig. 5.1                                    | 110 |

| Figure 5.15 | Circuit to implement variable node                                                 | 111 |

| Figure 5.16 | System level architecture of the (32,8) LDPC decoder                                                                     | 113 |

|-------------|--------------------------------------------------------------------------------------------------------------------------|-----|

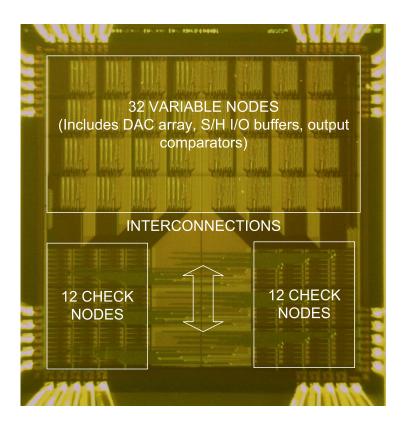

| Figure 5.17 | Die microphotograph of the chip                                                                                          | 114 |

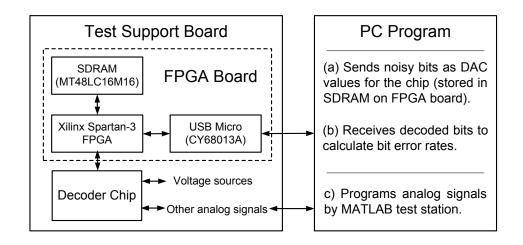

| Figure 5.18 | Experimental setup of the chip                                                                                           | 115 |

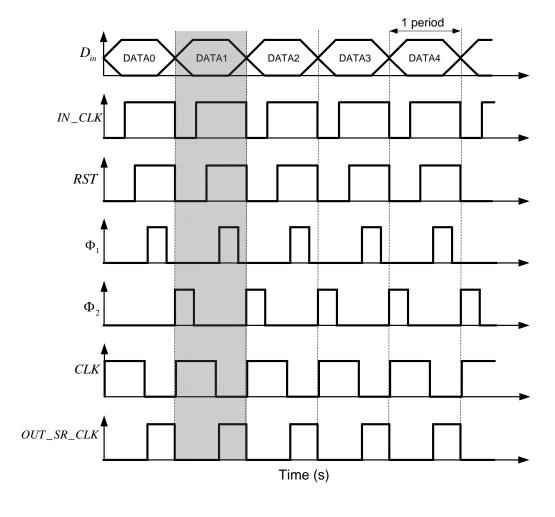

| Figure 5.19 | Timing diagram of digital signals used to control the operation of the LDPC decoder chip                                 | 115 |

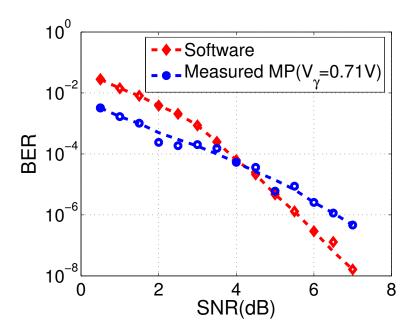

| Figure 5.20 | Comparison of BER of the MP-based LDPC decoder using software simulation and measurements from the fabricated prototypes | 116 |

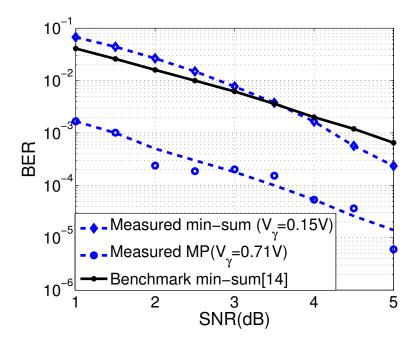

| Figure 5.21 | Comparison of BERs of the measured MP-based LDPC decoder and a benchmark min-sum LDPC decoder                            | 116 |

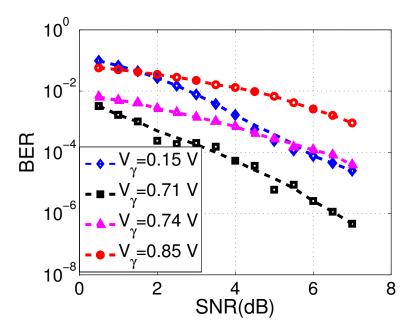

| Figure 5.22 | Comparison of measured BER performances for different values of the hyper-parameter $\gamma$                             | 117 |

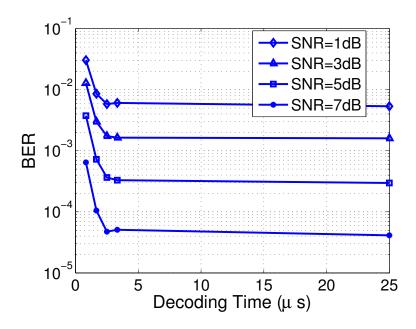

| Figure 5.23 | Measured BER performances of the MP-based LDPC decoder ( $V_{\gamma}=0.74V$ ) for different decoding times (throughput)  | 117 |

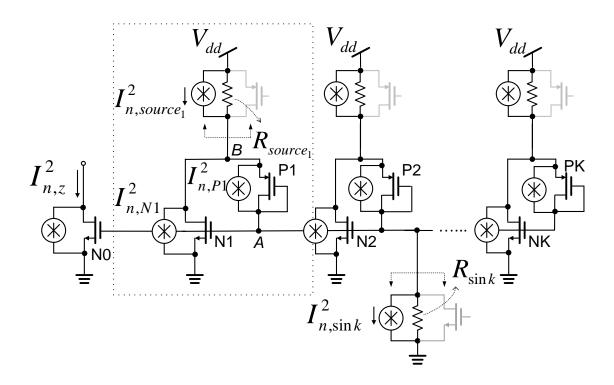

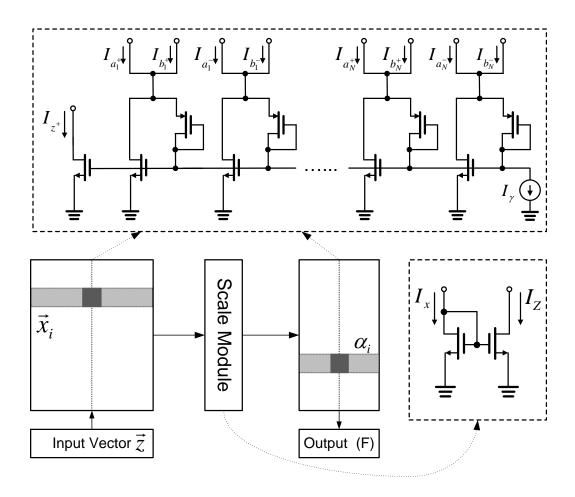

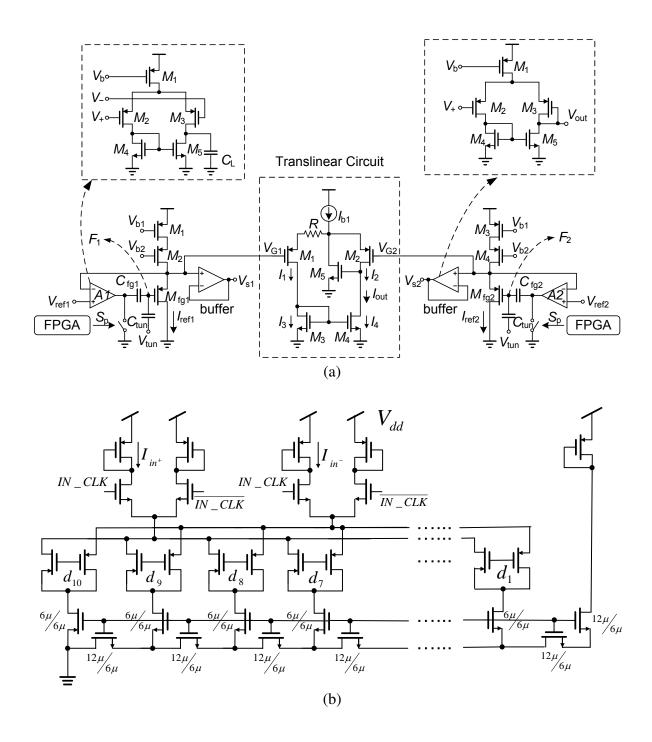

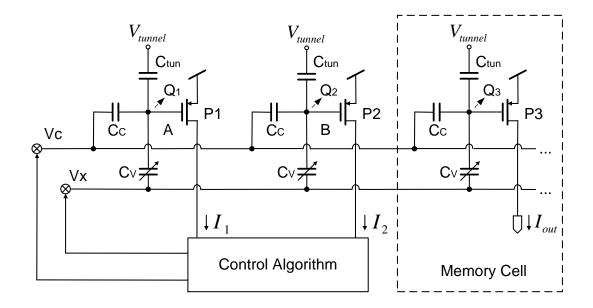

| Figure 6.1  | The circuit diagram of the MP-based SVM                                                                                  | 125 |

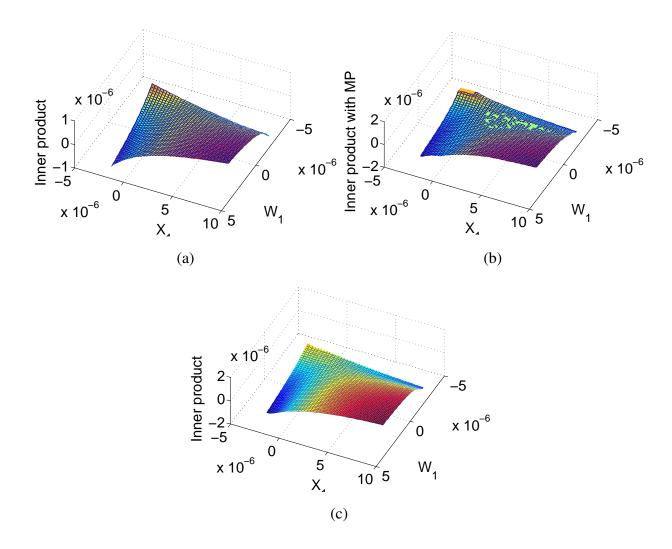

| Figure 6.2  | Multiplication computed by (a) "log-sum-exp" function (b) MP-based             |     |

|-------------|--------------------------------------------------------------------------------|-----|

|             | function with $\gamma=1.2$ (in Matlab) (c) MP-based function with $\gamma=1.2$ |     |

|             | (in Cadence)                                                                   | 127 |

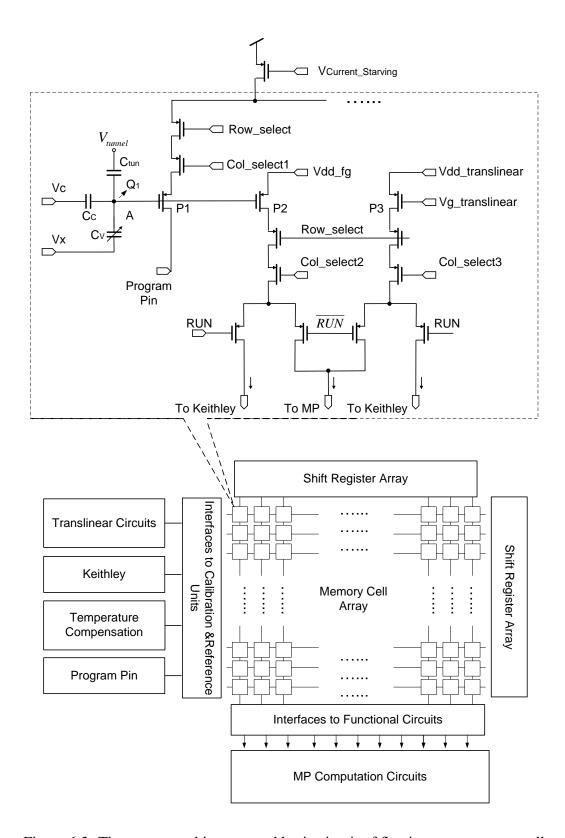

| Figure 6.3  | The system architecture and basic circuit of floating-gate memory cells.       | 130 |

|             |                                                                                |     |

| Figure 6.4  | The basic concept of translinear Ohm's law                                     | 133 |

|             |                                                                                |     |

| Figure 6.5  | Schematic of the translinear logarithmic current-to-current converter          | 134 |

|             |                                                                                |     |

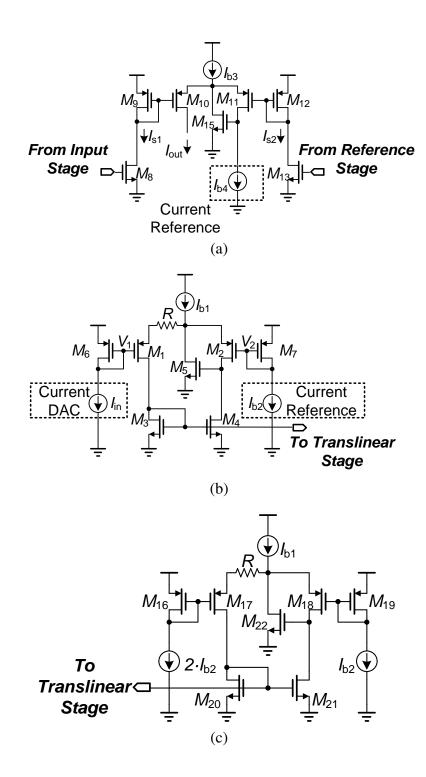

| Figure 6.6  | Proposed logarithmic amplifier: (a) basic circuit of translinear stage; (b)    |     |

|             | basic circuit of input stage; (c) basic circuit of reference stage             | 136 |

|             |                                                                                |     |

| Figure 6.7  | Basic circuit of (a) current reference; (b) current DAC                        | 138 |

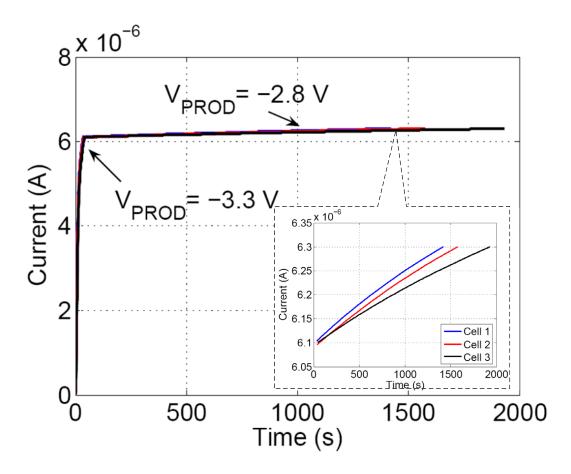

| Figure 6.8  | Proposed floating-gate based current reference and current memory cells        | 141 |

|             |                                                                                |     |

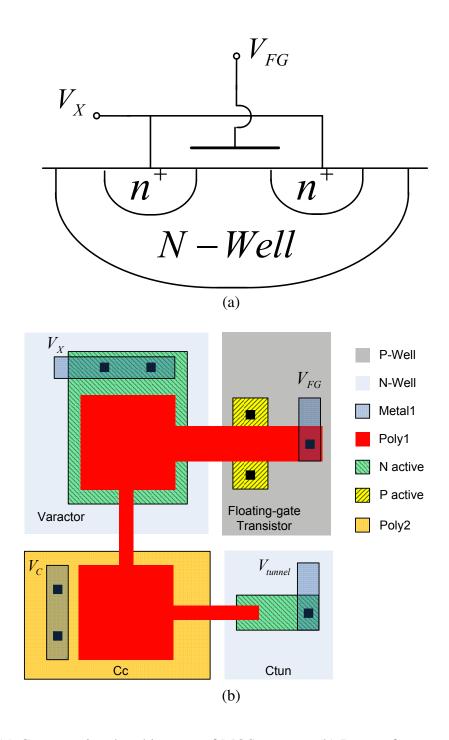

| Figure 6.9  | (a) Cross-sectional architecture of MOS varactor (b) Layout for memory         |     |

|             | cell in Fig. 6.8                                                               | 144 |

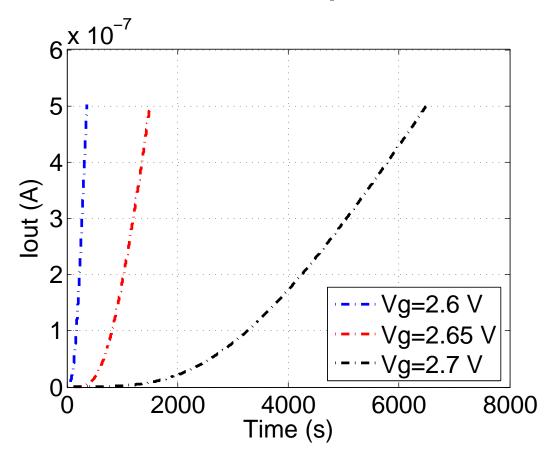

| Figure 6.10 | Floating-gate transistor current with respect to current starving voltage .    | 145 |

|             |                                                                                |     |

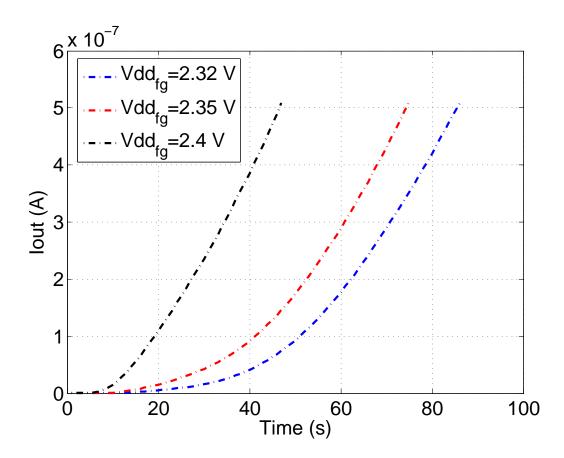

| Figure 6.11 | Floating-gate transistor current with respect to Vdd_fg                        | 146 |

|             |                                                                                |     |

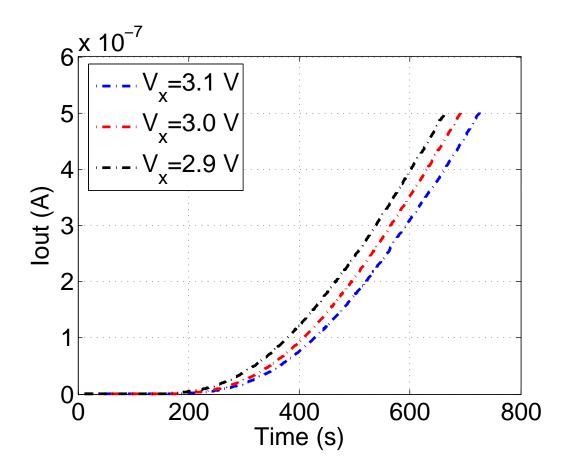

| Figure 6.12 | Floating-gate transistor current with respect to $V_{\mathcal{X}}$             | 147 |

| Figure 6.13             | Precise programming procedure for floating-gate transistors                                                                                                                                     | 148 |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

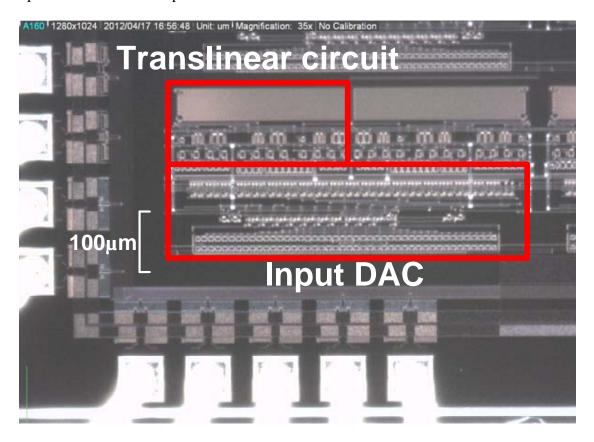

| Figure 6.14             | Die microphotograph of the chip                                                                                                                                                                 | 149 |

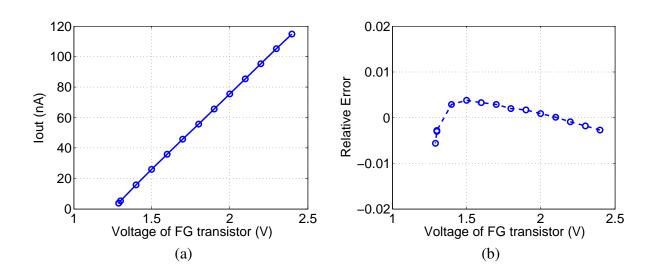

| Figure 6.15             | (a) Measurement current response and (b) relative error for the current reference                                                                                                               | 150 |

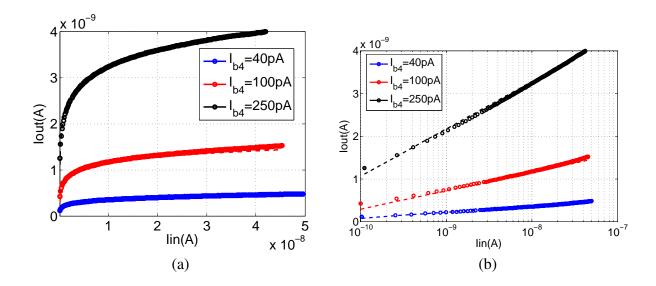

| Figure 6.16             | Measurement results for the logarithmic current conversion                                                                                                                                      | 151 |

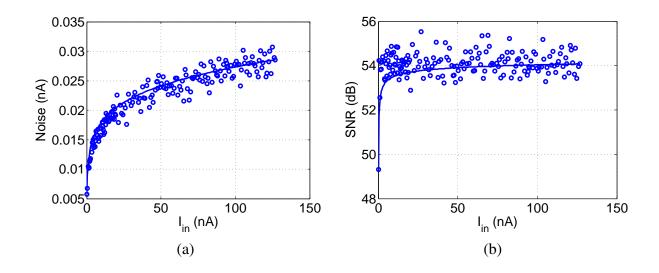

| Figure 6.17 Figure 6.18 | (a) Noise of $I_{out}$ versus $I_{in}$ ; (b) SNR of $I_{out}$                                                                                                                                   |     |

|                         |                                                                                                                                                                                                 |     |

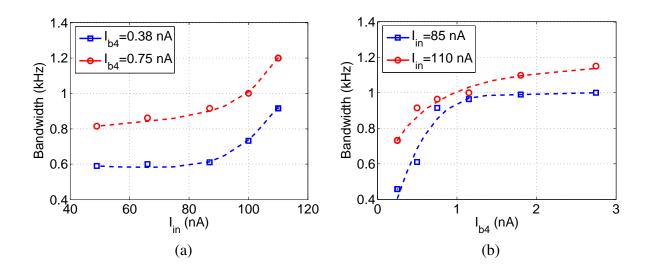

| Figure 6.19             | Measured response plotting bandwidth with respect to current                                                                                                                                    | 155 |

| Figure 6.20             | Die microphotograph of the chip                                                                                                                                                                 | 157 |

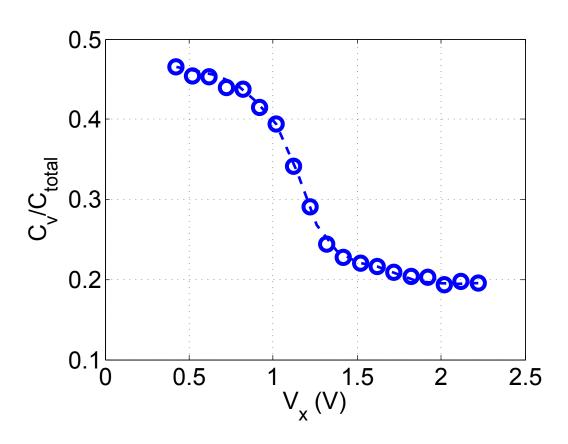

| Figure 6.21             | The C-V curve of MOS capacitor                                                                                                                                                                  | 158 |

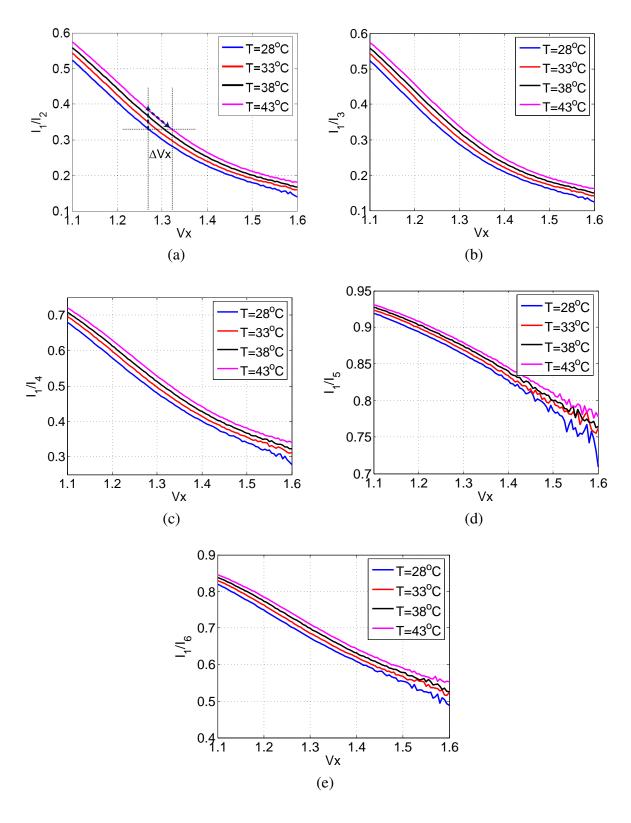

| Figure 6.22             | Measured response plotting (a) $\frac{I_1}{I_2}$ (b) $\frac{I_1}{I_3}$ (c) $\frac{I_1}{I_4}$ (d) $\frac{I_1}{I_5}$ (e) $\frac{I_1}{I_6}$ with respect to $V_x$ under 28°C, 33°C, 38°C, and 43°C | 160 |

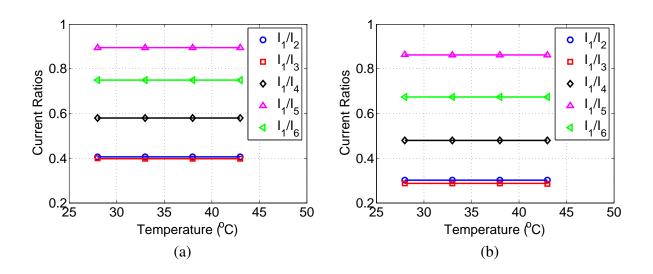

| Figure 6.23             | Measured response plotting temperature compensated current ratios under $V_x$ of (a)1.2V (b)1.3V                                                                                                | 161 |

| Figure 7.1              | Improved MP circuit with cascode current mirrors                                                                                                                                                | 165 |

| Figure 7.2  | Decoupled MP circuit to prevent gate leakage  | 166 |

|-------------|-----------------------------------------------|-----|

| 1 15u10 7.2 | Decoupled will effect to prevent gate leakage | 100 |

## Chapter 1

## Introduction

Digital signal processing (DSP) has been prevalent in all computing systems for the past five decades. Since its beginnings in early 1950's, the progress in the field of DSP has paralleled the growth of digital computers, as signified by the celebrated Moore's law [9]. The key milestones in the area of DSP include the development of the Fast Fourier Transform (FFT) in 1965 [10] followed by the implementation of DSP algorithms on integrated circuit (IC) technology in 1980's. The use of analog signal processing (ASP) can be traced back to an earlier time than its digital counterpart, primarily driven by the need to process naturally occurring signals (image, speech) which are inherently "analog". However, due to rapid progress in digital IC technology and due to the limitations imposed by analog artifacts, in 1970's analog computers were gradually superseded by digital computers. Many experts even predicted the demise of ASP in early 1980s. However, the interest in ASP was renewed a decade ago, primarily due to the need for more energy efficient and high-density signal processing systems. The inspiration for achieving this using ASP techniques came from biological computing systems which are inherently "analog". Biological neural processors excel at solving hard problems in sensory signal processing (video and speech)

by sustaining high computational throughput while keeping energy dissipation at a minimal level. At the core of these neural processors and similarly analog signal processors are massively parallel circuits which exploit computational primitives inherent in device physics to achieve high energy-efficiency and high computational density. In this dissertation, we will follow the ASP principle as a guideline to investigate energy efficient computing systems.

From a practical point-of-view there are additional advantages of ASP over DSP techniques which are listed below:

#### (a) Practical limitations in the analog-to-digital converters (ADC) design.

Since all the naturally occurring signals are analog, ADC is the essential element attached to DSP systems. Many DSP applications are required to recover signals over a wide dynamic range or from a noisy background, which necessitate high speed and high resolution ADC. However, the design of ADC for high resolution/high performance and low power dissipation is one of the challenges nowadays. It seems that the scaling factor is not affecting ADC as much as DSP efficiency. Resolution of ADCs has been increased at 1.5 bits/5 years [11]. As a consequence, the long design time of ADC has become an increasingly severe constraint for the system design as well.

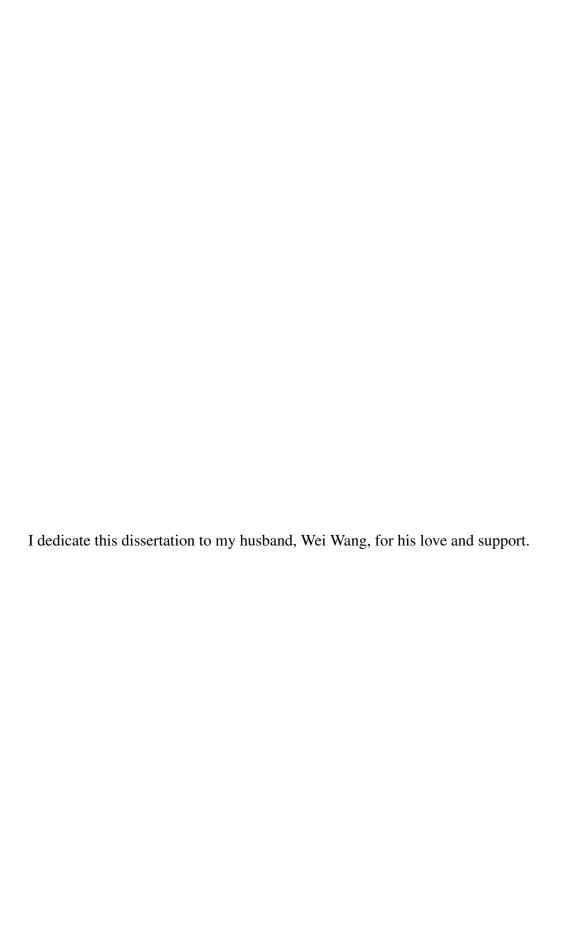

One efficient solution is the cooperative analog/digital signal processing (CADSP), proposed by Hasler in [2, 3]. By utilizing ASP at the front-end, the ADC complexity is reduced significantly, and hence the overall system complexity [2, 3]. Fig. 1.1 shows the tradeoff between CADSP and DSP.

#### (b) The limited power consumption.

Nowadays, an increasing desire for portability has been posed on electronic devices. A low power dissipation is attractive and crucial in these applications to obtain a long battery

Figure 1.1: Illustration of the tradeoffs in (a)DSP and (b)CADSP systems [2, 3]. For interpretation of the references to color in this and all other figures, the reader is referred to the electronic version of this dissertation.

life. Power consumption of DSP, measured in mW/MIPS, reduces by half around every 18 months [4]. This has been keeping pace with Moore's law [9]. Even so, a fixed power budget still constrains the increasing proliferation of portable electronics.

In contrast, ASP tends to be more power efficient. Since ASP block lacks ADC as shown in Fig. 1.1, which has been proved to be a major energy consumer, especially for the scaled-down system. Table 1.1 lists all the key elements power consumption of a state-of-the-art 0.6- $\mu$ m CMOS image sensor with mixed-signal processor array [1]. It can be seen that the power consumption of ADC is a major factor amongst all and occupies more than one-third of the total amount.

Furthermore, the arithmetic unit of DSP, which consists of digital multipliers and adders, also consumes more energy than ASP. The main cause is less number of transistors used in the case of ASP than DSP. As a consequence, even custom digital solutions are inadequate for ultralow-power applications [12].

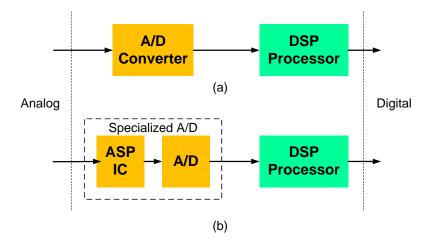

In Fig. 1.2 the power consumption of DSP and ASP are compared. The black square rep-

Table 1.1: Power dissipation of major components for a 0.6  $\mu$ m mixed-signal CMOS image sensor [1]

| Supply voltage              | 5 V     |

|-----------------------------|---------|

| Processor unit              | 0.25 mW |

| Sensor, readout and biasing | 2.25 mW |

| ADC                         | 21 mW   |

| FIFO memory                 | 83 mW   |

resents the power consumption of a state-of-the-art DSP core [5]. It seems the power consumption of the DSP core follows Gene's law. The star represents the power consumption of an analog, floating-gate integrated chip [6]. And the circuit represents the power consumption of a CMOS analog processor that can be used for long-term, self-powered mechanical usage monitoring [7].

Figure 1.2: Power consumption comparison for DSP [4, 5] and ASP [6, 7].

#### (c) Size constraints.

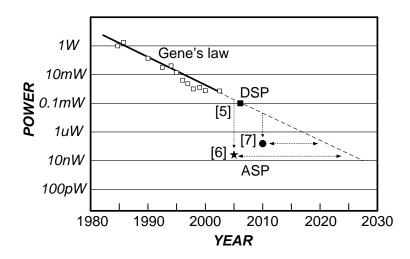

Circuit size constraints also favor analog VLSI circuits. It is often possible to perform complex operations on device physics with only a few transistors. Fig. 1.3 shows the comparison

of basic circuit schematics for digital/analog adders, and digital/analog multipliers implemented in metal-oxide-semiconductor field-effect transistors (MOSFET's). It is obvious that the number of transistors in digital implementation surpasses that in analog implementation.

Figure 1.3: Basic CMOS circuits for (a) digital half adder based on NAND and NOT gates; (b) digital multiplier based on (a); (c) analog adder; (d) analog multiplier (Gilbert cell).

#### (d) Speed requirements.

In recent years great effort has been put in real-time computation, which is applied throughout three-dimensional (3D) graphic systems, high-speed communication system, image sensors, etc.. For these applications, the defect of DSP arise largely from the fact that all the operations in a single arithmetic unit have to be carried out in sequence. In contrast, ASP has a simpler implementation and an inherent parallel architecture for computation. Thus when the signal processing has to be executed under the condition of high speed or high frequency, ASP outperforms DSP on almost all the metrics.

Although there are some crucial reasons for that ASP remains indispensable for scientific computations, there are still some problems existing for ASP. One primary disadvantage is the lack of flexibility. By directly exploiting the computational primitives inherent in the device physics, complicated non-linear functions can be implemented in analog using significantly lower number of transistors compared to its digital counterpart. However, this methodology only works for specific computations. For instance, the subthreshold translinear characteristic of MOS transistor can only be used to solve log-domain computations. Whereas DSP can be used to solve almost any computation by programming.

Another disadvantage lies in the high noise sensitivity for analog implementation. As is known, analog circuits is more vulnerable to noise than digital circuits. It can be explained as that the number in analog computation is represented by continuous voltages or currents, which will be deteriorated by noise easily. Digital system, however, due to the quantization and bi-value logic representation (either one or zero) of discrete signals, is more robust to noise. Only when the noise levels are high enough to flip logical bit, otherwise it works without any effect on precision of the result.

Also the effective resolution of the computing system is a major concern for signal processors. To evaluate the input effort to obtain a designated resolution, in [2, 13], a comprehensive metric "cost" is proposed. It is calculated based on a variety of metrics ranging from the circuit performance metrics like size, power dissipation, etc. to the human effort and other resources involved in the design or fabrication. The comparison of cost versus resolution is described as Fig. 1.4 shows. It can be seen that a "threshold" exists. When the required computation resolution is beyond the threshold, it is less "expensive" to use digital implementation, otherwise, it is more "worthy" to use analog implementation instead of digital.

Figure 1.4: Resolution versus "cost" on using ASP or DSP [2].

In summary, ASP is suitable for applications where

- precision/resolution of computation is not required strictly;

- a stringent budget for power, area, or number of transistors is imposed on the system design (e.g. image sensors);

• high-speed or fully-parallel computation is required (e.g. analog decoders);

## 1.1 Motivation for the proposed research

The underlying principle of analog computation is to represent numbers as physical quantities such as current, voltage, charge, time, etc. and then use the physics of the device for computing (e.g. addition, subtraction, multiplication, etc.). Amongst all the analog computation techniques, translinear analog signal processing (TASP) is the most widely used and the most intensively researched method. Since TASP technique was introduced by Gilbert in 1975 [14], the method has been applied for synthesis of neural, filter and radio-frequency circuits. TASP utilizes the linear relation between the transconductance and the current of the device, and can be readily implemented on MOSFETs and bipolar transistors. In Table 1.2 we summarize different variants and application of the TASP principle that has been reported in the literature:

Table 1.2: Milestones in TASP

| Year         | Device Characteristic                                         | Operation Region | Analog Computation               |  |

|--------------|---------------------------------------------------------------|------------------|----------------------------------|--|

|              | Utilized                                                      |                  | Circuits Synthesized             |  |

| Static TASP  |                                                               |                  |                                  |  |

| 1975 [14]    | $I \propto e^{V}$                                             | weak inversion   | multiplier, divider [15],        |  |

|              |                                                               |                  | maximum [16]                     |  |

| 1991 [17]    | $I \propto V^2$                                               | strong inversion | square, square-root, polynomial, |  |

|              |                                                               |                  | multiplier-divider [18]          |  |

| 2001 [19]    | $I \propto e^{(w_1 V_1 + \dots + w_N V_N)}$                   | weak inversion   | square, square-root,             |  |

|              |                                                               |                  | divider, magnitude of vector     |  |

| Dynamic TASP |                                                               |                  |                                  |  |

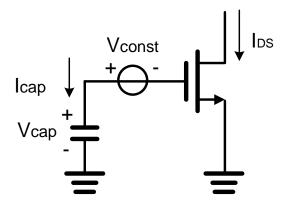

| 1979 [20]    | $CU_T I_{DS}^{} = I_{cap} I_{DS}$                             | weak inversion   | first-order filter               |  |

| 1997 [21]    | $CU_T I_{DS} = I_{cap} I_{DS}$ $CU_T I_{DS} = I_{cap} I_{DS}$ | weak inversion   | RMS-DC converting                |  |

| 1998 [22]    | $CU_T I_{DS}$ = $I_{cap} I_{DS}$                              | weak inversion   | second-order filter              |  |

The advantages of TASP circuits are as follows:

- A high functional density, which explains the extensive application of translinear circuits in neural networks.

- Insensitivity to temperature due to  $U_T$  cancellation inside the translinear loop.

- Low-power consumption due to the absence of passive components. In translinear filters implementation, only transistors and capacitors are required.

- A large dynamic range. The trend toward low supply voltages causes a decrease of the dynamic range for filters implemented with conventional circuit techniques, for which companding may be a possible solution. Whereas companding is implicitly performed in translinear filters as a consequence of the exponential behavior of the translinear devices.

- High controllability. Most parameters can be controlled by tuning the current, which is doomed by the translinear principles.

However, there are some disadvantages of TASP circuits when implemented in CMOS. To understand these disadvantages, we first briefly describe the operating regions of a MOS transistor. Fig. 1.5 shows the current-vs-gate voltage response of a typical n-type MOSFET. The characteristic consists of three different operating regions namely: (a) weak inversion: where the current is exponentially dependent on the gate voltage; (b) strong inversion: where the current is quadratically dependent on the gate voltage; and (c) moderate inversion: is the intermediate region between the strong and the weak inversion. Operating in each of these regions have specific advantages which are summarized below:

• In weak inversion region, the minimum power consumption is achieved (low  $I_D$ ).

- In strong inversion region, the higher operational speed can be obtained (high  $I_D$ , high  $g_m$ ).

- In moderate inversion region, an optimal compromise between power consumption and speed can be achieved.

The power consumption (energy-efficiency), speed trade-off can also be expressed using the "gm/ID" metric [8], where  $g_m$  is the input transconductance of the MOS transistor and  $I_D$  is the drain current flowing through the transistor. The parameter  $g_m$  effectively determines the speed of the transistor and the parameter  $I_D$  determines its power consumption.  $g_m/I_D$  is chosen as a metric since it reflects the efficiency to translate current (i.e. power) into transconductance. The greater the  $g_m/I_D$  value is, the greater the transconductance we obtain at a constant current value [8]. Fig. 1.5 displays the  $g_m/I_D$  versus the drain current  $I_D$  for MOS transistors under the three operating regions. Fig. 1.5 shows that in weak inversion region, we obtain the highest  $g_m/I_D$ , thus the best power efficiency.

As can be observed from table 1.2, TASP circuits are designed to operate in only one specific operating region. Thus it lacks flexibility, or the trade-off capability across the operation regions, which is a severe problem when a high dynamic range is required. This limits the application of TASP circuits in designing more complex and flexible analog signal processors.

To solve this problem, we propose ASP circuits that only depend on the universal conservation principles like the Kirchhoff's current law, as illustrated in Fig. 1.3 (c). By construction, ASP circuits based on universal conservation principles will have several advantages over their TASP counterparts which are:

- Independence on transistor operation regions since its underlying principle follows physical laws (e.g. universal conservation law).

- Wide dynamic range due to the unlimited operation region.

- Diverse ways of implementation (e.g. charge-mode, voltage-mode, time-mode, etc.). For instance, Fig. 1.6 illustrates how reverse water-filling can naturally be implemented using a charge-coupled device. Initially, a fixed amount of charge (shown by shaded area in Fig. 1.6a) is introduced into the charge-coupled device (CCD). As potential barriers (wells) are increased adiabatically charge re-distributes itself (Fig. 1.6b) amongst the wells. At equilibrium (Fig. 1.6c) total charge accumulated in the potential wells (residue) and the normalization level is determined by charge conservation principles. Even though potential wells have been used in the above example the procedure is applicable to other physical quantities (current, mass, energy) implemented by different analog structures (MEMS, microfluidic devices). However, since current-mode circuits is the most easy and mature way of implementation, in this dissertation, we adhere to current-mode implementation.

- Insensitivity to the outside variations (e.g. temperature).

However, the using universal conservation laws restricts the choice of computations that can be precisely implemented. That leads to the main hypothesis of this dissertation: many signal processing algorithms exhibit an inherent calibration ability, and hence their performance remains unaffected by the use of "approximate" analog computing techniques which is proposed in this study. Also, approximations at a circuit level would require a bottom-up and top-down synthesis of signal processing algorithms as is illustrated in Fig. 1.7 and is compared with the conventional top-down design flow for a TASP based synthesis. The chart in Fig. 1.7 shows that many of the approximation techniques have be simulated, verified and calibrated at the algorithmic and system level before prototyping on hardware. However, algorithmic and system levels of the design flow offers more flexibility in implementing a given system and hence can overcome performance limitations due to low-level approximations. In this dissertation, we plan to illustrate this using two

specific applications: (a) designing high-performance analog LDPC decoders; and (b) designing ultra energy-efficient analog SVM.

#### 1.2 Scientific contributions

This dissertation is motivated by improving the energy efficiency of computation implementation with ASP while resorting to the physical law to ensure bias-scalability. The major scientific contributions are listed below:

- (a) An analog signal processing (ASP) algorithm named margin propagation (MP) as an efficient piece-wise linear (PWL) approximation technique to a "log-sum-exp" function along with its current-mode analog circuit implementation is proposed. Due to its underlying principle of conservative law, MP algorithm can be mapped to various hardware easily. The current-mode MP circuit implementation is designed to be bias-scalable. This characteristic is beneficial for computational circuit since it enables the design adaptive to various applications with different specification requirements.

- (b) A wide-range of mathematical functions are synthesized with MP-based bias-scalable analog computational circuits. The synthesized functions include addition, subtraction, multiplication, division, power and polynomial computation, etc.. MP circuits operate in the log-likelihood domain where complex functions such as multiplication, division, square-root operations are mapped into simpler operations like addition, subtraction or scaling, making circuit design less complex. The circuits can operate over a wider dynamic range as the transistors can span different biasing regions.

- (c) A 100pJ/bit, (32,8) CMOS analog low-density parity-check (LDPC) decoder based on MP

is designed and implemented. One fascinating property is its capability of trading off BER performance with energy efficiency due to the tunable hyper parameter  $\gamma$  in MP algorithm. The prototyped MP-based LDPC decoder can achieve an energy efficiency of 100nJ/bit while an optimal configuration can also deliver up to 3 dB improvement in BER compared to the benchmark min-sum LDPC decoder. This design is helpful for high energy-efficiency high error-correcting performance analog LDPC decoder design.

- (d) An analog energy-scalable MP-based support vector machine (SVM) is designed and implemented. The prototype stores 2052 SVM parameters into floating-gate memory array and is fully programmable. Due to the using of MP computation circuit, the prototyped SVM is energy-scalable.

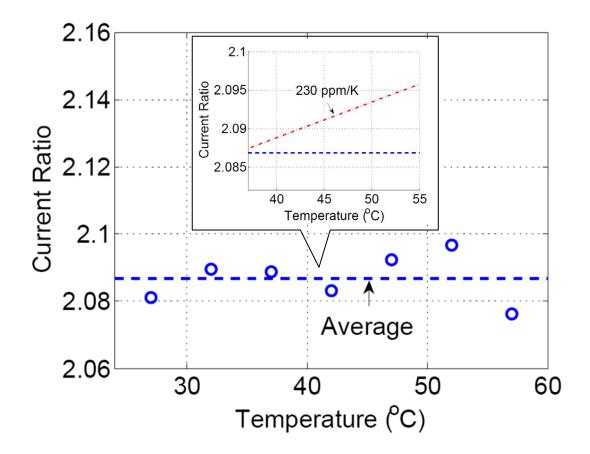

- (e) A novel current-input current-output logarithmic amplifier circuit is designed and implemented. This design based on translinear Ohm's law directly generates currents as a logarithmic function of the input current, which exhibits a dynamic range of 120dB and a temperature sensitivity of 230 ppm/K, while consuming less than 100nW of power. This design brings three major benefits for implementing logarithmic amplifier circuit: high dynamic range, low power consumption, and temperature compensation.

- (f) A novel varactor driven temperature compensation circuitry of CMOS floating-gate current memory is designed and implemented. By adapting the floating-gate capacitance with voltage controlled capacitor (varactor), this design enables temperature dependent factors be effectively canceled. With this design, a temperature sensitivity of 150 ppm/K is achieved. This design is instructive for implementing high-density, temperature compensated floating-gate current memories.

## 1.3 Dissertation Organization

The dissertation is organized as follows: Other ASP research work is briefly introduced in chapter 2. The MP algorithm related theories and properties are introduced in detail in chapter 3. The circuit implementation and synthesized analog computation circuits are introduced in chapter 4. The applications of MP-based PWL circuits are described in chapter 5 and 6.

In chapter 2, the device models of MOS transistor are introduced first as background material. Then a thorough survey of state-of-the-art research work in ASP is illustrated, i.e. a survey on translinear analog signal processing circuits.

Chapter 3 presents MP algorithm related theories. Fundamental definitions and mathematical properties of MP algorithm are illustrated first, followed by the proof that MP algorithm is a PWL approximation for "log-sum-exp" function. These definitions and properties serves as the theoretical fundamental for later chapters.

Since MP is a PWL approximation algorithm to "log-sum-exp" function, a wide variety of scientific computation can be synthesized with MP algorithm. In chapter 4, the basic current-mode circuit implementation for MP algorithm is presented. Based on the basic MP circuit block, a variety of analog computation circuits are synthesized, which include addition, subtraction, multiplication, division, power, inner-product, polynomial, and tanh. The PWL approximation effect of MP-based circuits are demonstrated by the simulation results.

Chapter 5 presents an LDPC decoder which is implemented based on the MP circuits. This chapter can be divided into theory sections and implementation sections. The theory sections starts with the metrics to evaluated the performance of LDPC decoders and a significant property of LDPC decoder: performance trade-off. Density evolution is introduced as an analytical tool and utilized to evaluate the message sparsity performance for the MP-based LDPC decoding al-

gorithm and the other two conventional algorithms. The subsequent simulation results verify the density evolution analysis results as well as the BER performance. It is also demonstrated that the trade-off capability of MP-based LDPC decoder can be realized elegantly by just tuning the hyper parameter  $\gamma$ . The implementation sections start with circuit for basic module. Then the systematic architecture is introduced. The test setup and the measurement results are presented.

Chapter 6 presents another application of the MP-based PWL circuits: an analog SVM. In this application, the inner product computation of vector, the addition, multiplication, square of scalar are all synthesized with MP-based PWL circuit. In this chapter, the core computation, the system architecture and primary circuits are introduced in sequence. Finally, the simulation results and the measurement results are demonstrated.

Chapter 7 offers conclusions and outlook.

Figure 1.5:  $log(I_D)$  versus  $V_{GS}$ ,  $g_m$  versus  $V_{GS}$ , and  $g_m/I_D$  versus  $I_D/(W/L)$  curves for various operation regions [8].

Figure 1.6: Illustration of the proposed concept for designing scalable analog computational systems. The depth of potential wells can be controlled by an external voltage source. At equilibrium the charge re-distributes amongst potential wells to satisfy charge conservation laws.

Figure 1.7: Top-down design procedure for conventional TASP and the bottom-up procedure we propose.

# Chapter 2

# **Device Models and Translinear Analog**

# **Signal Processing**

### 2.1 Device Models of MOS Transistor

Fig. 2.1 illustrates the terminals of MOS transistors. Since the model of n-type MOS and that of p-type MOS only differ in polarity definition of current flow through the devices, their mathematic models only differs in signs. Thus only NMOS transistors are discussed thereinafter.

Figure 2.1: MOS symbols

The operation of a MOSFET can be separated into three different modes, depending on the voltages at the terminals. The most frequently used models of MOSFET are for the operation in strong inversion (or called "above threshold operation") and weak inversion (or called "subthreshold conduction").

The strong inversion model is described as follows:

$$I_{DS} = \frac{\mu_n C_{ox}}{2\kappa} \frac{W}{L} [\kappa (V_G - V_T) - V_S]^2. \tag{2.1}$$

In equation (2.1), W and L denotes the width and length of transistor respectively.  $\frac{W}{L}$  is called the aspect ratio.  $\mu_n$  represents the mobility of electrons. And  $C_{ox}$  denotes the gate oxide capacitance per unit area.  $V_T$  represents the threshold voltage.  $\kappa$  is a parameter reflecting the effectiveness of the gate potential in controlling the channel current, which is always approximated as  $\kappa \simeq 1$  for strong inversion. According to (2.1), the relationship between the current flow and the voltages can be described as "square".

The weak inversion model is described as:

$$I_{DS} = I_0 e^{(1-\kappa)V_{BS}/U_T} e^{\kappa V_{GS}/U_T} (1 - e^{-V_{DS}/U_T} + V_{DS}/V_0). \tag{2.2}$$

In this equation,  $V_{GS}$  is the gate-to-source potential,  $V_{DS}$  is the drain-to-source potential,  $V_{BS}$  is the bulk-to-source potential (body effect),  $I_0$  is the zero-bias current for the given device,  $V_0$  is the early voltage, and  $U_T$  is the thermodynamic voltage. For devices in subthreshold saturation, which is determined by  $V_{DS} \geq 4U_T$ , neglecting the early effect and the body effect, equation

#### (2.2) can be simplified as

$$I_{DS} = I_0 e^{\kappa V} GS/UT. (2.3)$$

According to (2.3), the current is the exponential of the potential. Also we can deduce the input transconductance in subthreshold saturation region as:

$$g_{m} = \frac{\partial I_{DS}}{\partial V_{GS}} = \frac{\kappa I_{DS}}{U_{T}}.$$

(2.4)

And the output transconductance in subthreshold saturation region as:

$$g_d = \frac{\partial I_{DS}}{\partial V_{DS}} = \frac{I_{DS}}{V_0}. (2.5)$$

It can be seen that  $g_m$  and  $g_d$  are linear to the current  $I_{DS}$  in this operation region.

There is no uniform model for MOSFET throughout all the operation regions until it was developed by C. C. Enz, F. Krummenacher and E. A. Vittoz. Enz-Krummenacher-Vittoz in 1995, named as EKV model. With EKV model, all the currents, transconductance, the intrinsic capacitance, and thermal noise can be expressed in a continuous way in all operation regions, including weak inversion, moderate inversion, strong inversion, conduction, and saturation. The equation of EKV model is described as

$$I_{DS} = I_{S}log^{2} \left[ 1 + e^{(\kappa(V_{G} - V_{T}) - V_{S})/2U_{T}} \right] - I_{S}log^{2} \left[ 1 + e^{(\kappa(V_{G} - V_{T}) - V_{D})/2U_{T}} \right]. \tag{2.6}$$

In this equation,  $I_S$  is a specific current, which depends essentially on the aspect ratio  $\frac{W}{L}$  and the

mobility  $\mu_n$ .

## 2.2 Translinear Analog Signal Processing

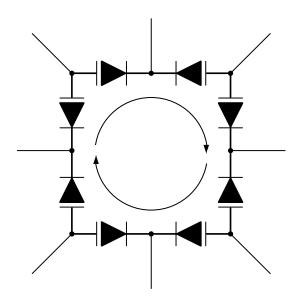

Figure 2.2: An alternating translinear loop of NMOS transistors. Here the number of clockwise facing transistors in junction is the same as the number of counterclockwise facing transistors.

The translinear principle was defined by Gilbert in 1975 [14], originally with bipolar transistors. In translinear circuits, the exponential current-voltage characteristic of bipolar transistor is exploited. With the emergence of MOSFET circuit, translinear principle is extended into MOS circuits, since MOS transistors in subthreshold region also have the exponential current-voltage non-linearity characteristic, as shown in (2.3). The translinear principle states that, in a closed loop of tranlinear devices comprising an equal number of of clockwise facing and counterclockwise facing junction devices, their currents follows:

$$\prod_{j \in CW} \frac{I_j}{S_j} = \prod_{j \in CCW} \frac{I_j}{S_j},\tag{2.7}$$

where CW and CCW denote the set of junction transistors clockwise facing and counterclockwise facing respectively.  $I_j$  denotes the  $I_{DS}$  of the transistor. S denotes the aspect ratio, i.e. W/L ratio of the transistor. Fig. 2.2 shows a conceptual alternating translinear loop comprising NMOS transistors.

Note that the translinear principle is derived by Kirchhoff's voltage law for the loop, which is:

$$\sum_{j \in CW} V_{GS(j)} = \sum_{j \in CCW} V_{GS(j)}, \tag{2.8}$$

In 1991, the translinear principle was extended by Seevinck and Wiegerink [17]. They generalized the translinear principle with the statement that the transconductance of a device is linear in the controlling voltage rather than it being linear in the current, as Gilbert intended originally. In this generalized translinear principle, the square-law MOS characteristic, as we show in equation (2.1), is exploited. Correspondingly, the MOS transistors in a translinear loop they presented were biased in strong inversion. And their translinear principle takes the form as

$$\sum_{j \in CW} \sqrt{\frac{I_j}{S_j}} = \sum_{j \in CCW} \sqrt{\frac{I_j}{S_j}}.$$

(2.9)

This generalized translinear principle is suggested to be renamed as voltage-translinear circuits to prevent possible confusion [23].

However, there is no translinear principle describing the behavior of translinear loops when any of the transistors enters the moderate inversion region, where the device is in neither weak inversion nor strong inversion, but in between. In this region, the current-voltage characteristic follows neither the exponential form as shown in equation (2.3) nor the square-law form as described in equation (2.1).

The EKV model, which is described in (2.6), provides a model for the current-voltage characteristics of the MOS transistor at all levels of inversion including moderate inversion. In 2008, Minch brought out a generalized translinear principle for alternating loops of saturated MOS transistors that is valid at all levels of inversion based on the EKV model [24]. This generalized translinear principle reduces to the conventional one when all transistors in a translinear loop are biased in weak inversion and reduces to the voltage-translinear principle when all transistors in the loop are biased in strong inversion. They model the current-voltage characteristic of an NMOS transistor with its bulk tied to ground as:

$$I_{sat} = SI_S log^2 (1 + e^{(\kappa (V_G - V_{T0}) - V_S)/2U_T}), \tag{2.10}$$

where S=W/L denotes the aspect ratio,  $\kappa=C_{ox}/(C_{ox}+C_{dep})$  denotes the subthreshold slope factor,  $V_{T0}$  denotes the zero-bias threshold voltage,  $U_T=kT/q$  denotes the thermal voltage, and  $I_S=2\mu_nC_{ox}U_T^2/\kappa$  denotes the transistor's specific current. Based on this equation it is explicitly to deduce

$$\kappa(V_G - V_{T0}) - V_S = 2U_T log(e^{\sqrt{I_{sat}/SI_S}} - 1).$$

(2.11)

When the transistor is in weak inversion, by expanding  $e^{\sqrt{I_{sat}/SI_{S}}}$  in a Maclaurin series and retaining the constant and linear terms, we obtain the approximation as

$$\kappa(V_G - V_{T0}) - V_S \approx U_T log \frac{I_{sat}}{SI_S}.$$

(2.12)

When the transistor is in strong inversion, -1 is negligible compared to  $e^{\sqrt{I_{sat}/SI_S}}$ , therefore

we can obtain

$$\kappa(V_G - V_{T0}) - V_S \approx 2U_T \sqrt{\frac{I_{sat}}{SI_S}}.$$

(2.13)

Based on equation (2.12) and (2.13), we can derive translinear principle on weak inversion, shown in (2.9), and voltage-translinear principle on strong inversion, shown in (2.10). And the continuous moderate inversion model is obtained on equation (2.11) as well.

Based on these aforementioned translinear principles, continuous-time translinear analog signal processing (TASP) systems are constructed. TASP circuits can be divided into two major classes: static translinear circuits and dynamic translinear circuits.

Static translinear circuits exploit the exponential relation between voltage and current to realize static linear and nonlinear transfer functions, such as products, quotients, arbitrary fixed power laws, etc. [15, 25, 18, 26]. With such operations, we can implement signal-processing algorithms involving auto-correlation, cross-correlation, signal energy computation, least-mean-square (LMS) error metric computation, and the like [23, 25]. For instance, the Gilbert multiplier [15] shown in Fig. 1.3 (d) is a static translinear circuit. For the circuit of Fig. 1.3 (d):

$$I_1^+ = \frac{I_b}{1 + e^{-(V_1^+ - V_1^-)/U_T}}, \ I_1^- = \frac{I_b}{1 + e^{(V_1^+ - V_1^-)/U_T}}$$

(2.14)

$$I_{2}^{+} = \frac{I_{1}^{+}}{1 + e^{-(V_{2}^{+} - V_{2}^{-})/U_{T}}}, \ I_{2}^{-} = \frac{I_{1}^{+}}{1 + e^{(V_{2}^{+} - V_{2}^{-})/U_{T}}}$$

(2.15)

$$I_3^+ = \frac{I_1^-}{1 + e^{(V_2^+ - V_2^-)/U_T}}, \ I_3^- = \frac{I_1^-}{1 + e^{-(V_2^+ - V_2^-)/U_T}}$$

(2.16)

If we denote  $(V_1^+ - V_1^-)/U_T = x$ ,  $(V_2^+ - V_2^-)/U_T = y$ , we can obtain

$$I_{out}^{+} = I_{2}^{+} + I_{3}^{+} = I_{b} \frac{e^{x}e^{y} + 1}{(e^{x} + 1)(e^{y} + 1)}$$

(2.17)

$$I_{out}^{-} = I_{2}^{-} + I_{3}^{-} = I_{b} \frac{e^{x} + e^{y}}{(e^{x} + 1)(e^{y} + 1)}$$

(2.18)

Thus,

$$I_{out}^{+} - I_{out}^{-} = I_b tanh(\frac{x}{2}) tanh(\frac{y}{2})$$

$$(2.19)$$

By tailor series expression, here we take  $tanh(z) \approx z$ . Then

$$I_{out} \approx I_b \cdot \frac{x}{2} \cdot \frac{y}{2} \tag{2.20}$$

$$\propto x \cdot y.$$

(2.21)

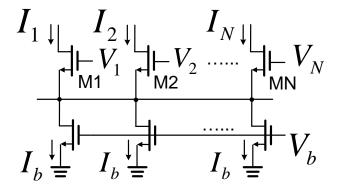

Another example of static translinear circuit is "winner-take-all" circuit, which can be used to find out the maximum amongst a couple of inputs [16]. A voltage-in-current-out winner-take-all circuit is shown in Fig. 2.3. In this circuit, current flow through each branch follows:

$$I_{i} = \frac{e^{\kappa V_{i}/U_{T}}}{\sum_{j=1}^{N} e^{\kappa V_{j}/U_{T}}} \cdot N \cdot I_{b}$$

(2.22)

Due to the fast decay of exponential, at equilibrium, the branch with the maximum voltage takes all the currents and the other branch obtains currents which decays gradually to zero. Consequently, the winner (maximum) is easy to pick out.

There is also an increasing effort to develop new circuit design techniques in order to build

Figure 2.3: A voltage-in-current-out winner-take-all circuit.

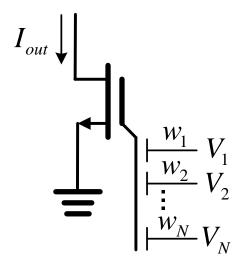

analog information-processing systems. In 2001, Minch proposed multiple-input translinear element (MITE) networks [19], which produces an output current that is exponential in a weighted sum of its input voltages. MITEs are simply implemented using multiple-input floating gate MOS (FGMOS) transistors. An MITE is shown in Fig. 2.4. The output current  $I_{out}$  follows:

Figure 2.4: A multiple-input translinear element (MITE).

$$I_{out} \propto e^{(w_1 V_1 + w_2 V_2 + \dots + w_N V_N)}$$

(2.23)

From equation (2.23) it can be seen that if these weights are adjusted according to some learning algorithm, such as the least-mean-square (LMS) algorithm or the recursive least-squares (RLS) algorithm, these built-in weights can be used to implement a variety of linear adaptive signal-processing architectures. In this respect, TASP circuits are also applied into neural systems [27, 28, 29, 30]. Furthermore, these weights can be programmed in a digital fashion to realize reconfigurability in TASP systems. Such reconfigurable analog signal processing systems are called field-programmable analog arrays (FPAAs) [6]. This kind of TASP FPAA is analogous to an  $E^2PROM$ -based field programmable gate arrays (FPGA) in digital domain.

Based on MITEs, a variety of static and dynamic translinear circuits can be synthesized (e.g. the vector-magnitude circuit, the vector-normalization circuit, the second-order low-pass filter, and the rms-to-dc converter) [19, 31, 32, 26].

By admitting capacitors in the translinear loops, the dynamic translinear circuits are constructed to deal with frequency dependent transfer functions. The dynamic translinear principle can be explained with reference to the circuit shown in Fig.2.5. The expression for  $I_{cap}$  is easily found

Figure 2.5: Principle of dynamic translinear circuits.

to be

$$I_{cap} = CU_T \frac{\dot{I_{DS}}}{I_{DS}}, \tag{2.24}$$

which shows that  $I_{cap}$  is a nonlinear function of  $I_{DS}$  and its time derivative  $I_{DS}^{\dot{}}$ . Equation (2.24) can be rewritten as

$$CU_T I_{DS}^{\dot{}} = I_{cap} I_{DS}, \tag{2.25}$$

which states the dynamic translinear principle: A time derivative of a current can be mapped onto a product of currents [33].

The first dynamic translinear circuit, or log-domain filter, was originally introduced by Adams in 1979 [20]. The first-order filter described in [20] is in fact a translinear circuit. Another milestone is a general class of filters, called exponential state-space filters, which comprise a number of translinear loops, first published by Frey [34]. The exponential state-space filters enables the design of higher order log-domain filters[35, 36]. Since then the interest of dynamic translinear filter increases dramatically. More studies were reported in this area [37, 38, 39, 40, 41, 42].

However, the dynamic translinear principle is not limited to filters, or linear differential equations. It also can be utilized to realize nonlinear differential equations using transistors and capacitors only. In [21], the nonlinear differential equations describing the rms-dc conversion function are implemented on the dynamic translinear principle. Another example is [22], in which a translinear second-order oscillator was implemented. Some other example functions described by nonlinear differential equations and implemented by translinear circuits are phase-locked loops (PLL's) [43], translinear sinusoidal frequency tripler [44], etc..

## Chapter 3

# Theory of PWL technique based on margin propagation

## 3.1 Definition of MP algorithm

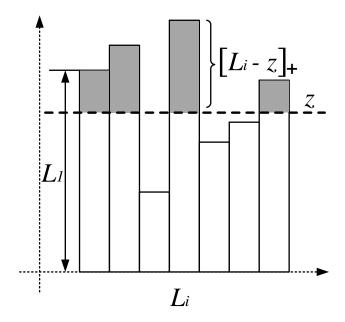

At the core of MP algorithm is the reverse water-filling procedure, which has been described in detail in [45, 46]. Given a set of scores  $L_i \in \mathbb{R}, i=1,...,N$ , reverse water-filling computes a normalization factor z according to the constraint:

$$\sum_{i=1}^{N} [L_i - z]_+ = \gamma \tag{3.1}$$

where  $[\cdot]_+=max(\cdot,0)$  denotes a rectification operation and  $\gamma\geq 0$  represents a parameter of the algorithm. Computation of z according to constraint (3.1) is summarized in the Algorithm 1. The algorithm recursively computes the factor z such that the net balance of log-likelihood scores  $L_i$  in excess of z equals  $\gamma$ .

The solution to equation (3.1) can also be visualized using Figure 3.1, where the cumulative

#### **Algorithm 1** Reverse water-filling procedure to compute the parameter z

```

Require: Set of log-likelihood scores \{L_i\}, i=1,..,N.

Ensure: z=0, N=1, T=0

a=max\{L_i\}

\{s\}\leftarrow\{L_i\}-\{a\}

while T<\gamma & m< N do

b=max\{s\}

T\leftarrow T+M(a-b)

a\leftarrow b

\{s\}\leftarrow\{s\}-\{b\}

m\leftarrow m+1

end while

z\leftarrow b+M(\gamma-T)

```

score beyond the normalization factor z (shown by the shaded area) equals to  $\gamma$ . To be practical, we always limit z in the range of  $z \leq \max_i L_i$ . The computation of z can be expressed as an equivalent function  $M(\mathcal{L}, \gamma)$  whose inputs are a set of log-likelihood scores  $\mathcal{L} = \{L_i\}, i = 1, ..., N$  of size N and a hyper-parameter  $\gamma$ :

$$z^{mp} = M(\mathcal{L}, \gamma). \tag{3.2}$$

## 3.2 Properties of MP algorithm

In this section we present some of the key properties of MP function  $M(\mathcal{L}, \gamma)$ . Since margin approximation uses thresholds  $[x]_+ = \max(x, 0)$ , we first state two lemmas which will be useful for proving some of the other properties.

**Lemma 1:**  $\forall a, b \in R$ ,

$$[a]_{+} - [b]_{+} \le [a - b]_{+}.$$

Figure 3.1: Illustration of reverse water-filling procedure

Lemma 2:  $\forall a, b \in R$ ,

$$[a]_+ + [b]_+ \le [a+b]_+.$$

The proof of **Lemma 1** and **Lemma 2** is straightforward and can be found in any standard analysis textbook. For the sake of brevity, only the statement and the illustration of some of the properties are presented in this section and all the proofs have been presented in detail in the appendix.

**Property 1 (Scaling Property):** For any  $\alpha \in R$ ,  $\alpha > 0$  and a set of scores  $\mathcal{L} = \{L_i\}, i = 1,...,N$

$$M(\alpha \mathcal{L}, \alpha \gamma) = \alpha M(\mathcal{L}, \gamma).$$

(3.3)

Here  $\alpha \mathcal{L} = \{\alpha L_i\}, i=1,..,N$ . The proof of this property is simple since if the condition

$$\sum_{i=1}^{N} [L_i - z]_+ = \gamma$$

is satisfied, then the following condition

$$\sum_{i=1}^{N} [\alpha L_i - \alpha z]_+ = \alpha \gamma$$

is also satisfied. Figure 3.2 illustrates the scaling property of margin approximation function, where the threshold z scales with the scaling of the log-likelihood scores and the hyper-parameter  $\gamma$ .

Figure 3.2: Scaling property of margin propagation

**Property 2 (Monotonicity):** Given a set of scores  $\mathcal{L}=\{L_i\}, i=1,..,N$  and if  $\gamma_1 \geq \gamma_2 \geq 0$  then

$$\mathit{M}(\mathcal{L},\gamma_1) \leq \mathit{M}(\mathcal{L},\gamma_2)$$

One of the important implications of the monotonicity is the asymptotic property when  $\gamma \to 0$  and is given by

$$\lim_{\gamma \to 0} M(\mathcal{L}, \gamma) = \max(\mathcal{L}). \tag{3.4}$$

The importance of this asymptotic property is that the min-sum algorithm for LDPC decoding is a special case of the proposed margin propagation algorithm.

Proof. Given

$$\begin{cases}

\sum_{i=1}^{N} [L_i - z_1]_+ = \gamma_1, \\

\sum_{i=1}^{N} [L_i - z_2]_+ = \gamma_2, \\

\gamma_1 \ge \gamma_2 \ge 0,

\end{cases} (3.5)$$

what we need to prove is

$$z_1 \leq z_2$$

.

If we subtract the first equation by the second equation in (3.5), we can get

$$\sum_{i=1}^{N} ([L_i - z_1]_+ - [L_i - z_2]_+) = \gamma_1 - \gamma_2 \ge 0.$$

(3.6)

Based on Lemma 1,

$$\sum_{i=1}^{N} [z_2 - z_1]_{+} \ge \sum_{i=1}^{N} ([L_i - z_1]_{+} - [L_i - z_2]_{+}).$$

Combined with (3.6), it can be deduced that

$$\sum_{i=1}^{N} [z_2 - z_1]_+ \ge 0.$$

Consequently,

$$z_2 - z_1 \ge 0.$$

In conclusion,

$$z_1 \leq z_2$$

.

**Property 3 (Convexity Property):** Given a set of coefficients  $\{\alpha_k\}$  satisfying  $0 \le \alpha_k \le 1$  and  $\sum_k \alpha_k = 1$  and given a set of hyper-parameters  $\{\gamma_k\}$

$$M(\mathcal{L}, \sum_{k} \alpha_k \gamma_k) \ge \sum_{k} \alpha_k M(\mathcal{L}, \gamma_k).$$

*Proof.* Given the same group of  $L_i$ s, and a set of  $\gamma_k, k=1,..,n$

$$\begin{cases}

\sum_{i=1}^{N} [L_i - z_1]_{+} = \gamma_1, \\

\sum_{i=1}^{N} [L_i - z_2]_{+} = \gamma_2, \\

\vdots \\

\sum_{i=1}^{N} [L_i - z_n]_{+} = \gamma_n,

\end{cases} (3.7)$$

Based on Property 1, we can transform the equations in (3.7) as

$$\begin{cases} \sum_{i=1}^{N} [\alpha_{1}L_{i} - \alpha_{1}z_{1}]_{+} = \alpha_{1}\gamma_{1}, \\ \sum_{i=1}^{N} [\alpha_{2}L_{i} - \alpha_{2}z_{2}]_{+} = \alpha_{2}\gamma_{2}, \\ \vdots \\ \sum_{i=1}^{N} [\alpha_{n}L_{i} - \alpha_{n}z_{n}]_{+} = \alpha_{n}\gamma_{n}, \end{cases}$$

Add the above equations up, based on Lemma 2, we will get

$$\sum_{i=1}^{N} \left[ L_i - \sum_{k=1}^{n} \alpha_k z_k \right]_{+} \ge \sum_{k=1}^{n} \alpha_k \gamma_k.$$

Denote z' satisfies

$$\sum_{i=1}^{N} \left[ L_i - z' \right]_{+} = \sum_{k=1}^{n} \alpha_k \gamma_k.$$

Based on Property 1, then  $z' \ge \sum_{k=1}^n \alpha_k z_k$ .

That is,

$$\mathit{M}(\mathcal{L}, \sum_{k} \alpha_{k} \gamma_{k}) \geq \sum_{k} \alpha_{k} \mathit{M}(\mathcal{L}, \gamma_{k}).$$

**Property 4 (Superposition Property):** Given two sets of scores  $\mathcal{L}$  and  $\mathcal{G}$  of size N with a well defined ordering and if  $\mathcal{L} + \mathcal{G}$  represent an element by element scalar addition then

$$M(\mathcal{L} + \mathcal{G}, \gamma) \leq M(\mathcal{L}, \gamma) + M(\mathcal{G}, \gamma).$$

Proof.

$$\begin{cases} \sum_{i=1}^{N} [L_i - z_1]_+ = \gamma, \\ \sum_{i=1}^{N} [g_i - z_2]_+ = \gamma, \end{cases}$$

(3.8)

what we need to prove is if

$$\sum_{i=1}^{N} [L_i + g_i - z_3]_+ = \gamma, \tag{3.9}$$

then

$$z_3 \le z_1 + z_2$$

.

All the  $L_i$ s are sorted and rearranged in a decreasing order so that  $L_1' \geq L_2' \geq L_3' \ldots \geq L_N'$ . We use  $N_1$  to represent the number of  $L_i'$ s above the threshold  $z_1$ . The same operations are done to  $g_i$ s. All the  $g_i$ s are sorted and rearranged decreasingly as  $g_1' \geq g_2' \geq g_3' \ldots \geq g_N'$ . And the number of  $g_i'$ s above the threshold  $z_2$  is  $N_2$ .

Rewrite (3.8) as

$$\begin{cases}

\sum_{i=1}^{N_1} L_i' - N_1 z_1 = \gamma, \\

\sum_{i=1}^{N_2} g_i' - N_2 z_2 = \gamma,

\end{cases}$$

(3.10)

Assume  $N_2 \ge N_1$ , then from the bottom equation in (3.10), we get

$$0 \le \sum_{i=1}^{N_1} g_i' - N_1 z_2 \le \gamma. \tag{3.11}$$

Add both sides of (3.11) to those of the upper equation in (3.10), we can get

$$\gamma \le \sum_{i=1}^{N_1} L_i' + \sum_{i=1}^{N_1} g_i' - N_1 z_1 - N_1 z_2 \le 2\gamma.$$

(3.12)

(3.12) can be transformed as

$$\sum_{i=1}^{N_1} [L_i' + g_i' - (z_1 + z_2)] \ge \gamma,$$

from which we can deduce that

$$\sum_{i=1}^{N} [L_i + g_i - (z_1 + z_2)]_+ \ge \gamma, \tag{3.13}$$

Given (3.9) and (3.13), based on Property 2, it can be deduced that

$$z_3 \le z_1 + z_2$$

.

And vice versa if we assume  $N_1 \ge N_2$ . If written in MP function,

$$M(\mathcal{L} + \mathcal{G}, \gamma) \leq M(\mathcal{L}, \gamma) + M(\mathcal{G}, \gamma).$$

Under special condition the above property reduces to an equality and is given by **Property 5**(Offset Invariance): Given a set of scores  $\mathcal{L}$  of size N and a scalar  $g \in \mathcal{R}$  then

$$M(\mathcal{L} + g, \gamma) = M(\mathcal{L}, \gamma) + g.$$

Property 5 implies that if a constant offset to all the elements of input set leads to an equivalent offset in the output of the margin approximation function.

*Proof.* Based on the proof of Property 4, given

$$\sum_{i=1}^{N} [L_i - z]_+ = \gamma,$$

if  $\mathcal G$  is a scalar set with each  $g_i=g,g\in\mathcal R$ , 3.9 can be rewritten as

$$\sum_{i=1}^{N} [L_i + g - (z+g)]_{+} = \gamma,$$

Written in MP function format,

$$M(\mathcal{L} + g, \gamma) = M(\mathcal{L}, \gamma) + g.$$

**Property 6 (Invariance Property):** Given a set of scores  $\mathcal L$  of size N, and given a set of scores  $\mathcal G$  whose elements satisfy  $g_i \leq M(\mathcal L, \gamma), i=1,...,N$ , then

$$M(\mathcal{L}\bigcup \mathcal{G}, \gamma) = M(\mathcal{L}, \gamma).$$

Proof. Given

$$\sum_{i=1}^{N} [L_i - z]_+ = \gamma,$$

$\forall g_j, j \in [1, n], \text{ since } g_j \ll z,$

$$\sum_{j=1}^{n} [g_j - z]_{+} = 0$$

which means

$$\sum_{i=1}^{N} [L_i - z]_+ + \sum_{i=1}^{n} [g_j - z]_+ = \gamma.$$

Therefore, we can get

$$M(\mathcal{L}\bigcup\mathcal{G},\gamma)=M(\mathcal{L},\gamma).$$

# 3.3 PWL approximation based on MP algorithm

The generalized form of a "log-sum-exp" function is described as

$$z_{log} = \log\left(\sum_{i=1}^{N} e^{L_i}\right). \tag{3.14}$$

The Piecewise-linear (PWL) approximation of "log-sum-exp" function can be achieved with MP algorithm.

*Proof.* Assume that (3.14) and (3.2) share the same group of operands  $L_1, \ldots, L_N, L_i \in R, i = 1, \ldots, N$ . If the operands are sorted and rearranged in a decreasing order as  $L_1' \geq L_2' \ldots \geq L_N'$ , (3.14) can be rewritten as

$$z_{log} = \log\left(\sum_{i=1}^{N} e^{L_i'}\right),\tag{3.15}$$

For MP algorithm, (3.2) is rewritten as

$$z = M(L'_1, \dots, L'_N, \gamma).$$

(3.16)

If the number of  $L_i'$ s above threshold z is n,  $1 \le n \le N$ , according to the definition of MP

algorithm, (3.1) is rewritten as

$$\sum_{i=1}^{n} \left( L_i' - z \right) = \gamma,$$

$$\sum_{i=1}^{n} L_i' - nz = \gamma.$$

(3.17)

And z can be deduced as

$$z = \frac{\sum_{i=1}^{n} L_i'}{n} - \frac{\gamma}{n}.$$

(3.18)

For (3.18), under the conditions (a)  $\gamma$  and all the other  $L_i'$ s are fixed except  $L_n'$  (b)  $L_n'$  is varying within the range not below the threshold z, we have

$$\frac{\partial z}{\partial L_n'} = \frac{1}{n}. (3.19)$$

For  $z_{log}$  in (3.15), under the same conditions (a) and (b),

$$\frac{\partial z_{log}}{\partial L'_n} = \frac{e^{L'_n}}{\sum_{i=1}^N e^{L'_i}} = \frac{1}{\sum_{i=1}^N e^{(L'_i - L'_n)}}.$$

(3.20)

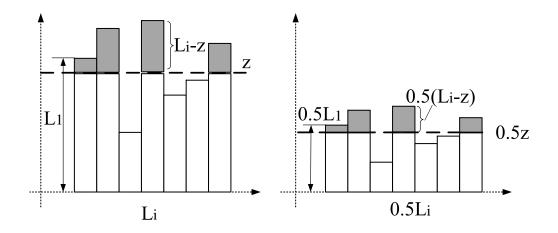

Define a function  $u(L_i', L_n')$  to approximate  $e^{(L_i' - L_n')}$  as

$$u(L'_{i}, L'_{n}) = \begin{cases} 1, & L'_{i} \ge L'_{n}, \\ 0, & L'_{i} < L'_{n}, \end{cases} \quad 1 \le n \le N.$$

Fig. 3.3 shows us the curve of  $u(L_i', L_n')$  and its PWL approximating effect to that of  $e^{(L_i' - L_n')}$ .

Figure 3.3: The curve of  $e^{(L_i^{\prime}-L_n^{\prime})}$  and its PWL approximation curve of  $u(L_i^{\prime},L_n^{\prime})$

Since the number of  $L'_i$ 's not less than  $L'_n$  is n, then

$$\sum_{i=1}^{N} u(L_i', L_n') = \sum_{i=1}^{n} u(L_i', L_n') = n.$$

(3.21)

Therefore,

$$\frac{\partial z_{log}}{\partial L'_n} \approx \frac{1}{\sum_{i=1}^N u(L'_i, L'_n)} = \frac{1}{n}.$$

(3.22)

Comparing (3.19) and (3.22), we can find out that