# ON THE DESIGN OF SWITCHED-CAPACITOR CONVERTERS FOR LOW POWER APPLICATIONS

By

Yaqub Alhussain Mahnashi

#### A DISSERTATION

Submitted to Michigan State University in partial fulfillment of the requirements for the degree of

Electrical Engineering — Doctor of Philosophy

2018

#### ABSTRACT

#### ON THE DESIGN OF SWITCHED-CAPACITOR CONVERTERS FOR LOW POWER APPLICATIONS

#### By

#### Yaqub Alhussain Mahnashi

Power conversion is crucial to most electronic systems due to different voltage levels requirement within the system. Switched-capacitor converters are a subset of switching mode converters, where the energy is transferred from the input to the output using only capacitors and switches. SC converters provide compact solution due to its magnetic-less structure, which makes them ideal to fulfill the high density requirement in low power applications. In literature, Dickson SC converter is considered a good candidate for low power applications compared to other SC topologies. Yet, Fibonacci SC (FSC) topology can be competitive due to their minimum area requirement and relatively good efficiency performance. In addition, FSC provides the highest voltage-conversion-ratio (VCR) using the least number of components, and hence can be useful in high gain applications. Therefore, the main goal of this dissertation is to introduce FSC as a viable solution for low power applications. This dissertation contributes in three domains: (1) SC theory, (2) FSC synthesis and (3) FSC design and implementation.

For the first part, the well-known SC fundamental limit theory, proposed in 1995 by Mark S. Makowski et al, is revisited. This theory sets the VCR boundaries for a specific number of k flying capacitors in a SC converter. Although this limit is valid for the positive VCR, we found that another condition must be satisfied for the negative VCR. As a result, we propose a generalized version of the theory to overcome these limitations, which establishes the foundation for the rest of the work in this dissertation. Second part of the dissertation

explores the FSC synthesis problem. In fact, synthesizing nonlinear SC converters like FSC to achieve certain/multiple VCR is not trivial, and usually performed using ad-hoc approach. Therefore, an efficient algorithm to address the SC synthesis problem is proposed, which is made available as an open-source tool, called *FSC Synthesizer*, to promote the use of FSC. The proposed tool is verified by implementing FSC converter that achieves four VCRs.

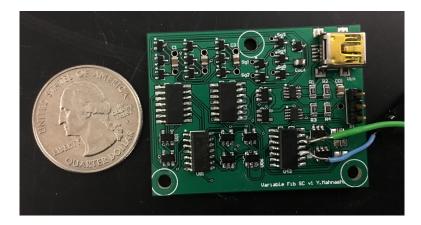

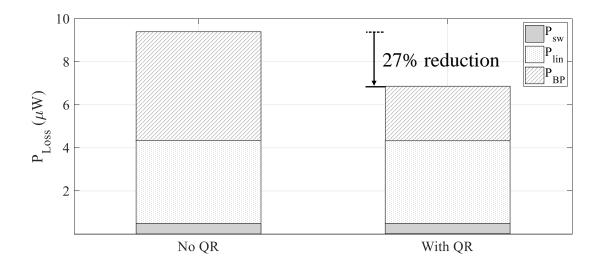

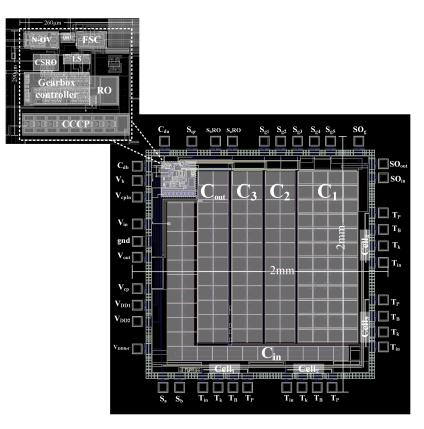

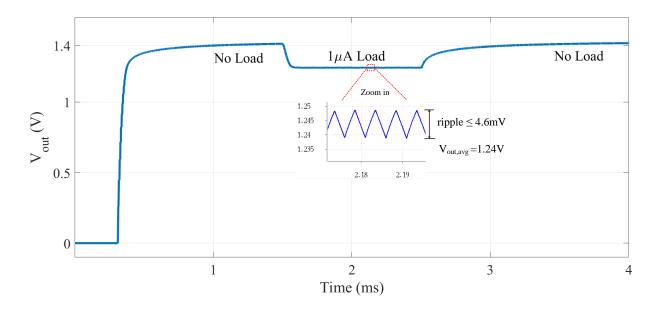

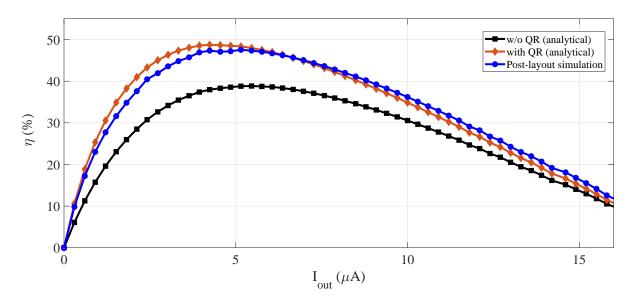

Finally, the design procedure and analysis of a variable FSC converter is investigated in both, discrete and on-chip implementation. For the first part, discrete FSC design is studied, and a prototype for a variable FSC is built and tested. The PCB occupies an area of 2.7inch<sup>2</sup>, which includes the controller and FSC. The adaptive VCR technique is employed to regulate the output voltage. For 300-600mV input voltage, the proposed converter provides a mean output voltage of almost 1.46V with a 2.67% discrepancy from 1.5V nominal designed voltage. For the second part, the on-chip integration challenges including parasitic charge loss and start-up from low voltage, are studied. A charge recycling technique exploiting the presence of parasitic capacitors in each other phase of FSC converter has been employed resulting in 27% reduction in the power loss, which improves the overall efficiency by 12.7%. For a proof-of-concept, a monolithic FSC is implemented in  $0.5\mu$ m CMOS technology on 4mm<sup>2</sup> die area. The post-layout simulation is carried out using Virtuoso ADE. With 0.3V input voltage, the system achieves 47.5% peak power efficiency with 5 $\mu$ W load. Copyright by YAQUB ALHUSSAIN MAHNASHI 2018 This dissertation is dedicated to the memory of my beloved father, Alhussain Mahnashi, who always believed in his son. Rest in peace, father...

#### ACKNOWLEDGMENTS

I would like to take this opportunity to express my sincere appreciation for all the support and encouragement that have led to the completion of this dissertation. I am greatly indebted to my advisor, Prof. Fang Z. Peng, for his continuous support, help and encouragement throughout my PhD studies at Michigan State University.

I would also like to thank Prof. Bingsen Wang, Prof. Wen Li, and Prof. Chunqi Qian for serving on my committee. I am deeply grateful to them for their valuable comments and insightful discussions. I owe a sincere acknowledgment to Saudi Arabia government through King Fahd University of Petroleum and Minerals to grant me a prestigious scholarship to peruse my PhD studies.

Special thanks go to my colleagues in the Power Electronics and Motor Drives Lab: Dr. Shuitao Yang, Dr. Gujing Han, Dr.Wei Qian, Deepak Gunasekaran, Ujjwal Karki, Hulong Zeng, Xiaorui Wang, Yunting Liu, Allan Taylor, Nomar Gozález-Santini, Omar Aljawhari and Petros Taskas, for making my stay at Michigan State University more enjoyable, and for their insightful and helpful academic inputs.

I am greatly grateful to my family and friends for their tremendous support and encouragement. My profound gratitude is to my mother for her endless love, prayers and support. I could not be more grateful to my beloved wife and sons, Yusuf and Albara. This dissertation would not have been accomplished without their love, care, patience and support. Thank you all for making this dream a reality.

## TABLE OF CONTENTS

| LIST ( | DF TABLES                                              |

|--------|--------------------------------------------------------|

| LIST ( | DF FIGURES                                             |

| KEY 7  | TO ABBREVIATIONS                                       |

| Chapte | er 1 Introduction                                      |

| 1.1    | Overview                                               |

| 1.2    | A Brief History on SC Development                      |

| 1.3    | Research Scope and Contributions                       |

| 1.4    | Report Organization                                    |

| Chapte | er 2 SC Converter Fundamental Theory                   |

| 2.1    | Introduction                                           |

| 2.2    | General SC Fundamental Limit                           |

| 2.3    | MIMO SC converter                                      |

| 2.4    | Summary                                                |

|        |                                                        |

| Chapte |                                                        |

| 3.1    | Related Work                                           |

| 3.2    | Proposed FSC Synthesis                                 |

| 3.3    | Case Study and Results                                 |

|        | 3.3.1 FSC Converter with VCR= $30$                     |

|        | 3.3.2 Variable FSC Converter with VCR= $5, 4, 3, 5/2$  |

|        | 3.3.3 Variable FSC Converter with VCR=1, $3/4$ , $2/3$ |

| 3.4    | Summary                                                |

| Chapte | er 4 Reconfigurable FSC Converter: Discrete Design     |

| 4.1    | Theoretical Analysis                                   |

|        | 4.1.1 Converter Equivalent Resistance                  |

|        | 4.1.2 Power Loss Analysis                              |

|        | 4.1.3 Output Regulation Methods                        |

| 4.2    | Converter Design                                       |

|        | 4.2.1 Power Loss Calculation                           |

|        | 4.2.2 Components Selection                             |

|        | 4.2.3 Control Circuit                                  |

| 4.3    | Results                                                |

| 4.4    | Summary                                                |

| Chapte                                                                  | er 5 Integrated FSC Converter                                               | 56                               |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------|

| 5.1                                                                     | On-chip Devices                                                             | 56                               |

|                                                                         | 5.1.1 Switch Implementation                                                 | 57                               |

|                                                                         | 5.1.2 IC Solar Cells                                                        | 60                               |

|                                                                         | 5.1.3 IC Capacitors                                                         | 61                               |

| 5.2                                                                     | IC FSC challenges                                                           | 63                               |

|                                                                         | 5.2.1 Startup Mechanism                                                     | 63                               |

|                                                                         | 5.2.2 Parasitic Capacitor                                                   | 65                               |

| 5.3                                                                     | IC FSC Converter Analysis                                                   | 67                               |

|                                                                         | 5.3.1 Die Area Analysis                                                     | 67                               |

|                                                                         | 5.3.2 Power Loss Analysis                                                   | 68                               |

| 5.4                                                                     | IC FSC Converter Design                                                     | 69                               |

| 5.5                                                                     | Summary                                                                     | 74                               |

|                                                                         |                                                                             |                                  |

| Chapte                                                                  | er 6 Analog and Digital Circuit Design                                      | 75                               |

| Chapte<br>6.1                                                           |                                                                             | <b>75</b><br>76                  |

| -                                                                       | Cross-Coupled Charge Pump Design                                            |                                  |

| 6.1                                                                     | Cross-Coupled Charge Pump Design                                            | 76                               |

| 6.1<br>6.2                                                              | Cross-Coupled Charge Pump Design                                            | 76<br>79                         |

| 6.1<br>6.2<br>6.3                                                       | Cross-Coupled Charge Pump Design                                            | 76<br>79<br>82                   |

| $ \begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \end{array} $               | Cross-Coupled Charge Pump Design                                            | 76<br>79<br>82<br>88             |

| $ \begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \end{array} $        | Cross-Coupled Charge Pump Design                                            | 76<br>79<br>82<br>88<br>89       |

| $ \begin{array}{c} 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ 6.6 \end{array} $ | Cross-Coupled Charge Pump Design       ************************************ | 76<br>79<br>82<br>88<br>89<br>93 |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>Chapte                        | Cross-Coupled Charge Pump Design                                            | 76<br>79<br>82<br>88<br>89<br>93 |

## LIST OF TABLES

| Table 3.1: | All possible realizations for FSC with VCR= $5/3$                              | 22 |

|------------|--------------------------------------------------------------------------------|----|

| Table 3.2: | Comparison of SC converter synthesis techniques                                | 23 |

| Table 3.3: | All possible realizations for VCR= $30/1$                                      | 28 |

| Table 3.4: | Optimized realization for variable FSC with VCR=5, 4, 3, $5/2$                 | 30 |

| Table 3.5: | LUT for converter synthesized by proposed method $\ldots \ldots \ldots \ldots$ | 31 |

| Table 3.6: | LUT for converter in $[21]$                                                    | 33 |

| Table 4.1: | Variable FSC converter design specifications                                   | 44 |

| Table 4.2: | Different chimerical switches with their specifications                        | 49 |

| Table 4.3: | LUT for variable FSC converter                                                 | 52 |

| Table 5.1: | Ambient sources.                                                               | 64 |

| Table 5.2: | C5 technology parameters                                                       | 71 |

| Table 6.1: | Truth table for N-T DFF.                                                       | 86 |

| Table 6.2: | IC pin configurations                                                          | 90 |

| Table 6.3: | Performance Comparison with SC converters in the literature                    | 95 |

## LIST OF FIGURES

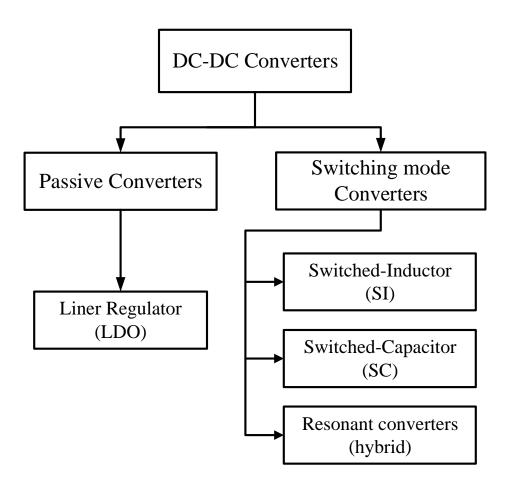

| Figure 1.1: | Types of DC-DC converters.                                                                                           | 2  |

|-------------|----------------------------------------------------------------------------------------------------------------------|----|

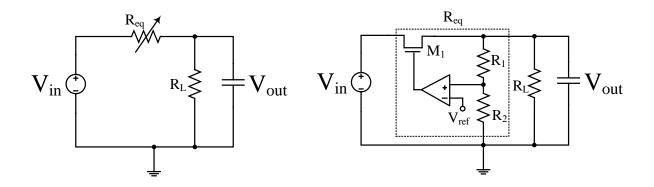

| Figure 1.2: | Linear regulator (LDO) circuit.                                                                                      | 2  |

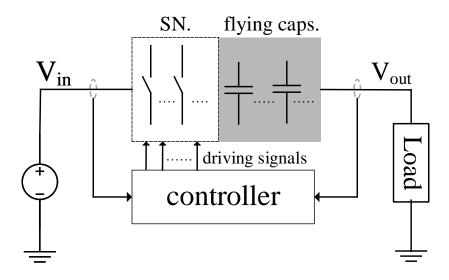

| Figure 1.3: | Functional SC converter building blocks.                                                                             | 4  |

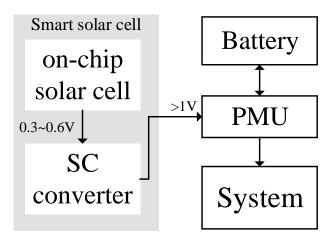

| Figure 1.4: | Conceptual smart cell building blocks                                                                                | 5  |

| Figure 1.5: | (a) Cockroft-Walton multiplier, (b) Dickson charge pump                                                              | 7  |

| Figure 2.1: | One cell FSC converter                                                                                               | 13 |

| Figure 2.2: | VCRs for one flying capacitor FSC converter in steady state                                                          | 14 |

| Figure 2.3: | General structure for FSC converter.                                                                                 | 15 |

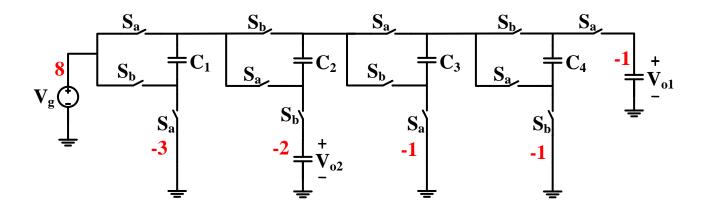

| Figure 2.4: | Circuit realization for FSC converter with dual outputs                                                              | 18 |

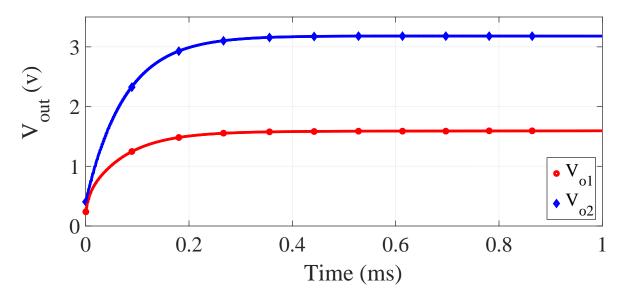

| Figure 2.5: | Output voltage waveforms for dual outputs FSC converter                                                              | 19 |

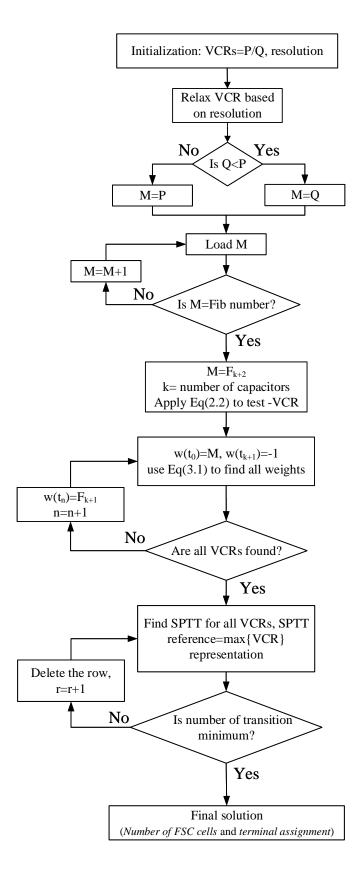

| Figure 3.1: | Flow chart for the proposed algorithm.                                                                               | 26 |

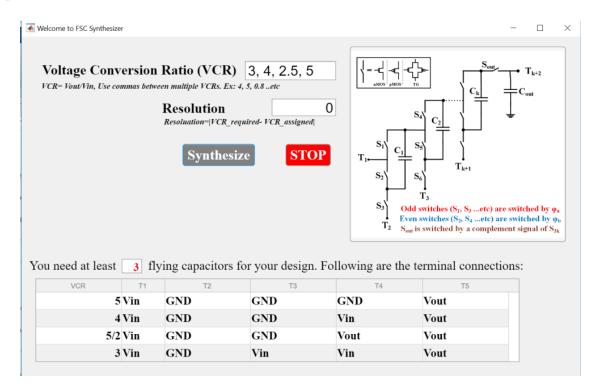

| Figure 3.2: | Terminal assignments using $FSC$ Synthesizer for variable FSC with VCR=5, 3, 4, 5/2                                  | 29 |

| Figure 3.3: | Variable FSC with VCR=5, 3, 4, $5/2$                                                                                 | 30 |

| Figure 3.4: | Buck SC converter with VCR=1, $3/4$ , $2/3$ : (a) FSC topology using proposed method. (b) Converter proposed in [21] | 32 |

| Figure 4.1: | SC converter steady state model                                                                                      | 35 |

| Figure 4.2: | SC converter equivalent impedance vs switching frequency                                                             | 36 |

| Figure 4.3: | FSC converter with VCR=3                                                                                             | 37 |

| Figure 4.4: | FSC converter with VCR=3: (a) state I, $S_a=1$ , $S_b=0$ . (b) state II, $S_a=0$<br>$S_b=1$                          | 38 |

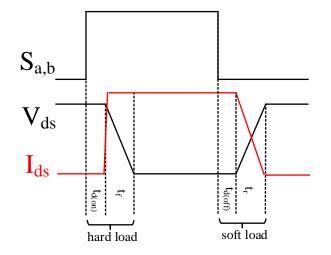

| Figure 4.5: | Gate switching intervals.                                                                                            | 42 |

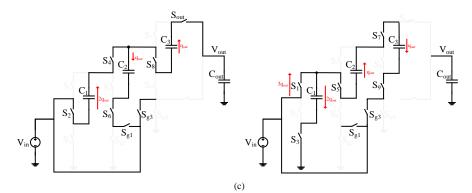

| Figure 4.6:  | Variable FSC with VCR=5, 3, 4, $5/2$                                                     | 45 |

|--------------|------------------------------------------------------------------------------------------|----|

| Figure 4.7:  | All operation states for proposed FSC: (a) VCR=5, (b) VCR=4, (c) VCR=3, and (d) VCR=5/2. | 46 |

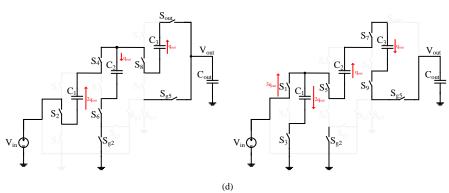

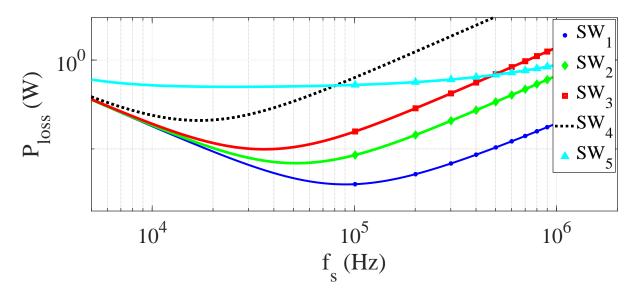

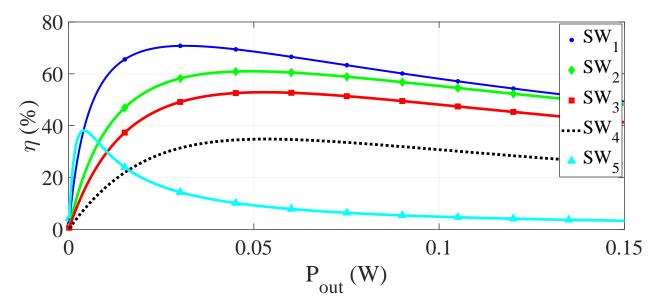

| Figure 4.8:  | $P_{loss}$ verses switching frequency for different switches                             | 49 |

| Figure 4.9:  | Efficiency for different loads                                                           | 50 |

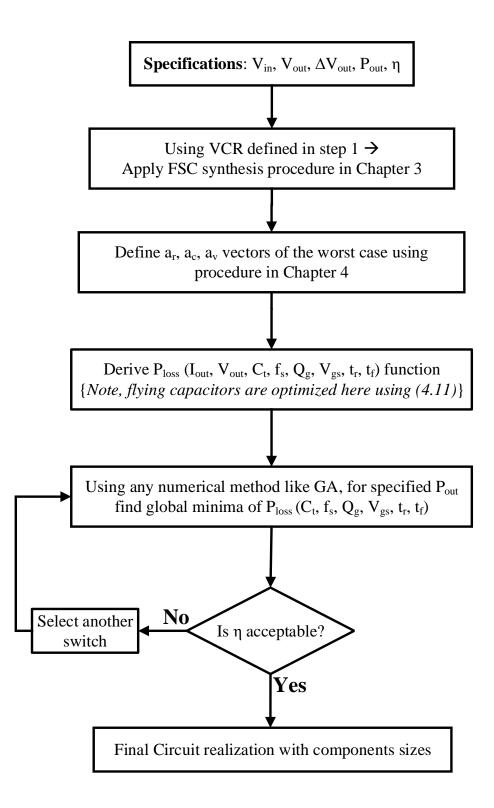

| Figure 4.10: | Variable FSC converter design flow chart using discrete components                       | 51 |

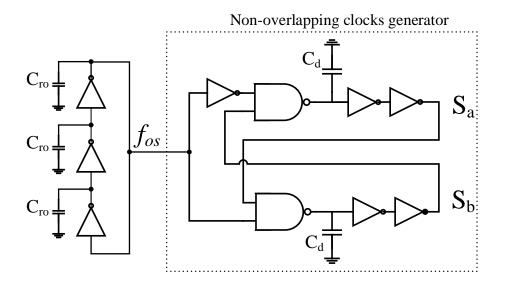

| Figure 4.11: | Ring oscillator with non-overlapping clocks generator                                    | 52 |

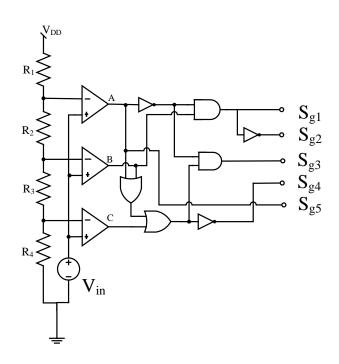

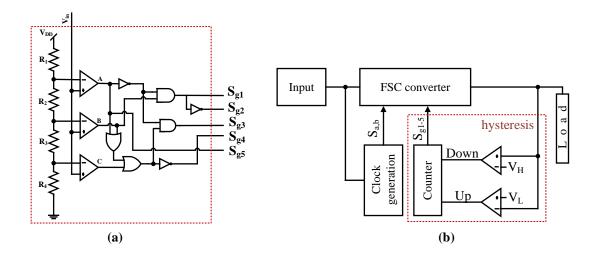

| Figure 4.12: | The gearbox signals control circuit.                                                     | 53 |

| Figure 4.13: | Variable FSC converter PCB                                                               | 53 |

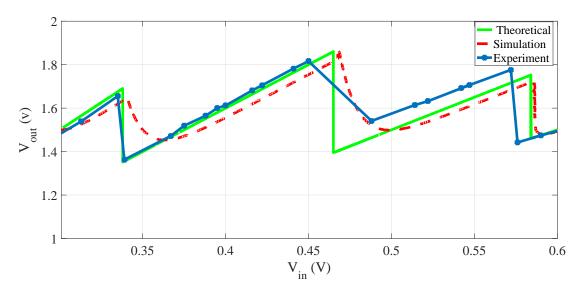

| Figure 4.14: | $V_{out}$ response to $V_{in}$ for variable FSC converter                                | 54 |

| Figure 5.1:  | CMOS structure.                                                                          | 57 |

| Figure 5.2:  | Photo-diodes available in CMOS process. Reproduced from [36]                             | 61 |

| Figure 5.3:  | On-chip PIP capacitor: (a) simple model, (b) 3D layout structure                         | 62 |

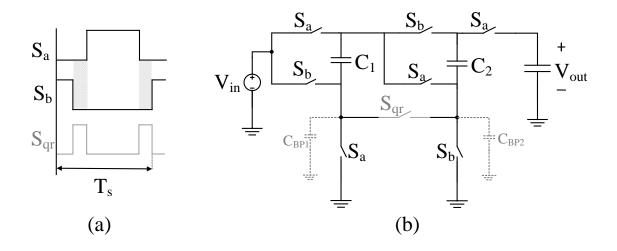

| Figure 5.4:  | Dead-time charge recycling (QR): (a) Timing signals, (b) FSC converter.                  | 66 |

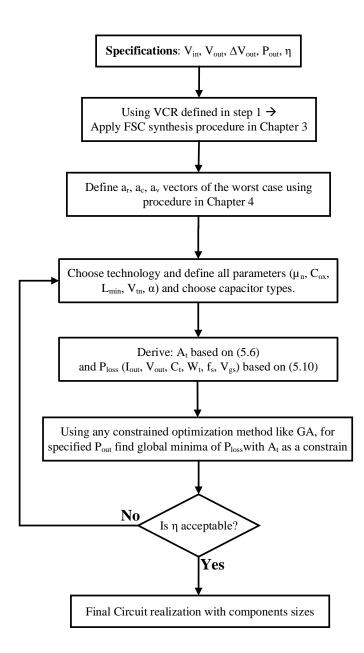

| Figure 5.5:  | IC FSC design procedure flow chart                                                       | 70 |

| Figure 5.6:  | Proposed FSC with parasitic capacitors.                                                  | 72 |

| Figure 5.7:  | Power losses shares with and without charge recycling (QR). $\ldots$ .                   | 73 |

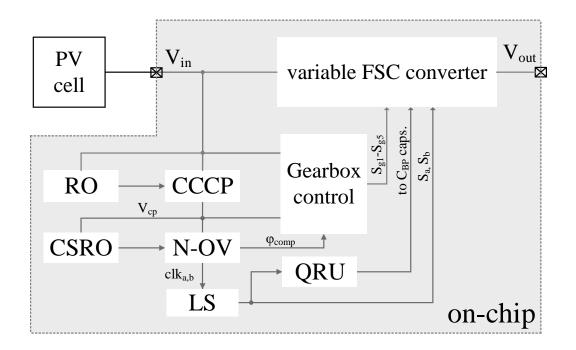

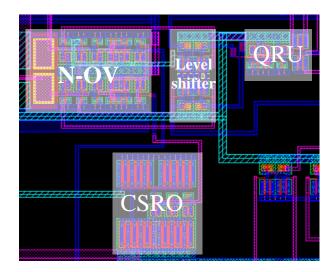

| Figure 6.1:  | FSC IC building blocks                                                                   | 75 |

| Figure 6.2:  | Possible FSC controller structures: (a) Feed-forward, (b) Hysteresis con-<br>troller     | 76 |

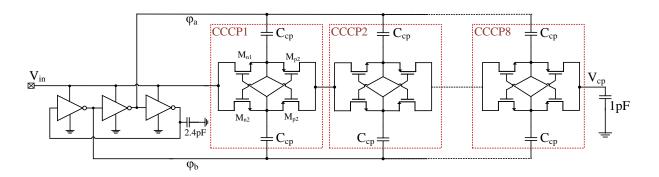

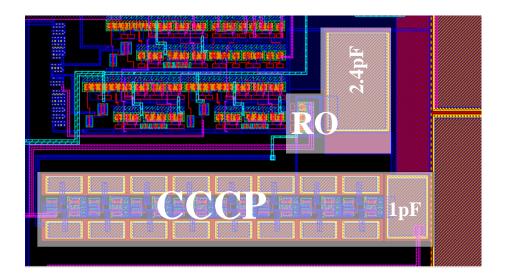

| Figure 6.3:  | Three-stage RO with eight CCCP modules                                                   | 77 |

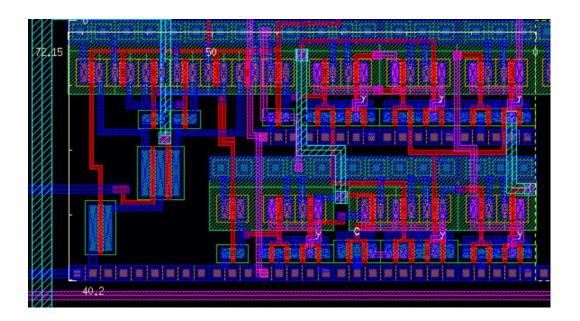

| Figure 6.4:  | Layout of RO with CCCP.                                                                  | 78 |

| Figure 6.5:  | Post-Layout simulation for the startup circuit using 0.5V input voltage.                 | 79 |

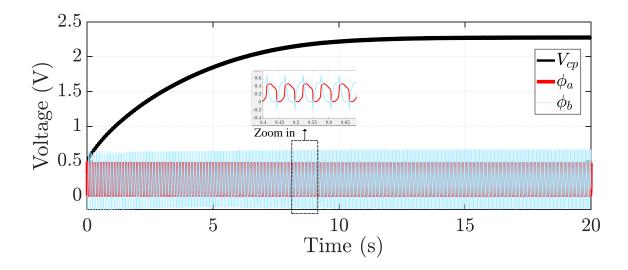

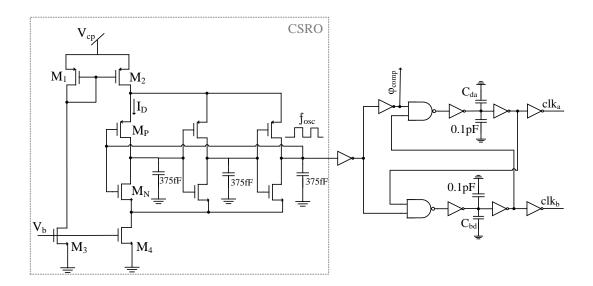

| Figure 6.6:  | Three-stage CSRO with non-overlapping clock generator                                    | 80 |

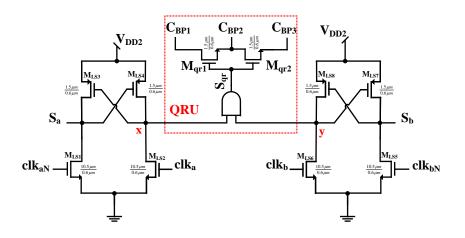

| Figure 6.7:  | Level shifters with QRU.                                                                                                                              | 81 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 6.8:  | Clocks generation layout.                                                                                                                             | 81 |

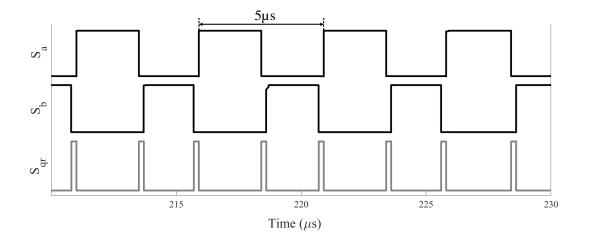

| Figure 6.9:  | Clocks waveforms (post-layout simulation)                                                                                                             | 82 |

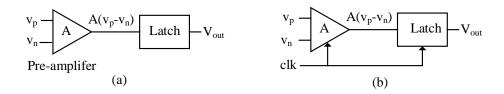

| Figure 6.10: | Comparator functional blocks: (a) Static comparator. (b) Dynamic com-<br>parator                                                                      | 83 |

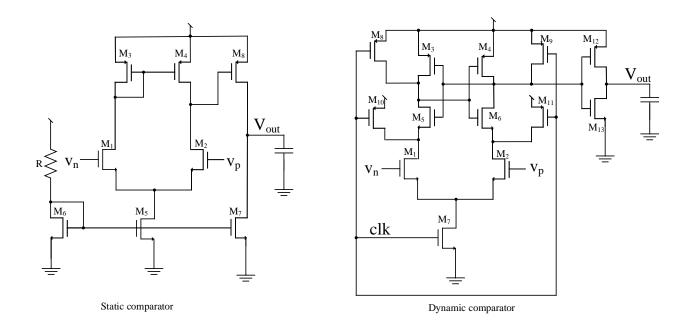

| Figure 6.11: | CMOS comparator structures                                                                                                                            | 83 |

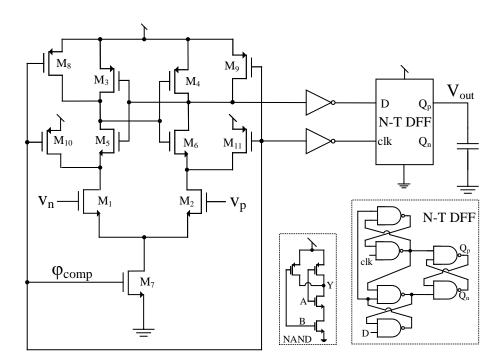

| Figure 6.12: | Proposed CMOS dynamic comparator.                                                                                                                     | 85 |

| Figure 6.13: | CMOS dynamic comparator layout                                                                                                                        | 86 |

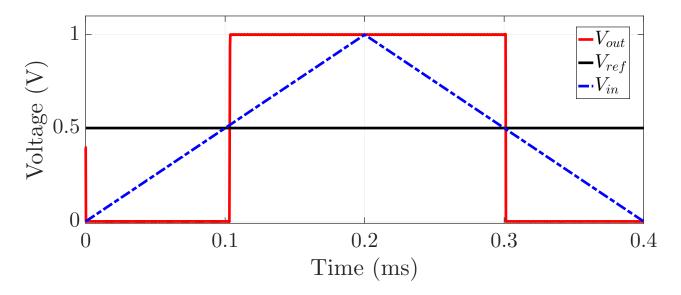

| Figure 6.14: | Post-layout simulation for the proposed dynamic comparator. $\ldots$ .                                                                                | 87 |

| Figure 6.15: | The gearbox controller layout.                                                                                                                        | 87 |

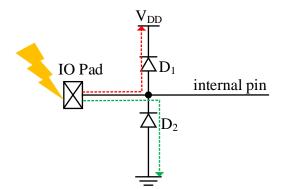

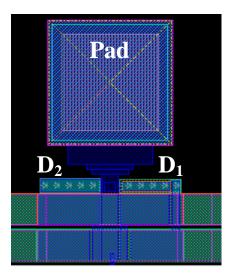

| Figure 6.16: | ESD for IO pads.                                                                                                                                      | 88 |

| Figure 6.17: | Layout of an IO pad with ESD                                                                                                                          | 89 |

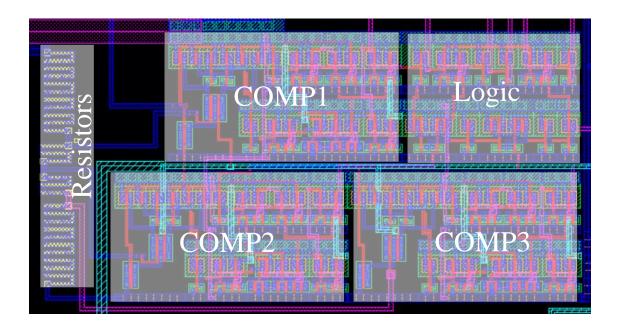

| Figure 6.18: | The chip layout with pin configuration.                                                                                                               | 91 |

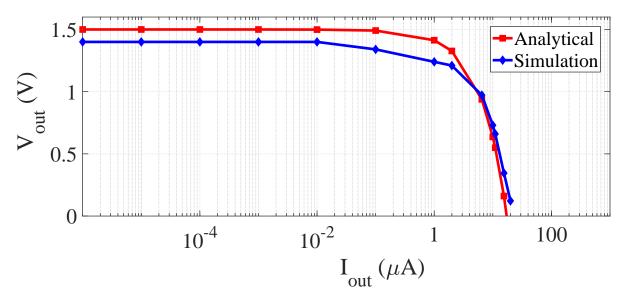

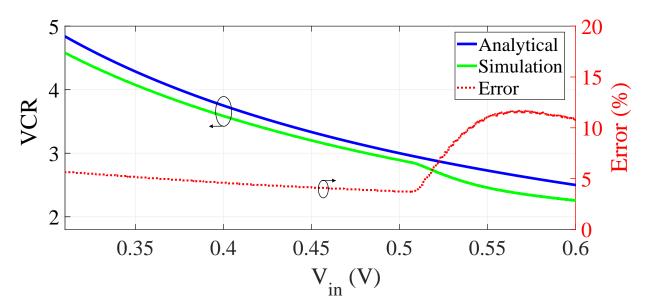

| Figure 6.19: | Efficiency verses $I_{out}$ for the proposed FSC converter with 300mV input voltage                                                                   | 93 |

| Figure 6.20: | Efficiency verses $I_{out}$ for the proposed FSC converter with 300mV input voltage                                                                   | 94 |

| Figure 6.21: | $V_{out}$ verses $I_{out}$ for the proposed FSC converter with 300mV input voltage.                                                                   | 94 |

| Figure 6.22: | VCR verses $V_{in}$ for the proposed FSC converter                                                                                                    | 95 |

| Figure 7.1:  | MIMO SC conceptual blocks for possible applications: (left) on-chip power management unit for microprocessors, and (right) energy harvest-ing system. | 99 |

## **KEY TO ABBREVIATIONS**

- **SSL** Slow Switching Limit

- ${\bf FSL}$  Fast Switching Limit

- $\mathbf{VCE}$ Voltage Conversion Efficiency

- PCE Power Conversion Efficiency

- **ZVS** Zero Voltage Switching

- ${\bf RO}~{\rm Ring}~{\rm Oscillator}$

- **CSRO** Current-Starved Ring Oscillator

- **EH** Energy Harvesting

- AQP Auxiliary Charge Pump

- NCP1 modified Dickson Charge Pump Version 1

- NCP2 modified Dickson Charge Pump Version 2

- ${\bf CCCP}$  Cross-Coupled Charge Pump

- ${\bf TP}~$  Top Plate

- **BP** Bottom Plate

# Chapter 1

# Introduction

In this chapter, the switched-capacitor (SC) converter is introduced. For lower power applications, many SC configurations can be utilized. However, Fibonacci SC converter (FSC) [1,2] and Dickson converter [3] are considered to be the best topologies due to their less area requirement and good efficiency performance. Therefore, an overview of these topologies will be presented, and followed by the research scope and summary of contributions.

#### 1.1 Overview

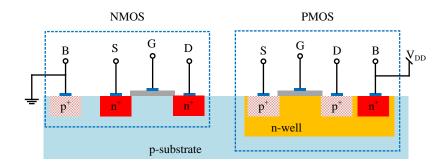

The power conversion is crucial in most electronic systems. As shown in Figure 1.1, there are two ways to implement DC-DC converters: passive and switching-mode implementation. The DC-DC converters are used to step-down or step-up the input voltage based on the system requirement. For step-down conversion, passive implementation or so-called linear regulators (LDO) are commonly used due to less area requirement and easy control. Figure 1.2 illustrates a simple implementation of LDO, which is basically a voltage divider circuit implemented around an active controlled switch that works as a variable resistor. Despite its simplicity and minimal active area requirement, LDO suffers from low efficiency and only can be used for step-down conversion [4]. Note that, the LDO efficiency can be very high if the output voltage is close to the input voltage, i.e theoretically 100% efficiency can be achieved when no conversion is performed ( $V_{in}=V_{out}$ ).

Figure 1.1: Types of DC-DC converters.

Figure 1.2: Linear regulator (LDO) circuit.

The switching mode converters are more versatile as they can be implemented to stepdown or step-up the input voltage [5]. In addition, some converters are capable of both conversions owing to the intelligent control circuit and converter design. Switching mode converters are implemented using switch networks (SN) and storage elements to transfer the input energy to the output. Based on the storage element, the switching converters can be categorized into three main groups: switched-capacitor (SC), switched-inductor (SI) and resonant converters (hybrid), see Figure 1.1. Examples of SI converters include buck, boost, SEPIC, Ćuk, Flyback converters and many others [6]. They are widely used in commercial products due to their high efficiency and relatively simple design. However, the main disadvantage of SI converters is the use of an inductor which is a bulky element and usually associated with poor EMI performance.

On the other hand, the SC converters, sometimes referred to as charge pumps [7], use capacitors as storage elements, commonly referred to as flying capacitors, which makes them attractive for monolithic IC integration due to their compact and magnetic-less features, the functional blocks diagram is depicted in Figure 1.3. Dickson, Fibonacci, ladder, seriesparallel and voltage doubler and their variants are examples of SC converters. Most SC converters can be driven in open loop scenario using at least two non-overlapping clocks to avoid shoot-through states. Despite these advantages, SC converters suffer from poor output regulation and the conversion efficiency drops drastically when the output voltage deviate from the target voltage due to the input voltage change and/or loading effect. Therefore, achieving more voltage-conversion-ratios (VCR) minimizes the error between the output and target voltage which effectively improve the efficiency. Ideally, a the better conversion performance can be achieved by increasing the number of VCR. Yet, synthesizing SC converter to perform multiple VCR is considered a major challenge, commonly referred to as SC synthesis problem.

Figure 1.3: Functional SC converter building blocks.

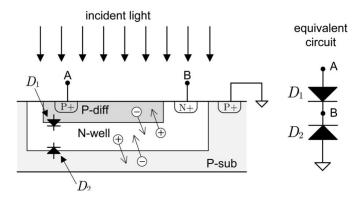

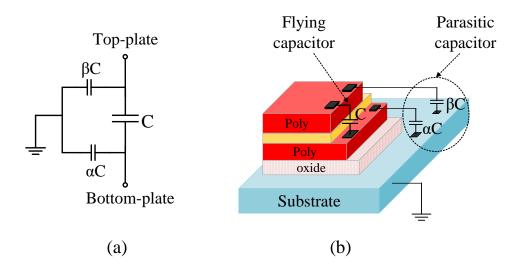

Generally, solar energy is abundant and can be utilized to prolong the battery life for applications that require expensive or invasive battery replacement, such as wireless sensor nodes (WSN) and bio-implementable devices. To drive this work to a practical implementation, we consider a smart solar cell which consists of an on-chip solar cell, implemented using photo-diodes, and SC boost converter as shown in Figure 1.4. The concept of smart solar cell is to replace conventional solar cell with low open circuit voltage,  $V_{oc}$ , with a system containing the solar cell and boost converter to output higher voltage level that can recharge a battery or power a system. Also, smart solar cell is expected to be autonomous meaning, the integrated converter starts up and operate without any external biasing. In addition, the converter needs to smart enough to detect  $V_{oc}$  variations, usually 0.3 - 0.6V in miniaturized solar cells, and apply any technique for output regulation. Referring to Figure 1.4, the smart solar cell supplies the power management unit (PMU) with a dc voltage >1V which is adequate to power up microsystem in some applications. Then, PMU is responsible to power up the system, WSN or implanted device ..etc, from the smart solar cell. In case if there is no enough power, PMU bypasses the smart solar cell and supply power to the system using the battery. For this operation, we need to design a SC converter that can startup from low voltage and configures itself to provide enough supply voltage and all are done autonomously and without any external component. There are some challenges that limits a high efficiency in IC SC converters. Therefore, in this work, we will focus only on the SC converter block. In the following section, a brief history of SC development is presented.

Figure 1.4: Conceptual smart cell building blocks.

### **1.2** A Brief History on SC Development

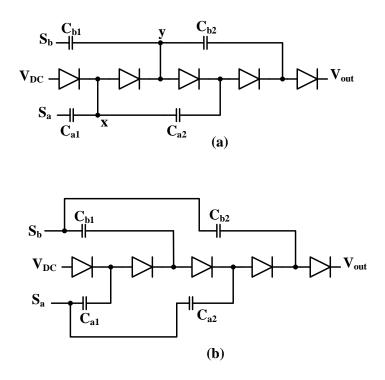

SC converters can be traced back to the first high voltage Cockroft-Walton (CW) multiplier [8]. This multiplier suffers from high stray capacitance and to have efficient multiplication, pumping capacitors need to be very large which is impractical in monolithic integration. To overcome this problem, the CW multiplier was modified by connecting pumping capacitors in parallel to the input instead of being connected in series. This is a well-known Dickson charge pump (CP) [3], or sometimes referred to as linear charge pump (LQP) because the VCR is linear and can take any integer from 1...n, where  $n \ge 1$ . Therefore, CW multiplier and Dickson CP are quite similar in basic structure and operation, but working in two different power and voltage levels.

The CW multiplier was developed for high voltage generation of 800kV whereas Dickson CP was intended for low power applications enabling integration in the same substrate. Figure 1.5 illustrates both circuits, highlighting the similarities between them. Dickson basically connected the flying capacitors to the clock instead of being connected in series as in CW circuit. This decreases the stray capacitance at the junctions, x and y, which improves the total converter performance. Since then, Dickson CP has been the main voltage multiplier in IC circuits. The output voltage in Dickson CP can be found using the following equation:

$$V_{out} = n(V_{in} - V_D), \tag{1.1}$$

where n is the number of stages, and each stage consists of a diode and flying capacitor.  $V_D$  is the diode voltage drop which is approximately 500-700mV, and it equals the threshold voltage  $(V_{th})$  if the diode is implemented using a MOS transistor. Dickson converter suffers from the diode voltage drop. Therefore, to achieve higher voltage level, the diode voltage drop needs to compensated by adding more stages.

Following Dickson invention, many topologies have been proposed in three main trends: solving the voltage regulation, decreasing the component stress and shrinking the converter size. The authors in [1] proposed a SC converter where the VCR follows Fibonacci series, which since then has been considered the first brick in FSC development. Later, the the-

Figure 1.5: (a) Cockroft-Walton multiplier, (b) Dickson charge pump.

oretical limits of SC converter is proved in [2], resulting in two important theorems which help to set guidelines for developing SC converters. This is well-known as the SC fundamental limit theory. Also, FSC has been proved to have the least number of number of flying capacitors and switches to implement specific VCR, which lends itself to high power density applications. Multi-phase FSC can be also implemented to achieve higher and/or balanced VCR [9, 10], and the performance limits of multi-phase can be found in [11]. However, multi-phase requires complicated control unit compared to a simple two on-off states control in the two-phase FSC converter. Therefore, two-phase FSC converter will be considered throughout this work.

#### **1.3** Research Scope and Contributions

The aim of this work is to present theoretical analysis of the SC converter, investigate the multi VCR SC synthesis, and discuss the design of a variable FSC converter in discrete and IC implementations targeting low power applications. The contributions of this dissertation can be summarized in the following:

- 1. Generalizing the SC fundamental limit theory.

- Proposing a novel algorithm to synthesize variable FSC converters. To the best knowledge of the author, this is the first generic method to configure a variable FSC converter. An open-source tool is built based on this algorithm to promote the FSC use.

- 3. Proposing design procedures and optimization to implement FSC converter in low power applications for both discrete and IC implementation.

- 4. Proposing an IC controller with charge recycling technique to minimize the parasitic charge loss in IC FSC converter. Ideally, this technique decreases the parasitic capacitors power loss by 50%. The concept of charge recycling is not new but implementing this technique to FSC without transforming the FSC to interleaved structure is proposed here.

## **1.4 Report Organization**

The rest of the report is structured as follows. In Chapter 2, we present the proposed generalized equation to the SC fundamental limit. Synthesizing FSC converters is discussed in Chapter 3 and the proposed algorithm is presented. In Chapter 4 and 5, we present the

design and implementation of discrete and integrated FSC converter, respectively. Finally, the report is concluded and future work is provided in Chapter 7.

## Chapter 2

# SC Converter Fundamental Theory

In this chapter, the fundamental limit theory in SC converter is introduced and studied. This theory is insufficient to determine the accurate boundaries for all negative VCRs in a SC converter. This work extends the theory to all possible cases of SC converters resulting in a general form<sup>1</sup>. The proposed theory in this chapter will be used later in synthesizing FSC converter.

#### 2.1 Introduction

The fundamental limit in SC converter design which was proved in [2] is a well-known theory in the literature. The limit creates the foundation for SC converters design and synthesis. The fundamental limit theory consists of two theorems that define the voltageconversion-ratio ( $VCR = V_{out}/V_{in}$ ) boundaries for k flying capacitors in a SC converter, and the minimum number of switches to realize that converter. The first theorem is the main concern in this work. It states that for k flying (pumping) capacitors in an SC converter, the numerator and denominator of achievable VCR follow the Fibonacci series. They are bounded by 1 as the minimum limit and  $F_{k+2}$  as a maximum limit, as shown in the following

<sup>&</sup>lt;sup>1</sup>The work presented in the chapter has been published in IEEE Transaction of Power Electronics [12].

equation:

$$\frac{V_{out}}{V_{in}} = \frac{P}{Q},\tag{2.1}$$

where  $1 \leq (P,Q) \leq F_{k+2}$ , k is the number of flying capacitors in the circuit and  $F_k$  is the  $k^{th}$  Fibonacci number found in the Fibonacci series,  $F = (1, 2, 3, 5, 8, 13, 21...F_k)$ . The SC converter that has VCR follows or implement this limit is called FSC converter.

This fundamental limit is a powerful basis to minimize the effort of designing and implementing new SC converter topologies. It also helps providing a figure of merit to compare between different topologies in terms of achievable VCR and element counts. However, this limit only discusses the positive VCR boundaries and it does not explore the negative VCR boundaries which is considered as a first limitation. In this paper, we propose a general expression that overcomes this limitation and sets the boundaries for all possible VCRs.

The second limitation of the fundamental limit arises from the focus on single-inputsingle-output structure only. However, the multiple-input-multiple-output (MIMO) SC converter structures is desired in some applications. Extending the fundamental limit in (2.1) to include MIMO concept leads to provide a truly generic theory of the fundamental limit. This chapter is intended to explore and study these two limitations and propose generic expressions in both cases using FSC topology because it is the best to represent the theory. Examples of different cases and the practical implications are also discussed to verify the theory.

### 2.2 General SC Fundamental Limit

In some applications, negative output voltage polarities are desired. In this case, however, the fundamental limit fails to define the real boundaries that SC converter can achieve for the negative VCR. Generalizing the fundamental limit to cover all possible combinations of VCR is needed. The following expression divided the VCR in two regions, positive and negative. In both, the VCR still follow the Fibonacci series but the boundaries are different. As (2.2) describes,

$$\frac{V_{out}}{V_{in}} = \begin{cases} +\frac{P}{Q} & 1 \le \max|Q, P| \le F_{k+2} \\ -\frac{P}{Q} & 1 \le \max|Q, P| < F_{k+2} \end{cases},$$

(2.2)

negative VCRs are less than positive VCRs for the same converter. Note that, P/Q should be represented in their simplest form, for example 4/4 is considered as 1/1. The conditions in (2.2) are used to estimate the absolute minimum number of flying capacitors for desired VCR. More details about the practical implication of this expression are presented below.

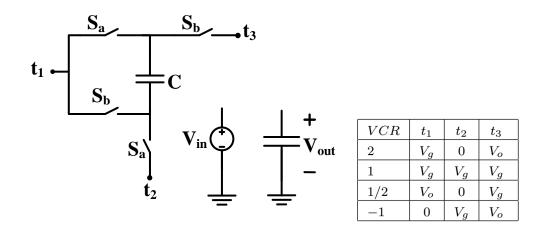

To better understand the expressions presented in (2.2), let us illustrate by using an FSC converter with one flying capacitor, shown in Fig. 2.1. The flying capacitor can be connected to  $V_g$ ,  $V_o$  or ground through the terminals  $t_1 - t_3$ . This converter can achieve (1/2, 1, 2) VCRs neglecting the sign, which can be found using (2.1). The negative VCRs were left out as a default, assuming that this converter is capable to achieve (-1/2, -1, -2) voltage conversion, which is incorrect. In fact, (2.2) reveals that with one flying capacitor, the converter can achieve only one negative VCR, which is -1. The look-up-table (LUT) for all possible terminal connections is presented in Figure 2.1, showing that this converter can achieve four distinct VCRs in total, (-1, 1/2, 1, 2).

Figure 2.1: One cell FSC converter.

On the other hand, the minimum number of flying capacitors needed to achieve other negative VCRs (-2, -1/2) can be found using (2.2). In this case, it can be found that a Fibonacci number of two or greater is required because max|P,Q|=2. Hence,  $F_4 = 3$ is the right limit for this converter, meaning two flying capacitors are needed to achieve the missing VCRs. Yet another example, if a (-1/4) Fibonacci SC converter needs to be designed. Applying the above steps resulted in  $F_5 = 5$ , which means the converter needs at least three flying capacitors. The design procedure has two steps:

- 1. Defining the real boundary limit using (2.2), i.e  $F_{k+2}$ .

- 2. Finding the number of required flying capacitors, which is k.

Spice simulation was conducted using ideal switches with  $R_{dson}=10m\Omega$ ,  $f_s=500k$ Hz and  $15\mu F$  flying capacitor. The MOSFET based switches are turned on and off, using 50% duty-cycle complementary non-overlapping square signals to avoid shoot-through states. All possible VCRs were plotted in steady-state and depicted in Figure 2.2. The simulation result agrees with the proposed theoretical expression. One note here, in case if the summation of P and Q is not a Fibonacci number, the next Fibonacci number is selected. For instance,

using VCR = -1/3, the summation of absolute values of the numerator and denominator is four which is not a Fibonacci number. Thus,  $F_5 = 5$  is assigned as a limit for this converter instead of four.

Figure 2.2: VCRs for one flying capacitor FSC converter in steady state.

#### 2.3 MIMO SC converter

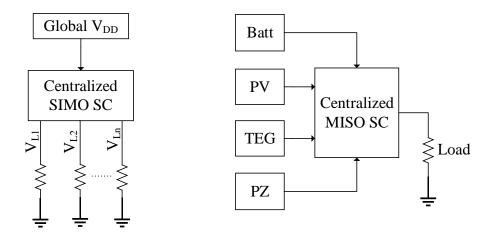

The MIMO SC converter and its special cases, the single-input-multiple-outputs (SIMO) and the multiple-input-single-output (MISO), are discussed here. As mentioned earlier, some applications require multiple outputs generated from one or multiple inputs, like the power management in microprocessors [13]. Usually, different DC-DC converters are employed to generate these different output levels. On the other hand, SIMO SC converters can do the job effectively achieving a real compact solution. Considering MISO SC converter implementation, a circuit for low power energy harvesting is used as an example. In this circuit, a single point-of-load is usually powered by multiple ambient sources to harvest more power. It can either be implemented by using different conventional SC converters, or by simply using the MISO SC converter which offers better solution in terms of power density. However, synthesizing these converters without knowing the VCR boundary limits is a tedious job. MIMO implementation is proposed in this paper by employing the terminal weight concept found in [14]. Although MIMO implementation can be extended to all SC converter topologies, only the MIMO Fibonacci SC converter is considered because the interest here is to investigate the fundamental limit theory.

Figure 2.3: General structure for FSC converter.

The general structure of the MIMO FSC converter is depicted in Figure 2.3. It consists of two main blocks: the converter core, which is composed of FSC cells, and a pool of voltage nodes. The voltage nodes are connected to the core using terminals. The number of these terminals depend on the number of available FSC cells in the core. For instance, the number of terminals in k cells FSC converter equals k + 2. These terminals are assigned a weight that depends on its position in the circuit. There are four conditions need to be met to assign the terminal weight and achieve FSC converter structure [14]. These conditions are as follows:

- 1.  $w_1 = F_{k+2}$ ,

- 2.  $w_{k+2} = -1$ ,

- 3.  $\sum_{i=1}^{k+2} w_j = 0,$

- 4.  $|w_j| = (1, 1, 2 \dots F_{k+2}).$

The first condition implies that the first terminal  $(t_1)$  has a positive weight equals to the maximum achievable VCR, which is  $F_{k+2}$ . The other terminals are assigned negative weights using the *b*-*d* conditions. Note that all terminal weights follow the Fibonacci series as suggested in step (4).

Suppose that the MIMO FSC converter consists of n inputs and m outputs. With careful terminal weight assignment, the following equation relates the input and output voltages, where  $n+m \le k+2$ :

$$\sum_{i=1}^{n} w_{vg_i} v_{g_i} + \sum_{j=1}^{m} w_{vo_j} v_{o_j} = 0.$$

(2.3)

This equation deals with MIMO realization. It defines the possible output voltage levels for MIMO converters. It incorporates all conditions mentioned above. In the following, a detailed procedure is presented to show how to use (2.2) and (3.1) in designing and realizing SC converters.

Suppose we have a system that requires two multiple output levels of 1.8V and 3.3V from one input source, which is common in power management circuits. There are two

approaches to design a DC-DC converter for this application, either using two different DC-DC converters or using the MIMO converter design concept. The latter has less component counts and makes it the optimal choice for this application. The steps to design the MIMO converter are as follows:

- 1. Defining how many inputs and outputs which allows us to find minimum limit for k.

- 2. Determining the maximum VCR using (2.2). Then, find new k and choose the highest value for k amongst the two steps (1) and (2).

- 3. Assigning terminal weight following the conditions listed in section 2.3.

- 4. Connecting the voltage nodes to terminals based on their weight.

Let us use the example stated earlier to verify the design procedure steps. We have an input voltage of 1V and we need to get 1.8V and 3.3V outputs. So, following the same design steps:

- 1. n=1, m=2 which implies  $1+2 \le k+2$ , and consequently, k need to be greater or equals one.

- 2. Maximum VCR here is 3.3 which is close to 7/2, Using equation (2.2), k greater than or equals four is required which corresponds to  $F_6=8$ . Therefore, the circuit needs at least four flying capacitors and six terminals (Figure 2.4) using FSC converter topology.

- 3. Terminal weights are assigned as following:

- (a)  $w_1 = F_{k+2} = 8$  and  $w_6 = -1$ .

- (b)  $w_2 + w_3 + w_4 + w_5 = -7$ , using a trial and error approach,  $w_2 = -3$ ,  $w_3 = -2$ ,  $w_4 = w_5 = -1$ . Note that, these terminal weights should follow the Fibonacci

Figure 2.4: Circuit realization for FSC converter with dual outputs.

series as stated earlier. For convenience, the terminal weights are also highlighted next to each terminal in Figure 2.4.

4. Output voltages relation is examined which helps in assigning the terminals. Detailed discussion of this step is to follow.

In this example, we have  $V_{o_2} \simeq 2V_{o_1}$  as a design requirement (1.8V, 3.3V). Accordingly, terminals need to be selected to guarantee this relation between the outputs. For instance, if  $V_{o_1}$  is connected to the second terminal in this converter which has a weight of three (Figure 2.4), the second output needs to be connected to a terminal that provides a weight of six which is impractical with this converter. In this case,  $V_{o_2}$  is connected to the third terminal which has a weight of two and  $V_{o_1}$  can connected to any of the last three terminals because they have same weights,  $w_4$ ,  $w_5$  and  $w_6$ . For convenience,  $V_{o_1}$  is connected to the last terminal. The input is connected to the first terminal, because positive VCRs are required. Using (3.1),  $8v_g = 2v_{o_2} + v_{o_1}$  which implies  $8v_g = 5v_{o_1}$  and  $8v_g = 3v_{o_2}$ .

Spice simulation was conducted for the example discussed above. Figure 2.4 shows the circuit realization where four  $15\mu$ F flying capacitors were used. The output capacitors are

Figure 2.5: Output voltage waveforms for dual outputs FSC converter.

kept high to maintain small output voltage ripple. The converter is operated using 50% duty-ratio complementary non-overlapping gate signals,  $S_a$  and  $S_b$ , in open loop control. These gate signals are provided using 500kHz pulse clock generator. Ideal switches with  $R_{dson}=10m\Omega$  are used as power switches. The output voltage waveforms of 3.2V and 1.6V are achieved using an input voltage of 1V. These converters outperform the single output voltage converter in terms of complexity and component count.

#### 2.4 Summary

In this chapter, two limitations in SC converter fundamental limit were discussed, and general expressions to overcome these limitations have been proposed. The design procedure using these expressions was introduced, which helps in designing SC converter for a variety of applications. The MIMO FSC converter has been reported for the first time in literature and the same concept can be extended to other SC topologies. Simulation results show an agreement with the theoretical analysis.

# Chapter 3

# SC Converter Synthesis

Synthesizing SC converter is a tedious and time consuming job and usually performed in an ad-hoc approach. This chapter discusses existing works to overcome this problem. Then, we propose an efficient algorithm to realize multi VCR FSC converter which is expected to be useful for wide input applications<sup>1</sup>.

### 3.1 Related Work

Generally, there are many ways to configure the SC converter. For instance, if one FSC cell of Figure 2.1 is considered, there are three possible combinations and it increases to seven combinations if we add another FSC cell. Considering FSC converter with k flying capacitors, there are  $F_{k+2}(F_{k+2}-1)+1$  possible combinations. So, synthesizing the FSC converter is not trivial and considered a major challenge in SC converter design compared to SI counterpart. A generic SC structure has been studied in [16] but the proposed synthesizing technique is not systematic and considers only one condition: whether the converter is designed for step-down or step-up. Details of configuring specific VCR were not discussed. Different approaches and algorithms were proposed to tackle the SC synthesis problem [14, 17–19] which are focused to realize the FSC or its variants.

In [17], an interesting approach to configure SC converter was proposed by connecting all

<sup>&</sup>lt;sup>1</sup>Part of the work presented in this chapter has been published in the proceedings of IEEE Workshop on Control and Modeling for Power Electronics (COMPEL), 2017 [15].

capacitor negative plates to the ground in the charging phase, and hence it is known as All Negative terminal connected To Zero topology (ANTZ), and then configuring the capacitors to deliver the charge to the output based on optimal vector path from the ANTZ tree. The ANTZ tree is composed of two main levels, the voltage source level, usually  $(V_{in}, V_{in})$ or simply (1,1), and flying capacitor levels. Each flying capacitor level is assigned a vector based on the possible voltage appears in the flying capacitor terminals  $(V_{c_i}, \Phi_1, V_{c_i}, \Phi_2)$ . Using ANTZ, many SC topologies can be configured including Fibonacci topology. However, this topology targets only step-up converters with non-fractional VCR and cannot be considered as a generic model for SC converter synthesis. In addition, composing the ANTZ tree is quite complicated especially for large number of flying capacitors and hence the design procedure is not straightforward.

The algorithm found in [18] is quite simple but not effective in finding all configurations for FSC converter. As an example, using this algorithm a VCR = 5/3 was found to be realizable in only three configurations (Figure 6 in [18]). However, it can be realized in four configurations using the proposed algorithm in this work, see Table 3.1. Details of the proposed algorithm is discussed Also, assigning capacitor polarities needs to be done by inspection which cannot be automated. In addition, the configuration table grows with the increase in the number of flying capacitors which complicates the synthesis process.

The third algorithm we want to discuss here is proposed in [19]. It takes two steps to synthesize the SC converter: (i) generating fundamental VCR using basic FSC converter and (ii) summing these fundamental VCR to generate the desired one. This method works the best with high VCR as it has less voltage stress than conventional FSC converter. However, it fails to maintain the minimum number of flying capacitors required for specific VCR based on the fundamental limit (2.2). Basically, it uses extra capacitors in the second part of the

| Terminal           | $t_1$    | $t_2$ | $t_3$ | $t_4$ | $t_5$ |

|--------------------|----------|-------|-------|-------|-------|

| Weight             | 5        | -2    | -1    | -1    | -1    |

|                    | 1        | 0     | 2     | 2     | 2     |

| SPTT code          | 1        | 2     | 0     | 0     | 2     |

| SI I I Code        | 1        | 2     | 0     | 2     | 0     |

|                    | 1        | 2     | 2     | 0     | 0     |

| Final SPTT code    | 1        | 2     | 0     | 0     | 2     |

| Number of Switches | 0        | 0     | 0     | 0     | 0     |

| Voltage nodes      | $V_{in}$ | Vout  | gnd   | gnd   | Vout  |

Table 3.1: All possible realizations for FSC with VCR=5/3

system to perform the addition. Also, it can be used only for an integer step-up SC converters like the ANTZ topology.

Recently, an algorithm to evaluate the SC converters is proposed in [20]. The evaluation is based on charge-multiplier concept which will be discussed thoroughly in the following chapters. However, their claim to be first attempt towards solving the SC synthesis is misleading as we already discussed some prior works in the literature. Moreover, the work in [20] shows only the ability to find charge-multiplier vectors for evaluation purposes, but the synthesis approach is not clear. For example, there is no limits for the number of required cells for specific VCR. Also, the algorithm targets a one-VCR applications and hence is not practical for multi-VCR. Despite all of that, the generic nature of the approach can be credited compared to topology-dependent approaches.

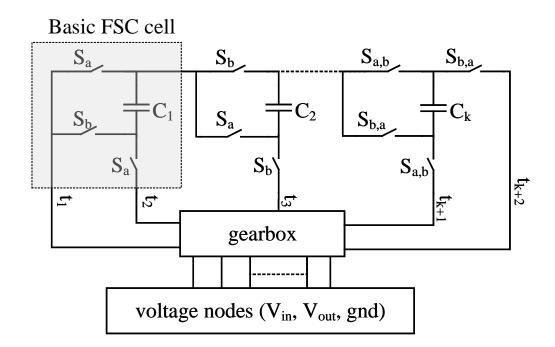

A canonical model was proposed in [14] to solve the realizability problem of FSC converter. This model was successful to synthesize the FSC converter to achieve any VCR including fractional and negative VCR. It proposed a gearbox circuit that configures the converter such a way to be able to perform certain VCR. Each flying capacitor terminal is assigned a weight based on Fibonacci series. Based on the terminal's weight and specified VCR, the gearbox circuit directs each terminal to specific voltage node ( $V_{in}$ ,  $V_{out}$ , gnd) via switches. However, it was developed only for a specific VCR and did not target multi VCRs which is sometimes desirable. Here, we extends the canonical model to synthesize a truly variable FSC converter by adjusting the gearbox switches. Details of the proposed algorithm is discussed in the following section. Table 3.2 summarizes the synthesis techniques with general comparison which concludes the effectiveness of the proposed algorithm in this work where a general FSC that provide any VCR can be synthesized.

Table 3.2: Comparison of SC converter synthesis techniques

|                  | COMPEL'14 [14] | TCAS-II'07 [17] | COMEL'15 [18] | EDSSC'09 [19] | This work |

|------------------|----------------|-----------------|---------------|---------------|-----------|

| Complexity level | Low            | High            | Avg.          | Avg.          | Low       |

| Capacitor count  | min.           | min.            | min.          | High          | min.      |

| Variable VCR     | No             | Yes             | No            | No            | Yes       |

## 3.2 Proposed FSC Synthesis

The canonical model proposed in [14] is shown in Figure 2.3. It consists of Fibonacci converter cells and a gearbox to change the voltage conversion requirement. The synthesis approach is approved mathematically, and hence it is used here as a basis to help synthesizing variable FSC converter. The Makowski general SC converter starts with selecting the minimum number of capacitors to achieve the maximum VCR by using equation (2.1). This step determines the number of converter cells and the number of the terminals to the gearbox.

The second step involves weight function assignments based on the VCR, this step is done using equation (3.1). It is assumed that each path in the gearbox has a fictitious single pole triple throw (SPTT) switch that connects the converter core to one of the three voltage nodes  $(V_{in}, V_{out}, gnd)$  in the blue box. These terminals carry some weight depending on the Fibonacci series,  $F = (1, 1, 2, 3, 5 \dots F_{k+2})$ , either in positive or negative values. Equation (3.1) is a condition that ensures all weight function values are part of Fibonacci series as follow:

$$w(t_1) + \sum_{i=2}^{k+2} w(t_i) = 0, \qquad (3.1)$$

where  $w(t_1)=F_{k+2}$ ,  $w(t_{k+2})=-1$  and  $w(t_k)\subset [-F_{k+1}, -F_k.... - 2, -1, -1]$ . Finally, the SPTT switch is assigned a code (0, 1 or 2) where 0, 1, and 2 means that the terminal is connected to ground,  $V_{in}$  and  $V_{out}$ , respectively. These steps allow synthesizing the SC Fibonacci converter for any VCR. Examples of positive and negative VCRs with thorough explanations and mathematical proof can be found in [14]. So, this canonical converter is very efficient in synthesizing SC converters but when considering a multi-VCR, an additional step is required to ensure the optimal realization. In fact, the converter in Figure 2.3 may be extended to other modular structural SC like serial-parallel, which was already covered in [14] and called semi-canonical, ladder and other topologies. Also, this method can be extended to multiple inputs and/or outputs which may find its way to different applications, such as harvesting energy from multiple ambient sources. However, these extensions are out of the scope of this work. The proposed algorithm to synthesize a variable FSC converter takes the following steps:

- 1. All three steps mentioned in section 3.2;

- (a) capacitor requirements.

- (b) terminals weight function assignment.

- (c) SPTT code assignment.

#### 2. Unique/optimal realization assignment.

The first step including (a)-(c), is already discussed in chapter 3. For the second step, the algorithm will search for the minimum number of state transitions in each realization compared to a reference set by the code, usually the SPTT code that corresponds to the maximum VCR. The number of state transitions here represents the number of switches in the gearbox circuit. Note that, these switches configure the SC converter in such a way that it can achieve all pre-assigned VCRs and hence they are considered the main attribute to the complexity level of the controller.

The whole algorithm flow chart is depicted in Figure 3.1. In this code, the user needs to specify the VCRs and degree of freedom, i.e resolution. The code will generate the minimum number of capacitors and terminals for each VCR using (2.2). Then, the weight functions are next to be determined. After that, the SPTT code for each realization is found, and an SPTT code reference is set by the code which is an important step to ensure all VCRs are realizable with the final solution. Next, the code allows to compare all SPTT codes to the reference and return SPTT codes that have a minimum number of state transitions. Note that, a state transition occurs whenever there is a change in the SPTT code for each terminal from (0 to 1), (0 to 2), (1 to 2), (2 to 1), or (2 to 0). The final SPTT code is found to be the optimal realization in terms of number of switches in the gearbox.

In some cases, the VCR required by the used can be relaxed, i.e 0.75 is assigned instead of 0.76, which allows realizing the converter by less number of capacitors. Therefore, to account for this degree of freedom, the resolution feature is added. It simply allows the algorithm to search for optimal VCRs that have the least number of capacitors. For exam-

Figure 3.1: Flow chart for the proposed algorithm.

ple, for VCR=0.76 and zero resolution, the code will assign seven flying capacitors because 0.76=19/20 in the simplest form. However, a resolution of 0.01 would relax the VCR to 0.75 and hence, only three flying capacitors are assigned. In fact, this feature allows finding all VCRs and helps the user to optimize the number of flying capacitors based on the specifications. The algorithm is implemented in MATLAB, and is made available as an open-source tool, called *FSC Synthesizer*. Using this open-source tool, the user can realize any VCR for FSC more efficiently, saving the time and effort required to go through trial and error route. In the following sections, some cases are presented to illustrate the workflow of *FSC Synthesizer*.

## **3.3** Case Study and Results

In this section, three cases will be discussed. These cases cover all types of FSC converter, single VCR and variable VCR. The last example shows the effectiveness of the proposed approach to simplify the controller circuit of an FSC converter.

#### 3.3.1 FSC Converter with VCR=30

The first example is to implement an FSC that has a single VCR equals to 30, which is one of the cases discussed in [14]. Using the proposed method, all solutions are validated and shown in Table 3.3. In addition, the proposed method selected the optimized SPTT code as shown in the Table which shows where the terminals are need to be connected. It also can be seen that no gearbox switches are needed which is expected in single VCR FSC converter.

| Terminal           | $t_1$ | $t_2$ | $t_3$ | $t_4$ | $t_5$ | $t_6$ | $t_7$ | $t_8$ | $t_9$ |

|--------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Weight             | 34    | -13   | -8    | -5    | -3    | -2    | -1    | -1    | -1    |

|                    | 1     | 0     | 0     | 0     | 0     | 1     | 2     | 1     | 1     |

|                    | 1     | 2     | 0     | 0     | 0     | 1     | 1     | 2     | 1     |

|                    | 1     | 2     | 0     | 2     | 0     | 1     | 1     | 1     | 2     |

|                    | 1     | 2     | 2     | 0     | 1     | 0     | 0     | 2     | 1     |

| SPTT code          | 1     | 0     | 0     | 0     | 1     | 0     | 2     | 0     | 1     |

|                    | 1     | 0     | 0     | 0     | 1     | 0     | 0     | 1     | 2     |

|                    | 1     | 0     | 0     | 0     | 1     | 0     | 2     | 1     | 0     |

|                    | 1     | 0     | 0     | 0     | 1     | 0     | 1     | 0     | 2     |

|                    | 1     | 0     | 0     | 0     | 1     | 0     | 1     | 2     | 0     |

| Final SPTT code    | 1     | 0     | 0     | 0     | 1     | 0     | 0     | 1     | 2     |

| Number of Switches | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Voltage nodes      | Vin   | gnd   | gnd   | gnd   | Vin   | gnd   | gnd   | Vin   | Vout  |

Table 3.3: All possible realizations for VCR=30/1

#### 3.3.2 Variable FSC Converter with VCR=5, 4, 3, 5/2

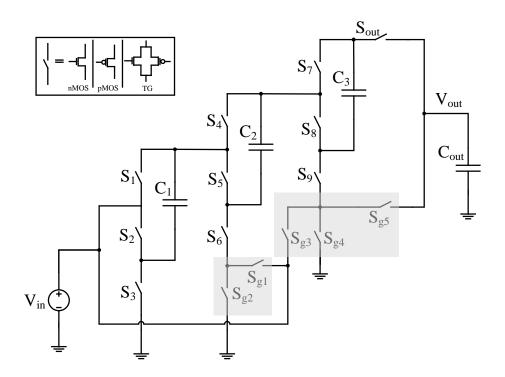

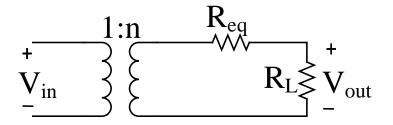

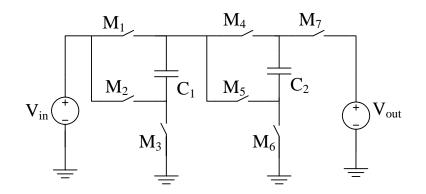

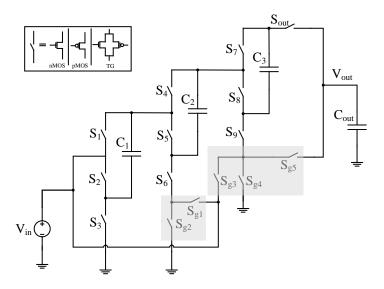

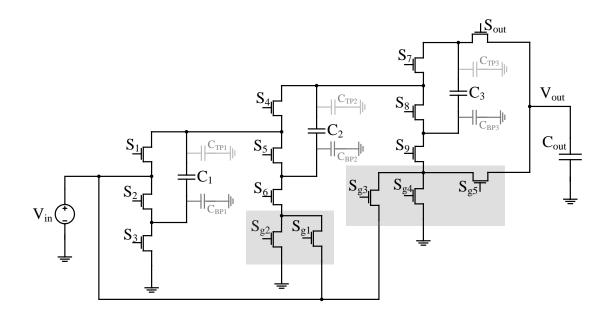

The second example considers the application discussed in chapter 1, where a variable FSC is required. As mentioned earlier, the miniaturized solar cell has a typical open voltage of  $0.3\sim0.6V$  and we want a regulated output voltage of 1.5V. Therefore, the VCR=5, 4, 3 and 5/2 are required. These VCRs are fed to the proposed code in section 3.2 to get the optimal circuit realization. This application needs only three flying capacitors using FSC topology. The SPTT gearbox code and number of switches are presented in Table 3.4. In this example, terminals 1, 2, and 5 preserve only one value along all circuit states which means *no switch* is required and the terminal is connected directly to its corresponding voltage node. In third terminal, however, the rows are toggling between *zero* and *one* which means *two switches* are required. For the forth terminal, the rows are changed between all voltage nodes which means *three switches* are required. Also by using *FSC synthesizer* as shown Figure 3.2, this converter requires three flying capacitors and five transistors for the gearbox control. Note that, due to the presence of all VCR in their simplest form, a zero resolution is chosen. The

SC converter realization is drawn in Figure 3.3. Note that,  $S_{g1} - S_{g5}$  transistors<sup>2</sup> configure the SC converter to change VCR if needed. Also, they are the only transistors that are controlled in closed loop, all other switches are driven by simple two complementary nonoverlapping clocks that are enabled when the converter starts up. This converter will be used in next chapters as a case study to implement variable FSC in both discrete and IC implementation.

Figure 3.2: Terminal assignments using FSC Synthesizer for variable FSC with VCR=5, 3, 4, 5/2.

## 3.3.3 Variable FSC Converter with VCR=1, 3/4, 2/3

The complexity of the converter control circuit is also another issue in SC converter design and can be related to the number of driving signals generated in close loop. Therefore, the less number of closed loop driving signals the simpler is the control circuit. We claim that

<sup>&</sup>lt;sup>2</sup>Note that,  $M_x$  and  $S_x$  are exchangeably used throughout this dissertation.

| Terminal           | $t_1$ | $t_2$ | $t_3$           | $t_4$                      | $t_5$ | Gain |

|--------------------|-------|-------|-----------------|----------------------------|-------|------|

| Weight             | 5     | -2    | -1              | -1                         | -1    | NA   |

| Final SPTT code    | 1     | 0     | 0               | 0                          | 2     | 5    |

|                    | 1     | 0     | 0               | 1                          | 2     | 4    |

|                    | 1     | 0     | 1               | 1                          | 2     | 3    |

|                    | 1     | 0     | 0               | 2                          | 2     | 5/2  |

| Number of Switches | 0     | 0     | 2               | 3                          | 0     | NA   |

| Voltage nodes      | Vin   | gnd   | $V_{in}$<br>gnd | $V_{in} \\ V_{out} \\ gnd$ | Vout  | NA   |

Table 3.4: Optimized realization for variable FSC with VCR=5, 4, 3, 5/2

Figure 3.3: Variable FSC with VCR=5, 3, 4, 5/2.

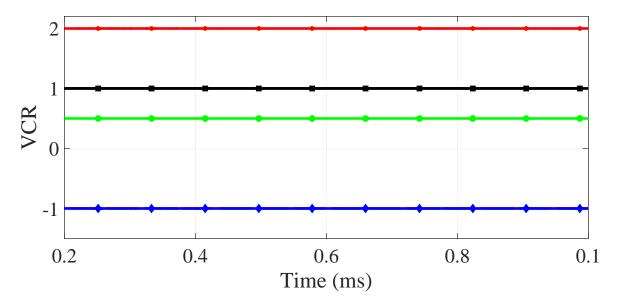

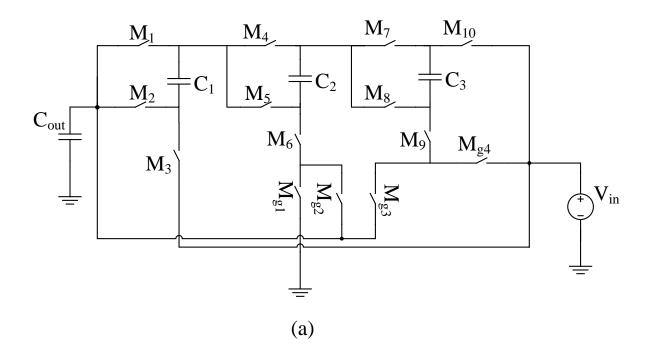

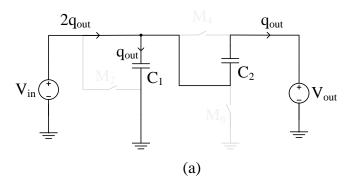

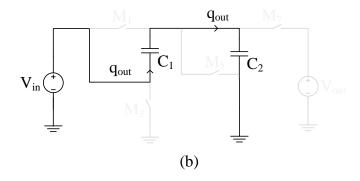

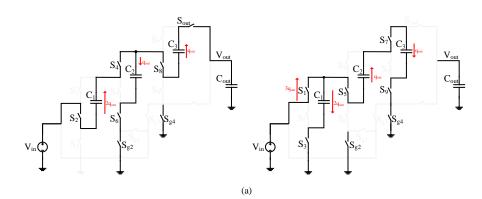

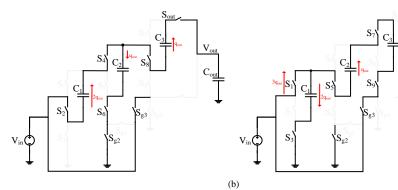

by using the proposed algorithm, the simplest controller circuit is achieved. We illustrate by comparing the control circuit of a buck converter that has three VCR (1, 3/4, 2/3) implemented using our method and the same converter in the literature implemented in ad-hoc way [21]. Implementing this buck converter using our methodology resulted in a circuit shown in Figure 3.4(a) with an LUT shown in Table 3.5. In [21], three capacitors and 13 switches were used to realize a buck converter with VCR = (1, 3/4, 2/3) with an LUT control signals shown in Table 3.6, their circuit realization is redrawn in Figure 3.4 (b). With a close look to the switch signals in Tables 3.5 and 3.6, one can see that ten switches (all except  $M_1, M_3$  and  $M_5$ ) of the circuit in Figure 3.4(b) need to be controlled in a closed-loop, i.e. they are not just a simple on-off (two states) control. On the other hand and for the same VCR, only four switches (  $M_{g1}-M_{g4})$  are controlled adaptively as illustrated in Table 3.5 using the proposed method. Not only that, but also each two switches among the four are complementary,  $M_{g1} = \bar{M}_{g2}$  and  $M_{g3} = \bar{M}_{g4}$ . Thus, only two signals are required to control the gearbox switches. Other switches,  $M_{1-10}$ , are controlled by the non-overlapping clocks  $(\phi_1 \text{ and } \phi_2)$  directly. This greatly simplifies the converter control unit.

| VCR              | 1        | 3/4      | 2/3      |

|------------------|----------|----------|----------|

| $M_{1-10(odd)}$  | $\phi_1$ | $\phi_1$ | $\phi_1$ |

| $M_{1-10(even)}$ | $\phi_2$ | $\phi_2$ | $\phi_2$ |

| $M_{g1}$         | 0        | 1        | 1        |

| $M_{g2}$         | 1        | 0        | 0        |

| $M_{g3}$         | 1        | 1        | 0        |

| $M_{g4}$         | 0        | 0        | 1        |

Table 3.5: LUT for converter synthesized by proposed method

Figure 3.4: Buck SC converter with VCR=1, 3/4, 2/3: (a) FSC topology using proposed method. (b) Converter proposed in [21].

| VCR             | 1        | 3/4      | 2/3      |

|-----------------|----------|----------|----------|

| $M_1$           | $\phi_1$ | $\phi_1$ | $\phi_1$ |

| $M_2$           | 0        | $\phi_1$ | $\phi_1$ |

| $M_3$           | $\phi_2$ | $\phi_2$ | $\phi_2$ |

| $M_4$           | 1        | 0        | 0        |

| $M_5$           | $\phi_1$ | $\phi_1$ | $\phi_1$ |

| $M_6$           | 0        | $\phi_1$ | $\phi_1$ |

| $M_7$           | $\phi_2$ | 0        | 0        |

| $M_8$           | 1        | 0        | $\phi_2$ |

| $M_9$           | 0        | $\phi_2$ | $\phi_2$ |

| $M_{10}$        | 0        | $\phi_1$ | $\phi_2$ |

| M <sub>11</sub> | 0        | $\phi_1$ | 0        |

| $M_{12}$        | 0        | $\phi_2$ | 0        |

| $M_{13}$        | 0        | $\phi_2$ | 0        |

Table 3.6: LUT for converter in [21]

## 3.4 Summary

The SC converter synthesis problem is introduced and solutions are discussed. The proposed algorithm achieves an optimal SC realization for mulit-VCR in almost no time which makes it desirable as a fast tool to synthesize SC converters. As practical examples, three cases were presented. The proposed method also simplifies the converter control by decreasing the number of close loop driving signals. A comparison between the control method for one converter found in literature and the other synthesized in the proposed method is discussed. For the same number of VCRs, it is found that the control of the proposed one is much easier compared to the other.

## Chapter 4

# Reconfigurable FSC Converter: Discrete Design

This chapter aims to study the design and implementation of discrete FSC converter. Although multi-phase FSC converters provide more VCR as discussed earlier, the two-phases FSC are to be considered in this work due their simplicity in design and control. The discrete differs from the IC integration in terms of power loss analysis and components selection.

## 4.1 Theoretical Analysis

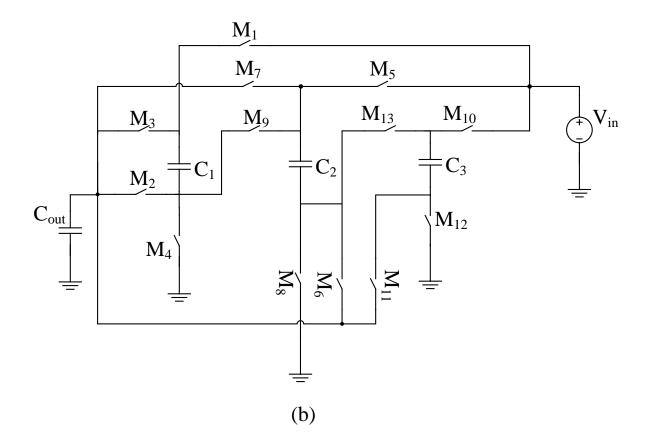

The SC converter equivalent circuit is shown in Figure 4.1. It consists of an ideal conversion term (n = VCR), and equivalent impedance  $(R_{eq})$  which models all switch turn-on resistances and charge redistribution in the flying capacitors. The output voltage can be calculated using the following equation:

$$V_{out} = nV_{in}\frac{1}{1+\frac{R_{eq}}{R_L}}.$$

(4.1)

Figure 4.1: SC converter steady state model.

#### 4.1.1 Converter Equivalent Resistance

There are enormous published works trying to improve the SC models. Some models are summarized and compared in recent work [22]. The model proposed in [23] will be utilized in this paper due to its generic nature and easy implementation for complex SC topologies like FSC. Also, it provides useful insight to component sizing and converter optimization.

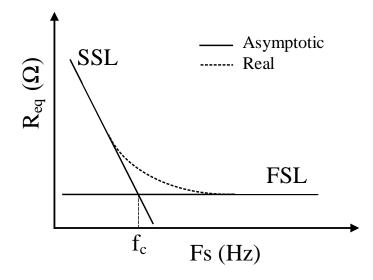

There are two switching limits for  $R_{eq}$  as shown in Figure 4.2: slow switching limit (SSL) and fast switching limit (FSL) [23–26]. The slow switching occurs when the switching period  $(T_s)$  is less than the flying capacitor time constant ( $\tau_c = RC_{fly}$ ), in other words  $f_s < f_c$ as illustrated in Figure 4.2, and the switches in SSL region can be assumed to be ideal, i.e  $R_{ron} = 0$  and  $R_{roff} = \infty$ . On the other hand, the fast switching spans the region where  $f_s$  is much higher than  $f_c$ , and  $R_{eq}$  is minimized. In fact,  $R_{FSL}$ , which is the converter impedance at FSL, is considered the minimum impedance value a converter can achieve. Nevertheless, the converter is usually operated around  $f_c$  or less to avoid high switching loss and achieve smooth charge transfer. In fast switching mode, the flying capacitor can be modeled as an ideal voltage source, which implies there is no charge loss in charging and discharging the capacitor or so-called charge redistribution loss [16]. To get an optimal equivalent resistance, both switching regions need to be considered. The converter impedance at SSL and FSL,  $R_{SSL}$  and  $R_{FSL}$ , and the total converter equivalent resistor  $(R_{eq})$  can be calculated as following:

$$R_{SSL} = \sum_{i=1}^{k} \frac{(a_{c_i}^2)}{C_i f_s},$$

(4.2)

$$R_{FSL} = \sum_{j=1}^{m} \frac{(a_{r_j}^2) R_{on_j}}{D_j},$$

(4.3)

$$R_{eq} = \sqrt{R_{SSL}^2 + R_{FSL}^2},\tag{4.4}$$

where where  $f_s$  is the switching frequency,  $R_{on}$  is the switch turn-on resistance, D is the duty ratio of the gate signals which is normally equals 0.5, k is the number of flying capacitors and m is the number of switches. The  $a_{c_i}$  and  $a_{r_j}$  are the charge multiplier of the  $i^{th}$  capacitor and the  $j^{th}$  switch respectively.

Figure 4.2: SC converter equivalent impedance vs switching frequency.

The charge multiplier vectors,  $a_r$  and  $a_c$ , relate the charge flows into the capacitor and switch to the output charge, meaning  $a_{rj} = q_{rj}/q_{out}$  and  $a_{ci} = q_{ci}/q_{out}$ . The charge vectors are very useful in converter optimization as will be discussed later. To find the charge vectors, sub-vectors  $a_{r,c}^1$  and  $a_{r,c}^2$  which define the charge vectors in each phase, need to be determined by drawing the converter in each state and finding the charge in each element. Due to the charge conservation, the following equations;  $q_{out}^1 + q_{out}^2 = 1$  and  $a_{rj,ci}^1 + a_{rj,ci}^2 = 0$ , helps identifying the charge quantity in each phase. Then,  $a_{ci}$  can be found by taking the absolute value of  $a_{ci}^1$ . Likewise,  $a_{rj}$  can be determined by taking the corresponding nonzero element in  $a_{rj}^1$  and  $a_{rj}^2$ .

Figure 4.3: FSC converter with VCR=3.

To follow with theoretical analysis, an example of FSC converter with VCR equals three is shown in Figure 4.3. The converter has two states as shown in Figure 4.4, which will be used to compose  $a_{c,r}^1$ ,  $a_{c,r}^2$  and  $a_{c,r}$  as following:

$$\begin{bmatrix} a_{c_1}^1 & a_{c_2}^1 \\ a_{c_1}^2 & a_{c_2}^2 \end{bmatrix} = \begin{bmatrix} 1 & -1 \\ -1 & 1 \end{bmatrix}$$

Figure 4.4: FSC converter with VCR=3: (a) state I,  $S_a=1$ ,  $S_b=0$ . (b) state II,  $S_a=0$   $S_b=1$ .

$$\implies a_{c} = \begin{bmatrix} 1 & 1 \end{bmatrix}$$

$$a_{r_{1}}^{1} a_{r_{2}}^{1} a_{r_{3}}^{1} a_{r_{4}}^{1} a_{r_{5}}^{1} a_{r_{6}}^{1} a_{r_{7}}^{1} \\ a_{r_{1}}^{2} a_{r_{2}}^{2} a_{r_{3}}^{2} a_{r_{4}}^{2} a_{r_{5}}^{2} a_{r_{6}}^{2} a_{r_{7}}^{2} \end{bmatrix} = \begin{bmatrix} 2 & 0 & 1 & 0 & 1 & 0 & 1 \\ 0 & 1 & 0 & 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 & 0 & 1 & 0 \end{bmatrix}$$

$$\implies a_{r} = \begin{bmatrix} 2 & 1 & 1 & 1 & 1 & 1 \end{bmatrix}$$

$$(4.6)$$

In this work, a blocking voltage vector is also introduced,  $a_{v_{c,r}}$ . This vector defines the blocking and rated voltages for the capacitors and switches with respect to the output voltage,  $a_{v_{c,r}} = V_{c,r}/V_{out}$ . To do this, we first find  $V_{c,r}$  in terms of  $V_{in}$ , and then divide by VCR to get  $V_{c,r}$  as a function of  $V_{out}$ . Also, we could find  $V_{c,r}$  in terms of  $V_{out}$  in one step by reversing the analysis. Note that, all previous analysis is related to the output voltage and charge. Therefore, we need  $V_{c,r}$  to be as a function of  $V_{out}$  to be consistent and get a meaningful results that helps analyzing and optimizing the converter. For the switches, the blocking voltage is the maximum voltage which the switch can withstands without breaking out, and usually determined during the off state. Likewise, the blocking voltage for the capacitor is defined to be the maximum voltage across the capacitor in both states. Defining the blocking voltage vectors is very useful in power analysis calculation which will be discussed in the next section. As an example, let us consider the converter discussed earlier (Figure 4.3),  $a_{vc,r}$  can be found as following:

$$\begin{bmatrix} a_{vc_1}^1 & a_{vc_2}^1 \\ a_{vc_1}^2 & a_{vc_2}^2 \end{bmatrix} = \begin{bmatrix} 1/3 & 2/3 \\ 1/3 & 2/3 \end{bmatrix}$$

$$\implies a_{vc} = \begin{bmatrix} 1/3 & 2/3 \end{bmatrix}$$

(4.7)

$$\begin{bmatrix} a_{vr_1}^1 & a_{vr_2}^1 & a_{vr_3}^1 & a_{vr_4}^1 & a_{vr_5}^1 & a_{vr_6}^1 & a_{vr_7}^1 \\ a_{vr_1}^2 & a_{vr_2}^2 & a_{vr_3}^2 & a_{vr_4}^2 & a_{vr_5}^2 & a_{vr_6}^2 & a_{vr_7}^2 \end{bmatrix} = \begin{bmatrix} 0 & 1/3 & 0 & 2/3 & 0 & 1/3 & 0 \\ 1/3 & 0 & 1/3 & 0 & 2/3 & 0 & 1/3 \end{bmatrix}$$

$$\implies a_{vr} = \begin{bmatrix} 1/3 & 1/3 & 1/3 & 2/3 & 2/3 & 1/3 & 1/3 \end{bmatrix}$$

(4.8)

Finally and to have a concrete theoretical analysis, let us study the optimized converter expressions. The optimization procedure proposed in [24] explicitly derived the expressions of optimized  $R^*_{SSL}$  and  $R^*_{FSL}$  based on  $a_c$  and  $a_r$  respectively. This optimization minimizes  $P_{loss}$  by sizing the flying capacitor and transistors according to  $a_c$  and  $a_r$  vectors. Therefore,  $R_{SSL}^*$  and  $R_{FSL}^*$  can be calculated as following:

$$R_{SSL}^* = \frac{1}{C_t f_s} (\sum_{i=1}^k a_{c_i})^2, \tag{4.9}$$

$$R_{FSL}^* = 2R_{on_t} (\sum_{j=1}^m a_{r_j})^2, \tag{4.10}$$

$$C_i^* = \frac{a_{c_i}}{\sum_k a_{c_k}} C_t, \tag{4.11}$$

$$R_{on_j}^* = \frac{\sum_m a_{r_m}}{a_{r_j}} R_{on_t},\tag{4.12}$$

where  $C_t$  is the total flying capacitance in the converter and  $R_{on_t}$  is the total turn-on resistances of all switches in the converter. For discrete implementation, (4.3) and (4.9) will be used to quantify  $R_{eq}$  because the switch turn-on resistance is fixed once the transistor is selected and hence it can not be optimized. The flying capacitors are sized using (4.11). The  $a_v$  and  $a_r$  vectors are useful for selecting suitable capacitor and switch rating.

#### 4.1.2 Power Loss Analysis

The efficiency in SC converters can be categorized into two parts: the voltage conversion efficiency (VCE) and power conversion efficiency (PCE or commonly  $\eta$ ). They can be quantified by the following equations:

$$VCE = \frac{V_{out}}{V_{out}^T},\tag{4.13}$$

$$\eta = \frac{P_{out}}{P_{out} + P_{loss}},\tag{4.14}$$

where  $V_{out}^{T}$  is the target output voltage, and equals  $nV_{in}$  seen across the secondary side of the ideal transformer in the average state model (Figure 4.1). Excluding the bottom-plate charge loss, the power losses ( $P_{loss}$ ) in low power SC converters are due to two main factors [27] as following:

1. Linear losses  $(P_{lin})$ : these include the conduction loss and charge redistribution loss in the flying capacitors. Due to their negligible effect, effective series resistor (ESR) of the flying capacitors, trace impedance are usually ignored. Then,  $P_{lin}$  can be calculated as following:

$$P_{lin} = I_{out}^2 R_{eq}, \tag{4.15}$$

$$\implies P_{lin} = I_{out}^2 \sqrt{\left[\frac{\left(\sum_{i=1}^k a_{c_i}\right)^2}{C_t f_s}\right]^2 + \left[2\sum_{j=1}^m (a_{r_j}^2)R_{on_j}\right]^2}.$$

(4.16)