# BUCK/BOOST CURRENT-SOURCE-INVERTER TOPOLOGIES, MODULATION AND APPLICATIONS IN HEV/EV MOTOR DRIVE

by

Qin Lei

# A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

**Electrical Engineering**

2012

#### **ABSTRACT**

# BUCK/BOOST CURRENT-SOURCE-INVERTER TOPOLOGIES, MODULATION AND APPLICATIONS IN HEV/EV MOTOR DRIVE

By

#### Oin Lei

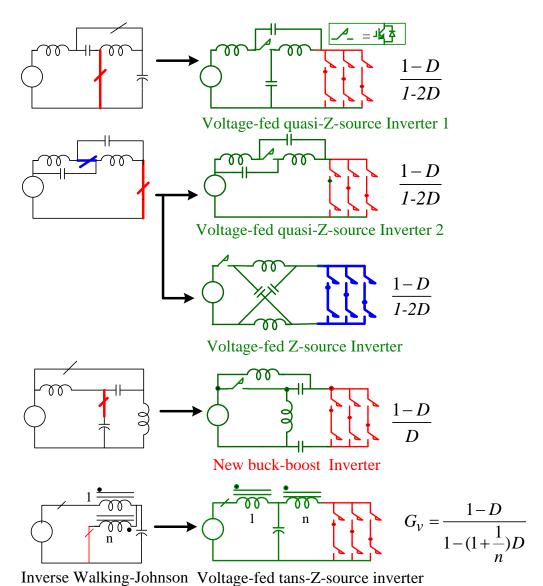

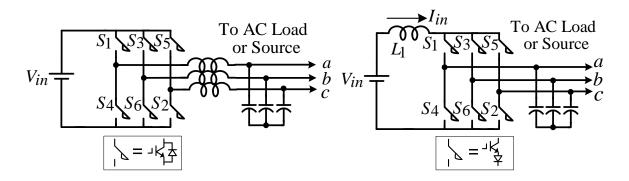

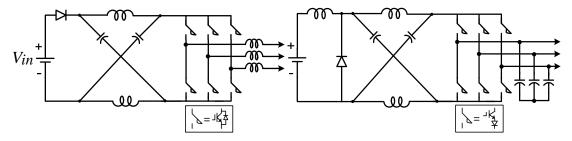

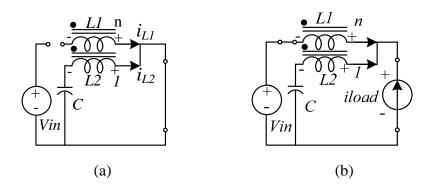

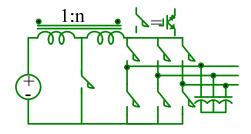

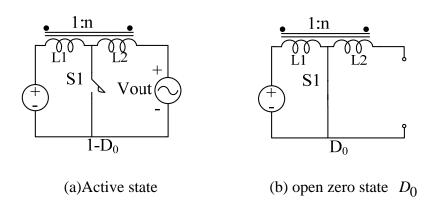

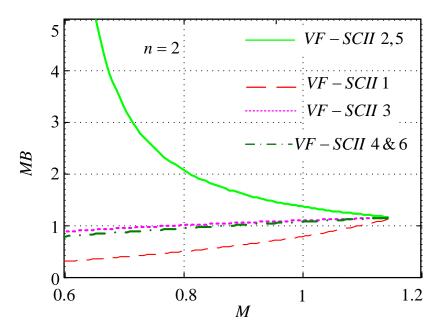

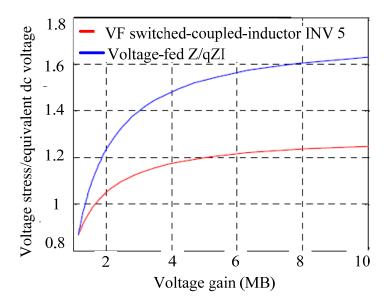

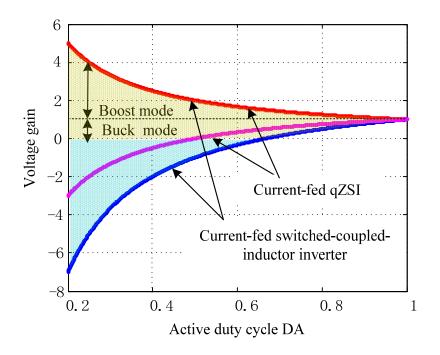

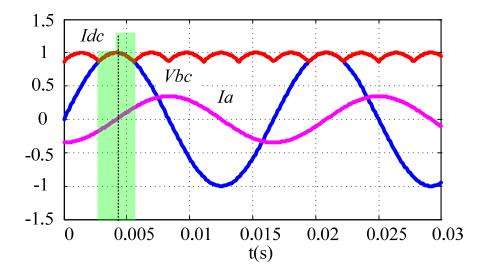

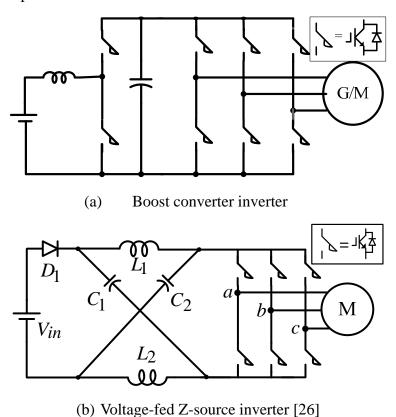

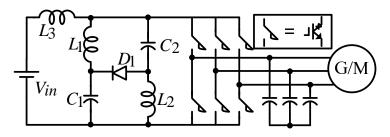

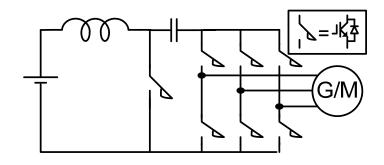

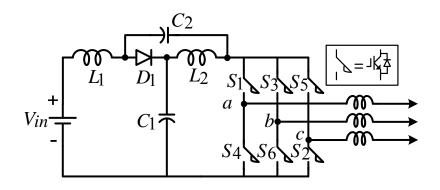

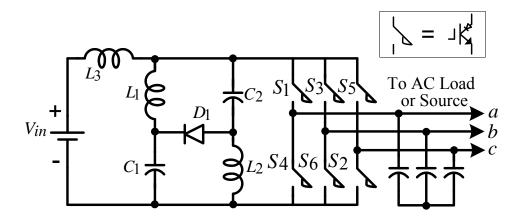

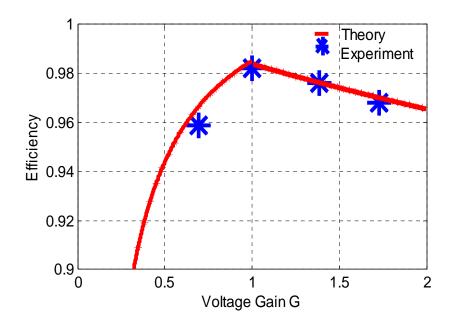

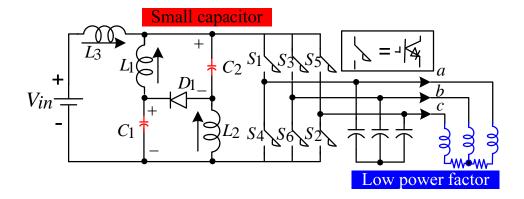

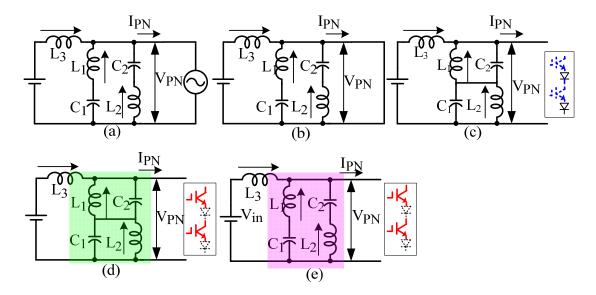

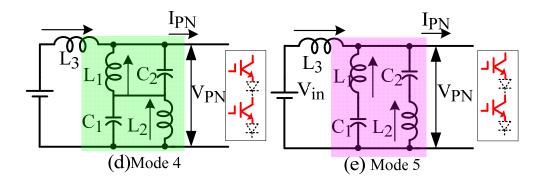

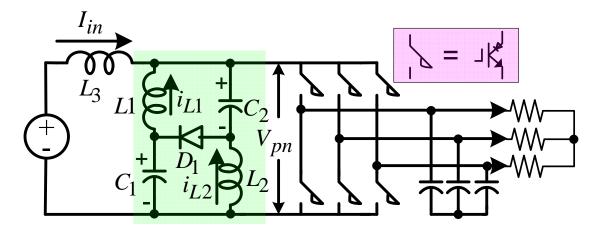

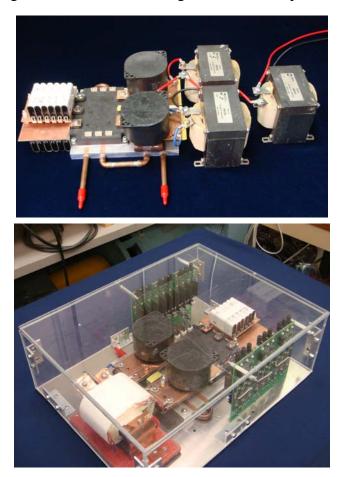

To provide higher boost ratio in motor drive or PV application, a new family of switched-coupled-inductor inverters has been proposed in this work, with voltage buck-boost function. The voltage-fed switched-coupled-inductor inverter has higher boost ratio and lower active device voltage stress than Z-source inverter at the same voltage gain, and has wider voltage buck/boost range than conventional boost-converter inverter. The current-fed switched-coupled-inductor inverter is a capacitor-less solution among the buck-boost inverters, which reduces the system size significantly. Compared to traditional boost-converter-inverter, it has less switch count, and less active device current stress. To achieve higher efficiency with a single-stage buck-boost inverter for HEV/EV motor drive application, a current-fed quasi-Z-source inverter topology has been selected and a 24kW prototype has been built in the lab. A zero vector placement technique in SVPWM has been proposed for this inverter to obtain lowest switching loss, lowest current ripple, lowest output harmonics and lowest voltage spike on the device in both constant torque and constant power operation regions, in order to achieve higher efficiency, higher power density and lower cost. A 24kW current-fed quasi-Z-source inverter has been built in the lab and tested. The full power rating efficiency reaches 97.6%, and peak efficiency reaches 98.2%, both of which have a 3%-4% improvement on traditional two stage configuration. The power density is 15.3KW/L, which also has 30% improvement on the commercial unit in HEV.

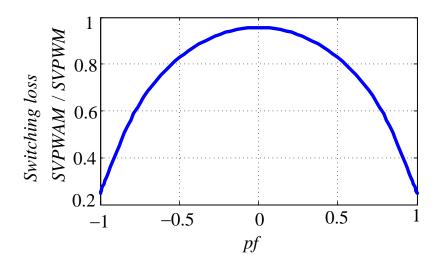

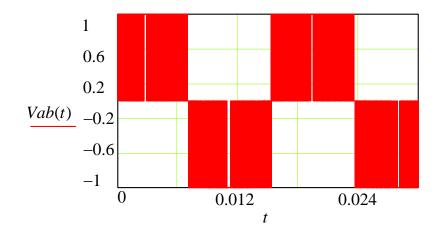

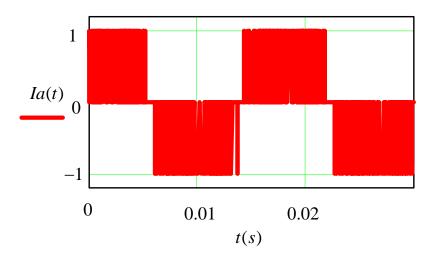

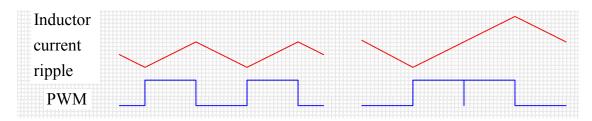

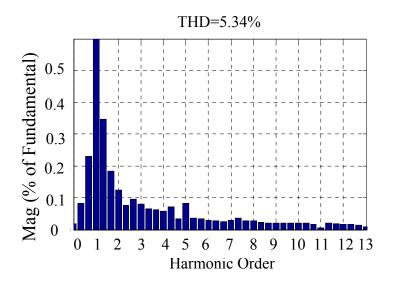

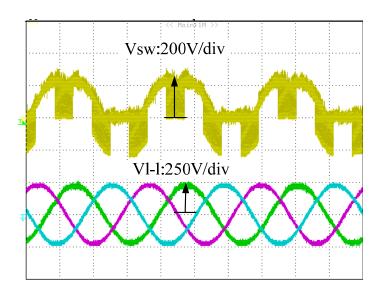

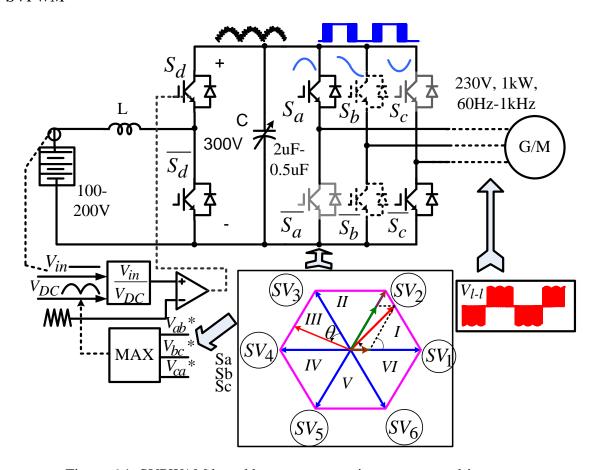

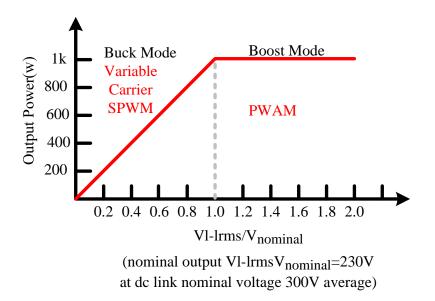

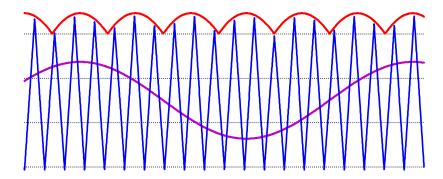

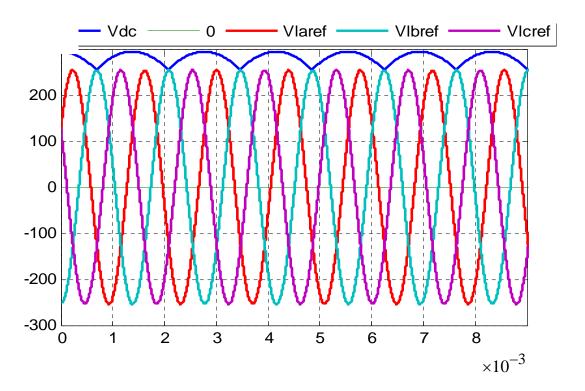

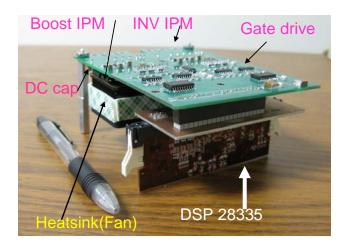

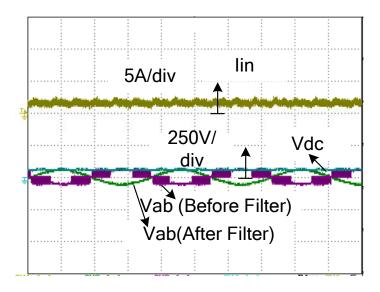

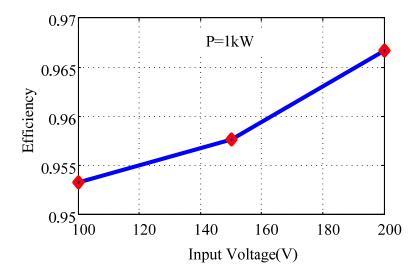

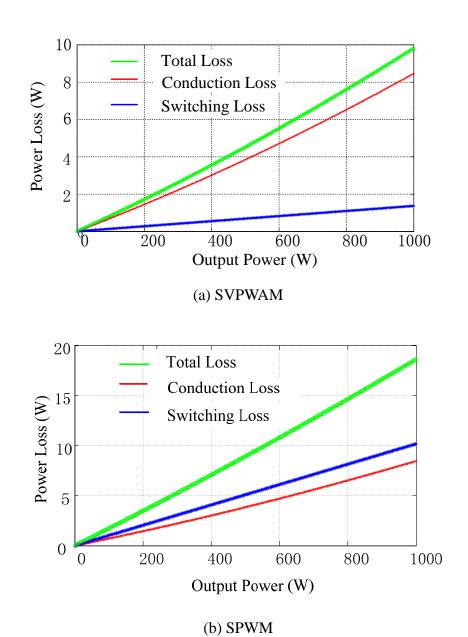

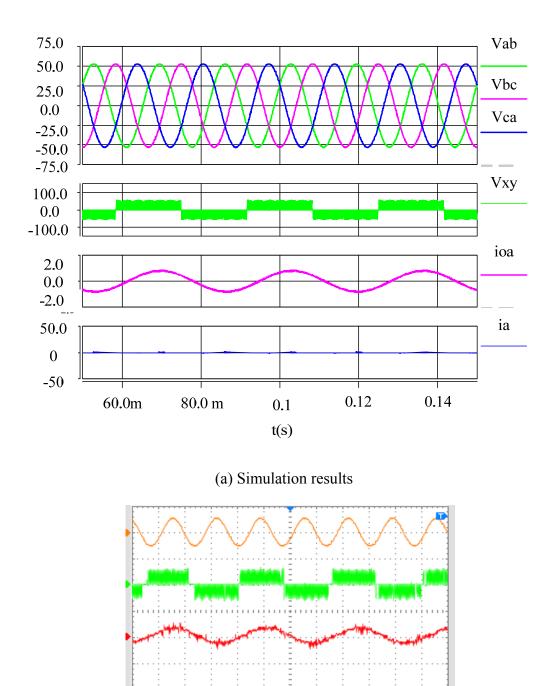

To achieve higher switching loss reduction, a Space-Vector-Pulse-Width-Amplitude Modulation (SVPWAM) method has been proposed for buck-boost current source inverter. By using this method, the switching loss is reduced by 60%, and the power density is increased by a factor of 2 to 3, with a less output harmonic distortion than normal SVPWM method. A 1 kW boost-converter-inverter prototype has been built and tested using this method. The overall system efficiency at full power rating reaches 96.7% and the whole system power density reaches 2.3 kW/L and 0.5 kW/lb, all of which are remarkable at this power rating. As a result, the proposed SVPWAM can make the buck-boost inverter suitable for applications that require high efficiency, high power density, high temperature, and low cost, such as EV motor drive or engine starter/alternator.

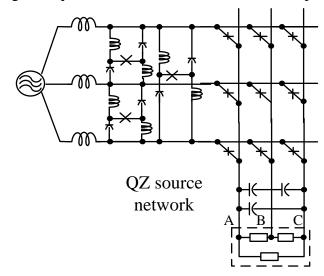

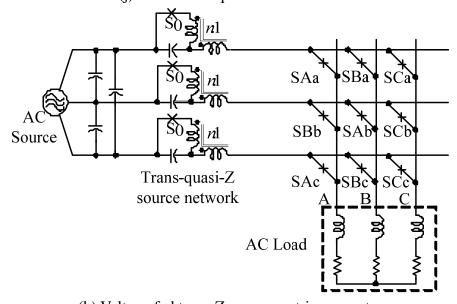

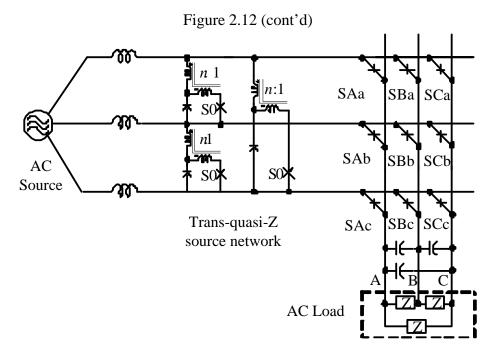

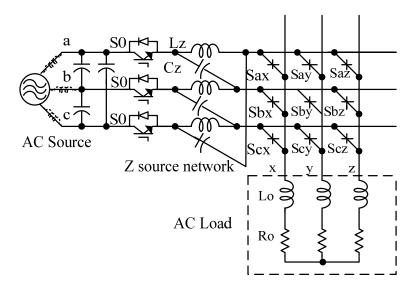

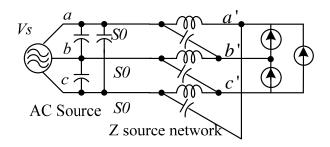

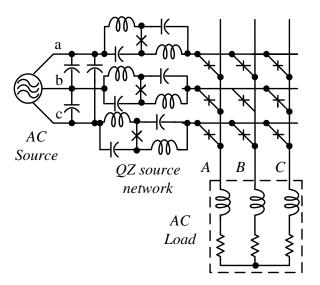

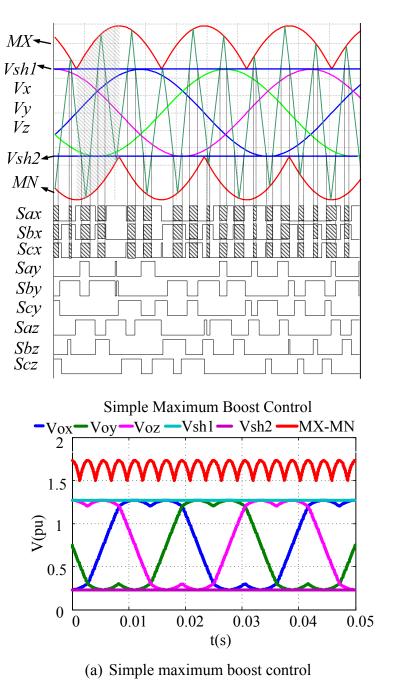

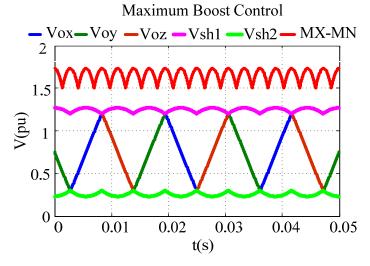

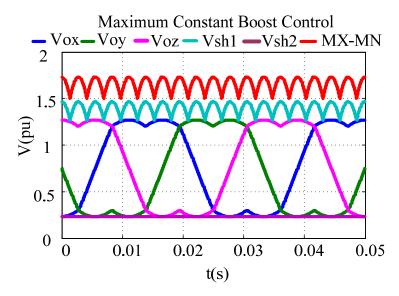

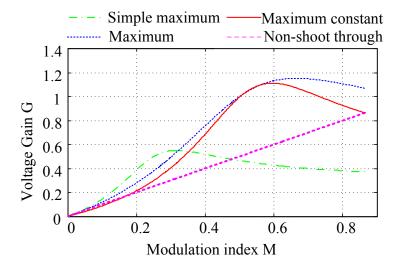

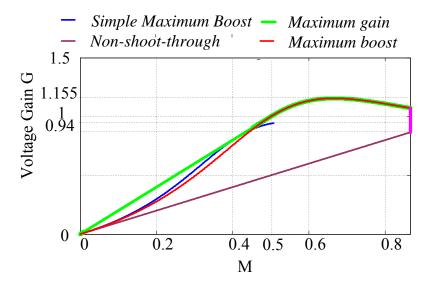

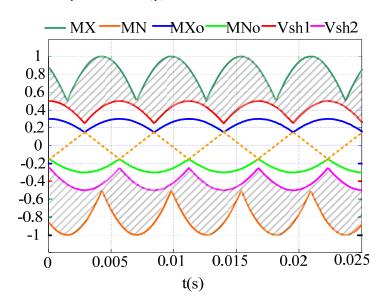

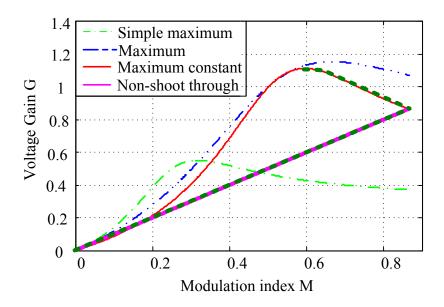

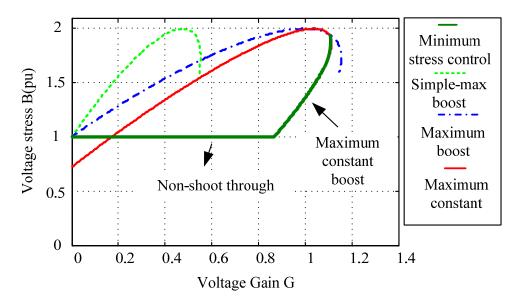

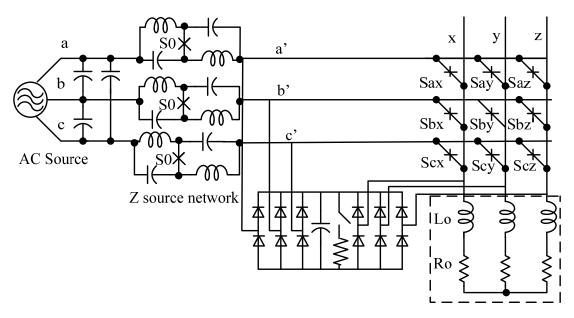

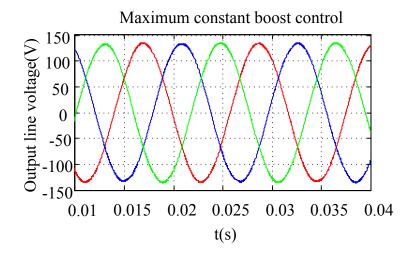

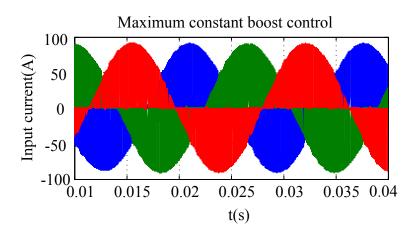

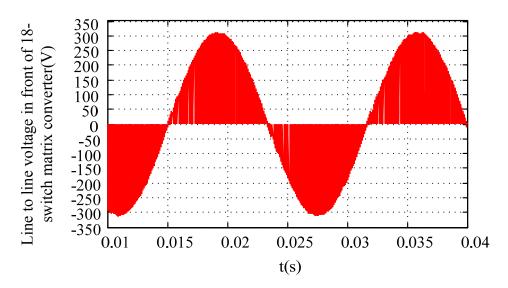

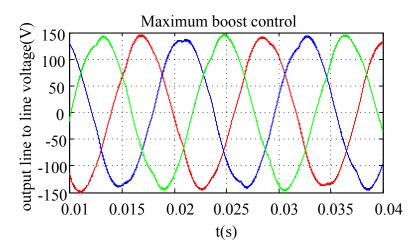

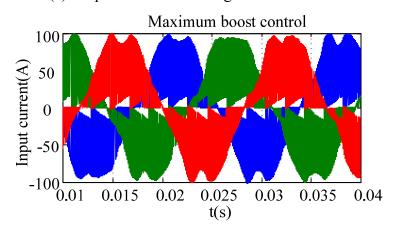

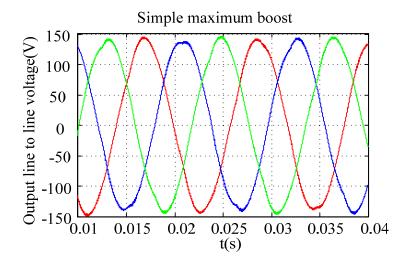

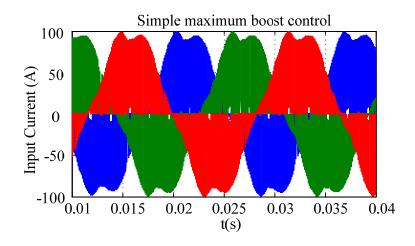

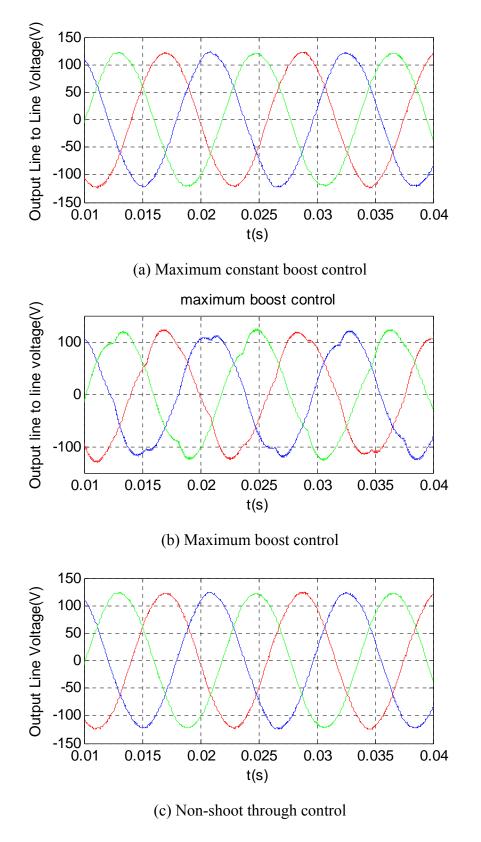

To implement buck-boost function on direct matrix converter, four control methods including simple maximum boost, maximum boost, maximum constant boost control and hybrid minimum stress control have been proposed for the newly proposed direct Z-source matrix converter, and verified with simulation/experiments.

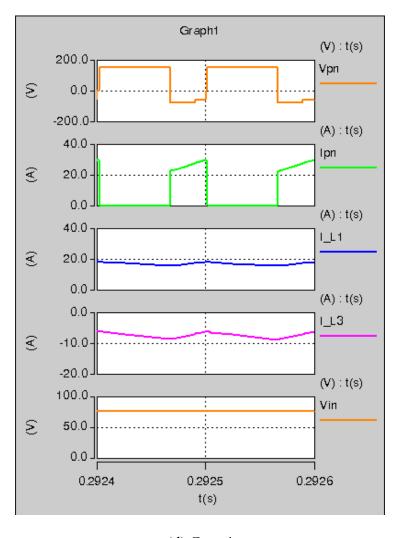

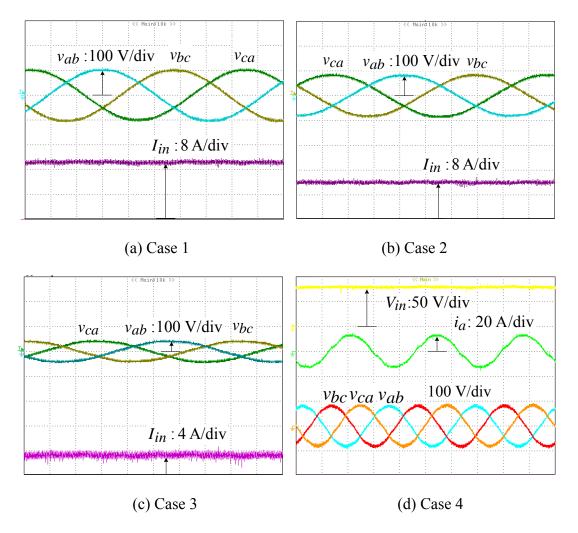

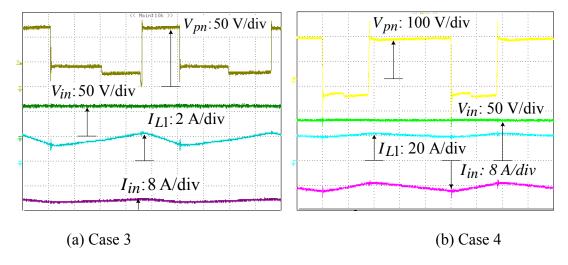

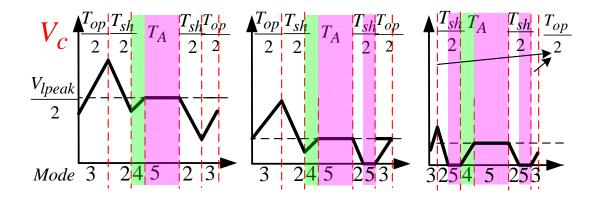

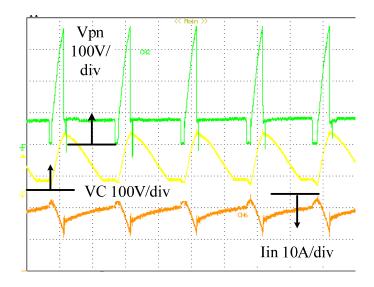

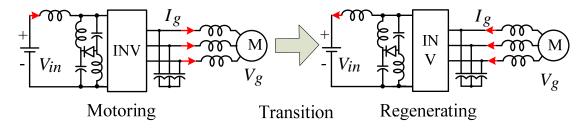

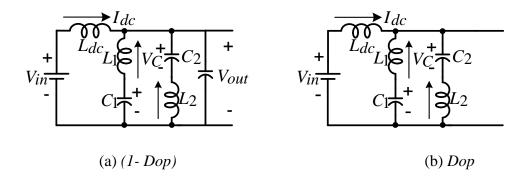

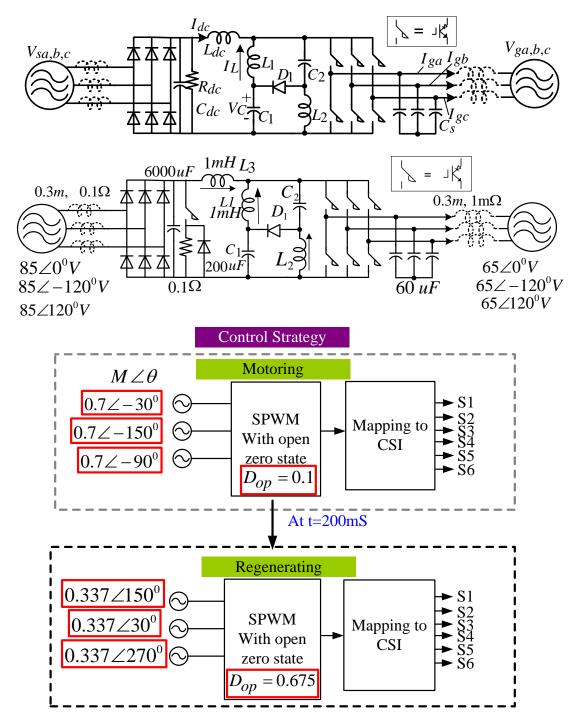

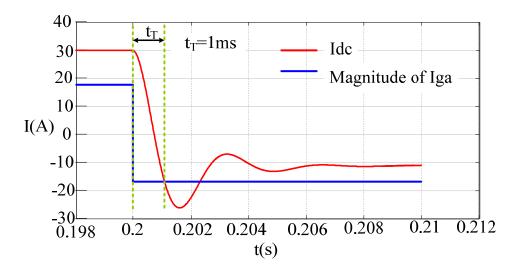

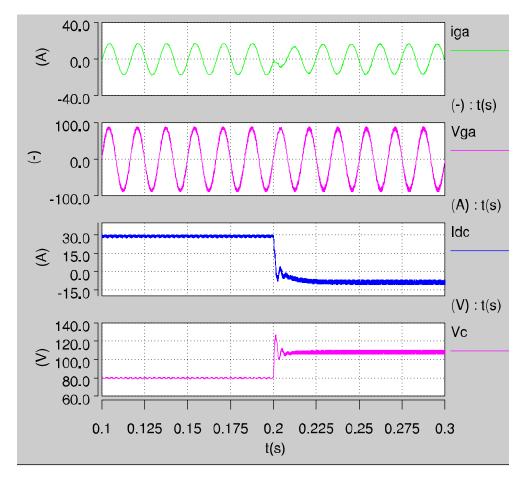

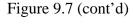

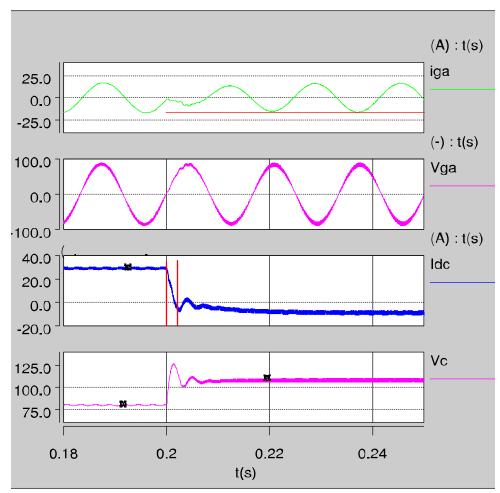

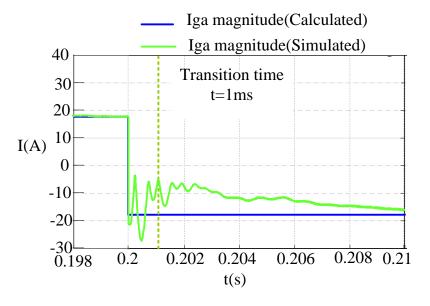

Two new discontinuous operation modes have been proposed for current-fed quasi-Z-source inverter topology. Simulation and experiment results are given to verify the theoretical analysis. A transient state-space model has been built for current-fed quasi-Z-source inverter to demonstrate its fast transient response in motoring and regenerating transition. The analytical, simulated and experimental results all show that the inverter only needs several switching cycle to complete the transition, which makes it suitable for HEV/EV motor drive application.

Dedicated to:

My parents, Chuping Lei and Airong Wang

My husband Junjun Xin,

And my brother Qiwei

#### **ACKNOWLEDGEMENTS**

I would like to thank all people who have helped and inspired me during my graduate study. I especially want to thank my advisor, Dr. Fang Z. Peng, for his guidance during my research and study. His perpetual energy and enthusiasm in research had motivated all his advisees, including me. His profound understanding and wide knowledge in power electronics field impressed me and made my research life become smooth and rewarding. I am also very grateful for my committee members, Dr. Bingsen Wang, Dr. Mitra Joydeep and Dr. Guoming Zhu for their suggestions and help.

All my lab buddies at the Power Electronics and Motor Drive Laboratory (PEMD) made it a convivial place to work. In particular, I would like to thank Dr. Shuitao Yang for his helpful guidance in the micro-grid project and current-fed quasi-Z-source inverter project. It is my great pleasure and fortune to work with him in the second year of graduate study. His intelligence, patient and tireless teaching guided me into and love this promising field. I also want to give my special thank to Dr Julio Cesar Rosas Caro, who is my first collaborator in this lab. He taught me many basic knowledge and practical skills in power electronics research, which is quite helpful in the whole process of my graduate study. I also would like to thank Dr. Dong Cao for his collaboration in the current-fed quasi-Z-source inverter project. His great passion for research and exigency for the results inspired me to think more and more and finally leaded to the success of the project.

Many thanks are also extended to my colleagues in PEMD Lab for their delightful discussions and friendship, Dr. Baoming Ge, Ms. Xi Lu, Mr. Shuai Jiang, Dr. Honnyong Cha, Mr. Xianhao Yu, Mr. Sisheng Liang, Dr. Wei Qian, Mr. Craig Rogers, Dr. Yi Huang, Mr. Joel Anderson, Mr. Jorge G. Cintron-Rivera, Dr. Uthane Supatti, Mr. Jianfeng Liu, in research and life through our interactions during the long hours in the lab. Thanks.

Finally and most importantly, I would like to thank my husband Junjun for his continuous support and encouragement, and numerous discussions. I also would like to thank my parents Chuping Lei and Airong Wang for their unconditional care for years. I also would like to thank my brother for his understanding and care. Their love to me and my love to them are the greatest motivation in my life.

# TABLE OF CONTENTS

| LIST | OF TABLES                                                                   | xi   |

|------|-----------------------------------------------------------------------------|------|

| LIST | OF FIGURES                                                                  | xiii |

| СНА  | APTER 1 INTRODUCTION                                                        | 1    |

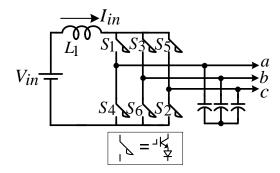

| 1.1. | Problems of conventional current source topology                            | 2    |

| 1.2. | Problems of conventional current source inverter modulation                 | 3    |

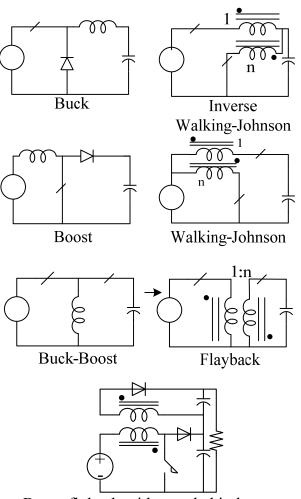

| 1.3. | Topology synthesis literature                                               | 7    |

|      | Problems of traditional matrix converter                                    |      |

| 1.5. | Scope of the dissertation                                                   | 9    |

| CHA  | APTER 2 CURRENT SOURCE INVERTER TOPOLOGIES                                  | 12   |

| 2.1. |                                                                             |      |

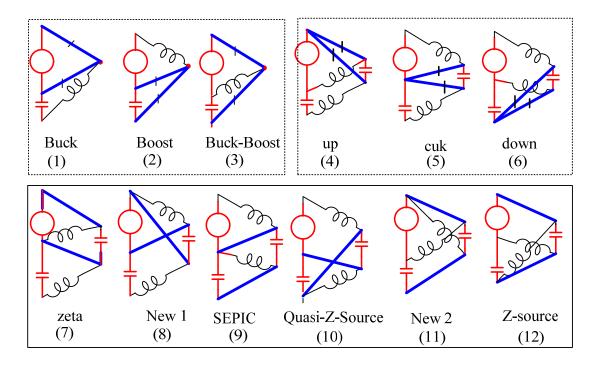

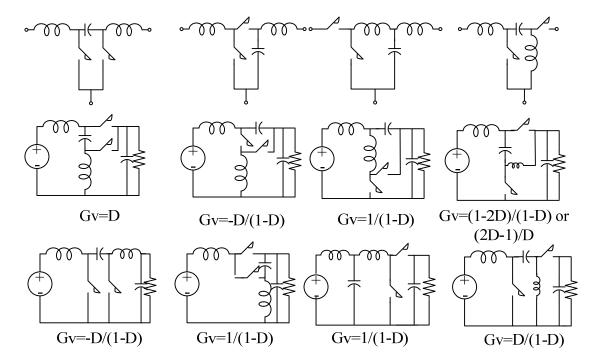

| 2.2. | Topology synthesis techniques                                               | 13   |

|      | 2.2.1. Graph Theory                                                         |      |

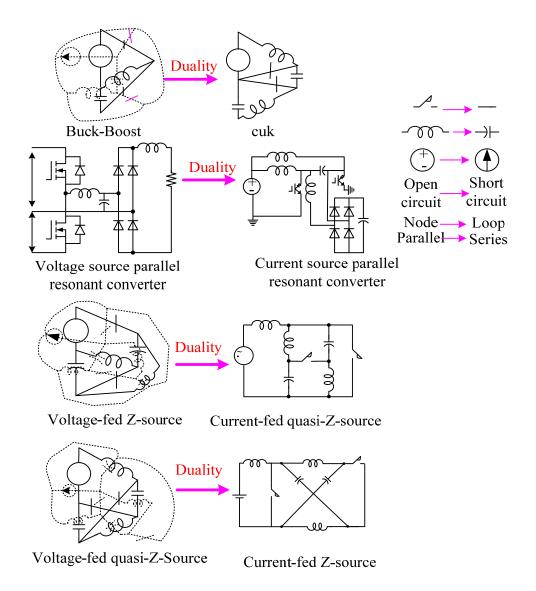

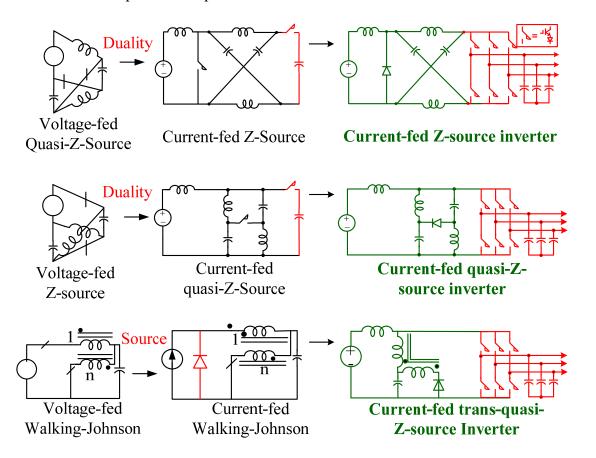

|      | 2.2.2. Duality                                                              |      |

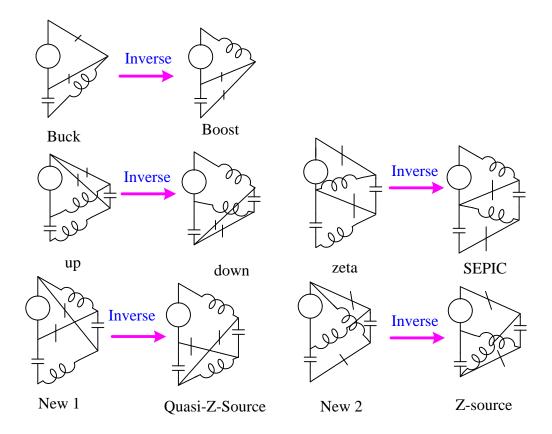

|      | 2.2.3. Bilateral inversion transformation                                   |      |

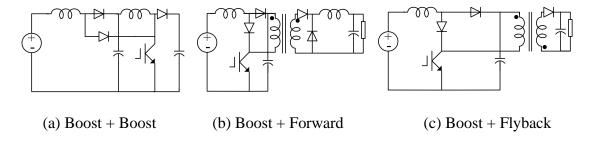

|      | 2.2.4. Cascade                                                              |      |

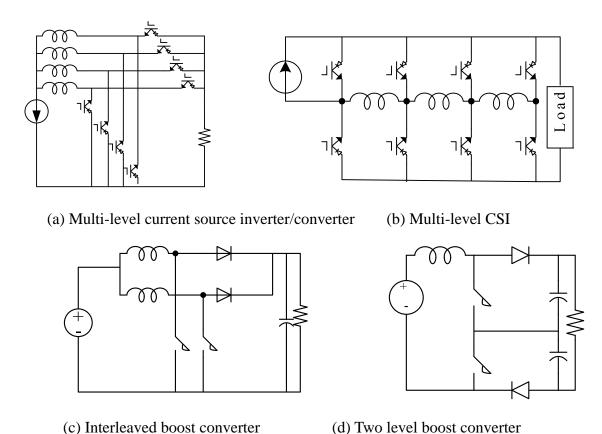

|      | 2.2.5. Parallel                                                             |      |

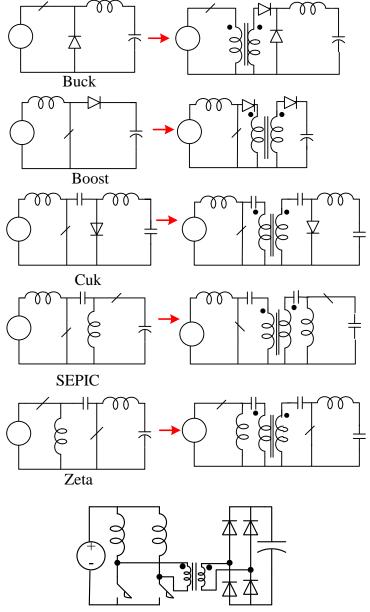

|      | 2.2.6. With transformers                                                    | _    |

|      | 2.2.7. Extension of canonical switching cell                                |      |

| 2.3. | Derivation of buck-boost Z-source inverters                                 |      |

| 2.4. | J U                                                                         |      |

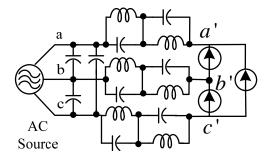

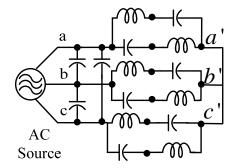

| 2.5. | Proposed switched-coupled-inductor inverter family with buck/boost function |      |

| 2.6. | 1 07                                                                        |      |

| 2.7. | Summary                                                                     | 37   |

| CHA  | APTER 3 STEADY STATE CIRCUIT ANALYSIS                                       |      |

| 3.1. | Introduction                                                                | _    |

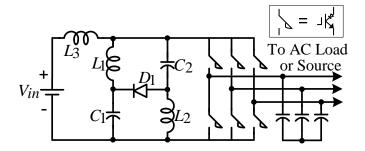

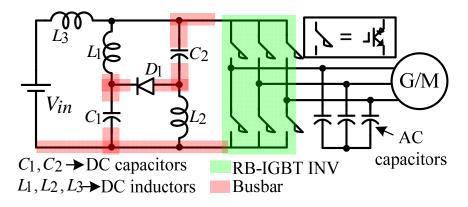

| 3.2. | Current-fed quasi-Z-source inverter                                         | 43   |

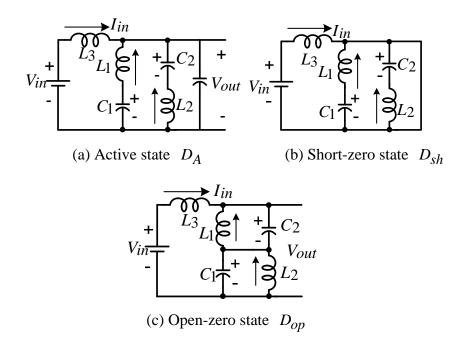

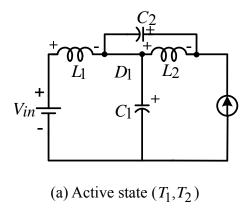

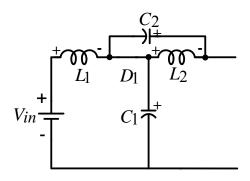

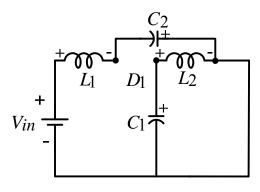

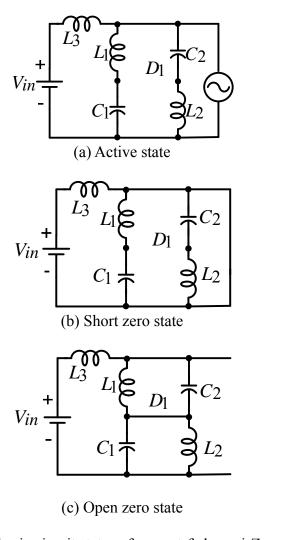

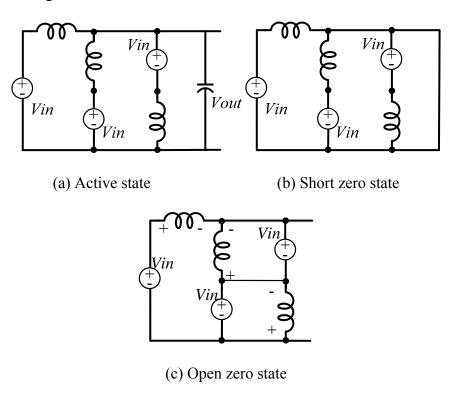

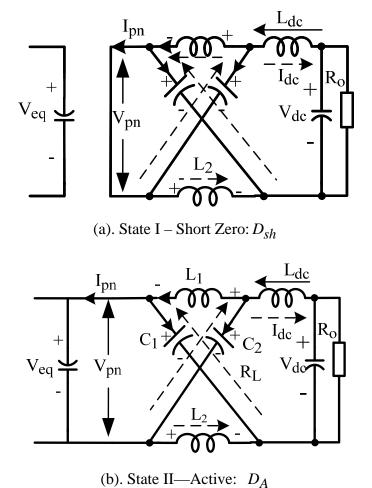

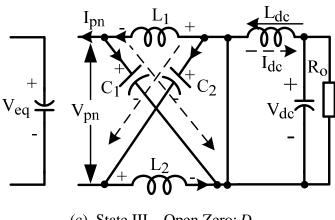

|      | 3.2.1. Equivalent circuit states                                            |      |

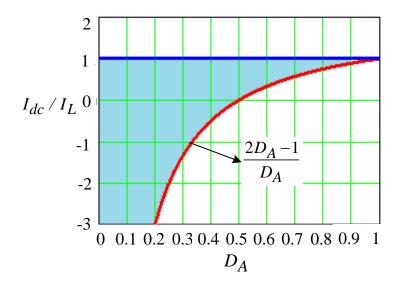

|      | 3.2.2. Voltage gain and current gain                                        |      |

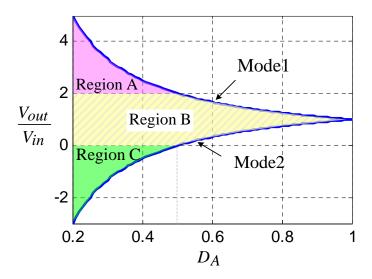

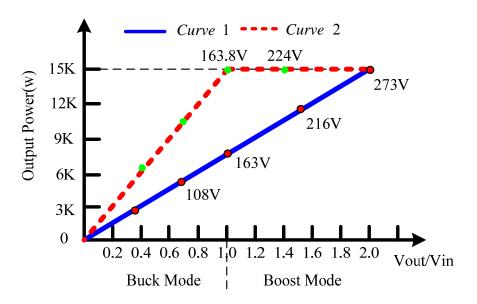

|      | 3.2.3. Operation regions                                                    |      |

|      | 3.2.4. Calculation of the ac output voltage and current                     |      |

|      | 3.2.5. Passive component stress and total switching device power rating     |      |

| 3.3. | Current-fed Z-source rectifier                                              |      |

|      | 3.3.1. Equivalent circuit states                                            | 54   |

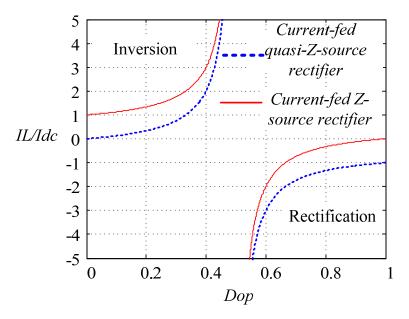

|      | 3.3.2. Voltage gain equation                                                |      |

|      | 3.3.3. Operation regions                                                    |      |

|      | 3.3.4. Calculation of the ac output voltage and current                     |      |

|      | 3.3.5. Design of Z-network L and C in continuous mode                       | 61   |

| 3.4. | 1                                                                           |      |

|      | 3.4.1. Voltage-fed switched-coupled-inductor inverter                       |      |

|      | 3.4.1.1. Equivalent circuit states                                          | 64   |

|      | 3.4.1.2. Voltage and current gain                                           |      |

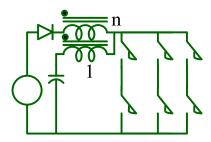

|      | 3.4.2. Current-fed Switched-Coupled-Inductor Inverter                       | 69   |

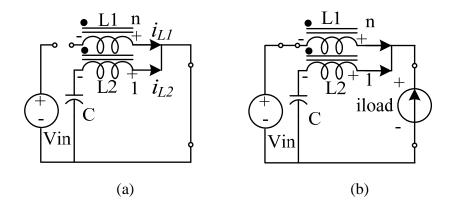

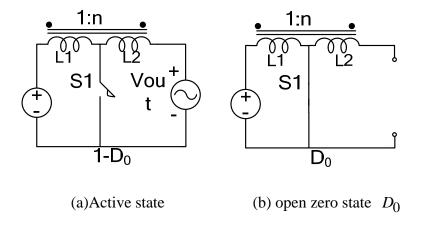

|      | 3.4.2.1. Equivalent circuit sates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | 3.4.2.2. Voltage gain and current gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69         |

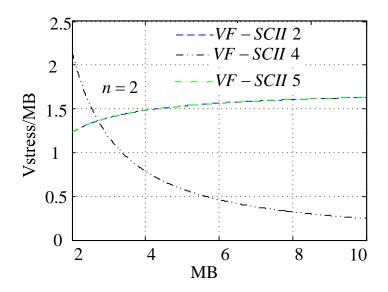

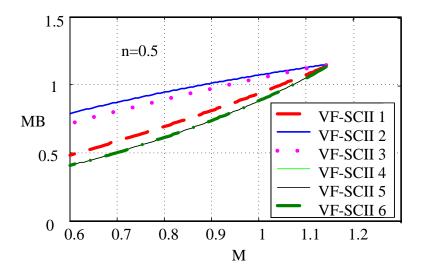

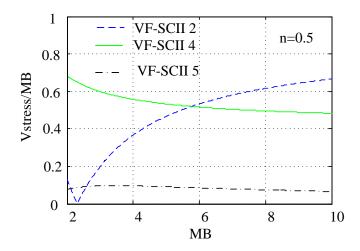

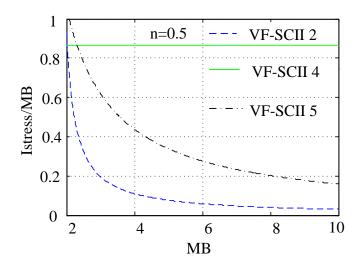

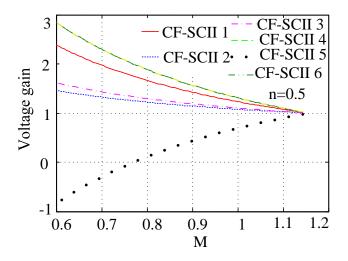

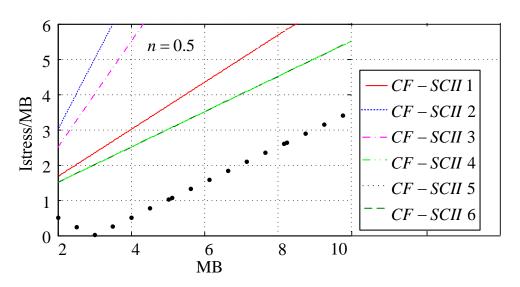

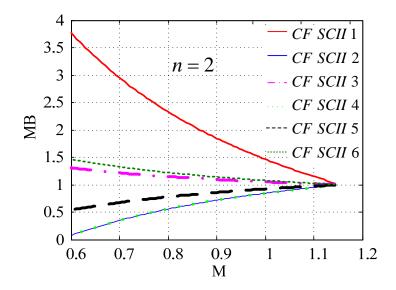

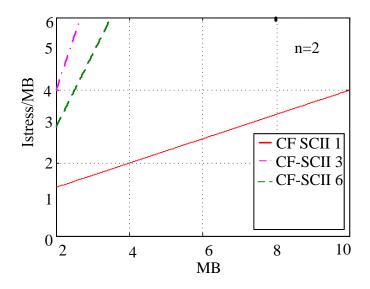

|      | 3.4.2.3. Voltage and current stress comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 71         |

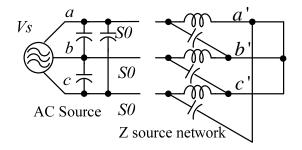

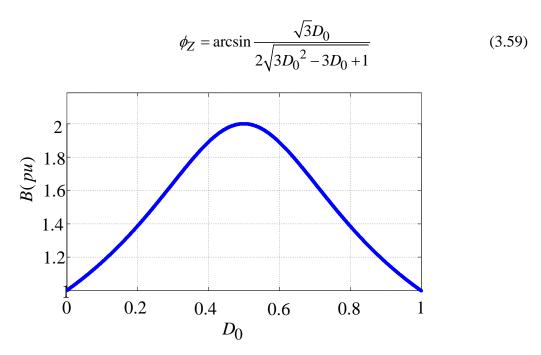

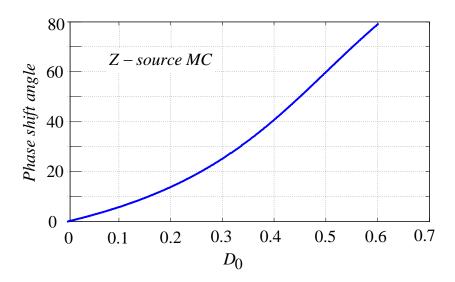

| 3.5. | Direct Z-source matrix converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 77         |

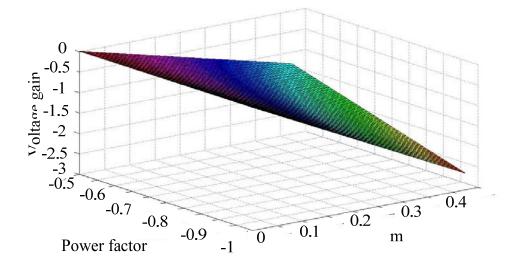

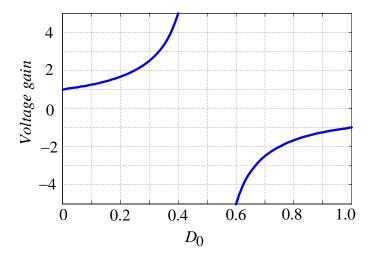

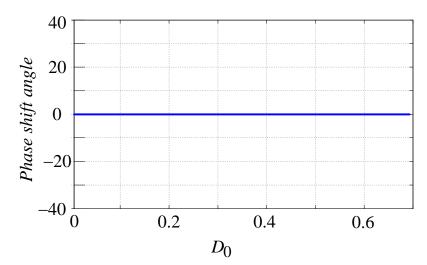

|      | 3.5.1. Voltage-fed Z-source matrix converter boost ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78         |

|      | 3.5.2. Voltage-fed quasi-Z-source matrix converter boost ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83         |

| 3.6. | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87         |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|      | APTER 4 MODULATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

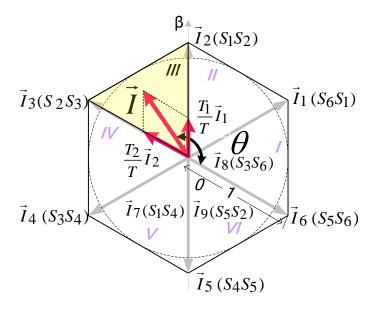

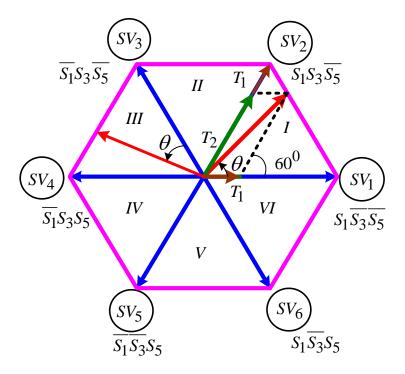

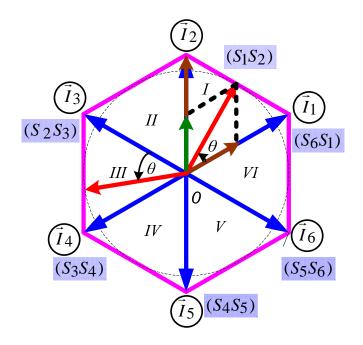

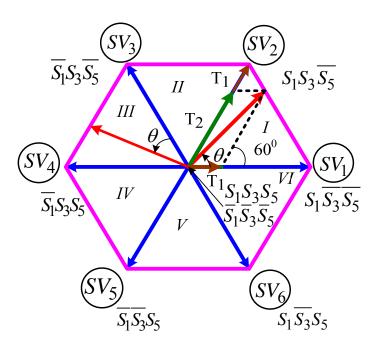

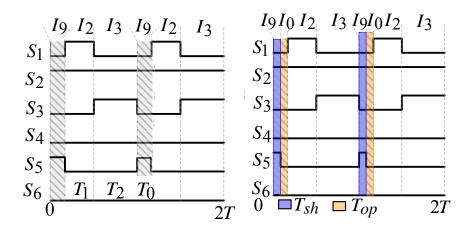

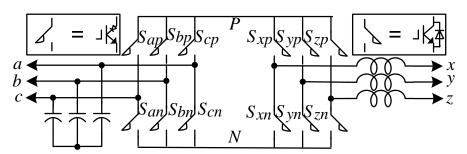

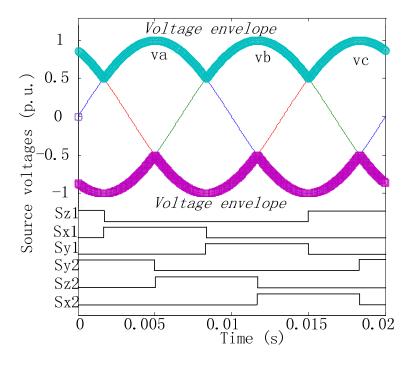

| 4.2. | Discontinuous SVPWM and Equivalent Carrier-based modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

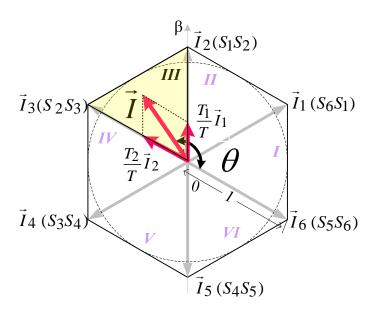

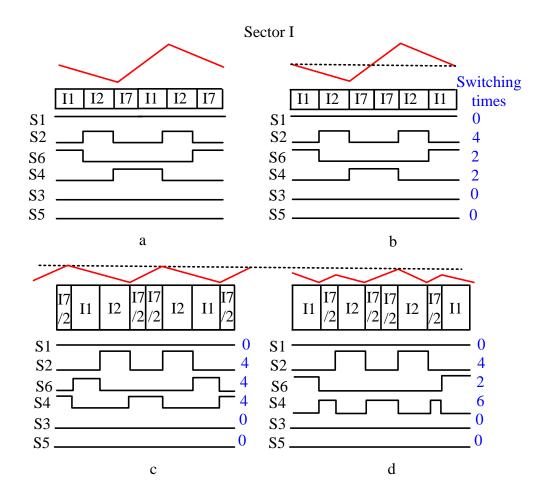

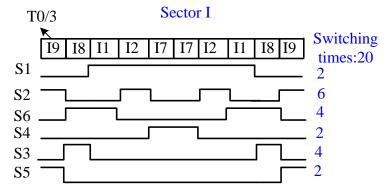

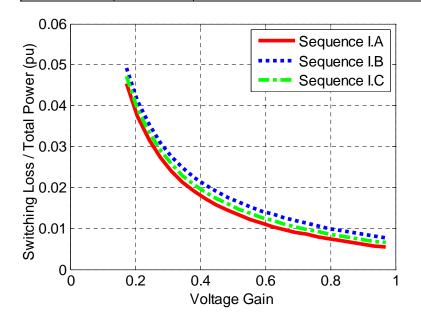

|      | 4.2.1. Selection of zero vector in terms of minimum switching times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

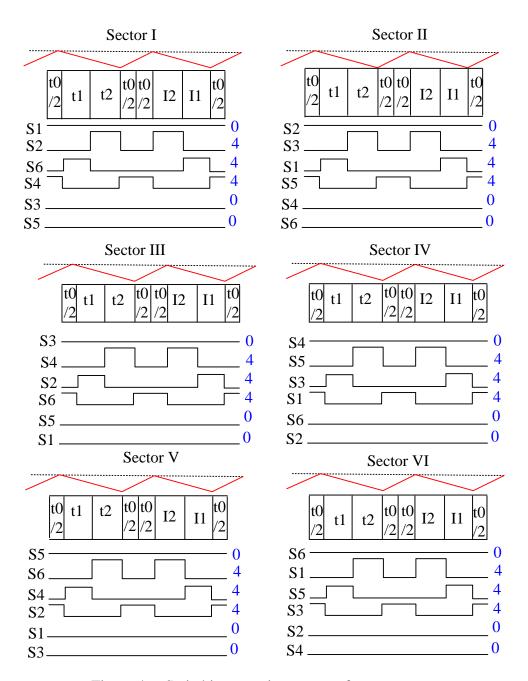

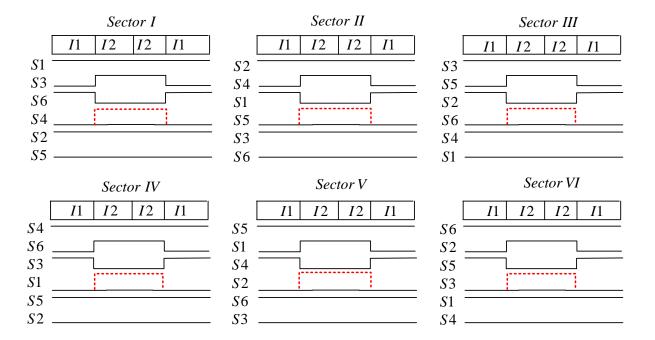

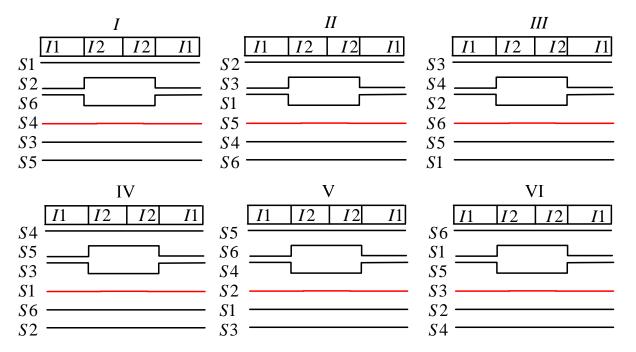

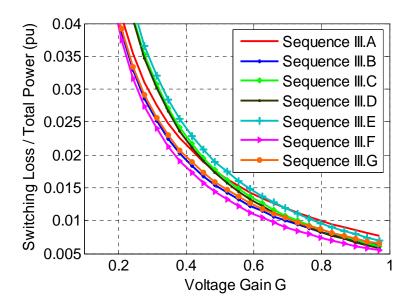

|      | 4.2.2. Selection of switching sequence in each sector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

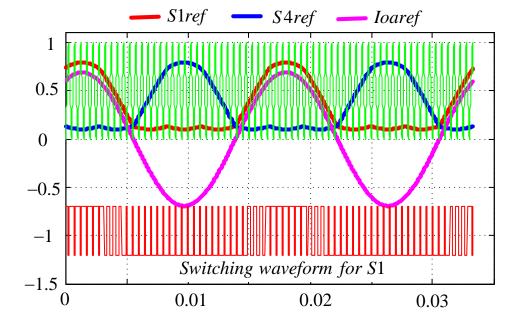

|      | 4.2.3. Equivalent reference-carrier modulation for DPWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 96         |

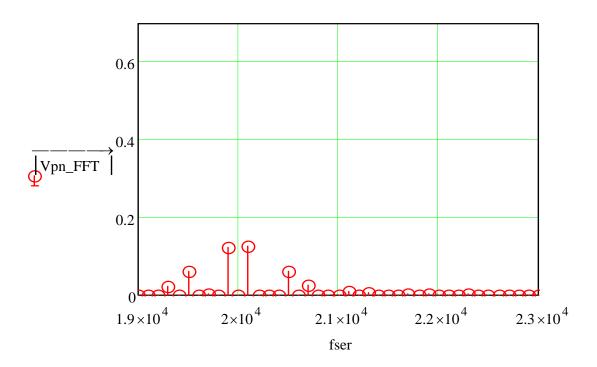

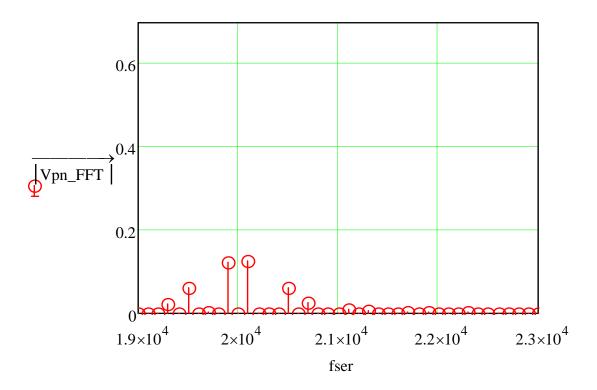

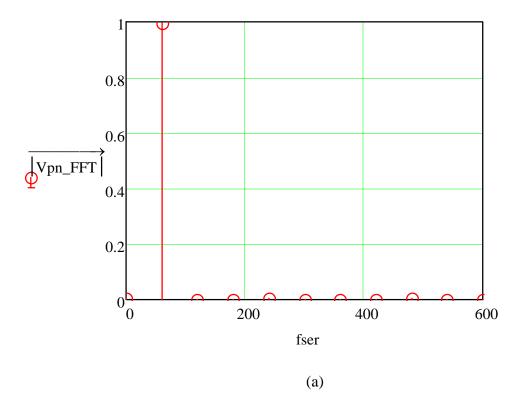

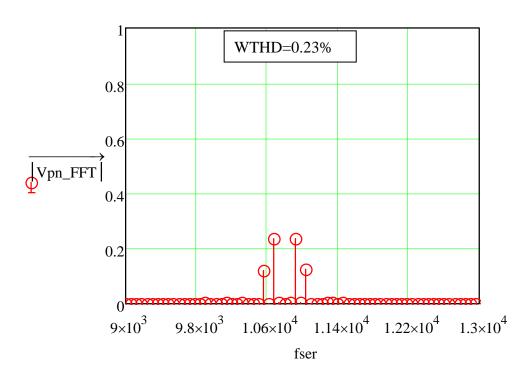

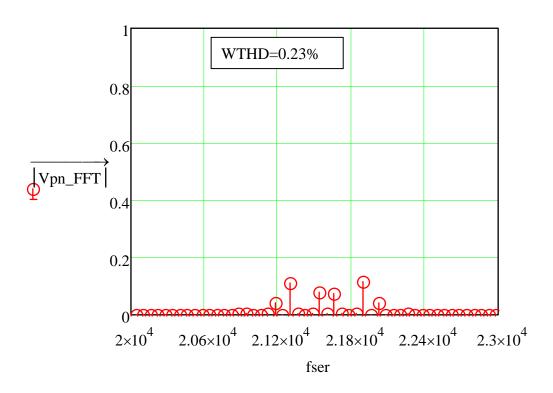

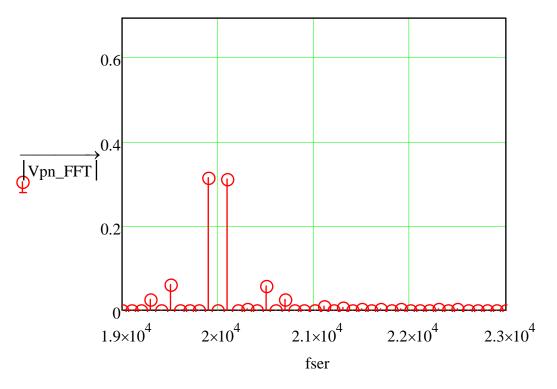

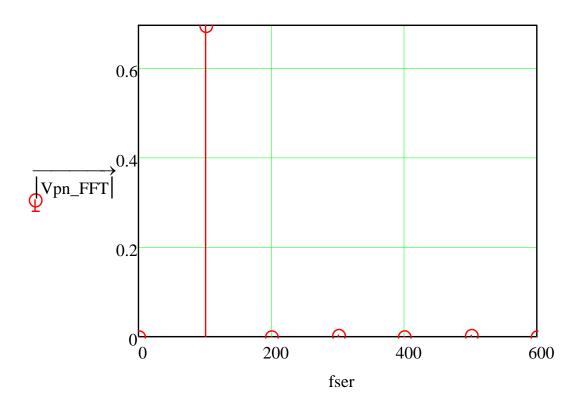

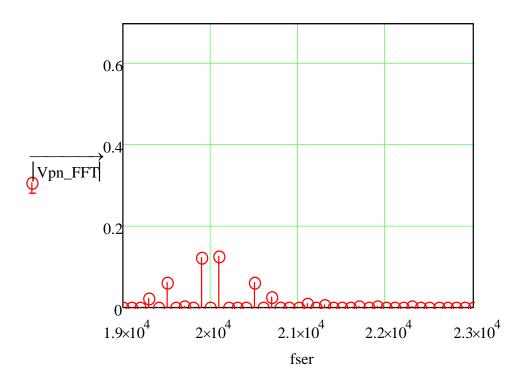

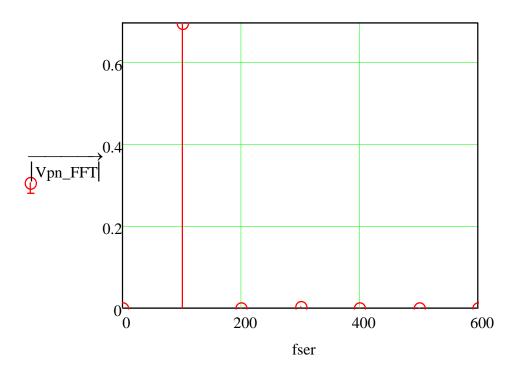

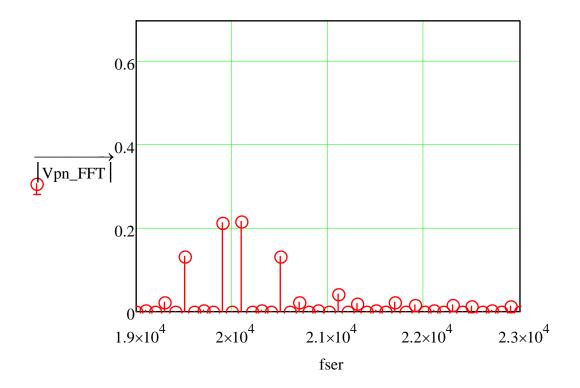

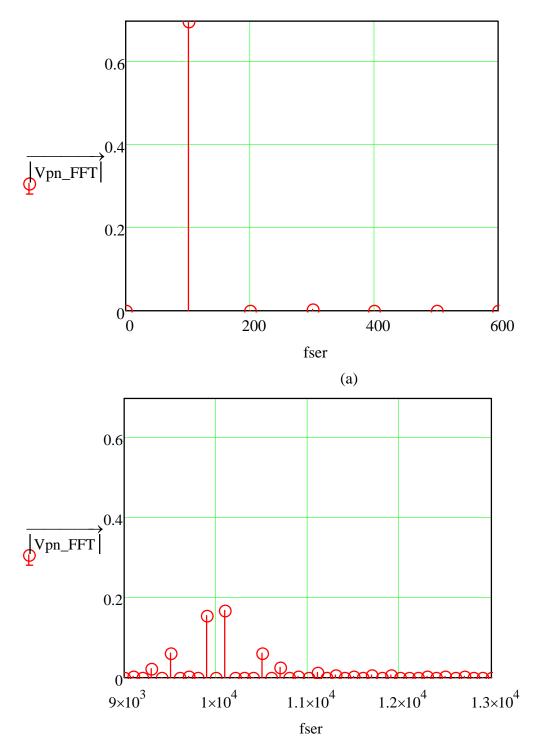

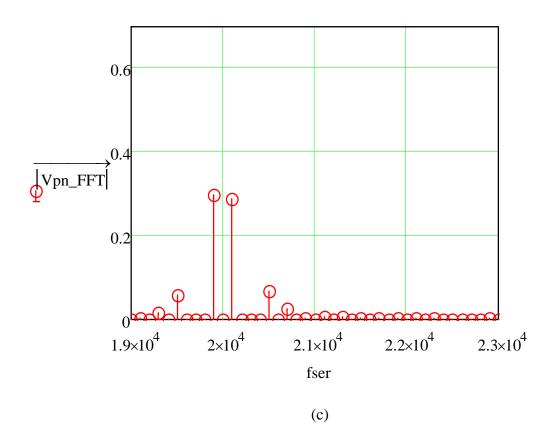

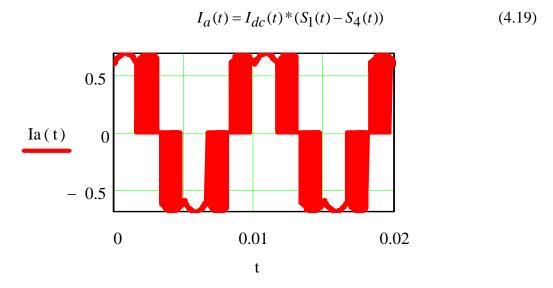

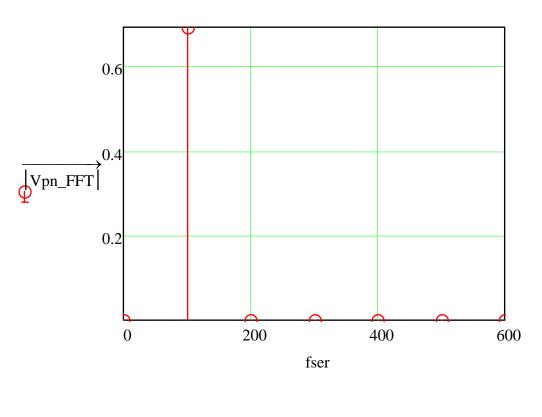

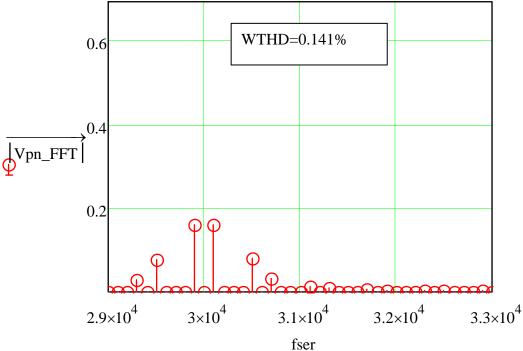

|      | 4.2.4. Numerical Spectrum analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

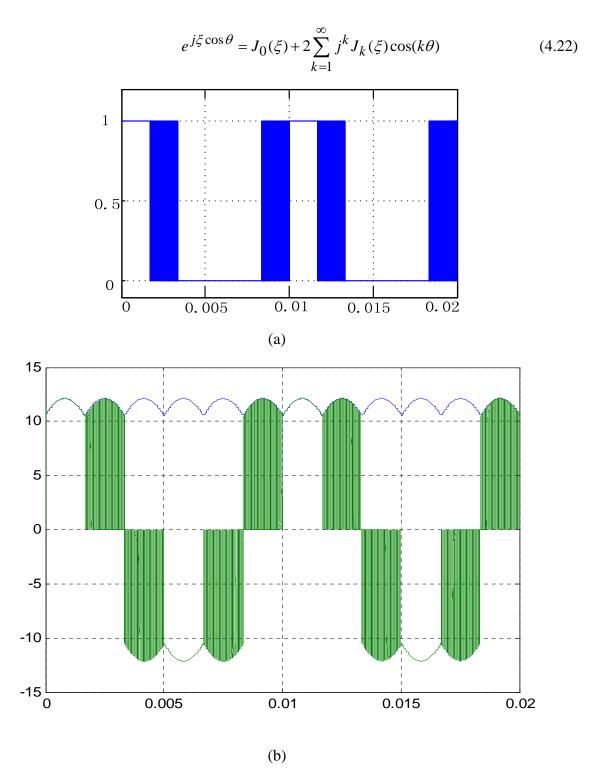

|      | 4.2.5. Analytical double Fourier analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

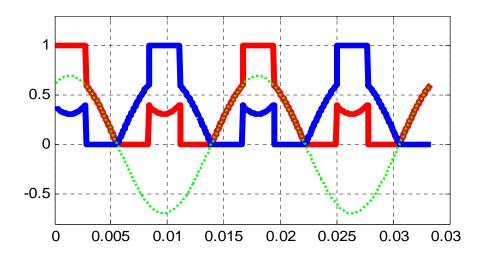

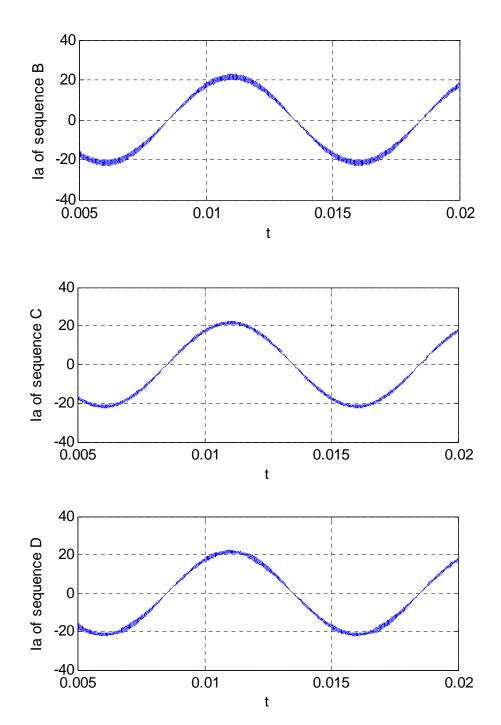

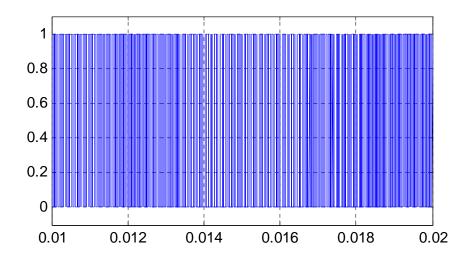

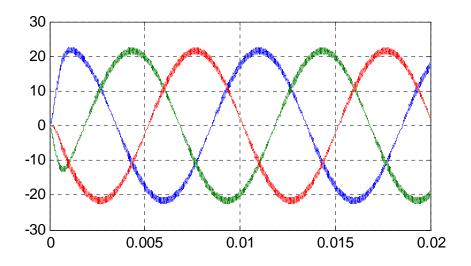

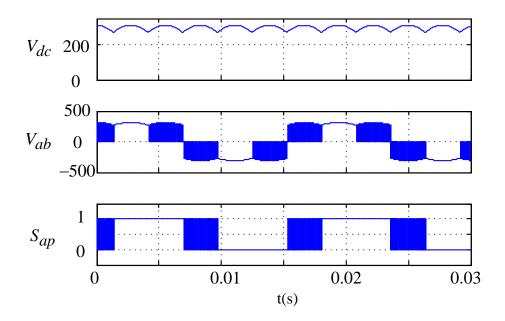

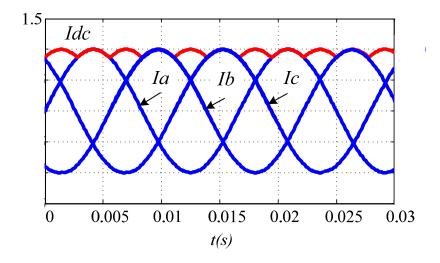

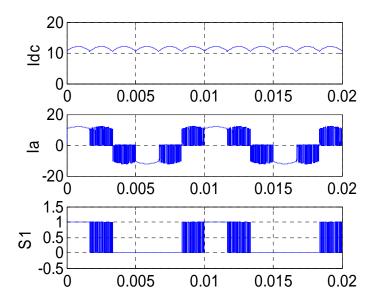

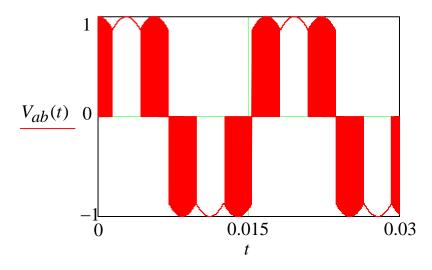

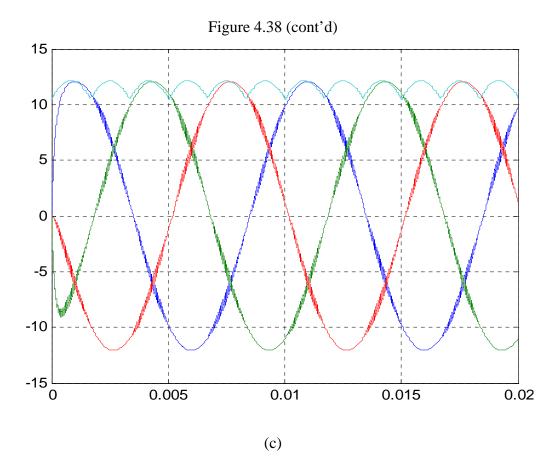

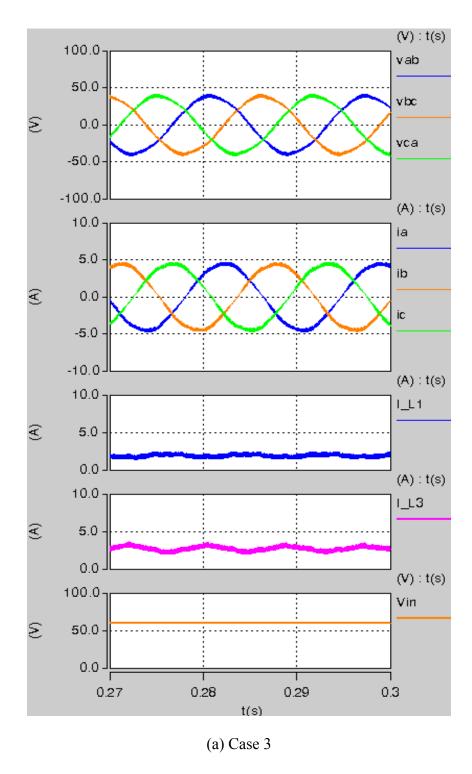

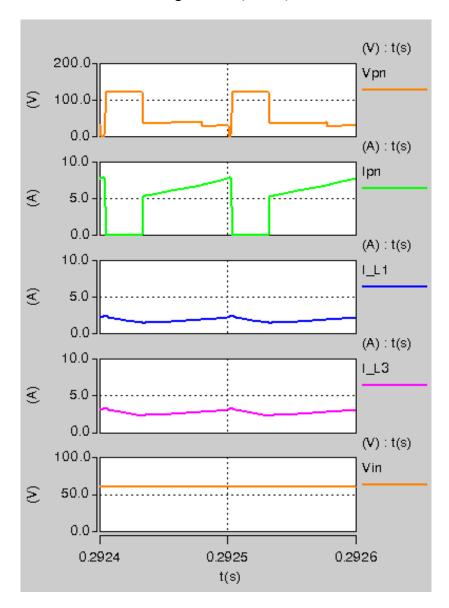

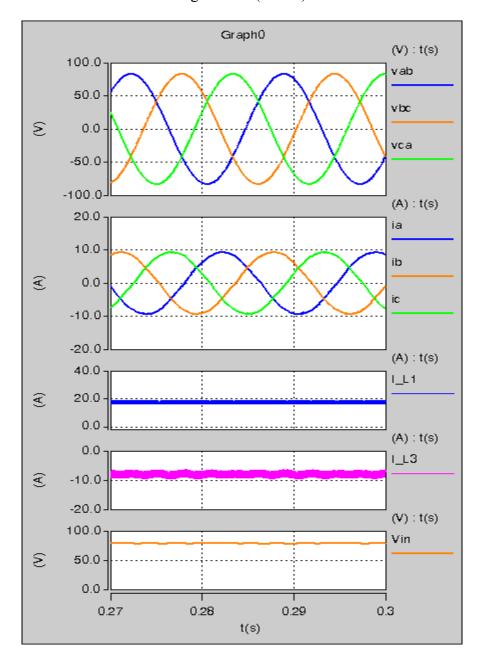

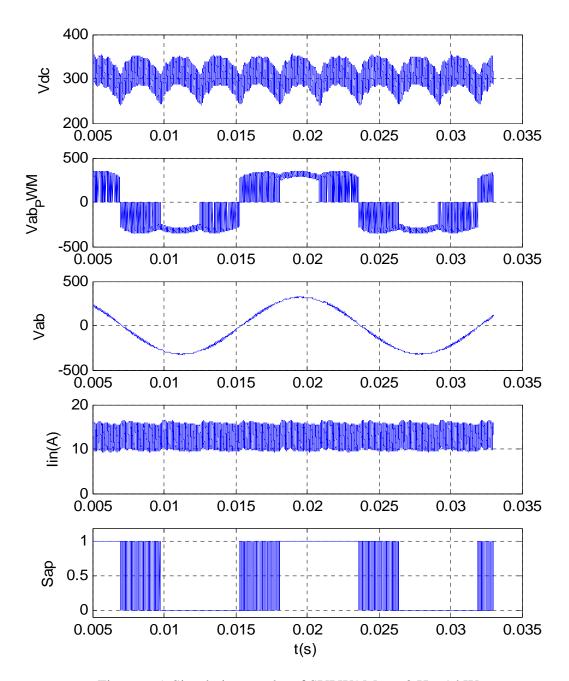

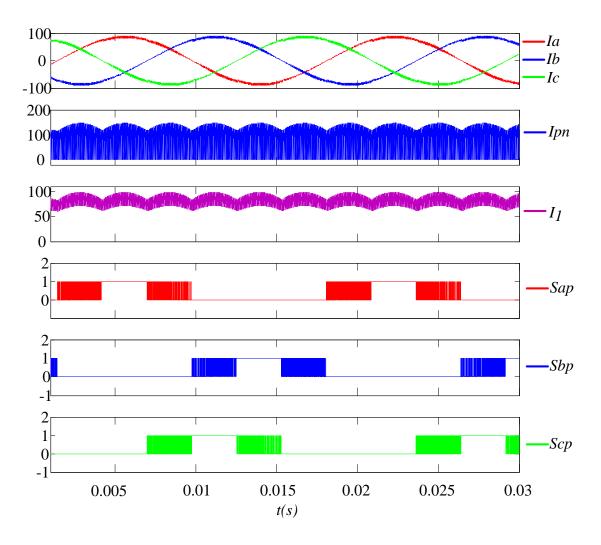

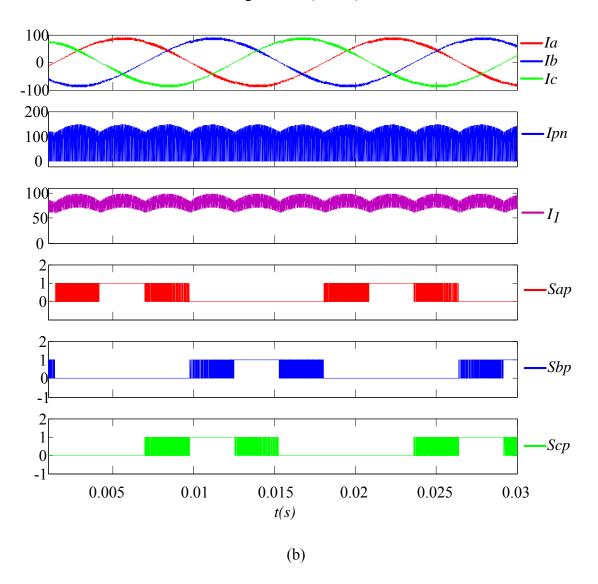

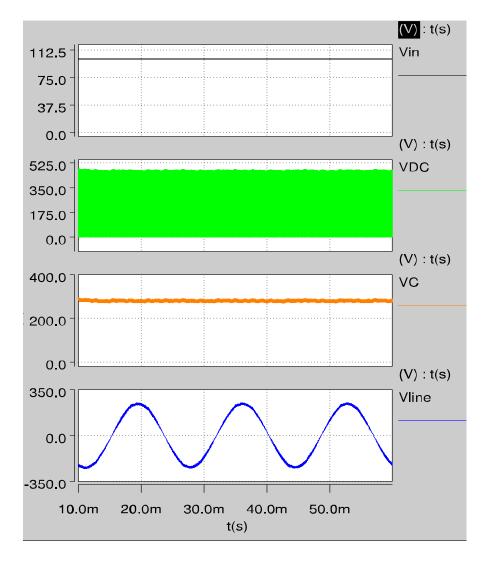

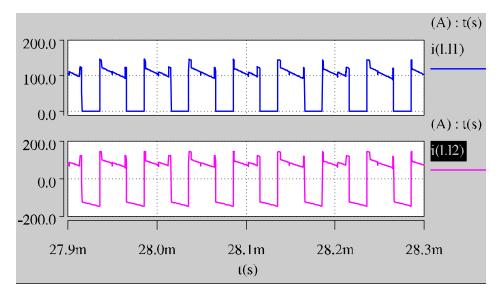

| 4.0  | 4.2.6. Simulation results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

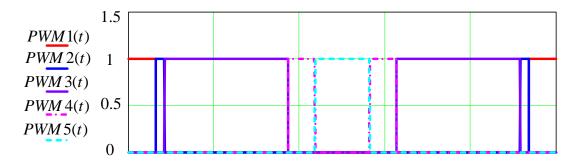

| 4.3. | Continuous SVPWM and Equivalent Carrier-based modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 104        |

|      | 4.3.1. Selection of zero states in each sector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

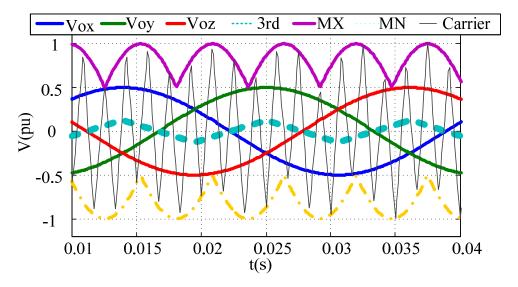

|      | 4.3.2. Equivalent carrier-based modulation for continuous SVPWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 105        |

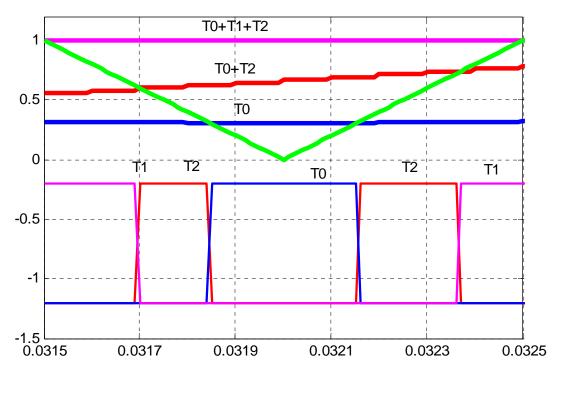

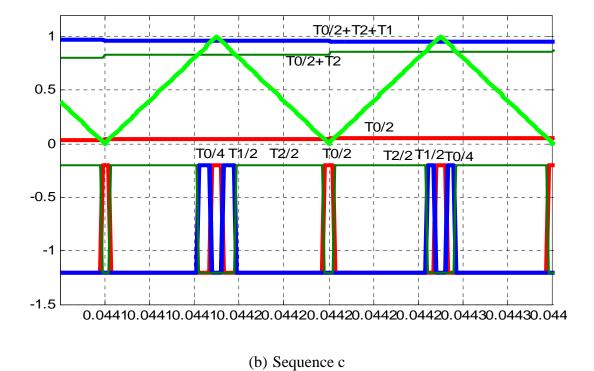

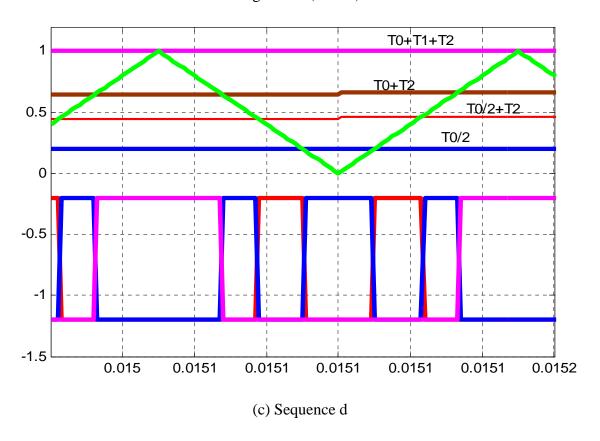

|      | 4.3.3. Sequences of vectors in each switching cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 106        |

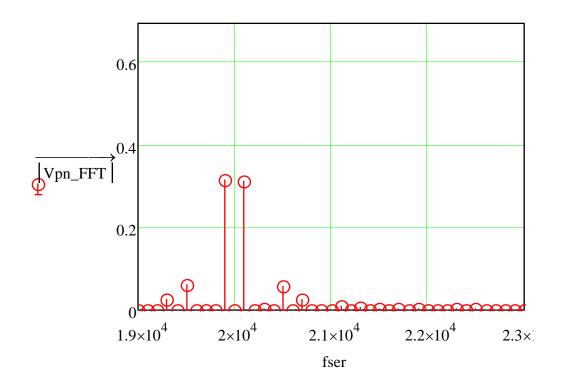

|      | 4.3.4. Numerical FFT spectrum analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

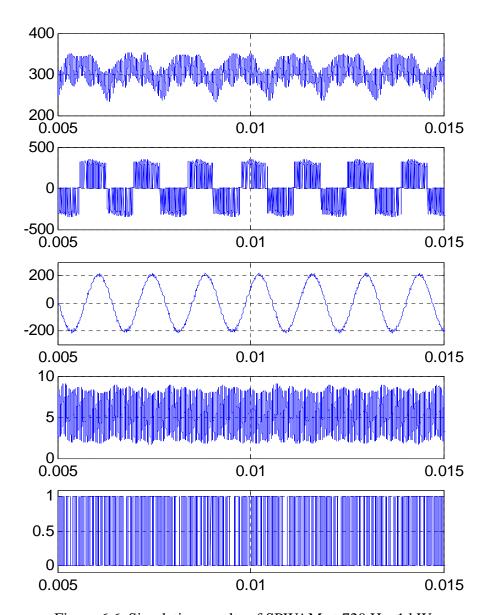

| 4.4  | 4.3.5. Simulation results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

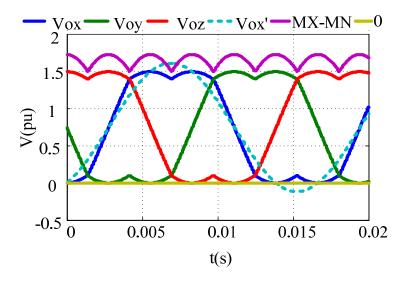

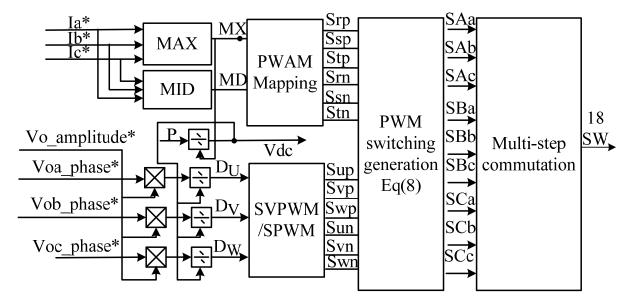

| 4.4. | Space-Vector-Pulse-Width-Amplitude-Modulation (SVPWAM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 109<br>110 |

|      | 4.4.1. SVPWAM for Voltage Source Inverter(VSI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

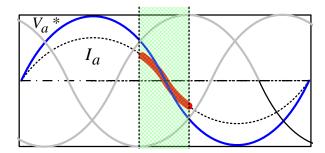

|      | 4.4.1.1. Principle of SVPWAM control in VSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 110<br>115 |

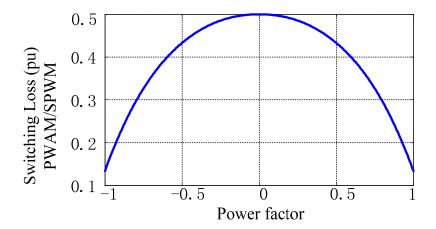

|      | 4.4.1.2. Inverter switching loss reduction for VSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 115<br>117 |

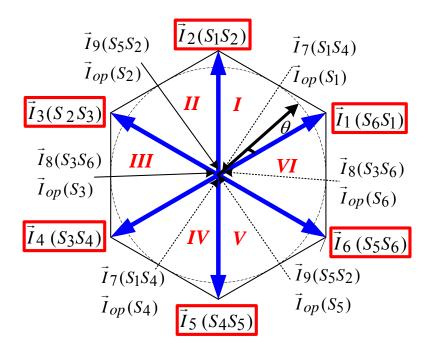

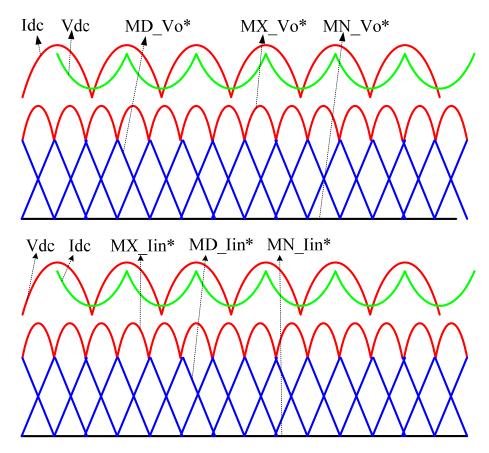

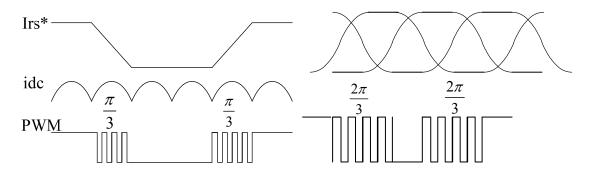

|      | 4.4.2.1 Principle of SVDWAM in CSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|      | 4.4.2.1. Principle of SVPWAM in CSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11/<br>120 |

|      | 4.4.2.2. Inverter switching loss reduction for CS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 120        |

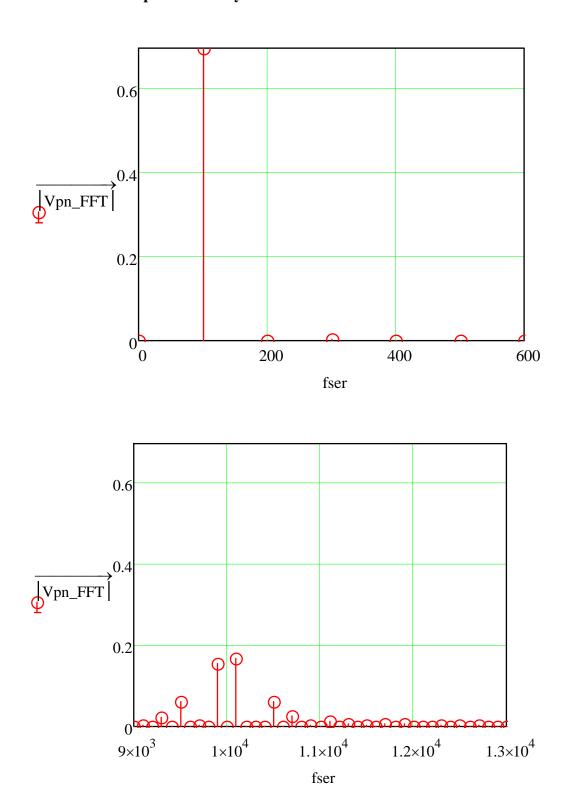

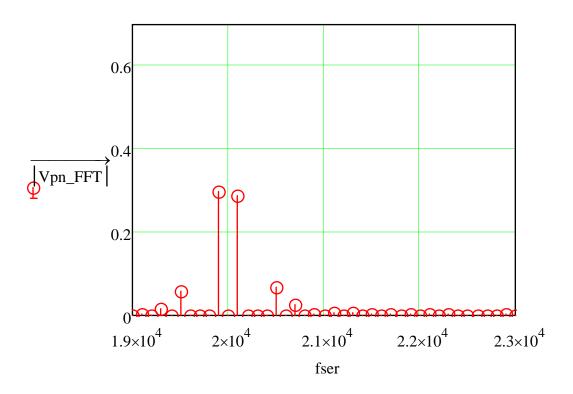

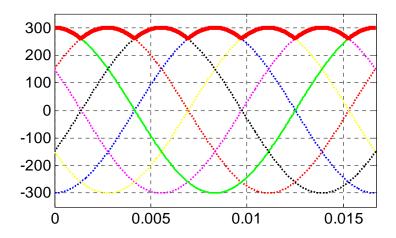

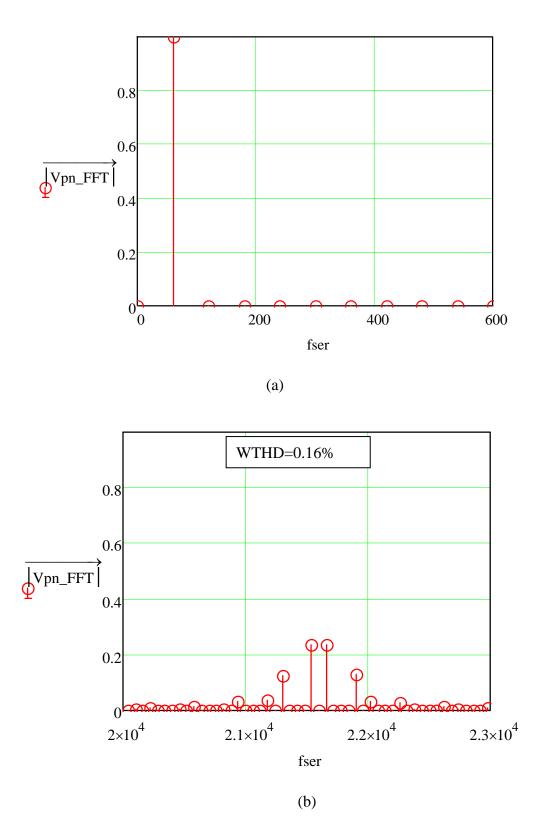

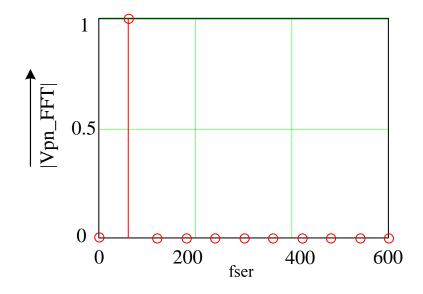

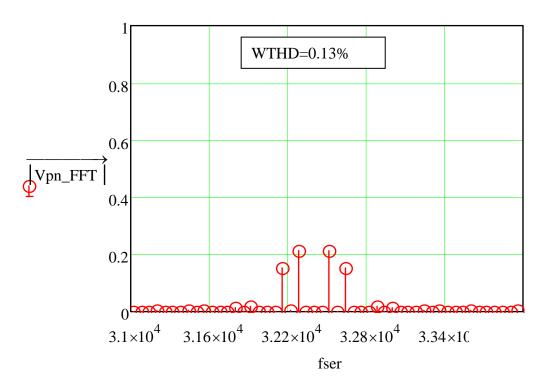

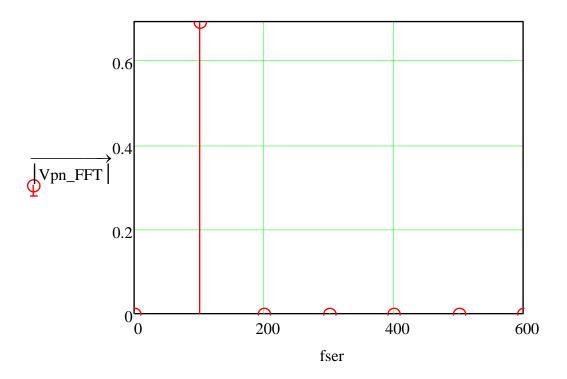

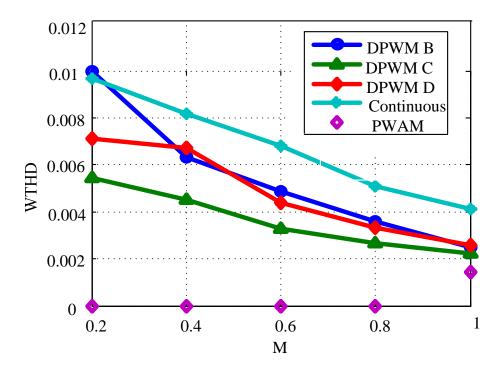

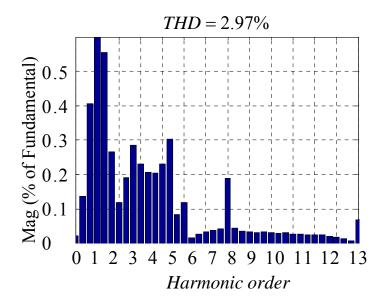

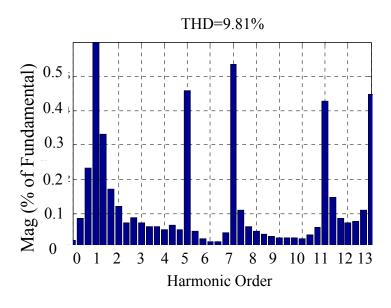

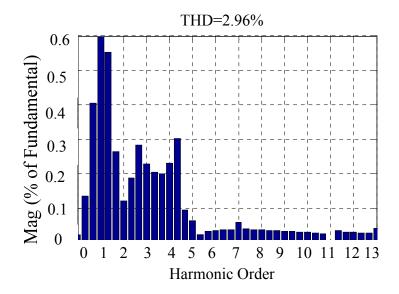

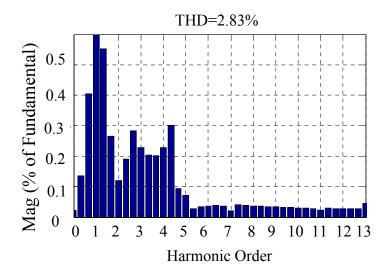

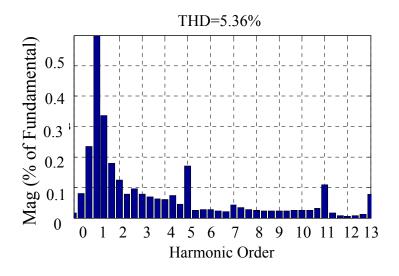

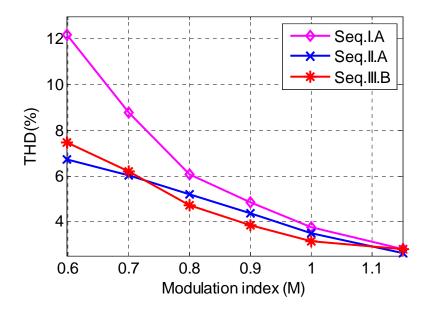

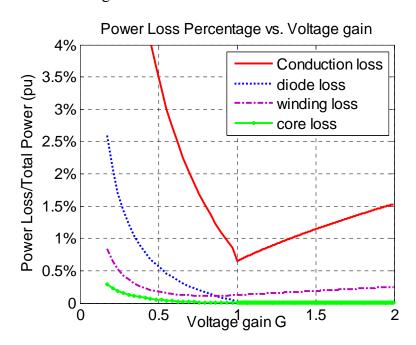

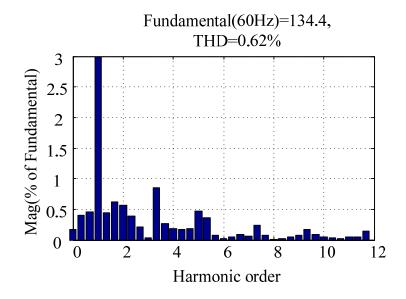

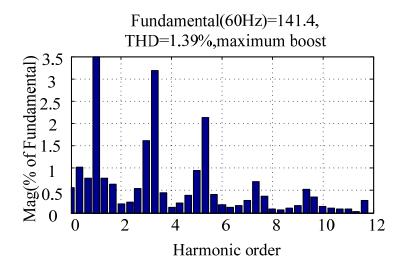

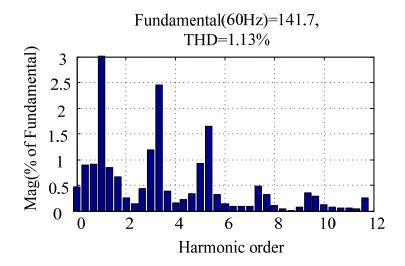

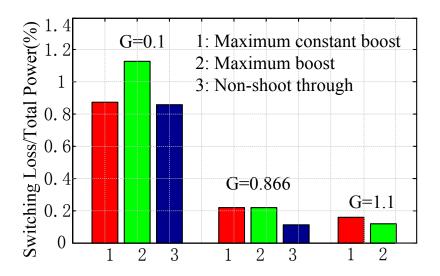

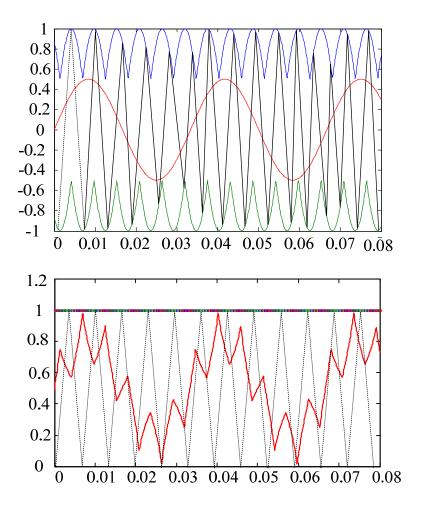

|      | 4.4.3.1. Spectrum comparison between SPWM, discontinuous SVI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

|      | and SVPWAM in VSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

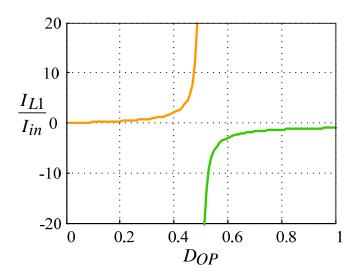

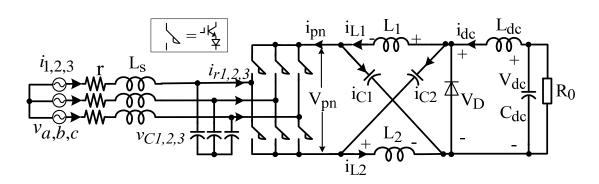

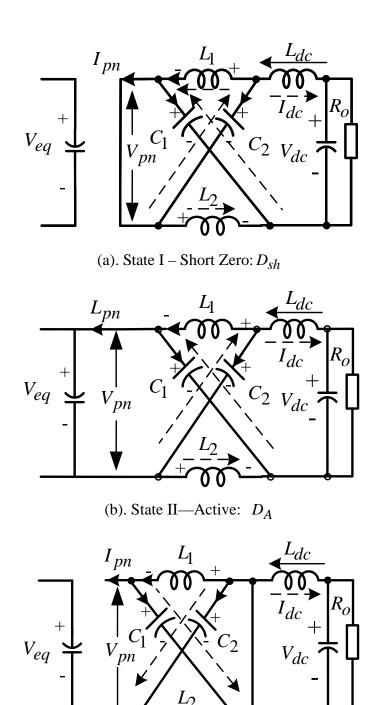

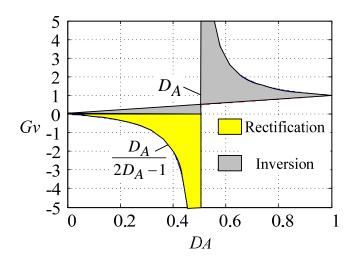

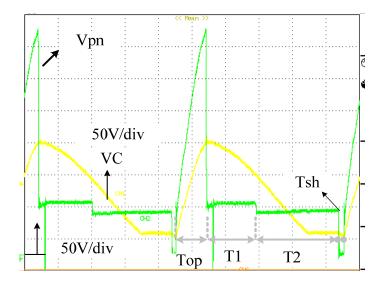

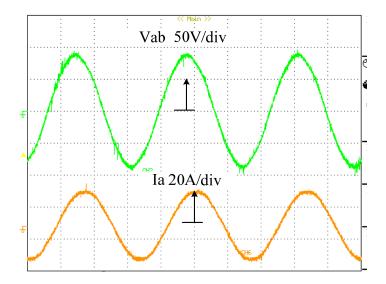

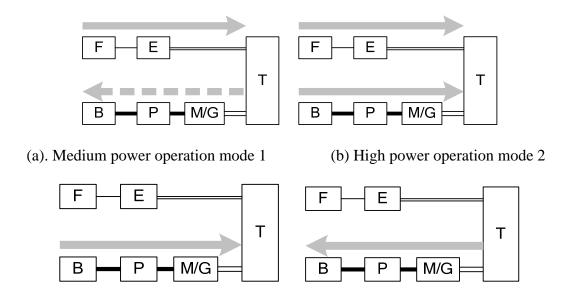

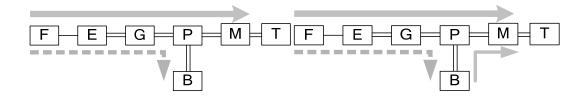

|      | 4.4.3.2. Spectrum comparison between discontinuous SVPWM, continuous SVPWM, continuo |            |