RETURNING MATERIALS:

Place in book drop to

remove this checkout from

your record. FINES will

be charged if book is

returned after the date

stamped below.

# EVALUATION OF A SINGLE VLSI CHIP ALGORITHM FOR TRIANGULATING LARGE BAND FORM MATRICES

Ву

Wen Chang Hsu

## A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Electrical Engineering and Systems Science

#### **ABSTRACT**

# EVALUATION OF A SINGLE VLSI CHIP ALGORITHM FOR TRIANGULATING LARGE BAND FORM MATRICES

By

#### Wen Chang Hsu

One of the efficient procedures to solve a large, sparse system of linear equations,  $\underline{A} \cdot \underline{x} = \underline{b}$ , as encountered in a variety of common engineering problems, is to go through fast, band matrix triangulation utilizing concurrent Gaussian elimination. This algorithm may be implemented using systolic computing cells configured into a simple, regularly connected processing array. With the most recent advances in microelectronics technology, it will soon be possible to fabricate this computing array on a single chip.

A computing structure, utilizing both parallel and pipeline concepts to triangulate an augmented band form coefficient matrix  $\left\{ \underline{A} \mid \underline{b} \right\}$  in O(N) time steps, where N is the order of the matrix, is presented. This new design utilizes only O(B<sup>2</sup>) processing cells, where B is the matrix bandwidth. This compares favorably to previous algorithms which require O(N<sup>2</sup>) cells. Hardware arithmetic algorithms of MAC and DC, the required processing cells of the computing structure, are designed and evaluated.

Three I/O circuits are presented and compared with respect to area-time trade-offs. An optimal input strategy, the data controlled algorithm and optimal output strategy, the SCS algorithm are chosen.

A transistor level circuit simulation, based on parameters of word size, matrix bandwidth and minimum lithographic linewidth, provided parameters of area geometry and delay time estimations for the I/O and computing structures. The ultimate goal of this simulation was to provide two important comparisons, total propagation delay and chip size versus matrix bandwidth. For a given matrix bandwidth, the optimal chip size and throughput speed based on current and projected lithographic linewidths were evaluated. Bottlenecking of the I/O operands was not observed for word lengths  $\geq$  16 bits and small matrix bandwidths.

These results, in turn, lead to an assessment of the feasibility and advantages of this class of special purpose VLSI computing structures.

To my parents

Mr. and Mrs. Chiung-Yung Hsu

#### **ACKNOWLEDGEMENTS**

The author wishes to express his sincere appreciation to his major advisor, Dr. Michael A. Shanblatt, for his guidance and encouragement in the course of this research.

He also wishes to thank the committee members, Dr. P. D. Fisher, Dr. R. G. Reynolds, Dr. E. D. Goodman and Dr. S. R. Crouch for giving the valuable suggestions and comments in this research.

Finally, the author owes a special thank you to his wife, Huey-Fen, for her confidence and emotional support that only a wife can give.

Work reported here was supported in part by NSF under Grant ECS-8106675.

# TABLE OF CONTENTS

|       |                                            |                                                    |                       |                          |                  |                       |                        |                   |                |          |          |          |          |                |   |   |   |   | Page                             |

|-------|--------------------------------------------|----------------------------------------------------|-----------------------|--------------------------|------------------|-----------------------|------------------------|-------------------|----------------|----------|----------|----------|----------|----------------|---|---|---|---|----------------------------------|

| ACKNO | WLEDGEN                                    | MENTS                                              | •                     | •                        |                  | •                     | •                      | •                 | •              | •        | •        | •        | •        | •              | • | • | • | • | iii                              |

| LIST  | OF TABI                                    | LES                                                | •                     | • (                      |                  | •                     | •                      | •                 | •              | •        | •        | •        | •        | •              | • | • | • | • | vi                               |

| LIST  | OF FIGU                                    | JRES                                               | •                     | • (                      |                  | •                     | •                      | •                 | •              | •        | •        | •        | •        | •              | • | • | • | • | vii                              |

| I.    | INTRODU<br>1.1<br>1.2<br>1.3               | State                                              | eme<br>oac            | nt<br>h                  | of               | •                     | rot                    | ole<br>•          | m<br>•         | •        | •        | •        | •        | •              | • | • | • | • | 1<br>3<br>5<br>7                 |

| II.   | BACKGRO                                    | Array<br>Nat                                       | y P                   | rode d                   | ces<br>of        | Ga                    | rs<br>uss              | an<br>sia         | d              | th<br>El |          | Ve       | ct       | :01            |   |   |   |   | 10<br>10                         |

|       | 2.2                                        | VLSI<br>Sys<br>Desig                               | sto                   | lio                      | c P              | lg                    | ori                    | ith               | ms             |          |          | SI       |          |                |   |   |   |   | 14<br>17                         |

| III.  | COMPUTI<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | ING ST<br>Band<br>Array<br>Cell,<br>Float<br>Funct | FO<br>S<br>P          | rm<br>tri<br>ori<br>g-1  | Al<br>uct<br>t a | go<br>ur<br>ind<br>nt | rit<br>e a<br>Ti<br>Co | thm<br>and<br>ime | T<br>Sid       | im<br>lo | ir<br>t  | ng<br>Cc | ·<br>oun | •<br>•<br>• ts | • | • | • | • | 22<br>22<br>26<br>31<br>32<br>35 |

| IV.   | INPUT/04.1<br>4.2<br>4.3                   | OUTPUT<br>SCS I<br>Binar<br>Data<br>Inp<br>Discu   | np<br>Co<br>Co<br>out | ut,<br>Tre<br>nt:<br>/O: | /Oi<br>ee<br>rol | St<br>St<br>le        | ut<br>rud<br>d<br>Ci   | Ci<br>ctu<br>irc  | rc<br>re<br>ui | ui<br>t  | .t       | •        | •        | •              | • | • | • | • | 46<br>47<br>50<br>55<br>57       |

| v.    | SIMULAT<br>5.1<br>5.2<br>5.3               | Chip<br>Chip<br>Propa                              | Ar<br>aga             | ea<br>tio                | Cc<br>on         | mp<br>De              | uta<br>lay             | ati<br>y C        | on<br>om       | pu       | •<br>ıta | ati      | on       | •              | • | • | • | • | 60<br>63<br>65                   |

|      |        |          |     |     |            |     |     |     |     |             |     |     |     |    |   |   |   |   | Page |

|------|--------|----------|-----|-----|------------|-----|-----|-----|-----|-------------|-----|-----|-----|----|---|---|---|---|------|

| VI.  | SIMULA | rion res | SUI | LTS | 5 <i>1</i> | ANI | ) I | EVA | ALU | JA'         | ric | ON  | •   | •  | • | • | • | • | 68   |

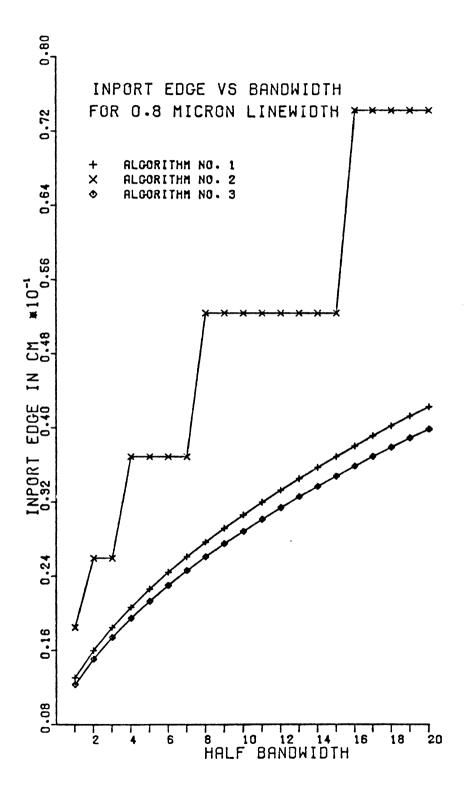

|      | 6.1    | Compar   | iso | on  | 01         | : 1 | [/( | ) ( | Sti | rat         | tec | jie | es  | •  | • | • | • | • | 69   |

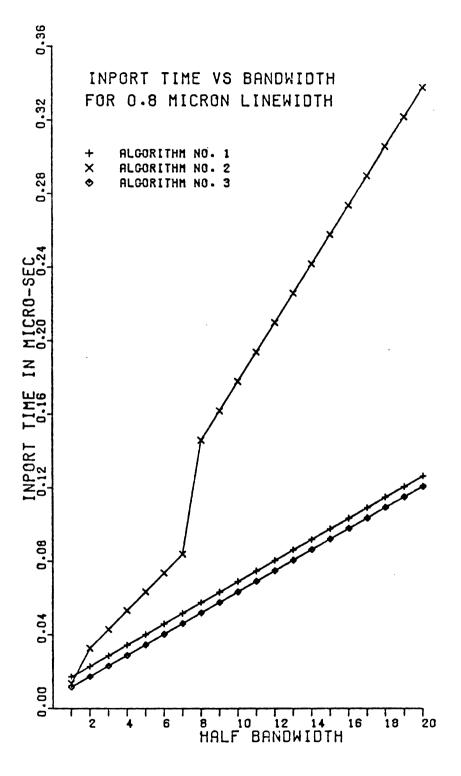

|      | 6.1.   | l INPOR  | RT  | St  | ra         | ate | egy | , 9 | Se: | le          | cti | ioi | า   | •  | • | • | • | • | 70   |

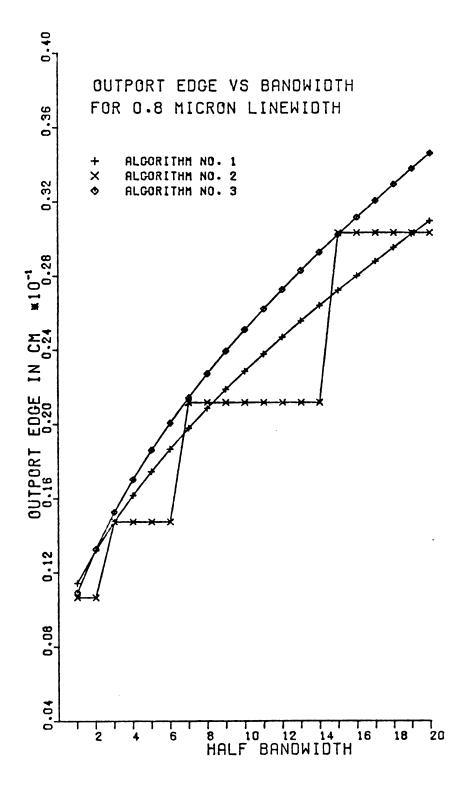

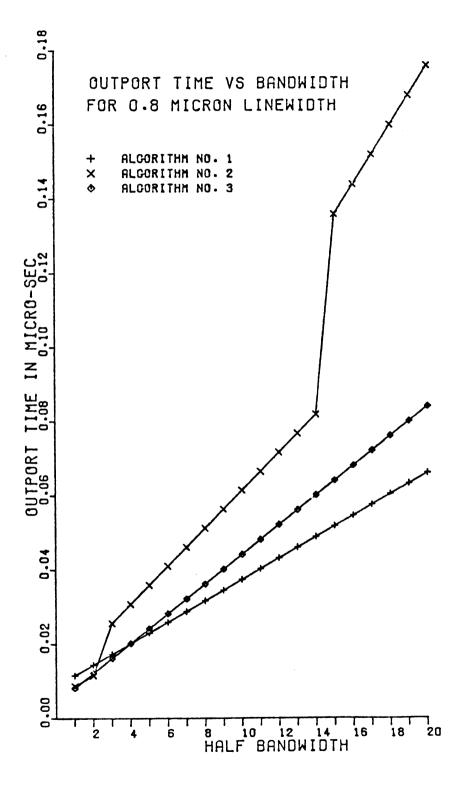

|      | 6.1.   | 2 OUTPO  | DR: | r s | sti        | at  | eç. | ју  | Se  | <b>e</b> 16 | ect | ii  | on  | •  | • | • | • | • | 73   |

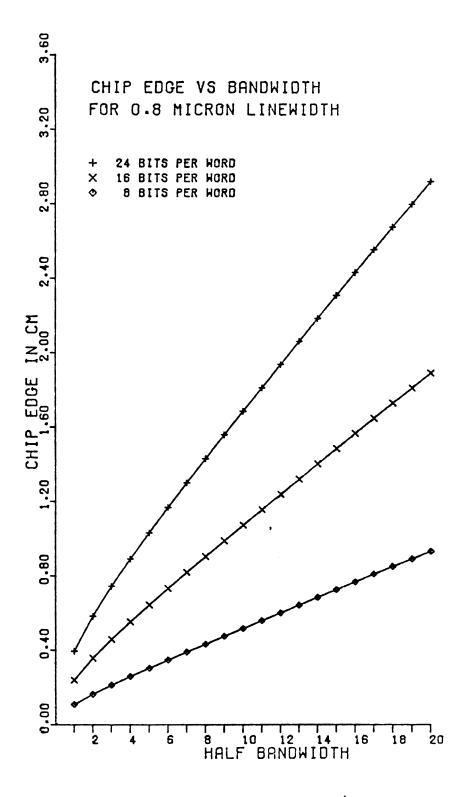

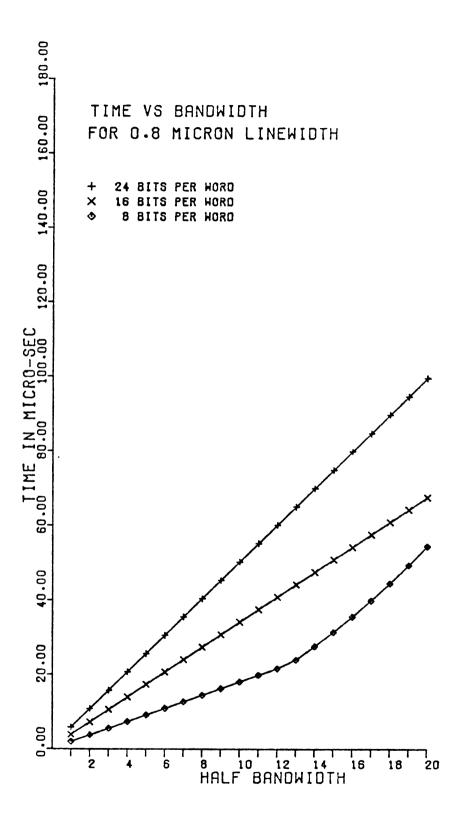

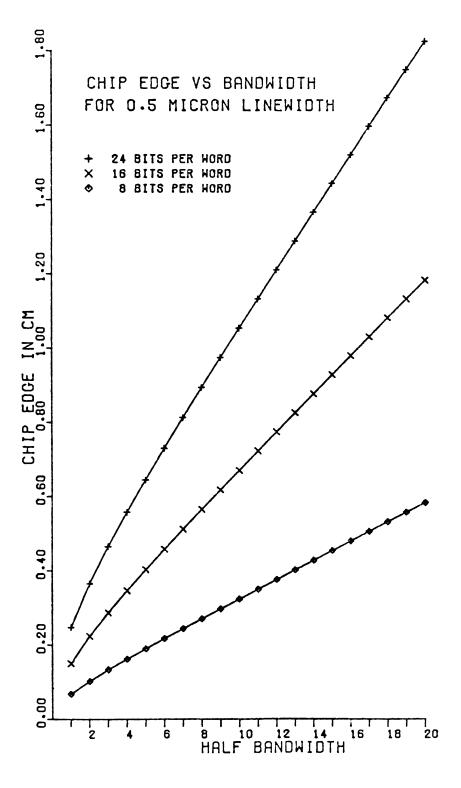

|      | 6.2    | Entire   | Cł  | nip | 5          | Sin | nu  | la  | tio | on          | Re  | esi | 111 | ts | • | • | • | • | 78   |

| VII. | CONCLU | SIONS .  | •   | •   | •          | •   | •   | •   | •   |             | •   | •   | •   | •  | • | • | • | • | 87   |

|      |        | Summary  |     |     |            |     |     |     |     |             |     |     |     |    |   |   |   |   | 87   |

|      |        | Future   |     |     |            |     |     |     |     |             |     |     |     |    |   |   |   |   | 90   |

|      | BIBLIO | GRAPHY   | •   | •   |            | •   |     | •   | •   | •           | •   | •   | •   |    | • |   |   | • | . 92 |

## LIST OF TABLES

| Table |                                                                                                                            | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------|------|

| 3.1   | Port-coefficient timing table                                                                                              | 30   |

| 5.1   | Significant module data                                                                                                    | 67   |

| 6.la  | Total chip area and time results of algorithm #3 (INPORT) and #1 (OUTPORT) for 8 bits per word at $\lambda$ = 0.8 $\mu$ m  | 76   |

| 6.1b  | Total chip area and time results of algorithm #3 (INPORT) and #2 (OUTPORT) for 8 bits per word at $\lambda$ = 0.8 $\mu$ m  | 76   |

| 6.2a  | Total chip area and time results of algorithm #3 (INPORT) and #1 (OUTPORT) for 16 bits per word at $\lambda$ = 0.8 $\mu$ m | 77   |

| 6.2b  | Total chip area and time results of algorithm #3 (INPORT) and #2 (OUTPORT) for 16 bits per word at $\lambda$ = 0.8 $\mu$ m | 77   |

| 6.3   | Simulation time results for 8 and 16 bit words at $\lambda$ = 0.8 microns                                                  | 85   |

## LIST OF FIGURES

| Figure |                                                                                          |   | <u> </u> | age |

|--------|------------------------------------------------------------------------------------------|---|----------|-----|

| 2.1    | Vector nature of a full matrix row-order elimination step                                | • |          | 13  |

| 3.la   | Augmented matrix $\{ \underline{A} \mid \underline{b} \}$                                | • | •        | 24  |

| 3.1b   | Upper triangular elements of matrix $\{ \underline{A} \mid \underline{b} \} \dots \dots$ | • | •        | 24  |

| 3.2    | Large band form matrix                                                                   | • | •        | 25  |

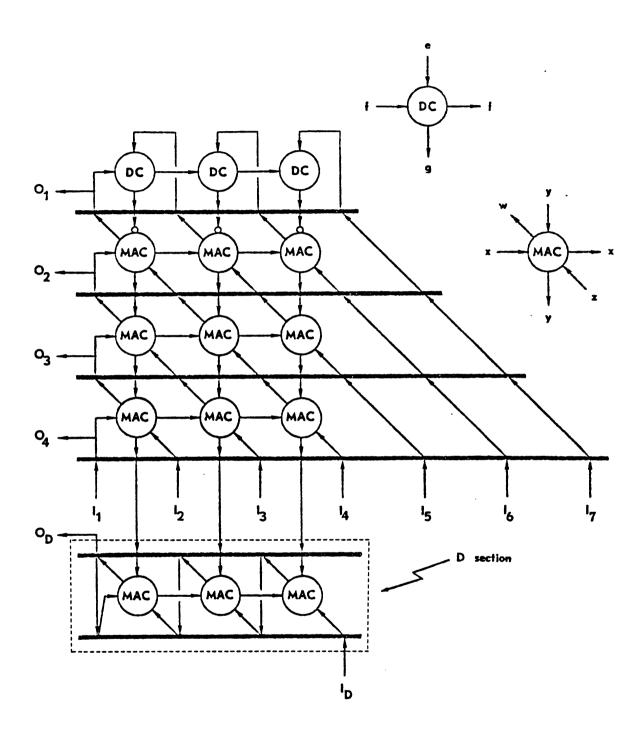

| 3.3    | Computing array structure for matrix of arbitrary dimension with B = 3                   | • | •        | 28  |

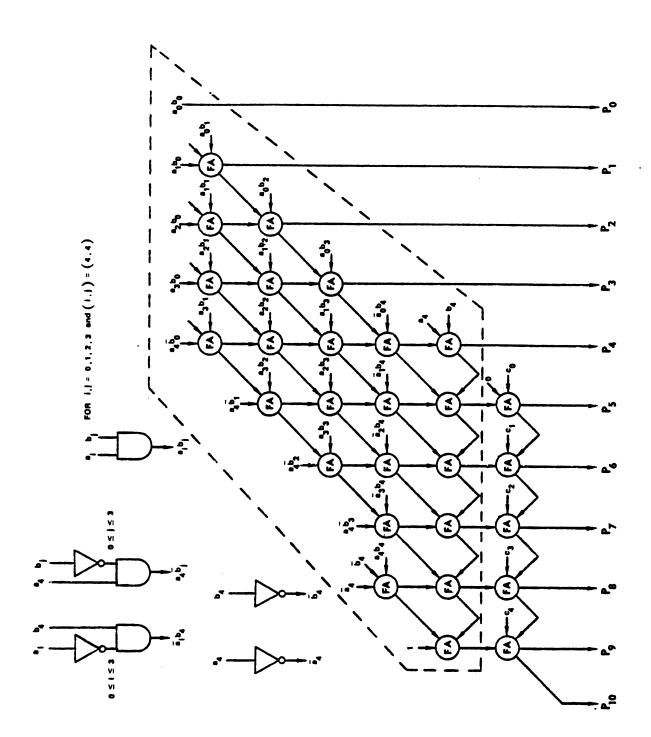

| 3.4    | Logic circuit diagram of a 5-by-5 Baugh-Wooley based MAC                                 | • | •        | 37  |

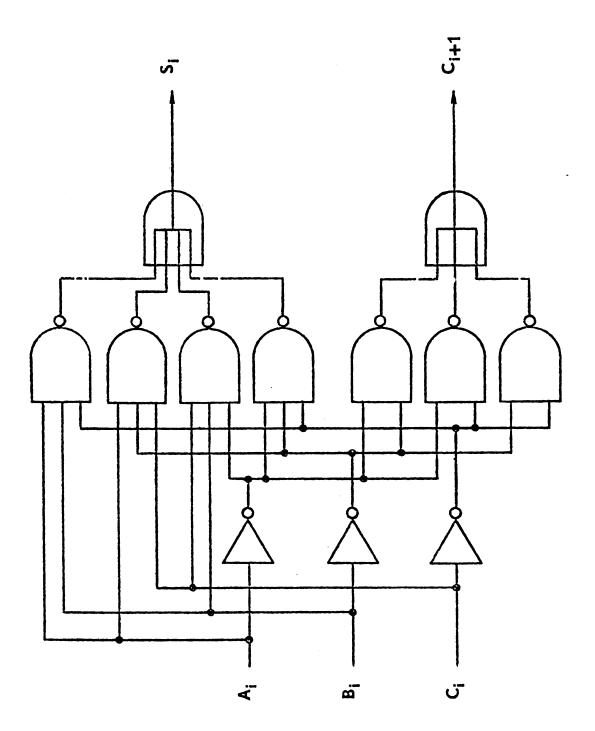

| 3.5    | Logic gate diagram of a one-bit full adder                                               | • | •        | 39  |

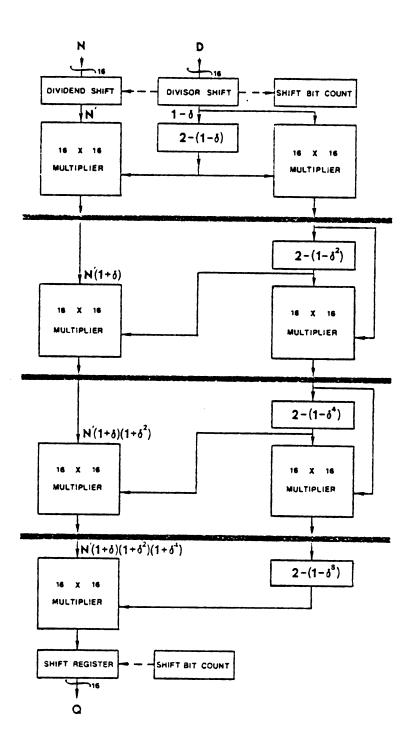

| 3.6    | A 16-by-16 convergence division algorithm based DC                                       | • | •        | 44  |

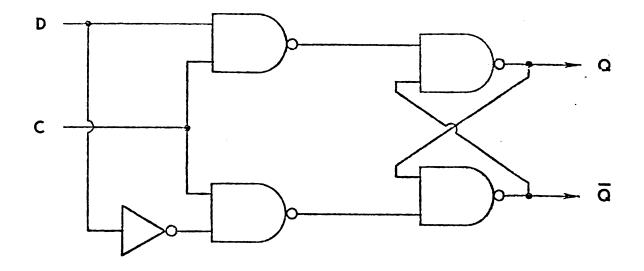

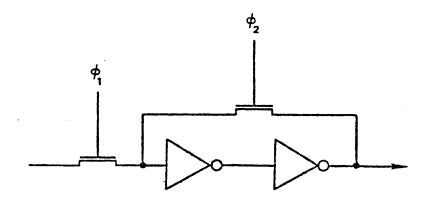

| 3.7    | D-type flip-flop                                                                         | • | •        | 45  |

| 3.8    | Dynamic latch controlled by two-phase nonoverlapping clock                               | • | •        | 45  |

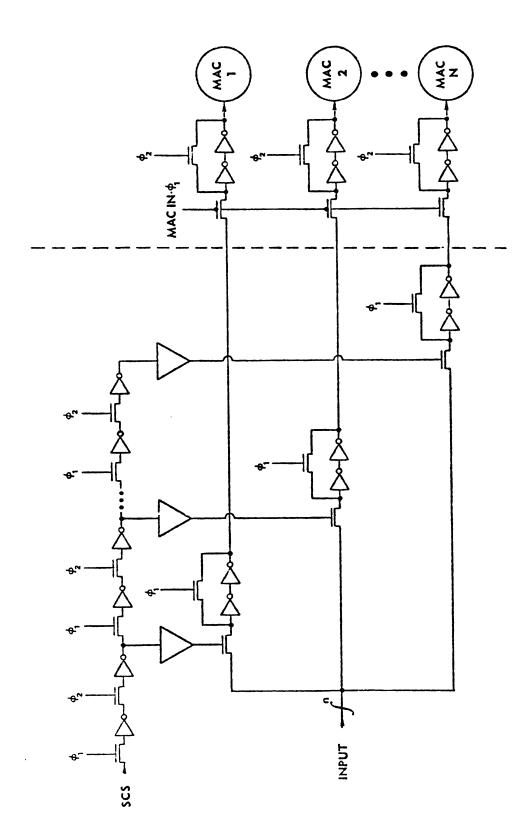

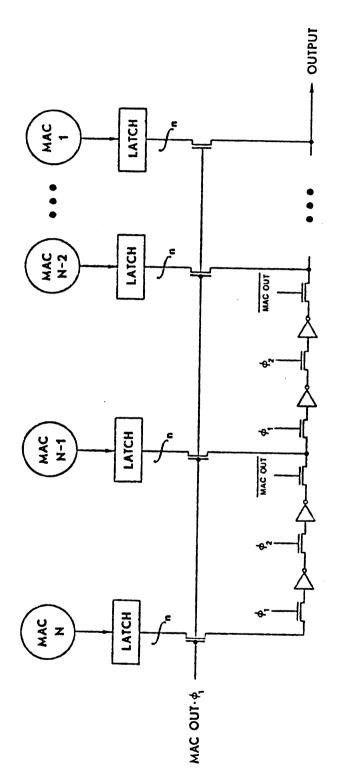

| 41     | SCS input circuit diagram                                                                | • | •        | 48  |

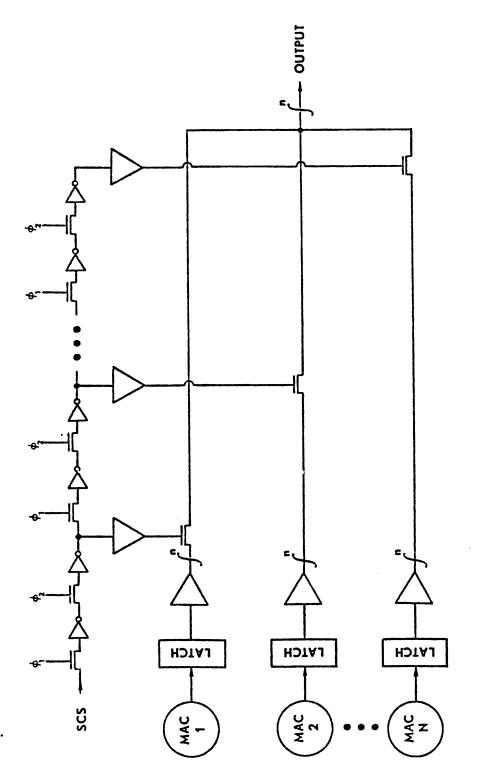

| 4.2    | SCS output circuit diagram                                                               | • | •        | 49  |

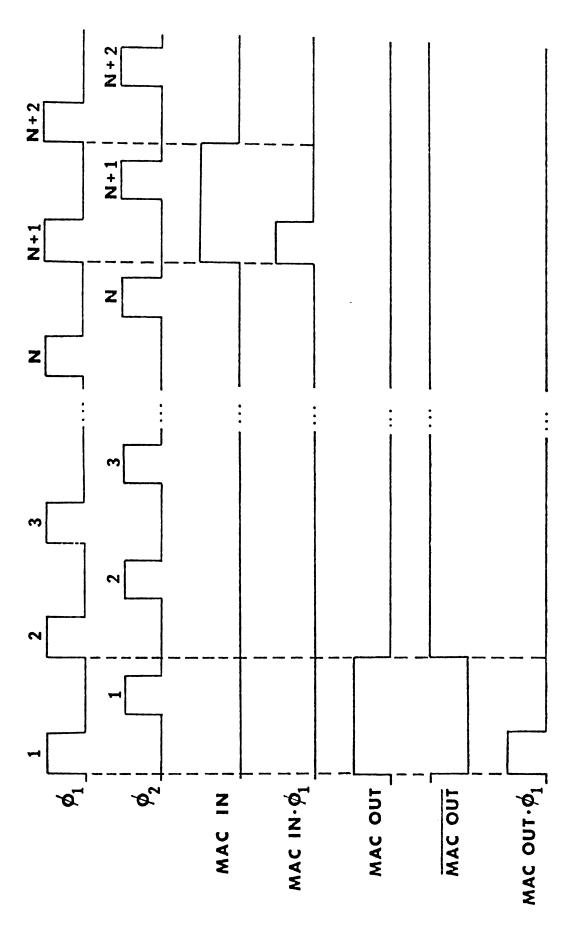

| 4.3    | Input and output circuit control signal timing diagram                                   | • | •        | 51  |

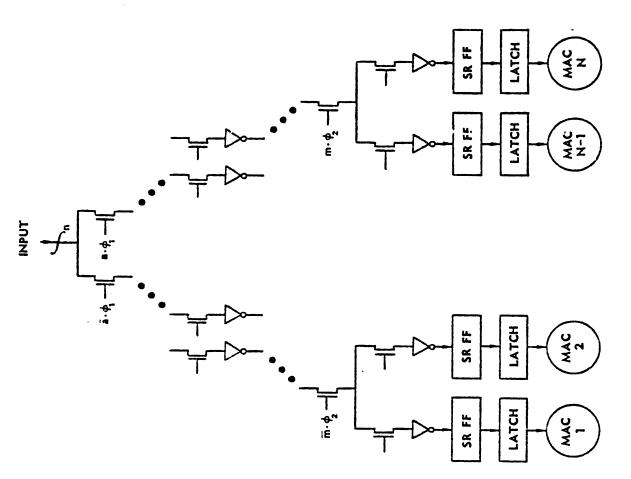

| 4.4    | Binary tree input structure                                                              | • | •        | 52  |

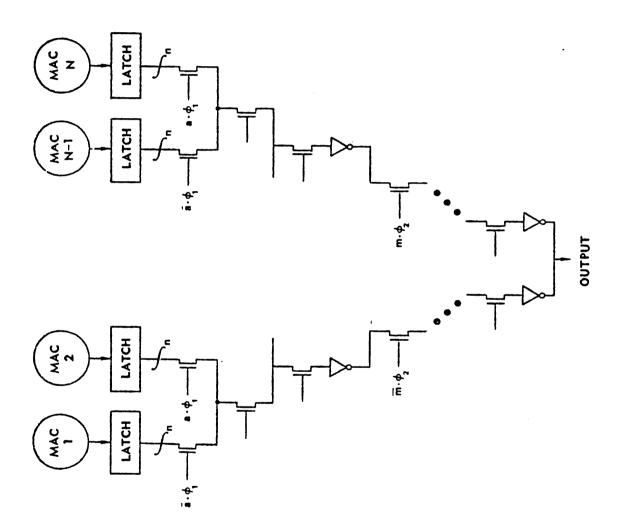

| 4.5    | Binary tree output structure                                                             | • | •        | 54  |

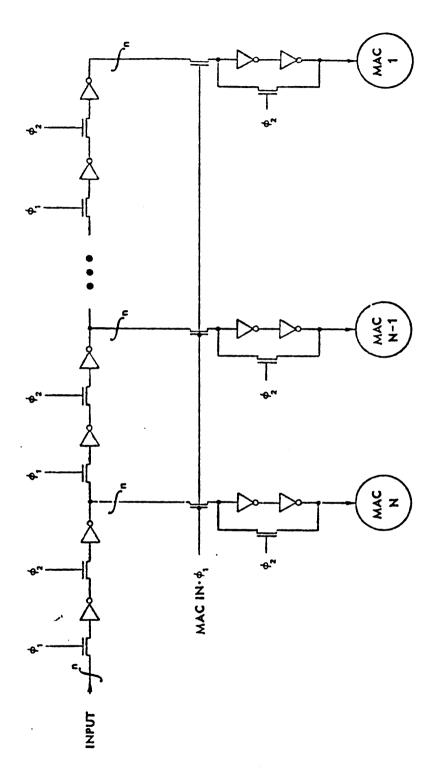

| 4.6    | Data controlled input circuit diagram.                                                   | • | •        | 56  |

| 4.7    | Data controlled output circuit diagram.                                                  |   | •        | 58  |

| <u>Figure</u> |                                                                                                                 | Page |

|---------------|-----------------------------------------------------------------------------------------------------------------|------|

| 6.1           | INPORT edge size versus matrix bandwidth for 16 bits per word at $\lambda$ = 0.8 $\mu$ m                        | 71   |

| 6.2           | INPORT delay time versus matrix bandwidth for 16 bits per word at $\lambda$ = 0.8 $\mu$ m                       | 72   |

| 6.3           | OUTPORT edge size versus matrix bandwidth for 16 bits per word at $\lambda$ = 0.8 $\mu$ m                       | 74   |

| 6.4           | OUTPORT delay time versus matrix bandwidth for 16 bits per word at $\lambda$ = 0.8 $\mu$ m                      | 75   |

| 6.5           | Entire chip edge size versus matrix bandwidth for 8, 16 and 24 bits per word at $\lambda = 0.8 \ \mu\text{m}$   | 80   |

| 6.6           | Entire chip propagation delay versus matrix bandwidth for 8, 16 and 24 bits per word at $\lambda$ = 0.8 $\mu$ m | 81   |

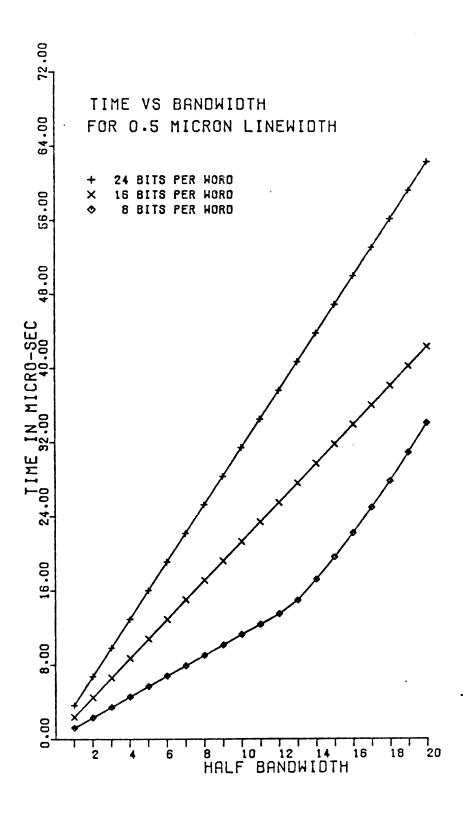

| 6.7           | Entire chip edge size versus matrix bandwidth for 8, 16 and 24 bits per word at $\lambda$ = 0.5 $\mu$ m         | 82   |

| 6.8           | Entire chip propagation delay versus matrix bandwidth for 8, 16 and                                             | 83   |

#### CHAPTER I

#### INTRODUCTION

High speed VLSI (Very Large Scale Integration) computing arrays, based on concurrent Gaussian elimination, for triangulating the linear equation system  $A \cdot x = b$ become a topic of recent interest. By combining parallel and pipeline concepts, these "systolic arrays" [1] can rapidly execute the numerous inner-product step operations which serial computers must tediously operate upon sequentially. It is projected that these high performance algorithms can be implemented directly using low cost, high speed VLSI circuit technology either on a simple chip, or perhaps in a modular fashion on a few chips. These devices can then be attached to either dedicated or general purpose host computers as plug-in components capable of producing fast solution vectors to large scale systems of equations. This concept is similar to the currently available attached peripheral array processors and to those devices which perform dedicated fast Fourier transforms exclusively in hardware.

The work described herein advances this topic by the design of a computing algorithm to triangulate systems of arbitrary size which have been permuted, a priori, to minimum band form. The algorithm is applicable to any structurally symmetric, diagonally dominant coefficient matrix. This permits use of the algorithm on many naturally occuring band form matrices and, more importantly, on the highly

sparse, diagonally dominant matrices arising from a multitude of engineering and scientific problem formulations.

The salient feature of the algorithm is that the key

restriction limiting network size is on the reduced matrix

bandwidth, not on the original network dimension. Moreover,

several good heuristic bandwidth reduction algorithms, based

on graph theoretic concepts, already exist and are quite

easy to implement [2, 3].

It is assumed that the permutation of  $\underline{A}$  to minimum band form involves full row and column pivoting so as to ensure the retention of the necessary property of diagonal dominance.

The processing elements of the computing structure were originally designed to operate with fixed-point binary numbers. But the nature of this structure also allows these PE's to work with the mantissas of floating-point input operands provided that all exponent values have been equalized and stored in the host processor. More details of this idea will be presented in Chapter III.

In a single chip system, operand input and output may present a bottleneck due to some very practical problems of packaging considerations. Therefore, high speed serial-to-parallel input and parallel-to-serial output circuits must be included in the design so as to minimize any potential bottleneck and thus retain optimal system throughput. Three different I/O strategies are presented in Chapter IV. Comparisons are made in terms of area and propagation delay requirements.

The final quantifications of area geometry and propagation delay for the total chip, composed of the computing structure with the optimal input/output strategies, are examined via a chip model simulation in terms of matrix bandwidth, word size and lithographic linewidth.

These simulation results are intended to provide a realistic estimation of the feasibility, with respect to problem size and throughput, of this type of systolic array numerical algorithm fabricated on a single VLSI chip. This, in turn, will shed light on how these ideas may benefit the numerous scientific and engineering problems for which enhanced throughput in the rapid solution of large scale simultaneous equations is greatly desired.

#### 1.1 Statement of Problem

VLSI based dedicated computing structures offer great potential for optimizing problem throughput and hardware investment. Yet many aspects of the design and implementation of these ideas still remain incomplete or underdeveloped. Such problems include the inner details of various processing elements, packaging constraints and input/output considerations.

The goal of this work is to develop and assess aspects of a special purpose VLSI computing architecture to triangulate large scale, band form, linear equation systems. Specific areas to be examined are as follows:

1. The design and evaluation of a computing array

structure for this problem type is presented. The global dimensions of this structure are based on a function of coefficient matrix bandwidth and on the assumption of an implementation of the row-ordered permutation of Gaussian elimination resulting in a strict upper triangulation of the coefficient matrix. A coefficient input and output patterns are presented.

- 2. Individual processing elements are designed and evaluated. This includes exploration of various fixed-point multiplier, adder and divider algorithms. Selection of the best algorithms are based on comparisons of speed, area, modularity and local communication properties.

- 3. Possible input demultiplexer and output multiplexer circuit designs are evaluated. Parameters which are examined include area geometry, propagation delay and a consideration of the effects of the fundamental limitation of pinouts per chip. I/O designs are also evaluated with respect to potential bottlenecking of operands which can severely degrade the overall system throughput.

- 4. Realistic estimation of the total propagation delay versus matrix bandwidth and chip size versus matrix bandwidth of the entire chip is made by incorporating the optimal computing structure and I/O circuit designs.

The results of this work, particularly tasks 1 and 4, enable a more comprehensive assessment of VLSI's potential for reducing solution time of large linear equation system problems.

## 1.2 Approach

In the past few years the advantages of systolic, hexconnected array structures, realizable with VLSI technology, were introduced [12, 13]. These structures have been shown to be applicable to many matrix computation problems including Gaussian elimination [16, 17].

The first step of this work is the development of a computing array to perform a complete factorization (not merely L-U decomposition) of an N x (N + 1) matrix ( $\underline{A}$  augmented by  $\underline{b}$ ) in minimum unit time. In other words, the objective is to create a set of possible input patterns from the nonzero entries of a matrix, most suitably in band form, and implement a computing structure in a simple hexagonal array. The plan is that these two structures, the input pattern and the computing array, may be manipulated back and forth until their subsequent output pattern fits the required upper triangular pattern. The output pattern should be that which is most conducive to rapid back-substitution.

The second step entails study of the input/output problems for the main body of the chip - the developed computing array. The number of pinouts per chip of current and projected VLSI technology give primary ideas on how control

signals, fan-in demultiplexer and fan-out multiplexer circuits must be developed. In order to avoid a potentially serious I/O bottleneck problem, the major point of these input and output circuit designs is to provide high speed channels for operand routing. Also, design regularity and low power requirements, necessary for good VLSI implementation, are considered.

The third step develops some of the inner details of the processing element structures. In order to fully assess the area geometry and propagation delay of these processing elements, schematic logic circuit diagrams of various arithmetic algorithms are studied. For example, the method for designing an MAC (Multiply-Add Cell) encompasses the following:

- 1. Review existing LSI multiplication algorithms and evaluate the optimal hardware implementation in terms of design complexity, local connection properties, modularity, speed and area. Also, study a possible attached high-speed full adder using identical procedures.

- 2. Develop a network realization of the chosen optimal fixed-point arithmetic algorithm for a complete MAC. This step will lead to quantification of the necessary performance measurements of area geometry and propagation delay.

- 3. Develop a hand layout of the fundamental building block modules, such as a full-adder, in terms of

scalable minimum lithographic linewidth,  $\lambda$ . Using these design layouts, quantify the  $A_C$  (area per cell) in terms of  $\lambda$ , and  $T_C$  (propagation delay per cell).  $T_C$  will be determined in terms of typical basic inverter discharge time, also a function of  $\lambda$ , and any non-negligible communication path delays.

The fourth step is the development and evaluation of the required building block modules for several possible I/O circuit strategies, then quantify area geometries and propagation delays of these modules using the methodology of step 3.

The fifth and final step is a Fortran-coded simulation to provide two important comparisons, total propagation delay versus matrix bandwidth and chip size versus matrix bandwidth. These comparisons are determined by varying parameters of minimum lithgraphic linewidth, word size and matrix bandwidth. The results, combined with predictions of future trends in VLSI technology, will help evaluate, and hopefully promote, the feasibility and advantages of special purpose VLSI computing structures as linear equation solvers.

#### 1.3 Contributions

This section provides readers with an additional understanding of the original research which has been accomplished in this dissertation work.

- 1. The successful design of a new VLSI systolic array algorithm based on concurrent Gaussian elimination is presented. This algorithm is unique in that it triangulates a band form matrix  $\underline{A}$  augmented by vector  $\underline{b}$  (in other words,  $\left\{\underline{A} \mid \underline{b}\right\}$ ). The array requires O(N) unit time and O(B<sup>2</sup>) processing elements, (where N and B are the dimension and half bandwidth of  $\underline{A}$ , respectively). The new algorithm, requiring O(B<sup>2</sup>) processing elements represents a dramatic improvement over previously published algorithms of this form which have required O(N<sup>2</sup>) PE's. This is a tremendous saving, particularly when B << N.

- 2. The inner details of processing element designs are developed and assessed. This entails evaluating and configuring the required MAC's (Multiply and Add Cell) and DC's (Divider Cell). The best designs were obtained subject to criteria of design regularity, design complexity, chip area and propagation delay requirements.

- 3. The best input strategy, the data controlled algorithm and the best output strategy, the shift-register control sequence (SCS) algorithm, were developed and evaluated. These strategies helped tremendously in minimizing a potential I/O bottleneck problem which was anticipated in systolic array structures of this type.

- 4. Determinations of the entire chip area geometry and total propagation delay were obtained using a

comprehensive chip simulation. Results were based on various word size, minimum lithographic linewidth and matrix bandwidth parameters. The simulation results have indicated that this type of special purpose VLSI chip indeed provides rapid triangulation of large scale, band form linear equation systems.

#### CHAPTER II

#### BACKGROUND

2.1 Array Processors and the Vector Nature of Gaussian Elimination

Array processors are generally realized as one (vector) two (matrix) dimensions of processing elements which allow data operands to be processed in parallel. In the literature [37], array processors have been defined as those structures for which the information unit (data string) is an array of one or two dimensions. This would define processors in which both serial and parallel execution would be implemented in a pipelined or even a parallel pipelined The definition of array processors as used here are those systems where the processing elements have both parallel and pipelined structures. There are two basic classifications of array processors. First, the stand alone type, such as the CRAY-1 or the CDC STAR-100, and second, the scientific processors like the AP-120 B/FPS-164 family or the MAP-300. The latter classification has been referred to as a special algorithm processor [37]. Array architectures are most advantageous for problem types which are vector or array oriented with highly repetitive arithmetic operations. The typical operations include vector addition and subtraction, matrix multiplication and convolution, and many advanced functions like fast Fourier transform. Applications of array processors have been proven to be

cost-effective in areas such satellite image processing [4], power system network computation [5], reservoir simulation [6], and pattern recognition [7].

For a class of large scale, linear equation systems,  $\underline{A} \cdot \underline{x} = \underline{b}$ , the method of reducing solution time via array processors is to apply a vectorized form of Gaussian elimination optimizing the use of these processors' parallel and pipelined structures in the triangulation procedure of the coefficient matrix.

For example, consider an N x N matrix. A possible FORTRAN coded program segment to perform rwo-order Gaussian elimination is

DO 1 K = 1, N

DO 1 J = 1, K

DO 1 I = J + 1, N

IF (K.EQ.J) GO TO 2

A(K,I) = A(K,I) - A(K,J) \* A(J,I)

GO TO 1

A(K,I) = A(K,I)/A(J,J)

2

1

CONTINUE

The best way to expose the vector nature of this row-ordered elimination is to inspect the inner loop, on index I, of this Fortran program. Neglecting, at first, the conditional branch step for the diagonal divide operation, the program can be rewritten as,

DO 1 K = 1, NDO 1 J = 1, KDO 1 I = J + 1, NA(K,I) = A(K,I) - A(K,J) \* A(J,I)

1

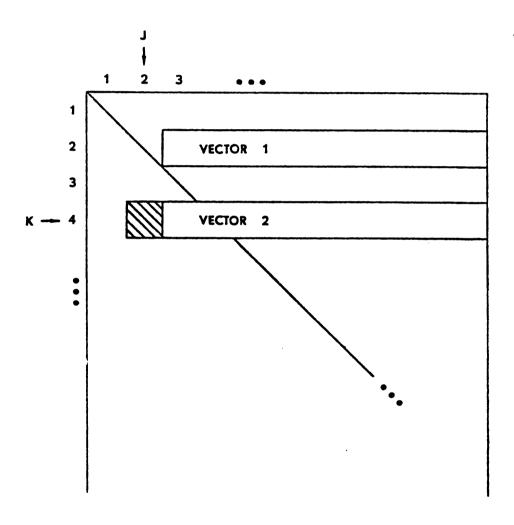

The DO loop on index I, from J+1 to N, is again the inner loop. For each J in the second loop, from 1 to K, the inner loop can be completed in two vector operations. The vectors and scalar operands required at this step are illustrated in Figure 2.1. In this example, K = 4, J = 2 and element A(4,2) is to be eliminated from the remainder of row 4.

The two vector operations required to eliminate A(4,2) are as follows. First, scalar-vector multiplication, that is, scalar element A(4,2) multiplies vector 1. Second, vector-vector subtraction, that is, vector 2 is subtracted from the updated vector 1. These vector functions are commonly available in most array processors' program libraries [8].

To illustrate the advantages of the array processors' melding of parallel and pipelined structures, assume a segmented multiplier where the operation time of the longest segment is  $T_{\rm op}$ . Also, assume that both a pipelined and serial processor use the same segmented multiplier, but, the serial processor does not use the pipelined capability. Then, neglecting the set-up time, it takes  $T_{\rm op}$  time for each multiply using the pipelined structure and  $n \cdot T_{\rm op}$  time, where

Figure 2.1 Vector nature of a full matrix row-order elimination step [8].

n is the number of segments, for the serial processor to perform its multiply.

If we consider a vector of length N, the serial computer requires N·n Top time to complete the entire vector multiplication; whereas the segmented architecture can perform this multiplication in N·Top time, neglecting set-up time. Under this simple assumption, the pipelined processor is potentially n times faster than the serial version. Therefore, array processors have computational advantages over serial computers on vector oriented problems. One fundamental drawback, however, is the optimal utilization of array processors' capabilities. A programmer must be able to detect optimal parallelism and pipelining of mathematical forms, then write efficient code for the array processor to achieve optimal and cost-effective results.

## 2.2 VLSI Architectures and Systolic Algorithms

Progress in microelectronics has been extremely rapid in the past few years. The ability to fabricate 10<sup>7</sup> to 10<sup>8</sup> transistors on a single chip will be possible by the late 1980's [9, 10]. Array processors, as mentioned, are in many ways still general purpose machines (i.e., programable). With VLSI technology, the design of truly special purpose machines will become a reality.

VLSI implementations will improve cost, speed and size of electronic components. Current interest lies in designing high-performance parallel algorithms that can be

implemented directly with low cost, high speed VLSI hardware. These devices are designed to be attached to a general purpose host computer as a plug-in component, capable of performing high speed, cost-effective computation.

A direct VLSI implementation of any computational algorithm should have the following properties [11]:

- A. Regularity -

- The algorithm must be implemented by only a few types of processing elements so as to reduce the design complexity and design cost.

- B. Local Communication -The processing elements must connect only to their nearest neighbors; global communications are to be avoided at all cost.

- C. Parallelism and Pipelining The algorithm should ideally use both parallel and pipelined processing concepts.

A "systolic algorithm", which employs both parallel and pipelined processing concepts, is one which can be implemented by a network of simple, regular processors that compute and transmit data synchronously [1]. These processors, with planar external connections, can be configured into various geometric structures utilizing different frameworks [12]. Kung first presented a special purpose array structure built of standard inner product step processors and one division function processor to carry out the L-U decomposition algorithm on a full matrix of arbitrary size

[13]. This algorithm is well suited for a VLSI chip implementation because of its regular processing cell structure, local communication paths and efficient parallelism and pipelining.

Kung provided researchers with an innovative idea and encouraged others to develop different arithmetic algorithms using VLSI systolic function elements [12]. In his work, however, he neglects mention of any practical details, such as I/O considerations and processor cell designs. These issues will be considered in later chapters of this thesis.

Recently, several researchers have advanced the notion that these systolic array architectures can be configured to other highly concurrent numerical algorithms such as matrix multiplication, matrix inversion and recursive digital filtering [1, 9, 13, 14, 15]. Especially, Hwang and Cheng have designed a VLSI architecture to perform L-U decomposition of an entire linear system of equations  $\left\{ \underline{A} \mid \underline{b} \right\}$ , advancing Kung's design of merely triangulating  $\underline{A}$ . The upper triangular portion of the whole system's L-U decomposition is analogous to the forward elimination algorithm used in dense matrix linear equation systems [16, 17]. The required time slots and processing elements of this previously published algorithm, when used for triangulating band form linear equation problems, are O(N) and O(N<sup>2</sup>), respectively.

## 2.3 Design Methodology of VLSI Systems

A systematic method is essential in designing this kind of complex system. The design problems can best be tackled when decomposed into several subproblems with simple and clear interrelationships.

VLSI chip design may involve the layout of as many as  $2 \times 10^5$  gates on a chip [18]. Due to this complexity it is crucial to utilize a supporting system design methodology. Three basic design concepts - hierarchy, regularity and testability must be followed to ease VLSI design complexity. A brief description of each term is given below:

### 1. Design hierarchy -

VLSI system designers are forced to use both top-down analysis and bottom-up synthesis procedures [11]. For practical VLSI system design, it is almost impossible to consider global data and control flow, circuit design and transistor characteristics all at once. Consequently, the top-down design levels are partitioned into five levels as follows:

#### A. Algorithm level -

The initial step involves exporing possible parallelism and pipelining of the given problem. Then, the algorithms' performance, i.e. chip area and time parameters, may be estimated as functions of problem parameters; for example, matrix dimension.

Finally, the optimal algorithm is evaluated and

chosen in terms of area-time trade-off, design complexity and practical design constraints.

#### B. Block level -

At this step, implementation of the algorithm via functional blocks linked by data and control flow begins. This level of design combines circuit functions and relative circuit positions as well as signal inputs and outputs of different blocks.

#### C. Gate level -

Configuration of the function blocks with logic gates (NAND, NOR, INVERTER, etc.) and memory elements (flip-flops, delay lines, etc.) is performed at this stage. Additionally at this point, a fault diagnosis or fault testing procedure is used to detect the proper function of the logic circuits. These results may then be used to compare with future field testing results. In other words, a set of benchmark parameters are formulated.

#### D. Transistor level -

Next, gate level circuits are transferred to the primary transistor level circuits. The area geometry ration of pull-up transistor to pull-down transistor of the logic gates, according to various gate categories and gate couplings, are calculated.

## E. Physical layout level -

The complexity of a VLSI system obviously makes hand layout too cumbersome to even consider.

Modern CAD (Computer-Aided Design) layout tools, such as an interactive layout system, enable the designer to create and edit element layout patterns directly on a CRT screen. The final pattern, called a design file, can be represented in an intermediate form; for example, the CIF (Caltech Intermediate Form) [9]. Then, the intermediate form file is transferred to a pattern generation file which in turn is used in the mask making process.

## 2. Design regularity -

The purpose of incorporating design regularity is to minimize the design time. In bottom-up synthesis, if only a few primitive cells have been used for creating function blocks, then the design time will decrease tremendously. Also, the area geometry of the interconnection wires can be reduced by manipulating possible processing element configurations.

## 3. Design testability -

In the past, SSI and MSI logic designers were trained to design with the fewest gates. In this simple situation AC design parameters such as rise time, fall time and circuit delay could easily be tested. The inherent complexity of a VLSI chip, however, now makes the testability consideration much more important. The task is is even more complex since, with VLSI, it is impossible to test every circuit. Consequently, circuit or logic

simulation is required to create a fault-free model, which forms a benchmark by which actual results may be judged. An actual circuit is then exercised by means of a set of stimuli called an input vector. Then, the result or output vector is measured and compared with the result of the logic simulation.

Eichelberger has suggested two new concepts of logical structure design conducive to VLSI design and testability [19]. First, one must structure the design so that the subsystem operation time is calculated by the output stabilization time due to the changes of input states. For synchronous logic, the output response time is the obvious limiting factor in determining minimum clock cycle time. Second, one should design the internal storage elements as shift-register type latches, which greatly simplifies the testing procedure.

These two concepts can be especially beneficial for testing high speed pipelined structures. Data flow is controlled by a two-phase nonoverlapping clock which controls the latches; one phase for pumping data into latch, the other for refreshing or pumping out data. The clock cycle time is determined by the sum of the steady-state delay of the subsystem and latch. The advantages of this type of VLSI testability are two-fold. First, the internal storage elements (latches) provide the input/output ports for tester's probes and thus, a convenient way to at least

isolate faulty circuits. Second, since data flow is synchronously controlled, the clock rate can be slowed down during the test.

#### CHAPTER III

#### COMPUTING STRUCTURE DESIGN

### 3.1 Band Form Algorithm

Central to the development of a systolic array for band matrix triangulation are some definitions of the type of applicable band forms and the nature of Gaussian elimination for such matrices. The algorithm is most analogous to the row-ordered permutation of the elimination procedure. The following definitions allow a quantification of operative matrix elements as a function of B, the matrix bandwidth. This will ultimately lead to quantification of crucial parameters of the computing structure, also functionally related to B.

An N x N band form matrix will be defined as

$$\underline{A} = \left\{ a_{ij} : a_{ij} = 0, \forall |i - j| > B \right\}$$

(3-1)

where B, the bandwidth is given by

$$B = \max \left\{ \left| i - j \right| : a_{ij} \neq 0 \right\}$$

(3-2)

for i, j = 1, 2,..., N. Note that structural symmetry only (not absolute symmetry) is implicit in this definition. Furthermore, B, as defined here, is sometimes referred to as the half-bandwidth, spanning from the matrix diagonal to the rightmost nonzero matrix element.

The entire equation system,  $\underline{A} \cdot \underline{x} = \underline{b}$ , can then be described by the pair  $(\underline{A}, \underline{b})$ , where  $\underline{A} = \{a_{ij}\}$  is an N x N

matrix in structurally symmetric band form of bandwidth B and  $\underline{b}=(b_1,\,b_2,\ldots,\,b_N)^T$  is a column vector of size N. Conducive to Gaussian elimination, the system can be described as an N x (N + 1) augmented matrix  $\left\{ \underline{A} \mid \underline{b} \right\}$ .

The elimination procedure will reduce  $\left\{ \underline{A} \mid \underline{b} \right\}$  to upper triangular elements  $U = \left\{ u_{ij} \right\}$  for i = (1, 2, ..., N), j = (i, i+1,..., i+B), augmented by a revised column vector  $\underline{d}$ . This can be easily illustrated by considering a 9 x 10 augmented system with a bandwidth of 3 as depicted in Figure 3.1a. After the upper triangulation has been performed, the system appears as illustrated in Figure 3.1b.

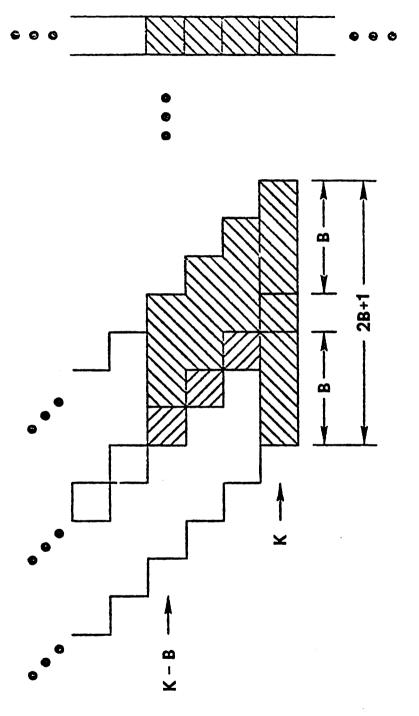

For larger systems, some more interesting aspects can be exposed. Consider a large  $\underline{A}$  with B << N. An examination of the elimination of row k from such a system, as shown in Figure 3.2, reveals some useful information.

The shaded areas of this figure represent the total number of matrix elements required to perform the elimination of row k. As depicted, the length, in matrix elements, of row k is 2B + 1. This will be called the working row. Neglecting the zero elements then, the width of an augmented working row is merely 2B + 2 nonzero elements.

Examining the required upper triangular elements needed to eliminate the augmented working row, a simple geometric analysis reveals that  $B^2$  + B elements of  $\underline{A}$  are required. In addition, again neglecting null entries, B elements of the  $\underline{d}$  vector (resolved  $\underline{b}$  vector elements) are required. Thus the total number of active nonzero elements involved in the

Figure 3.1a Augmented matrix  $\{ \underline{A} \mid \underline{b} \}$ .

| u <sub>12</sub> | <sup>u</sup> 13 | <sup>u</sup> 14                 |                                 |                                                                                                                                                 |                                                                                                                                             |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                         | dı                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|-----------------|---------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| u <sub>22</sub> | u <sub>23</sub> | <sup>u</sup> 24                 | u <sub>25</sub>                 |                                                                                                                                                 |                                                                                                                                             |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                         | d <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 | u <sub>33</sub> | u <sub>34</sub>                 | <sup>u</sup> 35                 | <sup>u</sup> 36                                                                                                                                 |                                                                                                                                             |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                         | $d_3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 |                 | u <sub>44</sub>                 | <sup>u</sup> 45                 | u <sub>46</sub>                                                                                                                                 | u <sub>47</sub>                                                                                                                             |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                         | d <sub>4</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                 |                                 | u <sub>55</sub>                 | <sup>u</sup> 56                                                                                                                                 | u <sub>57</sub>                                                                                                                             | <sup>u</sup> 58                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                         | d <sub>5</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                 |                                 |                                 | <sup>u</sup> 66                                                                                                                                 | <sup>u</sup> 67                                                                                                                             | <sup>u</sup> 68                                                                                                                                                                                                                               | <sup>u</sup> 69                                                                                                                                                                                                                                         | d <sub>6</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                 |                                 |                                 |                                                                                                                                                 | u <sub>77</sub>                                                                                                                             | <sup>u</sup> 78                                                                                                                                                                                                                               | <sup>u</sup> 79                                                                                                                                                                                                                                         | d <sub>7</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                 |                                 |                                 |                                                                                                                                                 |                                                                                                                                             | u <sub>88</sub>                                                                                                                                                                                                                               | u <sub>89</sub>                                                                                                                                                                                                                                         | d <sub>8</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                 |                                 |                                 |                                                                                                                                                 |                                                                                                                                             |                                                                                                                                                                                                                                               | u <sub>99</sub>                                                                                                                                                                                                                                         | d <sub>9</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                 | <sup>u</sup> 22 <sup>u</sup> 23 | <sup>u</sup> 33 <sup>u</sup> 34 | u <sub>22</sub> u <sub>23</sub> u <sub>24</sub> u <sub>25</sub> u <sub>33</sub> u <sub>34</sub> u <sub>35</sub> u <sub>44</sub> u <sub>45</sub> | u22       u23       u24       u25       u36         u33       u34       u35       u36         u44       u45       u46         u56       u56 | u22       u23       u24       u25       u36       u36       u36       u36       u36       u47         u44       u45       u46       u47       u47       u56       u57         u54       u56       u67       u67       u67       u67       u67 | u22       u23       u24       u25       u36       u36       u47       u48       u46       u47       u47       u56       u56       u57       u58         u44       u54       u54       u56       u67       u68         u54       u57       u78       u78 | u22       u23       u24       u25       u36       u36       u25       u36       u36       u36       u37       u38       u38       u38       u38       u39       u |

Figure 3.1b Upper triangular elements of matrix  $\{ A \mid \underline{b} \}$ .

Figure 3.2 Large band form matrix.

elimination of augmented row k is given

$$E = B^2 + 4B + 2 \tag{3.3}$$

These elements, i.e., the shaded areas of Figure 3.2, will be referred to as the "window" of elements required to eliminate any given row k.

Now, focusing on the development of an ideal systolic computing array for such a band form system, a reasonable objective is to have the size of the array, in processing elements, related to this window of elimination. The window can then be viewed as "sliding down" the main diagonal eliminating rows as it passes. This is analogous to the function of the systolic array; row k is eliminated while the new augmented working row k + 1 is brought in; simultaneously, the resolved elements just above the window are placed on the output lines.

The advantage of such a scheme is simple and of great consequence. The size of the computing array, as will be shown, is limited by B, the bandwidth, in both width and depth.

## 3.2 Array Structure and Timing

Creation of the actual systolic array structure required manipulating a set of possible coefficient input patterns and arithmetic processing cells in order to produce properly resolved upper triangular elements at the output ports. Restrictions were based on structural simplicity,

regular connectivity and an ideal upper bound of O(B<sup>2</sup>) processing cells. Actual input alignment, as will be seen, required the injection of dummy zero and one elements, used as "spacers" in the operand string. The output string, also regularly interlaced with spacers, contains the necessary resolved upper triangular factors and the resolved column vector d for subsequent back-substitution.

The systolic array operates synchronously with latch arrays controlling operand flows between processing cells. There are no storage elements, save the latches, in the array.

The most difficult part of the design was to correctly align the <u>b</u> vector element stream through the array. Many of the possible input patterns and cell permutations presented data interference and conflict problems. This was eventually overcome by isolating those processing cells which perform the actual operations of resolving <u>b</u> into <u>d</u>; this portion of the hardware is called the D section. It is, however, constructed of precisely the same cells as the rest of the systolic array, differing only in interconnection pathways.

The array structure for a matrix of arbitrary dimension, N, and of bandwidth B=3 is presented in Figure 3.3. Two types of processing cells are used, corresponding to the two operations of the Gaussian elimination procedure.

The first and majority cell is labeled MAC (Multiply and Add Cell). It has previously been called an inner

Figure 3.3 Computing array structure for matrix of arbitrary dimension with B = 3.

product step processing element, and is a 3-input, 3-output cell calculating w = xy + z and performing the transfer x = x and y = y. The second cell performs the diagonal divide operation and is labeled DC (Division Cell). It is a 2-input, 2-output cell. The DC performs the division g = e/f and the transfer f = f. Both cell types are illustrated in Figure 3.3.

The complementation circle shown on the input of the topmost row of MAC's refers to a two's complement operation.

Inter-row registration, providing operand synchronization, is depicted by the thick black lines.

The array structure supports separate upward and downward traffic flows. Input coefficients are synchronously pumped into ports  $I_1$  through  $I_7$ . The number of required input ports is given by the full breadth of the matrix band or 2B+1 (refer to Figure 3.2). Columns of  $\underline{A}$  enter the ports every two cycles interspersed with the proper spacer elements. Table 3.1, a timing table, illustrates the operand strings for the example B=3 corresponding to Figure 3.3.

Once this initial upward stream reaches the DC level it proceeds downward toward the D section. At this point in time,  $t_3$  in the example,  $\underline{b}$  vector operands begin to enter port  $I_D$  of the D section. At the end of  $t_3$ ,  $b_1$  reaches the w output of the rightmost MAC in the D section and latches appropriately. During  $t_5$ ,  $b_2$  pumps in from  $I_D$  and  $b_1$  is transferred to the bottom latch of the D section waiting to

|                                  | 11              | 12              | 13                                    | 14              | <sup>I</sup> 5    | 16              | 17              | ID             | 0,              | 02               | 03              | 04              | 00             |

|----------------------------------|-----------------|-----------------|---------------------------------------|-----------------|-------------------|-----------------|-----------------|----------------|-----------------|------------------|-----------------|-----------------|----------------|

| tı                               |                 |                 |                                       | all             | a <sub>21</sub>   | a <sub>31</sub> | a <sub>41</sub> |                | <del></del>     |                  |                 |                 |                |

| t <sub>2</sub>                   |                 |                 |                                       |                 |                   |                 |                 |                |                 |                  |                 |                 | •              |

| t <sub>2</sub><br>t <sub>3</sub> |                 |                 | <sup>a</sup> 12                       | a <sub>22</sub> | <sup>a</sup> 32   | <sup>a</sup> 42 | a <sub>52</sub> | bl             |                 |                  |                 |                 |                |

| t <sub>4</sub>                   |                 |                 |                                       |                 |                   |                 |                 |                | וויי            |                  |                 |                 |                |

| t <sub>5</sub>                   |                 | <sup>a</sup> 13 | <sup>a</sup> 23                       | <sup>a</sup> 33 | <sup>a</sup> 43   | <sup>a</sup> 53 | <sup>a</sup> 63 | b <sub>2</sub> |                 | u <sub>12</sub>  |                 |                 |                |

| t <sub>6</sub>                   |                 |                 |                                       |                 |                   |                 |                 |                | u <sub>22</sub> |                  | <sup>u</sup> 13 |                 |                |

| t <sub>7</sub>                   | a <sub>14</sub> | a24             | <sup>a</sup> 34                       | a <sub>44</sub> | <sup>a</sup> 54   | <sup>a</sup> 64 | <sup>a</sup> 74 | b <sub>3</sub> |                 | u <sub>23</sub>  |                 | u <sub>14</sub> |                |

| t <sub>8</sub>                   |                 |                 |                                       | 1               |                   |                 |                 |                | u <sub>33</sub> |                  | <sup>u</sup> 24 |                 | d1             |

| t <sub>g</sub>                   | <sup>a</sup> 25 | <sup>a</sup> 35 | <sup>a</sup> 45                       | <sup>a</sup> 55 | , a <sub>65</sub> | <sup>a</sup> 75 | <sup>a</sup> 85 | b <sub>4</sub> |                 | <sup>U</sup> 34  |                 | u <sub>25</sub> | 1              |

| t <sub>10</sub>                  |                 |                 |                                       | 1               |                   |                 |                 |                | u <sub>44</sub> |                  | <sup>u</sup> 35 |                 | d <sub>2</sub> |

| <sup>t</sup> 11                  | <sup>a</sup> 36 | <sup>a</sup> 46 | <sup>a</sup> 56                       | <sup>a</sup> 66 | <sup>a</sup> 76   | <sup>a</sup> 86 | <sup>a</sup> 96 | b <sub>5</sub> |                 | <sup>'u</sup> 45 |                 | u <sub>36</sub> | į              |

| <sup>t</sup> 12                  |                 |                 |                                       | 1               |                   |                 |                 |                | u <sub>55</sub> |                  | <sup>u</sup> 46 |                 | d <sub>3</sub> |

| t <sub>13</sub>                  | a <sub>47</sub> | <sup>a</sup> 57 | <sup>a</sup> 67                       | a <sub>77</sub> | <sup>a</sup> 87   | <sup>a</sup> 97 |                 | <sup>b</sup> 6 |                 | u <sub>56</sub>  |                 | u <sub>47</sub> | l              |

| t <sub>14</sub>                  |                 |                 |                                       | ı               |                   |                 |                 |                | u <sub>66</sub> |                  | u <sub>57</sub> |                 | d <sub>4</sub> |

| t <sub>15</sub>                  | a <sub>58</sub> | <sup>a</sup> 68 | <sup>a</sup> 78                       | <sup>a</sup> 88 | <sup>a</sup> 98   |                 |                 | b <sub>7</sub> |                 | <sup>u</sup> 67  |                 | <sup>u</sup> 58 |                |

| t <sub>16</sub>                  |                 |                 |                                       | 1               |                   |                 |                 |                | <sup>u</sup> 77 |                  | <sup>u</sup> 68 |                 | d <sub>5</sub> |

| <sup>t</sup> 17                  | <sup>a</sup> 69 | a <sub>79</sub> | <sup>8</sup> 89                       | a <sub>99</sub> |                   |                 |                 | bg             |                 | <sup>u</sup> 78  |                 | u <sub>69</sub> |                |

| <sup>t</sup> 18                  |                 |                 |                                       |                 |                   |                 |                 |                | <sup>u</sup> 88 |                  | u <sub>79</sub> |                 | d <sub>6</sub> |

| <sup>2</sup> 19                  |                 |                 |                                       |                 |                   |                 |                 | b <sub>9</sub> |                 | u <sub>89</sub>  |                 |                 | l              |

| t <sub>20</sub>                  |                 | · .             | · · · · · · · · · · · · · · · · · · · |                 |                   |                 | 1               |                | u <sub>99</sub> |                  |                 |                 | d <sub>7</sub> |

| <sup>t</sup> 21                  |                 |                 |                                       |                 |                   |                 |                 |                |                 |                  |                 |                 |                |

| t <sub>22</sub>                  |                 |                 |                                       |                 |                   |                 |                 |                |                 |                  |                 |                 | d <sub>8</sub> |

| t <sub>23</sub>                  | 1               |                 |                                       |                 |                   |                 |                 |                |                 |                  |                 |                 |                |

| t <sub>24</sub>                  |                 |                 |                                       |                 |                   |                 |                 |                |                 |                  |                 |                 | <b>d</b> 9     |

Table 3.1 Port-coefficient timing table.

enter input z of the second rightmost MAC.

Once the first column of lower triangular factors reaches the y inputs of the D section, the bottommost latches are filled with the required  $b_i$  elements so that the generation of the new right hand side vector elements,  $d_i$ ,  $i=2,3,\ldots$ , N, can begin. Note that during the previous time step,  $d_1$  (which equals  $b_1$ ) appeared at port  $0_d$  of the D section. Then, D section outputs appear at port  $0_d$  every two time slots.

# 3.3 Cell, Port and Time Slot Counts

The salient property of this new algorithm is that crucial counts of input-output ports and processing cells are found to be functionally related to the matrix bandwidth and not the full matrix dimension. This fact is quite important as many systems of large dimension yield tightly banded matrices. Furthermore, many sparse coefficient matrices can be reordered into band form which for some problem types have been shown to yield B = 0.10 N [8].

It has been determined that the number of input/output ports are 2B + 2 and B + 2, respectively. It must be remembered that each port is m bits wide, m being the number of bits per word. This introduces a very critical pin limitation problem which will be addressed in the input/output circuit design chapter.

The algorithm requires far less processing cells than previously published schemes which could be classified as

requiring  $O(N^2)$  cells, N being the full matrix dimension [16]. Specifically, B(B+1) MAC's and B DC's are required, advantageously classifying the algorithm as needing just  $O(B^2)$  cells. Of course, this can only be applied to those sparse coefficient matrices for which bandwidth reduction is effective.

As far as time requirements are concerned, the new algorithm requires 2N + 2B time slots, thus classifying it as an O(N) algorithm. This is on the same order as other systolic array algorithms, which require many more processing cells for this type of problem [16].

# 3.4 Floating-point Considerations

The computing structure presented in Section 3.2 is basically constrained to a fixed-point binary number system due to the nature of its processing element designs. It is possible, however, to consider processing fixed-point numbers which are the pre-adjusted mantissas of previous floating-point coefficients. This possibility, of course, is a crude approach to a true floating-point solution, but, due to current limitations of chip size and lithographic linewidth, it deserves further investigation for, at best, a near term application. It is realized, and must not be understated, that this approach is extremely vulnerable to the dynamic range of the input matrix entries and will work only for those problems which possess well tempered coefficients of tight dynamic range. A possible candidate for

this dedicated computing structure is the class of matrices with all positive and strictly diagonally dominant coefficients, such as the admittance matrix of a power system load flow problem. For a well conditioned matrix with these properties, no unpredictable overflow problem will occur during the elimination procedure if the following proposed fixed-point scheme is considered.