# SWITCHED CAPACITOR-BASED DC-DC CONVERTER WITH ULTRA-HIGH EFFICIENCY, POWER DENSITY AND VOLTAGE REGULATION CAPABILITY

By

Deepak Gunasekaran

## A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

Electrical Engineering—Doctor of Philosophy

2018

#### **ABSTRACT**

# SWITCHED CAPACITOR-BASED DC-DC CONVERTER WITH ULTRA-HIGH EFFICIENCY, POWER DENSITY AND VOLTAGE REGULATION CAPABILITY

By

## Deepak Gunasekaran

High efficiency and high power-density DC-DC converters are a key requirement in modern Power Electronics systems. Solar photovoltaic (PV) systems, EV/HEV powertrains and Data-centers are a few key examples. Traditional bridge-based DC-DC converters are commonly used in most systems that need a high voltage-gain. The presence of multiple stages in them affects the overall efficiency of the converter. In comparison, Dickson type switched capacitor DC-DC converters (SCCs) offer a single stage solution that lead to key advantages such as high efficiency, high power density, ease of control and elimination of central magnetic components in the system. However, their application in power conversion is limited due to the following reasons:

- Conventional SCCs have two fixed operating states. Operating the converter between these

states leads to a fixed voltage gain in boost mode and fixed step-down ratio in buck mode

operation. The output voltage cannot be regulated for varying inputs and results in larger

output capacitor ratings and larger voltage stress on downstream converters.

- 2. As the required voltage-gain increases, it leads to increased switch count and larger volume of required passives. Due to the presence of multiple floating switches, it also increases the complexity of gate drive and auxiliary power stages. This leads to lower efficiency and power density at high gains.

The key contributions of this dissertation to the field of switched capacitor-based power conversion are as follows:

- 1. The concept of utilizing additional transition mode operating states for Dickson type SCCs is introduced. This enables the possibility of achieving real-time gain variation using SCCs without adding additional stages or passive components down-stream. These states are designed to not affect the steady-state efficiency of the converter. In comparison to traditional SCCs, it results in a 30% reduction in the voltage rating of output capacitors and down-stream converter switches when used for a PV system application. A peak efficiency of 96+% is achieved for a 1-kW prototype.

- 2. During gain transition, transient current at the input side of the SCCs relies (to some extent) on the trace inductance present in individual switched capacitor cells. A capacitive energy re-distribution approach for switched capacitor cells is proposed to minimize the input current transitions seen at the input of the converter. This enables 'smooth' gain transitions in the SCCs. Experimental results on a 1-kW prototype converter illustrate that peak current transient is limited to well-within 1.5 times the rated current through the converter.

- 3. A resonant Dickson type SCC configuration using GaN HEMTs that enables ultra-high efficiency and power density at high voltage step-down ratios is proposed. Some of the key aspects of the proposed configuration are the ability to maintain minimum number of switches, a distributed inductive-capacitive approach to power transfer in each individual SCC cell, a highly-efficient integrated gate drive stage and optimally designed passive components. The proposed configuration is designed to meet specifications of a 270 V/28 V (nominal) power converter in a more-electric aircraft. A peak efficiency of 99.1% and a power density of over 5 kW/L is achieved for a 300 W converter prototype.

Dedicated to my wife, Vidhya Ramalingam, for always being my pillar of strength.

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to express my gratitude to my advisor, Dr. Fang Z.Peng. I thank him for accepting me as a student and guiding me all the way. His amazing level of expertise in the field, motivation, kind heartedness and trust in me has enabled me to hone a diverse set of skills crucial for a career in power electronics. I can't thank him enough for everything he has done for me. I consider it an honor to be his student.

At this point, I want to thank a few key people without whom I wouldn't have made it this far. First, my father, Dr.M.K.Gunasekaran for being my role-model. His limitless passion for engineering, ultra-efficient work rate and high standards of excellence are my greatest sources of inspiration. Next, to my master's advisor, Dr. L. Umanand for building my foundation and for making Power Electronics and research extremely interesting during my formative years back in Bangalore, India.

I would like to thank my MSU professors: Dr. Joydeep Mitra for teaching me a set of excellent courses on Power Systems and his valuable suggestions as a committee member. Dr. Elias Strangas for teaching a wonderful course on Motor Drives. Dr. Bingsen Wang and Dr. Chunqi Qian for their valuable comments and suggestions as committee members.

I am indebted to the various funding sources that enabled me to work on several different projects at MSU. Dr.Peng's research assistantships for majority of my stay, the ECE department for several fellowships and teaching assistantships, OISS for the ISEA award and multiple tuition awards. The

Lillian-Kumata foundation for a tuition award, Engineering Dean's office and Graduate school for travel support and Graduate school for the research enhancement award.

I would like to thank the following PE lab folk for their help and good camaraderie during my stay in the lab: Ujjwal Karki, Hulong Zeng, Xiaorui- Wang, Yunting Liu, Nomar Gonzales, Yaqub Mahnashi and Allan Taylor. I would like to specially acknowledge my good friend, Ujjwal Karki for always having my back during uncertain times and for his help with recording waveforms on several occasions. I would also like to thank visiting professors, Gujing Han and Liang Qin and exchange doctoral student Kazuto Takagi for their contributions and friendship. My journey wouldn't have been the same without all of these people. I would like to thank my good friends of East Lansing: Abhijna Parigi and Danny O'Donnell for going over and beyond to help me and coach me at times of dire need. They always make me feel at home. Gopi Musunuru for his good sense of humor and light-heartedness that always help me unwind.

Last, I would like to thank the people who form my 'backbone': My wife for brightening up my life. Her infinite love and affection have made me a better and stronger person. It is her constant motivation and support that helped me get over the finish line. My mother for being a great friend, for always being my anchor and for selflessly dedicating her life to her kids' cause. But for her sacrifices, I wouldn't have made it far. My father for inspiring me, constantly challenging me and always bringing the best out of me. My sister for always looking up to me and for filling my life with joy ever since she was born. My parents-in-law and brother-in-law for being ever so kind and for having immense trust in my pursuits. I am fortunate to have them as my family. My grandparents for leaving me with wonderful memories. My great-great-grandfather of Modachur for his legacy that continues to inspire generations to dream big.

# TABLE OF CONTENTS

| LIST OF TABLES                                                                            | ix |

|-------------------------------------------------------------------------------------------|----|

| LIST OF FIGURES                                                                           | x  |

| CHAPTER 1 INTRODUCTION                                                                    | 1  |

| 1.1 Centralized magnetics-based DC-DC converters                                          | 3  |

| 1.2 Switched Capacitor based DC-DC converters (SCCs)                                      | 5  |

| 1.3 The need for voltage regulation in Dickson type converters                            |    |

| 1.4 Ultra-high efficiency and power density SCC's for large voltage gains/step-down ratio |    |

| 1.5 Theses and their potential impact in power electronics systems                        | 12 |

| 1.6 Structure and Scope of the dissertation                                               |    |

| CHAPTER 2 VARIABLE (N/M)X SWITCHED CAPACITOR DC –DC CONVERTER                             | 16 |

| 2.1 Introduction                                                                          | 16 |

| 2.2 The (N/M)X Converter: General Configuration                                           | 20 |

| 2.3 Gain Variation using the (n/m)X converter                                             | 24 |

| 2.3.1 Load independent "shift-down"                                                       | 24 |

| 2.3.2 Load independent gain "shift-up"                                                    |    |

| 2.4 Equivalent Circuit and Transient Currents during Load- Independent Mode Change        | 28 |

| 2.4.1 8X to 6X Mode Transition                                                            | 29 |

| 2.4.2 6X to 4X Mode Transition                                                            | 34 |

| 2.4.3 4X to 6X Mode Transition                                                            | 34 |

| 2.5 Transient over-voltage analysis                                                       | 38 |

| 2.6 Design and Specifications of an (N/M)X Converter Prototype                            | 41 |

| 2.7 Experimental Prototype                                                                | 43 |

| 2.8 Design of a variable (4/0.5)X converter                                               |    |

| 2.9 Experimental Results                                                                  | 47 |

| 2.9.1 Fractional output using the (4/0.5)X converter                                      | 47 |

| 2.9.2 Controller implementation                                                           | 49 |

| 2.9.3 Load independent dynamic mode change                                                | 50 |

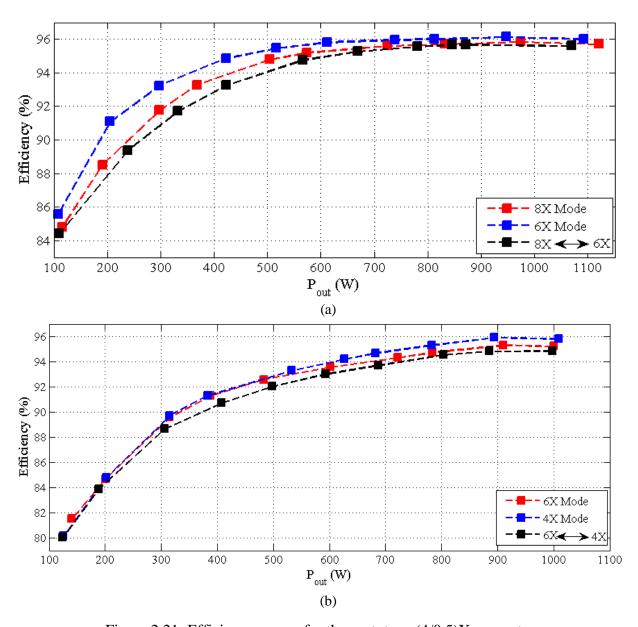

| 2.10 Efficiency analysis of (4/0.5)X Converter                                            |    |

| 2.11 Conclusions                                                                          | 57 |

| CHAPTER 3 IMPROVED "SOFT" GAIN-TRANSITION METHODS FOR (N/M)X                              |    |

| CONVERTER                                                                                 | 58 |

| 3.1 Introduction                                                                          | 58 |

| 3.2 The (n/m)X converter during transition between modes                                  |    |

| 3.3 Load assisted soft-transition in Gain                                                 |    |

| 3.3.1 Load assisted "Shift-down" mode using a dissipative load                            |    |

| 3.3.2 Load assisted "Shift-up" mode using a regenerative load                             |    |

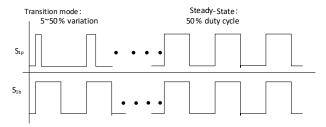

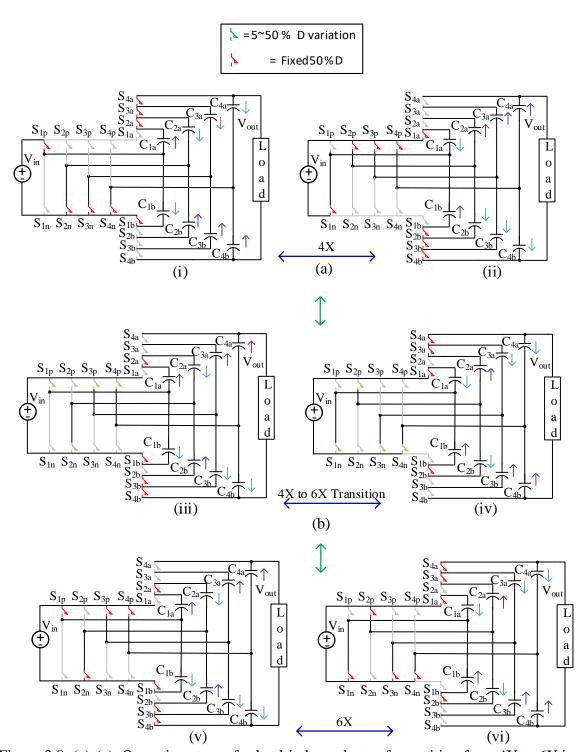

| 3.4 Load Independent Soft-Transition in Gain                                              | 68 |

| 3.4.1 Operating stage (a): 6X mode                                                        | 69 |

| 3.4.2 Operating stage (b): 6X to 8X mode transition         | 70            |

|-------------------------------------------------------------|---------------|

| 3.4.3 Operating stage (c): 8X mode                          |               |

| 3.5 Experimental Results                                    |               |

| 3.5.1 Load assisted soft-transition                         |               |

| 3.5.2 Load independent soft-transition                      |               |

| 3.6 Conclusion                                              |               |

| CHAPTER 4 ULTRA-HIGH EFFICIENCY AND POWER DENSITY RES       | ONANT DICKSON |

| CONVERTER                                                   | 80            |

| 4.1 Introduction                                            |               |

| 4.2 Resonant Dickson Converter                              | 83            |

| 4.2.1 Configuration                                         | 83            |

| 4.2.2 Operating modes                                       |               |

| 4.3 Loss Optimization                                       | 87            |

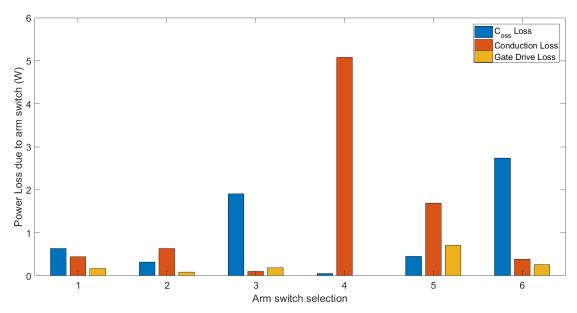

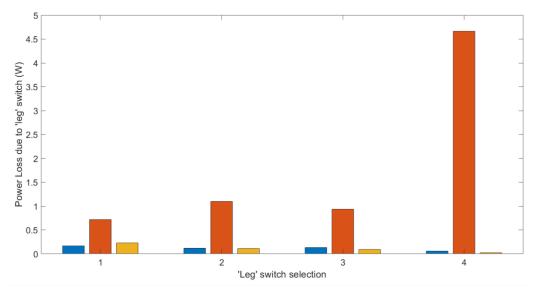

| 4.3.1 Optimal Switch selection                              | 87            |

| 4.3.2 Design of Passives                                    | 94            |

| 4.4 Efficient and Compact Gate Drive solution for GaN HEMTs | 98            |

| 4.5 Prototype Development                                   | 104           |

| 4.6 Experimental Results                                    | 108           |

| 4.7 Conclusion                                              | 113           |

| CHAPTER 5 CONCLUSION AND FUTURE WORK                        | 115           |

| 5.1 Summary of Chapter 2                                    | 115           |

| 5.2 Summary of Chapter 3                                    | 116           |

| 5.3 Summary of Chapter 4                                    | 117           |

| DEEEDENCES                                                  | 110           |

# LIST OF TABLES

| Table 1.1: Summary of switch and capacitor ratings in Dickson type converters                                                 |

|-------------------------------------------------------------------------------------------------------------------------------|

| Table 2.1: Input and load specifications of an example converter/inverter system                                              |

| Table 2.2: Gain selection based on input voltage variation in a (n/m)X converter                                              |

| Table 2.3: Component/ Parameter selection based on steady state operation of (4/0.5)X converter                               |

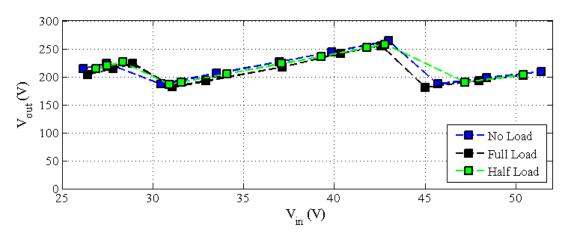

| Table 2.4: Experimentally Measured Gains for different location of the input voltage using an (n/m)X converter                |

| Table 2.5: Worst case error between theoretical and experimentally obtained gains for different loads in a (4/0.5)X converter |

| Table 4.1: Switches with superior FOM considered for arm switches                                                             |

| Table 4.2: Switches with superior FOM considered for leg switches                                                             |

| Table 4.3: Estimated loss for the overall converter considering conduction, switching and gate drive losses                   |

| Table 4.4: Suitable MLCC capacitors commercially available for selection of arm capacitance. 96                               |

| Table 4.5: Specifications of the LC network for a 280 V/ 28 V resonant Dickson converter for a resonant frequency of 85 kHz.  |

| Table 4.6: Key features of the pulse-transformer gate drive stage suitable for a GaN gate drive.                              |

| Table 4.7: Measured power draw from pulse-transformer based gate drive stage for GaN 103                                      |

| Table 4.8: Summary of different gate drive techniques for GaN HEMTs at 100 kHz switching.                                     |

| Table 4.9: Voltage step-down ratio vs load power at steady-state, V <sub>in</sub> =280 V 112                                  |

# LIST OF FIGURES

| Figure 1.1: Block diagrams of power converter/inverter systems in different applications: (a): Residential solar PV system, (b): Hybrid/Electric Vehicle (HEV/EV) powertrain, (c): More Electric-aircraft (MEA) power system |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Two types of magnetics-based DC-DC converters, (a): Two-switch bidirectional boost/buck converter, (b): Bidirectional Full-bridge DC-DC converter                                                                |

| Figure 1.3: The three variants of Dickson converter: (a) The original Dickson converter[8], (b): Modular Multi-level Clamped Capacitor converter (MMCCC[10]), (c): NX converter[11] 8                                        |

| Figure 2.1: A generic (k/m)X converter.                                                                                                                                                                                      |

| Figure 2.2: Operating states of an 8X converter.                                                                                                                                                                             |

| Figure 2.3: A (4/0.5)X converter with different locations of input voltage                                                                                                                                                   |

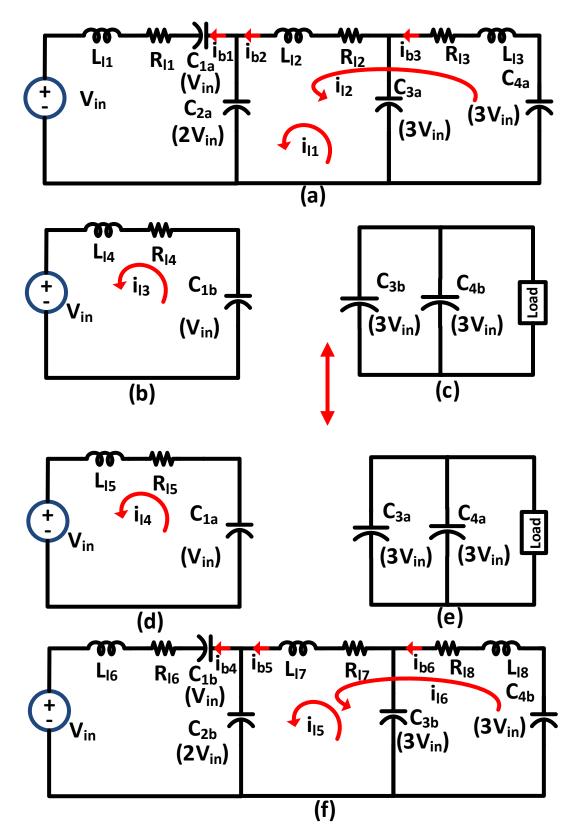

| Figure 2.4: Operating states for load independent "shift-up" and "shift-down" in voltage gain 27                                                                                                                             |

| Figure 2.5: Transient current loops during 8X to 6X mode transition                                                                                                                                                          |

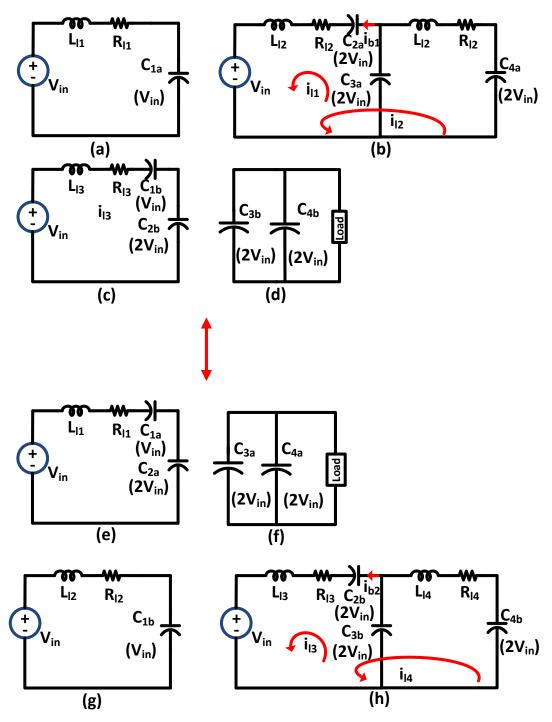

| Figure 2.6: Transient current loops during 6X to 4X Transition                                                                                                                                                               |

| Figure 2.7: Transient current loops during 4X to 6X Transition                                                                                                                                                               |

| Figure 2.8: Transient current loops during 6X to 8X Transition                                                                                                                                                               |

| Figure 2.9: (4/0.5)X Converter with lumped trace inductances                                                                                                                                                                 |

| Figure 2.10: (a) Inductor Current path during load during operation in 6X mode (Load independent), (b) Inductor current path during dead-time interval of 6X mode (Load-                                                     |

| independent)                                                                                                                                                                                                                 |

| Figure 2.11: Block diagram of an example converter/inverter system                                                                                                                                                           |

| Figure 2.12: Output voltage of DC-DC converter stage, $V_o$ for an input voltage of $V_{in}$ in a nX and $(n/m)X$ converter                                                                                                  |

| Figure 2.13: Block Diagram of the overall experimental setup                                                                                                                                                                 |

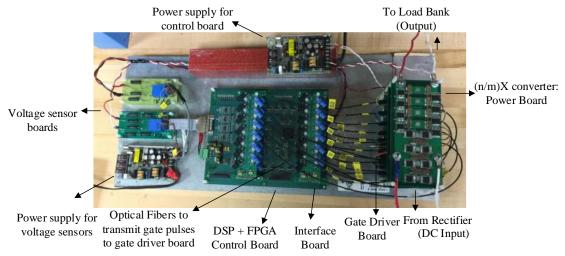

| Figure 2.14: Photograph of the overall experimental setup                                                                                                                                                                    |

| Figure 2.15: Worst- case transient current (Calculated) in (4/0.5)X converter                                                                                                                                                |

| Figure 2.16: Block schematic of the feed forward-control implemented on the prototype converter. 49                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

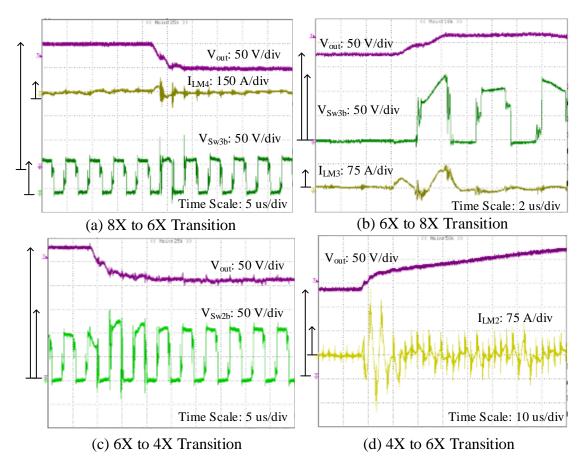

| Figure 2.17: Load independent mode change using the (4/0.5)X converter                                                                                                                                       |

| Figure 2.19: Transient over-voltage and current during load independent mode change 53                                                                                                                       |

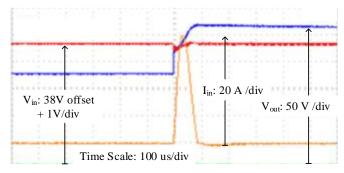

| Figure 2.20: Input transient during 4X to 6X load-independent mode change                                                                                                                                    |

| Figure 2.21: Efficiency curves for the prototype (4/0.5)X converter                                                                                                                                          |

| Figure 3.1: A $(4/0.5)X$ converter with lumped inductances $L_M$ and $L_{T_*}$                                                                                                                               |

| Figure 3.2: An operating state for the (n/m) X converter (a) Current direction resulting in natural clamping for all switches, (b): Current direction resulting in no natural clamping for the arm switches. |

| Figure 3.3: (a) Switching state during 8X to 6X transition, (b): dead-time interval during gain transition.                                                                                                  |

| Figure 3.4: Operating states in load assisted "shift-down" and "shift-up" for a (4/0.5)X converter.                                                                                                          |

| Figure 3.5: Illustration of loop and input current transients                                                                                                                                                |

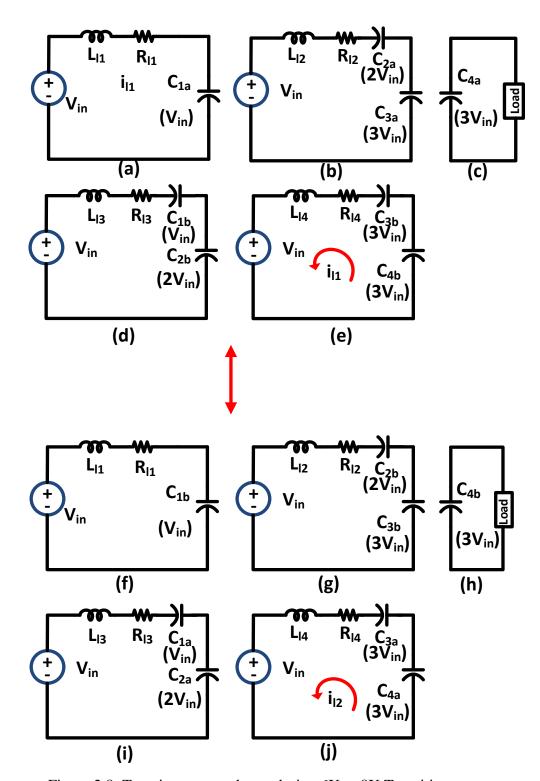

| Figure 3.6: (a)-(c): Operating stages for load-independent soft transition from 6X to 8X in a (4/0.5) X converter                                                                                            |

| Figure 3.7: Illustration of duty cycle control for leg switches in a (n/m)X converter                                                                                                                        |

| Figure 3.8: (a)-(c): Operating stages for load-independent soft transition from 4X to 6X in a (4/0.5) X converter                                                                                            |

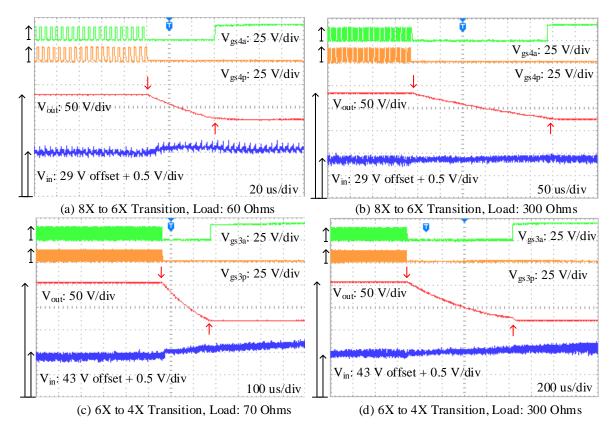

| Figure 3.9: Experimental results for the load assisted soft-transition                                                                                                                                       |

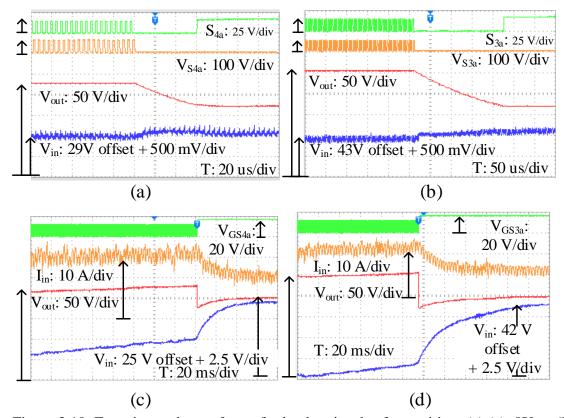

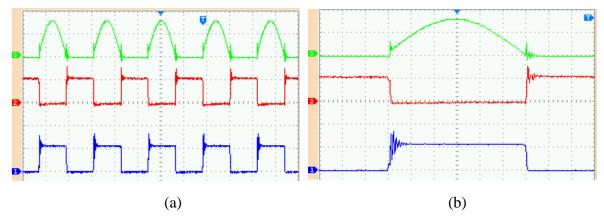

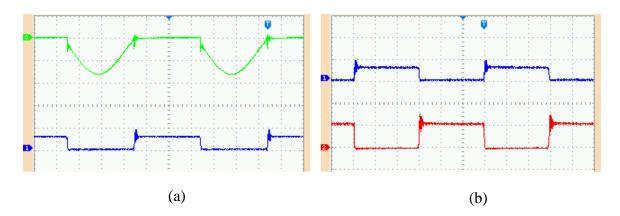

| Figure 3.10: Experimental waveforms for load assisted soft-transition: (a),(c): 8X to 6X Transition at Vin=30 V, Load = 60 Ohms, (b), (d) 6X to 4X Transition, Vin = 44 V, load = 70 Ohms.                   |

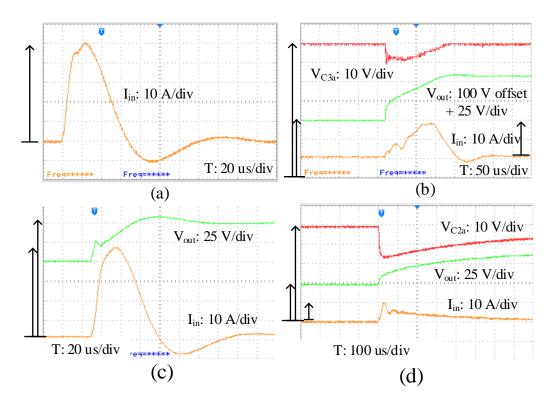

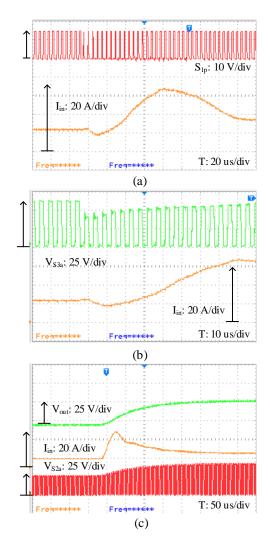

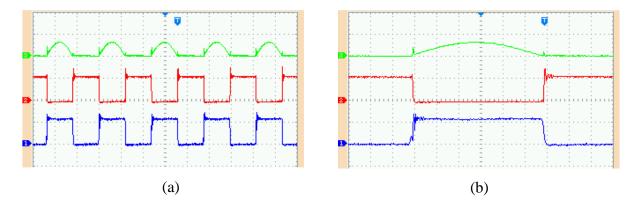

| Figure 3.11: Experimental results for load independent soft-transition: (a),(b): 6X to 8X Transition at Vin=25 V, No load. (c), (d) 4X to 6X Transition, Vin = 25 V, No load                                 |

| Figure 3.12: Experimental results for load independent soft-transition: (a)-(b): 6X to 8X Transition at Vin=25 V, Load =50 Ohms. (c): 4X to 6X Transition, Vin = 25 V, Load: 50 Ohms.                                         |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 4.1: Conventional Dickson type converter with a voltage step-down ratio of 4 ( $V_{in}/V_o$ ). 81                                                                                                                      |   |

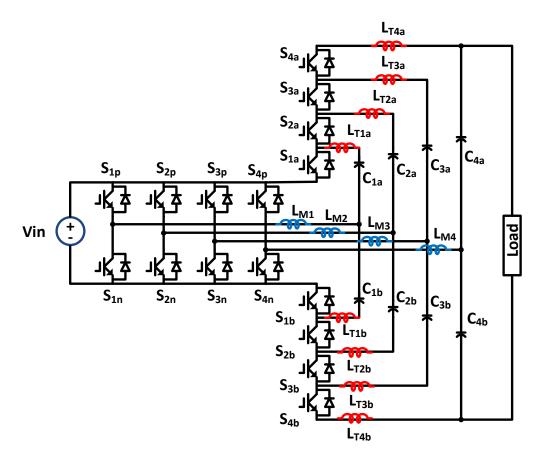

| Figure 4.2: Schematic of 280 V/28 V resonant Dickson converter                                                                                                                                                                | 1 |

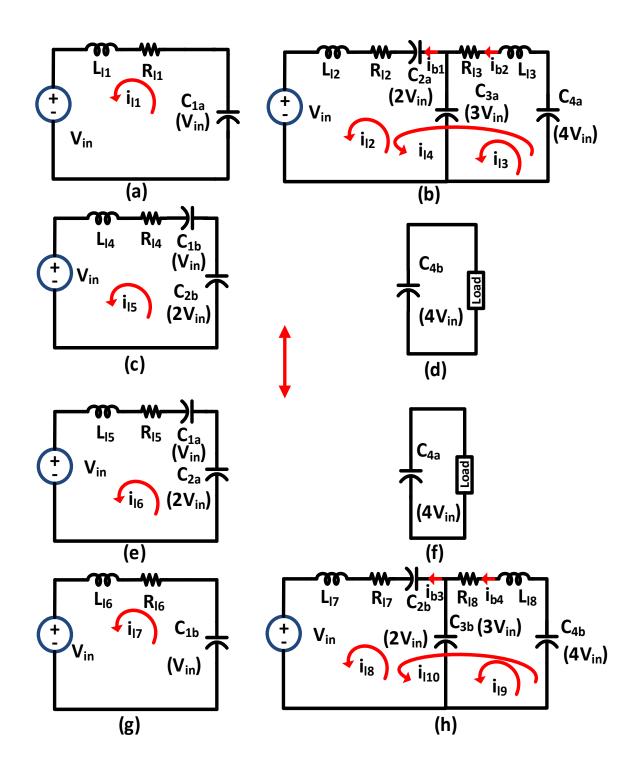

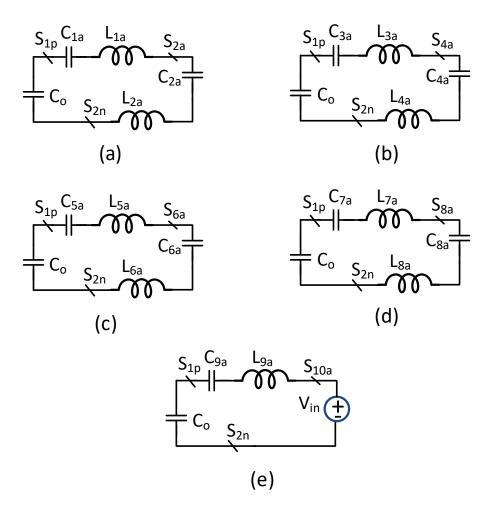

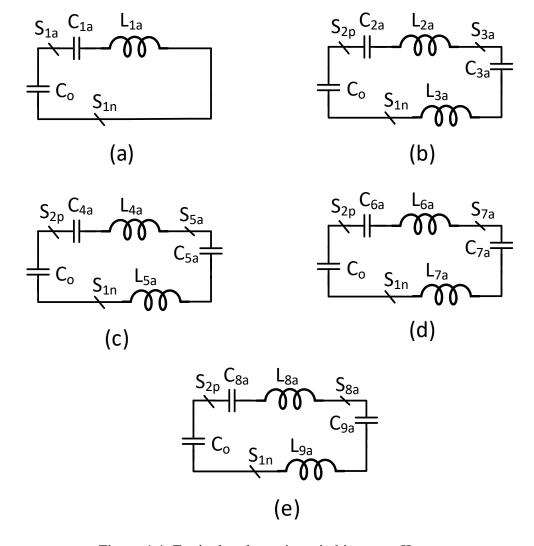

| Figure 4.3: Equivalent loops in switching state I                                                                                                                                                                             | 5 |

| Figure 4.4: Equivalent loops in switching state II                                                                                                                                                                            | 5 |

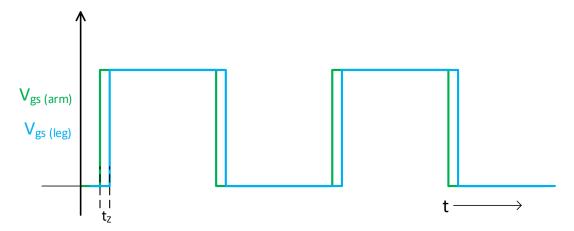

| Figure 4.5: Tuning the turn-on time of arm and leg switches to minimize switching losses in leg switches                                                                                                                      |   |

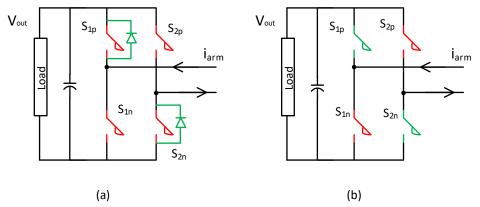

| Figure 4.6: (a) arm currents flowing through body diodes of leg switches when OFF; (b) Arm currents flowing through the leg switches when ON                                                                                  | ) |

| Figure 4.7: Estimated loss distribution for different arm switches in Table 4.1                                                                                                                                               | 3 |

| Figure 4.8: Estimated loss distribution for different 'leg' switches listed in Table 4.2                                                                                                                                      | 1 |

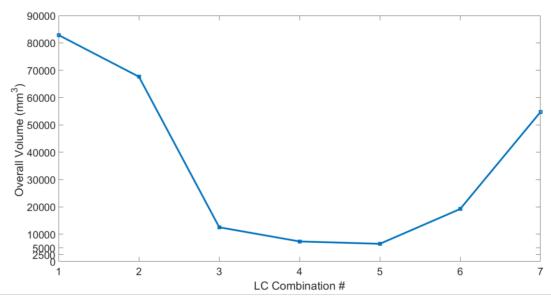

| Figure 4.9: Overall volume of LC network for seven different LC combinations based on commercially available components for a resonant frequency of 85 kHz                                                                    | 7 |

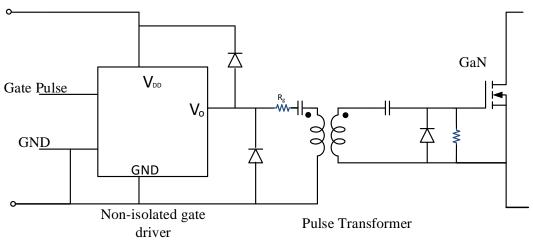

| Figure 4.10: Basic block schematic of pulse-transformer gate drive stage                                                                                                                                                      | l |

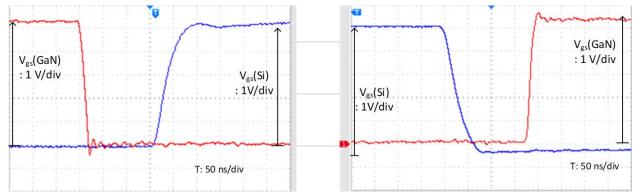

| Figure 4.11: Gate-source (Vgs) voltage of GaN (red) and Si MOSFET (blue) when driven using pulse-transformer based drive (a) falling edge of GaN and rising edge of MOSFET, (b) falling edge of MOSFET and rising edge of GaN | 3 |

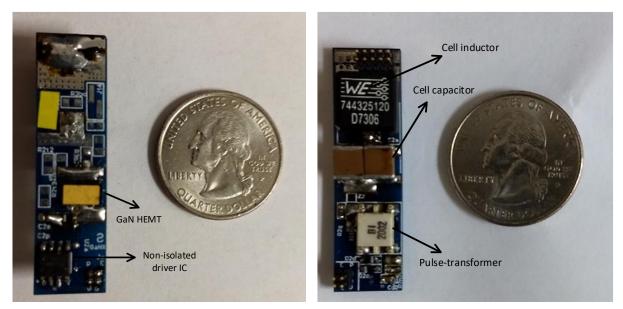

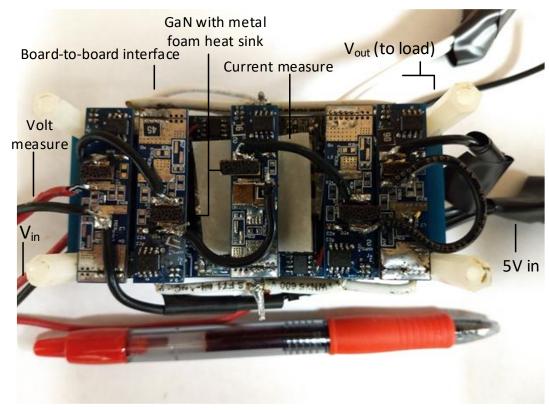

| Figure 4.12: (a) Top view of one module of the overall converter; (b) Bottom view of one module of the overall converter.                                                                                                     | 5 |

| Figure 4.13: Top view of fully assembled 280/28 V 300 W resonant Dickson prototype 106                                                                                                                                        | 5 |

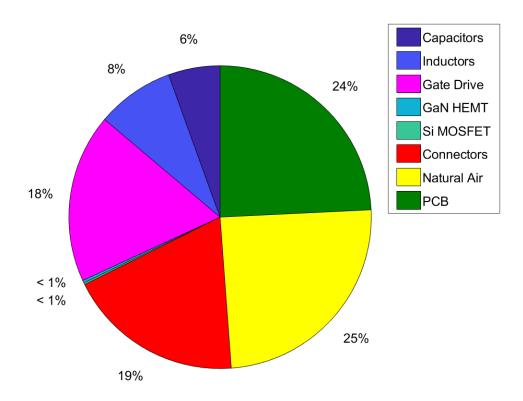

| Figure 4.14: Volume distribution of the prototype converter                                                                                                                                                                   | 7 |

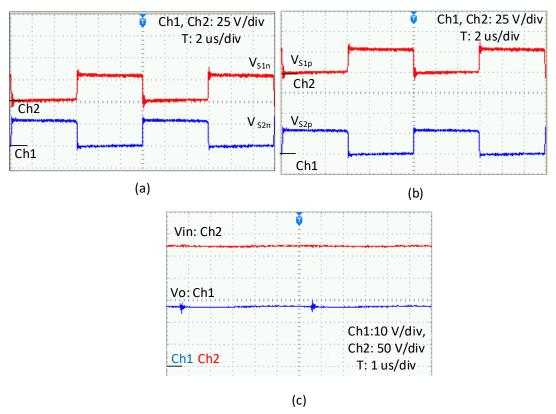

| Figure 4.15: (a), (b) Leg switch waveforms at Vin=280 V and full load; (c): Input and output voltage waveforms at rated load and input voltages                                                                               | ) |

| Figure 4.16: (a): GaN switch voltage waveform at 40% rated load. Ch1, $V_{S8}$ : 50V/div, Ch2, $V_{S7}$ : 50 V/div, Ch3, $I_7$ : 2A/div, T: 5us/div; (b): Zoomed in version of (a), 1us/div                                   |   |

| Figure 4.17: (a): GaN switch voltage waveform at 100% rated load. V <sub>S5</sub> : 50V/div, Ch2, V <sub>S4</sub> : 50 V/div, Ch3. I <sub>4</sub> : 2A/div.: T: 5us/div: (b): Zoomed in version of (a). T: 1us/div            | ) |

| Figure 4.18: (a) Current and voltage waveforms for inner-most current loop at 100% rated load.                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Ch1, V <sub>S1</sub> : 50 V/div, Ch2:-I <sub>1</sub> : 2A/div; (b) Comparison to switches outside inner-most loop, Ch1,                             |

| V <sub>S1</sub> : 50 V/div, Ch2, V <sub>S2</sub> : 50 V/div; ,T: 2us/div                                                                            |

|                                                                                                                                                     |

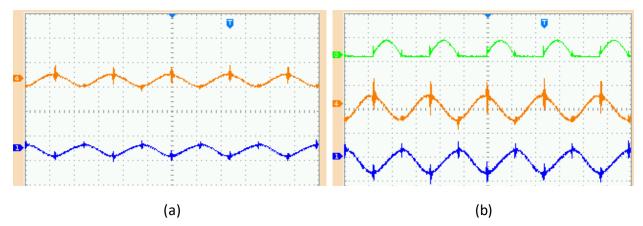

| Figure 4.19: (a) AC voltage ripple across different arm capacitors at 100% rated load. Ch1, $V_{C9}$                                                |

| 0 V/div, Ch4, V <sub>C6</sub> : 10/div; T: 5us/div (b) Ch1, V <sub>C5</sub> : 5 V/div; Ch4, V <sub>C8</sub> : 5 V/div, Ch3: I <sub>6</sub> : 5A/div |

| T: 5us/div                                                                                                                                          |

|                                                                                                                                                     |

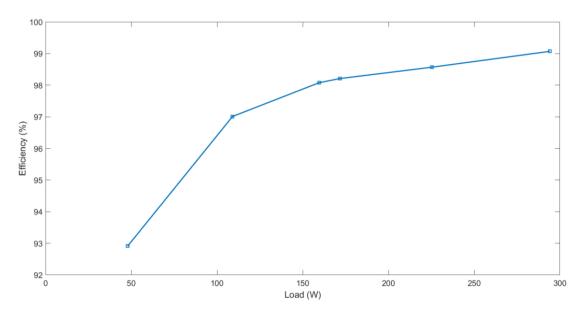

| Figure 4.20: Efficiency plots for the 280 V/28 V resonant Dickson Converter                                                                         |

#### **CHAPTER 1** INTRODUCTION

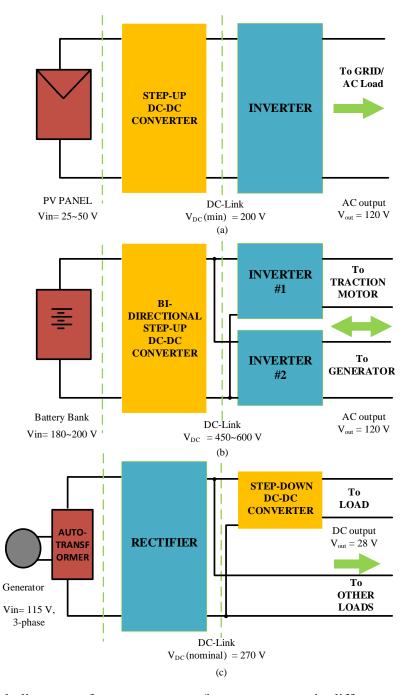

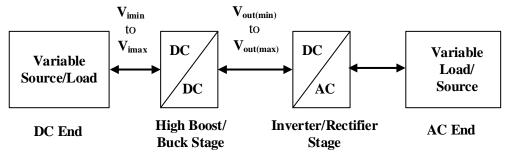

A power converter/inverter system (PCIS) is a key part of several different power electronics systems. Figure 1.1 illustrates the PCIS present in three key applications. In Figure 1.1 (a), the case of a residential solar photovoltaic (PV) power system is illustrated. In this configuration, the varying DC output voltage output of a solar panel, V<sub>in</sub> is converted to a nominal DC-link voltage of 200 V. The subsequent inverter stage produces the required AC voltage, V<sub>out</sub> (typically 120 V) to deliver power to standalone loads or the utility. Such implementations are commercially known as "PV micro-inverter" and are being widely installed in residential solar rooftops around the world [1]. String inverters that use a centralized inverter to interface to the grid also use require a DC-DC converter to interface to the utility or load.

Figure 1.1 (b) illustrates the case of a commercial hybrid electric/ electric vehicle power train [2]-[4]. Here, output voltage from the High-voltage (HV) battery pack, V<sub>in</sub> (typically about 200 V) is converted to a DC link voltage, V<sub>DC</sub> of 450 to 600 V using the step-up DC-DC converter. The subsequent inverter stages provide the required AC voltage for driving the traction motor and/or additional motor/generator unit. The HV battery pack is also charged by means of the generator feeding power through the inverter and step-up converter back to the battery pack. Hence, a bidirectional step-up DC-DC converter is needed for this application.

Figure 1.1 (c) illustrates part of the power system within a commercial more-electric-aircraft (MEA) [5]. Here, voltage output from the generator,  $V_{in}$  (typically 115 V) is converted to a DC link voltage,  $V_{DC}$  of 270 V using the rectifier. The 270 V DC-link voltage is converted to 28 V

using a step-down DC-DC converter to generate the required 28 V power supply in the aircraft.

The 270 V power supply required in the aircraft is directly derived from the DC-link voltage.

Figure 1.1: Block diagrams of power converter/inverter systems in different applications: (a): Residential solar PV system, (b): Hybrid/Electric Vehicle (HEV/EV) powertrain, (c): More Electric-aircraft (MEA) power system.

From the illustrations in these figures, it is clear that the role of the DC-DC converter is crucial for the operation of the overall PCIS. The ideal specifications of a DC-DC converter used in these cases can be generalized as follows:

- 1. High power density: Weight and size of the power converter translates to system cost in most cases. This is of added importance in case of airborne and automotive applications.

- 2. High efficiency: A more efficient system implies lesser auxiliary cooling systems leading to reduction in weight and hence cost.

- 3. Capable of large voltage gains: A gain of 8 required in case of residential PV systems, A gain of 10 required in a MEA.

- 4. Capable of bidirectional operation: To facilitate battery charging in the case of HEV powertrains.

- 5. Capable of operation at high temperature: In the case of a PV application, the entire unit is mounted outdoors, below the PV panel. In the case of EV and MEAs, the internal powertrain temperature is also much higher than the regular ambient temperature.

Existing high-gain DC-DC converters can be broadly classified into two different technologies depending on the type of power transfer involved in the converter. The benefits and limitations of each of these technologies are listed below:

#### 1.1 Centralized magnetics-based DC-DC converters

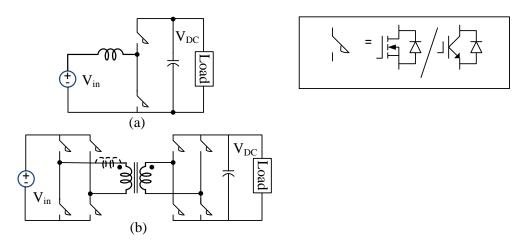

Figure 1.2 illustrates the basic power circuit of two key types of bidirectional centralized magnetics-based DC-DC converters. The semiconductor switches used in these circuits are

represented by means of generic switches. This convention is followed throughout this dissertation.

The two-switch bidirectional boost/buck converter in

Figure 1.2 (a) is suitable for gains in the range of 1 to 3. However, at higher gains, the efficiency of the converter reduces [6]. Additionally, perhaps more importantly, the overall voltage and current stress of the devices increase as the gain increases. In view of these, these converters are limited to voltage gains below 3 in a practical system. A centralized inductor designed to carry the highest current of the converter is indispensable to this converter structure. The size and packaging constraints of the central inductor limits the overall power density (W/in³) of the converter. In most cases, the required inductance is realized by using a magnetic core. However, the permeability of these materials reduces at higher temperatures leading to potential problems in control and operation of the converter.

Figure 1.2: Two types of magnetics-based DC-DC converters, (a): Two-switch bidirectional boost/buck converter, (b): Bidirectional Full-bridge DC-DC converter.

A generic structure of the bridge converter and its variants is illustrated in

Figure 1.2 (b). They are widely used in cases of high gains where the usage of a two-switch converter illustrated in

Figure 1.2 (a) is no longer practical. In this case, the converter essentially uses three power stages. In the first stage, the input DC voltage is converted to a high-frequency AC voltage across the transformer input terminals. In the next stage, this high frequency voltage is transferred to the secondary side or the output terminals of the transformer. In the final stage, the high-frequency AC voltage is rectified to provide a DC output voltage to the load. By designing the high-frequency transformer suitably, a large voltage gain can be obtained without significantly compromising the efficiency of the converter. However, the overall efficiency of the converter is now a function of the product of the individual power stages. Assuming a hypothetical 99% efficiency each for the input inverter stage, the transformer stage and the output rectifier stage leads to a system efficiency of about 97%. The voltage rating of the switches on the load side of the transformer has to be designed for the output voltage. On similar lines, the current rating of the switches on the input side of the converter has to be designed for the input current.

### 1.2 Switched Capacitor based DC-DC converters (SCCs)

Traditionally, switched-capacitor based DC-DC converter technology (also known as charge-pump) was used in low-voltage, low-power applications where the requirement for high efficiency was not a major concern [7]. Several different types of switched capacitor converters exist in literature [8]. However, one particular type, "Dickson converter" [9] offers numerous advantages for implementation at higher power levels and large voltage gains suitable for modern day PCIS. The key difference between the general structure of the centralized magnetics-based converters and the switched capacitor type converters lie in the overall energy storage and power transfer schemes. Switched capacitor converters use an entirely distributed approach in terms of storing energy. There is no single bulk energy storage capacitor or inductor. This leads to the ability to

have multiple power transfer loops occurring in parallel thereby avoiding the requirement for a three-stage cascaded power conversion scheme. This leads to high efficiency and low device stress (voltage and current rating of individual switches). The number of devices conducting the input current at any given time is also fixed irrespective of the voltage gain. This makes it suitable for a high efficiency, high power density converters.

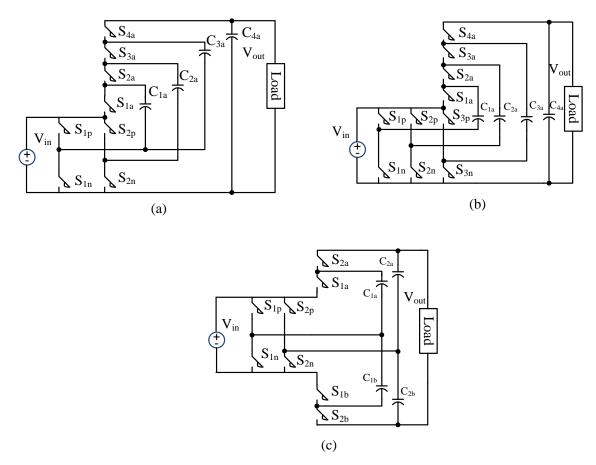

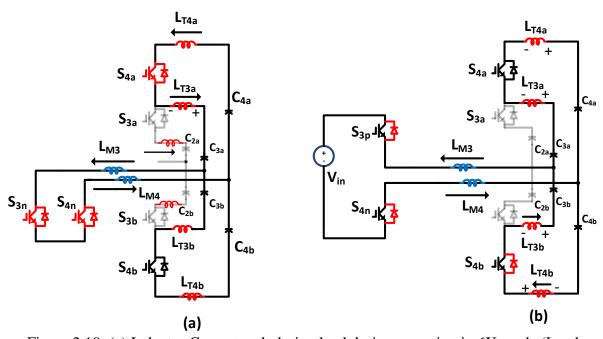

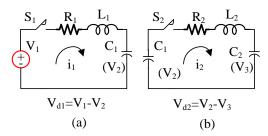

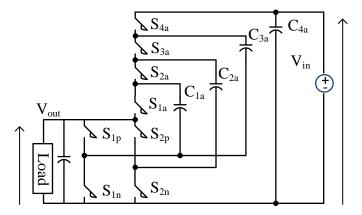

Since then, two other variants of the Dickson converter for a PCIS have been proposed. The three variants of the Dickson converter configured for a gain of 4 are illustrated in Figure 1.3. In all these variants, the switches clamped by the input voltage, V<sub>in</sub> are termed as "leg switches", the remaining switches are termed as "arm switches". The leg switches are labeled with subscripts p and n. The arm switches are labeled with subscripts a and b. This notation is followed throughout this dissertation.

The "original" Dickson converter proposed in [9] is illustrated in Figure 1.3 (a). Here, the converter is configured to have a gain of 4. The voltages across individual arm capacitors are  $V_{in}$ ,  $2V_{in}$ ,  $3V_{in}$  and  $4V_{in}$  respectively. The total number of switches and capacitors along peak voltage and average current ratings of individual switches are summarized in Table 1.1. From the table, it can be seen that the number of leg switches are fixed as 4 irrespective of the voltage gain. This leads to an average current rating of  $N*I_0$  for the 'leg' switches, where 'N' is the gain of the converter. The average current,  $I_0$  for the arm switches arises from an average current of  $2I_0$  during one half-cycle and 0 during the other in a switching period.

The MMCCC converter illustrated in Figure 1.3 (b) [10] essentially modularizes the leg switches in the original Dickson type converter. This leads to all the leg switches having identical current

ratings. While, the converter switch ratings are modular in nature, the number of capacitors and the voltage across individual capacitors remains the same.

The NX converter [11] illustrated in Figure 1.3 (c) reduces the voltage ratings of individual capacitors by essentially interleaving the arms of two Dickson type converters. However, the current ratings of the leg switches are doubled compared to the MMCCC type converter. Also, due to the interleaving nature, the output voltage ripple is minimized. This configuration leads to a compact and modularized configuration compared to the other two types.

| Dickson<br>Type | Arm Switches (a,b)    |               |                      | 'Leg' Switches |                 |                 | Capacito -rs                        | Total<br>Capacito | Total<br>Switc |

|-----------------|-----------------------|---------------|----------------------|----------------|-----------------|-----------------|-------------------------------------|-------------------|----------------|

|                 | No.of<br>switc<br>hes | Avg.<br>Curre | Peak<br>Volta-<br>ge | Numb<br>-er    | Curre<br>-nt    | Volta-<br>ge    | Voltage<br>Range                    | -rs               | -hes           |

| Original        | N-2                   | Io            | 2V <sub>in</sub>     | 4              | (N/2)I          | V <sub>in</sub> | V <sub>in</sub> to NV <sub>in</sub> | N                 | N+4            |

|                 | 2                     | $I_{o}$       | $V_{in}$             | -              | -               | -               | -                                   | -                 | -              |

| MMCCC           | N-2                   | $I_{o}$       | $2V_{in}$            | 2N-2           | $I_{o}$         | $V_{in}$        | $V_{in}$ to $NV_{in}$               | N                 | 3N-2           |

|                 | 2                     | $I_{o}$       | $V_{in}$             | -              | -               | -               | -                                   | -                 | -              |

| NX              | N-2                   | $I_{o}$       | $2V_{in}$            | N              | 2I <sub>o</sub> | $V_{in}$        | $V_{in}$ to $2V_{in}$               | N                 | 2N             |

|                 | 2                     | $I_{o}$       | $V_{in}$             | -              | -               | -               | -                                   | -                 | -              |

Table 1.1: Summary of switch and capacitor ratings in Dickson type converters.

Figure 1.3: The three variants of Dickson converter: (a) The original Dickson converter[8], (b): Modular Multi-level Clamped Capacitor converter (MMCCC[10]), (c): NX converter[11].

#### 1.3 The need for voltage regulation in Dickson type converters

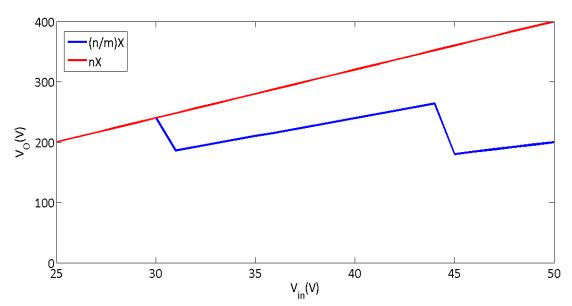

While the Dickson type converters have several advantages (as described above), they have some major limitations. First, the gain of the converter is fixed by design. Continuous voltage regulation is theoretically not possible without compromising the high efficiency of the converter. This essentially means that the downstream inverter in a PCIS has to be rated for the maximum output voltage of the DC-DC converter. For instance, in the PV case described in Figure 1.1(a), if the DC-DC stage is designed for a fixed gain of 8, the voltage rating of the switches has to be rated for 400 V. This is an over-design for generating the required 170 V at the AC terminals of the inverter. This leads to a larger size of the overall system.

Next, the Dickson type converters are only capable of achieving integer voltage gains. This is a major limitation in applications that need fractional voltage gains. In order to provide voltage regulation capability to the Dickson type converters, a few different methods are proposed in literature. These methods are reviewed here.

In [12], one method to achieve variable gains using the MMCCC variant of the Dickson converter is proposed. Here, individual MMCCC cells are cascaded by means of additional switches. By controlling the switching state of these additional switches, individual cells can either be bypassed or inserted into the path of power flow from the input to output. So, this method essentially uses multiple cascaded cells to achieve variable gains. This leads to large number of switches conducting the input current and leads to lower efficiency. This negates one of the key advantages of the Dickson type converter. The increased switch count further increases the overall cost and size of the system.

Yet another method to achieve a variable gain for the Dickson converter is proposed in [13]. Here, by introducing additional inductors and selecting the appropriate phase relationship between the two operating states of the converter, a fractional variation in gain can be achieved. By combining this gain variation with the method proposed in [12], a larger/finer regulation in gain is proposed. However, the maximum gain variation is a function of the load and the degree of gain variation is limited at lower loads. Also, the current ratings of individual devices are expected to be higher when the phase relationship between the operating states deviates from 50%. A peak efficiency of about 90% is reported for such a configuration. An identical method has also been proposed in [14], where the phase relationship between the two operating states is varied to achieve a continuous output voltage variation. In this case, the current rating of the individual switches increases drastically, and the system is no longer practical.

Yet another method to achieve variable output gains using the Dickson type converter has been proposed in [15]. Here, an additional switch/voltage divider network is provided to vary the input voltage provided to the switched capacitor network. This leads to increase in overall size of the converter and increased current stress for the input voltage source. In case of input voltage derived from large battery packs (such as EVs), this may also lead to charge unbalance between different cells of the battery. Fractional gains can be achieved by tapping into a fractional input voltage.

Other methods to achieve a variable and fractional gain for the Dickson type converters include the usage of an external/integrated downstream buck converter to provide the necessary voltage regulation and fractional gain [16]-[19]. However, for the purpose of this dissertation, this is considered as an external stage not part of the switched capacitor power stage.

Several other articles in literature discuss methods to achieve a variable output voltage using switched capacitor converters. However, they can all be classified into the above described types.

In order to advance the switched capacitor technology, especially for the Dickson type converters, there is a need to investigate methods to achieve variable and fractional output voltage without compromising on efficiency or adding large external magnetic components.

## 1.4 Ultra-high efficiency and power density SCC s for large voltage gains/step-down ratio

In order to achieve ultra-high efficiencies (over 98%) using SCCs, there is a need to minimize the overall losses in the system. In theory, operating SCCs with a minimum capacitor voltage ripple across individual capacitors [8] leads to improved efficiency. However, at a system level this

translates to increased switching frequencies for the individual switches. This can lead to increased switching losses for individual switches that can offset the benefits of operating at a lower capacitor voltage ripple. In order to overcome this limitation, resonant zero-current switched capacitor circuits and topologies have been investigated [20]-[24] overcome losses in each switched capacitor cell. While one part of switching losses can be eliminated by zero-current switching, the losses due to charging and discharging of the switch parasitic output capacitor, Coss and the input capacitor, Ciss is not influenced by this scheme.

The power semiconductor device space has truly evolved in the past decade. Gallium Nitride (GaN) power semiconductor device technology is mature and is commercially available at a viable price point to reap its benefits. These devices have extremely good figure of merit (FOM) numbers when compared to their Silicon counterparts. This has considerably changed the landscape of power electronics systems and is continuing to evolve [25]. The voltage ratings of GaN switches along with its small footprint and much improved Coss and Ciss parameters makes it a suitable candidate for switched capacitor type applications. It enables further improvement in efficiency and system power density. A few GaN based SCC topologies have been investigated for a 4:1 voltage step down ratio [26]-[28]. But, several applications require a much higher voltage step-down ratio (as discussed in the beginning of this section). As the required step-down ratio increases, the number of switches and capacitors in each arm of the converter increases. Increased component count is a potential concern for power density and efficiency. As majority of these switches are floating, efficient gate drive stage for each of these switches is another bottleneck. Thorough investigation on a suitable topology and system design optimization techniques for high-

gain resonant SCCs can go a long way in achieving high efficiency, high-power density SCC systems for a variety of applications discussed before.

#### 1.5 Theses and their potential impact in power electronics systems

Thesis 1: Real-time voltage regulation and fractional voltage gains in Dickson type switched capacitor DC-DC converter is achievable by means of controlled intermediate operating states in an otherwise constant operating state trajectory. Doing so does not impact steady-state efficiency of the converter or the sizing of passive components in the system.

**Impact:** For a PV micro-inverter system, this provides the unique opportunity to achieve real-time gain variation in a switched capacitor-based DC-DC converter stage. The overall voltage stress of the downstream inverter stage is reduced by over 30% (in comparison to traditional SCC) resulting in improved efficiency and reduced system cost. The dynamic response time of the overall system is also improved as the inverter DC link voltage is now well regulated. The ability to provide fractional voltage gains also enables optimal system design and unlocks newer applications that aren't possible with an integer voltage gain in the DC-DC stage.

Thesis 2: An improved voltage regulation method for Dickson type DC-DC converter that minimizes or eliminates large input current transients is achievable by utilizing the load and adjacent switched capacitor cells to re-distribute the energy in the switched capacitor network during gain transition.

**Impact:** Further improves usability of the Dickson type SCCs in applications that have tighter constraints in the transient/in rush current requirements. A typical example is that of an xEV

powertrain where there are tighter requirements for current transients drawn from batteries during normal operation.

Thesis 3: A resonant Dickson converter configuration that uses GaN switches, distributed inductive and capacitive elements in individual power transfer stages, combined with an integrated efficient gate drive and system-level loss optimization can result in an ultra-high efficiency (>99+%) and high power-density (~100 W/in³) DC-DC converter suitable for high voltage step-down ratios (>8).

Impact: So far, GaN based resonant Dickson converters have only been adopted for the power stage in low step-down ratio applications such as data-center power supplies (4:1 ratio). At higher step-down ratios, the increased number of switches and capacitor cells constrains the efficiency and power density of the system. By means of the configuration and system optimization techniques proposed here, ultra-high efficiency and power densities at high-gains (>8) are made possible. This leads to improved efficiency and power density in applications such as more-electric aircrafts that require a 270 V to 28 V step down at a high efficiency and power density.

#### 1.6 Structure and Scope of the dissertation

Chapter 2 is aimed at addressing Thesis 1. The need for voltage regulation and fractional voltage gains in switched capacitor converters is first introduced and the configuration of the converter termed as variable (n/m)X converter is introduced. New operating states for the (n/m)X converter are then proposed to achieve dynamic variation in gain. The proposed operating states utilize all the trace/stray inductance in the converter to achieve mode transition. No external magnetic

components are necessary. Detailed transient analysis and design methodology for a A 1-kW (n/m)X converter prototype suitable for a PV application along with the control blocks are presented. An example case is demonstrated to illustrate reduction in overall voltage stress of a PV PCIS by 33%. A peak efficiency of 96% is achieved for a Si based prototype. Experimental results obtained for the prototype validate the proposed theory.

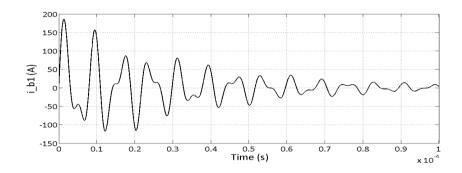

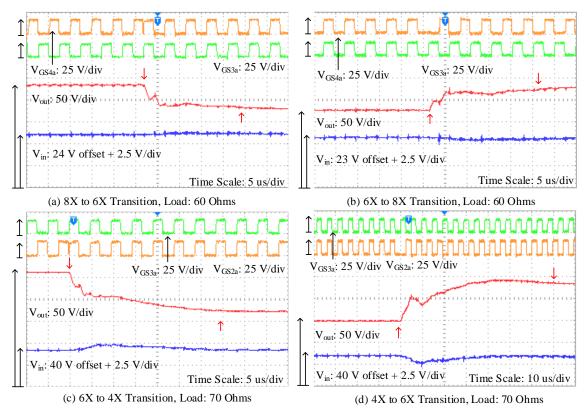

Chapter 3 is aimed at addressing Thesis 2. Improved gain transition methods for the (n/m)X converter are proposed. Here, the concept of soft-transition in gain is first introduced. Next, two different control methods to achieve a variation in gain with reduced input current transient are proposed. Using the proposed method, the input current transient is limited to within 150% of the peak load input current. Experimental results on a 1 kW prototype is then presented to validate the proposed theory.

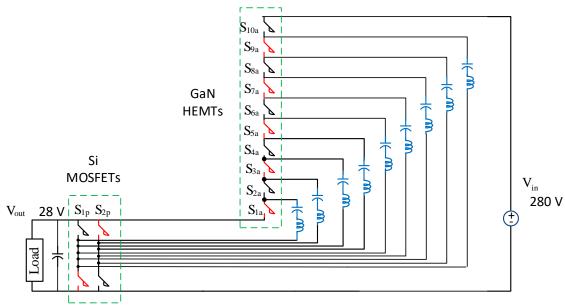

Chapter 4 is aimed at addressing Thesis 3. A GaN HEMT based resonant Dickson converter configuration is proposed that achieves ultra-high efficiency and power densities for high voltage step-down ratios (>8). System level loss optimization, efficient gate drive and optimization of passive component design form the key aspects of the chapter. The power stage of a 270 V/28 V (nominal gain of 10) converter in a more-electric aircraft (MEA) forms a good use case for the proposed converter. To this effect, a 300 W converter prototype is designed for this specification. A peak efficiency of 99.1% and a power density of 87 W/in<sup>3</sup> is achieved using this prototype. Every aspect of the converter design revolves around utilizing and extracting key benefits of GaN HEMTs for this application. The configuration and design methodology introduced here can be extended to other GaN based high gain (or step-down ratio) applications.

Chapter 5 provides concluding remarks and possible avenues for future research based on this dissertation.

## CHAPTER 2 VARIABLE (N/M)X SWITCHED CAPACITOR DC –DC CONVERTER

#### 2.1 Introduction

High voltage-gain bidirectional DC-DC converters play a major part in solar photovoltaic (PV) and electric vehicle (EV) applications. In the case of EV applications, a bidirectional high boost converter is used to interface power between the motor and generator units (in case of a power split based EV) and the battery bank as in [29]-[31]. In the case of solar PV module connected to the power grid or a standalone AC load, a high boost converter is essential to convert the varying input DC voltage (typically 1:2) to a fixed output DC voltage. This output DC voltage serves as the DC link voltage for the power inverter stage as in [30],[31]. For both these applications, a conventional boost converter (two-switches for bidirectional capability) is the preferred choice when the boost ratio is not too high. An isolated DC-DC converter is typically used when the boost ratio is high. While both these forms of boost converters can work reliably, both of them require bulky magnetic components. This reduces the power density of such converters. Additionally, the permeability of these magnetic components varies with change in temperature. This can lead to decrease in inductance with increasing temperature. This is a major bottleneck for both control and reliability at high temperatures. Depending on the magnitude of the required voltage gains, the switches also undergo high stress levels. The need to reduce inductance, achieve high power density and high efficiency output in DC-DC converters has seen an interesting development over the years. DC-DC converters based on multi-level converters (MLCs) have been known to increase power density [33]-[38]. In the flying capacitor structure in [32],[35], [36] and [37] the number of switches conducting the input current increases with increase in gain. Thus, at higher gain levels, this would lead to a larger voltage drop leading to low efficiency [38]. The Dickson converter introduced in [9] uses a switched capacitor circuit with no external magnetic components to

alleviate this problem by ensuring that only a minimum number of switches conduct current in any given path. The other benefits and limitations of switched capacitor-based circuits when used in power converters have been discussed in [17], [39] and [40]. But, it is established that Dickson based circuits offer superior performance in terms of modularity and scalability compared to other switched capacitor [8] configurations. More recently, a multilevel modular capacitor-clamped converter (MMCCC) circuit based on the Dickson converter has been proposed [10]. The circuit offers numerous advantages such as low device current conduction and the ability to eliminate external inductors. For any given current path, only a maximum of three devices conduct. This leads to high efficiency and makes the circuit suitable for high voltage gains. Also, the control mechanism for this circuit is extremely simple. However, the circuit has a total of 3N-2 switches for a given 'NX' conversion ratio. This circuit has been improved upon by [11], where a double wing structure is proposed in order to further reduce the current ripple in the output capacitors. The voltage ratings of individual capacitors have also been reduced significantly. The number of devices have also been brought down from 3N-2 to 2N leading to a reduction in overall device count. Additional embodiments such as multi-phase structure and soft-switching have been proposed in [23], [41]. The optimal design procedure for the double wing based switched capacitor circuit has been presented in [42]. In [43], a compact, high power density "NX converter" has been designed based on the double wing structure proposed in [11], [23] and [41]. The circuit uses a modular design for the entire power converter based on equal capacitances and trace inductances for every stage. But, the nX converter in [43] has just one operating point, where the output voltage is a fixed integer multiple of the input voltage. It is severely limited by its inability to provide dynamically varying voltage gains and fractional voltage gains. In [12], [13]embodiments of the "variable gain" MMCCC have been proposed. But, the design in [12] involves modification to the

basic cell and the cascading of several cells. This leads to a much higher switch count and lower efficiency due to multiple cascaded cells. In [13], the achievable maximum voltage gain is a function of the load, which limits its application. In [16], [45], variable voltage gains are achieved using cascaded switched capacitor cells. In [46], a binary and Fibonacci based switched capacitor circuit have been combined to provide variable voltage gains. In [15] and [47], fractional voltage gains using a ladder based switched capacitor converter and a Dickson based converter are achieved by using multiple tappings. But, in order to vary the gain during regular operation, an additional switch network is necessary. Although, in theory or for low power implementations, these circuits are capable of variable and fractional voltage gains, they are not used for over 100 W. Based on the limitations of existing switched capacitor-based circuits, there is a need for a power converter based on a switched capacitor circuit that can provide variable and fractional voltage gains at high efficiencies at higher power levels (close to 1 kW or more). The aim of this chapter is to propose a circuit configuration and its control method to achieve these functionalities using a generalized configuration of a Dickson based switched capacitor converter. The proposed converter is termed, (n/m)X converter owing to its ability to provide a variable fractional gain, n/m. The (n/m)X converter can be designed to achieve fractional gains that can be varied in discrete steps during regular operation of the converter. In order to achieve higher efficiency and high power density in the proposed circuit, cascading of multiple cells or additional switches are not used. Instead, new degrees of freedom within a switched capacitor cell are exploited to achieve the target. While, the proposed converter cannot offer continuous voltage regulation, the voltage gain can be varied in discrete steps. By suitably designing the converter for a set of variable voltage gains, the device voltage stress of the inverter in a converter/inverter system can be reduced significantly (over 33% in an example case disclosed in this chapter). Comparison with existing

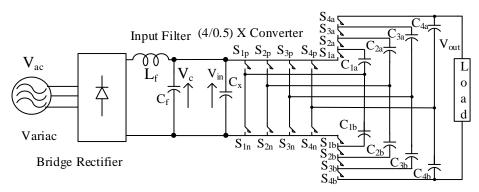

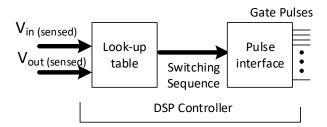

two-stage/integrated converters as in [18], [55]in terms of voltage regulation is avoided in this chapter as the proposed converter is not considered a replacement for such a system. The proposed converter has the potential to be used as the front end in any such two-stage or integrated converter systems to further improve voltage regulation with lower device voltage stress. Such an embodiment is beyond the scope of this chapter. Analysis of the different operating stages, description of multiple control methods, design procedure for an example converter/inverter system, efficiency analysis and experimental results for a 1kW prototype of a (4/0.5) X converter form the main crux of this chapter. An efficiency of over 95% is achieved using the converter when the gain is allowed to vary every 100 ms.

The rest of this chapter is organized as follows: Section 2.2 derives the structure of the (n/m)X converter from a generic (k/m) X structure. The various degrees of freedom present in the circuit are explored in this section. Sections 2.3 and 2.4 describe two methods to dynamically vary the gain of the (n/m)X converter (termed as "mode-change" throughout this chapter), one using assistance from the load and the other independent of the load. Various operating stages (during transition and steady state) encountered in both these methods are clearly described. Section 2.5 describes the equivalent circuits for every mode transition. Sections 0 describes the method to calculate the worst-case transient over-voltage. In section 2.7, the design procedure and specifications for a 1kW prototype of (4/0.5)X converter have been presented. Section 2.8 provides experimental results to demonstrate both, fractional voltage gains and variable voltage gains. Section 2.9 presents the efficiency curves obtained experimentally for the (4/0.5)X converter while in different operating states and during dynamic mode-change.

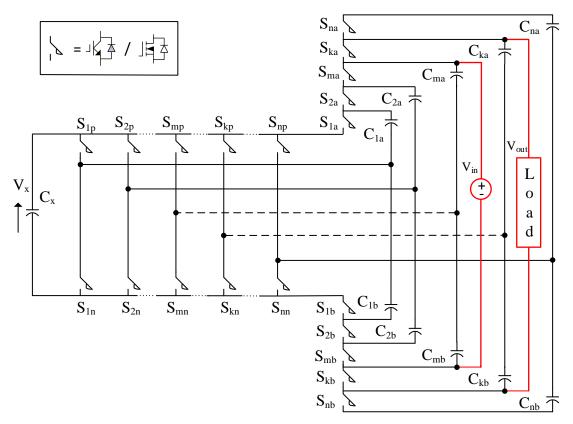

#### 2.2 The (N/M)X Converter: General Configuration

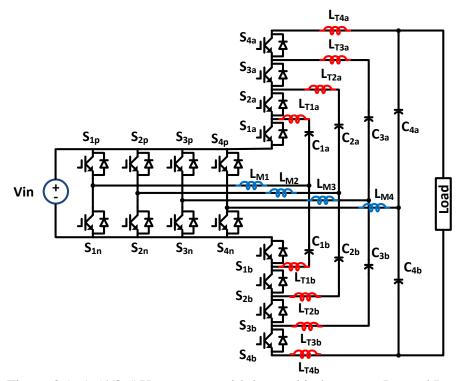

The (n/m)X converter is derived from a more generic (k/m)X structure. This section describes the generalized structure of the (k/m)X converter and proceeds to explain the (n/m)X converter. The basic configuration is illustrated in Figure 2.1. It can be seen that the proposed converter has 'n' different arms and 'n' different legs leading to a total of '2n' limbs. Each arm comprises of a series connection of two capacitors and two arm switches labeled with suffixes 'a' and 'b'.

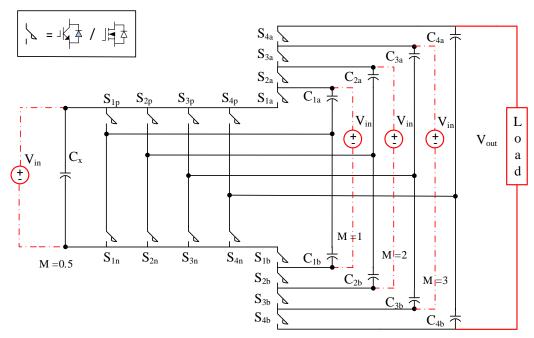

Figure 2.1: A generic (k/m)X converter.

For example, arm no. 1 comprises of capacitors  $C_{1a}$  and  $C_{1b}$  connected in series with switches  $S_{1a}$  and  $S_{1b}$ , arm 'm' comprises of capacitors  $C_{ma}$  and  $C_{mb}$  connected in series and so on. Each leg of the converter consists of a half-bridge cell with two switches switched in a complementary manner. Leg 1 consists of switches  $S_{1p}$  and  $S_{1n}$ , Leg 2 consists of switches  $S_{2p}$  and  $S_{2n}$  and so on. For the double wing structure proposed in [11], the relationship between input voltage and the voltage

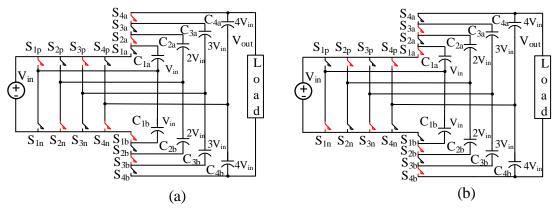

across individual capacitors has already been established. Figure 2.2 illustrates this relationship along with the two operating states to achieve a gain of 8. Switches marked in red indicate switches that are ON and those marked in black indicate switches that are OFF.

Figure 2.2: Operating states of an 8X converter.

In comparison to the structure of double wing nX converter in Figure 2.2, it can be observed that extra degrees of freedom with respect to the location of input voltage and load are introduced in the proposed structure. The input voltage  $V_{in}$  can now be connected across the capacitors of any of the 'n' arms of the converter. Similarly, the load (output voltage) can also be connected across the capacitors of any of the 'n' arms of the converter. Hereafter, the connection across the capacitors of an arm are simply referred to as connection across the corresponding arm. For a generic location of the input voltage,  $V_{in}$  across the m<sup>th</sup> arm of the converter, the "effective input" voltage,  $V_{X}$  across  $C_{X}$  can be expressed as,

$$V_{\chi} = \frac{1}{m} * \frac{V_{in}}{2} \tag{2.1}$$

Based on the voltage buildup across individual arm capacitors (Figure 2.2) in a double wing structure, for a generic location of the load across arm k, output voltage  $V_{out}$  can then be expressed as,

$$V_{out} = 2k * V_x = \frac{k}{m} * V_{in}$$

(2.2)

Where, 'm' is the arm (capacitors of the arm) across which the input voltage is connected, k is the arm across which the load is connected and k,  $m \le n$ . The converter is fully bidirectional. The relative magnitudes of k and m determine if the converter functions as a boost or buck converter. If k < m, the converter functions as a buck converter. On the other hand, if k > m,  $V_{out} > V_{in}$  and the converter functions as a boost converter. From Figure 2.1, it can also be seen that, another degree of freedom can be obtained by connecting the source/load across the converter leg. This is achieved by placing the source or load across  $C_X$ . If the input voltage,  $V_{in}$  is placed across  $C_X$  and the load is connected across the generic arm, 'k' as described above, the output voltage,

$$V_{out} = \frac{k}{1/2} V_{in} = 2k * V_{in}. \tag{2.3}$$

Comparing equations (2.2) and (2.3), it can be seen that for the input voltage being placed across,  $C_X$ , this presents a case of m=(1/2) for the generic (n/m)X converter. Similarly, if the load is placed across  $C_X$  (for buck functionality) and the input voltage is placed across the m<sup>th</sup> arm as described before, the output voltage  $V_{out}$  can now be described as,

$$V_{\text{out}} = \frac{\frac{1}{2}}{m} V_{\text{in}} = \frac{1}{k} * \frac{V_{\text{in}}}{2}$$

(2.4)

Comparing equations (2.2) and (2.4), it can be seen that placing the load across  $C_X$  presents a special case of the generic (k/m)X converter where, k=1/2. The acceptable values of k and m can now be listed as below,

$$k = \frac{1}{2} \text{ or } k = 1,2 \dots n.$$

(2.5)

On similar lines,

$$m = \frac{1}{2} \text{ or } m = 1, 2, \dots, n.$$

(2.6)

The double wing based nX converter developed in [11] now becomes a special case of the (k/m)X converter. The 8X converter developed in [43] can be represented as a fixed (4/0.5)X converter. The boost nX converter is obtained using k=n and m=1/2. The buck nX converter is obtained by using k=1/2 and m=n. For a given application, say the required ratio of output to input voltage (gain) is 1/4. Based on the discussion above, several sets of (m,k) values can provide the required gain (k/m) of 1/4. For instance, (2,1/2); (4,1) and (8,2) are all valid solutions. But, in order to provide the required gain with the minimum number of semiconductor devices, 'k' has to be minimized. Thus, for this case, (m,k) of (2,1/2) has the lowest overall device count. The overall system would only contain 2 arms. This implies 4 capacitors and each arm would necessitate four semiconductor switches leading to a total of 8. Hence, the design for a fixed output voltage gain is driven by the need to minimize 'k'. For a given boost converter configuration, the highest output voltage, V<sub>out</sub> for a given input voltage, V<sub>in</sub> can be achieved with k=n. Thus, k=n and m=1/2 provides the maximum possible gain. On the other hand, for a buck configuration, m=n and k=1/2 provides the minimum possible gain. Thus, the bounds for the maximum and minimum converter gains are determined by k=n and m=n respectively. This means that the (k/m)X converter functions as an (n/m)X boost converter or (k/n)X buck converter within the realms of the maximum and minimum output voltage requirements. The ability to vary the value of 'm' by varying the location of input voltage, V<sub>in</sub> in a (n/m)X configuration is shown in Figure 2.3. Using this method, fractional voltage gain can be achieved. The location of the input voltage now becomes a design parameter and is fixed based on the required voltage gain. The location of input voltage cannot be varied during operation. Experimental results illustrating the different fractional gains using a variable (4/(1/2))X or (4/0.5)X converter are presented in Section 2.7. The various possible gains achievable by varying m from  $\frac{1}{2}$  to 4 are, (4/1), (4/2), (4/3) and (4/4) respectively.

Figure 2.3: A (4/0.5)X converter with different locations of input voltage.

### 2.3 Gain Variation using the (n/m)X converter

As this method is independent of the type and magnitude of load, it is termed as "load independent" mode change.

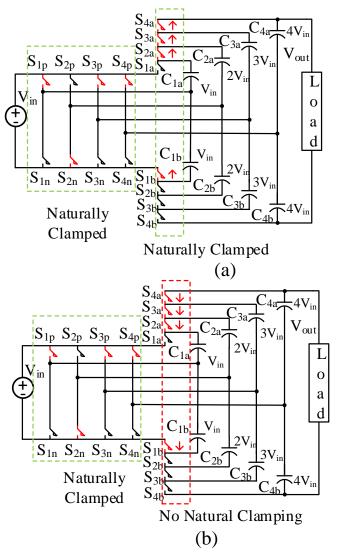

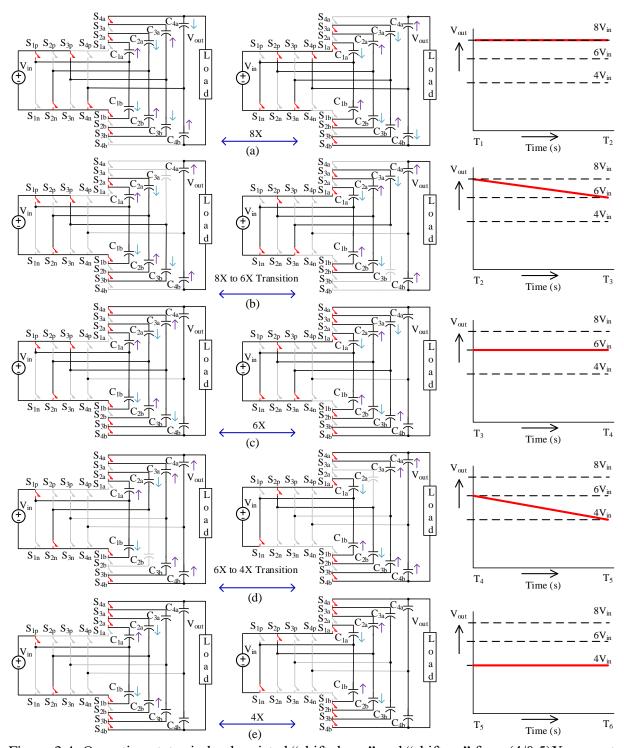

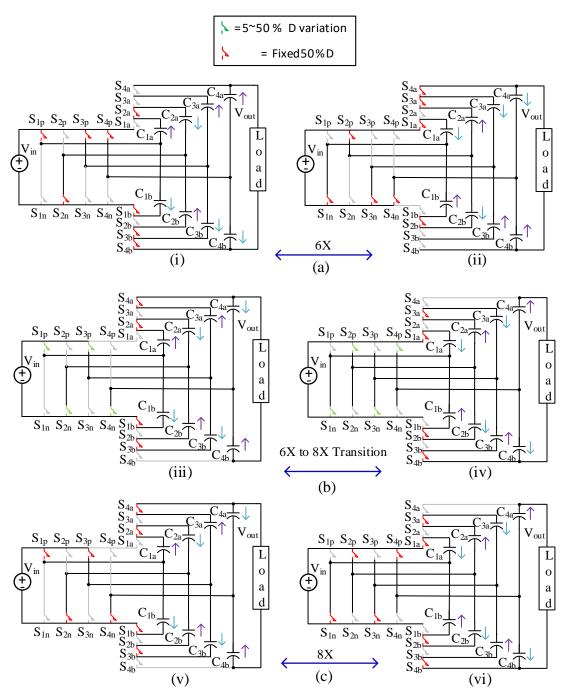

## 2.3.1 Load independent "shift-down"

Figure 2.4 (a) through (c) illustrates the trajectory of the various stages during load independent "shift-down" and Figure 2.4 (c) through (a) illustrates the trajectory of various stages resulting in load independent "shift-up" operation. In any given operating state, the switches marked in red indicate switches that are ON. Grey is used to indicate switches and current paths that are OFF due to the switches being OFF. The purple colored arrow adjacent to the arm capacitors indicates that the capacitor is being discharged in the corresponding operating state. The teal colored arrow indicates that the capacitor is being charged during the operating state. This color code is followed through the rest of the dissertation. For the (4/0.5)X converter, transitioning from stage (a) to (c) results in a "shift-down" from an initial gain of 8 to a final gain of 4. Each stage comprises of two

alternating operating states within a switching cycle (50% duration each) which are represented by means of roman numerals within each stage.

#### Stage (a)

The operating states ((i) and (ii)) within this stage are identical to that of the fixed 8X converter in [43]. The converter continuously switches between these two operating states in order to achieve a gain of 8. This is illustrated in Figure 2.4 (a). Each operating state in this stage exists for 50% duration in a given switching cycle. In steady state, the average voltage across capacitors  $C_{1a}$ ,  $C_{2a}$ ,  $C_{3a}$  and  $C_{4a}$  equal  $V_{in}$ ,  $2V_{in}$ ,  $3V_{in}$  and  $4V_{in}$  respectively. Due to the symmetric structure, the voltages across individual capacitors in the lower wing,  $C_{1b}$ ,  $C_{2b}$ ,  $C_{3b}$  and  $C_{4b}$  are equal to the voltages across corresponding capacitors in the upper wing.

### Stage (b)

Transition from stage (a) to (b) occurs when a gain "shift-down" operation from 8 to 6 is initiated. Stage (b) comprises of two alternating states (iii) and (iv), each lasting for 50% duration in a switching period. This is illustrated in Figure 2.4 (b). In operating states (iii) and (iv), the switching states in arm 4 and leg 4 are identical to switching states of switches in arm 3 and leg 3 respectively. In operating state (iii), capacitors  $C_{4b}$  and  $C_{3b}$  are essentially paralleled by means of switches  $S_{4b}$ ,  $S_{3p}$  and  $S_{4p}$ . Analysis of transients present during mode change are described in future sections of this dissertation. Operating state (iv) essentially parallels capacitors  $C_{3a}$  and  $C_{4a}$  by means of switches  $S_{4a}$ ,  $S_{3n}$  and  $S_{4n}$ . At the same time, a path for energy transfer between  $V_{in}$  and  $C_{4a}$  exists through  $S_{4a}$ ,  $S_{3a}$ ,  $C_{2a}$ ,  $S_{2p}$  and  $S_{4n}$ . The trace impedance limits the transient over-shoot in current occurring during the paralleling interval in both these cases. By continuously switching between operating states (iii) and (iv) for a duration of 50% in each switching cycle, capacitors  $C_{4a}$  and  $C_{4b}$  are discharged until they reach a voltage close to that of capacitors  $C_{3a}$  and  $C_{3b}$ . If the converter is

set at stage (b) during steady state operation, a fixed voltage gain of 6 can be achieved. From the operating state (iii) in Figure 2.4 (b), it can be observed that in steady state, capacitors  $C_{3b}$  and  $C_{4b}$  undergo charging (teal colored arrow) from two parallel input paths enabled by switches  $S_{3p}$ ,  $S_{4p}$ ,  $S_{3b}$  and  $S_{4b}$ . During the transients, the individual capacitor voltages will undergo transitions from the steady state value. The colored arrow represents the charge/discharge states for the capacitors once the voltages have been established. Methods to determine the transient mode currents are described in future sections of the dissertation. On similar lines, the capacitors  $C_{3a}$  and  $C_{4a}$  are represented by purple colored arrows indicating that they undergo a net discharge. They essentially two parallel load discharge paths. The path for discharge for  $C_{3a}$  is through the body diode of switch  $S_{4a}$  into the load. The body diodes across switches  $S_{4b}$  and  $S_{4a}$  ensure that the voltages across capacitors in arms 3 and 4 are balanced by automatically clamping in the event of a voltage unbalance.

#### Stage (c)

Transition from stage (b) to (c) occurs when a gain "shift-down" operation from 6 to 4 is initiated. Stage (c) comprises of two alternating states (v) and (vi), each lasting for 50% duration in a switching period. These operating states are illustrated in Figure 2.4 (c). When Stage (v) commences, the switching states in arms 3 and 4 are identical to the switching states of the switches in arm 2. The switching states of switches in legs 3 and 4 are identical to those of the switches in leg 2. This essentially connects capacitors  $C_{2b}$ ,  $C_{3b}$  and  $C_{4b}$  in parallel. In state (vi), capacitors  $C_{2a}$ ,  $C_{3a}$  and  $C_{4a}$  are all essentially paralleled. By continuously switching between operating states (v) and (vi), the voltage across capacitors  $C_{4a}$ ,  $C_{4b}$ ,  $C_{3a}$  and  $C_{3b}$  reach a value close to voltage across  $C_{2a}$  and  $C_{2b}$  (2V<sub>in</sub>). Thus, at steady state, operating in stage (c) leads to a voltage gain of 4.

## 2.3.2 Load independent gain "shift-up"

Transitioning from stage (c) to (a) in Figure 2.4 results in a "shift-up" from a gain of 4 to a gain of 8. The sequence of stages is the reverse of the sequence used for "shift-down" described before. The operating states within each of the stages remains the same as that described for "shift-down".

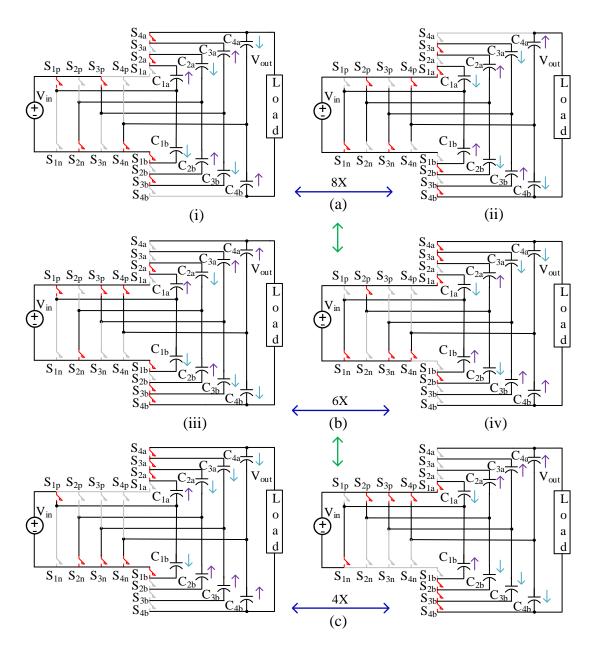

Figure 2.4: Operating states for load independent "shift-up" and "shift-down" in voltage gain.

This section describes the brief trajectory of all the operating states involved for the load-independent gain shift from 8 to 4 and back to 8. Detailed analysis of currents and voltage during transition along with equivalent circuits for each mode transition are described in future sections. While the energy loss during paralleling of capacitors with large voltage differences can affect the instantaneous efficiency, the converter can still be designed for high overall efficiency. The overall design of the converter to withstand transient conditions during mode change and achieve high overall efficiency forms an important aspect. This is described in Section 2.5. Experimental results for the load independent gain shift on a 1-kW prototype are presented in Section 2.7.

### 2.4 Equivalent Circuit and Transient Currents during Load- Independent Mode Change

In this dissertation, transient mode is defined as the time duration between initiation of mode change (from current gain level) and the time taken to reach the new steady state (to new gain level). Analysis of the circuit in transient mode is an important step in determining the transient voltage and currents through individual switches. In order to simplify the transient mode analysis, the simplified equivalent circuits for every such mode transition are first derived based on the operating states in Figure 2.4. Equations determining the transient current through the switches in each mode are then determined. The transient over-voltage across each switch is dependent on the transient current through each switch (described in Section 2.5). For this analysis, the steady state capacitor voltage ripple is ignored as it is much smaller than the capacitor voltage ripple in transient mode. The equivalent circuit also provides the charge/discharge paths for each of the capacitors involved.

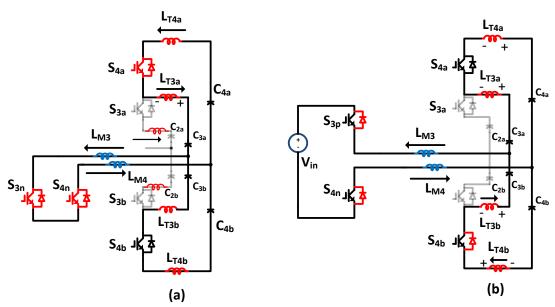

#### 2.4.1 8X to 6X Mode Transition