23525531

#### This is to certify that the

#### dissertation entitled

A Design Paradigm for Implementing Robotic

Control Algorithms in ASIC

presented by

Steven Siutit Leung

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Elec. Engr.

Malad Slumblatt Major professor

**>**

Date Feb. 6, 1989

MSU is an Affirmative Action/Equal Opportunity Institution

0-12771

PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due.

| DATE DUE | DATE DUE | DATE DUE |

|----------|----------|----------|

|          |          |          |

|          |          | :        |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

MSU Is An Affirmative Action/Equal Opportunity Institution

# A Design Paradigm

for

## **Implementing Robotic Control Algorithms in ASIC**

Ву

**Steven Siutit Leung**

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

**DOCTOR OF PHILOSOPHY**

Department of Electrical Engineering

1989

### A Design Paradigm

for

## **Implementing Robotic Control Algorithms in ASIC**

By

#### Steven Siutit Leung

#### **ABSTRACT**

The advent of the ASIC (Application-Specific Integrated Circuit) technology has created a new opportunity for robotic control — the feasibility of designing single-chip processors dedicated to the execution of a specific control algorithm. Central to meeting this challenge is a better understanding of the interactions among robotic algorithms, computational architectures, and the implementing technology. This research fulfils this need by developing a paradigm based on the architecture design of an ASIC chip implementing the algorithm for computing the inverse kinematic solution of a robot manipulator.

To provide system designers with a logical view of the implementing technology a broad range of ASIC design knowledge is organized into a conceptual framework consisting of three frames — design process, design hyperspace, and design repertoire. Under this framework, IC design is viewed as a process of making design decisions, and the emphasis is placed on the recognition and evaluation of design alternatives.

The process of making architecture design decisions is generalized into an ASIC architecture design methodology. The methodology partitions the architecture design process into three phases of functional unit configuration, communication configuration, and control configuration. To provide a focus for the decision making process, design information of each phase is represented by a form conducive to manipulation. To

facilitate the verification and testing process, the behavior of the chip is represented by an instruction set derived from the control signals. Thus, embodied in this methodology is the new concept of derived instruction set computer (DISC) design, a manifestation of the basic principle of allocating hardware resources based on the tradeoff analysis of the application needs and the potential benefits in the algorithm-specific processor design environment.

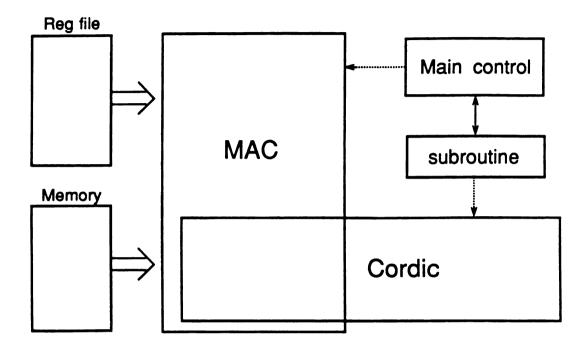

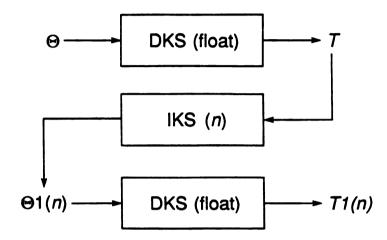

The execution of the ASIC architecture design methodology is then illustrated by the design of a gate array chip implementing the closed form IKS algorithm for a robotic manipulator. The analysis of architectural alternatives has led to the idea of synthesizing a MAC structure with a cordic core as an on-chip coprocessor. The resultant architecture, called MACC for Multiplier Accumulator with a Cordic Core, can compute the IKS in 125 instruction cycles, or 445 clock cycles. The architecture requires about 28K effective gates, or less than 50K actual gates with a gate utilization of 60%. VHDL simulation of the architecture indicates that a clock rate of 10 MHz is achievable. This clock rate enables the IKS to be computed in less than 45 µs. Compared with a single cordic processor implementation, the area of MACC is estimated to be about 23% larger, but the computation time is reduced by more that one third, giving a overall area-time efficiency of 1.866 over the single cordic processor approach.

To my parents and my remote lovers

#### Acknowledgements

Research has always been an expensive undertaking, but in today's highly competitive world it is quickly becoming a luxury affordable only to a few lucky souls. In this respect, I am especially grateful for the financial support from the Dean's Distinguished Fellowship, the All-University Research Initiation Grant, and in particular, the State of Michigan Research Excellence for Economic Development (REED) Fund. Without this support, this research effort, which has spanned over a period of more than five years since its initial conception, would not have been possible.

I wish to thank my major advisor, Dr. Michael A. Shanblatt, for providing me a free environment that has proven to be so vital not only to my personal growth but also to the success of this research. Michael's ability to liberate a student's spirit is enviable. His generousness and encouragements have the magic power of turning the possibility of a very productive life into reality. The patience, confidence, and trust that he places on our relationship have undoubtly established a solid foundation for a long-lasting friendship.

I am indebted to many people who have helped me technically and emotionally prepare for the ordeal in various ways. Among them, Dr. P. David Fisher to whom I first knew in my undergraduate years has been an example of professionalism and hard work for his students to follow. His ability to articulate technical concepts in their finest subtleties is admirable. His support and encouragement throughout my graduate years have been a constant source of joy. Dr. Harriett Rigas has also been supportive to this research. Her tough criticisms have steered my research into a more well rounded direction. Special thanks are also due to Dr. Moon Jung Chung of Computer Science Department for providing me very helpful tutorial materials on VHDL.

Steven Leung

East Lansing

Febuary 1989

# **Table of Contents**

| List of Figures                                                 | vii |

|-----------------------------------------------------------------|-----|

| List of Tables                                                  | ix  |

| Chapter 1. Introduction                                         | 1   |

| 1.1 Problem Statement                                           |     |

| 1.2 Approach                                                    |     |

| 1.3 Organization of the Dissertation                            |     |

| Chapter 2. Background                                           | 9   |

| 2.1 The ASIC Challenge                                          |     |

| 2.1.1 ASIC Design Styles                                        |     |

| 2.1.2 The Cutting Edge                                          |     |

| 2.1.3 Impact of ASIC on System Design                           |     |

| 2.2 Computer Architecture Design for Robotic Control            |     |

| 2.2.1 Trends in Architecture Design for Robotics                |     |

| 2.2.2 Dedicated Hardware Implementation Considerations          |     |

| 2.2.2.1 The Robotic Computation Hierarchy                       |     |

| 2.2.2.2 The Computational Needs                                 |     |

| 2.2.2.3 Economic Considerations                                 |     |

| 2.2.3 A Survey of Previous Work                                 |     |

| 2.2.3.1 Design Features                                         |     |

| 2.2.3.2 Design Approaches                                       |     |

| 2.2.4 Matching Architecture Styles to Algorithm Characteristics |     |

| 2.2.4.1 Metrics for Evaluating Architectural Effectiveness      |     |

| 2.2.4.2 Assessment of Advanced Architecture Concepts            |     |

| 2.2.4.2.1 Pipelining                                            |     |

| 2.2.4.2.2 RISC                                                  |     |

| 2.2.4.2.3 Systolic Array                                        |     |

| 2.2.4.2.4 Multiprocessors                                       |     |

| 2.3 Robotic Kinematics                                          |     |

| 2.3.1 The Direct Kinematic Solution                             |     |

| 2.3.2 The Inverse Kinematic Solution                            |     |

| 2.3.2.1 Numerical Method                                        |     |

| 2.3.2.2 Closed Form Solution                                    |     |

| 2.3.3 Previous Designs Dedicated to Kinematics Computations     |     |

| 2.4 Summary                                                     |     |

| Chapte       | er 3. A Conceptual Framework for ASIC Design               | 45 |

|--------------|------------------------------------------------------------|----|

| 3.1          | The Nature of ASIC Design                                  | 46 |

|              | 3.1.1 A Comparison of ASIC Design and SIC Design           |    |

|              | 3.1.2 A Decision-Making Perspective                        |    |

|              | versus a Transformation Perspective                        | 47 |

| 3.2          | The ASIC Design Process                                    | 49 |

|              | 3.2.1 VLSI Design Hierarchy                                | 50 |

|              | 3.2.2 VLSI Design Methodology                              | 50 |

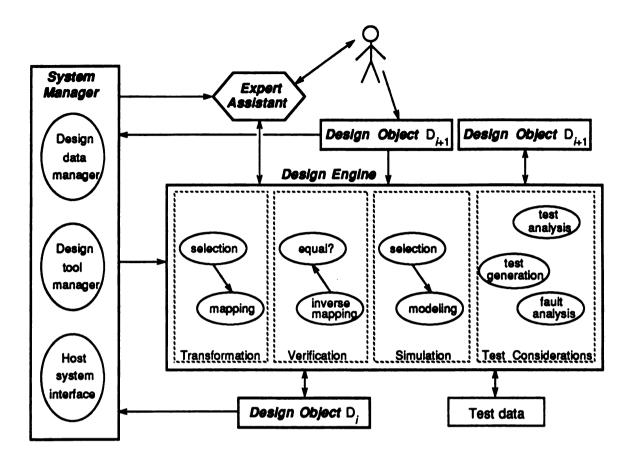

|              | 3.2.3 DOEMA: A Model for Methodology Implementation        | 52 |

|              | 3.2.3.1 The Design Object                                  | 54 |

|              | 3.2.3.2 The Design Engine                                  | 55 |

|              | 3.2.3.3 The System Manager                                 | 57 |

|              | 3.2.3.4 The Expert Assistant                               | 58 |

| 3.3          | The ASIC Design Hyperspace                                 | 59 |

|              | 3.3.1 The Design Space Concept                             | 60 |

|              | 3.3.2 The Architecture Space                               | 62 |

|              | 3.3.3 The Algorithm Space                                  | 64 |

| 3.4          | The ASIC Design Repertoire                                 | 67 |

|              | 3.4.1 Resource Configuration                               | 68 |

|              | 3.4.2 Algorithm Restructuring                              | 69 |

|              | 3.4.3 System Partitioning                                  | 70 |

| 3.5          | Summary                                                    | 71 |

| <b>C</b> 1 4 | 4 mi waa ah bara                                           |    |

| _            | er 4. The IKS Chip Design Paradigm                         |    |

| 4.1          | Introduction                                               |    |

|              | 4.1.1 Assumptions and Constraints                          |    |

|              | 4.1.2 Design Philosophy and Objective                      |    |

| 4.2          | An ASIC Architecture Design Methodology                    |    |

|              | 4.2.1 Overview                                             |    |

|              | 4.2.2 Phase 1: Functional Unit Configuration               |    |

|              | 4.2.2.1 Decision Focus: The Functional Unit Profile        |    |

|              | 4.2.2.2 Alternatives and Guidelines                        | •  |

|              | 4.2.3 Phase 2: Communication Configuration                 |    |

|              | 4.2.3.1 Decision Focus: The Dataflow Table                 |    |

|              | 4.2.3.2 Alternatives and Guidelines                        |    |

|              | 4.2.4 Phase 3: Control Configuration                       | 86 |

|              | 4.2.4.1 Decision Focus: The Control Signal Pattern Profile | 87 |

| 4.2.4          | 4.2 Alternatives and Guidelines                            | 8/  |

|----------------|------------------------------------------------------------|-----|

| 4.3 The IKS C  | Chip Architecture Design                                   | 88  |

| 4.3.1 Desi     | ign Decisions on Functional Units                          | 89  |

| 4.3.           | 1.1 The Characteristics of the IKS Algorithm               | 89  |

| 4.3.           | 1.2 Basic Architectural and Algorithmic Alternatives       | 92  |

| 4.3.           | 1.3 Simulation Results of Fixed-Point Calculation          | 95  |

| 4.3.           | 1.4 MACC Functional Unit Profile                           | 97  |

| 4.3.           | 1.5 The IKS Pseudocode                                     | 102 |

| 4.3.2 Desi     | ign Decisions on Communication Facilities                  | 102 |

| 4.3.2          | 2.1 Editing the Dataflow Table                             | 104 |

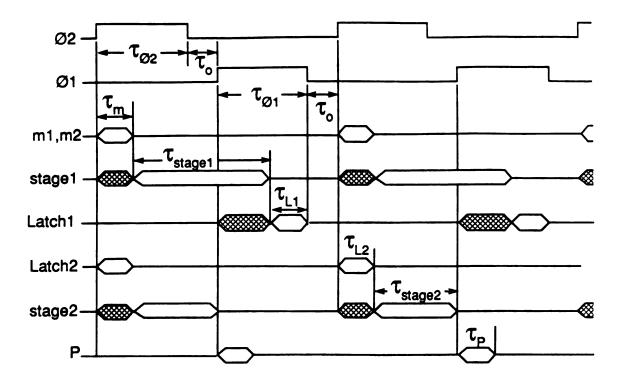

| 4.3.2          | 2.2 Timing Model of System Events                          | 106 |

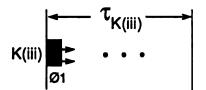

|                | 4.3.2.2.1 Timing of Phase-One Events                       | 108 |

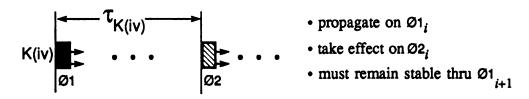

|                | 4.3.2.2.2 Timing of Phase-Two Events                       | 109 |

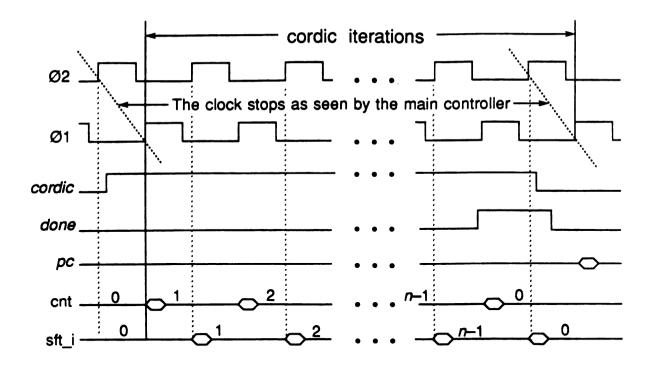

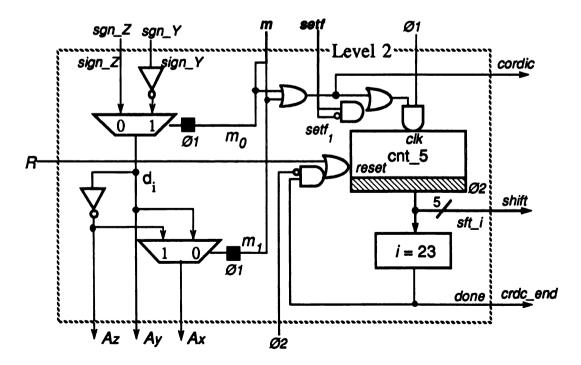

|                | 4.3.2.2.3 Timing of Cordic Execution                       | 111 |

|                | 4.3.2.2.4 Timing of the Multiplier                         | 112 |

|                | 4.3.2.2.5 Timing Constraints                               | 113 |

| 4.3.           | 2.3 The Interconnection Scheme of the IKS Chip             | 114 |

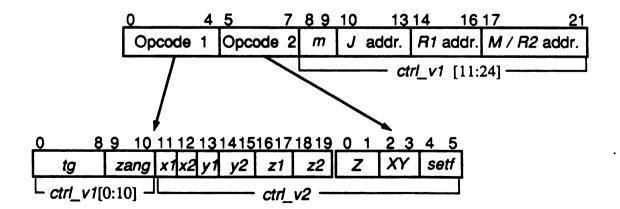

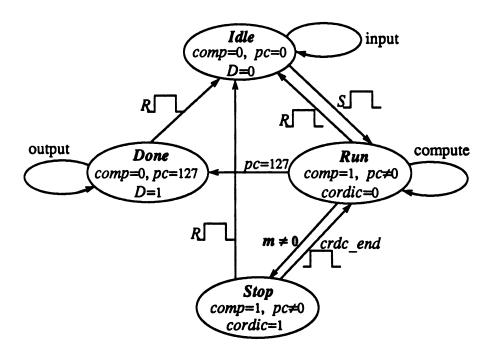

| 4.3.3 Des      | sign Decisions on the Control Structure and Mechanisms     | 116 |

| 4.3.           | 3.1 The IKS Chip Symbolic Control Signal Pattern Profile . | 118 |

| 4.3.           | 3.2 Coding Scheme Alternatives                             | 120 |

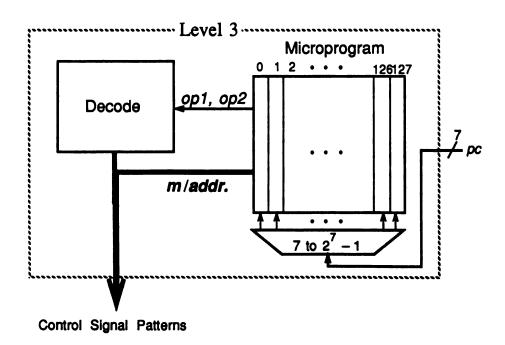

| 4.3.           | 3.3 The MACC Microcode and Instruction Set                 | 121 |

| 4.3.           | 3.4 The MACC Microprogram for the IKS Computation          | 122 |

| 4.3.4 Eva      | lluation                                                   | 122 |

| 4.3.           | 4.1 Area                                                   | 124 |

| 4.3.           | 4.2 Performance                                            | 125 |

| 4.3.           | 4.3 Resource Utilization                                   | 126 |

| 4.3.           | 4.4 Testability Considerations                             | 127 |

| 4.4 Summary    |                                                            | 129 |

| Chapter 5. Cir | cuit Decomposition and VHDL                                | 131 |

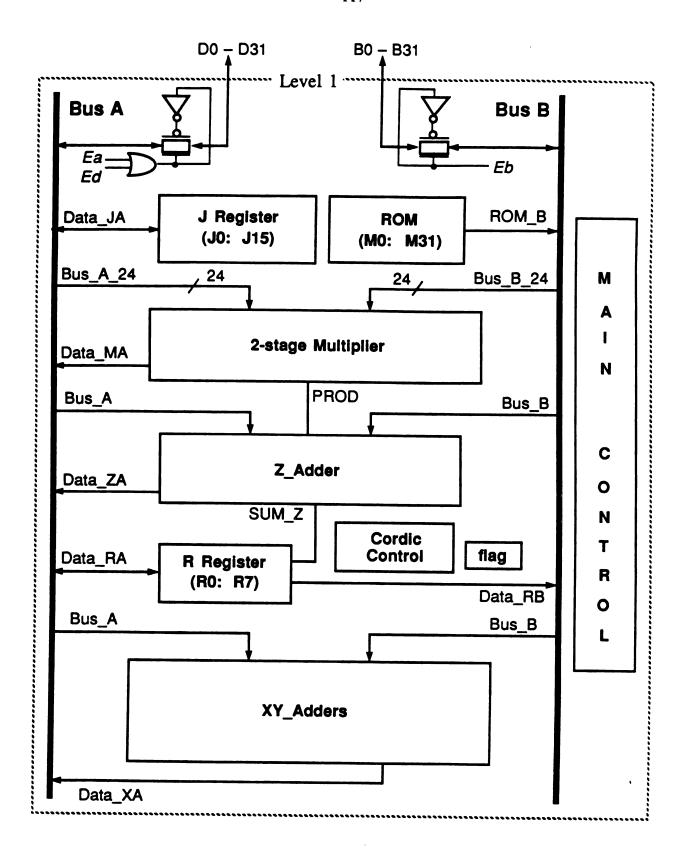

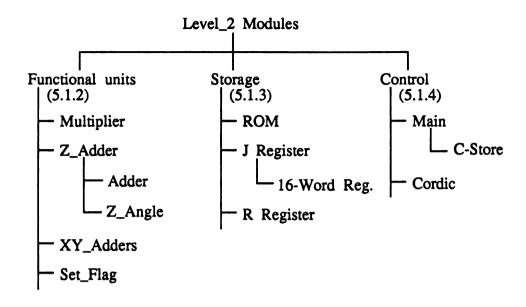

| _              | al Decomposition of the IKS Chip                           |     |

|                | ation                                                      |     |

|                | ctional Units                                              |     |

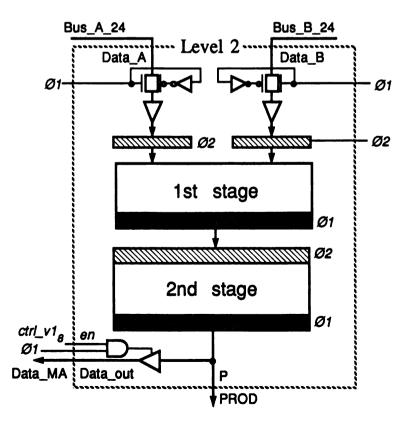

|                | 2.1 The Multiplier Module                                  |     |

|                | 2.2 The Z_Adder Module                                     |     |

| J.1            | 5.1.2.2.1 The Adder Sub-module                             |     |

|                | 5.1.2.2.2 The Z_Angle Sub-module                           |     |

|                | J.1.2.2.2 The L_Aligic Duo module                          | 130 |

| 5.1.2.3 The XY_Adders Module                                       | 137 |

|--------------------------------------------------------------------|-----|

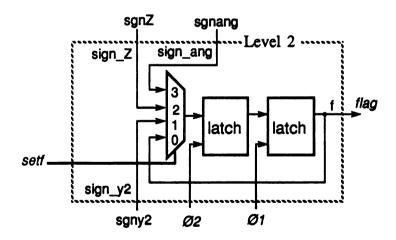

| 5.1.2.4 The Set_Flag Module                                        | 140 |

| 5.1.3 Storage                                                      | 140 |

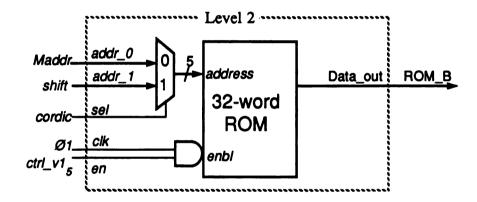

| 5.1.3.1 The ROM Module                                             | 141 |

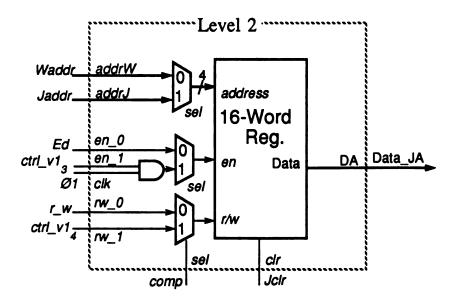

| 5.1.3.2 The J Register Module                                      | 141 |

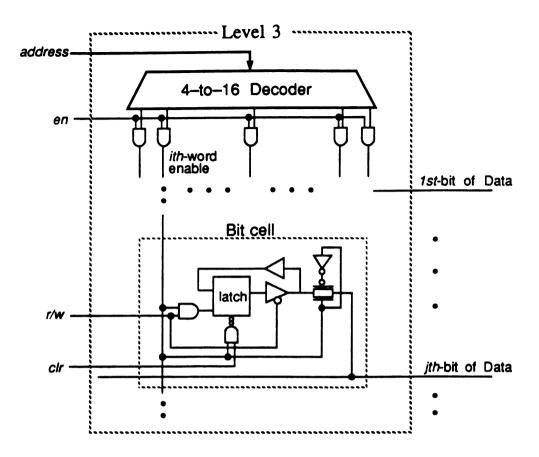

| 5.1.3.2.1 The 16-Word Register File                                | 142 |

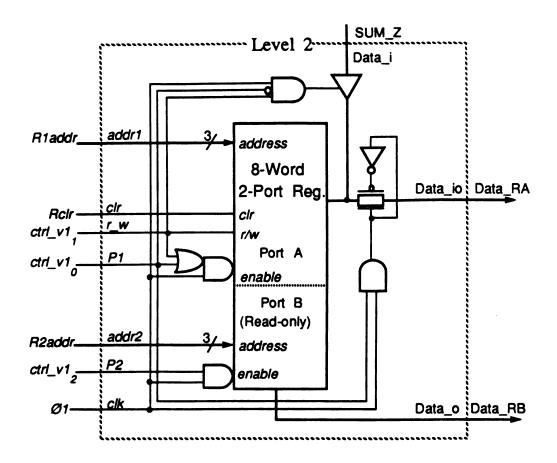

| 5.1.3.3 The R Register Module                                      | 143 |

| 5.1.4 Control                                                      | 145 |

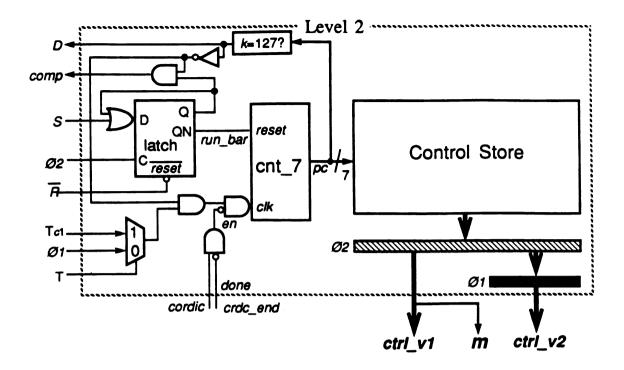

| 5.1.4.1 The Main Control Module                                    | 145 |

| 5.1.4.1.1 The Control Store Sub-module                             | 147 |

| 5.1.4.2 The Cordic Control Module                                  | 148 |

| 5.2 VHDL Simulation of the IKS Chip                                | 149 |

| 5.2.1 Simulation Objective and Modeling Approach                   | 149 |

| 5.2.1.1 Data Types                                                 | 150 |

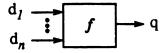

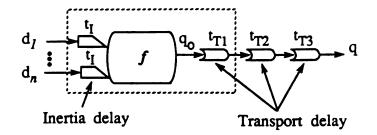

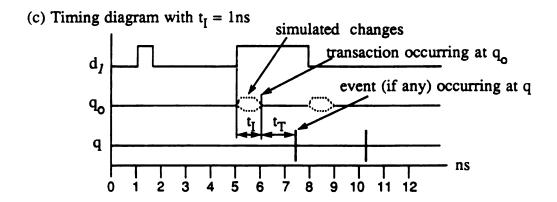

| 5.2.1.2 Delay Time                                                 | 152 |

| 5.2.1.3 Delay Time Parameters                                      | 154 |

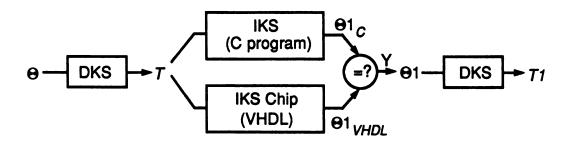

| 5.2.2 Simulation Results                                           | 155 |

| 5.2.2.1 Simulation of the Cordic Operation                         | 155 |

| 5.2.2.2 Simulation of MACC Instruction Set                         | 158 |

| 5.2.2.3 Simulation of the IKS Computation                          | 159 |

| Chapter 6. Conclusion                                              | 162 |

| 6.1 Summary                                                        | 162 |

| 6.2 Implications and Future Research                               | 164 |

| Appendices                                                         |     |

| Appendix A. The Closed Form IKS Algorithm for the PUMA             | 167 |

| Appendix B. The IKS Algorithm in Pseudocodes                       | 168 |

| Appendix C. Control Signal Definition                              | 169 |

| Appendix D. The MACC Encoding Scheme and Code-Maps                 | 171 |

| Appendix E. The MACC Microcode for Computing the IKS               | 173 |

| Appendix F. Estimates of the Gate Counts and Areas of the IKS Chip | 176 |

| Bibliography                                                       | 179 |

# **List of Figures**

| Figure 1. Relative merits of various ASIC implementation styles                | 10  |

|--------------------------------------------------------------------------------|-----|

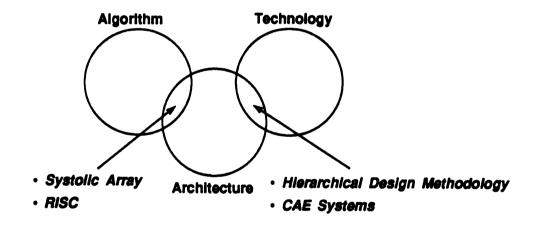

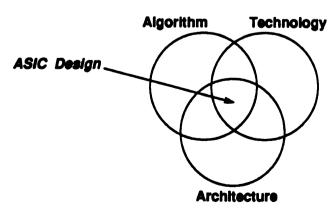

| Figure 2. Interactions among algorithms, architecture, and technology          | 16  |

| Figure 3. The three-layer computation hierarchy of a generic robotic system    | 21  |

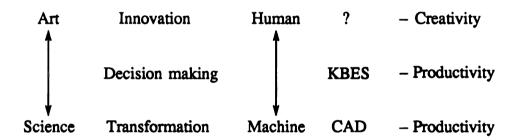

| Figure 4. The art-science dichotomy of design activities.                      | 47  |

| Figure 5. The DOEMA model for implementing ASIC design methodologies           | 53  |

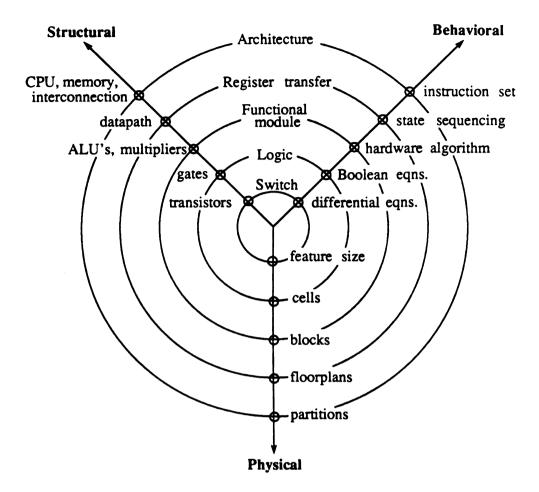

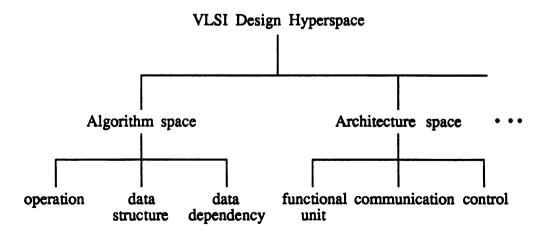

| Figure 6. A five-level hierarchy superimposed on the Y-chart                   |     |

| representation of the VLSI design hyperspace.                                  | 60  |

| Figure 7. An overview of the VLSI design hyperspace.                           | 61  |

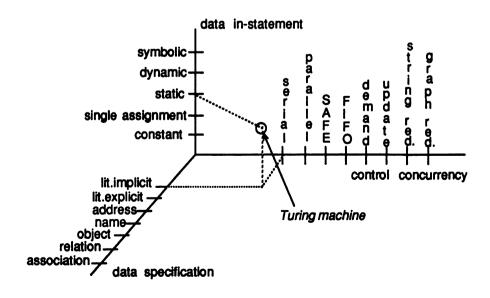

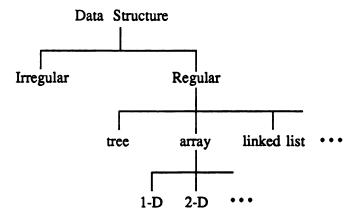

| Figure 8. Abstract architecture model space [Des84].                           | 62  |

| Figure 9. The data structure subspace.                                         | 65  |

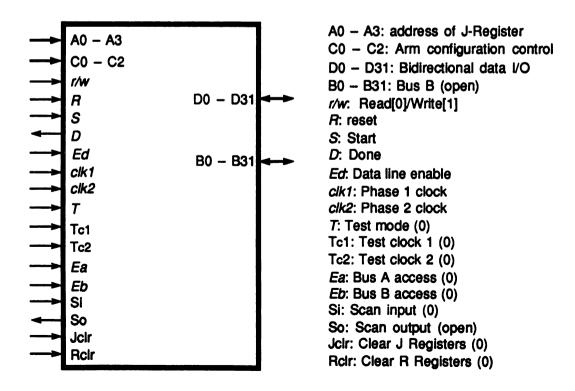

| Figure 10. The interface of the IKS chip.                                      | 73  |

| Figure 11. Organization of the IKS chip's signals into three 16-bit words      | 74  |

| Figure 12. Computing procedure using the IKS chip.                             | 74  |

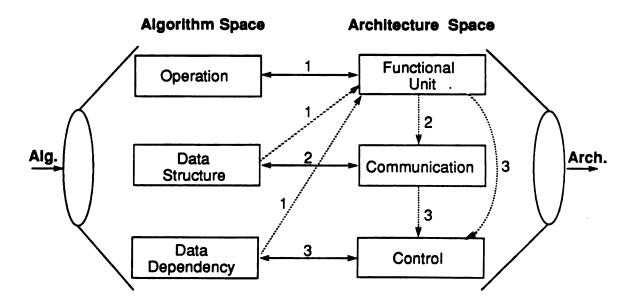

| Figure 13. Matching the architecture to the task algorithm.                    | 78  |

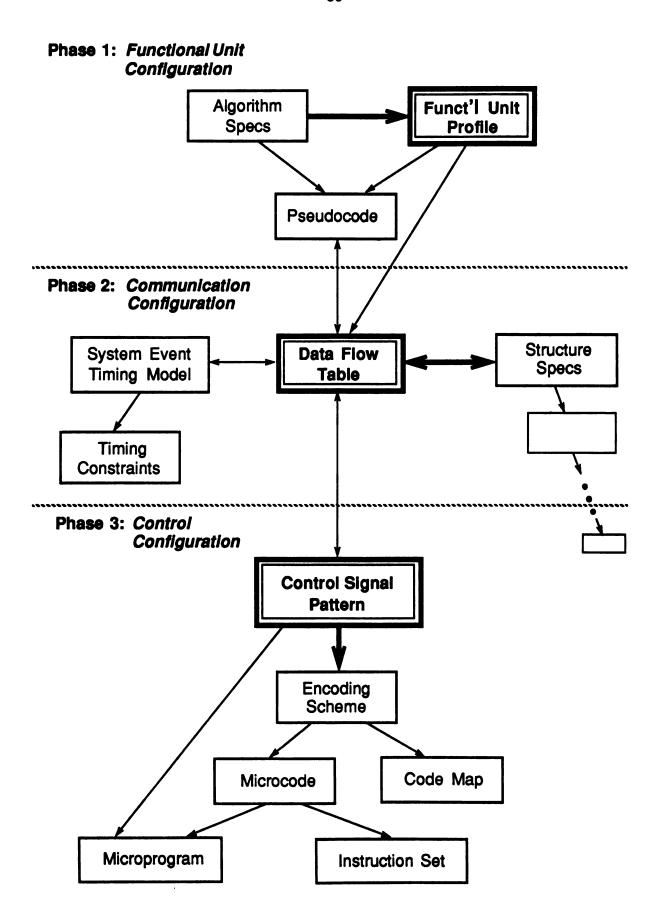

| Figure 14. The ASIC architecture design methodology.                           | 80  |

| Figure 15. The task graph of the IKS algorithm [LeCh87].                       | 91  |

| Figure 16. The architecture concept of MACC.                                   | 94  |

| Figure 17. The flow of the fixed-point simulation program.                     | 95  |

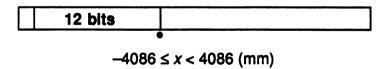

| Figure 18. The four data formats used in the IKS calculation.                  | 98  |

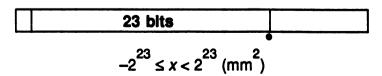

| Figure 19. Basic adder configurations for cordic execution.                    | 99  |

| Figure 20. The algorithmic descriptions for the three modes of the cordic core |     |

| Figure 21. A segment of the IKS dataflow table.                                | 105 |

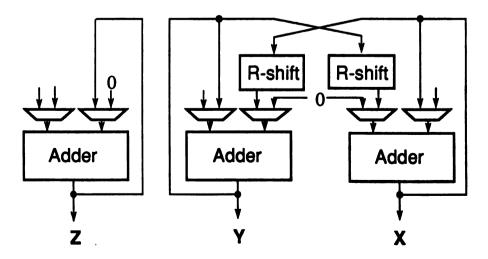

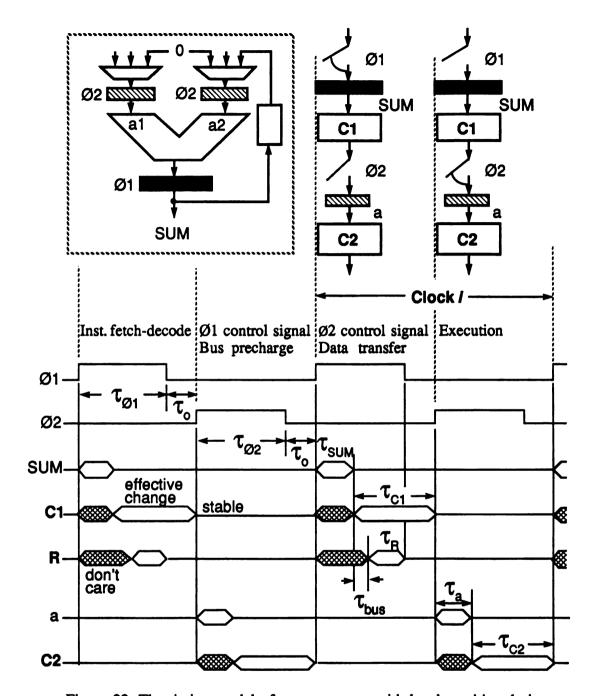

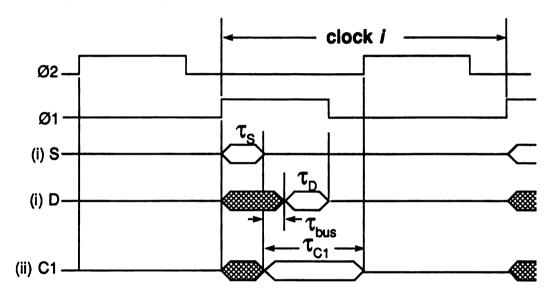

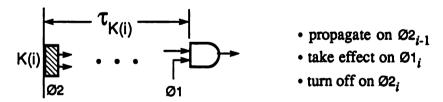

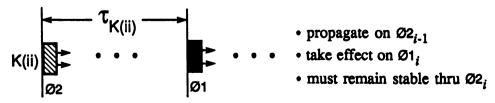

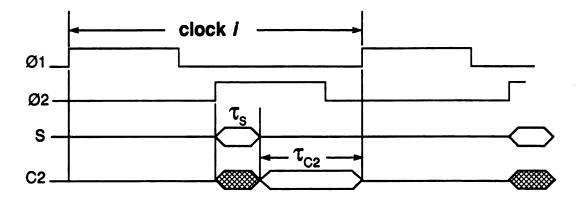

| Figure 22. The timing model of system events with level-sensitive design       | 107 |

| Figure 23. Timing model of phase-one events.                                   | 108 |

| Figure 24. Timing model of phase-two events.                                   | 110 |

| Figure 25. Timing diagram of the cordic execution.                             | 112 |

| Figure 26. Timing diagram of the multiplier.                                   | 113 |

| Figure 27. Timing constraints of the IKS chip                                  | 114 |

| Figure 28. The interconnection scheme of the IKS chip.                         | 117 |

| Figure 29. The MACC microcode format and the control signals                   | 121 |

| Figure 30. Organization of level-2 modules.                                    | 132 |

| Figure 31. The circuit diagram of the multiplier module                        | 133 |

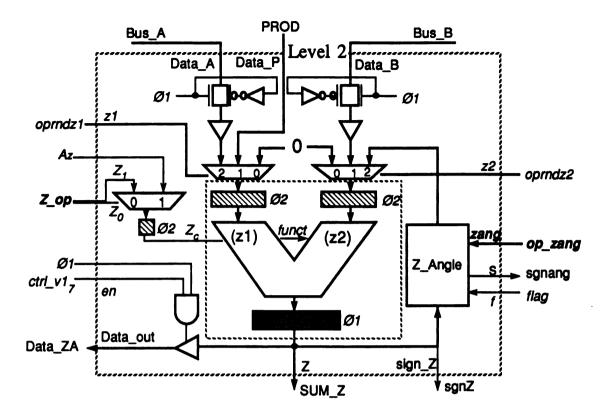

| Figure 32. The circuit diagram of the Z_Adder module                           | 136 |

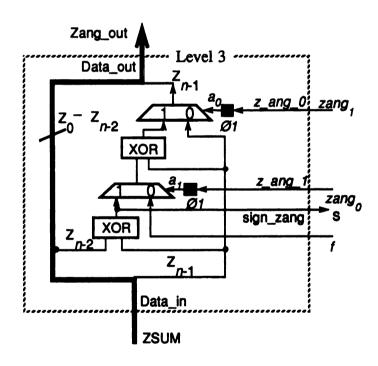

| Figure 33. The circuit diagram of the Z_Angle sub-module                       | 137 |

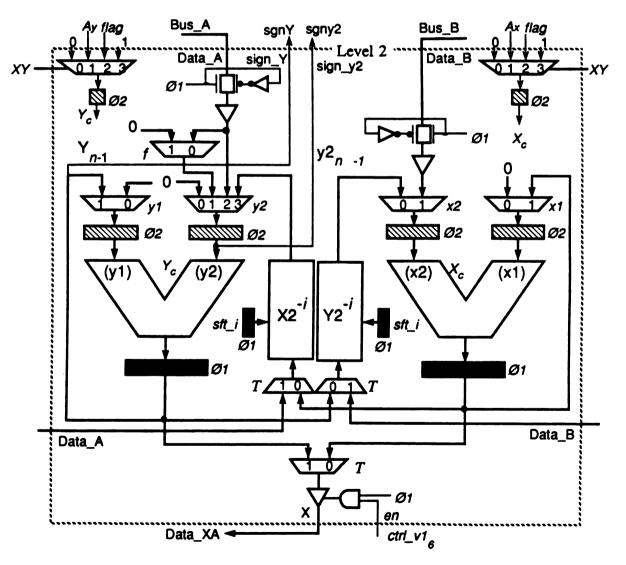

| Figure 34. The circuit diagram of the XY_Adder module                          | 139 |

| Figure 35. | The circuit diagram of the Set_Flag module.                         | 140 |

|------------|---------------------------------------------------------------------|-----|

| Figure 36. | The circuit diagram of the ROM module.                              | 141 |

| Figure 37. | The circuit diagram of the J Register module.                       | 142 |

| Figure 38. | The circuit diagram of a 16-word register file.                     | 143 |

| Figure 39. | The circuit diagram and functional table of the R Register module   | 144 |

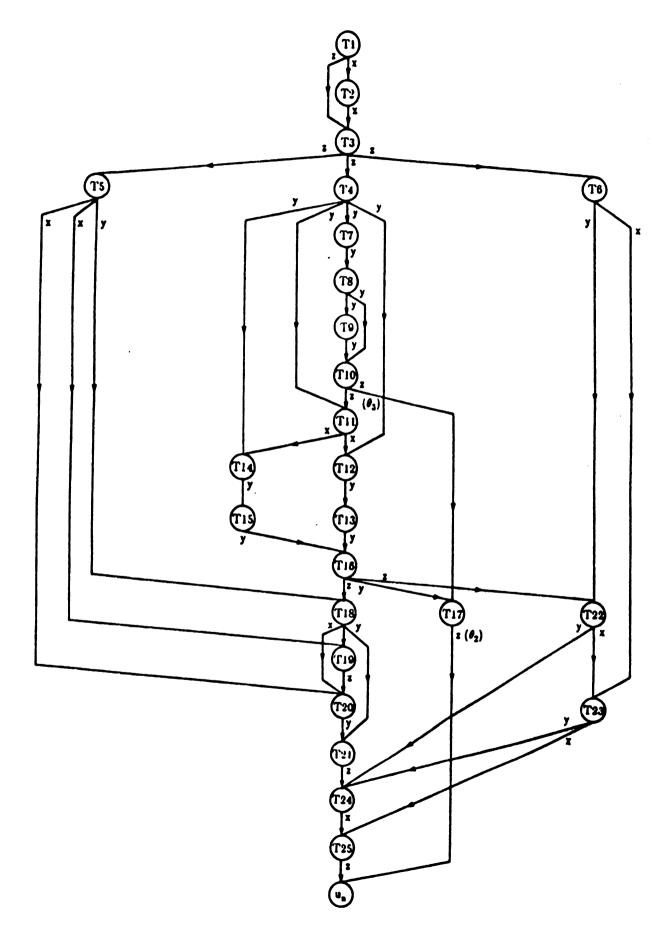

| Figure 40. | The state diagram of the IKS chip.                                  | 145 |

| Figure 41. | The circuit diagram of the main control module.                     | 146 |

| Figure 42. | The circuit diagram of the control store sub-module.                | 147 |

| Figure 43. | The circuit diagram of the cordic control module.                   | 148 |

| Figure 44. | The delay time model of a generic well formed combinational circuit | 153 |

| Figure 45. | The simulation result of mode 2 cordic operation.                   | 157 |

| Figure 46. | The flow of the IKS chip simulation.                                | 159 |

# **List of Tables**

| Table 1. A Comparison of Computer Architecture for Robotic Control           | 26  |

|------------------------------------------------------------------------------|-----|

| Table 2. Speedup and Efficiency of a Microprocessor System for               |     |

| Computing the Inverse Dynamic Equation.                                      | 38  |

| Table 3. A Comparison of Traditional Design and ASIC Design                  | 46  |

| Table 4. Hierarchy Levels, Abstractions, and Supporting Tools                | 51  |

| Table 5. Fundamental Data Dependencies                                       | 66  |

| Table 6. Operation Types and Counts in the IKS Computation                   | 90  |

| Table 7. Accuracy Distribution in the IKS Calculation                        |     |

| Using Fixed-Point Numbers.                                                   | 96  |

| Table 8. Summary of the MACC Functional Unit Profile                         | 103 |

| Table 9. The MACC Symbolic Control Signal Pattern Profile                    | 119 |

| Table 10. The MACC Instruction Set.                                          | 123 |

| Table 11. Area Estimate of the IKS Chip                                      | 124 |

| Table 12. Hardware Resources Utilization of the IKS Chip                     | 126 |

| Table 13. Utilization of the MACC Instruction Set in the IKS Calculation     | 127 |

| Table 14. Functional Table of the Z_Adder Module                             | 135 |

| Table 15. The Functional Table of the Z_Angle Sub-module                     | 137 |

| Table 16. The Functional Table of the X Adder.                               | 138 |

| Table 17. The Functional Table of the Y Adder                                | 138 |

| Table 18. The Values of the X and Y Adders Control Signals                   | 139 |

| Table 19. Summary of Testing of the Cordic Operations                        | 156 |

| Table 20. The Error of the IKS Computation with respect to the Joint Angles. | 160 |

| Table 21. The Error of the IKS Computation with respect to                   |     |

| the Position and Orientation.                                                | 161 |

### Chapter 1. Introduction

ASIC (Application-Specific Integrated Circuit) technology is revolutionizing the design, manufacturing, and marketing practices in electronics-related industries [Bel86]. The essence of this revolution is that in the pre-ASIC era, system designers dealt with microprocessors and standard integrated circuits (SICs), a design process of building systems from chips, whereas ASIC design is inherently a process of integrating systems into chips. This development necessitates a major change in the discipline of system design.

Central to meeting this ASIC challenge is a better understanding of the application requirements, algorithm characteristics, major architecture concepts, implementing technology, and, most important, their interactions [LeFS88]. While models, paradigms, or methodologies exist for each of these individual domains, their interactions lack any model or theory. The application-specific nature of the technology further complicates the effort to formalize these interactions.

The underlying theme of this research is that a decision-making perspective is conducive to a better understanding of the interactions among algorithm, architecture, and technology. That is, these interactions are best understood in terms of what design decisions are involved and how they are made in a practical design. Accordingly, the major thrust of this research is to develop an architecture design paradigm to expose these interactions. Principles behind the design decision making process can then be investigated. Understandings gained from the construction of the paradigm will facilitate future efforts in implementing application algorithms in ASIC hardware.

One application area that is of particular interest to this research effort is robotics. In recent years, advancement in technology has led to many novel applications. In these applications, sensory information is used extensively, and intelligence as well as real-

time response is often required to cope with the unstructured environment or unpredictable event times. The desired enhanced functionality for the next generation of robots — sensory information based adaptability and intelligence, locomotive ability, and real-time response — are creating new computation demands.

Recognizing the computational needs of robotics control, many researchers in the robotics community have been devoting considerable effort to developing special architectures for robotics applications [NiLe85, LeCh87, OrTs86, WaBu87]. These efforts, however, are based on the traditional SIC design approach. In the future, robot designs will become highly specialized and performance-oriented as required by novel applications. Robotic systems designed for these applications may not have an immediate large user base or a prolonged product lifetime due to their experimental nature. Such product requirements and market characteristics are matched best by ASIC technology. While the potential advantages of ASIC for robotics hardware design have been generally recognized [HeHK87], progress in adopting the ASIC technology has been slow. The development of an ASIC architecture design paradigm based on robotic control algorithms will help to speed up the transfer of this technology to the robotic community.

Because of its basic role in a robot control hierarchy, the algorithm for computing the inverse kinematic solution (IKS) is chosen for ASIC implementation. Among various approaches to computing the IKS, the closed form solution has the appeal of being well understood, widely applicable, typical of control algorithms in computation characteristics, and having known non-ASIC implementations. For these reasons, it was selected for special architecture implementation. By comparing the resultant design with previous implementations, advantages and tradeoffs of the ASIC approach can be better understood.

During the course of this research, the VHDL (VHSIC Hardware Description Language) has been approved by the IEEE as the standard HDL. This allows an architecture design to be documented independent of design approach and, to a lesser

degree, of technology. Moreover, documentation of a design in VHDL is formal since the design is described by a programming language (for which the syntax is formal) and its semantics can be verified by running the program. These features are highly desirable especially for a design being considered as a paradigm. Consequently, the IKS chip is described in VHDL and verified by extensive VHDL simulations.

#### 1.1 Problem Statement

Future intelligent robots are expected to have the capability of making real-time decisions in an unstructured environment. The need to process a huge amount of kinematic and sensory information in real time under various environmental constraints renders special computer architectures necessary [LeSh88a]. Many robotic control algorithms, however, are characterized by large-grain computation with strong serialdependence. Such characteristics favor algorithm-specific computational hardware implementation [LeSh88b]. The trend of algorithm-specific design is further reinforced by the advancement of ASIC technology which makes it cost-effective to implement application algorithms directly in silicon. System design with ASIC technology, however, is fundamentally different from the traditional off-the-shelf SIC approach. A better understanding of the interactions among the application algorithm, various architecture styles, and the implementing technology is needed. In response to these needs, the aim of this research is to develop a paradigm based on the architecture design of an ASIC chip to compute the inverse kinematic solution for a robotic manipulator. By illustrating what design decisions are involved and how they are made, the paradigm will provide guiding principles for robotic engineers in mapping control algorithms in ASIC.

#### 1.2 Approach

The general approach of this research is to 1) review design approaches and techniques of existing robotic computer architectures; 2) propose a model representing the essential aspects of ASIC design activities; 3) investigate the effectiveness of the model

in characterizing computational characteristics of robotics algorithms through the experiments of implementing the IKS algorithm in ASIC; and 4) construct a design paradigm based on the experience of the IKS chip design.

The first task, an in-depth analysis and comparison of existing robotic computer architectures, serves three purposes. First, the advanced and useful design techniques can be adopted as part of the design repertoire. Second, critiques on previous designs enable the avoidance of known pitfalls in design decisions. Third, it is foreseeable that ASIC technology will coexist and compete with advanced microprocessor technology in the future. Thus, the study can help to identify areas in which the application of ASIC technology has the greatest potential for success. For the purpose of ASIC implementation, the review is focused on two key issues: how specific the architecture design should be, and what architecture style should be chosen. An understanding gained from the study will help to differentiate the more promising alternatives from those of less potential and thus set the stage for the IKS chip experiments.

For the second task, a model representing essential aspects of ASIC design activities is developed in accordance with the idea of a "frame" as a representation of knowledge. This leads to the notion of a conceptual framework which consists of three knowledge frames — *Process, Hyperspace*, and *Repertoire*. The conceptual framework provides a logical view of the technology and thus allows engineers to acquire and accumulate VLSI knowledge systematically. In addition, the development of the conceptual framework represents a two-way interaction with the construction of the IKS chip paradigm. On the one hand, the IKS chip design is guided by understandings embodied in the conceptual framework; on the other hand, insights gained from the IKS chip design provide important feedback for improving the framework.

The third task involves designing an ASIC chip architecture for executing the IKS algorithm. The architecture design proceeds within the ASIC conceptual framework. Specifically, the IKS algorithm is characterized in terms of its position in the algorithm

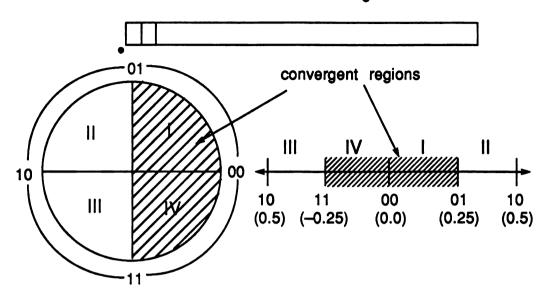

space. Architectural alternatives in functional units, interconnect topology, and control structure are identified and evaluated. Techniques classified in the design repertoire are applied with probable modifications. Analysis of the characteristics of the IKS algorithm leads to the architectural idea of a multiplier-accumulator pipeline overlapped with a CORDIC (COordinate Rotations DIgital Computer) core. The IKS algorithm is translated into a program written in pseudocodes assuming the MACC (Multiplier-Accumulator with a Cordic Core) datapath. The pseudocode program is then translated into a dataflow table and further manipulated using spreadsheet software. System timing diagrams, structural decomposition schemes, and communication links are concurrently developed and refined with the aid of the dataflow table. The dataflow table enables the designer to manipulate the computation flow of the application algorithm at the register-transfer level while maintaining a global perspective of the architecture. Once the interconnection scheme is satisfactory, the control signal patterns are specified and analyzed. An encoding scheme and the implementation of the control mechanism are determined. The control signal patterns are subsequently expressed as microcodes and further recast as the MACC instruction set. The microprogram, a microcode representation of the IKS computation, is then compiled from the dataflow table. The area and speed parameters of the resultant architecture are estimated based on data from the cell/functional module libraries of commercial ASIC products.

The IKS chip design is described in VHDL according to the circuit's structural hierarchy. Low-level building block circuits such as dynamic latches, multiplexers, shifters, counters, etc., are modeled and tested. Delayed time data are extracted from commercial gate array libraries and incorporated into the models. These building block circuits are then connected to form the next-level modules. Each of these modules is individually tested with regard to its functional specifications. The functional units and the storage elements are assembled to form the datapath, while various control modules are connected to form the entire control section. The timing aspects and the decoding mechanisms of the control section are verified. The datapath is then tested for the cordic

operation and the instruction set. Finally, the datapath is combined with the control section and additional interfacing logic to form the IKS chip. A C program is developed to generate realistic IKS input sets and expected outcomes. The VHDL description of the IKS chip is executed to simulate the IKS computation from input to output on different data sets.

The fourth task is the construction of the design paradigm based on the IKS chip architecture design. Central to the effectiveness of the paradigm is the illustration of interactions among the algorithm characteristics, the architecture styles, and the underlying technology in terms of architecture design decisions. Therefore, the investigation of the actual design process and the resultant architecture focuses upon the following issues:

- What are the major architecture design decisions and their relative importance?

- What are the alternatives associated with each of these decisions?

- What are the tradeoffs of these alternatives?

- What are the determinant factors in making each of these decisions?

- What are the relationships of these factors and the algorithmic characteristics?

An understanding of these issues is presented in the form of an ASIC architecture design methodology. The IKS chip architecture design then becomes an example of the execution of this methodology.

#### 1.3 Organization of the Dissertation

In Chapter 2, an overview of the ASIC technology is presented first. This is followed by a discussion of issues in designing computer architectures for robotics. The discussion serves three purposes: 1) to present the field of computational architecture design for robotics in general; 2) to analyze how ASIC can be used in robotics; and 3) to review major advanced architectural concepts from the perspective of understanding their

applicability in robotics. With this background, the basics of robotic kinematics and previous efforts on architecture design for computing the IKS are reviewed.

A conceptual framework for ASIC design is then presented in Chapter 3. The nature of design activities is first examined from a transformation perspective and a decision-making perspective. The conceptual framework organizes the knowledge of IC system design into three categories: design process, design hyperspace and design techniques. Key concepts presented in the process frame include the hierarchy approach, the role of methodology, and a model representing the implementation of methodologies. The hyperspace frame articulates the role of the design space concept and outlines the framing of the architecture space and algorithm space as a means to facilitate recognition of design alternatives. The repertoire catalogs techniques for evaluating design alternatives. These three frames deal with different aspects of ASIC design, but they are integrated through an underlying theme of viewing design as a decision making process. That is, system designers must structure the design process so that the solution space is manageable and design alternatives are consciously sought and evaluated. Because of the growing importance of high-level design decisions, the discussion of these concepts will focus on one particular step — the transformation from task algorithm to architecture specification.

Chapter 4 presents the architecture design paradigm of the IKS chip. It starts with a discussion of the assumptions and constraints of the IKS chip design effort. The design philosophy of this work is examined. The observation that architecture design in the ASIC environment is fundamentally different from that in the general purpose processor environment leads to the evolution of a design philosophy called DISC (Derived Instruction Set Computer). The fundamental principle of DISC states that the instruction set of an ASIC processor chip should be derived directly from its intended applications.

This design principle is embodied in an ASIC architecture design methodology developed from a decision-making perspective based on the notion of design space as delineated in the conceptual framework. The salient feature of this methodology is the division of the algorithm-to-architecture mapping into three phases with each phase

having its own decision focus. According to the nature of each design phase, the decision focus is further defined into a form conducive to manipulation. Specifically, the functional unit profile, the dataflow table, and the control signal pattern profile provide the decision foci for the design phases of functional unit configuration, communication configuration, and control configuration, respectively. Alternatives for each phase are discussed.

The execution of this methodology is then illustrated by the architecture design of the IKS chip. The design is described in accordance with the three design phases prescribed by the methodology. The entire architecture design is concluded by an evaluation of the effectiveness of the IKS chip architecture in terms of architecture-level performance, area required, and resource utilization. Testability issues are also addressed.

Chapter 5 is divided into two parts. The first part deals with the top-down hierarchical decomposition of the IKS chip. Functional tables of the chip's circuit modules are derived from the dataflow table. The design of each circuit module is carried out to sufficient detail that area and delay time parameters can be estimated from commercial gate array libraries. The complete design of the IKS chip is then described in VHDL programs according to the hierarchy of the circuit in a bottom-up fashion. The objective of the simulation is discussed and the modeling approach is explained. All building block circuits and functional circuit modules are individually simulated to verify that the program semantics are consistent with the functional specification of each module. Tested modules are instantiated as components in the next higher level description, i.e., the MACC datapath. The VHDL description of the datapath is then simulated to verify the cordic operation and the operation of the instruction set. Finally, the entire chip is simulated on realistic data sets from input to output. The results of three simulations are presented.

In Chapter 6, a summary of the major results and contributions of this research is presented. Implications for robotics architecture design, ASIC system design, and CAD tool designs are cited. Future research issues are identified and discussed.

### Chapter 2. Background

In this chapter, a brief overview of the ASIC technology is presented first. This is followed by a detailed discussion of issues in designing computer architectures for robotics. Previous efforts are reviewed from the perspective of understanding how ASIC can be applied to robotics. Specifically, two issues are addressed: how specific should an architecture design be, and what architecture style should be chosen? Then, the basics of robotic kinematics and previous efforts on architecture design for computing the IKS are reviewed.

#### 2.1 The ASIC Challenge

The strategic significance of ASIC technology is often compared to the previous microprocessor revolution. To obtain some insight into this challenge, the basics of the ASIC technology are reviewed and the impact of ASIC on system design is examined.

#### 2.1.1 ASIC Design Styles

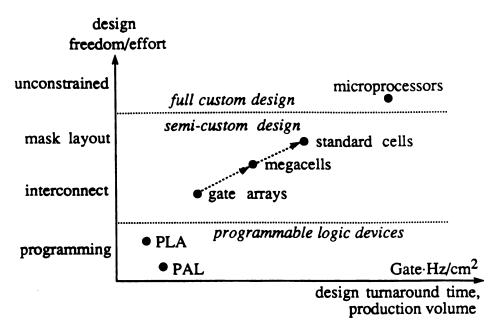

The term ASIC conveys in its meaning a mixture of aspects of design approach, implementation technology, market orientation, and the subsequent product requirements. Currently, it covers semicustom designs including programmable logic devices (PLD), gate arrays (GA), standard cells (SC), and full custom (FC) designs. The dominant interpretation refers to GA and SC. Figure 1 illustrates the relative merits of these implementation styles. The major distinction between styles is the degree of design freedom in layout: FC and SC in masks (with the latter having some restrictions in cell height and locations for connections), GA in metal interconnects, and PLD in fuses. The greater the degree of design freedom, the greater is the design effort and the longer the design turnaround time. On the other hand, under the same fabrication technology, the achievable performance, measured by the functional throughput rate (FTR) in

Figure 1. Relative merits of various ASIC implementation styles.

Gate-Hz/cm<sup>2</sup>, decreases from FC to SC to GA to PLD. In practice, the performance difference between SC and GA is relatively unimportant compared with that between semicustom designs and SIC designs; the determining factors in selecting a particular style are the acceptable design turnaround time and the projected production volume. For these reasons, GA has been the dominant choice for the past few years [Ber85]. In 1987, the industry was capable of fabricating arrays with a density of 35K usable gates using a 1.5-µm double metal CMOS process with over 200 I/O pins. Gate delays of less than 1 ns are typical [Lin87]. With yield densities of up to 150K gates using 1.5-µm feature size already in sight, projections have been made that yield densities can eventually reach 250-500K gates when the linewidth moves down to 1 µm or smaller [Col86]. To put this in perspective of computation power, note that a 16-by-16-bit signed integer array multiplier can be constructed with less than 2K gates.

Since most ASIC designs are implemented in either GA or SC, attention will be focused on these two design styles. In gate arrays, all levels of masks except the metal interconnections are predefined so that the wafer to a large extent can be prefabricated. This prefabrication of wafers is the main reason for the fast turnaround of prototype gate

arrays. For standard cells, all masks are customized, but the height of each cell is fixed to reduce the design complexity. With the more advanced module generation design approach, both the height and width of the cells can be varied. With its limited design freedom, the chip size of the gate array is typically two to three times to that of handcrafted designs [Hur85, OkSG86, EBCH86]. Compared with standard cells using the same processing technology, the FTR of the typical gate array is smaller. However, due to reduced design and processing complexity, the cost of gate arrays is lower for small production volumes.

As indicated by the dashed lines in Figure 1, a trend appears to link the various approaches. LSI Logic, for example, offers a "Structural Arrays" technique that combines both gate arrays and megacells [Waet85, WaRC87]. Other companies, like VLSI Technology, are offering gate arrays containing large standard cell blocks [McL86]. NEC is promoting a fully compatible gate array and standard cells package, and the computerized conversion of a design from gate arrays to standard cells. In contrast to the conversion approach, IBM has developed a design system that allows the complete intermix of standard cells and gate array functions. It can turn the unused cell locations into gate arrays in the background for personalization or for accommodation of minor design changes. Thus, by prefabricating masks which mainly consist of large standard cell macros (front-end-of-line masks), the standard cell product can be manufactured in gate array turnaround time [Hoet87]. Some other companies, like Silicon Design Labs, offer silicon compilers using a module generation approach to generate megacells [BuMa85]. As a result, the boundary between various semicustom design styles has become blurred. It is anticipated that a complete path of gate array, to standard cells, and to unconstrained design will emerge in the next few years. This will provide a more satisfactory solution to a wide variety of demands in terms of cost, performance, turnaround time, and production volume. An immediate implication is that design decisions regarding tradeoffs of implementation styles will become relatively unimportant since migration from one style to another can be achieved with much less effort. This trend underlines the importance of

an integrated environment, and inevitably puts pressure on companies that specialize in only one particular style.

#### 2.1.2 The Cutting Edge

Forces that motivate the technological advancement of ASIC include:

- Better performance;

- Higher reliability;

- Lower non-recurring cost;

- Faster design turnaround time;

- Tighter design security.

The first two of these driving forces are also applicable to general IC technology; the last three factors contribute to the popularity of ASIC. These factors are further examined in the remainder of this section.

#### • Better Performance

The demand for better performance has always been a major concern of the semiconductor industry. Currently, however, performance gain from processing technology is diminishing [NeVi87]. Clock speeds, the figure of merit in performance measure, of silicon microprocessor-based systems are limited to 50 MHz for off-the-shelf components. Moreover, in the SIC design environment, performance is further limited by compatibility concerns or the need to support the existing technology base. The addition into hardware of system-supporting functions, such as memory management and exception handling functions, imposes a penalty on performance in the form of system overhead per instruction [Hen84]. In contrast, such problems have less bearing on ASIC designs. In fact, the fundamental performance advantage of ASIC design is often not due to the more advanced processing technology (resulting in, for example, faster gate delay times), nor is it due to some exotic computation architecture. The advantage of ASIC is mainly derived from the fact that because of the application-specific orientation, many

system overhead functions usually associated with conventional microprocessors, or even RISC (Reduced Instruction Set Computer) processors, can be totally eliminated. Hence, with simpler control as the norm, the possibility of achieving very high performance through, for example, pipelining is greatly enhanced. Of course, this higher performance is measured with respect to the targeted applications, and is achieved at the expense of flexibility offered by general purpose microprocessors. This fundamental attribute of ASIC design emphasizes the importance of high-level design, particularly at the architecture level, for a given task algorithm. Additional advantages include the reduction of the overall system hardware size which may be critical in such applications as improving the locomotive ability of a robot or in airborne systems.

#### • Higher Reliability

Reliability is a complex matter. On the positive side, reliability at the system or board level decreases exponentially as the number of components increases. Because of the higher logic capacities, semicustom chips can replace a moderate to large number of standard chips and thus improve the system reliability. On the negative side, when existing designs are implemented in ASIC, previously accessible nodes for testing may become inaccessible. To maintain the same quality level, measured by the percentage of undetected defective products, requires a higher quality chip [Mey86]. This requirement translates into more stringent testing requirements of ASIC designs in general. But overall, current advancement in IC processing, packaging, and testing technologies have made greater improvements in IC reliability. For example, the failure rates for molded linear ICs under the industrial standard 168 hour burn-in test has been reduced from 21.48% in 1979 to 0.22% in 1982 [Pan86]. This is a two order-of-magnitude improvement in less than five years! As advanced fault-tolerant and testing techniques are incorporated into IC design, the reliability can be expected to increase. Therefore, by reducing the number of components at the board level through integration and by profiting from advancement in processing and testing technology, the ASIC approach offers a double gain in overall system reliability.

#### • Lower Non-recurring Cost

According to a 1986 survey, non-recurring development expenses for a 3,000-gate digital IC ranged from well under \$10,000 to over \$100,000 [VSDS86]. Further reduction in the cost of prototyping is expected. This will open up new opportunities for rapid prototyping and for the development of products that have either a short lifetime or require only a small production volume. But the cost factor of IC design must be examined in the context of the entire product cost at the system level, which includes cost of PCB design, assembling, and field maintenance. The benefit of ASIC in reducing the system cost, which accounts for 80% of the total product cost, is dramatic (due to smaller size, fewer components, less power consumption, reduced assembly cost, etc.) and often outweighs the development cost [FePa87]. A recent study has identified the level of integration (LOI) measured by gates per pin as the key determinant of the total IC-related cost, and ASICs can raise the number of gates per pin from 2 in MSI/SSI to a range of 40-200. The study further establishes that gate arrays have a lower cost than the MSI designs with build volumes as low as 1,000 devices if they replace at least 5-10 equivalent MSI/SSI circuits [FePa86, FePa87]. In fact, replacement of 20-60 equivalent ICs with current gate array technology is not unusual. A most striking conclusion is that when all cost variables are taken into account, significant cost-reduction opportunities lie in the virtual elimination of all MSI in system design.

#### • Faster Design Turnaround Time

From an economic standpoint, the timing of new product introductions into the market is often critical. Such a timing requirement is beginning to be satisfied with the semi-custom design approach. Faster turnaround time for ASIC production can be attributed to three reasons. First, most present day ASIC applications are implemented with either gate arrays or standard cells. For gate arrays especially, the processing time is significantly reduced since only metal interconnections need to be processed. Silicon foundries now advertise 15-day guaranteed service for CMOS 2-layer metal fabrication. The second reason is that sophisticated software design tools and CAE systems have

been developed which reduce the length of the physical design phase by reusing large portions of proven designs. For example, LSI Logic offers a compiler that can incorporate a 70-ns, 32-bit multiplier building block into the user's system and complete all design tasks, from routing, timing simulation to layout generation, within 48 hours [Ber85]. Finally, the third reason is that less stringent requirements, resulting from a reduced burden of system supporting functions, are also helping to shorten the design cycle.

#### • Tighter Design Security

Implementing task algorithms in ASIC hardware offers an effective leverage in controlling design security. Even though "reverse engineering" is always possible (particularly in the case of gate arrays) it still poses a considerable obstacle to piracy. This is especially true when compared with duplicating the software/firmware of, for example, microprocessor-based designs. By custom-designing critical system components, developers now can control the security of the architecture and algorithm. This factor may play an even more important role in the future.

#### 2.1.3 Impact of ASIC on System Design

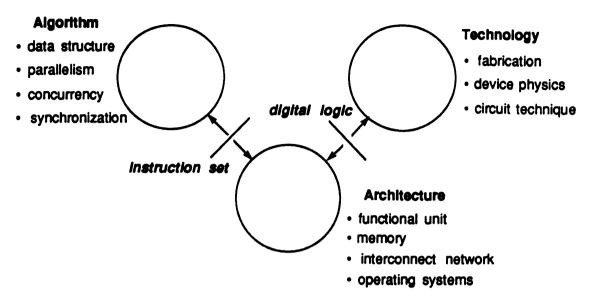

The impact of ASIC on system design can be better understood by examining the interaction patterns among the three domains of algorithm, architecture, and technology from a historical perspective. Figure 2 illustrates the evolution of these interactions from the pre-VLSI era to the ASIC era.

In the pre-VLSI era, the boundaries of these three domains were quite clear-cut. On the one hand, digital logic served well as an interface between architects who build systems from SICs and the process engineers who worked out the implementations of the circuits and devices. On the other hand, the instruction set also served well as an interface between architects and computer users who developed algorithms to be executed on machines whose behaviors are represented by the instruction sets.

As IC technology progressed to the VLSI era, the feasibility of integrating a large number of devices on a single chip established closer interactions between these three

#### (a) Before VLSI

#### (b) The VLSI Era

#### (c) The ASIC Era

Figure 2. Interactions among algorithm, architecture, and technology.

domains. On the architecture-technology side, the evolution of hierarchical design methodology as a means to control the complexity and the emergence of powerful CAE systems occurred. On the algorithm-architecture side, first systolic arrays and later RISC appeared as innovative architecture concepts that attempt to take advantage of both the architecture and certain algorithmic characteristics.

The advent of the ASIC era may be visualized as the formation of the overlapping region as illustrated in Figure 2(c). Compared with the microprocessor revolution in the pre-ASIC era, it is striking that system designers now must master a body of knowledge much larger than what was adequate previously. Indeed, integration of circuits is above all an integration of knowledge from the fundamentals of material properties, processing technology, device characteristics, circuit techniques, high-level abstractions of logic, and structural organization (architecture) principles [Seq83]. Integrating knowledge of this magnitude presents a tremendous hurdle to system designers and has created an increasingly wider gap between VLSI designers and application engineers. This gap is most plainly manifested as the disparity between our capability to fabricate and our capability to design [May85].

Moreover, system-level designs now involve users, CAE tools developers, and ASIC vendors. Interactions between these three parties are so complex that currently only the interface between CAE tools and silicon foundries, through the ASIC vendors, has begun to be standardized. The evolving nature of ASIC technology and the diversity in application areas, design tools, design approaches, and fabrication processes make it difficult to define clean interfaces between the three parties. Obviously, unlike the case of microprocessors, broadening the use of ASICs to new applications requires extraordinary effort. This effort, as made clear by the examination of the evolutionary development of the IC technology, must focus on attaining a better understanding of the interactions between application algorithms, architecture, and technology.

#### 2.2 Computer Architecture Design for Robotic Control

In the past few years a wealth of knowledge about computer architecture design for robotics has accumulated. Among the proposed designs, however, only a few have been implemented in labs and even fewer have appeared in commercial products. While previous computational needs are being satisfied due to advances in both design and technology, new applications continue to create new demands. The present condition of the robot market has forced researchers to rethink the future direction of the field and, as a result, a new research agenda has been proposed [Whi86]. In addition, nascent developments in ASIC technology have created new opportunities and challenges in architecture design. It now seems appropriate to reexamine previous efforts in robotic computer architecture designs.

Underlying the forces of market trends, ASIC technology, and the new robotics research agenda is the notion of "application specific". In this spirit, some trends in robotics applications are examined and issues involved in hardware implementations are considered. For the purpose of ASIC implementation, this study is focused on hardware designs for control. Selected previous works are then classified with respect to architecture types, design features, and performance. Based on the observations on design and application trends, design techniques, and architecture performance, the issue of how "specific" the architecture should be is addressed. Background on computer architecture design and the characterization of interactions between algorithms and architectures is then presented. With this background, four major architecture concepts — pipelining, RISC, systolic arrays, and multiprocessors — are reassessed for their applicability in robotics.

#### 2.2.1 Trends in Architecture Design for Robotics

The use of robots in industry has been focused on improving productivity through the automation of manufacturing. In the early 1980's, progress in computer technology and AI (Artificial Intelligence) research generated high expectations of furthering this goal by

introducing "intelligence" into robots. However, the 1982 forecast of an imminent robot boom has failed to become reality. In 1986, the sale of robots in the US reached only \$441M (6,219 units), far less than what was projected [Roo87]. It has become clear that in industrial applications, the use of robots is only one of the factors in the automation endeavor. Indeed, concepts such as design for assembly, environment structuring, and design-manufacturing integration might have much more to do with productivity than making robots intelligent [Whi86, Whi87].

At the same time, advancement in the technology has led to many novel applications. Robots are now operated in clean rooms, hospitals, nuclear plants, the deep seas, and in the future, in space stations. They are being used to inspect IC circuits, assist in surgical operations, perform surveillance and maintenance jobs. They are expected to supervise the fabrication of supercomputer chips in space and to help the elderly and disabled back on earth. Sensory information is used extensively in these new applications. To cope with the unstructured environment or unpredictable event times, intelligence and real-time response are often required. In contrast with traditional industrial applications, many of these new applications are relatively cost-insensitive but require robots with high performance and special features.

The differentiation of robotic R&D into these two directions has a profound impact on robotic computer architecture designs. In next section, some of the technical and economic implications are explored.

#### 2.2.2 Dedicated Hardware Implementation Considerations

Recognizing the computation demands for next generation robots, considerable research effort has been devoted to the development of special architectures for robotics. Future computation requirements, however, must be understood not only in terms of individual application needs, but also in the context of the overall system organization. Accordingly, a three-layer hierarchical computation model has been developed for a generic robotic system to provide a global view, permitting assessment of the

computational needs for control (manipulative and navigational) and sensory information processing. The economic implications of the application trends, market characteristics, and computational requirements on special hardware implementation are discussed.

#### 2.2.2.1 The Robotic Computation Hierarchy

Functions performed by the computer in modern robotic systems are hierarchically organized. Different computational needs for different applications (e.g., manipulative vs. navigational) must be examined in the context of the hierarchy in order to obtain an economical architectural solution. How the hierarchy is organized strongly influences the way it is implemented. For a technology as evolutionary as robotics, important considerations include allowing variation without jeopadizing standardization, and encouraging growth without destroying stability. These conflicting requirements are not unusual, particularly for a technology still in its infancy. However, there is a successful precedent in handling such a situation: the computer networking technology. The key of that success seems to lie in the fact that the computer networking hierarchy is organized by layers, which allows greater variations, in an open-architecture fashion. With this in mind, a robotic computation hierarchy model organized in a similar fashion, as illustrated in Figure 3, is presented.

In this model, the robotic functions are partitioned and organized into three layers: management, reasoning and device interaction. The top layer of management is mainly responsible for various routine tasks such as resource allocation, coordination, and user interfacing. The bottom layer of device interaction is directly coupled to various devices which can be divided into the two domains of manipulators/joint-actuators and sensors. The functions performed by the computer corresponding to these two domains are control and sensory information processing, each having its own hierarchy. A middle linking layer of reasoning consists of tasks such as world modeling, temporal and/or geometric reasoning, causal analysis, decision-making, and planning.

|                       | User                                                                                                                                                                                            |                                                                                                                   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Layer 2  Management   | <ul> <li>user interface</li> <li>— programming support</li> <li>— graphic/iconic protocols</li> <li>operating system environments</li> <li>resource allocation</li> <li>coordination</li> </ul> |                                                                                                                   |

| Layer 1               | <ul><li>decision making</li><li>causal reasoning</li></ul>                                                                                                                                      |                                                                                                                   |

| Reasoning             | <ul> <li>temporal reasoning</li> <li>geometric reasoning</li> <li>planning</li> <li>world modeling</li> </ul>                                                                                   |                                                                                                                   |

| Layer 0               | o control                                                                                                                                                                                       | o sensing                                                                                                         |

| Device<br>Interaction | <ul><li>adaptive control</li><li>force compliance</li><li>dynamics</li><li>kinematics</li></ul>                                                                                                 | <ul> <li>multisensor fusion</li> <li>interpretation</li> <li>feature extraction</li> <li>preprocessing</li> </ul> |

|                       | manipulators                                                                                                                                                                                    | sensors                                                                                                           |

Figure 3. The three-layer computation hierarchy of a generic robotic system.

With this model, a specific robotic computation system can be viewed as an instantiation driven by a particular application. In such an instantiation, certain components of the model robot can be absent or assume different importance. On the other hand, new application layers can be added on top of the management layer to provide sophisticated functions for developments such as simulations, FMS (Flexible Manufacturing System) or CIM (Computer Integrated Manufacturing).

#### 2.2.2.2 The Computational Needs

In the three-layer robotic computation hierarchy, tasks in Layer 2 belong to the domain of operating systems and thus are of a more general nature. Tasks in Layer 1 are largely in the research stage and not well understood yet. Since the purpose of this research is aimed at hardware implementation, the investigation of the computation needs is focused on control and sensory information processing.

The computational needs in control can be further divided into manipulator control and navigation control. In manipulator control, a sampling frequency of 60-100 Hz is considered adequate due to the mechanical constants of the arm; however, a sampling frequency as high as 5 KHz is anticipated [WaBu87]. The number of arithmetic operations (multiplication and addition) required in each cycle for a six-DOF (Degrees-of-Freedom) manipulator varies from under 1,500 with the inverse kinematics (Newton-Euler formulation) to over 6,000 with the resolved motion adaptive control method [LuWP80, LeLe84]. If performed with floating-point operations, the latter figure corresponds to a throughput requirement of 30 MFLOPS for a latency (response time) of 200 µs. Required types of elementary functions, such as trigonometric function and square root, vary from algorithm to algorithm.

The computational needs for navigation are less understood, but experiments confirm that enormous computation power is needed for perception processing and image-based world modeling. Also, the necessity for real-time response is obvious. Current experimental autonomous navigation vehicles can move at only a few kilometers per hour, and yet the on-board computer is already overwhelmed [Ada86, GoSt87]. If the navigation speed is to increase by an order of magnitude as planned, then the computation power must be increased even more due to the more stringent requirements for many concurrent control processes. Moreover, additional constraints are placed on the size, weight, and power consumption of the computation hardware because of the effect of payload on mobility.

Sensors that require special computation processing are associated with two particular types — visual and tactile. For visual sensing, if one image operation requires a simple operation on each pixel in an array of 256×256 gray level pixels, then a computation throughput of 2-4 MIPS is required at 30-60 Hz video frequency. Higher resolution with color information, combined with more complex image operations, can easily drive the throughput requirement into the billion operations per second level [Mon86]. Tactile sensor research is presently in a primitive stage with major emphasis in

searching for durable and robust materials. While the need for locally processing the sensor signals is generally recognized, the mechanism to do this is a subject of controversy [Har82, RaTa82, Gol84].

#### 2.2.2.3 Economic Considerations

The economics of designing special computer hardware involves two main factors — market and cost. According to the RIA (Robotic Industries Association), the number of US industrial robots installed in 1986 reached 25K. The market sale is projected to reach \$2,132M (125K units) in 1990 [Roo87]. As late as 1984, 80% of robot applications fell into just a few categories such as welding, spraying, machine loading, and material handling [ShGS84]. The auto industry has long been the primary user, although its market share is expected to decline from 60% in 1983 to 30% by 1989 [Coh85]. While the robot population is small, the number of species is large and growing. A recent robot database contains 220 industrial robots with payload from under 10 lbs to over 1,000 lbs and horizontal/vertical reach from a few inches to over 10 feet [McD85].

Another element in market consideration is the product lifetime. It is unrealistic to expect that a computational hardware design will last for decades since robotics and the related technology are still in a rapidly evolving state. In fact, the average product lifetime of the Sx controller, a popular controller for industrial robots from ASEA, is only about 6 years and shortening. The total number of S2 installations in its entire 6-year lifetime is 5,000 [Kee86]. In short, the robot market is characterized by small production volume, wide diversity, and accelerating dynamics. Predictably, as long as the so-called personal robot for household chores is not technically and economically feasible, these market characteristics are unlikely to change dramatically.

On the other side of the equation is the cost. For any specially designed hardware, the design cost rather than the production cost is usually the dominant component. For this reason, special IC designs for robotics have been out of the question in the past. But this situation is changing as ASIC technology becomes more prevalent. Non-recurring

cost of prototyping ASICs currently runs about \$20K for low-complexity designs and is expected to decline further [HiRa87]. In fact, the latest S3 controller contains several custom-designed LSI circuits. A recent study has established that gate array designs can be cost-effective even with production volumes of less than 1,000 units [FePa86]. Moreover, the cost of computer hardware is only part of the total cost of a robotic system. The benefits of using ASIC parts at the system level can outweigh the higher development cost. The time-to-market and performance features become the two most important factors in determining a product's success as the market moves in the application-specific and performance-oriented direction. The custom design approach, even at the IC component level, can be justified since these attributes can be met.

As can be seen from the previous discussion of application trends, new demands for computation power come primarily from novel applications. Robotic systems designed for these applications are highly specialized, experimental, and evolutionary in nature, and thus do not seem to have an immediate large user base. Hence, the strategy of designing a generic architecture encompassing the entire robotic computation hierarchy may not pay off, since the product requirements are so diverse and the total market is small and dynamic. Furthermore, when special hardware design is considered, at least one of the following conditions is usually present: either the tasks at hand are well understood (thus the algorithm that the hardware implements is relatively stable), or the required performance exceeds the capability of existing hardware. Taking all these factors into consideration, it appears premature to expand hardware design efforts beyond the device interaction layer. But even within this layer, how general (or specific) should an architecture design be? Before answering this question, an examination of previous efforts is useful.

# 2.2.3 A Survey of Previous Work

In light of ASIC hardware implementation, this study concentrates on architectures for control functions in the device interaction layer only. As a result, architectures for

image processing and a number of systems designed for support of programming and research environments are not included. The main focus is on the design approach and architecture styles.

A total of 13 designs for robotic control functions are reviewed. They constitute a collection of architectures rich in intended applications, architecture types, and design approaches. The selected works are compiled in Table 1. Information on performance, functional units, and the communication topology is based strictly on published data, while that of the control scheme in a number of cases is based on this author's assessment.

Among the 13 designs, over half are multiprocessor systems, especially in the hand control area. Most single processor systems are designed for specific control algorithms. Two designs are implemented in systolic arrays. In the remainder of this section, design features are summarized, followed by an analysis of the question of how specific an architecture design should be.

# 2.2.3.1 Design Features

Among the 13 designs, most are based on off-the-shelf functional units, but a number of architectures involve designing special IC chips, sometimes as a component of the target system. And among those off-the-shelf SIC-based designs, the emphasis is shifting from the first generation general-purpose microprocessors to the second generation special functional units such as digital signal processors (DSP), floating-point processors, or cordic processors.

The intended applications increasingly appear targeted to a specific algorithm. This trend is perhaps due primarily to the complexity of the algorithms involved, and secondarily to the generally decreasing hardware cost which makes a narrower application target economically feasible. This development is in tune with the market trend of "application specific". In parallel with the narrower target application, more designs are for processors, in contrast with stand-alone systems, and the design level is correspondingly shifted down the design hierarchy. From the perspective of the robotic

Table 1. A Comparison of Computer Architectures for Robotic Control.

|                     | Intended          |          | Desion     | Architecture                            | Characteristics           | stics           |                        |

|---------------------|-------------------|----------|------------|-----------------------------------------|---------------------------|-----------------|------------------------|

| Author              | Application       | Type     | Level      | Functional Units                        | Communication             | Control         | Performance            |

|                     | Hexanod           |          |            | S LSI-11/03                             | loosely coupled,          |                 | main cycle 117ms,      |

| KIWa82 <sup>2</sup> | (6 legs)          | Z        | System     | processors                              | fully connected           | centralized     | S = 3.47               |