24018348

# LIBRARY Michigan State University

14 6 5 P

This is to certify that the

dissertation entitled

Fault Prediction and Diagnosis In Large Analog Circuit Networks

presented by

Benlu Jiang

has been accepted towards fulfillment of the requirements for

Ph.D. degree in <u>Electrical</u>

Engineering

Major professor

Date July 10, 1989

PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due.

| DATE DUE | DATE DUE | DATE DUE |

|----------|----------|----------|

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

MSU Is An Affirmative Action/Equal Opportunity Institution

# FAULT PREDICTION AND DIAGNOSIS IN LARGE ANALOG CIRCUIT NETWORKS

By

Benlu Jiang

#### **A DISSERTATION**

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

**DOCTOR OF PHILOSOPHY**

Department of Electrical Engineering

#### **ABSTRACT**

# FAULT PREDICTION AND DIAGNOSIS IN LARGE ANALOG CIRCUIT NETWORKS

By

#### Benlu Jiang

Electronic circuits and systems have become so versatile and useful that they are indispensable in modern society. With the electronic systems continuously growing in the significance and pervasiveness of application, their testing becomes increasingly important and also more and more complex, difficult, and costly.

Most of the automatic testing and fault diagnosis algorithms proposed in literature work well only when nonfaulty components assume their nominal values exactly. In a practical circuit, the values of nonfault components may deviate from their nominal values within a predefined tolerance, and the faulty components may not be properly located or even be detected unless the system fails. This becomes the bottleneck of analog fault diagnosis. For a reliable design, we should identify potential faulty components as soon as possible before the system fails instead of doing fault location after the system fails.

In this dissertation, the fault prediction problem is initiated and a fault prediction algorithm is presented. For the case that the parameters of potential faulty components are assumed to change gradually during each maintenance period, by continuously monitoring the responses of the network, the proposed algorithm can precisely predict whether any of the network components are about to fail.

In order to apply the proposed algorithms to large circuit networks with reasonably high speed, a decomposition approach fault prediction algorithm is proposed. The approach can be used hierarchically to decompose a network into any desired level to predict and diagnose faulty subnetworks.

Due to technical limitation, it is difficult to provide proportionately more accessible terminals for testing purpose in large circuit networks. To deal with this problem, an analog build-in self-test (ABIST) structure is proposed which can provide more test points while still keeping low pin overhead and acquire test data at various test points simultaneously. It is the first analog BIST structure ever proposed for analog fault diagnosis. In order to properly design diagnosable networks, an efficient algorithm is developed to select an appropriate minimum set of test points.

In summary, this dissertation focuses on fault prediction and diagnosis. The proposed decomposition approach, ABIST structure and diagnosability design provide a useful means for fault prediction and diagnosis in large analog circuit networks.

To my parents:

Dazong Jiang and Zongxin Huang

#### **ACKNOWLEDGEMENTS**

I would like to thank Professor Chin-Long Wey, my thesis advisor, for his valuable inspiration and guidance throughout my graduate study. I would like to thank members of my thesis committee, Professors Greg Wierzba, Donald Reinhard, Edwin Kashy, and Michael Shanblatt, for their continual encouragement and many excellent comments during the course of my dissertation research.

I would like to acknowledge all the faculty members and students who gave me help and assistance during my studying at Michigan State University, and many friends who showed their support and concern.

I am very grateful to my parents Dazong Jiang and Zongxin Huang, for their years of concern, encouragement and support; to my husband Youran for his constant encouragement and direct assistance in the preparing of this manuscript; and to my daughter Lana for being so understanding.

# TABLE OF CONTENTS

| List of Tables                                    | ix |

|---------------------------------------------------|----|

| List of Figures                                   | X  |

| Chapter 1 Introduction                            | 1  |

| 1.1 Difficulty of Analog Fault Diagnosis          | 2  |

| 1.2 Methods and Comparison                        | 4  |

| 1.3 Motivation                                    | 6  |

| 1.4 Thesis Organization                           | 7  |

| Chapter 2 Fault Diagnosis                         | 9  |

| 2.1 Diagnosis Equation                            | 9  |

| 2.2 Fault Location                                | 12 |

| 2.3 Fault Evaluation                              | 13 |

| 2.4 Equivalent Fault Sets                         | 15 |

| 2.5 Software Implementation                       | 17 |

| 2.6 Examples                                      | 19 |

| Chapter 3 Fault Prediction                        | 28 |

| 3.1 Error Effect Analysis of Component Tolerance  | 29 |

| 3.2 Basic Concept of Fault Prediction             | 31 |

| 3.3 Fault Prediction Approach                     | 34 |

| 3.4 Examples                                      | 36 |

| 3.5 Discussion and Summary                        | 39 |

| Chapter 4 Decomposition Approach Fault Prediction | 40 |

| 4.1 Decomposition Approach                        | 41 |

| 4.2 Fault Prediction Approach                     | 47 |

| 4.3 Extension to Nonlinear Circuit Networks       | 53 |

| Chapter 5 BIST Structure                                 | 58  |

|----------------------------------------------------------|-----|

| 5.1 BIST Structure                                       | 58  |

| 5.2 Analog BIST Structure                                | 62  |

| 5.3 Simulation and Hardware Implementation               | 66  |

| 5.4 VLSI Implementation                                  | 71  |

| 5.4.1 Analog Switchs                                     | 71  |

| 5.4.2 Voltage Followers                                  | 72  |

| 5.4.2 Physical Layout                                    | 77  |

| Chapter 6 Design for Diagnosability                      | 79  |

| 6.1 Diagnosability Measurement                           | 80  |

| 6.2 Test Point Selection                                 | 82  |

| Chapter 7 Conclusions                                    | 91  |

| 7.1 Summary of Major Contributions                       | 91  |

| 7.2 Directions for Future Research                       | 93  |

| 7.2.1 Automatic Testing and Diagnosis                    | 93  |

| 7.2.2 Time Domain Analysis                               | 93  |

| 7.2.3 Fault Diagnosis for Analog/Digital Hybrid Circuits | 93  |

| 7.2.4 BIST Implementation                                | 95  |

| Appendices                                               | 97  |

| Ribliography                                             | 112 |

# LIST OF TABLES

| Table 2.1 $w_k$ and $\Delta x_k$ of Different Types of Components | 11 |

|-------------------------------------------------------------------|----|

| Table 2.2 Substituted Sources of Different Types of Components    | 14 |

| Table 2.3 W matrix of Example 2.1                                 | 21 |

| Table 2.4 Simulation Data of Example 2.1                          | 22 |

| Table 2.5 Component Evaluation                                    | 23 |

| Table 2.6 Component Values of Example 2.2                         | 24 |

| Table 2.7 W matrix of Example 2.2                                 | 25 |

| Table 2.8 Simulation Data of Example 2.2                          | 26 |

| Table 2.9 Simulation Results of Example 2.2                       | 27 |

| Table 3.1 Simulation Data 1 of Example 3.1                        | 37 |

| Table 3.2 Simulation Data 2 of Example 3.1                        | 37 |

| Table 3.3 Simulation Data of Example 3.2                          | 38 |

| Table 4.1 First Level Decomposition of Example 4.1                | 44 |

| Table 4.2 Second Level Decomposition of Example 4.1               | 45 |

| Table 4.3 First Level Decomposition of Example 4.2                | 45 |

| Table 4.4 Second Level Decomposition of Example 4.2               | 46 |

| Table 4.5 First Level Decomposition of Example 4.3                | 49 |

| Table 4.6 Second Level Decomposition of Example 4.3               | 49 |

| Table 4.7 Component Values of Example 4.4                         | 51 |

| Table 4.8 Simulation Result of Example 4.4                        | 52 |

| Table 4.9 Analysis in One Time Step                               | 53 |

| Table 4.10 Simulation Result 1 of Example 4.5                     | 56 |

| Table 4.11 Simulation Result 2 of Example 4.5                     | 57 |

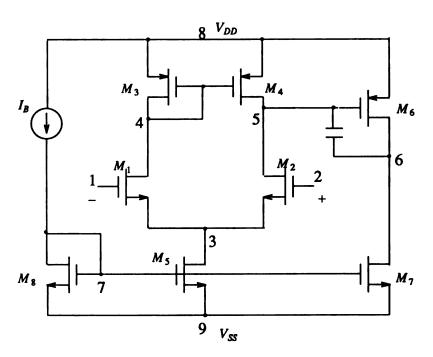

| Table 6.1 Device Parameters                                       | 73 |

| Table 6.2 Device Area                                             | 76 |

| Table 6.3 Simulation Result of an Op-amp Design                   | 76 |

| Table 7.1 Identical Groups of Example 7.1                         | 84 |

| Table 7.2 Test Point Selection and Compaction                     | 84 |

# LIST OF FIGURES

| Figure 2.1 | Circuit Networks                                                       | 10 |

|------------|------------------------------------------------------------------------|----|

| Figure 2.2 | Equivalent Faulty Network                                              | 13 |

| Figure 2.3 | A Resistor Network                                                     | 19 |

| Figure 2.4 | Equivalent Faulty Network of Figure 2.3                                | 23 |

| Figure 2.5 | An Active Circuit                                                      | 24 |

| Figure 3.1 | Circuit Networks                                                       | 29 |

| Figure 3.2 | Basic Concept of Fault Prediction                                      | 32 |

| Figure 3.3 | Prefault and Postfault Networks                                        | 34 |

| Figure 3.4 | An Active Filter                                                       | 38 |

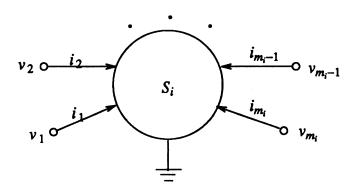

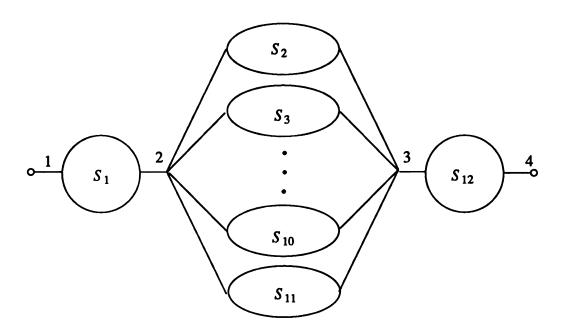

| Figure 4.1 | A Subnetwork $S_i$ with $m_i$ External Nodes                           | 41 |

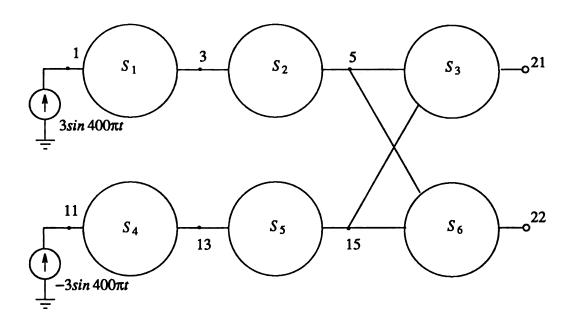

| Figure 4.2 | A Linear Network                                                       | 43 |

| Figure 4.3 | Decomposed Subnetworks S <sub>1</sub> and S <sub>2</sub>               | 43 |

| Figure 4.4 | Decomposed Subnetworks S <sub>3</sub> and S <sub>4</sub>               | 44 |

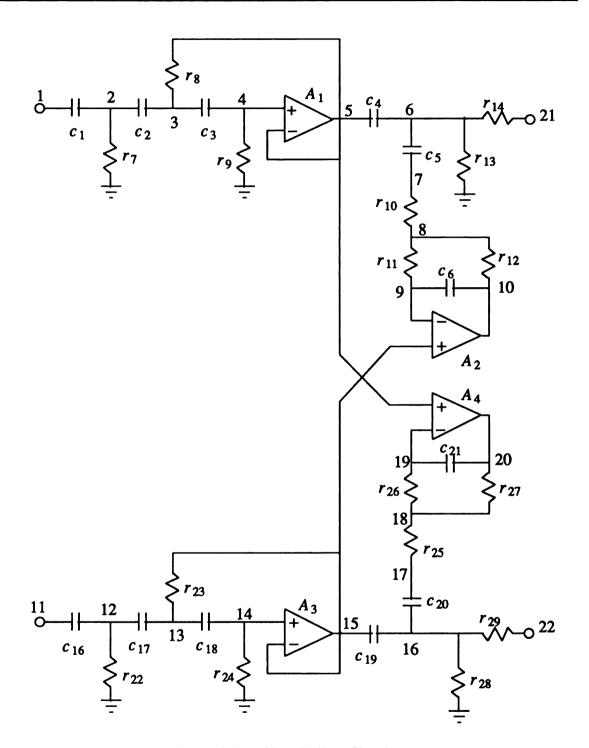

| Figure 4.5 | A Signal Filter Circuit                                                | 50 |

| Figure 4.6 | Decomposed Subnetworks                                                 | 51 |

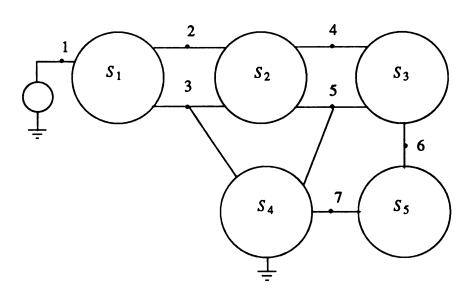

| Figure 4.7 | (a) A Network (b) Decomposed Subnetworks                               | 55 |

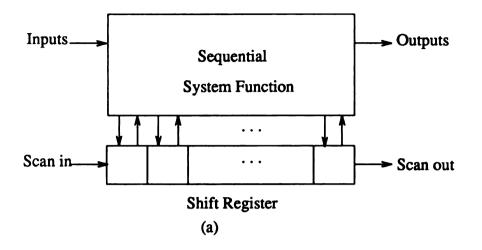

| Figure 5.1 | BIST Design of Digital Circuit: (a) Scan Design Using SRL;             |    |

|            | (b) SRL; and (c) a Shift Register with 3 SRLs                          | 60 |

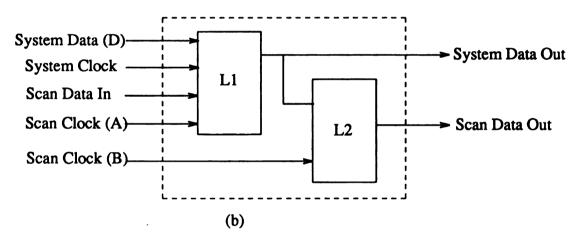

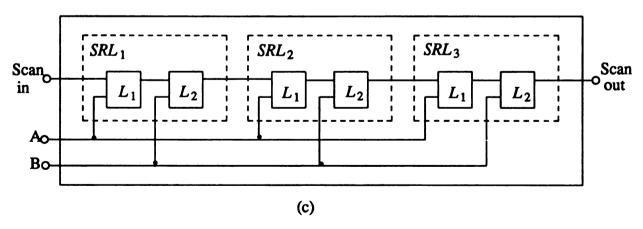

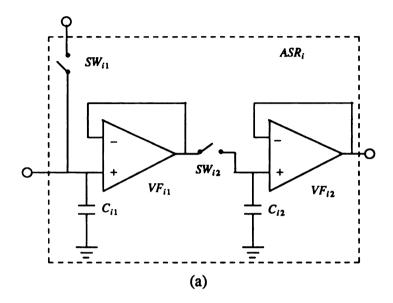

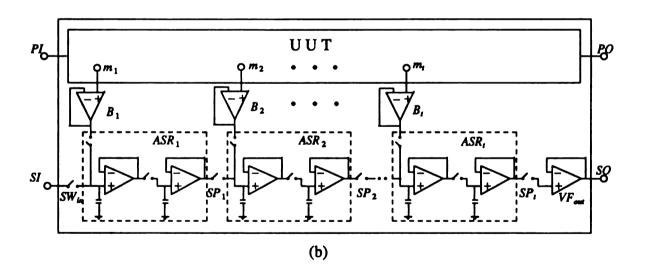

| Figure 5.2 | BIST Structure with Analog Shift Register                              |    |

|            | (a) Analog Shift Register ASR <sub>i</sub> ; and (b) Schematic Diagram | 61 |

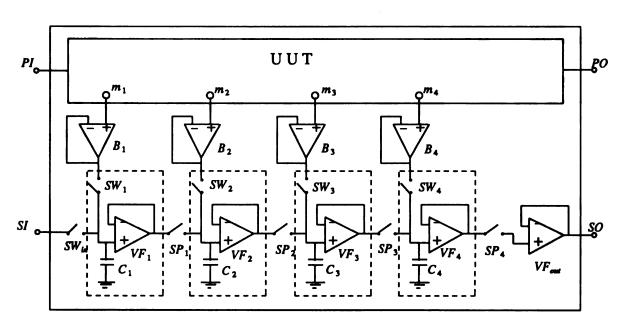

| Figure 5.3 | An Analog BIST Structure (ABIST)                                       | 62 |

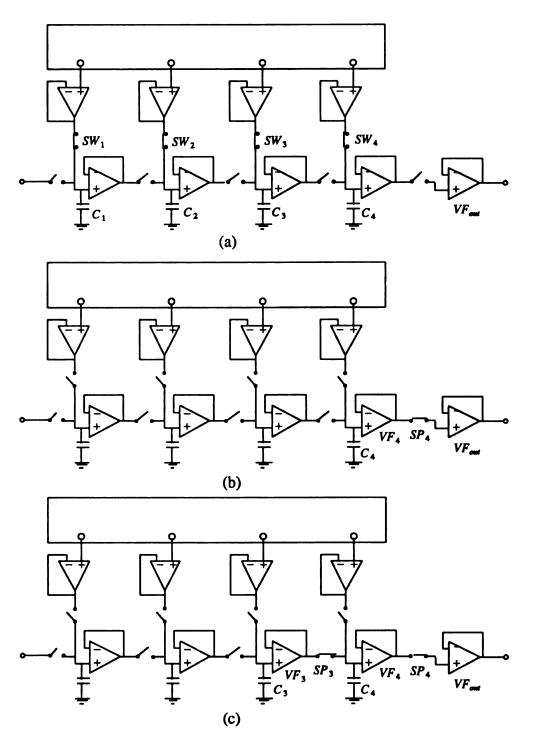

| Figure 5.4 | Switching Operation of the ABIST Structure:                            |    |

|            | (a) Parallel Loading; (b) & (c) Serial Passing                         | 64 |

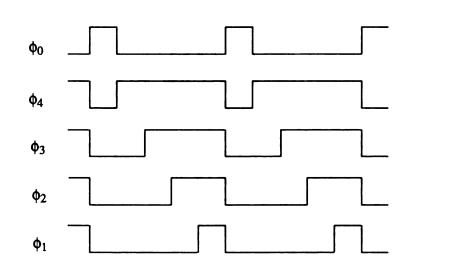

| Figure 5.5 Timing Diagram of ABIST Structure                                 | 65 |

|------------------------------------------------------------------------------|----|

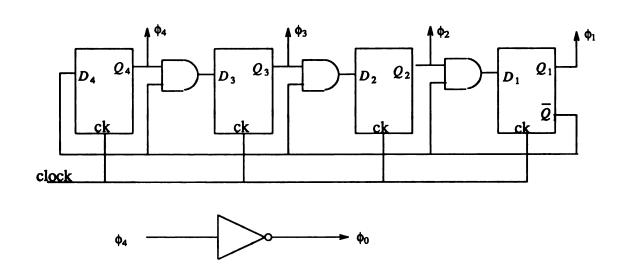

| Figure 5.6 Clock Circuit                                                     | 66 |

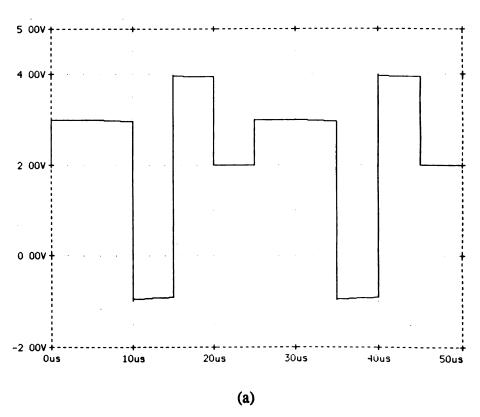

| Figure 5.7 PSPICE Simulation Results: (a) DC; (b) AC; and (c) Partion of (b) |    |

| Figure 5.7 Continuted                                                        | 69 |

| Figure 5.8 Observed Outputs from an Oscilloscope: (a) DC; and (b) AC         | 70 |

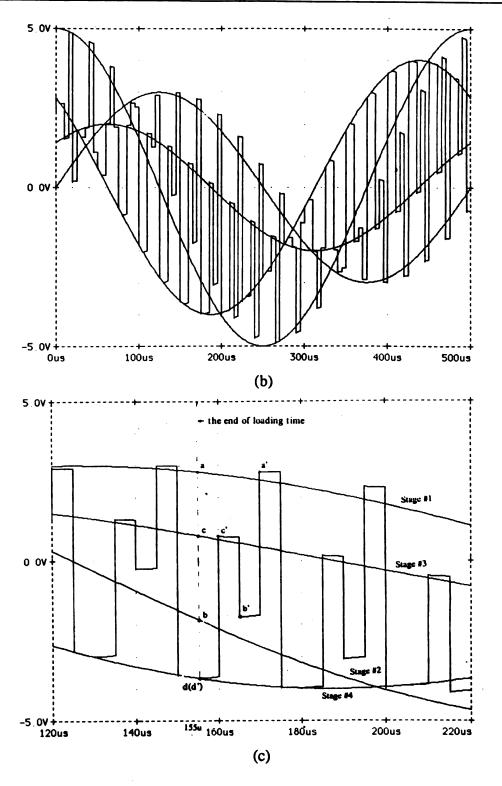

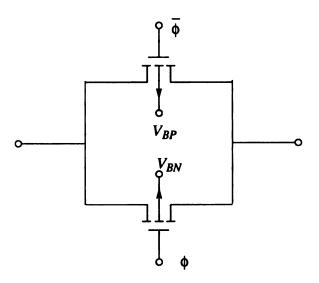

| Figure 5.9 CMOS Analog Switch                                                | 71 |

| Figure 5.10 CMOS Op-amp with N Channel Input                                 | 72 |

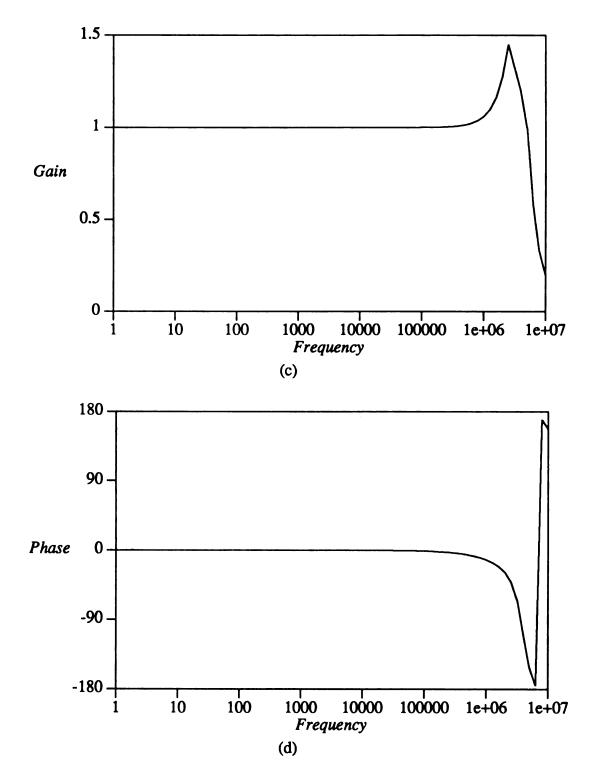

| Figure 5.11 Simulation Results:                                              |    |

| (a) Input CMR Simulation; (b) Transient Response;                            |    |

| (c) Magnitude Response; and (d) Phase Response                               | 74 |

| Figure 5.11 Continuted                                                       | 75 |

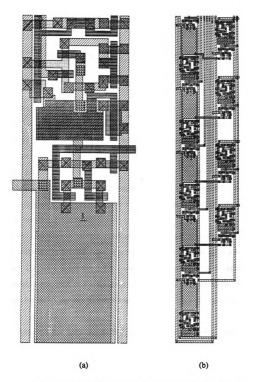

| Figure 5.12 ABIST Layout (a) one-stage (b) 4 Stage                           | 78 |

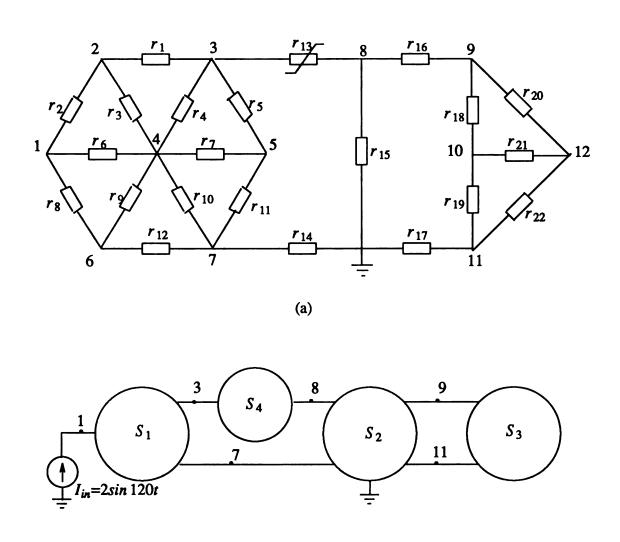

| Figure 6.1 The Network in Example 6.1                                        | 81 |

| Figure 6.2 A Ten Band Octave Equalizer                                       | 88 |

| Figure 6.3 A Decomposition of the Octave Equalizer                           | 89 |

| Figure 7.1 A Block Diagram of ATE                                            | 94 |

| Figure 7.2 ABIST Array                                                       | 96 |

# **CHAPTER 1**

#### INTRODUCTION

\_\_\_\_\_\_

Electric circuits and systems have become so versatile and useful that they are indispensable in modern society. With the electronic systems continually growing in the significance and pervasiveness of application, their testing becomes increasingly important and also more and more complex, difficult, and costly.

Electronics design has become more and more sophisticated since the last quarter of this century. Graphical algorithms have been replaced by CAD (Computer-Aided Design), and features of design implementation can be studied by simulation rather than requiring extensive breadboarding. Electronics maintenance, however, has changed very little during the same period. Therefore, our ability to design and manufacture complex electronic circuits is quickly outstripping our ability to maintain them, and the price reductions which have accompanied the new electronics technology are being offset by increased maintenance costs. Indeed, many industries are finding that the life cycle maintenance costs for their electronic equipment now exceeds their original capitol investment.

It is becoming apparent that the electronics maintenance process, like the design process, must be automated. For more than two decades, the subjects of automatic testing and fault diagnosis of electronic circuits have been of interest to researchers in the areas of circuits and systems [8, 25, 32, 33, 38]. Recently, with the rapidly increasing complexity and size of modern electronic systems, these subjects become more and

more important and critical.

The main problems in network testing are fault detection, fault location and fault prediction [3]. Fault detection refers to the discovery of something wrong in a circuit. Fault location concerns the identification of faults with components, functional modules, or subsystems, depending upon the requirement. Fault prediction alludes to the continuous monitoring of network responses so that any of the network elements which is about to fail can be identified. Fault diagnosis includes fault detection and location.

By a fault we mean, in general, any variation in component value, with respect to its nominal value which can cause the failure of the whole circuit. Two forms of faults are generally considered: catastrophic fault (hard fault), where the faulty element produces either a short circuit or an open circuit, and deviation fault (soft fault), where the faulty element deviates from its nominal value without reaching its extreme bounds. The soft faults are usually due to manufacturing tolerances, aging, or parasitic effects.

#### 1.1 DIFFICULTY OF ANALOG FAULT DIAGNOSIS

The research and theory development of digital testing started in the mid 1960's when the large-scale computers were readily available. The first commercialized test program did not become available until a decade later. Several digital automatic test program generation systems have been developed and widely used by both the military and industrial communities. From the mid 1970's, the test technology community began to face up to the analog test problem. Indeed, even in a predominantly digital world, analog systems were not disappearing. Analog systems were proving to be among the most unreliable and least readily tested of all electronic systems [26]. Presently, it is estimated that even though 80% of all boards are digital, 80% of the problems are analog.

Given our experience with the digital test problem and the analog computer-aided design problem, one might initially assume that the analog test problem could be resolved simply by integrating the tools and techniques of these two well-established fields. Unfortunately, the tremendous strides which have been made in digital test technology have not been paralleled by equal progress in the analog area. Fault diagnosis for analog circuits, in fact, has been found to be an extremely difficult problem to solve. The difficulty arises from a number of characteristics of the analog problem [3, 26] as listed below:

- (1) Tolerance: The actual values of analog components almost always deviate from the nominal values.

- (2) Modeling: An analog system has an infinite number of possible failures which may range from short circuit to open circuit. It leads the lack of good fault models for analog components such as the stuck-at-one and stuck-at-zero fault models which are widely accepted by the digital testing.

- (3) Measurement: An analog system usually has only a few nodes accessible for measurement and testing. Without breaking connection, it is difficult to measure currents.

- (4) Nonlinear nature: If a parameter value changes by a certain factor, the responses do not change by the same factor, i.e., the relationship between network responses and component characteristics is nonlinear, even though the circuit may be linear.

The nonlinear nature of the diagnosis problem can be observed from the following discussion. Consider a simple linear equation [26]:

$$Px = b ag{1.1}$$

$$y = Cx ag{1.2}$$

where b is the input-vector, y is the output-vector, x is the internal-vector, and P and C are compatible matrices. Suppose that P is changed to  $P + \Delta P$ , with b fixed, x will change to  $x + \Delta x$  accordingly, i.e.,

$$(P + \Delta P)(x + \Delta x) = b \tag{1.3}$$

Hence.

$$\Delta x = (P + \Delta P)^{-1} b - P^{-1} b \tag{1.4}$$

and

$$\Delta y = \phi(\Delta P; P, b, C) = C(P + \Delta P)^{-1}b - CP^{-1}b$$

(1.5)

The problem of solving for  $\Delta y$  from a given  $\Delta P$  is a well-known sensitivity problem. Conversely, solving for  $\Delta P$  from a given  $\Delta y$  is called the diagnosis problem. Because the above diagnosis function  $\phi$  may be highly nonlinear even for this simple linear equation, the inherent difficulty of the diagnosis problem is readily apparent.

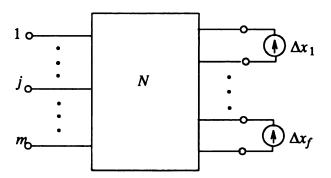

Let n be the size of the system and m be the number of test points, the dimensions of  $\Delta P$  and  $\Delta x$  are thus  $n \times n$  and  $m \times 1$ , respectively. An important feature in the diagnosis equation (1.5) is that  $m \ll n$ , that is, the number of equations is much less than the number of unknowns. This leads to the difficulty of solving the diagnosis equation.

#### 1.2 CLASSIFICATION AND COMPARISON

In order to solve fault diagnosis problems, various fault diagnosis algorithms have been proposed. These diagnosis algorithms can be roughly classified into two categories [36]:

- (1) Pre-Test Simulation Technique,

- (2) Post-Test Simulation Technique.

The pre-test simulation technique requires the simulation of various possible faults and the storage of the results as a dictionary [12]. In other words, for each possible  $\Delta P$ , corresponding  $\Delta y$  is calculated and stored in a dictionary. The faulty network responses measured are compared with the dictionary entries and the closest entry to the responses by a certain measure determines the possible fault. This technique is commonly employed in digital testing and is characterized by minimal on-line computational requirements. However, the high cost of analog circuit simulation coupled with the large number of potential fault models limits the applicability of this algorithm.

The post-test simulation technique is to solve the diagnosis equation for  $\Delta P$  by either increasing the number of equations or decreasing the number of unknowns. It can be further divided into simulation with sufficient measurement and simulation with failure bounds. The former is to increase the number of equations by obtaining sufficient measurements from various test points [34, 40, 42]. The latter is to decrease the number of unknowns by first assuming some components that are good and verifying them later [15, 43, 48, 49, 50].

Since sufficient measurements are needed in the former approach, multiple frequencies are applied and extremely expensive on-line computation is required to solve the high complexity of the nonlinear diagnosis equation. In contrast, the latter approach requires only a single frequency for the measurement and performs a simple on-line computation.

To evaluate a practical analog diagnosis algorithm, the following criteria are concerned [36]: computational requirements, number of test points and test vector employed, robustness to tolerance effects, availability of models, and the degree to which the algorithm is amenable to parallel processing. Based on the above criteria, the Post-Test Simulation with Failure Bounds is better than others in test application.

#### 1.3 MOTIVATION

The research of analog fault diagnosis in the past years has posed several important and challenging problems [26]. First, a component tolerance problem is concerned. Some proposed algorithms work well for the case that the nonfault components assume their nominal value exactly. However, the values of nonfault components in a practical circuit may deviate from their nominal value within a predefined tolerance. As a result, the fault components may not be properly located or even be detected. This motivates the study of an algorithm that can alleviate the error effect due to component tolerance.

With the rapidly increasing complexity and size of modern electronic systems, the ability to adequately design a diagnosable system is a prime requisite for rapid fault location. Some fault location and prediction algorithms can precisely locate and predict faulty components for small size networks. Due to the substantial increase of on-line computation for a large network, however, direct implementation of such algorithms for a practically large circuit network would be impractical. In practice, a faulty network generally has failures in a small portion of the network and the remaining parts are fault-free. Decomposing a large circuit network into several small subnetworks seems a very attractive idea, and, thus, serves as motivation to study a decomposition approach fault diagnosis and fault prediction algorithm for large analog circuit networks.

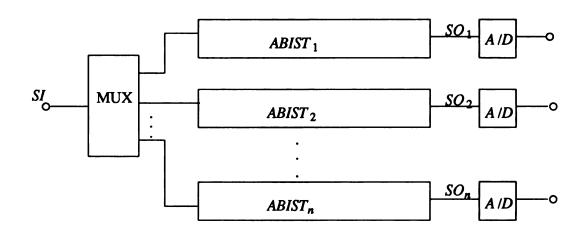

Usually, more test points can faster and more precisely locate faults, but, unfortunately, modern electronic systems are often multi-layered and/or coated, thereby limiting the accessibility of test points which are available at the externally accessible terminals of a printed circuit board. As the number of components in a unit increases, it is difficult to provide proportionately more I/O terminals. It limits the implementation of many fault diagnosis algorithms. In order to provide sufficiently more test points while still keeping low pin overhead for analog circuit testing, an analog Built-in Self-test structure (ABIST) is motivated.

Although an ABIST structure may provide as many test points as required for a circuit under test, the number of test points should not be indefinitely increased because of the placement and routing problems. Therefore, it is necessary to select an appropriate minimum set of test points that is sufficient to diagnose a circuit, as well as to develop an efficient test point selection algorithm.

#### 1.4 THESIS ORGANIZATION

This dissertation is organized as follows. In the next chapter, a fault location algorithm is presented. Basically, faults are located by checking the consistency or inconsistency of a set of linear equations. An Analog Automatic Test Program Generator (AATPG) software package is developed for fault diagnosis use. Some examples are presented which demonstrate that the proposed algorithms can precisely locate faults in analog circuits.

In Chapter 3, a fault prediction approach is proposed. For the case that the parameters of a potential faulty component are assumed to change gradually during each maintenance period, by continuously monitoring the responses of the network, the proposed fault prediction algorithm can predict whether or not any of the network components is about to fail. The predicted fault components are then replaced before the system actually fails.

In Chapter 4, a decomposition approach fault diagnosis and fault prediction algorithm for large circuit network is addressed. Basically, a large circuit network is decomposed into several small subnetworks. Also the error effect due to component tolerance in practical circuits can be alleviated and faults in large circuit networks can be precisely predicted. Also this approach can be extend for nonlinear circuits.

In Chapter 5, an analog Built-in Self-test (ABIST) structure is proposed. This structure not only provides more test points for analog circuit testing, but also acquires test data at various test points simultaneously. The detailed structure and its operations

are described, the simulation result and hardware implementation of the design are presented, and the VLSI implementation of the ABIST structure is discussed.

In Chapter 6, testability design principle is first outlined. Based on the design principle, the issues of diagnosability and test set generation are addressed.

Finally, the last chapter summarizes the work of this dissertation research and presents suggestions for related future research.

# **CHAPTER 2**

#### **FAULT DIAGNOSIS**

Fault diagnosis includes both fault detection and fault location. Fault detection is obviously a minimum requirement for fault location. When a circuit fails to a functional test, a diagnostic test is carried out to identify faulty components and to evaluate the faulty component values for studying the cause of failure. The information is fed back to the designer for further improvement. In this chapter, the emphasis is placed on the fault location of analog circuit networks. A diagnosis equation is derived first, followed by fault location and fault evaluation approach. An efficient fault location algorithm is presented and an AATPG that generates test programs for fault diagnosis use is discussed. Some examples are presented which demonstrate that the proposed algorithms can precisely locate faults in analog circuits.

#### 2.1 DIAGNOSIS EQUATION

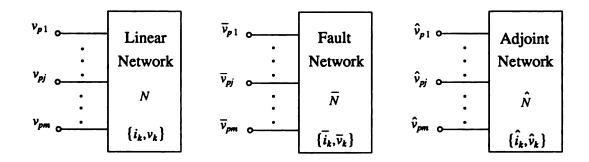

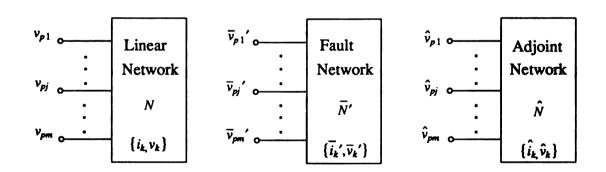

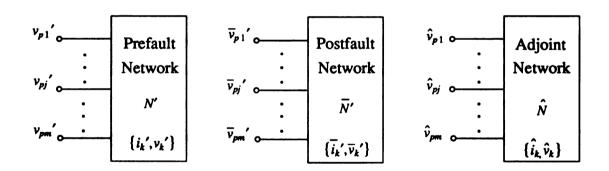

Based on Tellegen theorem [13] and the concept of the adjoint network [7], a diagnosis equation describing the relationship between the variation of component parameter and the change of voltage at accessible nodes is derived for a linear network. Consider a linear network, N, that has b internal branches and m accessible terminals. Let  $\overline{N}$  and  $\hat{N}$  be a faulty network and the adjoint network of N, respectively. The adjoint network  $\hat{N}$  is topologically identical to the original network N [7].

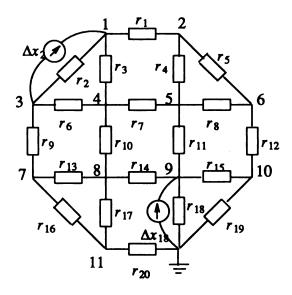

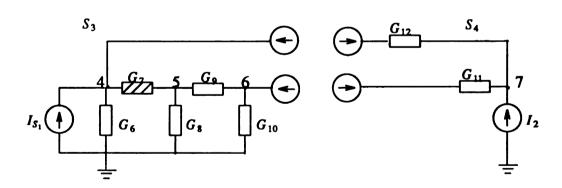

Figure 2.1 Circuit Networks.

Based on Tellegen theorem, we have

For N:

$$\sum_{k=1}^{b} (\hat{v}_k i_k - v_k \hat{i}_k) = -\sum_{j=1}^{m} (\hat{v}_{pj} i_{pj} - v_{pj} \hat{i}_{pj})$$

(2.1)

For

$$\overline{N}$$

:

$$\sum_{k=1}^{b} [\hat{v}_{k}(i_{k} + \Delta i_{k}) - (v_{k} + \Delta v_{k})\hat{i}_{k}] = -\sum_{j=1}^{m} [\hat{v}_{pj}(i_{pj} + \Delta i_{pj}) - (v_{pj} + \Delta v_{pj})\hat{i}_{pj}]$$

(2.2)

Subtracting Equation (2.2) from Equation (2.1), we get

$$\sum_{k=1}^{b} (\hat{v}_k \Delta i_k - \Delta v_k \hat{i}_k) = -\sum_{j=1}^{m} (\hat{v}_{pj} \Delta i_{pj} - \Delta v_{pj} \hat{i}_{pj})$$

(2.3)

With branch constraints

$$i_k = y_k v_k$$

,  $i_k + \Delta i_k = (y_k + \Delta y_k)(v_k + \Delta v_k)$ , and  $\hat{i}_k = y_k \hat{v}_k$ ,

Equation (2.3) yields

$$\sum_{k=1}^{b} \hat{v}_k \Delta x_k = \Delta p \tag{2.4}$$

where

$$\Delta x_k = \Delta y_k (v_k + \Delta v_k) = \Delta y_k \overline{v}_k, \tag{2.5}$$

$$\Delta p = \sum_{j=1}^{m} (\Delta v_{pj} \hat{i}_{pj} - \hat{v}_{pj} \Delta i_{pj})$$

(2.6)

A generalized form of Equation (2.4) can be expressed as

$$\sum_{k=1}^{b} w_k \Delta x_k = \Delta p \tag{2.7}$$

where  $w_k$  and  $\Delta x_k$  are listed in Table 2.1.

Table 2.1  $w_k$  and  $\Delta x_k$  of Different Types of Components

| Component type |      | w <sub>k</sub> | $\Delta x_k$                                            |

|----------------|------|----------------|---------------------------------------------------------|

| admittance     | у    | $\hat{v}_k$    | $\Delta y_k(v_k + \Delta v_k)$                          |

|                | cccs | $\hat{v}_k^h$  | $\Delta \beta_k (i_k^{\dot{i}} + \Delta i_k^{\dot{i}})$ |

| controlled     | vccs | $\hat{v}_k^h$  | $\Delta g_k(v_k^i + \Delta v_k^i)$                      |

| sources        | ccvs | $\hat{i}_k^h$  | $\Delta \gamma_k (i_k^j + \Delta i_k^j)$                |

|                | vcvs | îh<br>ik       | $\Delta\mu_k(v_k^i+\Delta v_k^i)$                       |

(Note: superscripts h and j represent controlled and controlling branches of a controlled source, respectively.)

Consider a matrix form for Equation (2.7)

$$W\Delta X = \Delta P \tag{2.8}$$

where

$$W = \begin{bmatrix} w_{11} & w_{12} & \cdots & w_{1b} \\ w_{21} & w_{22} & \cdots & w_{2b} \\ \vdots & \vdots & \ddots & \vdots \\ w_{m1} & w_{m2} & \cdots & w_{mb} \end{bmatrix}$$

$$\Delta X = [\Delta x_1 \ \Delta x_2 \cdots \Delta x_b]^T$$

$$\Delta P = [\Delta p_1 \Delta p_2 \cdots \Delta p_m]^T$$

Note that  $w_{ij} = \hat{v}_j^{(i)}$  represents the calculated voltage of the *j*th branch of the adjoint network when a unity current excitation is applied at the *i*th accessible terminal, and  $\Delta p_j = \Delta v_{pj} = \overline{v}_{pj} - v_{pj}$  is the voltage difference at the *j*-th terminals of both faulty and nonfaulty networks.

#### 2.2 FAULT LOCATION

Generally, the number of components in a circuit is always much more than the number of test points, i.e.,  $b \gg m$ . As a result, there is no unique nontrivial solution for (2.8). In practice, however, it is reasonable to assume that there are only a few faulty components in a reliably designed network. Of course, we do not know how many faulty components exist, or where they are located in advance.

Let f be the number of faulty components. Without loss of generality, we assume that the first f components are faulty and the others are nonfaulty, i.e.,  $\Delta y_k=0$ , or  $\Delta x_k=0$ , for  $k=f+1, \dots, b$ . Therefore, Equation (2.8) can be reduced as

$$W_f \Delta X_f = \Delta P \tag{2.9}$$

where

$$W_{f} = \begin{bmatrix} w_{11} & w_{12} & \cdots & w_{1f} \\ w_{21} & w_{22} & \cdots & w_{2f} \\ \vdots & \vdots & \ddots & \vdots \\ w_{m1} & w_{m2} & \cdots & w_{mf} \end{bmatrix}$$

$$\Delta X_f = [\Delta x_1 \ \Delta x_2 \cdots \Delta x_f]^T$$

Equation (2.9) has a unique nontrivial solution only if

$$rank[W_f \mid \Delta P] = rank[W_f] = f \tag{2.10}$$

The condition (2.10) determines the number of faulty components and also identifies the faulty components. The detailed fault location process is described in Algorithm I.

#### 2.3 FAULT EVALUATION

Once the faulty components are identified, we may evaluate the faulty component values to study the cause of the failures. Suppose that a matrix  $W_f$  of the corresponding faulty components satisfies condition (2.10), with the existence of the generalized inverse of  $W_f$ , Equation (2.9) yields

$$\Delta X_f = (W_f^T W_f)^{-1} W_f^T \Delta P \tag{2.11}$$

which gives the values of  $\Delta x_k$ , for  $k=1,2,\dots,f$ . The next step is to find all node voltages.

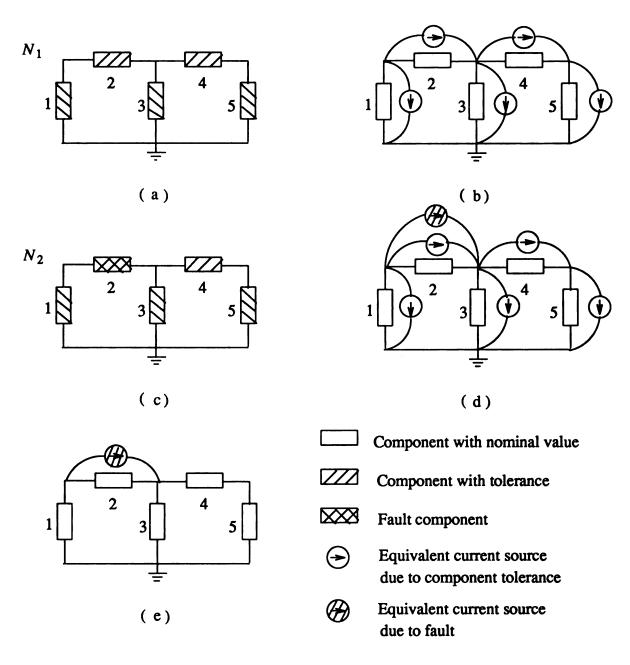

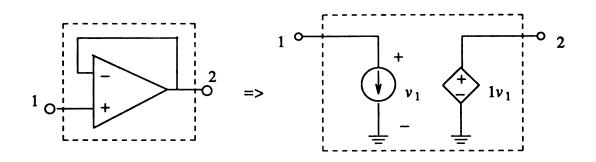

Suppose that the admittance of a faulty component is changed from y to  $y+\Delta y$ . This is equivalent to y connecting in parallel with  $\Delta y$ . According to the substitution theorem [13],  $\Delta y$  can be substituted by a current source  $\Delta x$ , which depends on the deviation  $\Delta y$  and its branch voltage, i.e.,  $\Delta x_k = \Delta y_k (v_k + \Delta v_k)$ . Similarly, the deviation of the controlled sources can be substituted by a source, referred to as *substituted source*, as illustrated in Table 2.2. Thus, a faulty network is equivalent to the corresponding non-faulty network N connecting with some substituted sources  $\Delta x_k$ , as shown in Figure 2.2.

Figure 2.2 Equivalent Faulty Network.

Table 2.2 Substituted Sources of Different Types of Components

| type | faulty components                                                                                                                                                                                                                            | substituted sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| у    | $ \begin{array}{c c} + & i_k + \Delta i_k \\ v_k + \Delta v_k & (y_k + \Delta y_k)(v_k + \Delta v_k) \\ - & 0 \end{array} $                                                                                                                  | $ \begin{array}{c c} + & i_k + \Delta i_k \\ \nu_k + \Delta \nu_k & y_k & \Delta y_k (\nu_k + \Delta \nu_k) \\ - & 0 \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| cccs | $+ \underbrace{\circ \overset{i_{k}^{h} + \Delta i_{k}^{h}}{\circ}}_{v_{k}^{h} + \Delta v_{k}^{h}} \underbrace{(\beta_{k} + \Delta \beta_{k})(v_{k}^{i} + \Delta v_{k}^{i})}_{(\beta_{k} + \Delta \beta_{k})(v_{k}^{i} + \Delta v_{k}^{i})}$ | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| vccs | $ \begin{array}{c c} + o i_k^h + \Delta i_k^h \\ v_k^h + \Delta v_k^h & \downarrow \\ - o & \downarrow \\ \end{array} $ $ \begin{array}{c c} (g_k + \Delta g_k)(v_k^l + \Delta v_k^l) \\ - o & \downarrow \end{array} $                      | $+ \underbrace{a_k^h + \Delta a_k^h}_{v_k^h + \Delta v_k^h} \underbrace{\psi}_{g_k} g_k \underbrace{\psi}_{\Delta g_k(v_k^i + \Delta v_k^i)}$ $- \underbrace{\psi}_{Q_k} g_k \underbrace{\psi}_{\Delta g_k(v_k^i + \Delta v_k^i)} g_k \psi$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ccvs | $ \begin{array}{c c} + & i_k^h + \Delta i_k^h \\ v_k^h + \Delta v_k^h & & \\ - & & \\ - & & \\ \end{array} $ $ \begin{array}{c} (\gamma_k + \Delta \gamma_k)(v_k^i + \Delta v_k^i) \\ - & & \\ \end{array} $                                 | $+ \circ \frac{i_k^h + \Delta i_k^h}{v_k^h + \Delta v_k^h} + \underbrace{-} \frac{\gamma_k}{\Delta \gamma_k (v_k^i + \Delta v_k^i)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| vcvs | $+ \underbrace{i_k^h + \Delta i_k^h}_{v_k^h + \Delta v_k^h} $ $- \underbrace{(\mu_k + \Delta \mu_k)(v_k^i + \Delta v_k^i)}_{-}$                                                                                                              | $+ \circ \stackrel{i_k^h + \Delta i_k^h}{ } \stackrel{\mu_k}{ $ |

For a nonfaulty network N the nodal equation is expressed as follows

$$[H] \begin{bmatrix} V_N \\ I_N \end{bmatrix} = [I_{sn}] \tag{2.12}$$

where H is the nodal admittance matrix,  $V_N$  is the node voltage vector,  $I_N$  is the current vector of the voltage controlled sources, and  $I_{sn}$  is the node current source vector. Similarly, the nodal equation of the faulty network of Figure 2.2 is expressed as

$$[H] \begin{bmatrix} \overline{V}_N \\ \overline{I}_N \end{bmatrix} = [I_{sn}] - [\Delta X_f] \tag{2.13}$$

where  $\overline{V}_N$  and  $\overline{I}_N$  are the node voltage and current vectors of the faulty network, where  $\Delta X_f$  is the substituted source vector. Since the matrix H, vectors  $I_{sn}$ , and  $\Delta X_f$  are all known, Equation (2.13) can be solved for the vector  $\overline{V}_N$  and  $\overline{I}_N$ . Once both  $\overline{V}_N$  and  $\overline{I}_N$  are computed, the faulty component deviation  $\Delta e_f$  can be evaluated by  $\Delta X_f$ .

#### 2.4 EQUIVALENT FAULT SETS

The number of faulty components and the faulty components can be determined by checking Equation (2.10). If a set of components satisfies the condition in Equation (2.10), the sets of components are referred to as *fault set candidates*. In practice, however, more than one candidate may be concluded. Moreover, only one candidate that contains all faulty components is the *actual fault set*, and the remaining candidates, referred to as *equivalent fault sets*, that contain some nonfaulty components, but they produce the same responses as the actual fault set at the accessible terminals. In other words,

$$rank[W_f | \Delta P] = rank[W_{f(act)} | \Delta P] = f$$

The existence of the equivalent fault sets is attributed to either the topological structure, or test points. The details are shown in the following properties.

#### **Property 2.1**

If the actual fault set contains a subset that consists of either

- a) l components in loop L which consists of l+1 components, or

- b) l components in cutset C which consists of l+1 components incident to an inaccessible node,

then an f-component-set formed by a combination of any l components of loop L or cutset C together with other f-l components of the actual fault set, is an equivalent fault set.

#### **Property 2.2**

If m-f+1 row dependence of  $W_f$  is consistent with row dependence of  $W_{f(act)}$ , and  $rank[W_f] = f$ , the f-component-set corresponding to  $W_f$  is an equivalent fault set.

The proofs of Properties 2.1 and 2.2 are shown in Appendix 1.

Recall that, in the fault location process, Equation (2.9) is used to estimate the number of faulty components and to evaluate the faulty component values. The underlying assumption for that process is  $\Delta x_k=0$ , for  $k=k+1, \dots, b$ , i.e., the components that are not in the fault set under processing, are faulty-free. The assumption is true only if the actual fault set is processed. Therefore, the evaluated values of the components in the actual fault set are virtually the same irrespective of the locations of the external excitations and the applied frequencies. However, the assumption is not true when the equivalent fault set is processed, because some  $\Delta x_k$ 's are not zeros. As a result, with the application of different frequencies or different locations of the excitations, the estimated values of the components in equivalent fault sets will be different. Based on this concept, we may identify the actual fault set either by applying a different frequency, or by relocating the external excitation for fault diagnosis use. In other words, if more than one fault sets are obtained in the fault location process, properly relocating the excitation is needed. From the component values estimated under two different excitations, we should be able to identify the actual fault set.

#### 2.5 SOFTWARE IMPLEMENTATION

The fault location algorithm discussed above is summarized in Algorithm I.

#### Algorithm I.

(off-line phase)

- Step 1. Input the network topology and its component nominal values to construct the nodal admittance matrix H.

- Step 2. Apply a unit current excitation to the *i*th accessible terminal of an adjoint network. Construct the matrix W by the computer branch voltages  $\hat{v}_{j}^{(i)}$   $(j=1,2,\dots,b,\ i=1,2,\dots,m)$  of adjoint networks

- Step 3. Calculate the voltage V at the accessible terminals of the fault-free network N.

(on-line phase)

- Step 1. Obtain the voltages  $\overline{V}$  measured at the accessible terminals of a faulty network, (either from the ATE or by simulation.)

- Step 2. Load the data generated in the off-line phase and initialize r=1.

- Step 3. Repeat

- 3.1. pick up a combination of r columns of matrix W to form  $W_r$ ;

- 3.2. Check if  $rank[W_r | \Delta P] = rank[W_r] = r$ ;

- 3.3.1. Calculate the following equations for the actual component value  $e_k$ ;

(a).

$$\Delta X_f = (W_f^T W_f)^{-1} W_f^T \Delta P$$

(b).

$$[H][\bar{V}_n] = [I_{sn}] - [\Delta X_f]$$

(c).

$$\Delta y_k(\overline{v}_k) = \Delta x_k$$

, where  $k=1,2,\cdots,f$

(d).

$$e_k = y_k + \Delta y_k$$

, where  $k = 1, 2, \dots, f$

- 3.3.2. If  $e_k > 0$ , record this fault set; *Until* all combinations are applied.

- Step 4. If no fault set is identified, then r=r+1, and Go To Step 3.

- Step 5. If only one possible fault set is concluded, then faulty elements are located, and the process is terminated.

Step 6. (more than one possible fault sets)

Apply the second excited source, and input the voltages measured at the accessible terminals of a faulty network.

#### Repeat

- 6.1. Take a fault set at a time;

- 6.2. Calculate the equations (a) to (d) of step 3.3.1 for  $e_k$ ;

- 6.3. If  $e_k < 0$ , eliminate this set;

Until all fault sets are applied.

Step 7. Compare two  $e_k$ 's obtained from Steps 3.3 and 6.2 for each fault set. If they are equal, then this set is the actual fault set.

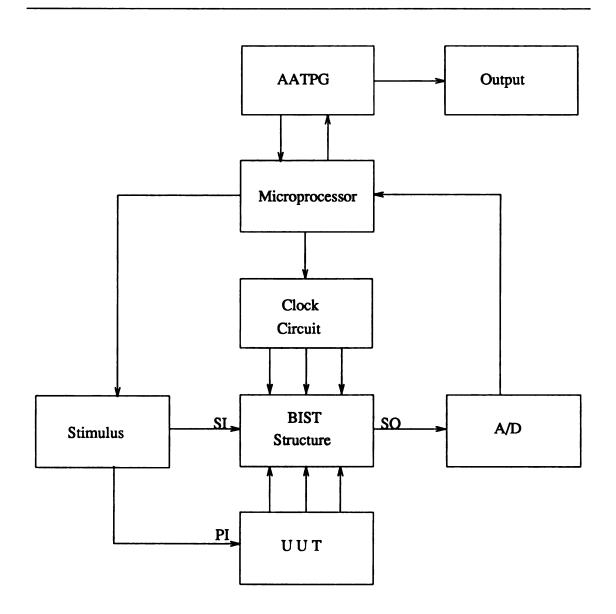

An Analog Automatic Test Program Generator (AATPG) that generates test programs for fault diagnosis use has been developed based on Algorithm I. The process is divided into two phases: off-line and on-line [23].

The off-line phase, corresponding to the test system design stage, is used by the test system designer to input nominal network specifications and generate a data base which is used by the on-line phase. The input requirements in the test program generation are circuit description, input frequency, and accessible test terminals. During the on-line phase, the data generated by off-line phase (the admittance matrix H, the matrix W, and the accessible terminal voltage V) are loaded. The test data are acquired either by fault simulation or from ATE (Automatic Test Equipment). With the measured voltages, Algorithm I is carried out to identify the faulty components and evaluate the component values.

In both off-line and on-line phases, AATPG provides user-oriented interfaces to simplify the process of generating a new test program. The AATPG has been implemented on VAX 8600 (ULTRIX) in Fortran and C [23].

#### 2.6 EXAMPLES

In order to demonstrate the effectiveness of the proposed fault location algorithm, two examples are given.

#### Example 2.1

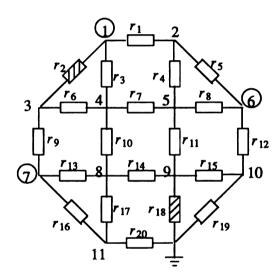

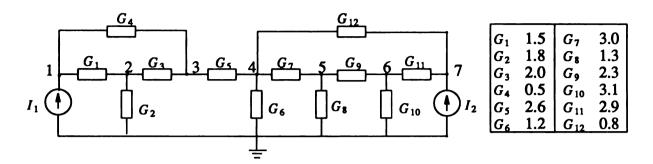

Consider a linear resistive network, as shown in Figure 2.3, consisting of all unity resistances. Suppose that nodes 1, 6 and 7 are taken as the test points.

Figure 2.3 The Resistor Network in Example 2.1.

In the off-line phase, the W-matrix and the voltages that are measured at the test points when the network is fault-free, must be established before the test is conducted. According to the schematic circuit diagram of Figure 2.3, the H-matrix is generated as follows

$$H = \begin{bmatrix} 3 & -1 & -1 & -1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ -1 & 3 & 0 & 0 & -1 & -1 & 0 & 0 & 0 & 0 & 0 & 0 \\ -1 & 0 & 3 & -1 & 0 & 0 & -1 & 0 & 0 & 0 & 0 & 0 \\ -1 & 0 & -1 & 4 & -1 & 0 & 0 & -1 & 0 & 0 & 0 & 0 \\ 0 & -1 & 0 & -1 & 4 & -1 & 0 & 0 & -1 & 0 & 0 & 0 \\ 0 & -1 & 0 & 0 & -1 & 3 & 0 & 0 & 0 & -1 & 0 & 0 \\ 0 & 0 & -1 & 0 & 0 & 0 & 3 & -1 & 0 & 0 & -1 & 0 \\ 0 & 0 & 0 & -1 & 0 & 0 & -1 & 4 & -1 & 0 & -1 & 0 \\ 0 & 0 & 0 & 0 & 0 & -1 & 0 & 0 & -1 & 3 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & -1 & -1 & 0 & 0 & 3 & 0 & 0 \end{bmatrix}$$

Taking the *H*-matrix, the *W*-matrix is constructed as follows. We first apply a unity excitation current to the node 1 of the adjoint network  $\hat{N}$ , and then calculate the branch voltages of the network  $\hat{N}$ , which is listed in the first column of *W*-matrix in Table 2.3. The remaining columns of the *W*-matrix are formed in a similar way. The computed voltage vector V for the nominal network is shown in the second column of Table 2.4.

When the test is being conducted, the measured test data may be obtained from an automatic test equipment (ATE). In this moment, however, the ATE is not available and thus a set of simulated test data is employed. In this example, we assume that the components 2 and 18 are faulty with  $r_2$ =0.4 $\Omega$  and  $r_{18}$ =1.5 $\Omega$ . Column 3 and 4 of Table 2.4 list the measured test data  $\overline{V}$  and the voltage difference,  $\Delta P = V - \overline{V}$ , respectively.

Table 2.3 W Matrix of Example 2.1

| element | (1)                 | (6)                  | (7)                  |

|---------|---------------------|----------------------|----------------------|

| 1       | 3.5000 <i>e</i> –01 | -1.3750e -01         | 1.1250e –01          |

| 2       | 3.0000e -01         | 8.3333 <i>e</i> –02  | -1.1667 <i>e</i> -01 |

| 3       | 3.5000 <i>e</i> –01 | 5.4167 <i>e</i> –02  | 4.1667 <i>e</i> –03  |

| 4       | 1.5000e –01         | 7.9167e <b>–</b> 02  | 2.9167 <i>e</i> –02  |

| 5       | 2.0000 <i>e</i> –01 | −2.1667 <i>e</i> −01 | 8.3333 <i>e</i> –02  |

| 6       | 5.0000e-02          | −2.9167 <i>e</i> −02 | 1.2083 <i>e</i> –01  |

| 7       | 1.5000 <i>e</i> –01 | -1.1250e -01         | 1.3750e –01          |

| 8       | 5.0000e –02         | −2.9583 <i>e</i> −01 | 5.4167e-02           |

| 9       | 2.5000 <i>e</i> –01 | 1.1250e –01          | -2.3750e -01         |

| 10      | 2.5000 <i>e</i> –01 | 1.3750e –01          | −1.2500 <i>e</i> −02 |

| 11      | 2.5000 <i>e</i> –01 | 2.6250e –01          | 1.1250e –01          |

| 12      | 2.5000 <i>e</i> –01 | 4.8750e –01          | 1.3750e –01          |

| 13      | 5.0000e –02         | -4.1666 <i>e</i> -03 | 3.4583 <i>e</i> –01  |

| 14      | 1.5000 <i>e</i> –01 | 1.2500 <i>e</i> –02  | 2.6250e –01          |

| 15      | 5.0000e –02         | −7.0833 <i>e</i> −02 | 7.9167 <i>e</i> – 02 |

| 16      | 2.0000 <i>e</i> –01 | 1.1667 <i>e</i> –01  | 4.1667 <i>e</i> –01  |

| 17      | 1.5000e -01         | 1.2083 <i>e</i> –01  | 7.0833 <i>e</i> –02  |

| 18      | 3.5000 <i>e</i> –01 | 3.4583 <i>e</i> –01  | 2.9583 <i>e</i> –01  |

| 19      | 3.0000e –01         | 4.1667 <i>e</i> –01  | 2.1667 <i>e</i> –01  |

| 20      | 3.5000 <i>e</i> –01 | 2.3750e –01          | 4.8750e –01          |

|  | Node | V                   | $ar{v}$             | ΔΡ                  |

|--|------|---------------------|---------------------|---------------------|

|  | 1    | 1.1000e+00          | 1.0750e+00          | -2.5026e -02        |

|  | 6    | 5.5000 <i>e</i> –01 | 5.7751 <i>e</i> –01 | 2.7505 <i>e</i> –02 |

|  | 7    | 5.5000e -01         | 6.1960e –01         | 6.9599 <i>e</i> –02 |

Table 2.4 Simulation Data of Example 2.1

Since we do not know how many faulty components exist, we will first check the number of faulty components. Specifically, we start with f=1 for Equation (2.10) and find that the following matrix satisfies Equation (2.10) when f=2,

$$[W_f, \Delta P] = \begin{bmatrix} 2 & 18 & \Delta P \\ 3.0000e - 01 & 3.5000e - 01 & -2.5026e - 02 \\ 8.3333e - 02 & 3.4583e - 01 & 2.7505e - 02 \\ 7 & -1.1667e - 01 & 2.9583e - 01 & 6.9599e - 02 \end{bmatrix}$$

Since the fault set {2,18} is the only candidate, the components 2 and 18 are identified as faulty.

The values of the faulty component 2 and 18 can be computed as follows. First, Equation (2.11) is used to calculate  $\Delta X_f$ , which is listed in the second column of Table 2.5. Then, two substituted current sources  $\Delta X_f$ , i.e.,  $\Delta x_2$  and  $\Delta x_{18}$ , are connected in parallel with corresponding components 2 and 18, as shown as Figure 2.4. The Vectors  $\overline{V}_N$  and  $\overline{I}_N$  of the substituted network are computed from Equation (2.13). In this example, the branch voltage vector  $\overline{V}_N$  for components 2 and 18 are listed in the third column of Table 2.5. The computed branch voltages are used to evaluate the component deviation, i.e.,  $\Delta y = \Delta x_k/\overline{v}_k$ , k=2,18. Finally, the faulty component values are determined by  $e_k = y_k + \Delta y_k$ , or  $r_2 = 1/e_k = 0.4$  and  $r_{18} = 1.5$ .

Table 2.5 Component Evaluation

| Component | $\Delta X_f$ | branch voltage | $\Delta y_k$ | $r_k = \frac{1}{e_k}$ |

|-----------|--------------|----------------|--------------|-----------------------|

| 2 18      | 2.4512e-01   | 1.6341e-01     | 1.5000e+00   | 4.0000e-01            |

|           | -1.3860e-01  | 4.1579e-01     | -3.3334e-01  | 1.5000e+00            |

Figure 2.4 Equivalent Faulty Network in Figure 2.3.

### Example 2.2

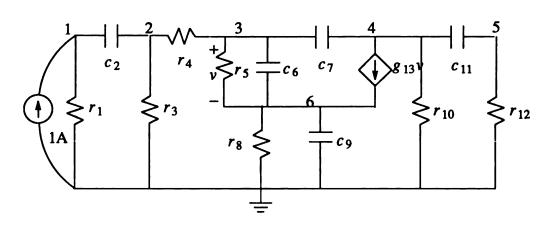

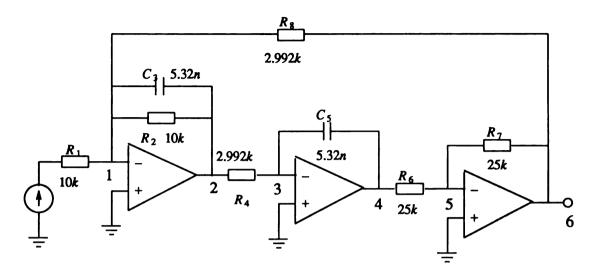

Consider a linear active circuit with a controlled source, as shown in Figure 2.5. The component values are listed in Table 2.6, and the nodes 1, 2, 4 and 5 are taken as the test points.

Figure 2.5 An Active Circuit.

Table 2.6 Component Values of Example 2.2

| Component      | Value | Component       | Value |

|----------------|-------|-----------------|-------|

| $r_1$          | 20Ω   | r <sub>8</sub>  | 30Ω   |

| c 2            | 20μF  | <i>C</i> 9      | 10μF  |

| $r_3$          | 75Ω   | r <sub>10</sub> | 10Ω   |

| r <sub>4</sub> | 10Ω   | c 11            | 20μF  |

| r <sub>5</sub> | 40Ω   | r <sub>12</sub> | 10Ω   |

| c 6            | 15μF  | <i>g</i> 13     | 10    |

| c 7            | 25μF  |                 |       |

Table 2.7 W Matrix of Example 2.2

| element | (1)          | (2)          | (4)          | (5)          |

|---------|--------------|--------------|--------------|--------------|

| 1       | ( 6.1229e+00 | ( 6.1229e+00 | (1.2229e-03  | ( 1.2357e-03 |

|         | -1.3835e-02) | -8.3133e-03) | -1.6108e-02) | -1.6107e-02) |

| 2       | (5.7220e-06  | (3.3379e-06  | ( 6.4091e-06 | ( 6.4089e-06 |

|         | -5.5215e-03) | 2.4362e-03)  | 4.8615e-07)  | 4.9174e-07)  |

| 3       | ( 6.1229e+00 | ( 6.1229e+00 | (1.2164e-03  | (1.2293e-03  |

|         | -8.3133e-03) | -1.0750e-02) | -1.6109e-02) | -1.6108e-02) |

| 4       | ( 6.1221e+00 | ( 6.1221e+00 | (-7.7410e-04 | (-7.8222e-04 |

|         | 7.8425e-03)  | 5.4066e-03)  | 1.0202e-02)  | 1.0201e-02)  |

| 5       | (7.2482e-04  | (7.2227e-04  | ( 1.8619e-03 | ( 1.8702e-03 |

|         | -6.4148e-03) | -6.4151e-03) | -1.0403e-02) | -1.0401e-02) |

| 6       | (7.2482e-04  | (7.2227e-04  | ( 1.8619e-03 | ( 1.8702e-03 |

|         | -6.4148e-03) | -6.4151e-03) | -1.0403e-02) | -1.0401e-02) |

| 7       | (-2.0568e-05 | (-2.0569e-05 | (-4.1600e-05 | (-4.6664e-05 |

|         | -1.0487e-06) | -1.0394e-06) | 6.3636e-03)  | 6.3636e-03)  |

| 8       | ( 6.9070e-05 | ( 6.5195e-05 | ( 1.2868e-04 | (1.4134e-04  |

|         | -9.7410e-03) | -9.7411e-03) | -1.5908e-02) | -1.5908e-02) |

| 9       | ( 6.9070e-05 | ( 6.5195e-05 | ( 1.2868e-04 | (1.4134e-04  |

|         | -9.7410e-03) | -9.7411e-03) | -1.5908e-02) | -1.5908e-02) |

| 10      | ( 8.1446e-04 | ( 8.0803e-04 | ( 2.0322e-03 | ( 2.0582e-03 |

|         | -1.6155e-02) | -1.6155e-02) | -3.2674e-02) | -3.2672e-02) |

| 11      | (-1.2855e-05 | (-1.2855e-05 | (-2.6000e-05 | (-3.2331e-05 |

|         | -6.5751e-07) | -6.5379e-07) | -1.6354e-06) | 7.9561e-03)  |

| 12      | ( 8.2731e-04 | ( 8.2089e-04 | ( 2.0582e-03 | ( 2.0905e-03 |

|         | -1.6154e-02) | -1.6154e-02) | -3.2672e-02) | -4.0628e-02) |

| 13      | (7.4539e-04  | (7.4284e-04  | (1.9035e-03  | ( 1.9168e-03 |

|         | -6.4137e-03) | -6.4140e-03) | -1.6766e-02) | -1.6765e-02) |

Similar to Example 2.1, the W-matrix is computed as shown in Table 2.7, and the voltage vector V is listed in the second column of Table 2.8. If we assume that the components  $r_4$  and  $g_{13}$  are faulty with  $r_4$ =20 $\Omega$  and  $g_{13}$ =50, the faulty components are located in accordance with the measured voltage vector  $\overline{V}$  and  $\Delta P$  shown in Table 2.8.

Table 2.8 Simulation Data of Example 2.2

| Node | V                             | $\bar{v}$                  | ΔΡ                        |

|------|-------------------------------|----------------------------|---------------------------|

| 1    | (6.1229e+00,-1.3835e-02)      | (8.8244e+00,-7.4149e-03)   | (2.7015e+00,6.4199e-03)   |

| 2    | (6.1229e+00,-8.3133e-03)      | (8.8244e+00,-2.9683e-03)   | (2.7015e+00,5.3449e-03)   |

| 4    | (1.2229e - 03, -1.6108e - 02) | (3.1670e -03,-1.0020e -02) | (1.9442e -03,6.0881e -03) |

| 5    | (1.2357e-03,-1.6107e-02)      | (3.1750e-03,-1.0018e-02)   | (1.9393e-03,6.0896e-03)   |

Table 2.9 illustrates all fault set candidates that satisfy Equation (2.10). In order to precisely identify the actual fault set, the unity excitation current is relocated at node 5. Table 2.9 lists the evaluated component values for these two excitations. From the differences listed in Table 2.9, the actual fault set  $\{4,13\}$  is identified, i.e., the components 4 and 13 are known as faulty with  $r_4=1/0.05=20$ , and  $g_{13}=50$ , which are consistent with the given simulated fault values.

Table 2.9 Simulation Results of Example 2.2

| Fault  | Fault values evaluated                                    |                                                            |             |  |  |  |

|--------|-----------------------------------------------------------|------------------------------------------------------------|-------------|--|--|--|

| set    | Excitation at node 1                                      | Excitation at node 5                                       | Difference  |  |  |  |

| 3 4    | (1.9341e-02,-1.0381e-02)<br>(4.4008e-02, 1.0394e-02)      | (2.0956e+01, 7.5264e+00)<br>(1.8184e+01, 3.0937e+00)       | 9.9934e –01 |  |  |  |

| 4<br>5 | (5.0006e-02, 2.47396e-06)<br>(5.8136e+01,-1.8496e+01)     | (5.0627e -02, -8.8866e -03)<br>(5.8135e +01, -1.8504e +01) | 1.7336e-01  |  |  |  |

| 4 6    | (5.0006e -02, 2.4740e -06)<br>(9.2486e +00, 1.2056e +01)  | (5.0627e -02, -8.8866e -03)<br>(9.2485e +00, 1.2055e +01)  | 1.7336e –01 |  |  |  |

| 4 7    | (4.9992e -02, -5.5611e -06)<br>(1.0575e +00, 2.2879e +00) | (4.2446e –02, 1.0026e –02)<br>(2.0806e +01, 1.2509e +01)   | 9.1597e-01  |  |  |  |

| 4 8    | (5.0005e-02, 3.3373e-06)<br>(2.9067e+01, 5.6407e+00)      | (5.2221e-02,-8.8738e-03)<br>(2.9068e+01, 5.6390e+00)       | 1.7273e-01  |  |  |  |

| 4 9    | (5.0005e-02, 3.3373e-06)<br>(4.6209e+00, 1.0898e+01)      | (5.2221e-02,-8.8738e-03)<br>(4.6211e+00, 1.0897e+01)       | 1.7273e-01  |  |  |  |

| 4 10   | (5.0003e -02, 1.4904e -06)<br>(7.9698e +00, 1.9130e +00)  | (5.1185e -02, -4.1434e -03)<br>(6.2489e +00, 1.9185e +00)  | 2.0996e-01  |  |  |  |

| 4 13   | (5.0000e-02, 1.8072e-10)<br>(5.000e+01, 3.48859e-03)      | (5.0000e-02, 3.7433e-08)<br>(5.000e+01,-1.5038e-04)        | 8.2385e-05  |  |  |  |

## **CHAPTER 3**

## **FAULT PREDICTION**

For the case that the nonfaulty components assume their nominal value exactly, referred to as the *ideal case*, the proposed fault location algorithm can precisely locate faults. On the other hand, for the *practical case* that the nonfaulty component values may deviate from their nominal values with a predefined component tolerance, the algorithm still can locate the most of the faults. In some situations, however, the deviation may affect the determination of the system status even though all components are fault-free. This accumulation is referred to as the *error effect*. In the ideal case, the error effect is merely the truncation error of the computer. In the practical case, however, the error effect highly depends on the predefined deviation percentage of the nonfaulty components.

Our study has found that if the predefined deviation percentage is within 5%, the proposal location algorithm can confidently locate those (soft) faulty components whose values are deviated, at least, 50% of the nominals. When the fault deviation is less than 50%, however, it is really difficult to determine whether the system failed. Moreover, if we assume that the parameters of a potential faulty component are changed gradually, the faulty components can then be detected after system failed. For a reliable design, the potential faulty components should be identified as soon as possible and replaced before the system fails. Therefore, a fault prediction algorithm is motivated.