This is to certify that the

dissertation entitled

PARALLEL COMPUTATION MODELS: REPRESENTATION, ANALYSIS AND APPLICATIONS

presented by

Xian-He SUN

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Computer Science

Major professor

Date 11/2/90

MSU is an Affirmative Action/Equal Opportunity Institution

0-12771

| DATE DUE | DATE DUE | DATE DUE |

|----------|----------|----------|

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due.

> ISU Is An Affirmative Action/Equal Opportunity Institution c:\circ\dimedus.pm3-p.1

> > \_

## PARALLEL COMPUTATION MODELS: REPRESENTATION, ANALYSIS AND APPLICATIONS

By

Xian-He Sun

### A DISSERTATION

Submitted to Michigan State University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

Department of Computer Science

1990

#### ABSTRACT

## PARALLEL COMPUTATION MODELS: REPRESENTATION, ANALYSIS AND APPLICATIONS

#### By

#### Xian-He Sun

Although there are various multiprocessors available, both software support and algorithm development for these machines are far behind their hardware counterpart. This is especially true for multicomputers in which each processor has its own local memory. A new concept, *compute-exchange computation*, is proposed for efficient parallel algorithm design in multicomputers. Based on this new concept, the most frequently used scientific and engineering applications can be describled by a simple structured representation. Structured design and rethinking, therefore, become possible. The basic building blocks of these structures, called parallel computation models, are identified and studied. A performance metric of parallel processing, *parallel speedup*, is carefully examined. A new model of speedup is presented which considers the memory capacity as an influential factor and provides the quantum of the tradeoff between time and space.

These research results are useful in many areas of computer science. The dissertation focuses on two areas: efficient algorithm design and performance prediction. Examples chosen from real applications will be used in both areas to illustrate the concept and usefulness of the computation models. The applications used for efficient algorithm design are *solving large scale tridiagonal systems* and *solving electrical power flow problems*. Several novel algorithms are developed for these two applications based on combinations of computation models. Implementation results confirm that these algorithms are competitive with any existing algorithm in the field. ©Copyright By Xian-He Sun .

•

.

1990

Dedicated to my parents Yu Lin and Chang-Xiang Sun and to my family.

•

٠

iv

#### ACKNOWLEDGMENTS

I would like to express my sincere appreciation to all of the faculty members who have helped and contributed to make this work a reality. This includes Professor Lionel M. Ni, my thesis advisor, for his support, guidance and inspiration, and Professors Richard Enbody, Moon Jung Chung, and Richard Hill for their insightful comments and serving in my Ph.D. committee, and Professors Nabil Kamel, Abdol Esfahanian and Fathi Salam for their encouragement.

I would like to acknowledge all of my fellow students who have given me help and friendship during my stay at MSU. In particular, I wish to thank Dr. Chung-Ta King, Jayashree Ramanathan, Dongyul Ra, Paul Wolberg, Xian-La Lin, and Honda Shing, for their help and valuable discussions, and David Robinson, Dr. Shixiong Guo and Ten Hwan Tzen for their cooperation and wonderful work.

I am very grateful to my parents and parents-in-law for their years support, concern and understanding. I am indebted to my wife Hong Zhang-Sun for her constant encouragement, assistance and care during the course of my graduate studies.

This research has been supported in part by National Science Foundation under grant ECS-88-14027.

## **Table of Contents**

| Li | st of       | Table                           | 8                                             |    |    |   |           | viii |

|----|-------------|---------------------------------|-----------------------------------------------|----|----|---|-----------|------|

| Li | st of       | Figur                           | es                                            |    |    |   |           | ix   |

| 1  | INJ         | ROD                             | UCTION                                        |    |    |   |           | 1    |

|    | 1.1         | Multic                          | computers                                     |    | •  | • | •         | 2    |

|    | 1. <b>2</b> | Parall                          | el Algorithm Design Considerations            |    | •  |   | •         | 3    |

|    |             | 1.2.1                           | Sources of Degradation                        |    | •  | • | •         | 4    |

|    |             | 1.2.2                           | Algorithm Characteristics                     |    | •  | • | •         | 6    |

|    | 1.3         | Motiv                           | ation and Problem Statement                   |    | •  | • | •         | 8    |

|    | 1.4         | Thesis                          | organization                                  | •• | •  | • | •         | 10   |

| 2  | PE          | RFOR                            | MANCE METRIC OF PARALLEL ALGORITHMS           |    |    |   |           | 12   |

|    | 2.1         | Prelin                          | ninary                                        |    | •  | • | •         | 13   |

|    | 2.2         | Model                           | s of Speedup                                  |    | •  | • |           | 17   |

|    | 2.3         | Simpli                          | ified Models of Speedup                       |    |    | • |           | 19   |

|    | 2.4         | Comp                            | arison Study                                  |    | •  | • | •         | 26   |

| 3  | PAI         | RALLI                           | EL COMPUTATION MODELS FOR SCIENTIFIC CO       | M  | [P | Ū | <b>T-</b> |      |

|    | INC         | r<br>F                          |                                               |    |    |   |           | 29   |

|    | 3.1         | Struct                          | ured Representation                           |    | •  |   | •         | 30   |

|    | 3.2         | 3.2 Parallel Computation Models |                                               | 36 |    |   |           |      |

|    |             | <b>3.2</b> .1                   | Local Computation Model                       |    | •  | • | •         | 38   |

|    |             | 3.2.2                           | Global-Exchange Computation Model             |    | •  |   |           | 39   |

|    |             | 3.2.3                           | Compute-Aggregate-Broadcast Computation Model |    | •  | • | •         | 39   |

|    |             | 3.2.4                           | Divide-and-Conquer Computation Model          |    |    | • | •         | 40   |

|    |             | 3.2.5                           | Domain Decomposition Model                    |    | •  | • | •         | 44   |

|    |             | 3.2.6                           | Pipeline (Ring) Computation Model             |    | •  | • | •         | 45   |

|    |            | 3.2.7 Recursive Doubling Computation Model       | 46  |

|----|------------|--------------------------------------------------|-----|

|    | 3.3        | Application Considerations                       | 49  |

| 4  | AP         | PLICATION-DRIVEN ALGORITHM DESIGN                | 52  |

|    | 4.1        | Preliminary                                      | 53  |

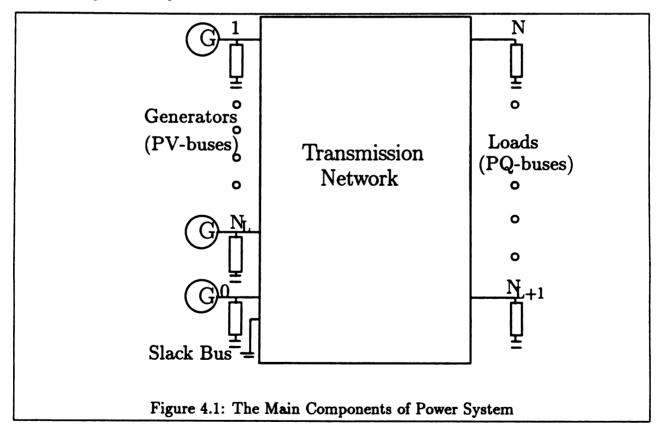

|    | 4.2        | Power Flow Application                           | 54  |

|    | 4.3        | Homotopy Method                                  | 56  |

|    | 4.4        | Implementation Issues and Results                | 58  |

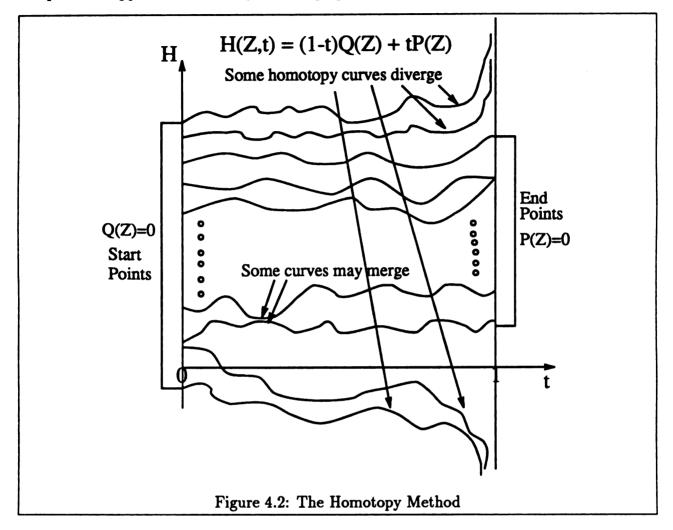

| 5  | AR         | CHITECTURE-DRIVEN ALGORITHM DESIGN               | 64  |

|    | 5.1        | Linear Tridiagonal Solvers                       | 65  |

|    |            | 5.1.1 The LU Decomposition Method                | 65  |

|    |            | 5.1.2 The Parallel Prefix Method                 | 66  |

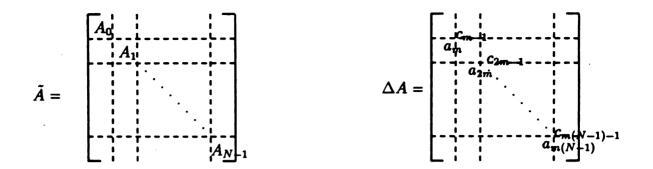

|    |            | 5.1.3 A Novel Matrix Partitioning Technique      | 67  |

|    | 5.2        | A Compute-Aggregate-Broadcast Computation Solver | 70  |

|    | <b>5.3</b> | A Global-Exchange Computation Model              | 73  |

|    | 5.4        | A Solver With More Than One Computation Model    | 75  |

|    | 5.5        | Comparison and Experimental Results              | 77  |

| 6  | PR         | EDICTION OF PERFORMANCE                          | 81  |

|    | 6.1        | Performance Formulations                         | 82  |

|    | 6.2        | Structured Prediction                            | 87  |

|    | 6.3        | The Influence of Problem Size on Speedup         | 90  |

| 7  | CO         | NCLUSION AND FUTURE RESEARCH                     | 97  |

|    | 7.1        | Summary and Major Contributions                  | 97  |

|    | 7.2        | Future Research Directions                       | 100 |

| Bi | bliog      | graphy                                           | 103 |

## List of Tables

# List of Figures

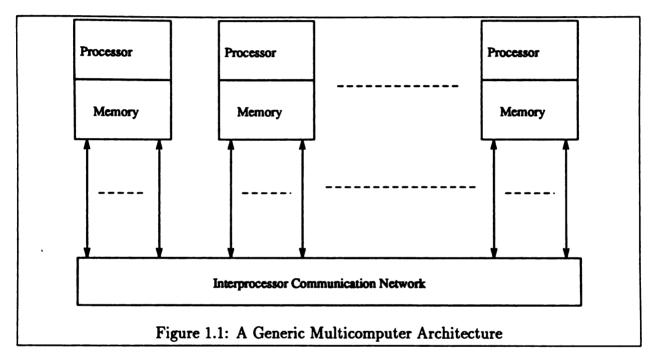

| 1.1  | A Generic Multicomputer Architecture              | 3  |

|------|---------------------------------------------------|----|

| 2.1  | Parallelism Profile of an Application             | 14 |

| 2.2  | Shape of the Application                          | 15 |

| 2.3  | Amdahl's Law                                      | 20 |

| 2.4  | Gustafson's Scaled Speedup                        | 21 |

| 2.5  | Simplified Memory-Bounded Scaled Speedup          | 22 |

| 2.6  | Matrix Multiplication with Local Computation      | 24 |

| 2.7  | Matrix Multiplication with Global Computation     | 24 |

| 2.8  | Amdahl's law, Gustafson's speedup and SMB speedup | 27 |

| 3.1  | Compute-Exchange Computation                      | 30 |

| 3.2  | Multicast Data Exchange                           | 32 |

| 3.3  | Conjunctive Data Exchange                         | 33 |

| 3.4  | Partitioning of Graphs                            | 34 |

| 3.5  | FFT (Butterfly) Computation                       | 35 |

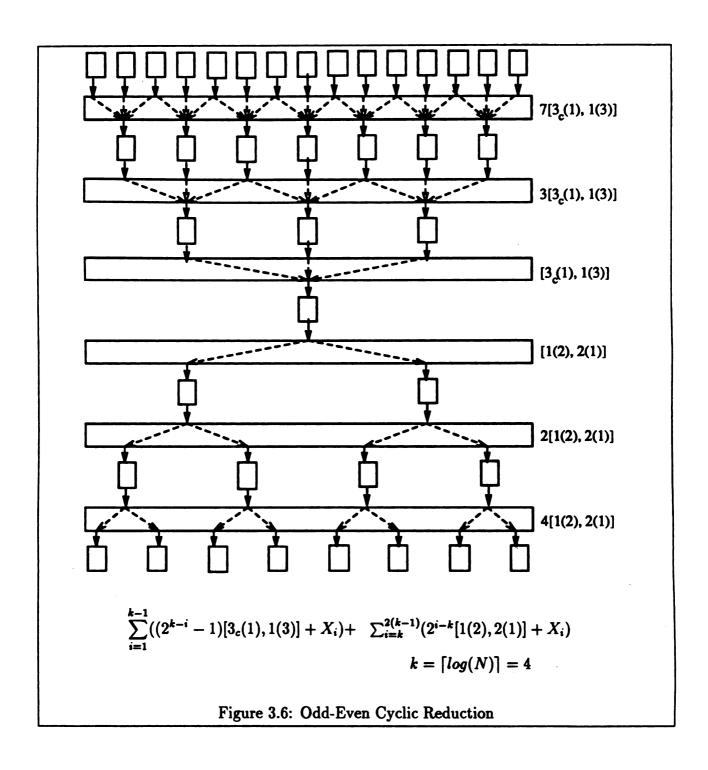

| 3.6  | Odd-Even Cyclic Reduction                         | 37 |

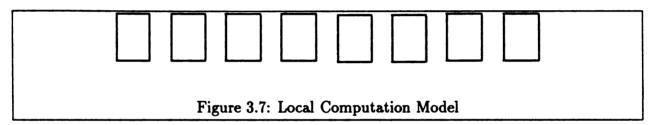

| 3.7  | Local Computation Model                           | 38 |

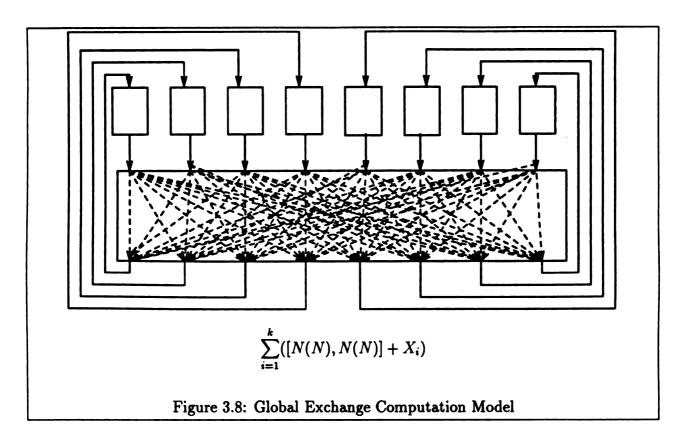

| 3.8  | Global Exchange Computation Model                 | 40 |

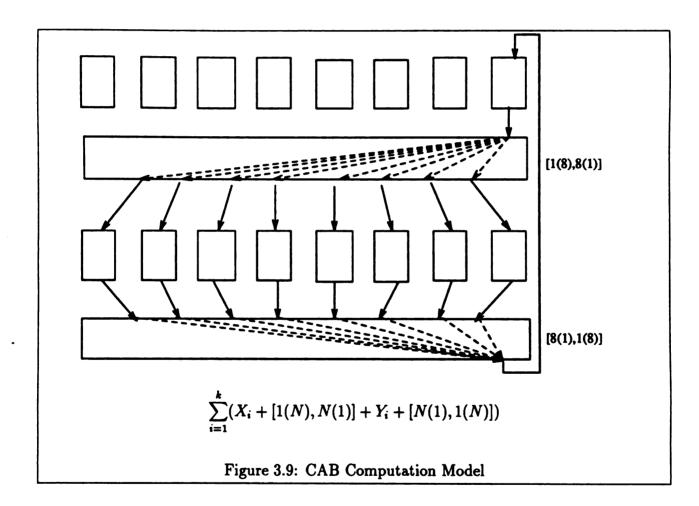

| 3.9  | CAB Computation Model                             | 41 |

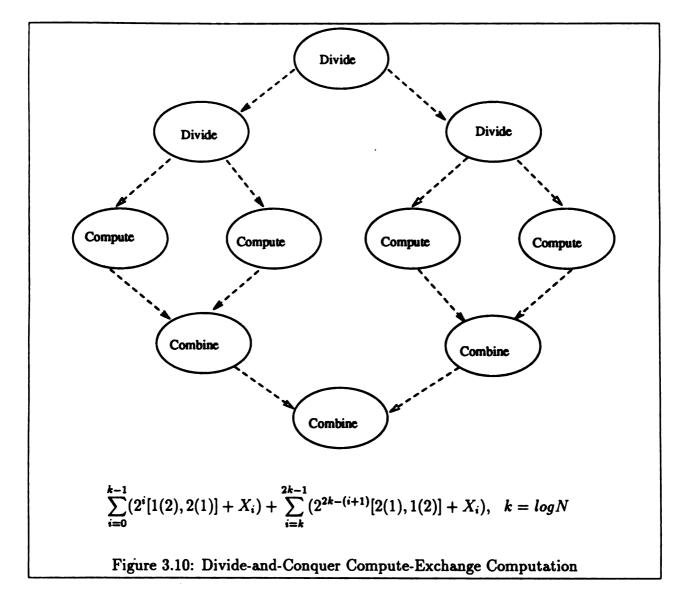

| 3.10 | Divide-and-Conquer Compute-Exchange Computation   | 42 |

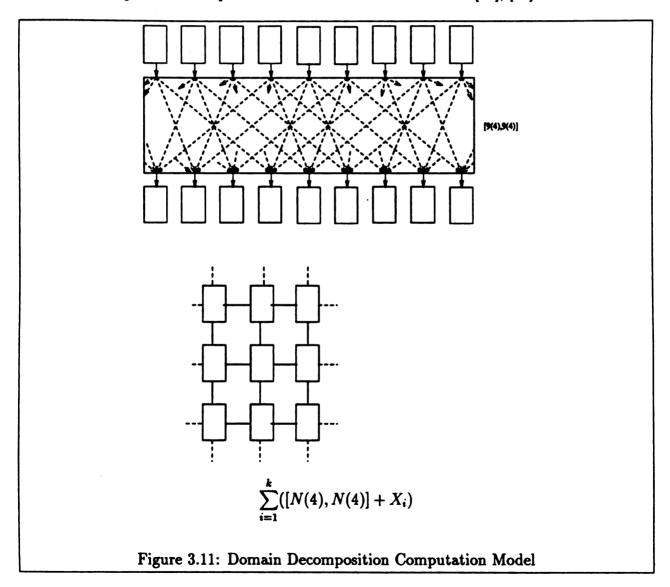

| 3.11 | Domain Decomposition Computation Model            | 44 |

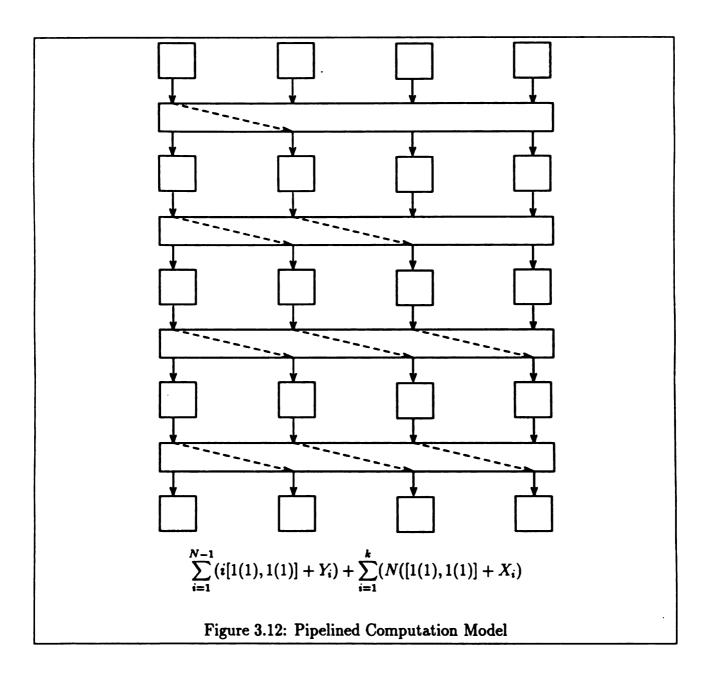

| 3.12 | Pipelined Computation Model                       | 47 |

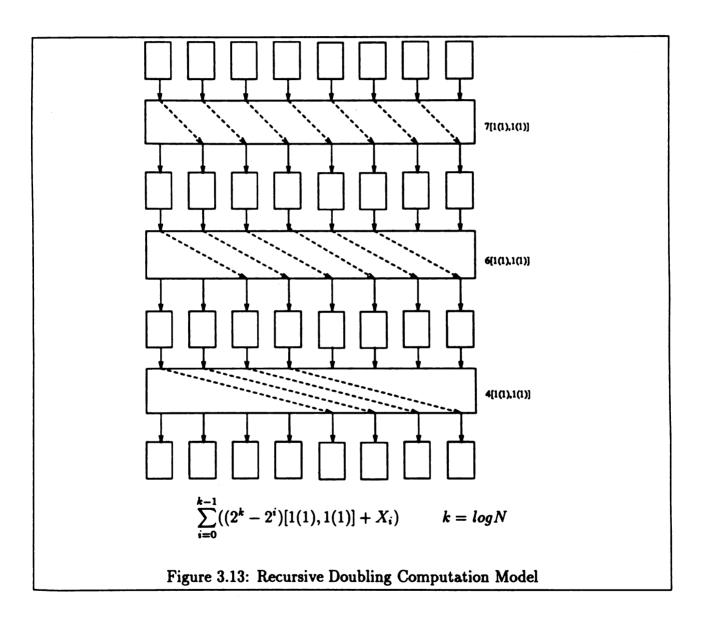

| 3.13 | Recursive Doubling Computation Model              | 50 |

| 4.1  | The Main Components of Power System               | 54 |

| 4.2  | The Homotopy Method                               | 59 |

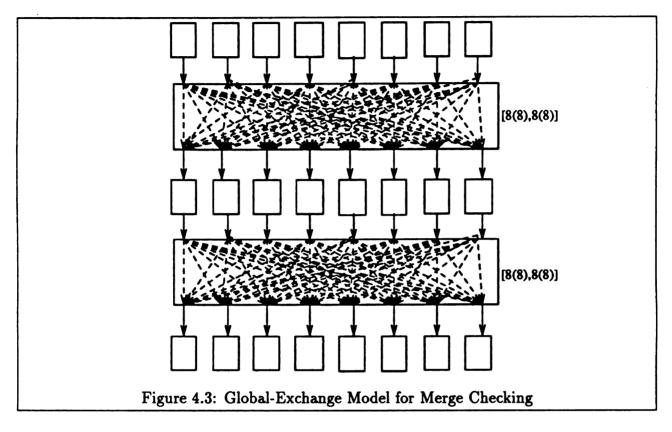

| 4.3  | Global-Exchange Model for Merge Checking          | 60 |

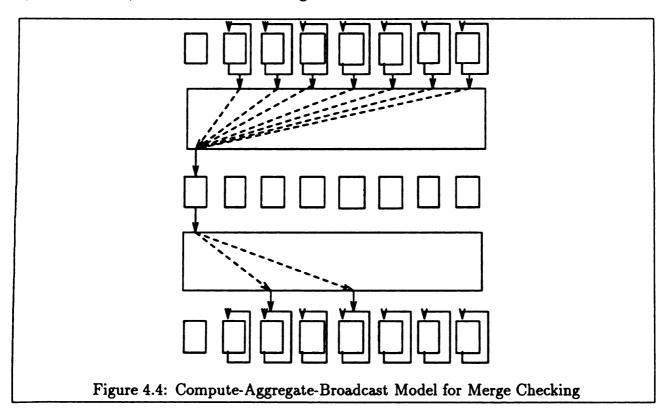

| 4.4 | Compute-Aggregate-Broadcast Model for Merge Checking       |

|-----|------------------------------------------------------------|

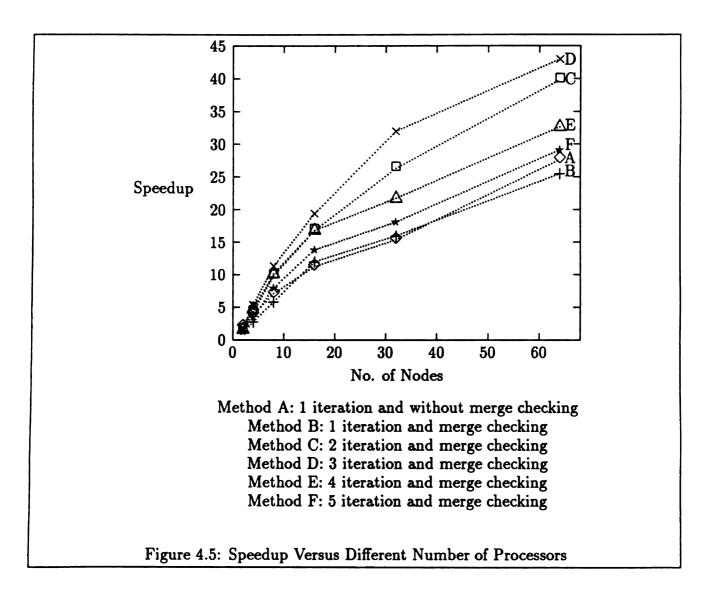

| 4.5 | Speedup Versus Different Number of Processors              |

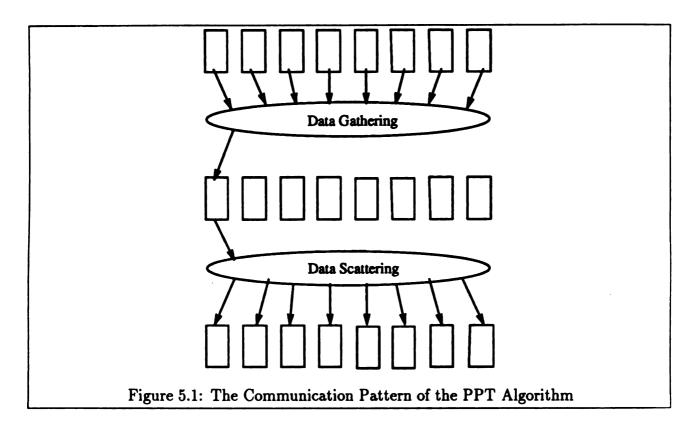

| 5.1 | The Communication Pattern of the PPT Algorithm             |

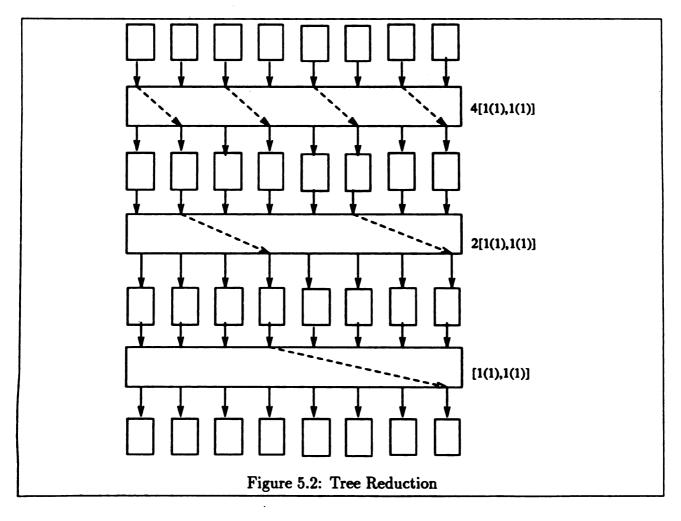

| 5.2 | Tree Reduction                                             |

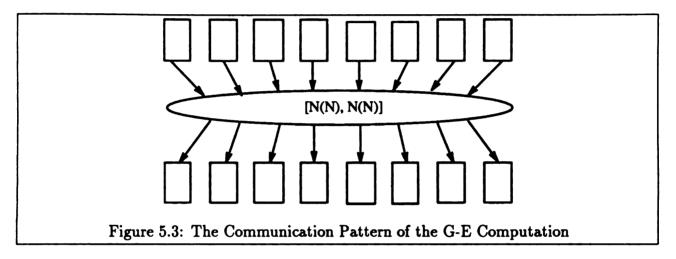

| 5.3 | The Communication Pattern of the G-E Computation           |

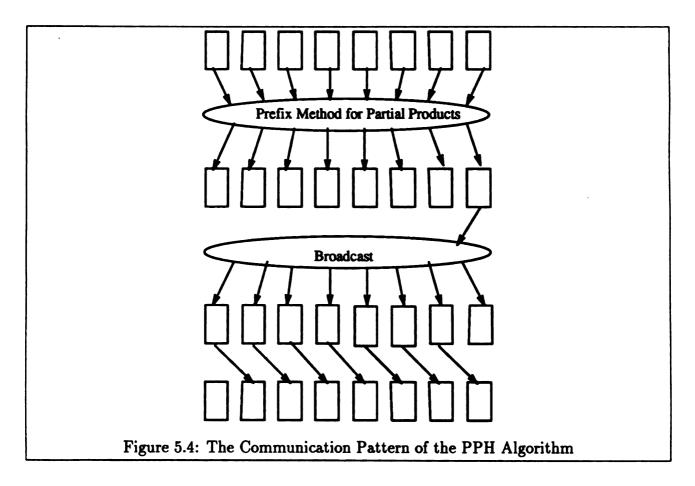

| 5.4 | The Communication Pattern of the PPH Algorithm             |

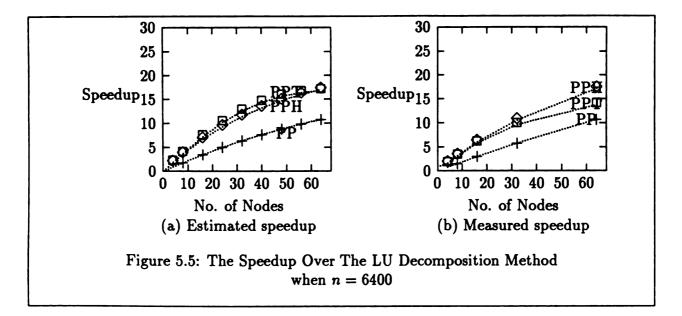

| 5.5 | The Speedup Over The LU Decomposition Method               |

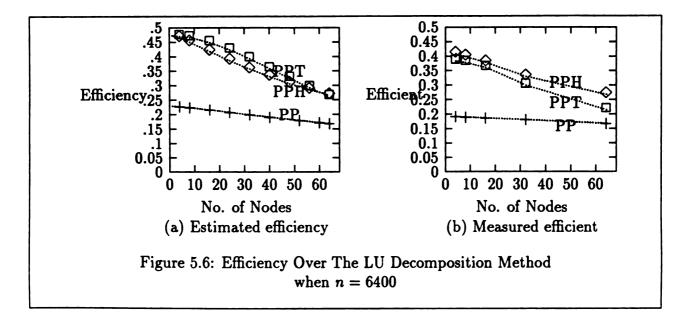

| 5.6 | Efficiency Over The LU Decomposition Method                |

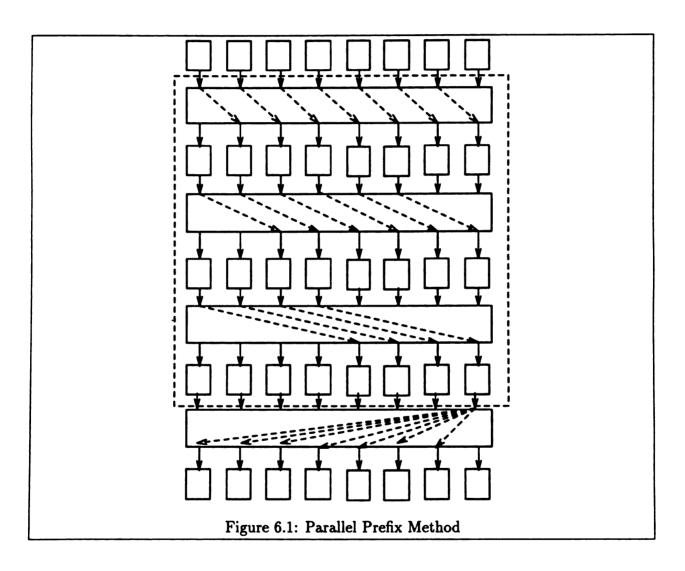

| 6.1 | Parallel Prefix Method                                     |

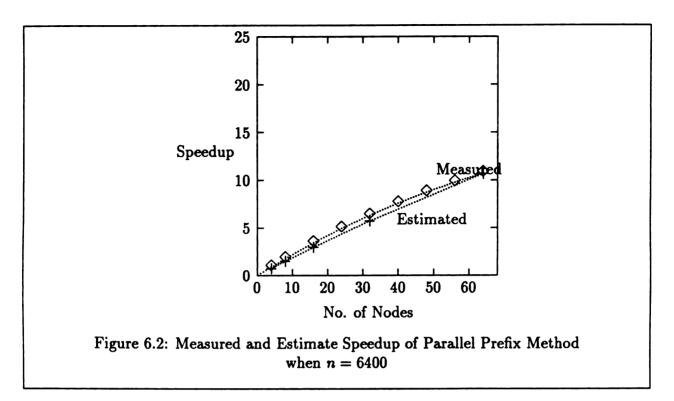

| 6.2 | Measured and Estimate Speedup of Parallel Prefix Method 91 |

## Chapter 1

## **INTRODUCTION**

Powerful computer systems able to handle computationally intensive problems are increasingly in demand in many scientific and engineering areas. To cope with these computational requirements, a natural trend is to construct systems consisting of multiple processors. This approach has been shown in recent years to be the most straightforward and cost-effective approach for achieving high performance. One system consisting of many processors communicating through an interconnection mechanism is called a *multiprocessor system* [28]. These processors are usually homogeneous, and the communication latency between processors is relatively small but non-negligible. The communication latency, along with other degradations, makes parallel computation much more complex than sequential computation. Much effort has been exerted and is currently being exerted to obtain highly efficient parallel computation. Although there are various multiprocessors available, software support and efficient algorithm development for these machines are far behind their hardware counterpart.

In scientific computing, there are several issues related to parallelization that do not arise in a serial context. The first issue is task partitioning, i.e., the breakdown of the total workload into smaller tasks, some or all of which, can be processed concurrently. This includes the proper sequencing of the tasks when some tasks are interdependent and cannot be executed simultaneously. The second issue is the synchronization of concurrent processes. In some methods, processes must wait at predetermined points for the completion of certain computations or for the arrival of certain data. The mechanisms used to enforce such synchronization have an important effect on algorithmic performance. A third issue is the communication of interim results between the processes. The objective here is to carry out the communication efficiently, which is problem dependent as well as machine dependent. The fourth issue is to obtain a good match between algorithmic requirements and architectural capabilities, i.e., the pairing of applications and architectures. From a parallel algorithm design point of view, the issue is how to explore all the execution potential of the underlying architecture, which includes the determination of the number of processors needed as well as task and data allocation across the processors. From the architecture point of view, architectures can be tailored for the execution of a fixed set of algorithms if the architectural requirement of the algorithms are understood.

All of the above issues are problem dependent. It is difficult, if not impossible, to derive any acceptable solution for parallel computation as a whole. For this reason the issues have been traditionally studied problem by problem and solved by brute force methods. However, the issues are important in a general context. A more general study is needed that does not reference a special problem. In this dissertation, a new concept, *compute-exchange computation*, is proposed. Based on this new concept, most of the frequently used scientific and engineering applications can be represented by a simple structured representation. Structured design and rethinking, therefore, become possible. The basic building blocks of these structures, called *parallel computation models*, are identified and studied. Issues of performance metrics for parallel computation are also examined. The results of this research are useful in many areas of computer science. The study presented will focus on two areas, efficient algorithm design and performance prediction.

This chapter is organized as follows. Section 1.1 will address the parallel systems considered in this study. Section 1.2 will discuss the parallel programming considerations. The motivation of the research will be given in Section 1.3. Finally, an overview of the dissertation will be found in Section 1.4.

#### **1.1 Multicomputers**

The parallel systems considered in this study are *multicomputers*. Multicomputers are message passing distributed-memory multiprocessors [28]. They are organized as an ensemble of small programmable computers, called *nodes*, and communicate through a point-to-point interprocessor communication network. Each memory module is physically associated with each processor. When the number of processors increases, the memory capacity also increases. Multicomputers with hundreds or thousands of processors are available commercially. Examples of first generation multicomputers include JPL's MARK III, Intel's iPSC (up to 128 processors), Ncube's NCUBE (up to 1024 processors), Ametek's S/14 (up to 256 processors) and FPS's T series (up to  $2^{14}$  processors) [55] [23] [21]. Note that the Connection Machine [25], though hypercube interconnected, is a bit-serial SIMD machine. New multicomputers are also emerging. Both Intel's iPSC-2 [46] and Ametek's 2010 [3] are classified as second generation multicomputers. The iWARP [6], being developed by Intel and CMU, is also an example of a high performance multicomputer. All first generation multicomputers adopt the store-and-forward communication mechanism and the hypercube topology. Second generation multicomputers have more advanced communication mechanisms. Although the processors are physically interconnected as a hypercube or a 2D-mesh, they are logically fully connected [3]. The structured representation proposed in this study aims at these new communication mechanisms. Multicomputers hold a promising potential for providing massive parallelism. In addition to architectural enhancement through an increase in computational capability and a decrease in communication latency, the full potential of a multicomputer cannot be exploited without a careful design of algorithms. The results of this research will benefit this careful design and should be useful in the design of future multicomputers to help accommodate those frequently used parallel computation models. A generic architecture of multicomputers is depicted in Figure 1.1.

### **1.2** Parallel Algorithm Design Considerations

During the past two decades, the computing community has witnessed a rapid growth of interest in parallel processing. The motivation behind this increasing interest is not that parallel computing is easier to program, but that there are physical and technological limits in uniprocessors. Modern VLSI technologies enable multiprocessors to be built and implemented at a very cost-effective rate for solving computationally intensive problems. However, the expected superior performance can be achieved only when all the advantages of the underlying architecture are exploited. These include partitioning an application in such a way that load balancing can be maximized and allocating the tasks in such a way that the communication overhead can be minimized. Neither this maximum nor minimum can be achieved easily. In fact, it has been shown that implementing parallel algorithms is much more difficult than most computer scientists had expected [30]. Parallelism degradations exist that could degrade the performance of parallel algorithms. Depending on their characteristics, different algorithms may be influenced by different degradations. In this section we shall address possible degradations and characteristics of parallel algorithms.

#### **1.2.1** Sources of Degradation

Parallel algorithms rarely achieve linear speedup for several reasons [18]. In designing efficient parallel algorithms, we have to know the sources of degradation and how to reduce their influence or remove them completely whenever possible. In this section sources of degradation are discussed. In the next section, parallel algorithms are characterized according to their inherent degradations.

- Communication delay. From a computation point of view, in addition to the transmission and propagation delay, there are two other communication delays [5]:

- Communication processing time. This is the time required to prepare information for transmission.

- Queuing time. Once information is assembled into packets for transmission on some communication link, it must wait in a queue prior to the start of its transmission. Queuing time is generally difficult to quantify precisely, but simplified models are often adequate to obtain valuable qualitative and quantitative conclusions [34].

Communication overhead can be reduced by overlapping communication with computation. The queuing, transmission, and propagation delays can possibly be overlapped with computations, but communication processing cannot.

Communication cost is a determining factor for the complexity of parallel algorithms. Various techniques have been developed to reduce communication overhead. These include designing efficient networks, overlapping communication with computation, and developing algorithms carefully. In second generation multicomputers, the number of hops from a source node to a destination node is not a major factor in determining the message delay times. However, there are three classical ways to reduce communication delay by restructuring algorithms which still hold true [31]: 1) reducing the quantity of information that must be communicated, 2) reducing the frequency with which messages must be sent, 3) overlapping communication with computation. In practice the above goals may not be mutually compatible.

• Uneven Allocation. It is desirable to distribute the computation load evenly so that all processors have an identical amount of work. However, load balancing is very difficult to achieve. High level module load balancing may lead to unbalanced computation due to the underlying data structure. Those processors that finish a step of computation earlier may have to wait until others are complete before continuing. Thus, the processing power of those processors is wasted.

Communication delay and uneven allocation are the main sources of degradation in parallel algorithms. Reducing these two degradations is difficult and may sometimes raise other degradations. Such tradeoffs between degradations can be used as a design technique to improve the overall performance.

- Redundant Work. Transferring intermediate results is more costly than computation for certain problems. Instead of transferring the results, we may wish to recompute the results. This kind of redundant work is adopted in solving eigenvalue problems [40] where eigenvalues are transferred and corresponding eigenvectors are recomputed. Another kind of redundant work comes from the load balancing: To reach agreement on shared data, an algorithm can either let one processor compute it while all the other processors wait or let all the processors compute it concurrently. Since the former involves waiting and receiving, the later is more favorable. This kind of redundant work is used in solving linear tridiagonal systems [60]. Redundant work decreases the communication overhead by increasing the computation requirement.

- Reduced Knowledge. If performing calculations improves the knowledge base of the algorithm, simultaneous calculations cannot make use of the most recent knowledge but must rely on information that is to some extent out of date. This is often the case in iterative methods where each iteration advances the knowledge base. For example, Jacobi algorithms are widely used in multicomputers, while Gauss-Seidel algorithms, which use the latest available information, usually converge faster than the corresponding Jacobi algorithm. Receiving the newest information requires frequent communication and synchronization, making Gauss-Seidel algorithms difficult to implement efficiently on multicomputers.

• Non-optimal. With more than one processor computing concurrently, the computational complexity might be misleading, since an algorithm could do more work and still be fast. The algorithm with the lowest computation count is very often sequential in nature. To achieve a high degree of parallelism, we may have to develop parallel algorithms which require more computation than the optimal sequential algorithms. We reduce the uneven allocation degradation by increasing the computation requirement. This increase in computation requirement will lower the performance gain of parallel processing, at least in the sense of absolute speedup (see Chapter 2).

#### **1.2.2** Algorithm Characteristics

Parallel algorithm characteristics have been studied for mapping parallel algorithms into parallel or distributed architectures [30]. In this section, parallel algorithms are characterized from a different point of view. We study how these characteristics degrade the performance of parallel algorithms.

- Data Parallelism versus functional parallelism. Parallelism can be achieved by dividing the data among the processors, or by decomposing the algorithm into segments that can be assigned to different processors. We call the former data parallelism and the latter functional parallelism. Data parallelism is the parallelism which comes from simultaneous operations across a set of data [26]. Thus, for data parallel algorithms each processor executes the same instructions on a different data set. Task partitioning is more flexible and load balancing is relatively easy to achieve. Algorithms based on functional parallelism typically use a small number of processors.

- Granularity. The granularity or grain size deals with average subtask size, which is measured in the number of instructions executed. It has a bearing on data allocation, communication requirements, processing capability, and memory requirements. Fine-grain algorithms often require frequent communication. Large-grain algorithms typically reduce the communication/computation ratio and have less communication penalty. This communication penalty reduction makes some computation models, that may be intolerable for fine-grain algorithms, favorable for large-grain algorithms. For example, with fine-grain parallelism, both pipelined Jacobi iteration and Gauss-Seidel iteration are unacceptable. With large-grain parallelism, these methods can achieve a near linear speedup [49], [5].

- Degree of Parallelism. We call the number of processes that can operate independently the degree of parallelism. Load balancing will be much more easily achieved for algorithms with a static degree of parallelism. Unfortunately, parallel algorithms with a dynamic degree of parallelism are not uncommon. An example is parallel Gaussian elimination algorithm. To eliminate the lower triangular elements, n 1 independent processes are available for elimination in the first column, n 2 independent processes are available for elimination in the second column, ..., and finally one process is available for elimination in the n 1<sup>th</sup> column. Another example is parallel Given Rotation [47]. For an n dimensional matrix, the degree of parallelism of Given Rotation goes up from 1 to n/2 and then goes down from n/2 to 1.

- Concurrency and Pipelining. From the viewpoint of scheduling, a parallel computation can be characterized as either concurrent or pipelined [29]. Concurrency exploits spatial parallelism by utilizing several processors executing multiple independent tasks simultaneously. Pipelining exploits temporal parallelism in which each processor (called a stage) behaves like a filter or transformer which operates on its input data and passes its output data to the succeeding processor as the later's input. A systolic array is a typical example of a pipelined computation in a synchronized environment. Through pipelining, communication occurs only between fixed and neighboring stages. Thus a very high ratio of computation to I/O rate will result. A more detailed study on pipeline computation can be found in [34] [49].

- Data Dependencies. Data dependencies have a major impact on the design of parallel algorithms. They influence data granularity, degree of parallelism and synchronization. Data dependency is so important that two nontraditional parallel machines, namely graph reduction machines and dataflow machines, have been proposed in which the order of instruction executions is implied by data dependencies [61]. By representing the operations as vertices and using directed edges to indicate the dependencies, data dependency can be represented by a directed dependency graph. Much information can be obtained by coloring the dependency graph. Operations with different colors cannot execute concurrently. From a design point of view, we would like to distribute operations with the different color to the same processor. The multicoloring method [5], which has been successfully employed in the solution of partial differential equations and in image processing, is a good example of grouping the operations according to data dependency.

• Methodology. There are a variety of methods for solving systems of equations, usually classified as direct and iterative methods. Direct methods follow fixed procedures and find the exact solution with a finite number of operations. Iterative methods do not obtain an exact solution in finite steps, they converge to a solution asymptotically. Nevertheless, iterative methods often yield a solution, within acceptable precision, after a relatively small number of iterations. In this case, they are preferred to direct methods. This is usually the case for linear systems when n is very large and the coefficient matrix is sparse, such as the system Ax = b which arises in the discretization of a linear partial differential equation and in many other applications. Iterative methods may also have smaller storage requirements than direct methods when the matrix A is sparse. The computation count of iterative methods depends on the number of iterations, which is problem dependent. Curve tracing is a special method for obtaining solutions, in which we start at one end of the curve and want to get to the other end point. The intermediate results along the curve are unimportant. A curve tracing method for solving power flow problems will be presented in Chapter 4. Several newly developed direct methods for solving tridiagonal linear systems will be given in Chapter 5.

#### **1.3** Motivation and Problem Statement

The complex interaction of the many architectural, hardware, and software features of parallel systems results in a larger space of possible performance behavior and an increase in algorithm design complexity. Designing efficient parallel algorithms requires that users to understand the performance characteristics of parallel machines and to modify their algorithm accordingly. These modifications are problem dependent. Therefore, parallel algorithms have had to be fine-tuned case by case to achieve higher performance. The painful, elusive design process has excluded casual users and restricted parallel computers to a rather small professional community. This situation needs to be changed to make parallel computers usable for other scientists.

We would like to reduce the burden of parallel algorithm design and make the design process more systematic. This raises the obvious questions: What are the techniques for developing efficient parallel algorithms? How could these techniques be used on a given application? To answer the first question, Nelson and Snyder [44] have proposed the concept of parallel paradigm and identified several paradigms. Paradigms are recognized high level methodologies common to many of the effective parallel algorithms. They are important, because they provide good examples and may help users understand parallel computation. However, these paradigms are described verbally and are isolated from each other. How to connect these paradigms with general applications is unknown.

In this dissertation, I approach these two questions from a different angle. I study parallel algorithm design from a general point of view. First, a representation methodology, *structured representation*, is developed. With this representation, most of the frequently used scientific and engineering applications can be represented by simple formulations. These formulations are combinations of some simple data structures, called *parallel computation models*, and provide adequate information about performance degradations. Parallel computation models are the basic building blocks of structured representations. Since both parallel computation models and parallel paradigms are commonly used data structures, it is not surprising that they share some similarities. Some of them even share the same name. A major advantage of parallel computation models over parallel paradigms is that computation models are based on mathematical formulations, and they are the constructing components of general scientific applications. The structured representation of most frequently used scientific and engineering applications consists of computation models. The design techniques used in computation models are the techniques needed for general scientific algorithm design, and the design techniques are used in a similar way.

A mathematical foundation is necessary in moving toward a systematic design methodology for parallel algorithms. Based on that foundation, different applications can be classified and manipulated. Forming structured representation and acquiring computation models are the first step in developing such a foundation. After computation models have been well identified and studied, the performance of an application can be predicted during its design stage, and systematically mapping algorithms onto architectures becomes possible.

Structured representation and computation models are important. They provide a fast way of estimating and understanding the performance of parallel programs in a parallel system. They lead to efficient parallel algorithm design for scientific and engineering applications. They provide guidelines for programming tools and systematic parallel algorithm design methodology. Also, they suggest how each multicomputer should be used in applications and which multicomputer is the best for a given application.

This study focuses on scientific computations. The models are built for scientific applications and examples are chosen from scientific applications. We are interested in scientific applications since scientific and engineering applications are the major driving force behind parallel processing and the data structures of scientific applications are relatively simple. With some effort, structured representation and computation models could possibly be extended to general non-numerical applications.

### **1.4 Thesis Organization**

This dissertation is organized as follows. In Chapter 2, we study the performance issues of parallel processing. The study focuses on one performance metric, parallel speedup. Three models of speedup are studied. They are fixed-size speedup, fixed-time speedup and memorybounded speedup. Memory-bounded speedup considers memory capacity as an influential factor and provides the quantum of the tradeoff between time and space. Two sets of speedup formulations are derived for these three models. One set requires more information and provides more accurate estimations. Another set considers a simplified case and provides a clear picture of the possible performance gain of parallel processing.

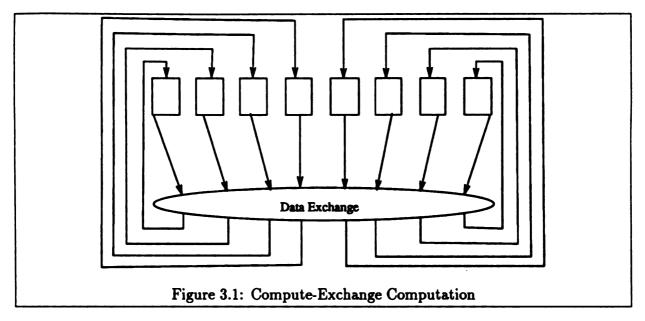

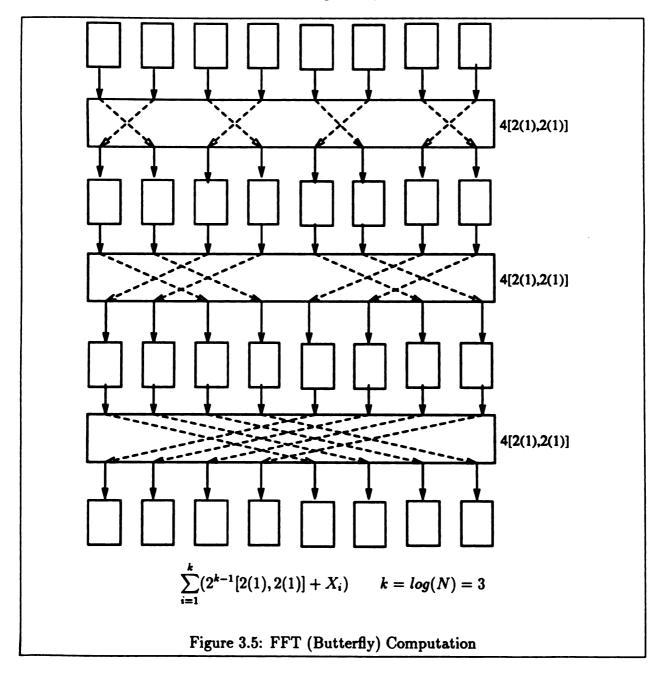

Structured representation is proposed in Chapter 3. Two different classes of dataexchange are identified. One is regular data-exchange. Another is conjunctive regular data-exchange. Notation is developed to represent these two classes of data-exchanges. A new concept, compute-exchange computation, is introduced. By this concept, every parallel computation can be divided into two parts, compute and data-exchange. Therefore, a parallel algorithm can be written in terms of data exchanges and computations, which is called structured representation. Some basic components of structured representation, called computation models, are also studied in Chapter 3. They are Local Computation Model, Global-Exchange Computation Model, Compute-Aggregate-Broadcast Computation Model, Divide-and-Conquer Computation Model, Domain Decomposition Computation Model, Pipeline (Ring) Computation Model, and Recursive Doubling Computation Model.

Parallel algorithms may be modified for different reasons to achieve high performance. The modifications, however, mainly follow two approaches: explore the inherent parallelism of the application to increase the concurrency and take advantage of the underlying architecture to reduce the communication overhead. Two applications are studied to illustrate how structured representation and computation models can be used in efficient algorithm design. The power flow problem is studied in Chapter 4 to demonstrate how structured representation can help in application-driven algorithm design. In Chapter 5, using the design process of linear tridiagonal solvers, we show how the parallel architecture will influence the choice of computation models. The power flow problem determines how electrical power generation and distribution should be changed with customer demand, so that the power system can be operated safely. We adopt the homotopy mathematical method to solve the power flow problem. Our first approach is an algorithm using the local computation model. Then, we change to a global-exchange computation. After learning more about the homotopy method, we modify our algorithm into a compute-aggregate-broadcast computation. Solving linear tridiagonal systems is a fundamental problem of scientific computation. We have developed tridiagonal solvers on a first generation NCUBE/7 hypercube multicomputer. To take advantage of the hypercube architecture, we change our design from compute-aggregate-broadcast computation to global-exchange computation. Then we change to a hybrid computation, which is a combination of two computation models. The last one gives the best performance. All the algorithms are implemented on an NCUBE multicomputer and the results can be found in the chapters that follow.

A new performance prediction methodology is presented in Chapter 6. This methodology adopts a divide-and-combine strategy. For a given application we write down its structured representation and find out the contained computation models. We then use the well-studied computation models to predict the performance of the given application. Examples are given and the performance measurements of identified computation models are studied. Instead of studying the performance on a given architecture, the performance is studied from a dynamic point of view. We study the influence of problem size on performance. Chapter 7 gives a summary of my major contributions and the direction of future research.

## Chapter 2

# PERFORMANCE METRIC OF PARALLEL ALGORITHMS

To study efficient parallel algorithm design we first have to understand the performance metrics. For sequential machines, elapsed time and memory space are the metrics by which algorithms are measured. With parallel machines, the performance measurement becomes more difficult. In addition to time and space, the performance parameters for parallel algorithms include the number of processors available, communication overhead and the inherent parallelism of the given application. For this reason, despite the fact that parallel processing has become a common approach for achieving high performance, performance evaluation techniques of parallel processing are weak. There is no well-established metric to measure the performance gain. This weakness is one of the reason which leads to confusion and limits the growth of parallel computation. In this chapter, we shall study issues of performance metrics and seek a better understanding of one metric, *parallel speedup*.

The most commonly used performance metric for parallel processing is speedup, which gives the performance gain of parallel processing versus sequential processing. However, with different emphases, speedup has been defined differently. One definition focuses on how much faster a problem can be solved with N processors. Thus, it compares the best sequential algorithm with the parallel algorithm under consideration. This definition is referred to as absolute speedup. Absolute speedup has two different definitions, one which considers machine resources and one which does not. In the first definition, speedup is defined as the ratio of elapsed time of the best sequential algorithm on one processor over the elapsed time of the parallel algorithm on N processors. In the second definition, the absolute speedup is defined as the ratio of elapsed time of the best sequential algorithm on the fastest sequential machine over the elapsed time of the parallel algorithm on the parallel machine [47]. Another type of speedup, called *relative speedup*, deals with the inherent parallelism of the parallel algorithm under consideration. It is defined as the ratio of the elapsed time of the parallel algorithm on one processor over the elapsed time of the parallel algorithm on N processors. Relative speedup is used because that the performance of parallel algorithms varies with the number of available processors. Comparing the algorithm itself with different numbers of processors gives information on the variations and the degradations of parallelism. Absolute speedup and relative speedup are two commonly used speedup measures. Other definitions of speedup also exist. For instance, considering the construction costs of processors, a costrelated speedup is defined in [4].

Among all of the defined speedups, relative speedup is probably the one which has had the most influence on parallel processing. Two well known speedup formulations have been proposed based on relative speedup. One is *Amdahl's law* [2] and another is *Gustafson's* scaled speedup [20]. Both of these two speedup formulations use a single parameter, the sequential portion of a parallel algorithm. They are simple and give much insight into the degradations of parallelism. Amdahl's law has a fixed problem size and is interested in how fast the response time could be. It suggests that massively parallel processing may not gain high speedup. Under the influence of Amdahl's law many parallel computers have been built with a small number of processors. Gustafson [20] approaches the problem from another point of view. He fixes the response time and is interested in how large a problem could be solved within this time. The argument of Gustafson is that the problem size should be increased to meet the available computation power for better results. Experimental results based on his argument show that speedup can increase linearly with the number of processors available [22].

In this chapter we shall provide a careful study of relative speedup and reserve the word speedup for relative speedup, unless explicit state otherwise. We first study three models of speedup, *fixed-size speedup*, *fixed-time speedup* and *memory-bounded speedup*. All three models are based on relative speedup. With both uneven allocation and communication overhead considered, general speedup formulations will be derived for all three models. When communication overhead is not considered and the workload only consists of sequential and perfectly parallel portions, the simplified fixed-size speedup is Amdahl's law; the simplified fixed-time speedup is Gustafson's scaled speedup; and, with one more parameter, the simplified memory-bounded speedup contains both Amdahl's law and Gustafson's speedup as its special cases. Therefore, from different points of view, the three models of speedup are unified.

### 2.1 Preliminary

The parallelism in an application can be characterized in different ways for different purposes, such as data dependency graph [61], task precedence graph [11], Petri Net [41] and average

parallelism [15]. For simplicity, speedup formulations generally use very few parameters and consider very high level characterizations of the parallelism. In our study we consider two main degradations of parallelism, uneven allocation and communication latency. The former degradation is application dependent. The latter degradation depends on both the application and the parallel computer under consideration. To give an accurate estimate, both of the degradations need to be considered. Uneven allocation is measured by degree of parallelism.

**Definition 1** The degree of parallelism of a program is an integer which indicates the number of processors that are busy computing at a particular instant in time, given an unbounded number of available processors.

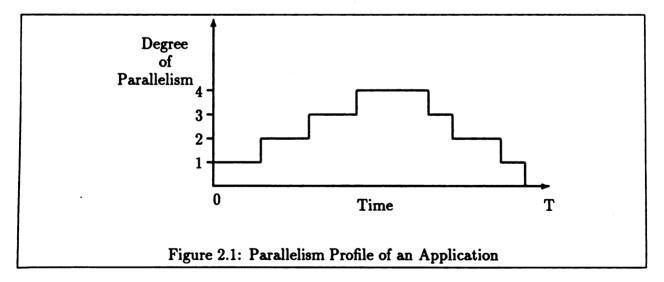

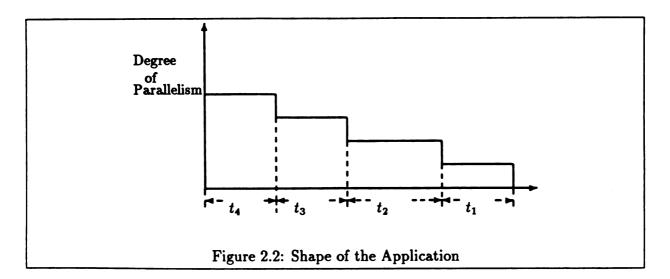

The degree of parallelism is a function of time. By drawing the degree of parallelism over the execution time of an application, a graph can be obtained. We refer to this graph as the *parallelism profile*. Software tools are available to determine the parallelism profile of large scientific and engineering applications [36]. Figure 2.1 is the parallelism profile of a hypothetical divide-and-conquer computation (see Section 3.2). By accumulating the time spent at each degree of parallelism, the profile can be rearranged to form the *shape* (see Figure 2.2) of the application [53].

**Definition 2** The average parallelism is the average number of processors that are busy during the execution of the program in question, given an unbounded number of available processors.

By definition, average parallelism is the ratio of the total service demand to the execution time with an unbounded number of available processors. This is equal to the speedup, given unbounded number of available processors and without considering communication latency. Therefore, average parallelism can be defined equivalently as follows [15].

**Definition 3** The average parallelism is the speedup, given an unbounded number of available processors and without considering communication latency.

Let W be the amount of work (computation) of an application. Let  $W_i$  be the amount of work executed with degree of parallelism *i*, and *m* be the maximum degree of parallelism. Thus,  $W = \sum_{i=1}^{m} W_i$ . The execution time for computing  $W_i$  with a single processor will be

$$t_i(1) = \frac{W_i}{\Delta},\tag{2.1}$$

where  $\triangle$  is the computing capacity of each processor. If there are *i* processors available, the execution time will be

$$t_i(i)=rac{W_i}{i\Delta}.$$

With an infinite number of processors available, the execution time will be

$$t_i = t_i(\infty) = \frac{W_i}{i\Delta}$$

for  $1 \le i \le m$ .

Therefore, without considering communication latency, the response time on a single processor and on an infinite number of processors will be

$$T(1) = \sum_{i=1}^{m} \frac{W_i}{\Delta}, \qquad (2.2)$$

$$T(\infty) = \sum_{i=1}^{m} \frac{W_i}{i\Delta}.$$

(2.3)

The speedup will be

$$S_{\infty} = \frac{T(1)}{T(\infty)} = \frac{\sum_{i=1}^{m} \frac{W_i}{\Delta}}{\sum_{i=1}^{m} \frac{W_i}{i\Delta}} = \frac{\sum_{i=1}^{m} W_i}{\sum_{i=1}^{m} W_i/i.}$$

(2.4)

The average parallelism, A, can be computed in terms of  $t_i$ ,

$$A = \sum_{i=1}^{m} \frac{it_i}{\sum_{i=1}^{m} t_i} = \frac{\sum_{i=1}^{m} it_i}{\sum_{i=1}^{m} t_i}.$$

(2.5)

Notice that  $t_i$  is the time for executing  $W_i$ . When an unbounded number of processors are available,  $t_i = \frac{W_i}{i\Delta}$ . Substituting  $t_i = \frac{W_i}{i\Delta}$  into Eq. (2.5), we have

$$A = \frac{\sum_{i=1}^{m} it_i}{\sum_{i=1}^{m} t_i} = \frac{\sum_{i=1}^{m} W_i}{\sum_i^m W_i/i} = S_{\infty}.$$

(2.6)

This gives a formal proof for the equivalence of Definition 2 and Definition 3. Average parallelism is a very important factor for speedup and efficiency. It has been carefully examined in [15].  $S_{\infty}$  gives the best possible speedup based on the inherent parallelism of an algorithm. There are no machine dependent factors considered. With only a limited number of available processors and with communication latency considered, the speedup will be less than the best speedup,  $S_{\infty}$ . If there are N processors available and N < i, then some processors have to do  $\frac{W_i}{i} \left[\frac{i}{N}\right]$  work and the rest of the processors will do  $\frac{W_i}{i} \left\lfloor \frac{i}{N} \right\rfloor$  work. In this case, assuming  $W_i$  and  $W_j$  cannot be solved simultaneously for  $i \neq j$ , the elapsed time will be

$$t_i(N) = \frac{W_i}{i\Delta} \lceil \frac{i}{N} \rceil$$

and

$$T(N) = \sum_{i=1}^{m} \frac{W_i}{i\Delta} \lceil \frac{i}{N} \rceil.$$

(2.7)

The speedup is

$$S_N = \frac{T(1)}{T(N)} = \frac{\sum_{i=1}^m W_i}{\sum_{i=1}^m \frac{W_i}{i} \left[\frac{i}{N}\right]}.$$

(2.8)

Communication latency is an important factor contributing to the complexity of a parallel algorithm. Unlike degree of parallelism, communication latency is machine dependent. It depends on the communication network, the routing scheme, and the adopted switching technique. For instance, the switching technique used in first generation multicomputers is store-and-forward. Second generation multicomputers adopt circuit switching or wormhole routing switching techniques. These new switching techniques reduce the communication cost considerably. Let  $Q_N$  be the communication overhead when N processors are used in parallel processing; the general speedup becomes

$$S_N = \frac{T(1)}{T(N)} = \frac{\sum_{i=1}^m W_i}{\left(\sum_{i=1}^m \frac{W_i}{i} \left\lceil \frac{i}{N} \right\rceil\right) + Q_N}.$$

(2.9)

### 2.2 Models of Speedup

In the last section we developed a general speedup formula and showed how the number of processors and degradation parameters will influence the performance. However, speedup is not only dependent on these parameters. It is also dependent on how we view the problem. With different points of view, we will get different models of speedup and will get different speedup formulations.

One viewpoint emphasizes shortening the time it takes to solve a problem by parallel processing. With more and more computation power available, the problem can be solved in less and less time. With more processors available, the system will provide a fast turnaround time and the user will have a shorter waiting time. A speedup formulation based on this philosophy is called a *fixed-size speedup*. In the previous section, we adopted fixed-size speedup implicitly. Equation (2.9) is the general speedup formula for fixed-size speedup. Fixed-size speedup is suitable for many applications.

For some applications we may have a time limitation, but we may not want to obtain the solution in the quickest way. If we have more computation power, we may want to increase the problem size, carry out more operations, get a more accurate solution, and keep the execution time unchanged. This viewpoint leads to a new model of speedup, called *fixed-time speedup*. Many scientific and engineering applications can be represented by some partial differential equations, which can be discretized for different choices of grid spacing. Coarser grids demand less computation, but finer grids give more accurate solutions. If more accurate solutions are desired, this kind of application will fit the fixed-time speedup model. One good example is weather forecasting. With more computation power, we may not want to give the forecast earlier. Rather, we may wish to add more factors into the weather model – increasing the problem size and getting a more accurate solution – thus providing a more precise forecast. For fixed-time speedup the workload is scaled up with the number of processors available. Let  $W'_i$  be the amount of scaled up work executed with degree of parallelism *i* and *m'* be the maximum degree of parallelism of the scaled up problem when N processors are available. In order to keep the same turnaround time as the sequential version, we must have

$$\sum_{i=1}^{m} W_i = \sum_{i=1}^{m'} \frac{W_i'}{i} \left\lceil \frac{i}{N} \right\rceil + Q_N$$

Thus, the general speedup formula for fixed-time speedup is

$$S'_{N} = \frac{\sum_{i=1}^{m'} W'_{i}}{\sum_{i=1}^{m'} \frac{W'_{i}}{i} \lceil \frac{i}{N} \rceil + Q_{N}} = \frac{\sum_{i=1}^{m'} W'_{i}}{\sum_{i=1}^{m} W_{i}}.$$

(2.10)

From our experience in using multicomputers, we have found that memory capacity plays a very important role in performance. Existing multicomputers do not support virtual memory, and memory is distributed and associated with each node. The memory associated with each node is relatively small. When solving an application with one processor, the problem size is more often bounded by the memory limitation than by the execution time limitation. With more nodes available, instead of keeping the execution time fixed, we may want to meet the memory capacity and increase the execution time. In general, the question is, if you want to increase the problem size, do you have enough memory for the size increase? If you do have adequate memory space for the size increase, and after the problem size is increased to meet the time limit you still have memory space available, do you want to increase the problem size further by using this unused memory space and to get an even better solution? For memory-bounded speedup the answer is yes. Like fixed-time speedup, memory-bounded speedup is a scaled speedup. The problem size is scaled up with system size. The difference is that in fixed-time speedup the execution time is the dominant factor and in memory-bounded speedup the memory capacity is the dominant factor. Most of the applications which fit fixed-time speedup will fit memory-bounded speedup when more accurate solutions are the goal. A good application for memory-bounded speedup is simulation. If we simulate a nuclear power plant, obtaining an accurate solution will probably be the highest priority.

With memory capacity considered as a factor of performance, the requirement of solving an application contains two parts. One is the computation requirement, which is the workload, and another is the memory requirement. For a given application, these two requirements are related to each other, and the workload can be seen as a function of the memory requirement. Let M represent the memory requirement and let g represent the function, we have W = g(M), or  $M = g^{-1}(W)$ , where  $g^{-1}$  is the inverse function of g. Under different architectures the memory capacity will change differently with the number of processors available. For multicomputers, the memory capacity increases linearly with the number of nodes available. If  $W = \sum_{i=1}^{m} W_i$  is the workload for sequential execution,  $W^* = \sum_{i=1}^{m^*} W_i^*$  is the scaled workload when N processors are available,  $m^*$  is the maximum degree of parallelism of the scaled problem, then the memory limitation for multicomputers can be stated as: the memory requirement for any active node is less than or equal to  $g^{-1}(\sum_{i=1}^{m} W_i)$ . Here the main point is that the memory occupation on each node is fixed. Equation (2.11) is the general speedup formula for memory-bounded speedup.

$$S_N^* = \frac{\sum_{i=1}^{m^*} W_i^*}{\sum_{i=1}^{m^*} \frac{W_i^*}{i} \lceil \frac{i}{N} \rceil + Q_N}$$

(2.11)

### 2.3 Simplified Models of Speedup

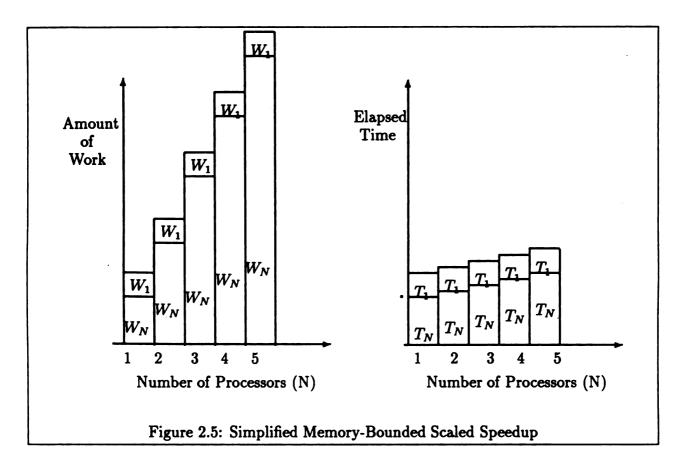

Three general speedup formulations have been proposed for three models of speedup. These formulations contain both uneven allocation and communication latency degradations. They are closer to actual speedup and give better upper bounds on the performance of parallel algorithms. On the other hand, these formulations are problem dependent and difficult to understand. They give more detailed information for each application, but lose the global view of the possible performance gain. In this section, we study a simplified case for speedup, which is the special case studied by Amdahl and Gustafson. We do not consider the communication overhead, so  $Q_N = 0$ , and we assume that the allocation only contains two parts, a sequential part and a perfectly parallel part. That is  $W_i = 0$ , for  $i \neq 1$  and  $i \neq N$ . We also assume that the sequential part is independent of the system size, i.e.,  $W_1 = W_1' = W_1^*$ .

Under this simplified case, the general fixed-size speedup formulation Eq.(2.9) becomes

$$S_N = \frac{W_1 + W_N}{W_1 + \frac{W_N}{N}},$$

(2.12)

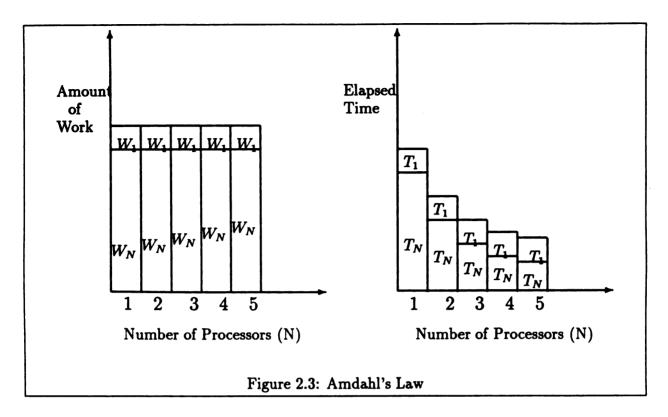

which is known as Amdahl's law. From Eq.(2.12) and Fig. 2.3 we can see when the number of processors increases the load on each processor decreases. Eventually, the sequential part will dominate the performance and the speedup is bounded by  $\frac{W_1+W_N}{W}$ .

Under the simplified conditions,  $\sum_{i=1}^{m} W_i = W_1 + W_N$  and  $\sum_{i=1}^{m'} \frac{\dot{W}'_i}{i} \left\lceil \frac{i}{N} \right\rceil + Q_N = W'_1 + \frac{W'_N}{N}$ . Therefore, for fixed-time speedup, we have  $W_1 + W_N = W'_1 + \frac{W'_N}{N}$ . Since  $W_1 = W'_1$ , we have  $W_N = \frac{W'_N}{N}$ . That is  $W'_N = NW_N$ . Equation (2.10) becomes

$$S'_{N} = \frac{\sum_{i=1}^{m'} W'_{i}}{\sum_{i=1}^{m} W_{i}} = \frac{W'_{1} + W'_{N}}{W_{1} + W_{N}} = \frac{W_{1} + NW_{N}}{W_{1} + W_{N}}.$$

(2.13)

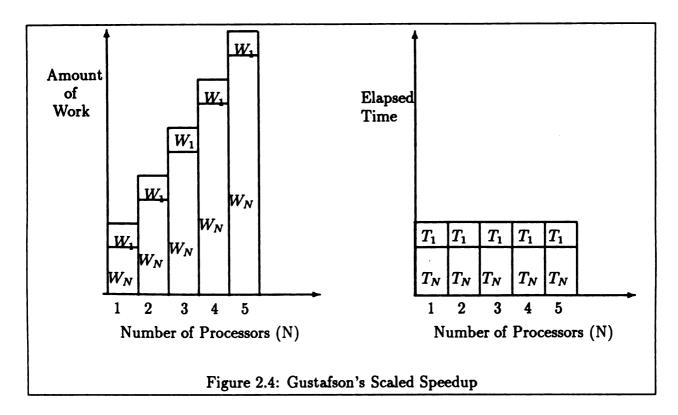

The simplified fixed-time speedup formula Eq.(2.13) is Gustafson's scaled speedup, which was proposed by Gustafson in 1988 [20]. From Eq.(2.13) we can see that the parallel portion of the application is scaled up linearly with the system size, and the speedup increases linearly with the system size. The relation of workload and elapsed time for Gustafson's scaled speedup is depicted in Figure (2.4), where  $T_1$  is the execution time for the sequential portion of work.  $T_N$  is the execution time for the parallel portion of load.

We need some preparation before deriving the simplified formulation for memory-bounded speedup.

**Definition 4** A function g is a semihomomorphism if there exists a function  $\bar{g}$  such that for any real number c and any variable x,  $g(cx) = \bar{g}(c)g(x)$ .

One class of semihomomorphism functions is the power function  $g(x) = x^b$ , where b is a rational number. In this case,  $\bar{g}$  is the same as the function g. Another class of semihomomorphism functions is the single term polynomial  $g(x) = ax^b$ , where a is a real constant and b is a rational number. For this kind of semihomomorphism functions,  $\bar{g}(x) = x^b$ , which is not the same as g(x).

The sequential portion of the workload,  $W_1$ , is independent of the system size. If we do not consider the influence of memory on the sequential portion we have the following theorem:

**Theorem 1** If W = g(M) for some semihomomorphism function g,  $g(cx) = \overline{g}(c)g(x)$ , then, with all data being shared by all the available processors and using all the available memory space, the simplified memory-bounded speedup is

$$S_N^* = \frac{W_1 + \bar{g}(N)W_N}{W_1 + \frac{\bar{g}(N)}{N}W_N}$$

(2.14)

**Proof:** As mentioned before,  $W_N$  is the parallel portion of the workload when one processor is used. Let the memory requirement of  $W_N$  be M,  $W_N = g(M)$ . M is the memory requirement when one node is available. With N nodes available, the memory capacity will increase to NM. Using all of the available memory, for the scaled parallel portion  $W_N^*$ ,  $W_N^* = g(NM) = \bar{g}(N)g(M)$ . Therefore,  $W_N^* = \bar{g}(N)W_N$  and

$$S_N^* = \frac{W_1^* + W_N^*}{W_1^* + W_N^*/N} = \frac{W_1 + \bar{g}(N)W_N}{W_1 + \frac{\bar{g}(N)}{N}W_N}$$

(2.15)

In the proof of Theorem (1), we claimed that  $W_N^* = g(NM) = \bar{g}g(M)$ . This claim is true under two assumptions: 1) the data is shared by all available processors, and 2) all the available memory space is used for better solutions. A computation with the first property is called global computation. Equation (2.14) is the simplified memory-bounded speedup

for global computation when memory is fully used. In general, data may be duplicated on different nodes and the available memory may not be fully used for increased problem size. Replacing the function  $\bar{g}$  by a general function G, that is  $W_N^* = G(N)W_N$ , a more generalized theorem will be

**Theorem 2** If  $W_N^* = G(N)W_N$  for some function G, then

$$S_N^* = \frac{W_1 + G(N)W_N}{W_1 + \frac{G(N)}{N}W_N}.$$

(2.16)

**Proof:** If  $W_N^* = G(N)W_N$  for some integer N, then

$$S_N^* = \frac{W_1^* + W_N^*}{W_1^* + \frac{W_N^*}{N}} = \frac{W_1 + G(N)W_N}{W_1 + \frac{G(N)}{N}W_N}.$$

(2.17)

Equation (2.16) will be referred to as simplified memory-bounded (SMB) scaled speedup. SMB scaled speedup is determined by the function G(N), which represents how the change of memory will influence the change of problem size. When the problem size is independent of the system size, the problem size is fixed, G(N) = 1. In this case, SMB scaled speedup is the same as Amdahl's law, i.e., Eq.(2.16) and Eq.(2.12) are equivalent. The *local computation* model is one computation model studied in Section 3.2. In the local computation model, when more processors are available, work will be replicated on these available processors. Computation is done locally on each node, and communication between nodes is not required. In this case, when memory is increased N times, the workload also increases N times, i.e., G(N) = N. In this case, SMB scaled speedup is the same as Gustafson's scaled speedup. SMB scaled speedup contains both Amdahl's law and Gustafson's scaled speedup as its special cases. For most scientific and engineering applications, the computation requirement increases faster than the memory requirement. For these applications,  $\bar{g}(N) > N$  and memory-bounded speedup will likely give a higher speedup than fixed-time speedup.

The proposed scaled speedup formulation, Eq.(2.16), may not be easy to fully understand at first glance. Here we use matrix multiplication to illustrate it. A matrix often represents some discretized continuum. Enlarging the matrix size generally will lead to a more accurate solution for the continuum. For matrices with dimension n, the computation requirement of matrix multiplication is  $2n^3$  and the memory requirement is  $3n^2$  (roughly). Thus,

$$W_N = 2n^3, \qquad M = 3n^2.$$

Writing  $W_N$  as a function of M, we have

$$W_N = 2\left(\frac{M}{3}\right)^{\frac{3}{2}}.$$

This means that

$$W_N = g(M) = 2\left(\frac{M}{3}\right)^{\frac{3}{2}}, \quad \bar{g}(N) = N^{\frac{3}{2}}.$$

(2.18)

The simplified memory-bounded speedup for global computation will be

$$S_N^{\bullet} = \frac{W_1 + N^{\frac{3}{2}} W_N}{W_1 + N^{\frac{1}{2}} W_N}.$$

(2.19)

Global computation uses distributed local memories as a large shared memory. All the data is distributed and shared. When these local memories are used locally without sharing, the computation is local computation and  $W_N^* = Ng(M)$ . This means that  $\bar{g} = N$ . The speedup is

$$S_N^* = \frac{W_1 + NW_N}{W_1 + W_N},$$

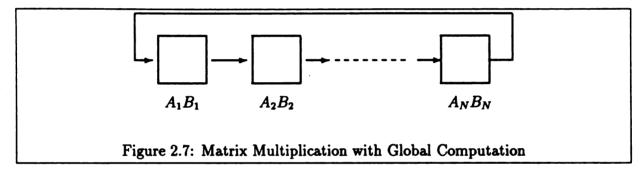

which is Gustafson's scaled speedup. For matrix multiplication C = AB, let  $A_i$  be the  $i^{th}$  row of A, i = 1, ..., n, and let  $B_j$  be the  $j^{th}$  column of B, i = 1, ..., n. The local computation and global computation of the matrix multiplication are shown in Figure (2.6) and (2.7), respectively. In global computation, the rows of matrix A are rotated after each row, column multiply.

We have studied two cases of memory-bounded scaled speedup, global computation and local computation. Most of the applications are some combination of these two computation styles. Data are distributed in one part and duplicated in the other part. The duplication may be required by inherent properties of the given application, or may be added in deliberately to reduce communication. Speedup formulations for these applications depend on the ratio of the global and the local computation. Deriving a speedup formulation for these combined applications is difficult, not only because we are facing a more complicated situation, but also because of the uncertainty of the ratio. The duplicated part might not increase with system size. It might increase, but with a speed which is different from the increasing speed of the global part. Also, an application may start as global computation, but, when the computation power increases, duplication may be added in as a part of the effort for a better solution. In general, G(N) is application dependent. We derive G(N) for a special case as an example. The structure of this derivation can be used as a guideline for general applications.

**Lemma 1** If function g is a semihomomorphism function,  $g(cx) = \overline{g}(c)g(x)$ ; and  $g^{-1}$  exists

and is also a semihomomorphism,  $g^{-1}(cx) = h(c)g^{-1}(x)$  for some function h, then  $\bar{g}$  has an inverse and  $\bar{g}^{-1} = h$ .

**Proof:** Since

$$cy = g[g^{-1}(cy)] = g[h(c)g^{-1}(y)] = \bar{g}[h(c)]g[g^{-1}(y)] = \bar{g}[h(c)]y,$$

we have

$$\bar{g}[h(c)] = c$$

for any real number c (2.20)

Also, since

$$cy = g^{-1}[g(cy)] = g^{-1}[\bar{g}(c)g(y)] = h[\bar{g}(c)]y,$$

we have

$h[\bar{g}(c)] = c$  for any real number c (2.21)

By Eq.(2.20) and Eq.(2.21), the function  $\bar{g}$  has an inverse and  $\bar{g}^{-1} = h$ .

**Theorem 3** Assume W = g(M) for some semihomomorphism function g, where  $g(cM) = \overline{g}(c)g(M)$ , g inverse exists and is a semihomomorphism. If the workload is scaled up to meet the time limitation with global computation first and the rest of the unused memory space is then used to increase the problem size further with local computation, we have

$$G(N) = (1 + \bar{g}[1 - \frac{\bar{g}^{-1}(N)}{N}])N.$$

(2.22)

**Proof:** By the fixed-time speedup, after the number of nodes changes from 1 to N, the parallel portion of work will increase from  $W_N$  to  $NW_N$  (see Figure 2.4). The storage requirement is given by the function  $g^{-1}$ . For operation requirement  $NW_N$ , the memory requirement is  $g^{-1}(NW_N) = \bar{g}^{-1}(N)g^{-1}(W_N)$ .

Let M represent the size of the memory associated with each node which can be used for parallel processing. Then, when the number of nodes equals 1, the total memory available is M, which is equal to  $g^{-1}(W_N)$ . When the number of nodes equals N, the total memory available changes to NM. We first fix the execution time and increase the problem size to meet the time limitation. After the fixed-time scale up, the unused memory space is the difference between current available memory and current memory requirement, which equals

$$NM - g^{-1}(NW_N) = NM - \bar{g}^{-1}(N)g^{-1}(W_N) = NM - \bar{g}^{-1}(N)M = (N - \bar{g}^{-1}(N))M.$$

The unused space at each node is

$$\frac{[N-\bar{g}^{-1}(N)]M}{N} = [1-\frac{\bar{g}^{-1}(N)}{N}]M.$$

The problem size can be further scaled by using this unused memory space. The further scaled computation on each node is given by the function g, and it is equal to

$$g\left(\left[1-\frac{\bar{g}^{-1}(N)}{N}\right]M\right) = \bar{g}\left(1-\frac{\bar{g}^{-1}(N)}{N}\right)g(M) = \bar{g}\left(1-\frac{\bar{g}^{-1}(N)}{N}\right)W_N \qquad (2.23)$$

Therefore, the computation on each node becomes

the original operation on each node + the operation increase on each node

$$= W_N + \bar{g}(1 - \frac{\bar{g}^{-1}(N)}{N})W_N = \left[1 + \bar{g}\left(1 - \frac{\bar{g}^{-1}(N)}{N}\right)\right]W_N, \qquad (2.24)$$

and, for the scaled parallel computation  $W_N^*$ ,

$$W_N^{\star} = N \left[ 1 + \bar{g} \left( 1 - \frac{\bar{g}^{-1}(N)}{N} \right) \right] W_N.$$

Thus, we have

$$G(N) = N[1 + \bar{g}(1 - \frac{\bar{g}^{-1}(N)}{N})].$$

(2.25)

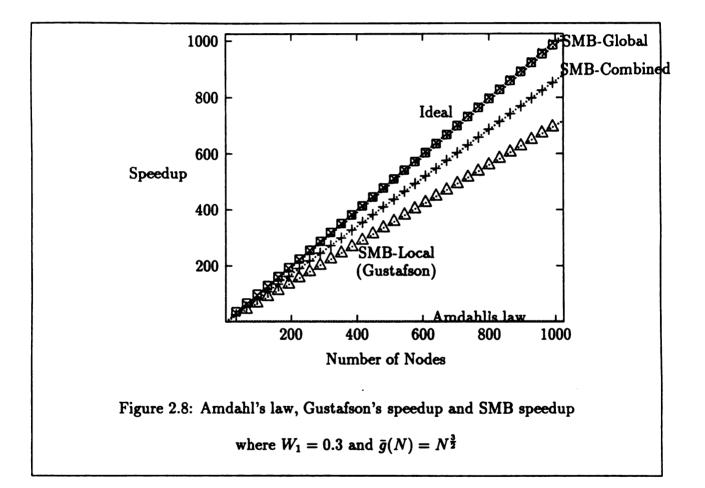

Figure 2.8 depicts the speedup difference among the fixed-sized model, the fixed-time model and the memory-bounded model. The function,  $\bar{g}$ , used in Figure 2.8 is the function for matrix multiplication,  $\bar{g}(N) = N^{\frac{3}{2}}$ . As most matrix computations have the same function  $\bar{g}(N) = N^{\frac{3}{2}}$ , the speedup relation depicted by Figure 2.8 is in general true for a large class of applications.

### 2.4 Comparison Study

It is known that the performance of parallel processing is influenced by the inherent parallelism of the application, by the computation power and by the memory capacity of the parallel computing system. However, how these three factors are related to each other, and how they influence the performance of parallel processing generally is unknown. Discovering

the answers to these unknowns is very important for designing efficient parallel algorithms and for constructing high performance parallel systems. In this paper one model of speedup, *memory-bounded speedup*, is carefully studied. This model is simple, and it contains all of these three factors as its parameters. It shows the degradations and the possible performance gain of parallel computation.

As part of the study on performance, two other models of speedup have also been studied. They are fixed-size speedup and fixed-time speedup. Two sets of speedup formulations have been derived for these two models of speedup and memory-bounded speedup. Formulations in the first set are general speedup formulas. These formulas contain more parameters and provide more accurate information. The second set of formulations only considers a special, simplified case. These formulations give the performance in principle and lead to a better understanding of parallel processing. The simplified fixed-size speedup is Amdahl's law, the simplified fixed-time speedup is Gustafson's scaled speedup, and the simplified memorybounded speedup contains both Amdahl's law and Gustafson's speedup as special cases. Amdhal's law suggests that the sequential portion of the workload will dominate the performance when the number of processors is large. Gustafson' scaled speedup claims that the influence of the sequential portion is independent of system size. Simplified memorybounded scaled speedup declares that the sequential fraction will change with the system size. Since the computation requirement increases faster than the memory requirement for most applications, the sequential fraction could be reduced when the number of processors increases.

The three models of speedup, fixed-size speedup, fixed-time speedup and memory-bounded speedup, are based on different viewpoints and are suitable for different classes of applications. Applications exist which do not fit any of the models of speedup, but satisfy some combination of the models.

## Chapter 3

# PARALLEL COMPUTATION MODELS FOR SCIENTIFIC COMPUTING

With more than one processor operating concurrently, parallel processing enlarges the range of possible performance and makes efficient algorithm design more important. We have studied performance metrics in the previous chapter. In this chapter, we focus on designing parallel algorithms, with emphasis on methodology and analysis.

One of the factors that makes parallel algorithm design difficult is the lack of guidelines. Different applications are rarely related to each other in the design process. Therefore, they have to be handled one by one in an *ad hoc* fashion. The experience of experts hardly benefits general users. In Section 3.1, we propose a representation system, called structured representation, for scientific and engineering applications. With this representation, the similarities between applications become obvious and applications can be compared, classified, and manipulated based on their structures. Developing structured representation is the first step toward the ultimate goal, replacing the *ad hoc* development of parallel applications with a rational methodology based on analysis and measurement.

A parallel algorithm cannot be efficient without considering the architectural aspects of the underlying multiprocessor. This is especially true for multicomputers where communication overhead is a major consideration. Mapping an application onto an architecture is both application dependent and architecture dependent. To lead to a systematic mapping, the basic building blocks of structured representation are identified and studied in Section 3.2. With structured representation, an application can be decomposed into a set of computational models which can be mapped onto the architecture using predefined strategies. We can modify our design by changing certain computation models. In this way, structured design and rethinking become possible. Casual users can develop efficient algorithms based on experts' experience. A general guideline for efficient algorithm design is provided.

#### **3.1** Structured Representation

Parallelism can be achieved by dividing a given application into pieces, called *subtasks*, and solving these pieces concurrently. Ideally, these subtasks can be solved independently, where the exchange of intermediate result is negligible. Some scientific and engineering applications have this nice, *easy parallelism* property. For these applications, it is natural to solve each of the subtasks locally on a different processor. This model of computation is called a *local computation model*.

The design of local computation algorithms is straightforward. Unfortunately, most applications do not have this easy parallelism property [1]. For most applications communication is necessary for exchanging data and coordinating activities. Although various asynchronous techniques have been designed to reduce the communication overhead, most communication must be achieved in a synchronous fashion, that is the receiving node must receive the communicated message before continuing. This synchronous communication requirement makes efficient algorithm design very difficult. The load needs to be balanced between synchronizations and special care has to be taken to reduce the communication overhead. Figure 3.1 depicts the general parallel computation pattern with synchronous communication considered. It shows that the solving process consists of two phases, compute and data-exchange. These two phases occur alternatively and repetitively, and, therefore, form the *computeexchange computation*. The data-exchange phase involves communication between compute phases. The communication patterns vary largely from application to application, and may be represented by a notation. To simplify this notation, we restrict ourselves to certain classes of communication, which are large enough for our purposes – describing the most frequently used scientific and engineering applications.

A processor sending a message in a communication is called a sender. A processor receiving message in a communication is called a receiver. A processor could be both sender and receiver in a communication. A graph G(V, E) is a structure which consists of a set of vertices  $V = \{v_1, v_2, ...\}$  and a set of edges  $E = \{e_1, e_2, ...\}$  [17]. If we let processors in a communication be vertices in a graph and add directed edge (v, w) from v to w if processor v sends a message to processor w; a digraph (directed graph) is formed. This digraph is called the communication digraph. Following the notations of graph theory [17], the outdegree of a vertex v is the number of edges which have v as their start-vertex. In other words, the outdegree of a vertex v is equal to the number of destinations that v sends its message to. For this reason we also call the outdegree of a vertex the degree of a sender. The indegree of a vertex and the degree of a receiver are defined similarly. The degree of a receiver is the number of sources from which it receives messages.

**Definition 5** A regular communication is a communication in which all senders have the same degree and all receivers have the same degree.

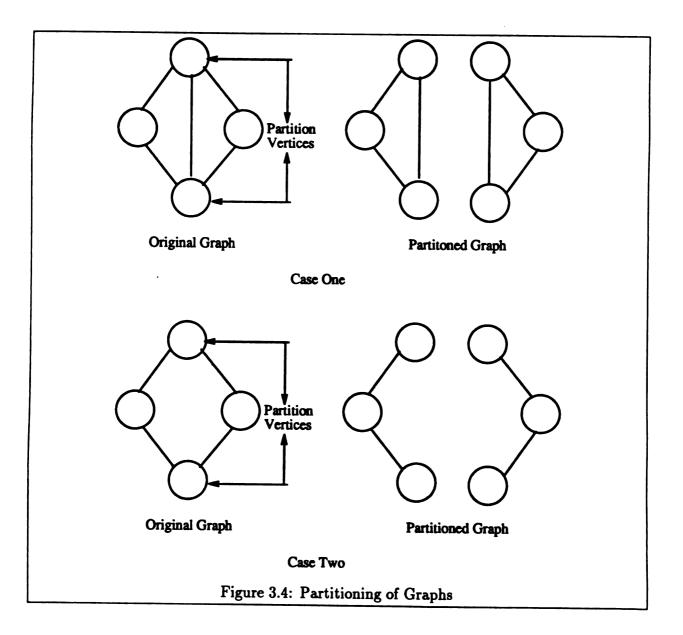

For a given undirected graph, if for every two vertices u and v there exists a path whose starting vertex is u and whose ending vertex is v, then the graph is connected. A connected subgraph G(V', E') is a connected component if there is no other connected subgraph containing G(V', E') as its proper subgraph.

The underlying (undirected) graph of a digraph is the graph resulting from the digraph if the direction of the edges is ignored. A connected component of a digraph is the corresponding subdigraph of the connected component of its underlying graph.

A connected component of the communication digraph is called a pattern of the communication.

**Definition 6** A regular communication is a regular data-exchange if it consists of one or more copies of the same pattern.

By our definition, the communication requirement of a regular data-exchange is given by the number of patterns it contains. The pattern of a communication is described by the number of senders and the number of receivers in this pattern. The complexity of each sender and of each receiver is given by its degree. Thus, a regular data-exchange can be represented using five parameters as

$$P[S(D), R(d)], \tag{3.1}$$

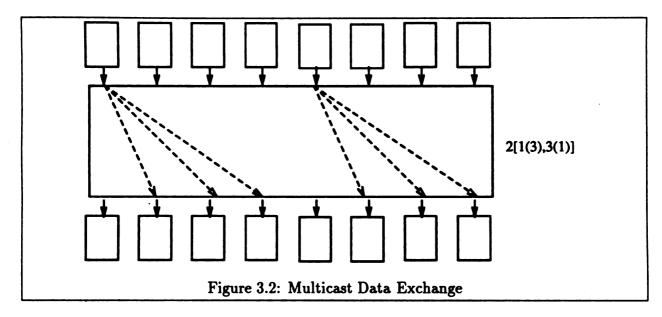

where P is the number of instance of the pattern, S is the number of senders in each instance of the pattern, and D is the degree of the senders. Similarly, R is the number of receivers in each instance of the pattern, and d is the degree of each receiver. An example of using this notation for presenting communication is given in Figure 3.2. Notation (3.1) describes a communication by five parameters. Since broadcast is not provided in neither first generation nor second generation multicomputers, messages must be sent one at a time. The number of times messages are sent and received is the dominant factor in communication may be needed when implementation is considered.

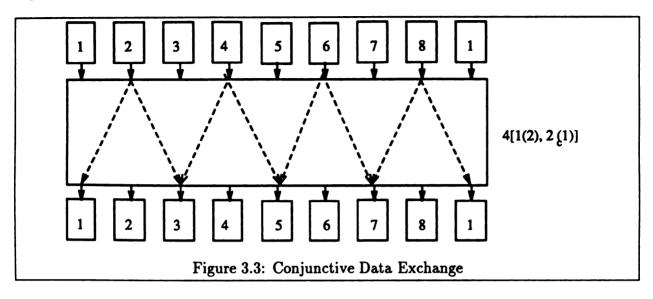

The second class of data-exchange which we want to identify is called *conjunctive regular data-exchange*. We use the same five parameters to identify conjunctive regular dataexchange. The difference between regular data-exchange and conjunctive regular dataexchange is that in conjunctive regular data-exchange the patterns are not disjoint, they conjoin one another. Consider two special cases: conjunction at the sender side only and conjunction at the receiver side only. We have two general notations,

$$P[S(D), R_c(d)], \tag{3.2}$$

and

$$P[S_c(D), R(d)], \tag{3.3}$$