1710316

#### This is to certify that the

#### dissertation entitled

A Framework for Multiprocessor Performance Characterization and Calibration

presented by

Arun K. Nanda

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Computer Science

Major professor

Date 10/12/92

## LIBRARY Michigan State University

PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due.

| DATE DUE | DATE DUE | DATE DUE |

|----------|----------|----------|

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

MSU is An Affirmative Action/Equal Opportunity Institution

# A Framework for Multiprocessor Performance Characterization and Calibration

$\mathbf{B}\mathbf{y}$

Arun K. Nanda

### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Computer Science

1992

#### ABSTRACT

# A Framework for Multiprocessor Performance Characterization and Calibration

$\mathbf{B}\mathbf{y}$

#### Arun K. Nanda

In parallel programs using the shared-variable paradigm, run-time communication overhead manifests itself along three principal dimensions, namely, shared data accesses (including memory contention, cache misses and non-local memory access latencies), inter-process synchronization operations, and global barrier synchronizations. Performance measurements to quantify the rate at which communication costs for an algorithm increases as more processors are used is integral to the study of an algorithm's efficiency and scalability. In this thesis, we explore the problem of performance characterization of a multiprocessor in the context of the shared-variable programming model with emphasis on characterizing the dynamic run-time behavior.

We have developed a hierarchical model to characterize multiprocessor system performance using a multi-phase computation structure with concurrent asynchronous execution within a phase. Two sets of system characterization parameters have been proposed that completely describe the static and dynamic behavior of a given input workload on a target multiprocessor system. The characterization parameters are calibrated by experimental measurements on the input workload. A series of loss functions are formulated to describe the performance degradation resulting from static and dynamic overheads, thus providing realistic estimates of performance loss.

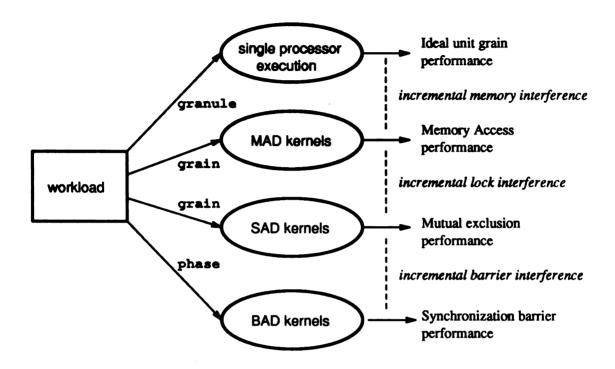

Since the characterization of performance is tied inextricably with the input workload, we have presented a flexible technique for benchmark workload generation, that can be tailored to fit a user's preference for selective workload characteristics. A family of workload emulation kernels, namely, the MAD, SAD and BAD kernels, have been designed to isolate and measure the incremental impact of memory contention, critical sections and barrier synchronization on performance, repectively, to calibrate the hierarchical performance model. We have demonstrated the applicability of the system characterization methodology and the effectiveness of the workload emulation kernels by evaluating the performance of several synthetic workloads on the Sequent Symmetry and BBN TC2000 commercial multiprocessors.

The proposed methodology is independent of any particular architecture or application. We believe that our approach to performance characterization will serve to model performance with greater fidelity than exists in the current state of art, since it incorporates the effect of both static and dynamic influences in a workload execution. Since a shared-variable programming paradigm is only assumed with no assumptions made about the organization of the shared address space, our framework can be used equally effectively to evaluate multiprocessors that provide a physical shared memory or highly-parallel systems that support a shared virtual memory.

Copyright © by Arun K. Nanda 1992 To my parents

#### **ACKNOWLEDGEMENTS**

I would like to take this opportunity to express my appreciation to those who have contributed to the completion of this dissertation. I will always be indebted to my advisor, Lionel Ni. He has been my mentor, my colleague, and my friend. His guidance has helped me mature as a researcher, and his respect for my ideas has made working with him very rewarding. I look forward to many fruitful interactions with him in the future.

I am very grateful to the other members of my dissertation committee: Richard Enbody, for his invaluable discussions on numerous occasions and comments to improve the readability of this thesis, his perpetual willingness to listen to whatever I had to say, be it research related or otherwise, and offer friendly advice; Abdol Esfahanian, for being my faculty advisor for two years, his critical suggestions on some aspects of this thesis, and for his time and support; V. Mandrekar, for his continuous encouragement and always accommodating me in his schedule at short notice.

I would like to thank the members of the Advanced Computing Research Facility at Argonne National Laboratory, especially Dave Levine, for providing me access to their computer systems and their help in arranging my special job scheduling requests.

My thanks to Honda Shing and Ten-Hwan Tzen for many enlightening discussions on research issues.

A person cannot accomplish anything without the help and understanding of family members. My mother's constant encouragement, in spite of her personal hardships, inspired me to do my best. My brother and sister always stood behind all my decisions. My father- and mother-in-law offered their patient understanding throughout the course of my doctorate work. I proudly share this accomplishment with them all.

Finally, my very special thanks to my wife Susmita, for sustaining me with her continuous love and understanding, and spending many a sleepless nights with me during my work to keep me company.

# TABLE OF CONTENTS

| L  | ST ( | OF TABLES                              | x          |

|----|------|----------------------------------------|------------|

| Ll | ST ( | OF FIGURES                             | хi         |

| 1  | INI  | TRODUCTION                             | 1          |

|    | 1.1  | Multiprocessor Performance Evaluation  | 2          |

|    | 1.2  | Survey of Benchmarks                   | 8          |

|    |      | 1.2.1 Synthetic Benchmarks             | 8          |

|    |      | 1.2.2 Kernel Benchmarks                | 9          |

|    |      | 1.2.3 Application Benchmarks           | 10         |

|    | 1.3  | Motivation and Problem Definition      | 10         |

|    | 1.4  | Objective and Scope of Research        | 14         |

|    | 1.5  | Thesis Outline                         | 20         |

| 2  | BA   | CKGROUND                               | 21         |

|    | 2.1  | Multiprocessor Memory Organization     | 21         |

|    | 2.2  | Limitations to Parallelism             | 24         |

|    |      | 2.2.1 Memory Access Contention         | 25         |

|    |      | 2.2.2 Spin Locks and Mutual Exclusion  | 31         |

|    |      | 2.2.3 Synchronization Barriers         | <b>3</b> 8 |

|    | 2.3  | Target System Architectures            | 40         |

|    | 2.4  | Summary                                | 45         |

| 3  | PE   | RFORMANCE CHARACTERIZATION METHODOLOGY | 46         |

|    | 3.1  | The Parallel Computation Model         | 47         |

|    | 3.2  | Workload Characterization              | 50         |

|    |      | 3.2.1 The Unit Grain                   | 51         |

|    |      | 3.2.2 Workload Classification          | 53         |

|    | 3.3  | Experimental Framework                 | 55         |

|    |      | 3.3.1 Measurement Structure            | 55         |

|    |      | 3.3.2 Workload Generation              | 50         |

|   | 3.4        | Perfor | mance Characterization Parameters     | 60  |

|---|------------|--------|---------------------------------------|-----|

|   |            | 3.4.1  | Static Parameters                     | 61  |

|   |            | 3.4.2  | Dynamic Parameters                    | 67  |

|   |            | 3.4.3  | Performance Metrics                   | 72  |

|   |            | 3.4.4  | Aggregate Multiphase Performance      | 74  |

|   | 3.5        | The V  | Vorkload Emulation Kernels            | 75  |

|   |            | 3.5.1  | Measurement of Incremental Overheads  | 76  |

|   |            | 3.5.2  | Kernel Structure                      | 78  |

|   |            | 3.5.3  | Minimization of Experimental Errors   | 80  |

|   | 3.6        | Summ   | nary                                  | 83  |

| 4 | MA         | D KE   | RNELS AND MEMORY ACCESS PERFORMANCE   | 85  |

|   | 4.1        | Prelin | ninary Studies                        | 86  |

|   |            | 4.1.1  | Workload Parameters                   | 86  |

|   |            | 4.1.2  | Quantities Measured                   | 88  |

|   |            | 4.1.3  | Memory Access Overhead Factors        | 88  |

|   |            | 4.1.4  | Experimental Results                  | 94  |

|   | 4.2        | MAD    | Workload Parameters                   | 97  |

|   |            | 4.2.1  | Unit Grain Characterization           | 98  |

|   |            | 4.2.2  | Output Metrics                        | 102 |

|   | 4.3        | Concu  | nrrent-Access Workloads               | 103 |

|   |            | 4.3.1  | Homogenous Workloads                  | 103 |

|   |            | 4.3.2  | Heterogenous Workloads                | 111 |

|   | 4.4        | Dual-  | Mode Access Workloads                 | 114 |

|   | 4.5        | Summ   | nary                                  | 115 |

| 5 | SA         | D KEI  | RNELS AND SYNCHRONIZATION PERFORMANCE | 117 |

|   | 5.1        | Prelin | ninary Studies                        | 118 |

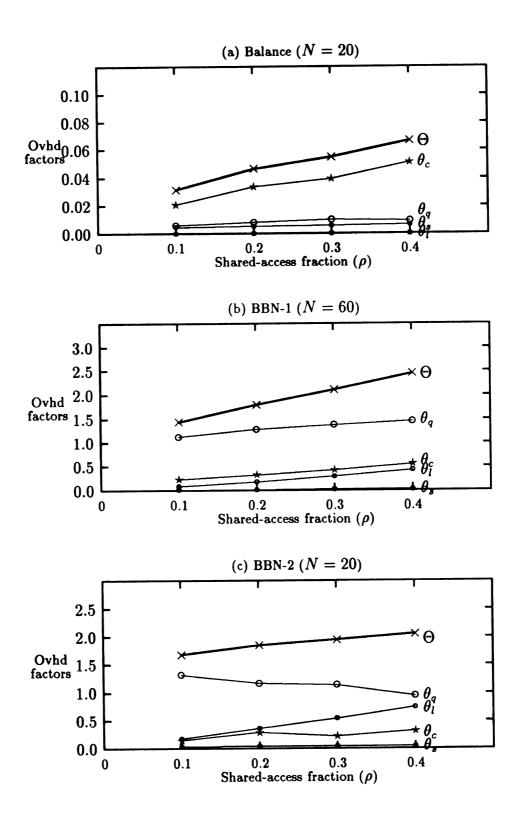

|   |            | 5.1.1  | Synchronization Overhead Factors      | 119 |

|   |            | 5.1.2  | Experimental Results                  | 121 |

|   | <b>5.2</b> | SAD    | Workload Parameters                   | 130 |

|   |            | 5.2.1  | Unit Grain Characterization           | 130 |

|   |            | 5.2.2  | Output Metrics                        | 132 |

|   |            | 5.2.3  | Lock Implementations Studied          | 133 |

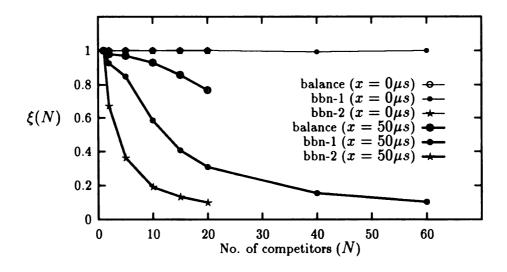

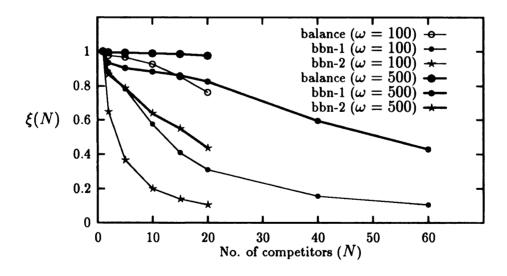

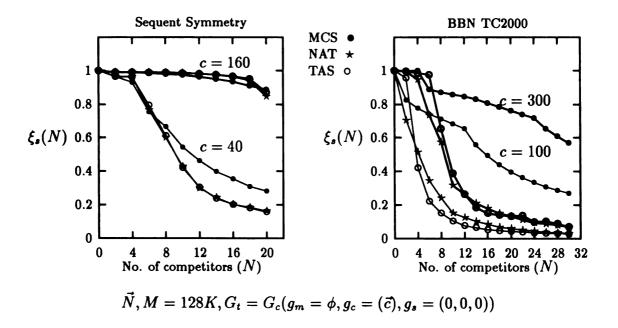

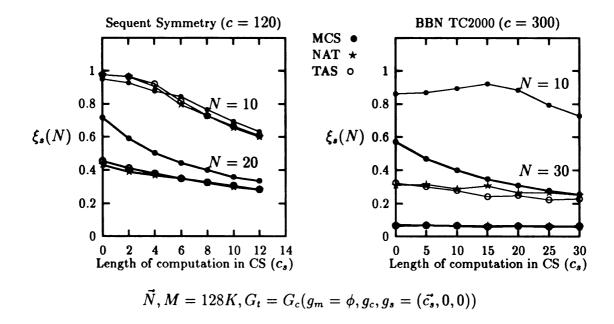

|   | 5.3        | Exclu  | sive-Access Workloads                 | 137 |

|   | <b>5.4</b> | Dual-  | Mode Access Workloads                 | 144 |

|   |            | 5.4.1  | Homogenous Workloads                  | 144 |

|   |            | 5.4.2  | Heterogenous Workloads                | 147 |

|          | 5.5  | Summary                                       | 150 |

|----------|------|-----------------------------------------------|-----|

| 6        | BA   | D KERNELS AND BARRIER PERFORMANCE             | 152 |

|          | 6.1  | BAD Workload Parameters                       | 153 |

|          |      | 6.1.1 Phase Characterization                  | 153 |

|          |      | 6.1.2 Output Metrics                          | 154 |

|          |      | 6.1.3 Barrier Implementations Studied         | 155 |

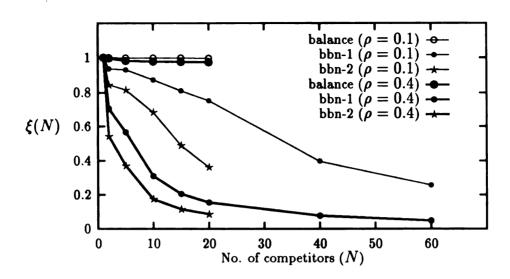

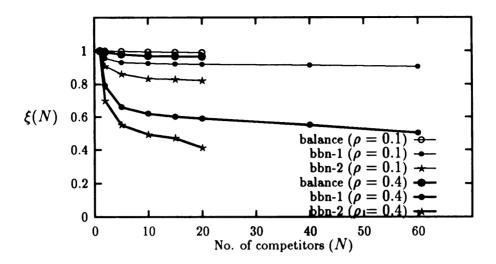

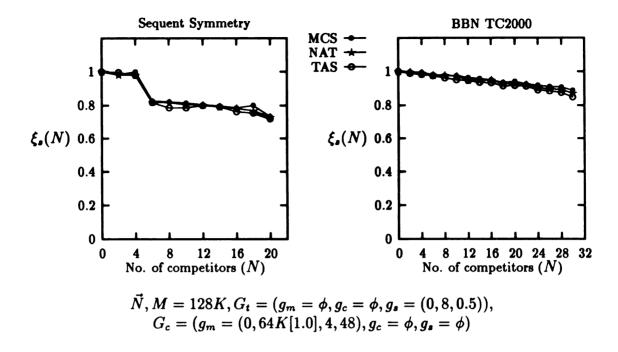

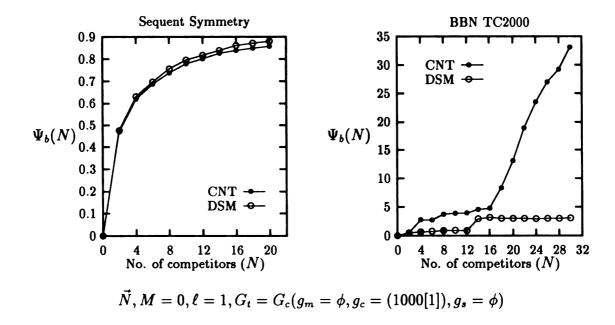

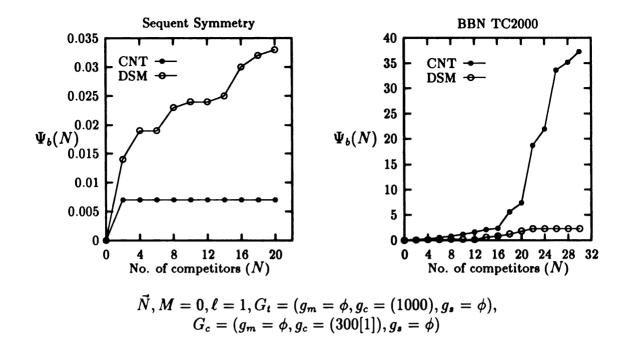

|          | 6.2  | Embarrassing Workloads                        | 158 |

|          |      | 6.2.1 Scalability of Barrier Implementations  | 162 |

|          |      | 6.2.2 Balanced Load and Simultaneous Arrivals | 162 |

|          |      | 6.2.3 Unbalanced Load and Staggered Arrivals  | 164 |

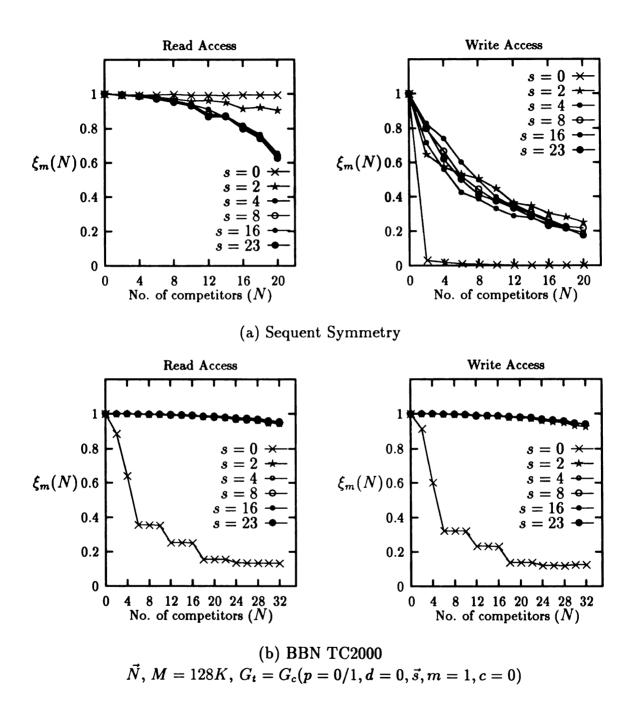

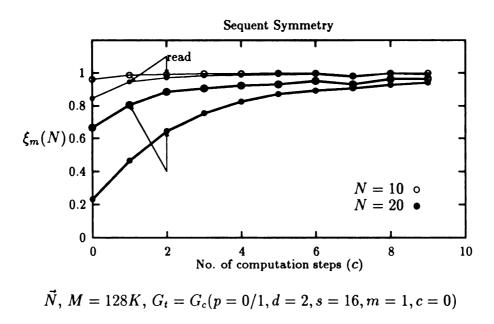

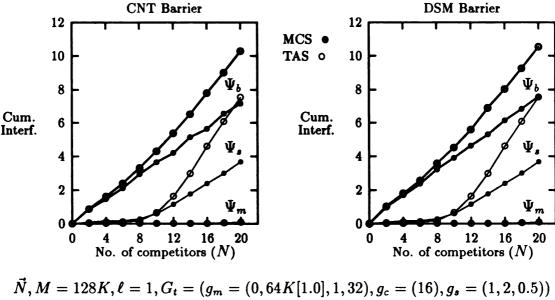

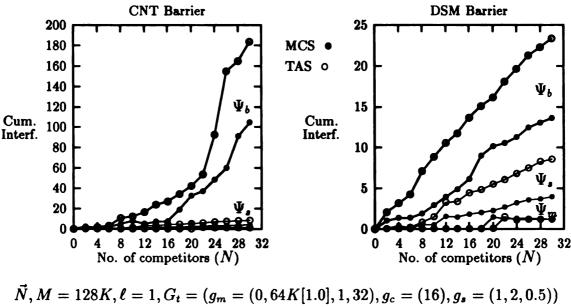

|          | 6.3  | Dual-Mode Access Workloads                    | 166 |

|          | 6.4  | Summary                                       | 169 |

| 7        | CO   | NCLUSIONS                                     | 171 |

|          | 7.1  | Research Contributions                        | 171 |

|          | 7.2  | Directions for Future Research                | 174 |

| <b>B</b> | IBLI | OGRAPHY                                       | 176 |

# LIST OF TABLES

| 1.1 | Performance level comparisons for three classes of multiprocessors                                                                          | 5   |  |  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| 2.1 | Summary of target system architectures                                                                                                      |     |  |  |

| 3.1 | An example of weights assigned to different types of floating-point operations to normalize their execution time to floating-point addition |     |  |  |

|     | time                                                                                                                                        | 53  |  |  |

| 3.2 | Summary of average shared data access time $t_m$                                                                                            | 63  |  |  |

| 3.3 | System characterization parameters                                                                                                          | 72  |  |  |

| 3.4 | Application parameters used in the performance model                                                                                        | 72  |  |  |

| 3.5 | Summary of access degradation kernel measurements                                                                                           | 79  |  |  |

| 0.0 | building of access degradation former measurements                                                                                          | ••  |  |  |

| 4.1 | Basic time measurements for the overhead factors model                                                                                      | 90  |  |  |

| 4.2 | Parameter settings for different workload types used in the preliminary                                                                     | 95  |  |  |

| 4.0 | studies                                                                                                                                     |     |  |  |

| 4.3 | Unit grain attributes for studying memory access behavior                                                                                   | 99  |  |  |

| 4.4 | Static characterization parameters for a homogenous workload with                                                                           | 100 |  |  |

|     | $M = 128K, G_t = G_c = (g_m = (0/1, 0, \vec{s}, 1), g_c = \phi, g_s = \phi)$                                                                | 106 |  |  |

| 5.1 | Actual execution times $(M = N + 1, \omega = 500, x = 50 \mu s)$                                                                            | 128 |  |  |

| 5.2 | Actual overhead times $(M = N + 1, \omega = 500, x = 50\mu s)$                                                                              | 128 |  |  |

| 5.3 | Unit grain attributes for studying synchronization behavior                                                                                 | 131 |  |  |

| 5.4 | Native lock support on each machine                                                                                                         | 134 |  |  |

| 5.5 | Pseudo-code for the TAS lock                                                                                                                | 134 |  |  |

| 5.6 | Latency of locks used in the SAD experiments                                                                                                | 138 |  |  |

| 5.7 | Half-performance lock factor $c_{1/2}$ for different lock implementations.                                                                  | 139 |  |  |

| 5.8 | Static characterization parameters for workloads used in incremental                                                                        |     |  |  |

|     | overhead measurements                                                                                                                       | 146 |  |  |

| 6.1 | Workload parameters for studying barrier performance                                                                                        | 153 |  |  |

# LIST OF FIGURES

| 1.1 | Performance measurement levels                                            | 4   |  |  |  |

|-----|---------------------------------------------------------------------------|-----|--|--|--|

| 1.2 | Steps in the experimental performance characterization method 1           |     |  |  |  |

| 2.1 | Organization of memory hierarchy in shared-memory multiprocessors         | 23  |  |  |  |

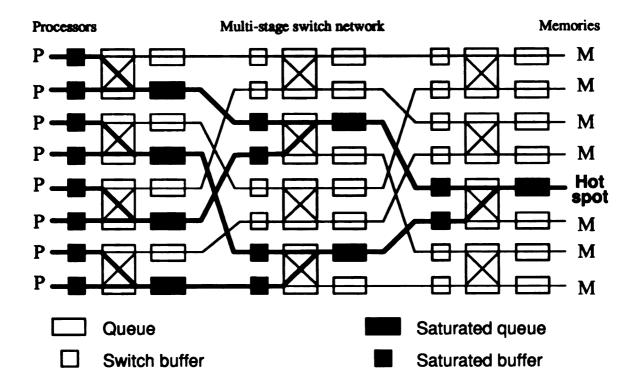

| 2.2 | Tree saturation as a result of hot spot accesses over a multistage inter- |     |  |  |  |

|     | connection network                                                        | 27  |  |  |  |

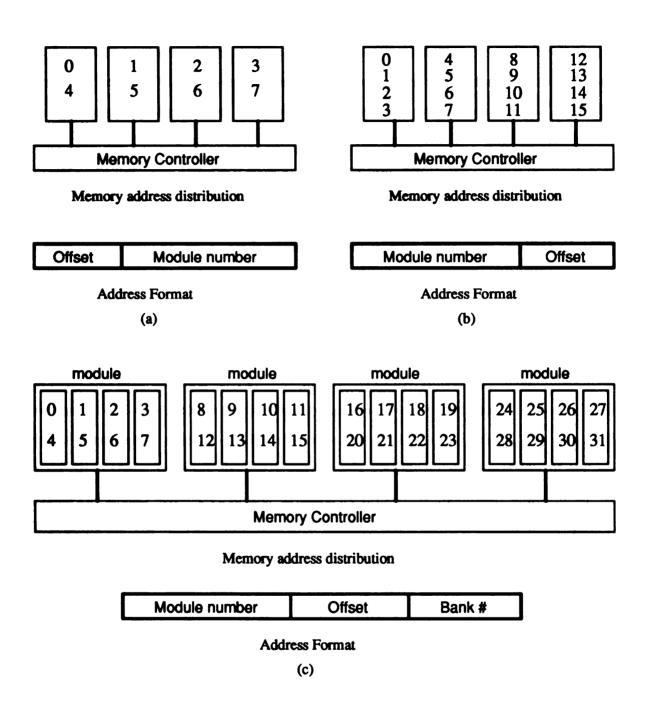

| 2.3 | Memory address interleaving techniques: (a) Fine interleaving with se-    |     |  |  |  |

|     | quential assignment across modules (one bank per module); (b) Coarse      |     |  |  |  |

|     | interleaving with sequential assignment within module (one bank per       |     |  |  |  |

|     | module); (c) Mixed scheme with fine interleaving among banks of a         |     |  |  |  |

|     | module and coarse interleaving among modules (multiple banks per          |     |  |  |  |

|     | module)                                                                   | 29  |  |  |  |

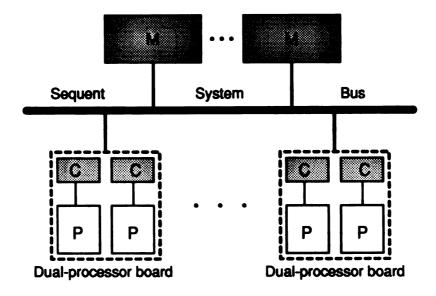

| 2.4 | Sequent Symmetry system architecture                                      | 41  |  |  |  |

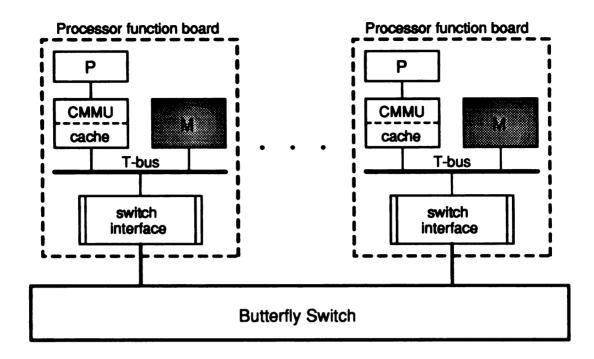

| 2.5 | BBN TC2000 system architecture                                            | 42  |  |  |  |

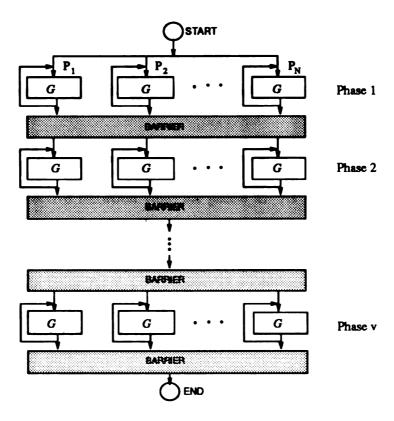

| 3.1 | Structure of parallel program execution                                   | 49  |  |  |  |

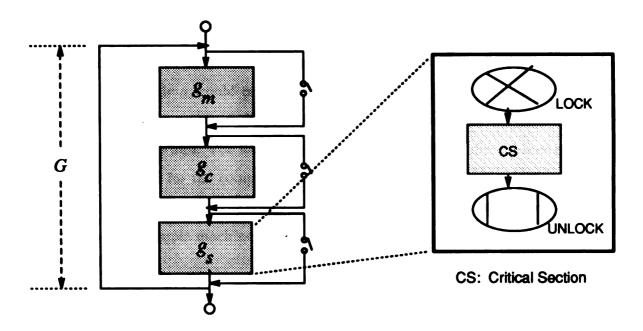

| 3.2 | Structure of a unit grain                                                 | 52  |  |  |  |

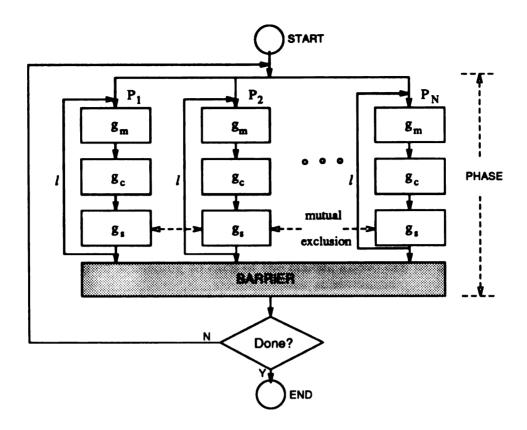

| 3.3 | Structure of a single computational phase                                 | 54  |  |  |  |

| 3.4 | Structure of the measurement framework                                    | 56  |  |  |  |

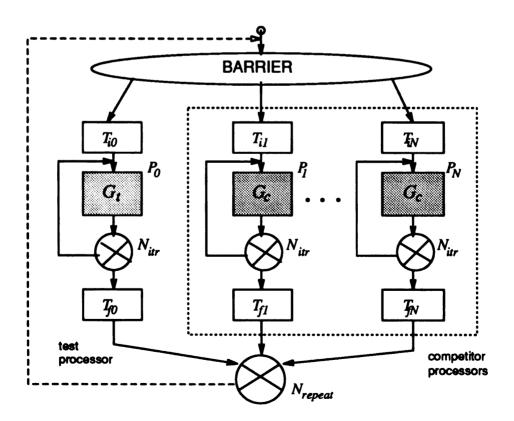

| 3.5 | Incremental measurement of dynamic overheads                              | 77  |  |  |  |

| 3.6 | The concurrent loop structure of the kernels                              | 80  |  |  |  |

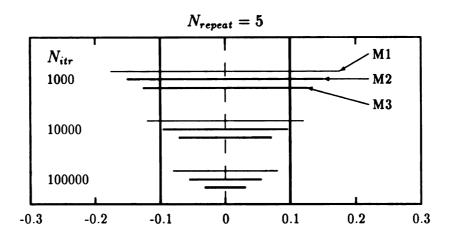

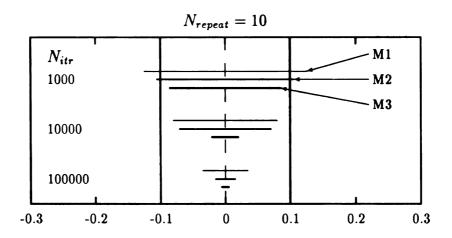

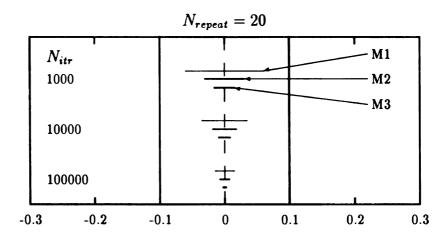

| 3.7 | Normalized 90 percent confidence intervals for three workload mea-        |     |  |  |  |

|     | surements on the Sequent Symmetry for $N_{repeat} = 5, 10, 20$            | 82  |  |  |  |

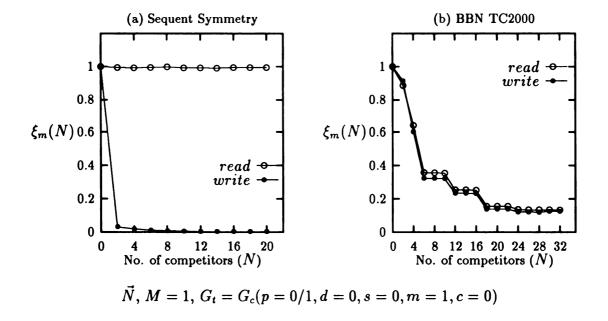

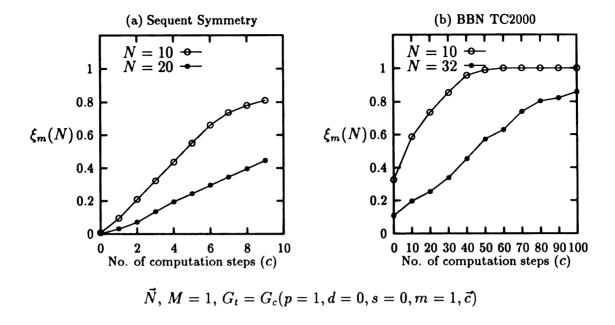

| 4.1 | Efficiency vs. $N$ $(M=1,\omega=100,x=0)$                                 | 96  |  |  |  |

| 4.2 | Efficiency vs. $N$ $(M = N + 1, \omega = 100, x = 0)$                     | 97  |  |  |  |

| 4.3 | Creation of memory access patterns using attributes $d$ and $s$           | 100 |  |  |  |

| 4.4 | Effect of spatial distribution of memory access stream on performance     | 105 |  |  |  |

| 4.5 | Effect of temporal distribution of memory access stream on performance    | 107 |  |  |  |

| 4.6 | Effect of contention for a memory location (hot-spot) on performance      | 108 |  |  |  |

| 4.7 | Effect of length of computation on hot-spot write performance             | 109 |  |  |  |

| 4.8        | Effect of shared-data size on read performance                            |     |  |  |  |

|------------|---------------------------------------------------------------------------|-----|--|--|--|

| 4.9        | Random access performance expressed in MegaWARPS                          |     |  |  |  |

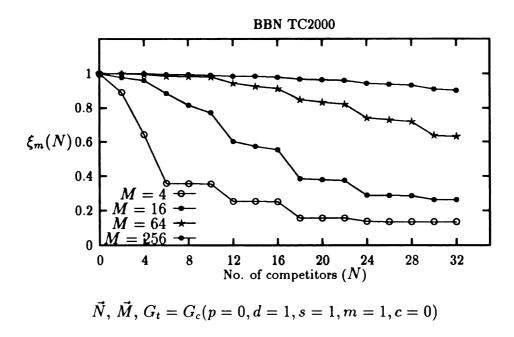

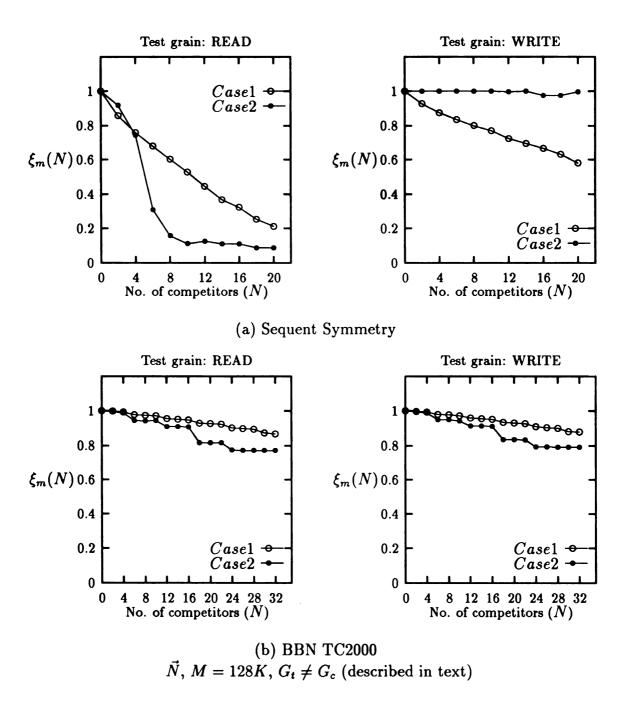

| 4.10       | Interaction between read and write memory-access streams                  |     |  |  |  |

| 4.11       | Effect of length of computation on interference between read and write    |     |  |  |  |

|            | streams                                                                   | 114 |  |  |  |

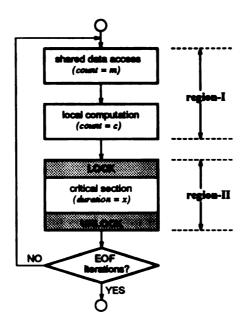

| 5.1        | Generic structure of program executed by every processor                  | 119 |  |  |  |

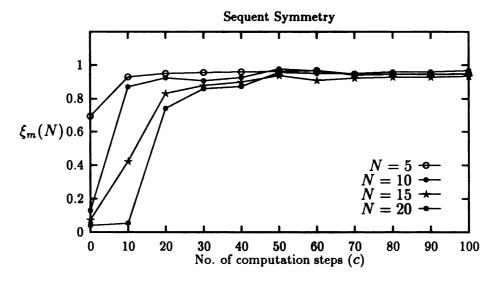

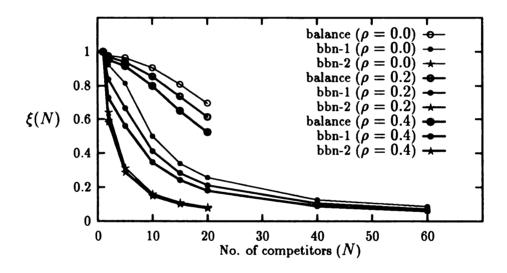

| <b>5.2</b> | Efficiency vs. $N$ $(M = N + 1, \omega = 100, \rho = 0)$                  | 121 |  |  |  |

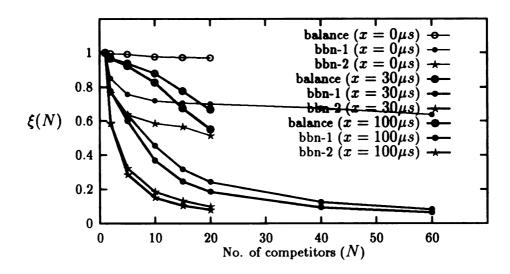

| <b>5.3</b> | Efficiency vs. $N \ (M = N + 1, \rho = 0.1, x = 30 \mu s) \dots$          | 122 |  |  |  |

| 5.4        | Efficiency vs. $N$ $(M = N + 1, \omega = 100, x = 100 \mu s)$             | 123 |  |  |  |

| 5.5        | Efficiency vs. $N$ $(M = N + 1, \omega = 100, \rho = 0.3)$                | 124 |  |  |  |

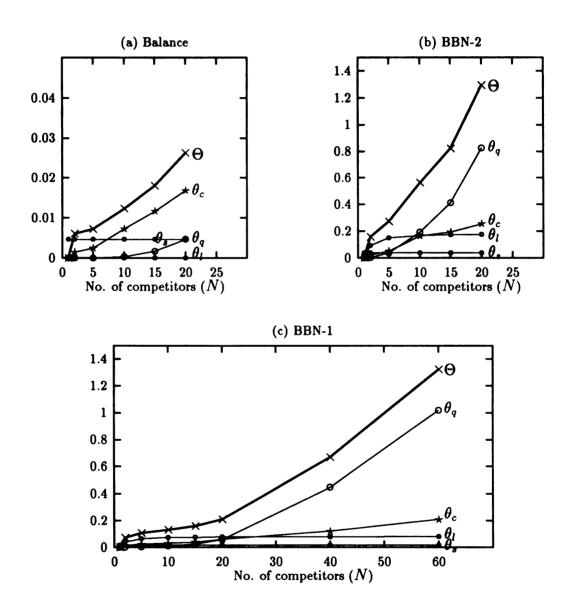

| 5.6        | Overhead components vs. $N$ ( $M=N+1, \omega=500, \rho=0.1, x=30 \mu s$ ) | 126 |  |  |  |

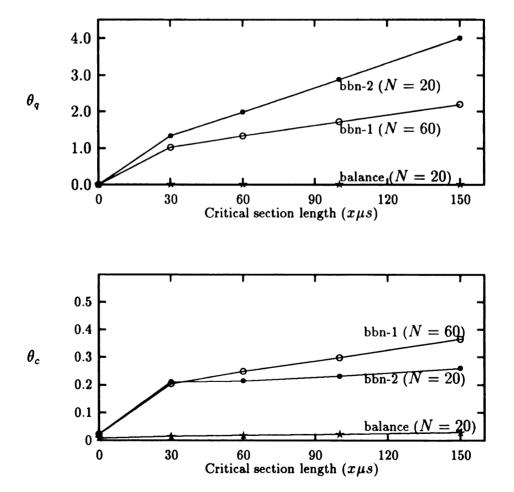

| 5.7        | Overhead components vs. $x$ $(M = N + 1, \omega = 500, \rho = 0.1)$       | 127 |  |  |  |

| 5.8        | Overhead components vs. $\rho$ $(M = N + 1, \omega = 500, x = 50\mu s)$   | 129 |  |  |  |

| 5.9        | Critical section structure                                                | 132 |  |  |  |

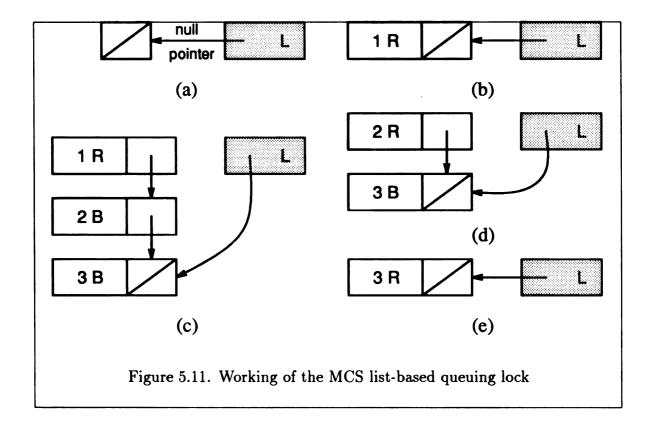

| 5.10       | Pseudo-code for the MCS list-based queuing lock                           | 136 |  |  |  |

| 5.11       | Working of the MCS list-based queuing lock                                | 137 |  |  |  |

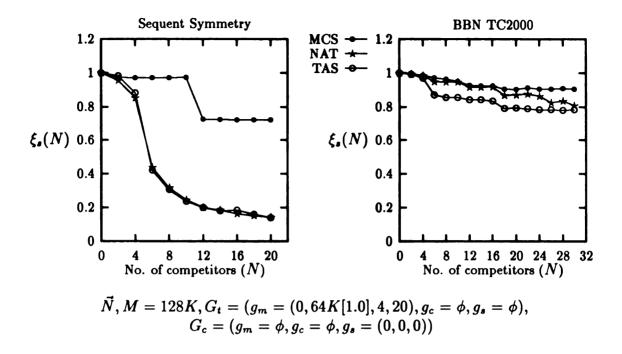

| 5.12       | Effect of frequency of CS on performance                                  | 141 |  |  |  |

| 5.13       | Effect of non-CS to CS computation ratio on performance                   | 143 |  |  |  |

| 5.14       | Effect of non-CS to CS shared data access ratio on performance            | 145 |  |  |  |

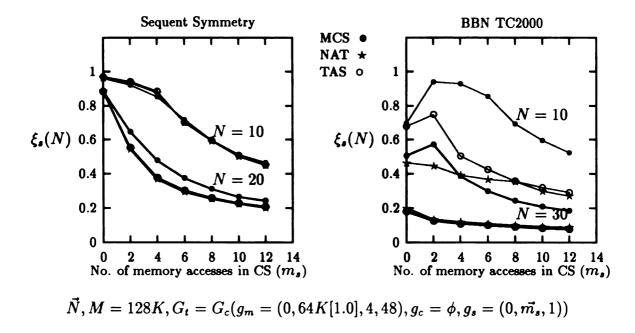

| 5.15       | Incremental interference measured with stride of access $s=1$             | 147 |  |  |  |

| 5.16       | Incremental interference measured with stride of access $s=23$            | 148 |  |  |  |

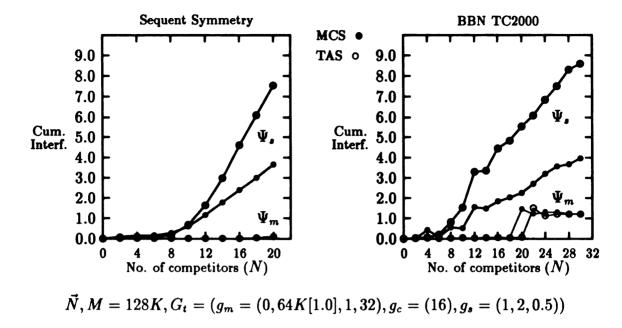

| 5.17       | Impact of non-CS memory accesses on CS execution performance              | 149 |  |  |  |

| 5.18       | Impact of CS spin-lock on non-CS memory accesses                          | 150 |  |  |  |

| 6.1        | Pseudo-code for a sense reversing centralized barrier                     | 155 |  |  |  |

| 6.2        | Pseudo-code for a distributed dissemination barrier                       | 157 |  |  |  |

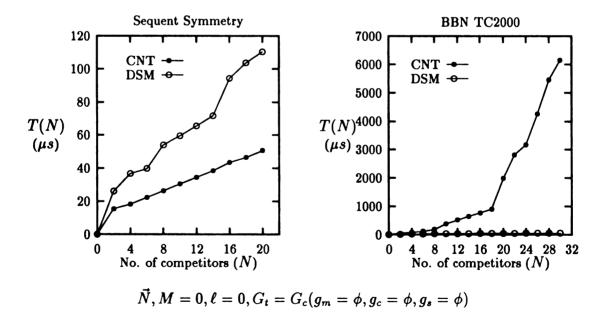

| 6.3        | Time to achieve barrier vs. $N$                                           | 161 |  |  |  |

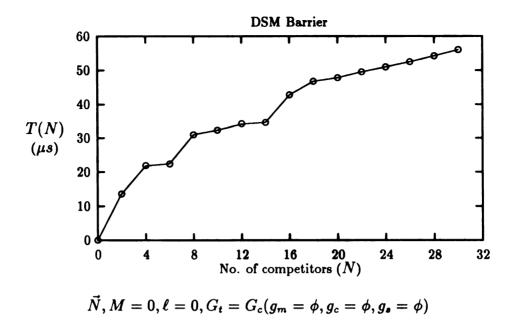

| 6.4        | Time to achieve DSM barrier on the TC2000                                 | 163 |  |  |  |

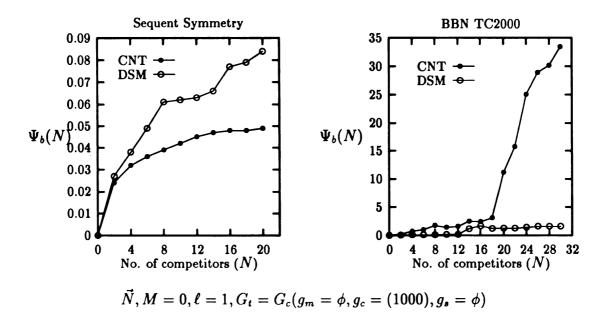

| 6.5        | Barrier performance of a perfectly balanced load                          | 164 |  |  |  |

| 6.6        | Barrier performance of an unbalanced load                                 | 165 |  |  |  |

| 6.7        | Performance of staggered arrivals at the barrier                          | 167 |  |  |  |

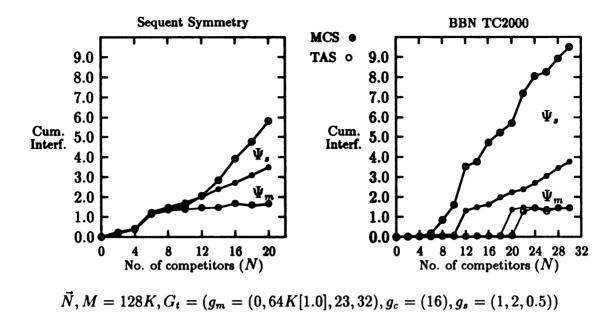

| 6.8        | Cumulative interferences unit stride workload on the Symmetry             | 168 |  |  |  |

| 6.9        | Cumulative interferences unit stride workload on the TC2000               | 169 |  |  |  |

# CHAPTER 1

# INTRODUCTION

The ever increasing need for faster and more powerful computers, coupled with the advent of fairly cheap microprocessors, has prompted considerable interest in massively parallel processor systems. Computational power has reached a plateau at the current state of technology for single processor systems [23], due to certain fundamental limits (i.e., the speed of light and the width of the atom) being approached. In an effort to sustain increases in the peak speed of new computer systems so as to bridge the discrepancy between computational needs and available computing power, designers have turned to multiple processors, vector arithmetic units, and other architectural innovations. Using a large number of low-cost processors for achieving supercomputing performance is attractive indeed. Unfortunately, it is much more difficult for a programmer or a compiler to take advantage of multiple processors than of a faster clock speed. As a result, many machines with complex architectures are able to deliver only a small fraction of their theoretical peak performance on all but the most ideal problems.

The purpose of this dissertation research is to develop a flexible approach to characterize multiprocessor systems for general purpose parallel programming that can measure and quantify the expected losses in parallel execution performance and determine performance bottlenecks for any selected workload. The proposed methodology provides a framework for customized benchmark workload generation and yields a set of parameters which characterize the target system. These parameters spotlight the strong and weak points of a machine and, hence, aid in the design of efficient

algorithms for it. It should be emphasized that it is not the intent of this thesis to address the issue of performance prediction of application programs. We have chosen the shared-memory programming model as the focus of our study. In this model, processes communicate with each other through shared-variables residing in globally accessible memory. The shared-memory programming model is widely believed to be easier to use than the message-passing model. The conceptual simplicity of the shared-memory model derives from similarities with sequential programming. Evidence in favor of the shared-memory model is the overwhelming dominance of shared-memory multiprocessors for general purpose parallel programming, and the considerable effort in software development designed to provide the illusion of shared memory on multicomputers.

In this introductory chapter, we elaborate some of the pertinent issues in multiprocessor performance evaluation, provide a brief survey of the commonly used multiprocessor benchmarks, and describe the objective and scope of this research.

# 1.1 Multiprocessor Performance Evaluation

The goal of computer performance evaluation is to identify opportunities for specific performance improvements throughout the life of a computer system and to guide the design of more effective architectures. The requirements of target applications motivate the development of new systems; the development of novel systems creates the need and the basis for performance evaluation research. Effective performance evaluation of highly-parallel systems is essential because these systems must function at the limits of their computing potential in order to meet the overwhelming demands of large scientific applications. However, analyzing the performance of multiple-processor systems is a very complex task since many factors jointly determine system performance, and the modification of some factors affects others. Since many different tradeoffs are involved, it is crucial to carefully tune various parameters such that a system achieves its peak performance.

Traditionally, three common approaches are used to evaluate multiprocessor per-

formance: analytical, simulation and experimental [56]. All three approaches are necessary because each has its own advantages and limitations. Analytical models are extremely powerful in the sense that they allow the analytical correlation of performance with organizational parameters. However, their applicability is not universal. In order to be tractable, they typically have to make many simplifying assumptions about the architecture and application characteristics that may not reflect an accurate representation of reality. For example, memory interference models for multiprocessors based on queueing theory often assume a randomly distributed (both in time and space) memory request stream. This assumption fails for many scientific and engineering applications that exhibit very regular data access patterns. If vector instructions are used to implement these codes they must exploit, and hence emphasize, this regularity in the temporal and spatial distribution of requests. Simulations can generally approximate reality more closely, but they are expensive to run and still do not replace real measurements. Moreover, interactions may be present on a real system that affect performance and are difficult to capture in a model.

The advantage of experimental performance analysis is, of course, that the performance of the real system is obtained as opposed to the performance of a model of the system. The drawback of such a solution is its experimental nature which limits the number of codes analyzed and generally does not provide any methodology for extrapolating the performance of an arbitrary code from the performance of the benchmark codes. Furthermore, even when using very simple benchmarks, there is no general method of correlating code characteristics with the performance observed.

Analytical and simulation modeling techniques find maximum applicability at the system design phase where they facilitate prediction of system behavior long before the actual hardware implementation. This helps in making judicious design decisions that can avoid considerable investment of resources in an inefficient design. For example, analytical models of processor-memory interconnection have been studied in [86, 11, 18, 19]. Analytical models of application (or algorithm) execution on a given architecture can also aid in asymptotic scalability studies [47, 42]. However, hardware related parameters in such models need to be calibrated by experimental

#### measurements.

Owing to the diversity of architectural approaches of a multiprocessor, the development of working models that can provide a true measure of the "actual" performance of these machines under workloads of interest can be an extremely complex, if not impossible, problem. Since a multitude of architectural and application parameters jointly determine system performance and the modification of some factors affects others, it is not feasible to construct an elegant yet tractable analytical model that encompasses all performance effects. Nondeterminism present in parallel program execution on multiprocessors introduces an additional degree of complexity into the performance measurement phenomenon. The dynamic run-time behavior of multiprocessor programs is impossible to capture accurately in analytical models.

In the face of the above difficulties, empirical results are the only reliable performance measures [29]. This has led to the use of benchmark programs to characterize and evaluate parallel computer performance (benchmarking). Although benchmarking is widely acknowledged to be a difficult and often controversial process [87, 97], it also provides one of the few recognized means of acquiring useful performance information about complex systems running complex tasks. The methodologies commonly used in computer benchmarking and the associated pitfalls encountered are described in [35].

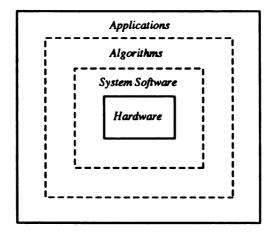

Figure 1.1. Performance measurement levels

There are four levels in the hierarchy of performance measurements [85] as illustrated in Figure 1.1. The answer to the oft-asked question, "How fast is it?" depends on the intended use of the performance data. At the lowest level lies the performance of the hardware design. Determining this performance provides both a validation of and directives for system software design. Only by understanding the strengths and weaknesses of the hardware can system software designers develop an implementation and user interface that maximizes the raw hardware potential available to the end user. Given some characteristics of the available processing resources and the services provided by the system software, users can develop algorithms that are best suited to the computer system's capabilities. Finally, the best mix of key algorithms will maximize the performance of user applications.

A complete performance characterization requires not only an analysis of the system's constituent levels, it also requires both *static* and *dynamic* characterizations. Static or average behavior analysis may mask transients that dramatically alter system performance. A combination of static and dynamic characterizations is also needed to understand the interactions between performance levels. Table 1.1 shows a subset of the important performance measurements at three levels for three classes parallel processing architectures.

Table 1.1. Performance level comparisons for three classes of multiprocessors

| Level           | Vector           | Shared-memory        | Message-passing |

|-----------------|------------------|----------------------|-----------------|

|                 | processors       | multiprocessors      | multicomputers  |

| Hardware        | Vector startup   | Memory contention    | Processor speed |

|                 | Memory conflicts | Network contention   | Communication   |

|                 | '                | Memory-cache         | latency and     |

|                 |                  | interaction          | bandwidth       |

| System software | Compiler         | Compiler             | OS support      |

| Algorithm       | Vectorization    | Shared-memory access | Communication   |

|                 |                  | Inter-processor      | pattern         |

|                 |                  | synchronization      |                 |

Historically, benchmarking has been employed for system procurements. It will certainly maintain its value in that arena as it expands to become the experimental basis for a developing theory of supercomputer and multiprocessor performance evaluation. The number of benchmarks currently used is growing day by day. Every new benchmark is created with the expectation that it will become the standard of the industry and that manufacturers and customers will use it as the definitive test to evaluate the performance of computer systems with similar architectures. A survey of the common benchmarks in use today is provided in Section 1.2.

One of the key questions in benchmarking has to do with what kind of unit constitutes the benchmark set. A number of general benchmarks such as Livermore Fortran Kernels, NAS Kernels and the Linpack Benchmark have emerged during the past two decades that are based on a collection of computation-intensive kernels extracted from a range of real application domains. Another benchmark called Whetstones, on the other hand, is based on a collection of synthetic kernels. All these benchmarks perform measurements at the "algorithms" level of Figure 1.1 and have one thing in common—each component kernel in the benchmark is designed to stress a particular aspect of system performance.

Discussions of benchmarking [35, 60, 117, 125] have lead to a growing recognition that the most accurate information on a system's aggregate performance is obtained by making measurements on complete applications (applications-based benchmarking). The underlying assumption here is that real engineering and scientific codes stress and evaluate machines in a way that kernels and algorithms cannot. Efforts in this direction include the Perfect, SPLASH and SLALOM benchmarks. Performance measurements at the applications level capture and reflect the interactions that occur within and between all the lower levels (Figure 1.1). Although this is indeed true, these benchmarks provide useful measures of performance only to the particular set of users that are represented by the benchmark applications. Because of the complexity of designing a complete application program, when tests are done at this level rather than on simpler units, the skill of the programmer may be a significant factor in the performance. Some of the limitations with this approach are:

- Complete applications are difficult to port to a new architecture. Unless the existing applications are modified and tuned to the new architecture, they may not yield optimal performance.

- The software technology for writing parallel programs is immature. It is unclear how well programs written with today's constructs will represent those that might be written in the future, and what the implications of this are for the effectiveness of evaluation studies performed today.

- The available programs might not represent the best parallelization of the problem they solve, but only one that is reasonable and convenient to implement. More significantly, large-scale parallel processing may call for very different algorithms than those implemented on smaller machines today.

- The relationships between applications and architectures take on new dimensions with parallelism. The number of architectural variables is much larger, making careful correlation of performance with code characteristics more difficult.

Empirical studies based on carefully defined benchmark experiments at all the levels in Figure 1.1 can provide a hierarchical path to a complete definition of system performance by extending our understanding of the incremental contributions made by architecture, technology, compilers, operating systems, algorithms, and programming implementations of physical problems.

Finally, there is the question of appropriate metrics to represent multiprocessor performance. A single figure of merit such as MIPS (Millions of Instructions Per Second) is meaningless in the context of the diverse CPU architectures available to-day. The single number metric MFLOPS (Millions of Floating point Operations Per Second) is more appropriate for scientific computations, but yet insufficient. From the end user's standpoint, perhaps the desirable metric would be MRPS (Millions of Results Per Second), although this metric would have no universal meaning. Usually, different benchmark program measurements are summarized in order to find the "average" performance of a computer. How to calculate these averages has been one of

the most confusing issues in performance evaluation [41, 117]. Siegel et al. provide a detailed discussion of other metrics used for multiprocessor performance in [115].

## 1.2 Survey of Benchmarks

Benchmarks are standard programs used to evaluate the performance of a wide range of computer systems. What distinguishes a benchmark from an ordinary program is a general consensus of opinion within the industry and research circles that the benchmark exercises a computer well. Common benchmarks fall into one of several categories. Synthetic benchmarks are small programs especially constructed for benchmarking purposes with the underlying assumption that the average characteristics of real programs can be statistically approximated by a small program. They do not perform any useful computation. Kernel benchmarks are code fragments extracted from real programs in which the code fragment is believed to be responsible for most of the execution time. Application benchmarks go with the assumption that complete real applications stress and evaluate machines in a way that kernels and code fragments cannot. The most important advantage of reducing benchmarks to kernels is that they may be rapidly ported to new computer architectures, whereas porting a mature application would need a lot more effort. However, complete applications provide the most accurate indication of performance.

The field of multiprocessor benchmarking is still evolving and not yet mature. The methodologies commonly used in supercomputer benchmarks and some of the pitfalls encountered are examined by Dongarra et al. in [35]. Although there are a wide variety of benchmarks available, some very site-specific, there is no consensus yet on the most effective and acceptable multiprocessor benchmarks. We summarize some of the more commonly used benchmarks in this section.

## 1.2.1 Synthetic Benchmarks

Whetstone. The Whetstone benchmark [27] was the first program in the literature explicitly designed for benchmarking. It is a synthetic program constructed with

nine small loops each containing statements of a particular type (integer arithmetic, floating-point arithmetic, "if" statements, calls, etc.). It uses mostly global data and has a high percentage of floating-point operations. Most of its execution time is spent in mathematical library functions. The benchmark results are reported as MWIPS (mega Whetstone instructions per second).

Dhrystone. This is another synthetic benchmark [123] that consists of 12 procedures included in one measurement loop with 94 statements. It contains no floating-point operations and a considerable percentage of its execution time is spent in string functions. Unlike Whetstone, it uses very little global data and emphasizes data locality. The benchmark results are given in Dhrystones per second.

#### 1.2.2 Kernel Benchmarks

Linpack. This is a numeric benchmark [33] with a high percentage of floating-point operations and no mathematical functions at all. More than 75 percent of its execution time is spent in a 15-line subroutine (called saxpy in the single-precision version and daxpy in the double-precision version). The results of this benchmark are reported in MFLOPS.

Livermore Fortran Kernels. Also called the Lawrence Livermore Loops, this benchmark [88] consists of 24 kernels (inner loops) of numeric computations from different areas of physical sciences. The individual loops range from a few lines to about one page of source code. They contain many floating-point computations and a high percentage of array accesses. The program computes MFLOPS rate for each kernel, for three different vector lengths.

NAS Kernels. This benchmark program [10] consists of approximately 1000 lines of Fortran code, organized into seven separate tests each containing a loop that iteratively calls a subroutine. The subroutines have been extracted from a variety of computational fluid dynamics problems currently being worked on the NASA Ames supercomputers. They all emphasize the vector performance of a computer system. The performance is measured in MFLOPS.

## 1.2.3 Application Benchmarks

Perfect Benchmarks. Prompted by Kuck and Sameh's proposal [69] and initiated by a group of academic and industrial collaborators, the goals of this effort were to define an applications-based methodology for supercomputer performance evaluation. The Perfect Benchmarks [29, 17] consist of 13 programs drawn from a variety of scientific and engineering fields with over 60,000 lines of Fortran source listing. The methodology requires a set of baseline measurements followed by any number of optimized measurements of each code.

SPLASH. Similar to the Perfect benchmarks, the Stanford Parallel Applications for Shared-Memory (SPLASH) [116] is a suite of seven applications drawn from several scientific and engineering problem domains. The applications are intended as a design aid for architects and software people working in the area of shared-memory multiprocessing.

**SLALOM.** The SLALOM benchmark [5] solves a complete problem dealing with "optical radiosity on the interior of a box". It times input, problem setup, solution, and output, not just the solution. It is the first benchmark based on fixed time rather than fixed problem comparison.

SPEC Benchmarks. Probably the most important current benchmarking effort is SPEC [120] — the systems performance evaluation cooperative effort. Its goal is to collect, standardize, and distribute large application programs that can be used as benchmarks. The SPEC suite consists of 10 benchmark programs. The results are given as performance relative to a VAX 11/780 using VMS compilers. A comprehensive number, the "SPECmark", is defined as the geometric mean of the relative performance of the 10 programs.

## 1.3 Motivation and Problem Definition

There are two distinct activities [110] in evaluating any computer that are often not distinguished in practice: system characterization and performance evaluation. The goal of system characterization is to obtain a set of parameters that fully describes

the system behavior at some level of abstraction. The characterization parameters spotlight the strong and weak points of the system they represent. Performance evaluation, on the other hand, is the measurement of some number of properties during the execution of a given workload. The properties measured may be the total execution time to complete some job steps, the utilization of system resources, the amount of parallel execution overhead, etc. It is important to note that the results depend on, and are only valid for, the workload used in the evaluation.

Accurate performance characterization of a computer is crucial to the design of effective algorithms for the system as it offers information on the sensitivity of the system to various workload attributes. By providing a validation suite for performance trends, it can guide the selection of appropriate values and tuning of important algorithmic parameters. Characterization of uniprocessor systems have been undertaken in [103] using a low-level machine architecture model and in [110] using a higher-level Abstract Fortran Machine model.

The performance characterization of a multiprocessor system introduces a number of new considerations due to the presence of interactions between concurrently executing processes. Inter-process communication, synchronization and contention for shared resources are the primary sources of interference that influence a concurrently executing process. Therefore, in addition to describing the static behavior of a single processor in isolation, multiprocessor performance characterization must also incorporate some mechanism to represent the dynamic execution behavior of multiple processors in the presence of these interactions. Further, the magnitude of the interference encountered is a function of not only the number of processors but also the parallel program structure and behavioral characteristics.

The well-known Amdahl's Law [4] is one of the earliest attempts to address the fundamental issue of parallel program performance. He qualitatively described the gross features of a typical performance spectrum arising in supercomputers. He considered the overall performance of a machine that has two modes of computing (one relatively slow, the other relatively fast) as a function of the time spent in each mode.

Ware [122] quantified the idea in the following model of multiprocessor performance:

$$Speedup = \frac{t_s + t_p}{t_s + t_p/p}$$

(1.1)

where  $t_s$  is the amount of time spent on serial parts of a program,  $t_p$  is the amount of time spent on parts of the program that can be executed in parallel, and p is the number of processors used. The numerator in Eq. 1.1 denotes the execution time on a single processor whereas the denominator denotes the execution time on p processors. Buzbee [25] has pointed out that this model neglects the effect of multiprocessor synchronization overhead. To correct this inadequacy, he proposed the additional term  $\sigma(p)$  in the parallel execution time, which is usually a monotonically increasing function. However, he did not suggest any method for quantifying  $\sigma(p)$ . Gustafson [54] has recently demonstrated that the assumptions underlying Amdahl's Law are inappropriate for the current approach to ensemble parallelism and has reformulated the law. Gelenbe [48, 49] has given a set of formulae that provide insight into the effective speedup of parallel programs by taking into account the capacity of a program to use its parallel structure effectively.

A three parameter  $(r_{\infty}, n_{1/2}, s_{1/2})$  description, introduced by Hockney [61, 63], characterizes the performance of vector multiprocessors in terms of its vector startup overhead and multiple instruction stream synchronization overhead. The parameter  $r_{\infty}$  is the asymptotic rate of the vector operation for large vectors,  $n_{1/2}$  is the vector length at which half the asymptotic rate is achieved, and  $s_{1/2}$  is the amount of useful arithmetic that could have been done during the time taken for synchronization. These three parameters were measured experimentally on a 2-CPU CRAY X-MP machine in [62].

All the above models ignore the dynamic effects of communication and synchronization on parallel program execution. More recently, Zhang [127] has presented a timing model based on a modified Ware model that incorporates the various shared-memory multiprocessor program execution effects into the sequential time component  $t_s$  of Eq. 1.1. He calibrated  $t_s$  and  $t_p$  using experimental measurements on some matrix

computations. Although this study demonstrates the various multiprocessor effects, it does not offer any method to deduce system behavior under other workloads. Analytical models for predicting multiprocessor performance on iterative algorithms in terms of the speed of the processor, memory and the interconnection network have been developed in [121, 28]. Statistical models for synchronous parallel algorithms have also been proposed in [84]. But these models do not include the effect of memory contention as a result of access patterns and mutual exclusion synchronization effects.

An experimental characterization technique for multiprocessor memory system behavior was developed by Gallivan et al. [45] using a set of "load/store" kernels to define memory access patterns. This method was used to study the relation of the Alliant FX/8 vector instruction set to its memory hierarchy. Although this technique is very effective for observing the dynamic behavior of concurrent memory access streams, it is limited in scope and does not address the other sources of performance degradation on a multiprocessor. Experimental study of memory access contention has also been reported in [24]. Numerous comparative studies of multicomputer/supercomputer performance on specific application programs exist in the literature [34, 82, 57, 32]. These studies, although interesting to read, frequently provide only anecdotal information.

Using standard benchmarks to evaluate machine performance is a widely used practice. Considerable effort has been expended to develop benchmark suites, as described in Section1.2, that are considered to reflect real workloads [69]. Although benchmarking is an excellent vehicle for "performance evaluation" (as defined earlier), there are a number of limitations to using it as an approach to "performance characterization":

- Each benchmark is itself a mixture of characteristics, and doesn't relate to a specific aspect of machine performance.

- They provide no insight as to which components of a given program workload have the potential of being the bottlenecks and to what extent.

From the standpoint of the person engaged in the performance measurement activ-

ity, the use of a standard benchmark program suffers from one significant limitation—the lack of control over the benchmark characteristics. Selecting any standard benchmark as the basis for performance evaluation automatically establishes an associated program workload that is built into the benchmark structure. Hence, it is not possible to experiment with changing individual parameters in the workload that affect performance so as to determine optimal settings for such parameters for a given architecture/application combination. Such selective characterization of performance along controlled performance dimensions is integral to the design and implementation of better algorithms. Upon identifying the most important parameters that have significant influence on system performance, we need to develop a simple model to understand and a method to quantify the incremental effect of each of the parameters on performance when they are observed separately. The method should also provide means for observing how different parameters interact. Based on these results, we can identify critical parameters and recognize performance bottlenecks.

Essentially, what is needed is a performance evaluation and characterization methodology that includes the following functional components:

- A flexible benchmark workload generator that can be tailored to highlight the performance of a system along selected dimensions.

- A measurement framework that can incrementally capture and quantify both the static and dynamic aspects of program behavior along the selected performance dimensions.

- A system characterization method that uses the measured quantities in a global timing model to help predict performance trends.

In this research, we address the above problem and present a new approach to selective performance evaluation and characterization for multiprocessor systems.

# 1.4 Objective and Scope of Research

The goal of this research is to explore the use of algorithm characteristics as an abstraction that can help in designing benchmark sets that measure the effect of those parameters which most significantly influence multiprocessor performance. The final objective of such an exercise is to evolve a "system characterization" of the system under test that can effectively guide the design of efficient algorithms. The impact of changing algorithmic parameters on algorithm performance can be predicted and validated using the characterization data suite. Knowledge of expected performance degradation of a multiprocessor program in advance, before actually writing it, helps support an efficient design and implementation methodology. The insight thus gained helps users (and eventually compilers) understand why a given computation runs slowly and how to redesign the algorithms to optimize performance.

We have focused on evaluations at the algorithm level, which means that the types of conclusions that may be drawn relates to how well the structure of an algorithm matches the capabilities of an architecture. Thus, the evaluations at this level do not address the question of how the algorithm fits into a complete task. However, algorithms are more often readily available than complete tasks, and solutions to complete applications are often constructed from a library of key algorithms. It will therefore be of interest to understand what is being learned from architecture evaluations performed at the algorithm level. Our approach will be to propose abstractions by which this sort of evaluation can be facilitated. The objective is to make more systematic the way in which benchmark sets are selected. The approach proposed in this research is intended to complement applications-based benchmarking as a method for performance evaluation.

We have restricted the scope of our studies to multiprocessors supporting a shared address space. The hardware architecture of the machine need not furnish a common shared-memory. The underlying programming model is assumed to be one using shared-variables. This programming model is widely used and is evident from the overwhelming dominance of shared-memory multiprocessors for general purpose parallel

programming both in the commercial and academic sectors. Examples of commercial multiprocessors include the Encore Multimax, the Sequent Balance and Symmetry, and the BBN GP1000 and TC2000 systems; among research prototypes are the NYU Ultracomputer [51], the IBM RP3 [104], and the Illinois Cedar [44] machines. Furthermore, a considerable effort in software development is designed to provide the illusion of shared memory on multicomputers [26, 20, 79, 78, 108, 40, 22]. By restricting our attention to a given class, we filter out some of the strong differences, allowing ourselves to understand the performance within a class more precisely.

The execution time of a task on a multiprocessor may be nondeterministic on account of queueing delays due to contention for shared resources such as memory or communication channels, or to data-dependent computation times. Variations in execution times generally result in synchronization delays where one task has to await the completion of other tasks. These synchronization delays are inherent in the structure of the algorithm and limit the potential speedup of the parallel algorithm over a serial algorithm. We distinguish between *implicit* and *explicit* synchronizations. Implicit synchronization is caused by the contention for shared resources (shared memory, critical sections). Algorithms exhibiting only implicit synchronizations have been called asynchronous [71]. Explicit synchronization mechanisms are normally used to enforce precedence relations in synchronized algorithms. This thesis specifically addresses the effect of implicit synchronizations in parallel algorithm execution.

Communication cost, synchronization overhead and the contention for shared resources are recognized as the main sources of overhead present in multiple-processor systems. The performance of a parallel program using shared-variables and exhibiting only implicit synchronizations is strongly influenced along three major dimensions: the distribution of shared-data over the memory hierarchy and the concurrent memory reference patterns to access them, mutually exclusive access to shared-data to preserve consistency, and the presence of global synchronization barriers. Along each performance dimension, the behavior of a given program is a complex function of a number of architectural as well as application parameters. It is important to be able to isolate and determine the effects of each of these components on overall system per-

formance. By increasing our ability to measure the pieces, combine their effects, and relate their contributions to architectural and algorithmic characteristics, we enhance our ability to model and predict performance in complex systems.

As discussed earlier, standard benchmark programs are not suitable for performing the task of system characterization since we cannot isolate the effects of each of the three performance factors when executing the benchmark workload. Although they provide good indication of the overall system performance, a user does not have any control on the benchmark characteristics. We need a flexible benchmark workload generator and a systematic measurement methodology to capture the incremental contribution of each performance factor to the total parallel execution overhead. We

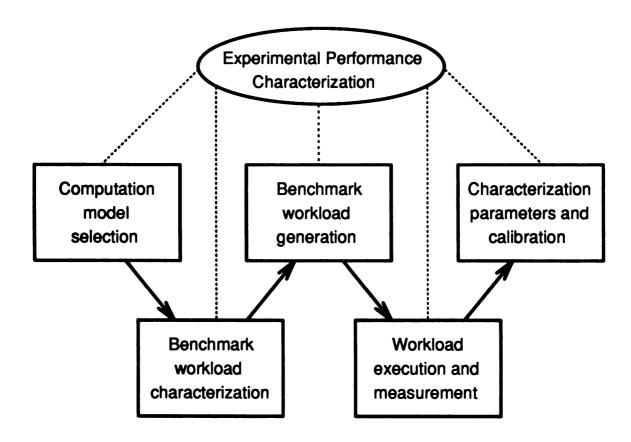

Figure 1.2. Steps in the experimental performance characterization method

have developed an experimental performance characterization method based on the

construction of synthetic executable workloads. These workloads have the advantage that they can be made parametric and hence flexible in representing workload characteristics. Although they have the disadvantage of possible lack of realism at the applications level, they can be made to reflect the algorithm characteristics quite accurately [121]. Our characterization technique consists of five distinct steps (Figure 1.2):

#### 1. Parallel computation model selection.

To be universally applicable, the system characterization measurements must be based on a uniform model of execution so that the results of an experiment can be related to previous and future experiments. We consider a class of structured multi-phase [91] iterative algorithms as our basis for characterizing multiprocessor performance. Many engineering and scientific applications are most frequently characterized as being highly iterative and adhere to this *phase-and-transition* model.

#### 2. Benchmark workload characterization.

The benchmark workload characterizer uses a hierarchical approach to construct a variety of artificial workloads of interest using the parameters that most influence the behavior of concurrent program execution. At the lowest level, it uses a single grain of computation, called a *unit grain*, as the unit of parallel workload specification. The unit grains are assembled into the multi-phase parallel computation structure at a higher level thus incorporating the algorithmic component into the workload.

#### 3. Benchmark workload generation.

Assigning appropriate values to the attributes used to characterize a unit grain creates synthetic workloads that are used as benchmarks for the characterization process. Values assigned to the attributes may be constant quantities thus creating invariant deterministic unit grain characteristics, or the attributes may be treated as random variables of known probabilistic distributions thereby producing stochastic unit grain behavior. The unit grain attributes are varied

in a controlled fashion to create parameter families that systematically traverse the input parameter space.

#### 4. Workload execution and performance measurement.

A family of workload emulation programs has been developed that use the workload specification to mimic the execution behavior of an actual program that would demonstrate the same workload characteristics. Three sets of such emulation programs have been designed corresponding to the three major performance dimensions described earlier; each measures and quantifies the performance degradation resulting from overheads along its associated dimension.

- Memory Access Degradation (MAD) kernels measure the overheads resulting from memory contention while accessing shared-data.

- Synchronization Access Degradation (SAD) kernels measure the overheads resulting from synchronization operations and mutually exclusive access to shared-data.

- Barrier Access Degradation (BAD) kernels measure the overheads resulting from the presence of synchronization barriers in parallel program execution.

The measurement framework allows for observation of interference between both homogenous and heterogenous concurrent processes.

#### 5. Performance characterization parameters.

Two performance metrics, unit grain efficiency and interference, are introduced to measure the relative performance of a workload as the number of parallel processes increases. The performance of a given workload as the number of processors vary is completely described by a set of six parameters — three constants  $(R_{\infty}, c_{1/2}, f_{1/2})$  and three functions  $(\psi_m(N), \psi_s(N), \psi_b(N))$ .

The usefulness of this methodology lies in its ability to selectively assess and characterize a shared-memory multiprocessor using synthetic benchmarks whose characteristics can be controlled by the person performing the evaluation. This is of

great practical importance to computer manufacturers as well as system and application programmers alike. For researchers, it is an important exercise if lessons are to be learned, particularly in the area of scalability. From a computer manufacturer's viewpoint, its use lies in evaluating a new system as soon as a prototype is running, using the measured values to determine performance bottlenecks and making architectural refinements. The measurements also provide performance data for competitive bidding. The goal for system and application programmers, on the other hand, is understanding how the characteristics of an algorithm relate to the constraints of an architecture. Further, most compilers for multiprocessor systems available today which feature automatic vectorization and/or parallelization incorporate explicitly or implicitly an econometric model of the processor for which they are targeted [112]. This model is used to evaluate when particular optimization choices should be invoked. The performance data obtained can be used to calibrate such models accurately.

### 1.5 Thesis Outline

The rest of this thesis is organized as follows. In Chapter 2, an overview of the organization of shared-memory multiprocessors is presented. The factors that limit parallelism on these machines along the three performance dimensions discussed in the previous section are examined in detail. A summary of the architectural features of the multiprocessor systems used for our experiments is also provided. The performance characterization framework and its components are described in Chapter 3. In Chapter 4, the use of the MAD kernels to evaluate the performance of shared-memory accesses and quantify the losses in parallelism due to memory contention is addressed. In Chapter 6, the study of performance losses due to inter-process synchronization using the SAD kernels is presented. The measurement of the impact of synchronization barriers on parallel execution performance using the BAD kernels is described in Chapter 6. Finally, Chapter 7 summarizes the major contributions of this research and provides directions for future research.

# CHAPTER 2

# **BACKGROUND**

Although multiprocessor systems do hold the potential for solving problems with vast computational requirements, it is by no means obvious that a particular algorithm will perform well on a given machine. Access to common memory is one of the key factors in the performance of shared-memory multiprocessors. Large-scale multiprocessors can encounter significant performance degradation due to a number of factors related to memory sharing. Contention for shared resources such as interconnection networks, memory modules and shared-variable locations, serialization of execution due to mutually exclusive access to shared-writable data, and synchronization barriers are all factors that limit the performance of parallel program execution on shared-memory multiprocessors. It is important to understand how these performance penalties depend on the various architecture and algorithm design parameters.

In this chapter we review the shared memory organization, the primary factors limiting parallel execution performance and the techniques used to reduce the impact of contention in shared-memory multiprocessors. A summary of the architectural features of the multiprocessor systems used in our experiments is also given.

## 2.1 Multiprocessor Memory Organization

In multiprocessors with global shared memory, parallel memory modules must be used to provide sufficient bandwidth for the processors. Furthermore, a suitable interconnection network must establish the effective sharing of the memory modules

between the processors. Memory access *latency* can become a critical problem in large systems when the distance between parts of the system is such that the time required for data transfer is excessive. In small-scale multiprocessors such as the Alliant FX/8 [102] and the Sequent Symmetry [80], all processors are attached to a single bus which connects them to a global memory. Memory latency is reduced by associating private caches with each processor. Cache coherence is enforced by protocols relying on a fast broadcast mechanism.

For large-scale multiprocessors, a single bus fails as an effective interconnect as its fixed bandwidth limits its scalability. Technology limitations make it too expensive to provide full hardware connectivity between all processors and memory modules. Therefore, large-scale multiprocessors are built with intermediate connectivity using interconnects such as multi-stage interconnection networks as in the BBN TC2000 [15] and the IBM RP3 [104] systems, point-to-point connections as in the Intel Touchstone DELTA [64], and hierarchical interconnects as in the Kendall Square Systems KSR1 [66] and the DASH multiprocessor [77]. Since broadcasting for cache coherence on these interconnects is cumbersome, larger systems either provide cache consistency using a directory-based protocol (as in the DASH project) or provide caching in a restricted fashion under software control (as in the BBN TC2000 and IBM RP3 systems).

One solution to the memory latency problem on large multiprocessors is to build a system in which not all memories are equally distant from all processors, thus allowing data of special interest to a particular processor to be profitably located near it. Distributing a variety of memories around the system (hierarchical organization) can minimize the average data access time and thereby improve system performance. Other approaches to reducing memory latency where the interconnection network itself is a component of the memory hierarchy have been explored in [90]. The number of shared memory modules has a great impact on memory contention. If the number of memory modules is less than the number of processors, memory contention will occur if all processors issue a shared memory request at the same time.

Multiprocessor systems differ in their design as to how the shared memory mod-

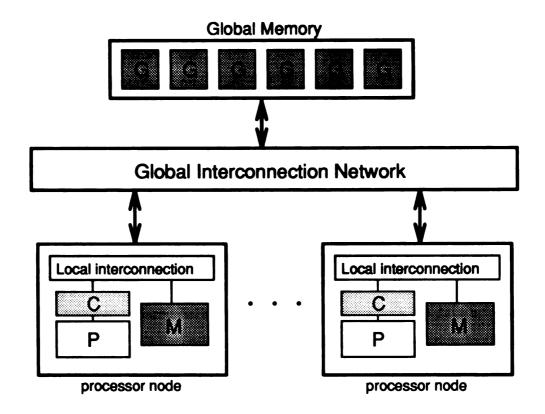

Figure 2.1. Organization of memory hierarchy in shared-memory multiprocessors

ules are distributed over the memory hierarchy and how they provide hardware and software so that each processor sees a single address space in this hierarchy. Typically, a memory module is either local, meaning that it attaches to one processor, or global, meaning that it is only accessible by sending requests through the interconnection network. A request from a processor to its local memory does not cause any network traffic. This kind of memory organization is depicted in Figure 2.1. Such a memory organization is motivated by price/performance reasons similar to the cache/main memory hierarchy prevalent in uniprocessors. Note that in small-scale multiprocessors, the memory local to each processor includes only its cache. Each processor node in Figure 2.1 could also be a cluster of nodes with each node having access to some local memory and cluster-global memory in addition to the system-global memory modules represented by G. The Illinois Cedar [44] system, for instance, has such a cluster organization.

Local memory modules (such as M in Fig. 2.1) can be divided further into shared

and private modules. Shared memory modules are accessible by all processors, whereas a private memory module is accessible only by the processor to which it is attached. Global memory modules (such as G in Fig. 2.1) are implicitly shared and private memory modules are implicitly local. Consequently, there are three types of memory modules: local/private, local/shared, and global/shared. For example, the BBN TC2000 has only local/shared memory modules, and the IBM RP3 can be set up to have both local/private and local/shared memory modules.

Private memory provides a means for reducing network traffic. Allocating private data structures to private memory means that requests for such data structures do not cause network traffic and occur with minimum latency. However, memory latency incurred in accessing shared data structures depends on where the data is located with respect to the requesting processor. The location-dependent variation in the latencies of shared-memory modules results in a non-uniform memory access time thus making the issue of data distribution over the memory hierarchy a critical consideration for performance. As an example, a remote memory access takes four times longer than a local memory access on the BBN TC2000. Architectures such as the KSR1 support dynamic migration of data to the point of demand.

# 2.2 Limitations to Parallelism

Communication, synchronization and contention for shared resources are recognized as the three primary sources of overhead in parallel program execution on multiple-processor systems. We consider only multi-phase asynchronous parallel algorithms constructed using the shared-memory programming model in this research. Since all communication between concurrent processes in such algorithms occurs through globally shared variables, the memory conflicts encountered in accessing the shared variables is critical to overall performance. The amount of memory contention, and the consequent performance degradation, depends not only upon the characteristics of the memory hierarchy and the distribution of shared-data over the hierarchy, but also on the characteristics of the data reference patterns and the interaction between

the two.

To ensure the consistency of concurrent updates to shared data, conflicting accesses must be protected within critical sections. In other words, a fundamental form of synchronization necessary for asynchronous parallel algorithms is mutual exclusion. Another form of synchronization commonly used by multi-phase algorithms to demarcate the individual phases is barrier synchronization. Barriers enforce the arrival of all participating processes at a point before any one of them can proceed further. Both critical sections and barriers induce sequential components into the execution profile of an asynchronous parallel algorithm thus resulting in loss of parallelism. Moreover, inefficient implementations of the mutual exclusion and barrier operations (in hardware or software) could also lead to performance degradation. In the following paragraphs, we discuss how each of these potential sources of loss in parallelism is affected by design choices and what techniques have been developed to minimize their impact.

# 2.2.1 Memory Access Contention

Distance is one reason for memory reference delays. A second reason is contention, which consists of both network contention and memory contention. Multiprocessor applications usually require shared data areas appropriately distributed over the memory modules. Memory conflicts may occur when two or more processors attempt to gain access to a shared resource along the processor-to-memory path simultaneously. The effect of memory conflicts, referred to as memory interference, may decrease the execution rate of the processors. We describe below the factors that cause memory access conflicts and contribute to performance penalties.

## Contention for processor-to-memory path

Processors executing concurrently contend not only for memory, but also for the path to memory. There are three principal ways of interconnecting processors and memory modules: bus, crossbar and multistage network. The bus, by its very nature, provides a common route shared between all processors to gain access to a global

memory space, thus enforcing sequential-access to the shared memory. The high-performance bus systems of today (e.g., the Sequent System Bus [114], the Encore Nanobus [38]) employ a split-transaction protocol whereby multiple memory access requests are pipelined onto the bus before a single memory transaction proceeds to completion. As a result, the bus capacity can be fully utilized if the memory reference pattern can constantly keep the bus busy. The data transfer capacity between processors and memories is determined by the bandwidth of the bus, and is therefore constant. This limits the number of processors that can be usefully incorporated into such a system, and hence fixes an upper limit on performance. Crossbars scale up linearly in terms of performance, but their major shortcoming is the cost and size which is proportional to the square of the number of interconnected components.

Multistage networks provide multiple parallel paths to memory, but processors may contend for paths through the network. Such paths consist of switches at each stage of the network and links between switches in different stages. The switches of a multistage network may be blocking or nonblocking. Blocking switches have buffers to hold messages waiting while some other message is using the switch. Nonblocking switches reject all but one of the conflicting requests so that no queues are formed. This distinction has important implications for system performance as shown by simulation studies conducted as part of the IBM RP3 project. These studies [105] show that small nonuniformities in memory reference patterns can lead to severe degradation of overall system performance due to some memory modules becoming hot. Such nonuniform patterns resulted in a phenomenon called tree saturation, where traffic to the hot memories queued up in the switches and interfered with all other traffic. This saturation effect propagates back through the network, as shown in Figure 2.2, fanning outward from the hot memory module in a tree-like fashion. This problem can be partially resolved by combining networks [105, 75]. On the other hand, nonblocking switches, by rejecting all but one of the conflicting memory requests, avoid the phenomenon of tree saturation [119] so that degraded performance is experienced only by the processors that access the hot memories. Thus, the design and implementation of the interconnection network have a profound effect on the processor-to-memory-path

Figure 2.2. Tree saturation as a result of hot spot accesses over a multistage interconnection network

delay experienced by memory accesses in large-scale multiprocessor systems.

## Contention for memory module

Even if the interconnection network meets the bandwidth requirements of the processor-memory traffic, memory contention can still cause a problem if the processor-memory traffic concentrates on a small number of memory modules. Therefore, it is essential to consider how data structures are allocated to the shared memory modules. A memory module can service only one request at a time (assuming multiport memories are not used). This causes multiple simultaneous requests to the same memory module to be serialized resulting in loss of parallelism.

Memory address interleaving is a technique [73, 99] used to reduce the effective memory access time and, hence, increase memory bandwidth by attempting to distribute the concurrent memory request streams from multiple processors evenly across multiple memory banks. Two broad classes of interleaving schemes used are modulo-

interleaving and random-interleaving. In the former scheme, a word with physical address  $\beta$  is mapped to the bank address  $\beta$  (modulo M), where M is the number of memory modules (assuming a single bank per memory module) and is called the degree of interleaving. The address format and address distribution for such fine interleaving is shown in Figure 2.3(a).