This is to certify that the thesis entitled

OP AMP MACROMODELS

presented by

RAOUDHA HAMZA

has been accepted towards fulfillment of the requirements for

Master's degree in Electrical Engineering

Date

MSU is an Affirmative Action/Equal Opportunity Institution

# LIBRARY Michigan State University

PLACE IN RETURN BOX to remove this checkout from your record.

TO AVOID FINES return on or before date due.

| DATE DUE | DATE DUE | DATE DUE |

|----------|----------|----------|

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

MSU is An Affirmative Action/Equal Opportunity Institution

c:/circhdetadue.pm3-p.1

# **OP AMP MACROMODELS**

Ву

Raoudha Hamza

# A THESIS

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

MASTER OF SCIENCE

Department of Electrical Engineering

1992

#### **ABSTRACT**

## OP AMP MACROMODELS

BY

## Raoudha Hamza

In this thesis, the circuit analysis and basic operations of two different op amp macromodels are described. One is called microsim model and the other one is called linear technology model. Some macromodel design procedures are presented, that enables the macromodel parameters to be found from typical data sheet or easily measured characteristics. Numerical examples are included using the  $\mu$ A741, LM124, LF411, LF355 and LTC1050. Some inaccuracies of the two models are explained followed by the device level performance. Finally some improvements of these models are proposed. The improvements include supply current, power supply rejection ratio, clipping voltage and common mode rejection ratio.

To my parents and my dear husband.

# **ACKNOWLEDGMENTS**

My gratitude to professor G.M. Wierzba for his guidance and assistance in completing this thesis.

My appreciation to Shoba Krishnan for her help in drawing the diagrams.

# TABLE OF CONTENTS

|      | LIS   | Γ OF FIGURES                           | vii                   |

|------|-------|----------------------------------------|-----------------------|

|      | LIS   | Γ OF TABLES                            | ix                    |

| I.   | Intro | oduction                               | 1                     |

|      | 1.1   | Introduction                           | 1                     |

|      | 1.2   | Boyle model                            |                       |

|      |       | Thesis summary                         | 3                     |

| II.  | Mic   | rosim model                            | 5                     |

|      | 2.1   | Introduction                           | 2<br>3<br>5<br>5<br>7 |

|      | 2.2   | Circuit Component and Operation        | 7                     |

|      |       | 2.2.1 Input stage                      | 7                     |

|      |       | 2.2.2 Intermediate stage               | 8                     |

|      |       | 2.2.3 Output stage                     | 8                     |

|      | 2.3   | Preview                                | 8                     |

|      | 2.4   | The NPN Bipolar Input Stage Macromodel | 9                     |

|      |       | 2.4.1 SPICE test circuits              | 9                     |

|      |       | 2.4.2 Model formulas                   | 20                    |

|      |       | 2.4.3 Design procedure                 | 40                    |

|      |       | 2.4.4 Numerical example                | 43                    |

|      | 2.5   | PNP Bipolar Input Stage Macromodel     | 46                    |

|      |       | 2.5.1 SPICE test circuits              | 47                    |

|      |       | 2.5.2 Model formulas                   | 48                    |

|      |       | 2.5.3 Design procedure                 | 48                    |

|      |       | 2.5.4 Numerical example                | 51                    |

|      | 2.6   | JFET Input Stage Macromodel            | . 54                  |

|      |       | 2.6.1 SPICE test circuits              | 54                    |

|      |       | 2.6.2 Model formulas                   | 55                    |

|      |       | 2.6.3 Design procedure                 | 61                    |

|      |       | 2.6.4 Numerical example                | 63                    |

| III. | Line  | ar Technology Model (LTC)              | 68                    |

|      | 3.1   | Introduction                           | 68                    |

|      | 3.2   | Circuit Component and Operation        | 70                    |

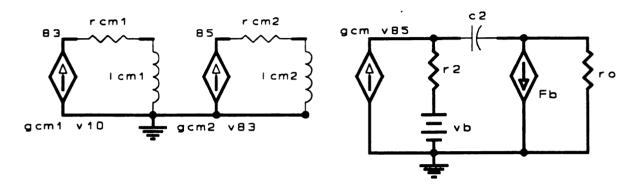

|      |       | 3.2.1 Input stage                      | 71                    |

|      |       | 3.2.2 Intermediate stage               | 71                    |

|     |                                 | 3.2.3    | Output stage                                    | 71  |

|-----|---------------------------------|----------|-------------------------------------------------|-----|

|     | 3.3                             | Previe   | w                                               | 72  |

|     | 3.4                             | JFET     | Input Stage Macomodel                           | 72  |

|     |                                 |          | SPICE test circuits                             | 74  |

|     |                                 | 3.4.2    | Model formulas                                  | 75  |

|     |                                 | 3.4.3    | Design procedure                                | 91  |

|     |                                 | 3.4.4    | Numerical example                               | 95  |

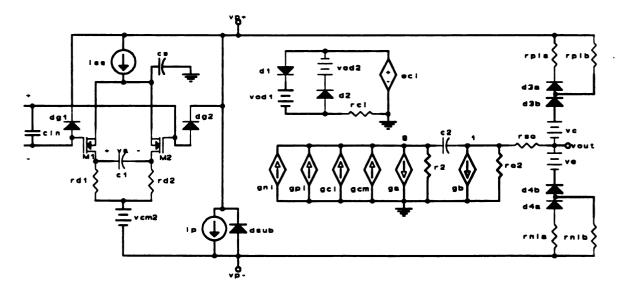

|     | 3.5                             | MOSF     | FET Input Stage Macromodel                      | 98  |

|     |                                 | 3.5.1    | SPICE test circuit                              | 100 |

|     |                                 | 3.5.2    | Model formulas                                  | 101 |

|     |                                 | 3.5.3    | Design procedure                                | 107 |

|     |                                 | 3.5.4    | Numerical example                               | 110 |

| IV. | Inac                            | curacies | s and Improvements of the Model                 | 114 |

|     | 4.1                             | Introd   | uction                                          | 114 |

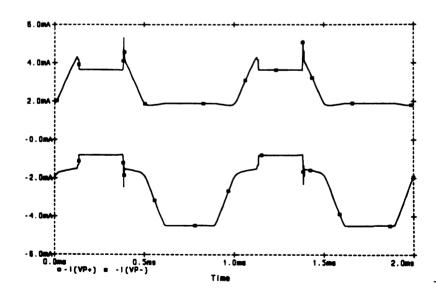

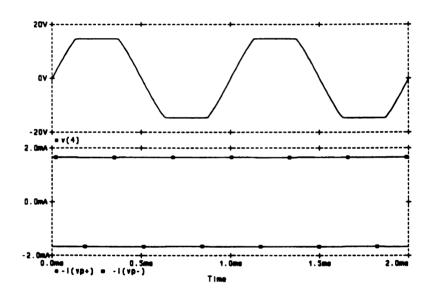

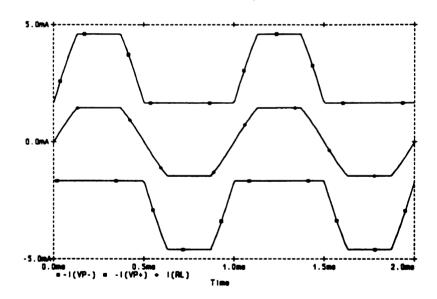

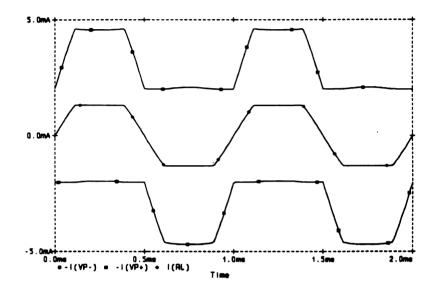

|     | 4.2                             | Supply   | y Current Test                                  | 114 |

|     |                                 | 4.2.1    | Microsim model                                  | 115 |

|     |                                 | 4.2.2    | LTC model                                       | 117 |

|     | 4.3                             | The E    | ffect of E <sub>GND</sub> in the Microsim Model | 118 |

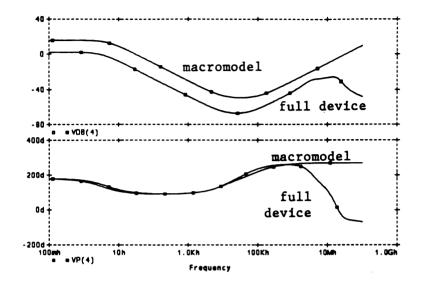

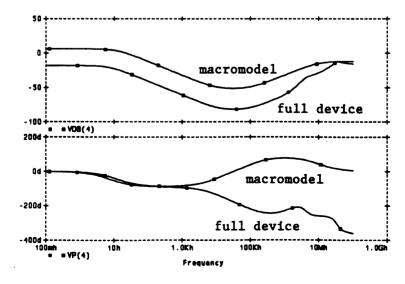

|     | 4.4                             | Power    | Supply Rejection Ratio (PSRR)                   | 119 |

|     |                                 | 4.4.1    | Microsim model                                  | 119 |

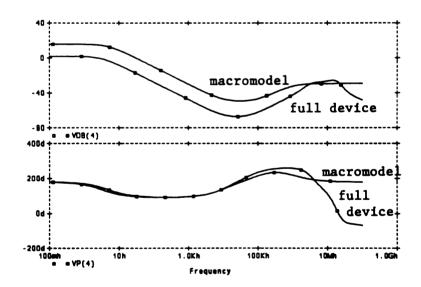

|     |                                 | 4.4.2    | LTC model                                       | 122 |

|     | 4.5                             | Clippi   | ng Voltage                                      | 124 |

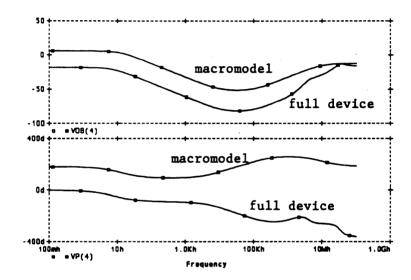

|     | 4.6                             | Comm     | non Mode Rejection Ratio (CMRR)                 | 126 |

|     |                                 | 4.6.1    | Microsim model                                  | 126 |

|     |                                 | 4.6.2    | LTC model                                       | 129 |

|     | 4.7                             | Nume     | rical Example                                   | 130 |

| V.  | Con                             | clusion  | and Future Research                             | 131 |

|     | 5.1                             | Conclu   | usion                                           | 131 |

|     | 5.2                             | Future   | Research                                        | 131 |

|     | APPENDIX A: List of SPICE files |          | 134                                             |     |

# LIST OF FIGURES

| 1.1  | Boyle macromodel                                                    | 3    |

|------|---------------------------------------------------------------------|------|

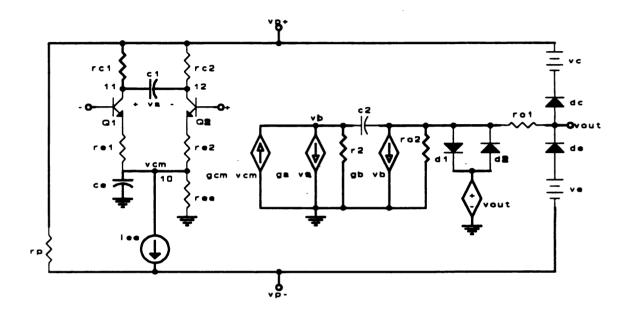

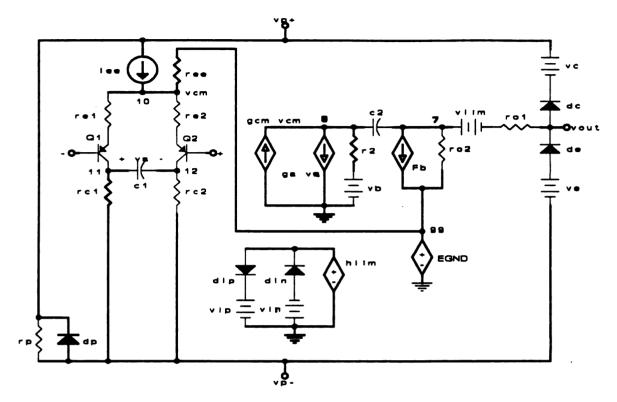

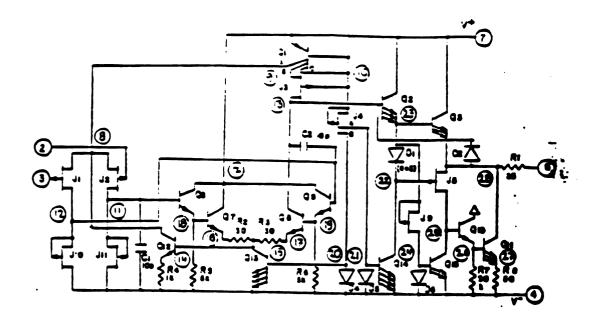

| 2.1  | Microsim macromodel of the µA741                                    | 6    |

| 2.2  | μA741 full device                                                   | 10   |

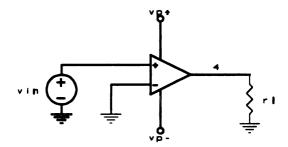

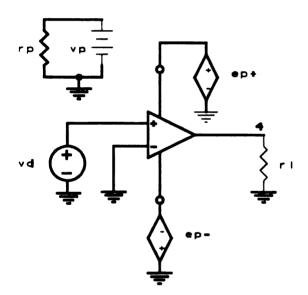

| 2.3a | Test circuit for dc transfer curve                                  | . 11 |

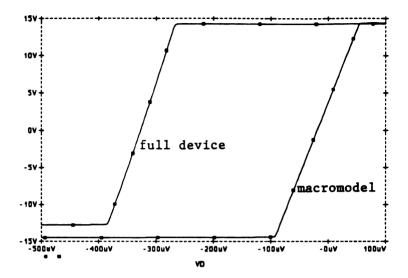

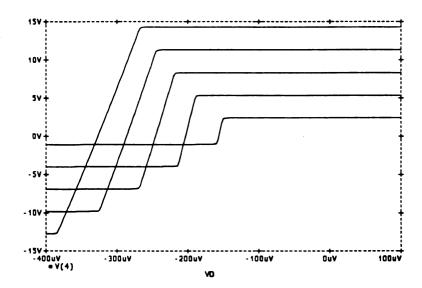

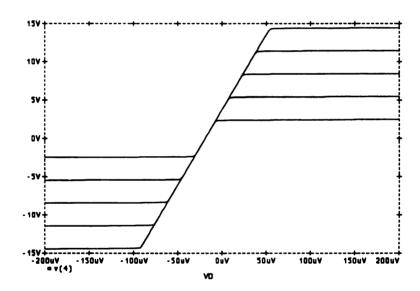

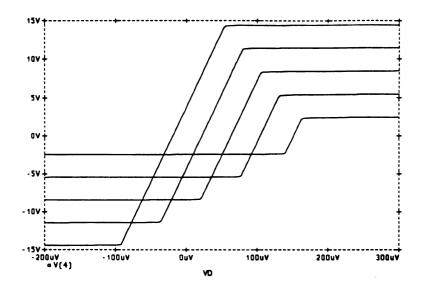

| 2.3b | dc transfer curve                                                   | 12   |

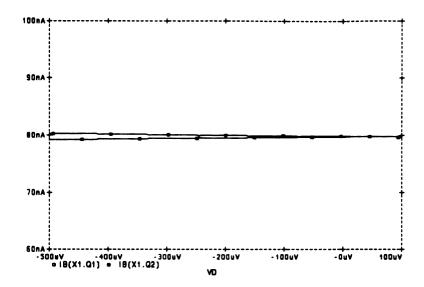

| 2.4a | Input bias current (macromodel)                                     | 13   |

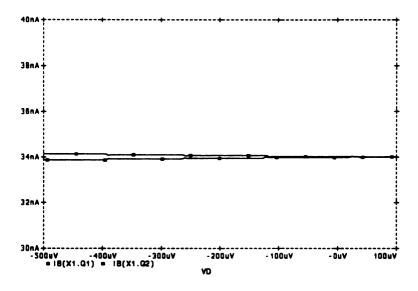

| 2.4b | Input bias current (full device)                                    | 13   |

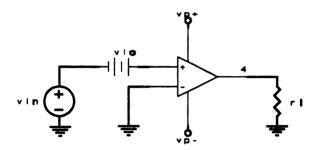

| 2.5a | Open loop test circuit                                              | 14   |

| 2.5b | Open loop gain and phase margin                                     | 15   |

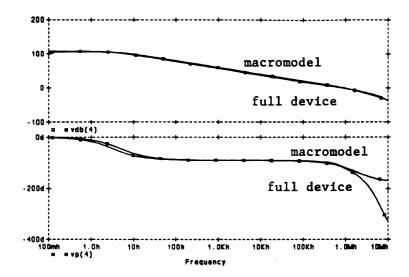

| 2.6a | Output impedance test circuit                                       | 16   |

| 2.6b | Output impedance versus frequencies                                 | 16   |

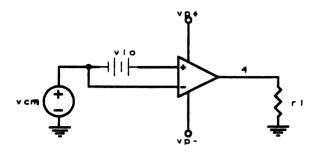

| 2.7a | Common mode test circuit                                            | 17   |

| 2.7b | Common mode gaim of the µA741                                       | 17   |

| 2.8a | Short current test circuit                                          | 18   |

| 2.8b | Short current of the µA741 macromodel                               | 18   |

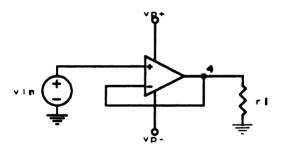

| 2.9a | Slew rate test circuit                                              | 19   |

| 2.9b | Slew rate of the µA741                                              | 19   |

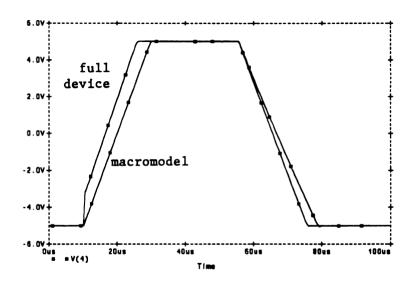

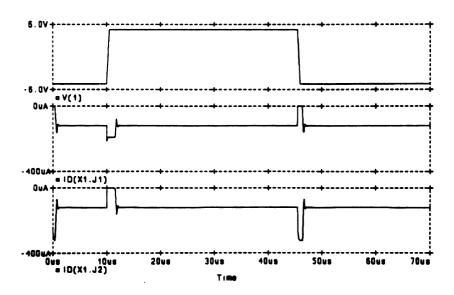

| 2.10 | Collector currents of Q <sub>1</sub> and Q <sub>2</sub>             | 20   |

| 2.11 | Voltages at node 6 and 7                                            | 20   |

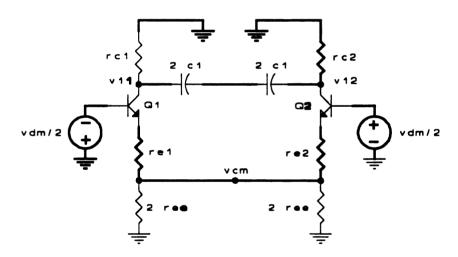

| 2.12 | Input stage differential mode                                       | 23   |

| 2.13 | More simplified input stage DM                                      | 24   |

| 2.14 | Currents in F <sub>b</sub> and v <sub>b</sub>                       | 26   |

| 2.15 | The resistance seen by c <sub>2</sub>                               | 28   |

| 2.16 | A simplified common mode input stage                                | 32   |

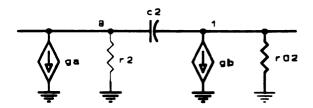

| 2.17 | Currents through c <sub>2</sub> and r <sub>o2</sub>                 | 35   |

| 2.18 | Currents through $F_b$ , $g_a$ , $v_{ip}$ and $v_b$                 | 36   |

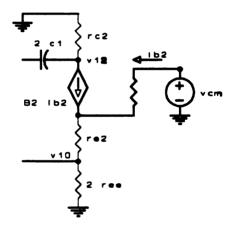

| 2.19 | Currents through F <sub>b</sub> , g <sub>a</sub> and d <sub>c</sub> | 40   |

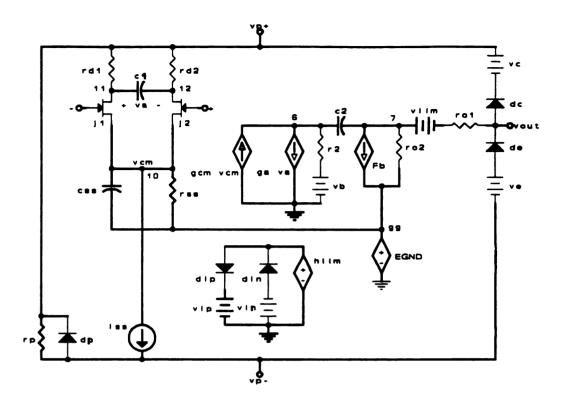

| 2.20 | Microsim macromodel of the LM124                                    | 47   |

| 2.21 | Microsim macromodel of the LF411                                    | 55   |

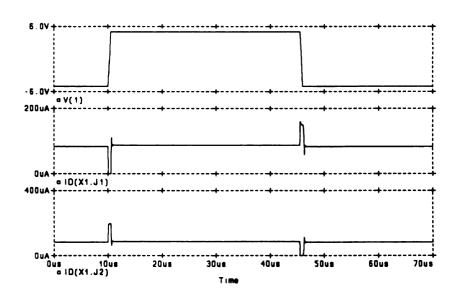

| 2.22 | Drain current of $j_1$ and $j_2$                                    | 56   |

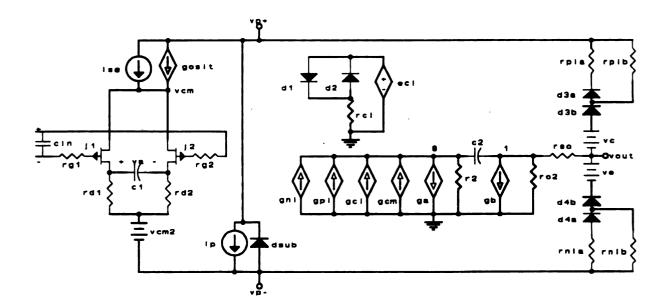

| 3.1  | LTC macromodel of the LF355                                         | 69   |

| 3.2  | LF355 full device                                                   | 73   |

| 3.3  | Drain current of i. and i.                                          | 77   |

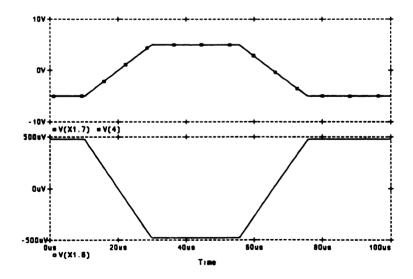

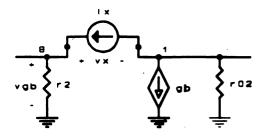

| 3.4  | Voltages at node 8 and node 1                                  | 78  |

|------|----------------------------------------------------------------|-----|

| 3.5  | Intermediate stage at DM input                                 | 79  |

| 3.6  | Resistance seen by c <sub>2</sub>                              | 81  |

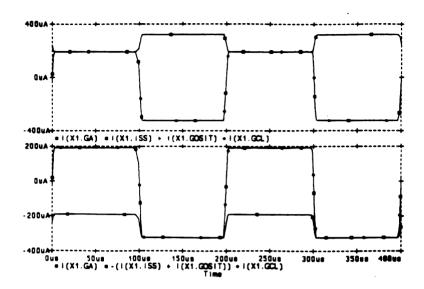

| 3.7  | The current flowing through g <sub>a</sub> and g <sub>cl</sub> | 88  |

| 3.8  | LTC macromodel of the LTC1050                                  | 99  |

| 4.1a | The supply current of the µA741 (full device)                  | 115 |

| 4.1b | The supply current of the µA741 macromodel                     | 116 |

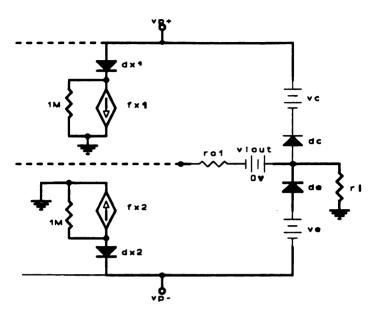

| 4.2a | The new output stage circuit                                   | 119 |

| 4.2b | The supply current of the modified macromodel                  | 117 |

| 4.3  | Supply current of the modified LF355 macromodel                | 118 |

| 4.4  | PSRR test circuit                                              | 119 |

| 4.4a | PSRR of the µA741 full device                                  | 120 |

| 4.4b | PSRR of the µA741 macromodel                                   | 121 |

| 4.4c | PSRR of the modified µA741 macromodel                          | 122 |

| 4.5a | PSRR of the LF355 full device                                  | 123 |

| 4.5b | PSRR of the modified LF355 macromodel                          | 123 |

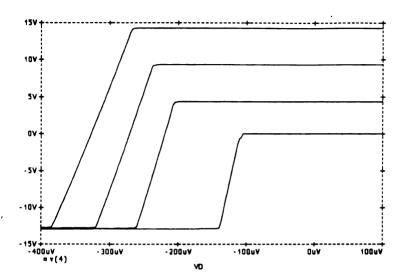

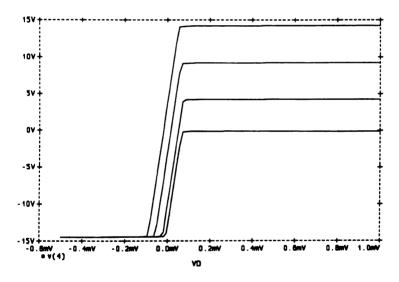

| 4.6a | Clipping voltage of the $\mu$ A741 full device                 | 125 |

| 4.6b | Clipping voltage of the modified macromodel (µA741)            | 125 |

| 4.7  | Additional components used for CM response                     | 128 |

| 4.8a | CM response of the modified macromodel                         | 129 |

| 4.8b | A more improved CM response                                    | 129 |

| 4.9a | CM response of the modified LF355 macromodel                   | 130 |

| 4.9b | A more improved CM response                                    | 130 |

# LIST OF TABLES

| 2.1        | SPICE file of the µA741 macromodel                       | 6   |

|------------|----------------------------------------------------------|-----|

| 2.2        | SPICE file of the µA741 full device                      | 10  |

| 2.3        | Parameters of the µA741                                  | 46  |

| 2.4        | SPICE file of the LM124 macromodel                       | 47  |

| 2.5        | Parameters of the LM124                                  | 53  |

| 2.6        | SPICE file of the LF411 macromodel                       | 54  |

| 2.7        | Parameters of the LF411                                  | 66  |

| 2.8        | Revised parameters of the LF411                          | 67  |

| 3.1        | SPICE file of the LF355 macromodel                       | 70  |

| 3.2        | SPICE file of the LF355 full device                      | 74  |

| 3.3        | Parameters of the LF355                                  | 98  |

| 3.4        | SPICE file of the LTC1050 macromodel                     | 100 |

| 3.5        | Parameters of the LTC1050                                | 113 |

| 4.1        | Values of the additional offset (µA741)                  | 122 |

| 4.2        | Values of the additional offset (LF355)                  | 124 |

| 4.3        | Values of the clipping voltage (µA741)                   | 126 |

| 4.4        | Parameters of the original and modified µA741 macromodel | 131 |

| <b>A.1</b> | SPICE file of Fig. 2.3a                                  | 134 |

| <b>A.2</b> | SPICE file of Fig. 2.5a                                  | 134 |

| <b>A.3</b> | SPICE file of Fig. 2.6a                                  | 135 |

| <b>A.4</b> | SPICE file of Fig. 2.7a                                  | 135 |

| A.5        | SPICE file of Fig. 2.8a                                  | 135 |

| <b>A.6</b> | SPICE file of Fig. 2.9a                                  | 136 |

| <b>A.7</b> | SPICE file of Fig. 2.14                                  | 136 |

| <b>A.8</b> | SPICE file of Fig. 2.19                                  | 136 |

| <b>A.9</b> | SPICE file of Fig. 2.22                                  | 136 |

| A.10       | SPICE file of Fig. 3.3 & 3.4                             | 136 |

| A.11       | SPICE file of Fig. 3.7                                   | 137 |

| A.12       | SPICE file of Fig. 4.1a                                  | 137 |

| A.13       | SPICE file of Fig. 4.1b                                  | 137 |

|            | SPICE file of Fig. 4.2b                                  | 137 |

| A.15       | SPICE file of Fig. 4.4a                                  | 137 |

|            | SPICE file of Fig. 4.4b                                  | 138 |

| A.17        | SPICE file of Fig. 4.4c | 138 |

|-------------|-------------------------|-----|

| A.18        | SPICE file of Fig. 4.6a | 138 |

| <b>A.19</b> | SPICE file of Fig. 4.6b | 138 |

## CHAPTER 1

#### Introduction

#### 1.1 Introduction

Electronic circuit simulators have certain limitations, such as the maximum number of nodes, devices, elements, etc. These limitations are established either by memory limitations or convergence problems. Even if adequate simulaters and computers are available, nowadays the required simulation time makes the analysis impractical for the design engineer. Therefore, the idea and use of macromodels in electronic design arose since 1970's. The purpose of the op amp macromodel is to provide an adequate pin for pin representation of op amp and to represent the electrical characteristics of the operational amplifier. Since the macromodel components are selected based on data sheet specifications, this allows the designer to accurately model a specific IC based on laboratory measurements.

A macromodel for all bipolar operational amplifier was developed by G.R Boyle, B.M cohn, D.O. Pederson and J.E Solomon [1]. This macromodel is referred to it as the Boyle model. Since this paper was published, the area of op amp macromodeling has been of interest to many SPICE users [6], [9], [2]. Later on the MOS bipolar and JFET

bipolar op amps were presented based on the original Boyle model [3] and others have worked on improving the Boyle model such as in [11], [9], [4], [2]. In all the work, the design procedures were not developed and sometimes even the design formulas were not derived such as in [9], [2]. The main focus of this thesis is to present a complete analysis of two macromodels one called the microsim model [9] and the other one is called the linear technology model [2]. These two models were published with no design formulas or design procedure. This thesis includes all the necessary design formulas of these two macromodels. A design procedure is established so that given the op amp specifications one can determine its macromodel parameters in a systematic way.

## 1.2 Boyle Model

The circuit diagram of the op amp Boyle macromodel is shown in Fig. 1.1. This model is divided into three stages. The input stage consists of two ideal transistors, sources and some passive elements. This stage produces the necessary linear and non-linear differential mode (DM) and common mode (CM) input characteristics. In addition, this stage is designed to have a unity voltage gain to reduce the complexity of the design equations. The intermediate stage produces the DM and CM voltage gain. Also a capacitance  $c_2$  is used at this stage to control the frequency and slew rate performances. The output stage provides a dc and ac output resistance for the op amp, the desired output voltage swing limits and is responsible for limiting short circuit output current. Since then, this strategy has been adapted by most of the op amp macromodels with of course

some improvements.

Figure 1.1 Boyle macromodel

## 1.3 Thesis Summary

This thesis concentrates on the analysis of two different designs of op amp macromodel: one called the microsim model, in chapter 2 and the other one called the linear technology model, in chapter 3.

Chapter 2 itself includes three different types of op amp macromodels: npn input stage macromodel (µA741), pnp input stage macromodel (LM124), n-channel JFET input stage marcomodel (LF411).

Chapter 3 also includes two different types of op amp macromodels: p-channel

JFET input stage macromodel (LF355), PMOS bipolar input stage macromodel (LTC1050).

In each of these chapters, the schematic diagram and its corresponding SPICE file of each op amp macromodel are provided followed by a set of SPICE test circuits to measure some of the typical op amp macromodel characteristics. Then, the design equations of each macromodel are derived with details which allows us to develop a systematic general design procedure for each type. Finally, a numerical example is used to verify the accuracy of the derived design equations by comparing the calculated measurements with the simulated ones.

Chapter 4 includes some models inaccuracies and some improvements to the two models.

Chapter 5 includes the conclusion and further research.

## CHAPTER 2

#### Microsim Model

#### 2.1 Introduction

In this chapter, the structure and basic operations of an op amp macromodel called the microsim model are described. The schematic diagram of an npn bipolar input stage macromodel (µA741) is shown in Fig. 2.1 as well as its SPICE file in Table. 2.1 [9]. The choice of the macromodel parameters are determined and explained later in other sections. This macromodel is designed by using elements inherent to SPICE such as ideal controlled source stages instead of transistors, and generally minimizes the number of pn junctions [1]. Two basic controlled sources dominate the microsim model: the voltage controlled voltage source (VCVS) and the voltage controlled current source (VCCS). This macromodel should represent the circuit behavior of an IC op amp for nonlinear dc, ac, and large signal transient responses.

The microsim model is fundamentally similar to the Boyle model [1] but with further adaptation such as the intermediate stage and the short circuit current limiter. However, the input stage and the voltage limiting circuit remain almost the same.

Figure 2.1 Microsim macromodel of the  $\mu A741$

Table 2.1 SPICE file of the  $\mu$ A741 macromodel

| *CONNECTIONS: + - VP+ VP- VOUT        | R2 6 9 100.0E3                 |

|---------------------------------------|--------------------------------|

| .SUBCKT UA741 1 2 3 4 5               | RC1 3 11 5.305E3               |

| C1 11 12 8.661E-12                    | RC2 3 12 5.305E3               |

| C2 6 7 30.00E-12                      | RE1 13 10 1.836E3              |

| DC 5 53 DX                            | RE2 14 10 1.836E3              |

| DE 54 5 DX                            | REE 10 99 13.19E6              |

| DLP 90 91 DX                          | RO1 8 5 50                     |

| DLN 92 90 DX                          | RO2 7 99 100                   |

| DP 4 3 DX                             | RP 3 4 18.16E3                 |

| EGND 99 0 POLY(2) (3,0) (4,0) 0 .5 .5 | VB 9 0 DC 0                    |

| FB 7 99 POLY(5) VB VC VE VLP          | VC 3 53 DC 1                   |

| + VLN                                 | VE 54 4 DC 1                   |

| + 0 10.61E6 -10E6 10E6 10E6 -10E6     | VLIM 7 8 DC 0                  |

| GA 6 0 11 12 188.5E-6                 | VLP 91 0 DC 40                 |

| GCM 0 6 10 99 5.961E-9                | VLN 0 92 DC 40                 |

| IEE 10 4 DC 15.16E-6                  | .MODEL DX D(IS=800.0E-18 RS=1) |

| HLIM 90 0 VLIM 1K                     | .MODEL QX NPN(IS=800.0E-18     |

| Q1 11 2 13 QX                         | BF=93.75)                      |

| Q2 12 1 14 QX                         | .ENDS                          |

|                                       |                                |

## 2.2 Circuit Component and Operation

The microsim model can be divided into three basic building blocks: input stage, intermediate stage and output stage which includes the short circuit current and voltage limiting. Each stage provides a certain characteristic.

## 2.2.1 Input stage

The input stage consists of two ideal transistors  $Q_1$ ,  $Q_2$ , resistances, a capacitance  $c_1$  and a current source noted  $I_{ee}$  or  $I_{se}$ . This stage produces the necessary linear and nonlinear differential mode (DM) and common-mode (CM) input characteristics and it is isolated from the rest of the stages to simplify the modeling of the slew rate and frequency response [3]. For simplicity and design flexibility, the input stage gain was chosen to be unity [1]. This normalization step increases the utility of the model by simplifying design expressions for gain bandwidth product as shown in the model formulas section. In addition, this unity gain enables other structures to be implemented such as pnp and JFET input stages without changing the basic design equations [2]. Also the two transistors are modeled in the SPICE with their simplest models which does not include internal capacitances or resistances.

#### 2.2.2 Intermediate stage

The elements  $g_a$ ,  $g_{cm}$ ,  $F_b$ ,  $r_2$ ,  $r_{o2}$  and  $c_2$  provide the DM and CM op amp gain and vary the frequency response characteristics. The capacitance  $c_2$  is used to provide the necessary ac output resistance change with frequency [1].

## 2.2.3 Output stage

The output stage provides a dc and ac output resistance of the op amp by the two resistances  $r_{o2}$  and  $r_{o1}$ .

The short circuit current limiting which provides the desired maximum short circuit current,  $I_{sc}$ , consists of two diodes  $d_{lp}$ ,  $d_{ln}$ , two dc voltage sources  $v_{lp}$ ,  $v_{ln}$  and a controlled voltage source  $h_{lim}$  which is controlled by the current flowing through  $r_{ol}$ . The elements  $d_{lp}$ ,  $v_{lp}$  provide the positive short circuit current  $I_{sc}$ , while  $d_{ln}$ ,  $v_{ln}$  provide the negative short circuit current  $I_{sc}$ .

The elements  $d_c$ ,  $v_c$  and  $d_e$ ,  $v_e$  provide voltage clamp circuits where the pair  $d_c$ ,  $v_c$  is for the positive voltage clamp and  $d_e$ ,  $v_e$  is for the negative voltage clamp.

#### 2.3 Preview

The focus of the rest of the chapter is on developing expressions for the values of the elements in the macromodel. This is done because the design formulas for this model have not been published. The starting point is to use SPICE simulations of a given

macromodel to establish the basic design equations. Then, a general procedure is developed for the prameter and element values in the macromodel. Finally, the last step is to check the design procedure by using a numerical example. This analysis is done for a three different input stage macromodels: npn input stage macromodel (µA741), pnp input stage macromodel (LM324) and n-channel JFET input stage macromodel (LF411).

## 2.4 The NPN Bipolar Input Stage Macromodel

One of the npn bipolar input stage macromodels is the  $\mu$ A741. The schematic diagram is shown in Fig. 2.1 and the corresponding SPICE file is shown in Table 2.1. Also, the schematic diagram shown in Fig. 2.2 is of the  $\mu$ A741 full device op amp and its corresponding SPICE file is in Table 2.2.

## 2.4.1 SPICE test circuits

The SPICE test circuits are established using the µA741 macromodel. Since, the µA741 full device is available, then there are additional SPICE test circuits to compare the full device with its macromodel. The SPICE test circuits include transfer characteristics, input bias and offset currents, open loop gain, output impedance, common mode gain, short circuit current and slew rate.

Figure 2.2 µA741 full device

Table 2.2 SPICE file of the  $\mu A741$  full device

| .SUBCKT UA741 4 5 1 13 25 | Q23A 13 17 23 13 M2            |

|---------------------------|--------------------------------|

| * + - Vp+ Vp- Vout        | Q23B 13 17 9 13 M2             |

| Q1 2 4 6 13 M1            | Q24 20 20 13 13 M2             |

| Q2 2 5 7 13 M1            | R1 11 13 1K                    |

| Q3 8 3 6 13 M2            | R2 12 13 1K                    |

| Q4 9 3 7 13 M2            | R3 10 13 50K                   |

| Q5 8 10 11 13 M1          | R4 14 13 5K                    |

| Q6 9 10 12 13 M1          | R5 16 15 39K                   |

| Q7 1 8 10 13 M1           | R6 24 25 27                    |

| Q8 2 2 1 13 M2            | R7 25 26 22                    |

| Q9 3 2 1 13 M2            | R8 19 13 100                   |

| Q10 3 15 14 13 M1         | R9 18 13 50K                   |

| Q11 15 15 13 13 M1        | R10 22 23 40K                  |

| Q12 16 16 1 13 M2         | R11 0 13 50K                   |

| Q13A 21 16 1 13 M2 .25    | CC 17 9 30P                    |

| Q13B 17 16 1 13 M2 .75    | .MODEL M1 NPN (BF=200 IS=1E-14 |

| Q14 1 21 24 13 M1 3       | + VAF=125 VJS=.75 RB=185 RC=15 |

| Q15 21 24 25 13 M1        | + CJE=.65P CJC=.36P TF=1.15N   |

| Q16 1 9 18 13 M1          | + TR=405N CJS=3.2P MJS=.5)     |

| Q17 17 18 19 13 M1        | .MODEL M2 LPNP (BF=50 IS=1E-14 |

| Q18 21 22 23 13 M1        | + VAF=50 VJS=.75 RB=500 RC=150 |

| Q19 21 21 22 13 M1        | + CJE=.1P CJC=1.05P TF=27.4N   |

| Q20 13 23 26 13 M2 3      | + TR=2540N CJS=5.1P MJS=.5)    |

| Q21 20 26 25 13 M2        | . ENDS                         |

| Q22 9 20 13 13 M1         |                                |

|                           |                                |

the wh

the V a

offs

## 2.4.1.1 Transfer characteristics

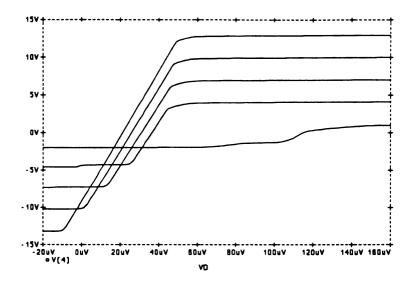

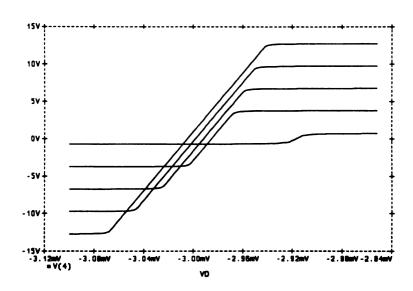

The circuit used for the transfer characteristics test is shown in Fig. 2.3a. Using the cursor in SPICE, one can determine the input offset voltage,  $v_{io}$  by reading the input when the output is zero. Fig. 2.3b shows the transfer curve for the macromodel where the input offset is measured to be -19.17  $\mu$ V and the saturation voltages are  $v_{out}$  = 14.45 V and  $v_{out}$  = -14.46 V. Also Fig. 2.3b shows the full device response where the input offset voltage is measured to be 327  $\mu$ V,  $v_{out}$  = 14.3 V and  $v_{out}$  = -12.77 V.

Figure 2.3a Test circuit for dc transfer curve

Figure 2.3b dc transfer curve

#### 2.4.1.2 Input bias and offset currents

Consider the circuit test of Fig. 2.3a. The input offset current,  $I_{io}$  is the difference between the current at the positive and negative input of the op amp. In other words, it is the difference between the base currents of the two bipolar transistors  $Q_1$ ,  $Q_2$  at the input stage [7]. The bias current,  $I_B$  is the average of the two input currents [7]. Fig. 2.4a shows the base currents for the macromodel where  $I_{B+} = 79.66$  nA,  $I_{B-} = 79.82$  nA.  $I_{B+}$  is the current at the positive input and  $I_{B-}$  is the one at the negative input of the op amp. Then,  $I_{Io} = 0.16$  nA. Fig. 2.4b shows the full device response where  $I_{B+} = 33.89$  nA and  $I_{B-} = 34.12$  nA, then,  $I_{Io} = 0.23$  nA and  $I_{B-} = 34.005$  nA.

2.4.1.

the gain

full device

Figure 2.4a Input bias current (macromodel)

Figure 2.4b Input bias current (full device)

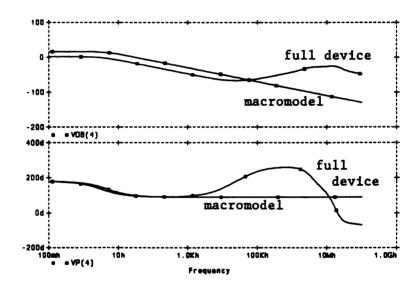

# 2.4.1.3 Open loop gain

The circuit used for the open loop gain test is shown in Fig. 2.5a. Fig. 2.5b shows the gain versus frequency and the phase versus frequency for both cases macromodel and full device. The dc gain  $A_{tmo}$  is equal to 105.9 dB, the 3dB frequency  $f_0$  is found to be

5.012 Hz. Therefore, the gain bandwidth product GBP which is defined as the product of  $A_{dmo}$  and  $f_0$  and is approximately equal to 988.57 KHz [7]. Also, the unity gain frequency,  $f_{\mu}$ , is located at 891.3 KHz and the phase margin,  $\phi_{pm}$ , is 63.1°. For the full device response  $A_{dmo} = 107.2$  dB, the 3dB frequency  $f_0$  is 3.286 Hz and the unity gain frequency  $f_{\mu} = 825.4$  KHz. Therefore, the GBP = 752.77 KHz. Also, the unity frequency  $f_{\mu} = 825.4$  KHz and the phase margin  $\phi_{pm} = 64.4$ °.

Figure 2.5a Open loop test circuit

Figure 2.5b Open loop gain and phase margin

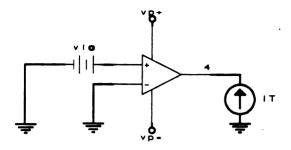

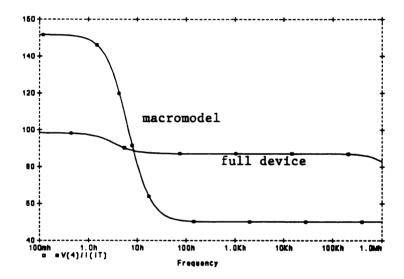

## 2.4.1.4 Output impedance

The output impedance is measured by using the circuit shown in Fig. 2.6a where the input is grounded and a test current  $I_T$  is applied at the output. The variation of the output impedance versus frequency is shown in Fig. 2.6b for both macromodel and full device of the  $\mu$ A741.

At low frequencies, the output impedance for the macromodel is measured to be 151.7  $\Omega$  and is called the dc output resistance  $r_{o-dc}$ . At high frequencies it becomes constant and is called ac output resistance,  $r_{o-dc}$  and is equal to 50.4  $\Omega$ . For the full device case,  $r_{o-dc} = 98.32 \Omega$  and  $r_{o-ac} = 87.17 \Omega$ .

Figure 2.6a Output impedance test circuit

Figure 2.6b Output impedance versus frequencies

## 2.4.1.5 Common mode gain

The common mode gain test circuit is shown in Fig. 2.7a. The corresponding simulation curves for both macromodel and full device are shown in Fig. 2.7b (gain versus frequency and phase versus frequency). Obviously, the dc common mode gain is not modelled at frequecies higher than 10 Khz. The common mode gain is measured to be 15.89 dB = 6.23 for the macromodel and is 2.059 dB = 1.267 for the full device.

Figure 2.7a Common mode test circuit

Figure 2.7b Common mode gain of the µA741

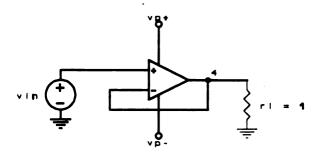

## 2.4.1.6 Short circuit current

The short circuit current test is shown in Fig. 2.8a. A very small resistance (1  $\Omega$ ) is connected to the output so the output is almost shorted. Fig. 2.8b shows the SPICE response of the macromodel where the positive short circuit current is measured to be  $I_{so}$  = 40.61 mA and the negative short circuit current is  $I_{so}$  = -40.61 mA.

Figure 2.8a Short current test circuit

Figure 2.8b Short current of the µA741 macromodel

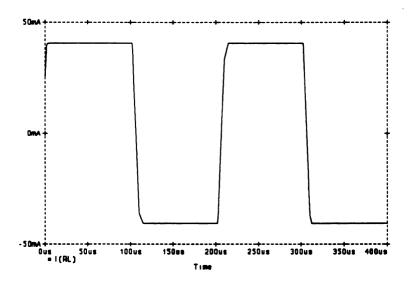

## 2.4.1.7 Slew rate

The slew rate is an important large signal characteristic of the operational amplifier and it is usually measured for the unity gain buffer amplifier as shown in Fig. 2.9a. The corresponding response is shown in Fig. 2.9b for both devices. As we can see the full device has a jump at the rising edge, which is not modeled correctly by the macromodel.

Figure 2.9a Slew rate test circuit

Figure 2.9b Slew rate of the µA741

## 2.4.2 Model formulas

# 2.4.2.1 Slew rate

Consider the unity gain buffer amplifier configuration as shown in Fig. 2.9a, the op amp input stage passes through several states. Fig. 2.10 shows the collector currents of the two transistors  $Q_1$ ,  $Q_2$ . From these SPICE simulations, we see that at the rising

edge of the input,  $Q_1$  is cutoff and  $Q_2$  is active, while at the falling edge of the input  $Q_1$  is active and  $Q_2$  is cutoff. Also, Fig. 2.11 shows that the voltage at the node 6,  $v_6$  is almost equal to zero and the voltage at node 7,  $v_7$  is almost equal to the output voltage,

$\mathbf{v}_{\mathrm{out}}$ .

Figure 2.10 Collector currents of  $Q_1$  and  $Q_2$

Figure 2.11 Voltages at node 6 and 7

a) Positive slew rate, SR+

At the rising edge of the input when  $Q_1$  is cutoff and  $Q_2$  is active, the current through the resistance  $r_{c2}$ ,  $I_{rc2}$  is almost equal to  $I_{ee}$  and  $I_{rc1} \approx 0$ .

Also  $v_a = v_{11} - v_{12} = r_{c2} \times I_{ee}$ . To simplify the design, the VCCS  $g_a$  is chosen to be equal to

$$g_a = \frac{1}{r_{c2}} = \frac{1}{r_{c1}}$$

then, the current flowing in the VCCS g<sub>a</sub> is equal to I<sub>ee</sub>, that is

$$g_{2}v_{2}=I_{cc}$$

Since  $v_6$  is a very small voltage and  $r_2$  is a large resistance, then most of the current  $I_{ee}$  flows through  $c_2$ . The voltage across  $c_2$ ,  $v_{c2}$  is equal to

$$V_{c2} = V_6 - V_7 = -V_7 = -V_{out}$$

then

$$v_{c2} = -\frac{I_{ee}}{C_2}t = -v_{out}$$

and

$$SR = \frac{\Delta v_{out}}{\Delta t} = \frac{I_{ee}}{c_{o}}$$

(2.1)

## b) Negative slew rate, SR

At the falling edge of the input when  $Q_1$  is active and  $Q_2$  is cutoff,  $Q_1$  is operating as a source follower tracking the variation of the output voltage.  $r_{e1}$  is a small resistance, therefore the output is across  $r_{ee}$  which is a very large resistance. Then the current flowing through  $r_{e1}$  is almost equal to  $I_{ee}$  and

hence

$$v_a = v_{11} - v_{12} = I_{ee} r_{c1}$$

Since v<sub>6</sub> is a very small voltage, then most of I<sub>ee</sub> flows out of c<sub>2</sub>, thus

$$v_{c2} = \frac{I_{ee}}{C_2} t = -v_{out}$$

and

$$SR^{-} = -\frac{I_{ee}}{c_{2}} \tag{2.2}$$

## 2.4.2.2 Transistor parameters

The two transistors used at the input stage,  $Q_1$  and  $Q_2$  are identical, therefore  $I_{io}$  is zero and  $I_B$  is equal to the base current

$$I_{B} = I_{B1} = I_{B2}$$

The saturation current  $IS_1$ ,  $IS_2$  of the transistors  $Q_1$ ,  $Q_2$  are also the same. The value of  $\beta_1$  and  $\beta_2$  for the two ideal transistors is obtained from the values of the base currents  $I_{B1}$  and  $I_{B2}$  and the collector current  $I_{C1}$  and  $I_{C2}$  where

$$I_{C1} = I_{C2} = \frac{I_{ee}}{2}$$

Hence

$$\beta_1 = \beta_2 = \frac{I_{ee}}{2I_n} \tag{2.3}$$

## 2.4.2.3 Input stage: rei, rci

The circuit of the input stage differential mode is shown in Fig. 2.12. The dc voltage sources are grounded while the dc current source are open circuit. Using Bartlett's Bisection theorem [8], the common nodes are left grounded. Then, the circuit of Fig. 2.12 becomes that shown in Fig. 2.13.

Figure 2.12 Input stage differential mode

Figure 2.13 More simplified input stage DM

At low frequencies,  $c_1$  is an open circuit then, the voltage  $v_{12}$  is equal to

$$v_{12} = -\beta_2 r_{c2} I_{B2} = -\beta_2 r_{c2} \frac{v_{dm}}{2(r_{x2} + r_{c2}(\beta_2 + 1))}$$

where  $r_{\pi 2}$  is the small signal input resistance between base and emitter, looking into the base [7]. Since  $v_{12} = -v_{11}$  then  $v_a = -2 v_{12}$ . The input stage gain  $A_{v1}$  is chosen to be one as was explained previously, then

$$A_{v1} = \frac{\beta_i r_{ci}}{(r_{ci} + r_{ci}(\beta_i + 1))} = 1$$

(2.4)

Through all the analysis, the subscript i could be 1 or 2 because the input stage is perfectly symmetric. Using the above equation  $r_{ei}$  is equal to

$$r_{ei} = r_{ci} - \frac{1}{g_{mi}} \tag{2.5}$$

where

$$\frac{\beta_i + 1}{\beta_i} = 1$$

and  $g_{mi}$  is the transconductance defined as follows

$$g_{mi} = \frac{\mathbf{v}_{T}}{\mathbf{I}_{Ci}} = \frac{\mathbf{r}_{mi}}{\beta_{i}} \tag{2.6}$$

$I_{Ci} = I_{ee}/2$  is the collector current,  $v_T = K T/q = .02583 V$  at T = 300K [7].

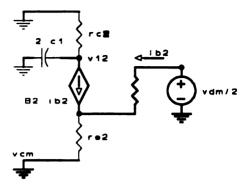

The current controlled current source  $F_b$  is a polynominal set of currents flowing through th dc voltages  $v_b$ ,  $v_c$ ,  $v_e$ ,  $v_{lp}$  and  $v_{ln}$  with  $a_1$ ,  $a_2$ ,  $a_3$ ,  $a_4$  and  $a_5$  are respectively the real coefficients.

$$F_{b} = a_{1}I_{vb} + a_{2}I_{vc} + a_{3}I_{ve} + a_{4}I_{vin} + a_{5}I_{vin}$$

(2.7)

When the op amp macromodel is operating in the linear region, the current flowing through  $F_b$  becomes equal to

$$F_b = a_1 I_{vb} \tag{2.8}$$

Equation 2.8 is also verified by using SPICE. The test circuit used is the same as in Fig. 2.9a where the input does not exceed the saturation voltage ( $v_{in} = 1 \text{ V}$ ). Fig. 2.14 shows that the current in  $F_b$  is almost equal to equation 2.8.

and

using equi

Since the i

Hence, the

The previou

Figure 2.14 Currents in  $F_b$  and  $v_b$

At dc, c<sub>2</sub> is an open circuit, then v<sub>6</sub> becomes equal to

$$v_6 = -g_a v_a r_2 = -I_{vb} r_2$$

and

$$\mathbf{v}_{7} = -\mathbf{F}_{b} \mathbf{r}_{o2} = \mathbf{v}_{out} \tag{2.9}$$

using equation 2.8, v<sub>7</sub> becomes

$$v_7 = a_1 I_{vb} r_{o2} = a_1 g_a v_a r_{o2}$$

(2.10)

Since the input stage gain  $A_{v1} = 1$  then  $v_a = v_{dm}$ , and from equation 2.9 and 2.10

$$v_{out} = a_1 g_a r_{o2} v_{dm}$$

Hence, the dc gain  $A_{dmo}$  is

$$A_{dmo} = a_1 g_a r_{o2} \tag{2.11}$$

The previous analysis holds for very low frequencies where  $c_2$  is an open circuit, but at

higher

one cap

applied

Also, v

From eq

$a_1$  is  $u_{SU}$

and the a

because a

where  $f_0$  is frequency.

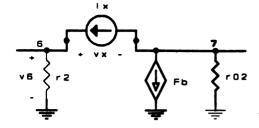

higher frequencies  $c_2$  becomes short and a pole occurs. The pole is found by using the one capacitor method [8]. To solve for the resistance seen by  $c_2$ , a test current source is applied in parallel with the capacitance  $c_2$  creating a voltage drop called  $v_x$  (see Fig. 2.15). Also,  $v_{dm}$  is set to zero, then  $v_a = 0$ ,

$$v_r = I_r r_2 + r_{o2} (F_h + I_r)$$

From equation 2.8

$$v_{x} = I_{x}r_{x} + r_{0}(a_{1}I_{x} + I_{x})$$

a<sub>1</sub> is usually much larger than 1, then

$$v_x = I_x(r_2 + a_1 r_{02})$$

and the above equation could be also approximated

$$v_{x} = I_{x} a_{1} r_{02}$$

because  $a_1 \times r_{o2}$  is much larger than  $r_2$ , hence the resistance seen by  $c_2$  is  $a_1 \times r_{o2}$ , then

$$f_0 = \frac{1}{(2\pi c_2 a_1 r_{o2})} \tag{2.14}$$

where  $f_0$  is the frequency at which the dominant pole occurs and it is also the 3dB cutoff frequency. Thus, the gain bandwidth product is

$$GBP = \frac{g_a}{2\pi c_2}$$

(2.15)

Figure 2.15 The resistance seen by c<sub>2</sub>

## 2.4.2.4 Input offset voltage: vio

Even though the input offset is meant to be zero in this type of op amp macromodel the value is measured to be -19.17  $\mu$ V. This offset is due to the voltage across  $r_{ee}$  which is fedback to the VCCS  $g_{cm}$  at the intermediate stage. In order to find an expression of the input offset, the positive and negative inputs of the macromodel are grounded, then an expression of  $v_{out}$  is established where

$$v_{io} = -\frac{v_{out}}{A_{dmo}}$$

(2.16)

Since the input stage is perfectly symmetric, then the voltage at the node 10,  $v_{10}$ , is equal to

$$\mathbf{v}_{10} = -\frac{\mathbf{I}_{ee}}{2} \mathbf{r}_{ei} - \mathbf{v}_{bei}$$

$v_{bei}$  is the base emitter voltage of the forward bias transistors  $Q_1$  or  $Q_2$  and is defined as follows

$$v_{bei} = v_T ln(\frac{I_{\infty}}{2IS})$$

IS is the saturation current of the transistor  $Q_1$  and  $Q_2$ . Since  $v_{in} = 0$  V then  $v_a = 0$  V and the output voltage is found to be

$$v_{out} = -g_{cm}v_{cm}r_{o2}a_1 + v_{99}$$

$v_{99}$  is the voltage at the node 99 and if the power supply are equal in magnitude then  $v_{99} = 0$  V because  $E_{GND}$  is averaging the power supplies.  $v_{cm}$  is the voltage drop across  $r_{ee}$ , thus it is the difference between  $v_{10}$  and  $v_{99}$ , using equation 2.16, the expression of  $v_{io}$  is as follows,

$$v_{io} = -\frac{g_{cm}}{g_a} \left[ \frac{I_{ee}}{2} r_{ei} + v_T ln(\frac{I_{ee}}{2IS}) + v_{99} \right] - \frac{v_{99}}{r_{02} a_1 g_a}$$

# 2.4.2.5 Input stage: $I_{\infty}$ and $r_{\infty}$

The value of the dc current source at the input stage for equal collector current is

$$I_{\infty} = 2(\frac{\beta+1}{\beta})I_{C} = 2I_{C}$$

The resistance  $r_{ee}$  is added to provide a finite CM input resistance. Because the current source  $I_{ee}$  is often realized with an npn transistor, the resistance  $r_{ee}$  is taken as its output resistance,

$$r_{ee} = \frac{V_A}{I_{ee}}$$

where  $V_A$  is the early voltage of the device [1].  $V_A$  for a small npn is typically 200 V.

### 2.4.2.6 Input stage: c<sub>1</sub>

From Fig. 2.5b and Fig. 2.12, a second pole occurs at  $f_2$ . Using the one capacitor method

$$f_2 = \frac{1}{4\pi r_{c2}c_1} \tag{2.17}$$

$c_1$  is added at the input stage to introduce the excess phase effects in the DM amplifier response [1]. The excess at  $f_2$  due to the non-dominant second pole is  $\Delta \phi$  defined as follows

$$\Delta \phi = 90^{\circ} - \phi_{pm}$$

where  $\varphi_{pm}$  is the phase margin of the DM open-loop response.

$$\tan |\Delta \phi| = \frac{f_{\mu}}{f_2}$$

Substituting equation 2.17 into the above equation [8]

$$\tan |\Delta \phi| = 4\pi r_{c2} c_1 f_{\mu}$$

Then, the necessary value of c<sub>1</sub> to produce the second pole is

2.4.2

Fig. 2.

where

Since ree

Substituti

The currer

Substituting

$$c_{1} = \frac{\tan |90^{\circ} - \phi_{pm}|}{4\pi f_{u} r_{c2}}$$

(2.18)

### 2.4.2.7 Interstage: g\_m

For CM response and after using the Bartlett's theorem, becomes that shown in Fig. 2.16 where the common nodes are left open, the dc voltage sources are grounded and dc current source becomes open circuit.

At low frequencies c<sub>2</sub> is an open circuit and

$$v_{10} = 2r_{m}(\beta_{i} + 1)i_{bi}$$

(2.19)

where

$$i_{bi} = \frac{v_{cm}}{r_{ri} + (\beta_i + 1)(r_{ci} + 2r_{co})}$$

Since  $r_{ee}$  is a very large resistance, then  $i_{bi}$  could be approximated to

$$i_{bi} = \frac{v_{cm}}{(\beta_i + 1)2r_{ei}}$$

(2.20)

Substituting equation 2.20 into 2.19

$$V_{10} = V_{cm}$$

The current flowing through r<sub>2</sub> is equal to

$$I_{vb} = -g_{cm}v_{cm}$$

Substituting the above equation into equation 2.9

$$v_{out} = a_1 g_{cm} r_{o2} v_{cm}$$

Hence, the common mode gain,  $A_{cm}$  is

$$A_{cm} = a_1 g_{cm} r_{o2} \tag{2.21}$$

The common mode rejection ratio (CMMR) is defined as the ratio of the DM gain to the CM gain [7], that is

$$CMMR = \frac{1}{r_{ci}g_{cm}}$$

(2.22)

Figure 2.16 A simplified common mode input stage

### 2.4.2.8 DC power drain

To model the actual dc power dissipation of an op amp, a resistance  $r_p$  is added into the macromodel [1]. The power dissipation is

$$p_d = (v_{p+} - v_{p-})I_{ee} + \frac{(v_{p+} - v_{p-})^2}{r_p}$$

The necessary value of r<sub>p</sub> to produce this dissipation is

$$r_{p} = \frac{(v_{p+} - v_{p-})^{2}}{p_{d} - (v_{p+} - v_{p-})I_{ee}}$$

(2.23)

The diode  $d_p$  is used across  $r_p$  for modeling the case of possible conduction. This can occur with incorrect power supply polarities. Also the diode  $d_p$  has an ohmic resitance noted as  $r_s$  and chosen to be 1  $\Omega$  to avoid the convergence problem.

## 2.4.2.9 Output stage: $r_{o1}$ and $r_{o2}$

The output stage provides the dc and ac output resistances. From Fig. 2.6b, the output resistance at low frequencies (dc output impedance) is

$$r_{o-dc} = r_{o1} + r_{o2}$$

(2.24)

At high frequencies, c<sub>2</sub> is short and the ac output impedance is

$$r_{o-ac} = r_{o1} + (r_2 \| \frac{1}{a_1} \| r_{o2})$$

(2.25)

Since a<sub>1</sub> is very large, then

### 2.4.2.10 Output stage: current limiting

### a) Sourcing current: I<sub>sc</sub>

The positive short circuit current,  $I_{\text{sc+}}$  is a sourcing current that occurs for positive output voltages. When the input and output do not exceed the saturation voltage of the op amp, the expression of the CCCS  $F_b$  becomes as follows

$$F_{b} = a_{1} I_{vb} + a_{4} I_{vip} \tag{2.26}$$

The current  $I_{vip}$  is used to absorbs the current flowing in  $F_b$ . The current flowing in  $r_{o1}$  is  $I_{se+}$  and from the SPICE simulation (see Fig 2.17) the current flowing through  $c_2$  is almost zero, that is

$$g_{a}v_{a} = -I_{vb} = I_{ee}$$

(2.27)

and

$$F_{b} = -(1 + \frac{r_{o1}}{r_{o2}})I_{sc}. {(2.28)}$$

Since  $I_{ee}$  and  $I_{sc+}$  are positive currents, then the two above equations show that,  $I_{vb}$  and  $F_b$  are negative currents. From equation 2.11, the coefficient  $a_1$  is found to be a very large positive number. Thus the product of  $a_1$  and  $I_{vb}$  is a large negative current. Also  $I_{vip}$  is defined to be a positive current. In order to make  $F_b$  a small internal current, the product of  $a_4$  and  $I_{vip}$  has to be positive. Thus  $a_4$  has to be positive coefficient and close to but smaller than  $a_1$  so that  $F_b$  is still negative current and satisfies equation 2.28.

Figure 2.17 Currents through c<sub>2</sub> and r<sub>o2</sub>

The CCVS h<sub>lim</sub> is defined as

$$h_{lim} = \alpha I_{vlim} = \alpha I_{sc}$$

.

$\alpha$  is a constant coefficient and usually selected to be equal to 1 K. On the other hand,  $h_{lim}$  is the summation of the voltage drop  $v_{dlp}$  across the diode  $d_{lp}$  and the dc voltage source  $v_{lp}$ . Therefore

$$v_{ip} = \alpha I_{sc} \cdot -v_{dip} \tag{2.29}$$

The voltage  $v_{lp}$  could be solved once  $v_{dlp}$  is determined and  $I_{so+}$  is specified. The voltage  $v_{dlp}$  is related to the current flowing through the diode  $d_{lp}$  which is equal to  $I_{vlp}$ , that is

$$v_{dip} = v_T ln(\frac{I_{vip}}{IS_{dip}})$$

where  $IS_{dip}$  is the diode saturation current of the diode,  $d_{ip}$  specified in SPICE program as IS and is arbitrarily chosen to be 8E-16 A. The value of  $I_{vip}$  is determined by equating equation 2.26 and 2.28, that is

$$I_{\text{vip}} = -\frac{1}{a_4} (1 + \frac{r_{\text{ol}}}{r_{\text{o2}}}) I_{\text{sc}} + \frac{a_1}{a_4} I_{\text{ee}}$$

Since a<sub>4</sub> is usually a large coefficient, then the above equation is approximated as follows,

$$I_{\text{vip}} = \frac{a_1}{a_4} I_{\text{ee}}$$

Hence

$$v_{dlp} = v_T ln(\frac{a_1 I_{ee}}{a_4 IS_{dlp}})$$

(2.30)

Finally, by substituting equation 2.30 into 2.29, the expression of  $v_{lp}$  is established

$$v_{ip} = \alpha I_{sc}. - v_T ln(\frac{a_1 I_{se}}{a_4 IS_{dip}})$$

(2.31)

All this analysis is checked by using SPICE (see Fig. 2.18).

Figure 2.18 Currents through  $F_b$ ,  $g_a$ ,  $v_{lp}$  and  $v_b$

### b) Sinking current: I<sub>sc.</sub>

The negative short circuit I<sub>sc</sub> is a sinking current that occurs at negative output

voltages. When the input and output do not exceed the saturation voltage of the op-amp, the expression of the CCCS  $F_b$  becomes as follows

$$F_{b} = a_{1}I_{vb} + a_{5}I_{v}$$

(2.32)

Now, the current flowing through  $r_{o1}$  is  $I_{sc.}$  and from the SPICE simulation (see Fig. 2.17), the current flowing through  $c_2$  is almost zero, that is

$$g_{v} = -I_{v} = -I_{c}$$

(2.33)

and

$$F_{b} = -(1 + \frac{r_{o1}}{r_{o2}})I_{sc}. \tag{2.34}$$

Since  $I_{sc}$  is a negative current then, the two above equation show that,  $I_{vb}$  and  $F_b$  are positive currents. The product of  $a_1$  and  $I_{vb}$  is a large positive current. Also the current  $I_{vin}$  is defined to be a negative current. In order to make  $F_b$  a small positive internal current, the product of  $a_5$  and  $I_{vin}$  has to be negative. Thus  $a_5$  is a negative coefficient and close to but smaller than  $a_1$ . If the negative short circuit current is equal in magnitude to the positive short circuit current, the  $a_4$  is equal to the absolute value of  $a_5$ .

The CCVS h<sub>lim</sub> is now defined as

$$h_{im} = \alpha I_{cc}$$

.

Also

$$h_{lim} = -v_{ln} - v_{dln}$$

then

$$v_{in} = -\alpha I_{sc} - v_{din}$$

(2.35)

The voltage  $v_{in}$  could be solved once  $v_{din}$  is determined and  $I_{sc}$  is specified. Following the same methodology done previously for the case of  $I_{sc}$ , the expression of  $v_{in}$  is found to be

$$v_{ln} = -\alpha I_{sc} - v_T ln(-\frac{a_1 I_{ee}}{a_x I S_{din}})$$

(2.37)

where  $IS_{din}$  is the saturation current of the diode  $d_{in}$ . It should be noted that  $I_{sc.}$  is a negative quantity.

#### 2.4.2.11 Output stage: voltage limiting

#### a) Positive voltage limiting

The positive output voltage is limited by the voltage by the voltage source diode clamp combinations  $v_c$ ,  $d_c$ . When the output clamps positively such as to forward bias  $d_c$ , a current flows in the diode  $d_c$ ,  $I_{dc}$  to absorbs the current flowing in CCCs  $F_b$ , thus

$$F_{b} = a_{1}I_{vb} - a_{2}I_{dc} \tag{2.38}$$

where  $I_{dc} = -I_{wc}$  because in SPICE the current is defined to flow from the positive node to the negative node. Also from the SPICE simulation (see Fig. 2.19), the current flowing in the VCCS  $g_a$  is

$$g_v = I_{c}$$

and the current I<sub>vb</sub> is approximately equal to -I<sub>ee</sub>, then equation 2.38 becomes now

$$F_{b} = -a_{1}I_{ee} - a_{2}I_{dc}$$

Since  $I_{dc}$  is a positive quantity, then  $a_2$  must be a negative coefficient to make  $F_b$  a small internal current and is close to but smaller than  $a_1$  in magnitude so that  $F_b$  is still negative small current as seen in Fig. 2.19. Therefore  $I_{dc}$  is approximately equal to

$$I_{dc} = -\frac{a_1}{a_2}I_{ee}$$

Since positive output voltage is limited by the voltage source diode clamp combinations  $v_c$ ,  $d_c$ , the clipping voltage is equal to

$$v_{\text{sat}} = v_{\text{p+}} - v_{\text{c}} + v_{\text{dc}} \tag{2.39}$$

where  $v_{dc}$  is the voltage drop across diode  $d_c$ . Since  $v_{sat+}$  is specified (for the  $\mu$ A741 is measured to be  $\pm 14.61$  V), then the value of  $v_c$  could be determined once  $v_{dc}$  is determined. This voltage is related to the current  $I_{dc}$  as follows

$$v_{dc} = v_T ln(-\frac{a_1 I_{ee}}{a_1 I_{dc}})$$

$IS_{dc}$  is the diode saturation current of the diode d<sub>c</sub> and is set arbitrarily equal to 8E-16 A. Finally using equation 2.39 and the above equation, the value of  $v_c$  is defined as below

$$v_c = v_{p_{+}} - v_{sat_{+}} + v_T ln(-\frac{a_1 I_{ee}}{a_2 IS_{dc}})$$

(2.40)

#### b) Negative voltage limiting

The negative output voltage is limited by the voltage source diode clamp combination  $v_e$ ,  $d_e$ . When the output clamps negatively such as to forward bias  $d_e$ ,  $v_{sat}$  is defined as follows

Follo found

where

2.4.3 D

in this se

model w

to have v

$$V_{\text{sat}} = V_{\text{p}} + V_{\text{e}} - V_{\text{de}}$$

Following the same methodology done in the case of the positive output clamp,  $v_e$  is found to be

$$v_e = -v_p + v_{sat} + v_T ln(\frac{a_1 I_{ee}}{a_3 IS_{de}})$$

(2.41)

where  $IS_{de} = IS_{dc}$  and  $a_3$  is a positive coefficient close to but smaller than  $a_1$ .

Figure 2.19 The current through F<sub>b</sub>, g<sub>a</sub> and d<sub>c</sub>

### 2.4.3 Design procedure

A summary of the design equations for the macromodel parameters is developed in this section. The following design procedure could be used for any op amp microsim model with npn bipolar transistor at the input stage. The starting point of the design is to have values of the typical response characteristics of the corresponding op amp, that

is, the following specifications are assumed available : SR<sup>+</sup>, SR<sup>-</sup>, I<sub>B</sub>, A<sub>dmo</sub>, f<sub> $\mu$ </sub>, GBP,  $\phi_{pm}$ ,

CMRR,  $r_{o\text{-ac}}$ ,  $r_{o\text{-dc}}$ ,  $I_{sc\text{-}}$ ,  $I_{sc\text{-}}$ ,  $v_{sat\text{-}}$ ,  $v_{sat\text{-}}$ , and  $p_d$ .

Step 1: Choose  $c_2 = c_c$  where  $c_c$  is used in the chip as a compensation capacitance.

Step 2:

Step 3:

$$\beta = \frac{I_{ee}}{2I_{p}}$$

Step 4: Choose the saturation current IS for the two transistors Q<sub>1</sub> and Q<sub>2</sub> to be equal to 8E-16 A.

Step 5:

$$r_{c1} = r_{c2} = \frac{1}{2\pi GBPc_2}$$

Step 6:

$$g_{mi} = \frac{I_{ee}}{2v_{T}}$$

Step 7:

$$r_{e1} = r_{e2} = r_{ci} - \frac{1}{g_{mi}}$$

Step 8: Choose  $V_A = 200 \text{ V}$ , then  $r_e = \frac{V_A}{I}$

$$r_e = \frac{V_A}{I_{co}}$$

Step 9:

$$c_1 = \frac{\tan |90^\circ - \phi_{pm}|}{4\pi f_n r_{c1}}$$

Step 10:

$$g_a = \frac{1}{r_{c2}}$$

Step 11:

$$g_{cm} = \frac{1}{CMMRr_{c1}}$$

Step 12: Choose

$$r_2 = 100 \text{ k}\Omega$$

.

Step 13:

$$r_{o2} = r_{o-dc} - r_{o-ac}$$

$$r_{o1} = r_{o-ac}$$

Step 14:

$$a_1 = \frac{A_{dmo}r_{c1}}{r_{o2}}$$

Step 15: Pick

$$-a_2 = a_3 = a_4 = -a_5 = a_1$$

, and then round them off.

Step 16: Choose the diode saturation current for all the diodes used in the model to be equal to 8E-16 A and the diode ohmic resistance  $r_s$  to be 1  $\Omega$ .

Step 17: Choose

$$\alpha = 1$$

K.

Step 18:

$$v_{lp} = \alpha I_{sc+} - v_T \ln \frac{a_1 I_{oe}}{a_4 I S_{dlp}}$$

Step 19:

$$v_{in} = -\alpha I_{sc} - v_{T} \ln - \frac{a_{1} I_{ee}}{a_{s} IS_{din}}$$

Step 20:

$$v_c = v_{p+} - v_{sat+} + v_T ln - \frac{a_1 I_{ee}}{a_2 IS_{dc}}$$

Step 21:

$$v_e = v_{p-} + v_{sat-} + v_T ln \frac{a_1 I_{ee}}{a_3 IS_{de}}$$

Step 22:

$$r_{p} = \frac{(v_{p} - v_{p})^{2}}{p_{d} - (v_{p} - v_{p})I_{ee}}$$

Step 23:

$$E_{GND} = \frac{v_{p^+} + v_{p^-}}{2}$$

### 2.4.4 Numerical example

A numerical example is used to illustrate the development of the parameters of the op amp macromodel and to verify the design formulas and procedure. This verification is done by finding the specifications of the model using the model formulas derived in the previous section and the macromodel parameter's values given in Table 2.1. Table 2.3 includes the calculated and the SPICE simulated measurements using the  $\mu$ A741 microsim macromodel as an example. A list of the equations used to find the calculated measurements are listed below.

$$SR = \frac{I_{\infty}}{c_2}$$

$$SR^{-} = -\frac{I_{ee}}{c_2}$$

$$I_{B} = \frac{I_{B1} + I_{B2}}{2} = \frac{I_{ee}}{2\beta}$$

4)

$$v_{io} = -\frac{g_{cm}}{g_a} \left[ \frac{I_{ee}}{2} r_{ei} + v_T ln(\frac{I_{ee}}{2IS}) + v_{99} \right] - \frac{v_{99}}{r_{02} a_1 g_a}$$

$$f_0 = \frac{1}{2\pi c_2 a_1 r_{02}}$$

$$A_{dmo} = a_1 g_s r_{o2}$$

$$GBP = \frac{g_a}{2\pi c_2}$$

8)

$$f_{\mu} = \sqrt{\frac{-f_2^2 + \sqrt{f_2^4 + 4A_{\text{denso}}^2 f_0^2 f_2^2}}{2}}$$

where

$$f_2 \frac{1}{4\pi r_{c2} c_1}$$

9)

$$\phi_{pm} = 90^{\circ} - \arctan \frac{f_{\mu}}{f_{2}}$$

$$CMMR = \frac{1}{r_{ci}g_{cm}}$$

$$r_{0\rightarrow 0}=r_{01}$$

$$r_{o-dc} = r_{o1} + r_{o2}$$

13)

$$I_{sc*} = \frac{1}{\alpha} (v_{lp} + v_T ln \frac{a_1 I_{ee}}{a_4 IS_{dlp}})$$

14)

$$I_{sc-} = -\frac{1}{\alpha} (v_{in} + v_T ln - \frac{a_1 I_{ee}}{a_5 IS_{din}})$$

15)

$$v_{sat+} = v_{p+} - v_c + v_T ln - \frac{a_1 I_{ee}}{a_2 IS_{dc}}$$

16)

$$v_{\text{sat}} = v_{p} + v_{e} - v_{T} \ln \frac{a_{1} I_{ee}}{a_{3} I S_{de}}$$

17)

$$p_{d} = (v_{p+} - v_{p-})I_{ee} + \frac{(v_{p+} - v_{p-})^{2}}{r_{p}}$$

Table 2.3 Parameters of the µA741

| Parameter          | Calculated   | Simulated    |

|--------------------|--------------|--------------|

| SR <sup>+</sup>    | 0.5053 v/μs  | 0.5074 v/μs  |

| SR <sup>-</sup>    | -0.5053 v/μs | -0.4957 v/µs |

| V <sub>io</sub>    | -19.24 μV    | -19.17 μV    |

| $I_{B}$            | 80.853 nA    | 79.742 nA    |

| $\mathbf{f_o}$     | 5.000 Hz     | 5.012 Hz     |

| A <sub>deno</sub>  | 106.02 dB    | 105.9 dB     |

| GBP                | 1 MHz        | 988.57 KHz   |

| $\mathbf{f}_{\mu}$ | 889.53 KHz   | 891.3 KHz    |

| Ф <sub>реп.</sub>  | 62.81°       | 63.1°        |

| CMRR               | 90 dB        | 90.01 dB     |

| r <sub>o-ac</sub>  | 50 Ω         | 50.4 Ω       |

| r <sub>o-de</sub>  | 150 Ω        | 151.7 Ω      |

| I <sub>sc+</sub>   | 40.614 mA    | 40.61 mA     |

| I <sub>sc</sub> .  | -40.614 mA   | -40.61 mA    |

| V <sub>sat+</sub>  | 14.614 V     | 14.61 V      |

| V <sub>sat-</sub>  | -14.614 V    | 14.61 V      |

| P <sub>d</sub>     | 50 mW        | 50 mW        |

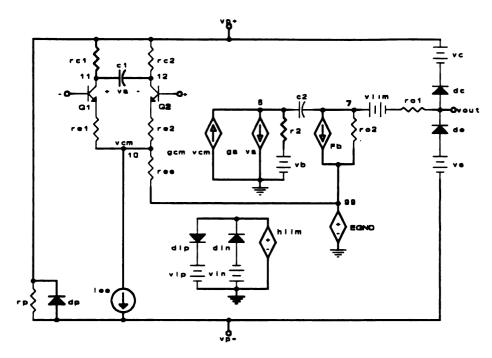

### 2.5 PNP Bipolar Input Stage Macromodel

The pnp input stage microsim macromodel schematic is the same as the npn input stage macromodel with of course pnp transistors replacing the npn transistors. This causes the input stage to be flipped over as it is seen in Fig. 2.20. This type of macromodel has been adapted to many op amps such as: LT1013, LM324, LM124,

subck:

25.1 SP

T macromod

<sup>op</sup> amp is

LM158, LM224, LM258, LM358 .....

Figure 2.20 Microsim macromodel of the LM124

Table 2.4 SPICE file of the LM124 macromodel

- \* + vp+ vp- vout

- \* for the rest of the file see SPICE library version 4.02 July 1989

### 2.5.1 SPICE test circuits

The same SPICE test circuits established previously using the npn input stage macromodel, now will be defined using the pnp input stage macromodel. The LM124 op amp is used as the example. The summarized data of the SPICE test circuit

2.

n

the b

voltag

stag

2.5.3 De

A

model wit to have the

Step 2:

Step 1: Ch

measurements are included in Table 2.5.

#### 2.5.2 Model formulas

The only difference between the npn and pnp input stage macromodel is the input stage. Even though all the previous analysis was done for the npn input stage, including the design equations, the same formulas hold exactly for the pnp macromodel except for the bias current and input offset voltage. The bias current is defined as a negative current since it is flowing out of the base. The input stage is also symmetric, but due to the voltage across  $r_{ee}$  the input offset is not zero and is defined as follows

$$v_{io} = \frac{g_{cm}}{g_a} \left[ \frac{I_{ee}}{2} r_{ei} + v_T ln(\frac{I_{ee}}{2IS}) - v_{99} \right] - \frac{v_{99}}{r_{02} a_1 g_a}$$

#### 2.5.3 Design procedure

A summary of the design equations for the macromodel parameters is developed in this section. The following design procedure could be used for any op amp microsim model with pnp bipolar transistor at the input stage. The starting point of the design is to have the following specifications of the corresponding op amp:  $SR^+$ ,  $SR^-$ ,  $I_B$ ,  $A_{dmo}$ , GBP,  $f_{\mu}$ ,  $\phi_{pm}$ , CMRR,  $r_{o-ac}$ ,  $r_{o-dc}$ ,  $I_{sc}$ ,  $V_{sst}$ ,  $V_{sst}$ , and  $p_d$ .

Step 1: Choose  $c_2 = c_c$  where  $c_c$  is used in the chip as a compensation capacitance.

Step 2:

$$I_{ee} = c_2 SR^+$$

9

8

Ste

Step

Step 7:

Step 8: (

Step 9:

Step 10:

Step 11:

ep 12: CH

$$\beta = \frac{I_{ee}}{-2I_{p}}$$

Step 4: Choose the saturation current for the two transistors  $Q_1$  and  $Q_2$  to be equal to 8E-16 A.

$$r_{c1} = r_{c2} = \frac{1}{2\pi GBPc_2}$$

$$g_{mi} = \frac{I_{ee}}{2v_{T}}$$

$$r_{e1} = r_{e2} = r_{ci} - \frac{1}{g_{mi}}$$

Step 8: Choose

$$V_A = 200 \text{ V}$$

, then  $r_{ee} = \frac{V_A}{I}$

$$r_{ee} = \frac{V_A}{I_{ee}}$$

$$c_1 = \frac{\tan|90^{\circ} - \phi_{pm}|}{4\pi f_{\mu} r_{c1}}$$

$$g_a = \frac{1}{r_{c2}}$$

$$g_{cm} = \frac{1}{CMMRr_{c1}}$$

Step 12: Choose  $r_2 = 100 \text{ k}\Omega$ .

S

Ste

Ste

equ:

Step

Step

Step 19

Step 20

Step 21:

Step 22:

$$r_{o2} = r_{o-dc} - r_{o-ac}$$

$$a_1 = \frac{A_{\text{demo}} r_{c1}}{r_{o2}}$$

Step 15: Pick  $-a_2 = a_3 = a_4 = -a_5 = a_1$ , and then round them off.

Step 16: Choose the diode saturation current for all the diodes used in the model to be equal to 8E-16 A and the diode ohmic resistance  $r_{s}$  to be 1  $\Omega$ .

Step 17: Choose  $\alpha = 1$  K.

$$v_{lp} = \alpha I_{sc} - v_T ln \frac{a_1 I_{ee}}{a_4 IS_{dip}}$$

$$v_{in} = -\alpha I_{sc} - v_{T} ln - \frac{a_{1}I_{ee}}{a_{5}IS_{din}}$$

$$v_c = v_{p+} - v_{sat+} + v_T ln - \frac{a_1 I_{ee}}{a_2 IS_{dc}}$$

$$v_e = v_{p-} + v_{sat-} + v_T ln \frac{a_1 I_{ee}}{a_1 I S_{de}}$$

$$r_{p} = \frac{(v_{p+} - v_{p-})^{2}}{p_{d} - (v_{p+} - v_{p-})I_{ee}}$$

Step 23:

$$E_{GND} = \frac{V_{p+} + V_{p-}}{2}$$

## 2.5.4 Numerical example

This verification is done by finding the specifications of the model using the model formulas derived in the previous section and the macromodel parameter's values given in Table 2.4. Table 2.5 includes the calculated and the SPICE simulated measurements using the LM124 microsim macromodel as an example. A list of the equations used to find the calculated measurements are listed below.

$$SR = \frac{I_{ee}}{c_2}$$

$$SR = -\frac{I_{ee}}{c_2}$$

3)

$$I_{B} = -\frac{I_{B1} + I_{B2}}{2} = -\frac{I_{ee}}{2\beta}$$

4)

$$v_{io} = \frac{g_{cm}}{g_a} \left[ \frac{I_{ee}}{2} r_{ei} + v_T ln(\frac{I_{ee}}{2IS}) - v_{gg} \right] - \frac{v_{gg}}{r_{o2} a_1 g_a}$$

$$f_0 = \frac{1}{2\pi c_2 a_1 r_{02}}$$

$$A_{dmo} = a_1 g_a r_{o2}$$

$$GBP = \frac{g_a}{2\pi c_2}$$

8)

$$f_{\mu} = \sqrt{\frac{-f_{2}^{2} + \sqrt{f_{2}^{4} + 4A_{\text{dmo}}^{2}f_{0}^{2}f_{2}^{2}}}{2}}$$

where

$$f_2 \frac{1}{4\pi r_{c2} c_1}$$

9)

$$\phi_{pm} = 90^{\circ} - \arctan \frac{f_{\mu}}{f_{2}}$$

$$CMMR = \frac{1}{r_{ci}g_{cm}}$$

$$r_{o-ac}=r_{o1}$$

12)

$$r_{0-dc} = r_{01} + r_{02}$$

13)

$$I_{sc*} = \frac{1}{\alpha} (v_{lp} + v_T ln \frac{a_1 I_{ee}}{a_4 IS_{dlp}})$$

14)

$$I_{sc} = -\frac{1}{\alpha} (v_{ln} + v_{T} ln - \frac{a_{1} I_{ee}}{a_{5} IS_{din}})$$

15)

$$v_{\text{sat}} = v_{p} - v_{c} + v_{T} \ln - \frac{a_{1} I_{ee}}{a_{2} I S_{dc}}$$

16)

$$v_{\text{sat}} = v_{p} + v_{e} - v_{T} \ln \frac{a_{1} I_{ee}}{a_{3} I S_{de}}$$

17)

$$p_{d} = (v_{p+} - v_{p-})I_{ee} + \frac{(v_{p+} - v_{p-})^{2}}{r_{p}}$$

Table 2.5 Parameters of the LM124

| Parameter          | Calculated  | Simulated        |

|--------------------|-------------|------------------|

| SR+                | 0.503 V/μs  | 0.4942 V/μs      |

| SR <sup>-</sup>    | -0.503 V/μs | -0.506 V/μs      |

| I <sub>B</sub>     | -45.26 nA   | -44.83 nA        |

| $\mathbf{f_0}$     | 10.00 Hz    | 10.00 Hz         |

| A <sub>demo</sub>  | 100 dB      | 99.91 d <b>B</b> |

| GBP                | 1 MHz       | 989.691 KHz      |

| $\mathrm{f}_{\mu}$ | 982.577 KHz | 962.4 KHz        |

| Фрем               | 79.29°      | 79.5°            |

| CMRR               | 85.43 dB    | 84.97 dB         |

| Г <sub>о-ас</sub>  | 50 Ω        | 50 Ω             |

| r <sub>o-dc</sub>  | 75 Ω        | 75.92 Ω          |

| I <sub>so+</sub>   | 40.613 mA   | 40.61 mA         |

| I <sub>sc</sub> .  | -40.613 mA  | -40.61 mA        |

| V <sub>sat+</sub>  | 14.113 V    | 14.11 V          |

| V <sub>sat</sub> . | -15.613 V   | -15.61 V         |

| Pa                 | 99.55 mW    | 99.5 mW          |

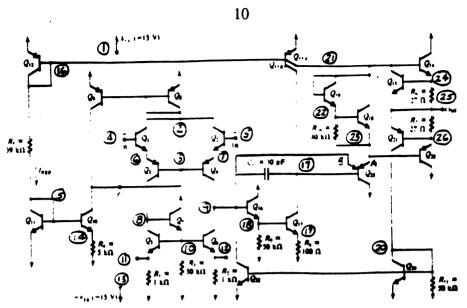

#### 2.6 JFET Input Stage

An other op amp macromodel designed by microsim is the n-channel JFET input stage macromodel (see Fig. 2.21). Its schematic is very similar to the bipolar transistor input stage macromodel with of course JFETs  $j_1$ ,  $j_2$  replacing the transistors  $Q_1$ ,  $Q_2$ . This macromodel has been adapted to several op amps such as: LF411, LF412, TLO82 and TLO84...... The only difference between these two macromodels is the input stage. The intermediate and output stages remain exactly the same as was described previously. The input stage now has a two n-channel JFETs  $j_1$ ,  $j_2$  instead of the two transistors  $Q_1$ ,  $Q_2$ . A capacitance  $c_{ss}$  is added to produce the asymmetric slew rate. Since the input stage has a unity dc gain, then the basic design equations remain the same.

Table 2.6 SPICE file of the LF411 macromodel

.subckt LF411 1 2 3 4 5

- \* + vp+ vp- vout

- \* (for the rest of the SPICE file see SPICE library version 4.02 July 1989)

#### 2.6.1 SPICE test circuits

The same SPICE test circuits established using bipolar input stage macromodel, now will be established using the n-channel JFET input stage macromodel such as the LF411. Table 2.7 provides the summarized data of the SPICE test circuits for the LF411.

Figure 2.21 Microsim model of the LF411

# 2.6.2 Model formulas

The basic operations and design formulas of a n-channel JFET input stage macromodel are described in this section.

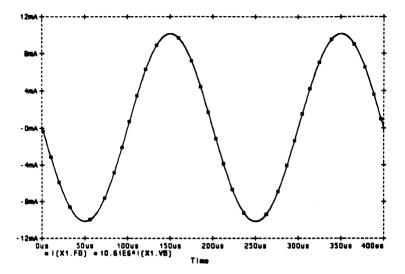

## 2.6.2.1 Slew rate

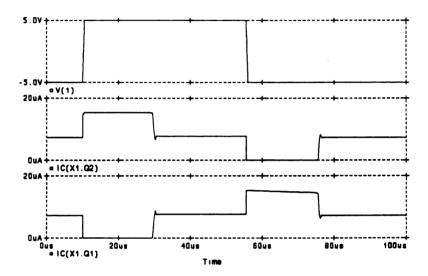

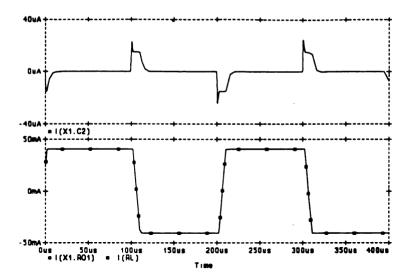

Consider the op amp (LF411) in a closed loop circuit as in Fig. 2.9a with a pulse at the input, the op amp passes through several states. Fig. 2.22 shows the input voltage, and the drain current of  $j_1$  and  $j_2$ .

a) Positive slew rate: SR+

The SPICE simulation (Fig. 2.22), shows that on the rising edge of the input,  $j_2$  is active and  $j_1$  is cutoff. The current flowing in the VCCS  $g_a$  is equal to  $I_{ss}$ . Then, the current  $I_{ss}$  flows out of  $c_2$  because  $r_2$  is usually a large resistance. The voltage across  $c_2$  is almost equal to the output voltage. Thus, the positive slew rate is found to be

$$SR = \frac{I_{ss}}{c_{s}}$$

Figure 2.22 Drain current of  $j_1$  and  $j_2$

#### b) Negative slew rate: SR

At the falling edge of the input, the SPICE simulation (Fig. 2.22) shows that  $j_1$  is active and  $j_2$  is cutoff. At this case  $j_1$  is operating as a source follower tracking the variation of the output voltage. The output voltage is all across the capacitor  $c_{ss}$ , then

$$SR^{-} = \frac{\Delta v_{out}}{\Delta t} = \frac{\Delta v_{css}}{\Delta t} = \frac{I_{css}}{c_{ss}}$$

| <b></b> |  | _4 |

|---------|--|----|

where  $I_{css}$  is the current flowing in  $c_{ss}$ . Since the slope is negative, then  $I_{css}$  is negative quantity and it is pumped out of  $c_{ss}$ . The current flowing in  $r_{d1}$ ,  $I_{rd1}$  is equal to the summation of  $I_{ss}$  and  $I_{css}$ , then

$$I_{\text{rel}} = I_{\text{sc}} + SR^{-}c_{\text{sc}} \tag{2.43}$$

From equation 2.42

$$SR = \frac{I_{rd2}}{c_2}$$

but in this case

$$v_a = -r_{d1}I_{c2}$$

Therefore

$$SR = \frac{I_{rd1}}{c_2}$$

Then, using equation 2.43

$$-c_2SR^-=I_{ss}+SR^-c_{ss}$$

that is

$$SR^{-} = -\frac{I_{ss}}{c_2 + c_{ss}}$$

The capacitance  $c_{ss}$  makes the slew rate asymmetric. That is  $SR^+$  is larger than  $SR^-$  in magnitude.

### 2.6.2.2 JFET parameters

The JFET used at the input stage are presented in SPICE program by the simplest models which does not include internal capacitance and resistances.

The input currents flowing in the gate of  $j_1$ ,  $j_2$  are due to the saturation currents of both pn junctions. The required value of the saturation current specified in SPICE program as IS could be established once the input offset and bias current are given. The SPICE JFET model has two diodes connected to the gate. Thus the gate current,  $I_{Bi}$ , is twice the saturation current,  $I_{Si}$ , of the corresponding JFET, that is

$$I_{Bi} = -2IS_{i}$$

The input offset current,  $I_{io}$  is the difference between the two base currents,

$$I_{io} = I_{B2} - I_{B1}$$

The bias current, I<sub>B</sub> is defined as follows

$$I_{B} = \frac{I_{B1} + I_{B2}}{2}$$

then, the saturation current IS, for each JFET is found to be

$$IS_i = \frac{1}{2}(-I_B \pm \frac{I_{io}}{2})$$

In the case of the microsim model, the JFETs at the input stage are identical, therefore  $I_{io} = 0$ , and  $IS_1 = IS_2 = IS$ .

As it was mentioned previously, the input stage gain has a unity dc gain, that is

$$A_{vl} = g_{m} r_{di} = 1 (2.44)$$

where  $g_m$  is the transconductance defined as follows

$$g_m = 2\sqrt{\beta \frac{I_{ss}}{2}}$$

using equation 2.44,

$$g_{\mathbf{m}} = \frac{1}{r_{di}} \tag{2.50}$$

So obviously, the value of  $\beta$  could be established once the value of  $r_{di}$  is determined, where

$$\beta = \frac{1}{2I_{xx}r_{di}^{2}} \tag{2.45}$$

The input offset voltage,  $v_{io}$  could be modelled as the difference in the threshold voltages of the two JFETs used at the input. This threshold voltage in noted in SPICE program as VTO, that is  $v_{io}$  is equal to

$$v_{io} = VTO_1 - VTO_2$$

where VTO<sub>1</sub> and VTO<sub>2</sub> are respectively the threshold voltage of  $j_1$ ,  $j_1$ . Since  $j_1$  and  $j_2$  have the same VTO, then  $v_{io} = 0$  V. So the microsim did not model the input offset current and the input offset voltage for this type of op amp macromodel. However from SPICE measurement, it shows that vio is different from zero and that is because of the voltage drop across  $r_{ss}$ .  $v_{io}$  is found to be equal to

$$v_{io} = -\frac{g_{cm}}{\sqrt{2\beta I_{ss}}} \left[ \sqrt{\frac{I_{ss}}{2\beta}} - VTO + v_{99} \right] - \frac{v_{99}}{r_{o2} a_1 \sqrt{2\beta I_{ss}}}$$

# 2.6.2.3 Input stage gain: r<sub>di</sub>

The intermediate and output stage design equations of the JFET input stage macromodel are the same as the bipolar input stage macromodel except for some minor changes due to the notation.

# 2.6.2.4 Input stage: r<sub>ss</sub>

The resistance  $r_{ss}$  is added for the same purpose as  $r_{ee}$  in case of bipolar input stage macromodel and is defined as

$$r_{ss} = \frac{V_A}{I_{ss}}$$

where  $V_A$  is the early voltage of the device.

#### 2.6.2.5 Intermediate and output stage

Since, the intermediate stage and output stage are exactly the same as the bipolar op amp macromodel, the previous analysis holds for this op amp macromodel. Therefore, the other design equation are the same as the bipolar input stage.

### 2.6.3 Design procedure

A summary of the design equations for the macromodel parameters is developed in this section. The following design procedure could be used for any op amp microsim model with a n-channel JFETs at the input stage. Given the following specifications:  $SR^+$ ,  $SR^-$ ,  $I_B$ ,  $A_{dmo}$ , GBP,  $f_{\mu}$ ,  $\phi_{pm}$ , CMRR,  $r_{o-ac}$ ,  $r_{o-dc}$ ,  $I_{sc+}$ ,  $I_{sc-}$ ,  $v_{sat+}$ ,  $v_{sat-}$  and  $p_d$ , then the design procedure is

Step 1: Choose  $c_2 = c_c$  where  $c_c$  is used in the chip as a compensation capacitance.

Step 2:

$$I_{x}=c_{x}SR^{+}$$

Step 3:

$$c_{ss} = \frac{I_{ss}}{-SR^-} - c_2$$

Assuming  $SR^+ > -SR^-$ .

Step 4: Choose the saturation current of the two JFETs to be equal to 12.5 pA and VTO = -1 V.

Step 5:

$$r_{di} = \frac{1}{2\pi c_2 GBP}$$

Step 6:

$$\beta = \frac{1}{2I_{m}r_{a}^{2}}$$

Step 7: Choose

$$V_A = 200 \text{ V}$$

, then  $r_{ss} = \frac{V_A}{I_{ss}}$

Step 8:

$$c_1 = \frac{\tan |90^\circ - \phi_{pm}|}{4\pi f_u r_{di}}$$

Step 9:

$$g_a = \frac{1}{r_{ab}}$$

Step 10:

$$g_{cm} = \frac{1}{CMMRr_{di}}$$

Step 11: Choose

$$r_2 = 100 \text{ k}\Omega$$

.

Step 12:

$$r_{o2} = r_{o-dc} - r_{o-ac}$$

$$r_{o1} = r_{o-ac}$$

Step 13:

$$a_1 = \frac{A_{\text{dmo}} r_{\text{di}}}{r_{\text{o}2}}$$

Step 14: Pick  $-a_2 = a_3 = a_4 = -a_5 = a_1$ , and then round them off.

Step 15: Choose the diode saturation current for all the diodes used in the model to be equal to 8E-16 A and the diode ohmic resistance  $r_s$  to be 1  $\Omega$ .

Step 16: Choose  $\alpha = 1 \text{ K}$

Step 17:

$$v_{lp} = \alpha I_{sc} - v_T ln \frac{a_1 I_{ee}}{a_4 IS_{dlp}}$$

Step 18:

$$v_{in} = -\alpha I_{sc} - v_{T} ln - \frac{a_{1} I_{ee}}{a_{5} IS_{din}}$$

Step 19:

$$v_c = v_{p+} - v_{sat+} + v_T ln - \frac{a_1 I_{ee}}{a_2 IS_{de}}$$

Step 20:

$$v_e = v_{p-} + v_{sat-} + v_T ln \frac{a_1 I_{ee}}{a_3 IS_{de}}$$

Step 21:

$$r_{p} = \frac{(v_{p+} - v_{p-})^{2}}{p_{d} - (v_{p+} - v_{p-})I_{ee}}$$

Step 22:

$$E_{GND} = \frac{v_{p+} + v_{p-}}{2}$$

### 2.6.4 Numerical example

This verification is done by finding the specifications of the model using the model formulas derived in the previous section and the macromodel parameter's values given in Table 2.6. Table 2.7 includes the calculated and the SPICE simulated measurements using the LF411 microsim macromodel as an example. A list of the equations used to find the calculated measurements are listed below.

$$SR = \frac{I_{ss}}{c_2}$$

$$SR = -\frac{I_{ss}}{c_2 + c_{ss}}$$

$$I_{B} = -2IS$$

4)

$$v_{io} = -\frac{g_{cm}}{\sqrt{2\beta I_{ss}}} \left[ \sqrt{\frac{I_{ss}}{2\beta}} - VTO + v_{99} \right] - \frac{v_{99}}{r_{o2} a_1 \sqrt{2\beta I_{ss}}}$$

$$f_0 = \frac{1}{2\pi c_2 a_1 r_{02}}$$

$$A_{dmo} = a_1 g_a r_{o2}$$

$$GBP = \frac{g_a}{2\pi c_2}$$

8)

$$f_{\mu} = \sqrt{\frac{-f_2^2 + \sqrt{f_2^4 + 4A_{dmo}^2 f_0^2 f_2^2}}{2}}$$

where

$$f_2 \frac{1}{4\pi r_{di} c_1}$$

$$\phi_{pm} = 90^{\circ} - \arctan \frac{f_{\mu}}{f_{2}}$$

$$CMMR = \frac{1}{r_{di}g_{cm}}$$

$$r_{o-ac} = r_{o1}$$

$$r_{o-dc} = r_{o1} + r_{o2}$$

I<sub>sc</sub> =

$$\frac{1}{\alpha} (v_{ip} + v_T ln \frac{a_i I_{ee}}{a_4 IS_{dip}})$$

14)

$$I_{sc-} = -\frac{1}{\alpha} (v_{ln} + v_{T} ln - \frac{a_{I} I_{ee}}{a_{5} IS_{din}})$$

15)

$$v_{\text{sat}} = v_{p} - v_{c} + v_{T} \ln - \frac{a_{1} I_{ee}}{a_{2} IS_{dc}}$$

16)

$$v_{sat} = v_{p} + v_{e} - v_{T} ln \frac{a_{1}I_{ee}}{a_{3}IS_{de}}$$

17)

$$p_{d} = (v_{p+} - v_{p-})I_{ee} + \frac{(v_{p+} - v_{p-})^{2}}{r_{p}}$$

Table 2.7 Parameters of the LF411

| Parameter            | Calculated   | Simulated  |

|----------------------|--------------|------------|

| SR⁺                  | 17 V/μs      | 19.6 V/μs  |

| SR <sup>-</sup>      | -11.975 V/μs | -15.07V/μs |

| V <sub>io</sub>      | -6.691 μV    | -3.25 μV   |

| I <sub>B</sub>       | -25 pA       | -40.32 pA  |

| $\mathbf{f_0}$       | 20.000 Hz    | 19.95 Hz   |

| A <sub>demo</sub>    | 106.02 dB    | 112 dB     |

| GBP                  | 4 MHz        | 7.942 MHz  |

| $\mathrm{f}_{\mu}$   | 3.292 MHz    | 5.412 MHz  |

| $\phi_{\mathbf{pm}}$ | 55.37°       | 41.4°      |

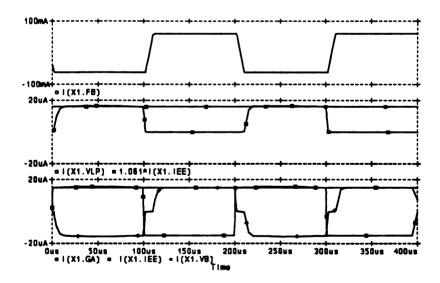

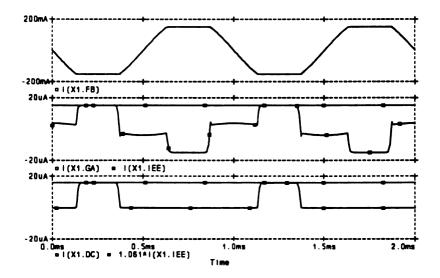

| CMRR                 | 100 dB       | 106.07 dB  |