### This is to certify that the

### dissertation entitled

# Design and Test of Current-mode Signal Processing Circuits

presented by

Shoba Krishnan

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Electrical Engineering

Date (AUG 4, 93

MSU is an Affirmative Action/Equal Opportunity Institution

0-12771

# LIBRARY Michigan State University

PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due.

| 1            | DATE DUE | DATE DUE |

|--------------|----------|----------|

| FEB_0_5_199/ |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

MSU Is An Affirmative Action/Equal Opportunity Institution c:\circ\datadus.pm3-p.1

# **Design and Test of Current-mode Signal Processing Circuits**

Вÿ

## Shoba Krishnan

### **A DISSERTATION**

submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

**DOCTOR OF PHILOSOPHY**

Department of Electrical Engineering

#### **ABSTRACT**

## **Design and Test of Current-mode Signal Processing Circuits**

#### By

#### Shoba Krishnan

The shrinking feature sizes of devices and their increasing density make it necessary that a reduced supply of 3.3V and lower operating voltages be used in order to enhance performance and reliability. The effects of this reduction are especially impressive for battery-operated systems, as this reduces power drain, which extends battery life and allows for smaller and lighter portable equipment. As pressures increase on VLSI designers to use lower power, voltage-mode techniques will deteriorate in performance due to reduced dynamic range and operating speeds. Analog design has historically been viewed as a voltage-dominated form of signal processing and, all too often, the electronics engineer will think in voltage terms rather than current simply because of the unavailability of current-mode signal processing circuits. Current-mode circuits, circuits in which signals are processed mainly in the current domain, will become increasingly important and attractive as they improve dynamic range and operating speed and have simpler circuitry and lower power consumption. In this study, these inherent advantages of current-mode techniques are applied to the design of data-acquisition and conversion circuits.

To decrease costs and increase performance of electronic circuits, it has become increasingly necessary to integrate both analog and digital circuits on-chip, thus making the

fabrication process very complicated. Current-mode circuits generally do not require high precision resistors or capacitors and can be designed almost exclusively with transistors making them fully compatible with most standard digital CMOS processes. Matched currents are typically generated using current mirrors which depend on good component device matching. Although the use of laser-trimming technology may result in good component device matching, the fabrication process is costly. This work develops and analyzes current-mode signal processing circuits in MOS technology that achieve their functionality without the need for well-matched components.

In real-time applications, it is important to achieve validation of the data generated from data-acquisition and conversion elements. Even though analog MOS circuits are becoming increasingly sophisticated in terms of checking and correcting themselves, the techniques used may not be appropriate when a fatal fault occurs during real-time operation. It would be preferable for the circuits to be designed such that they will indicate malfunction during normal operation and will not produce an erroneous result without an error indication. This dissertation implements time redundancy techniques in analog circuit design for reliability enhancement. In addition, current-mode Built-In Self-Test (BIST) structures are developed to increase the number of test points in a circuit, while still keeping low pin overhead.

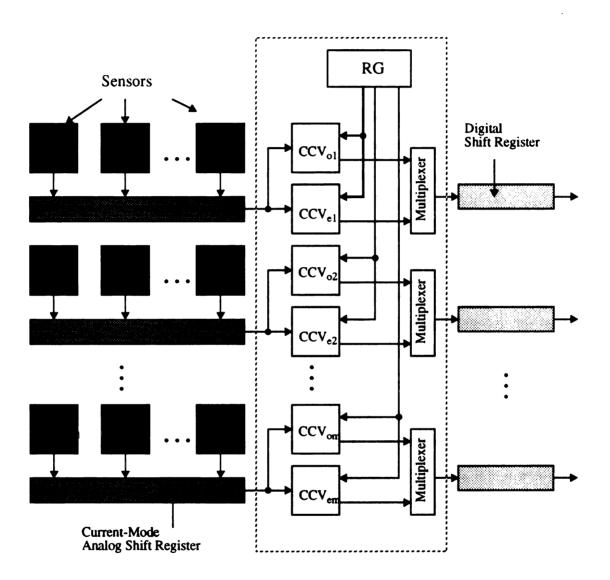

Sensor arrays, in which signal processing is integrated with the sensor, are being employed in many applications. The requirement on speed of the data-acquisition and conversion circuits in such implementations is not very high, but the reduction of the size and power consumption is the most important. Thus, the developed current-mode signal processing circuits and diagnosable design methodologies are well suited for the design of reliable integrated sensor arrays.

To my parents

Alamelu and Kalyana Krishnan

# **ACKNOWLEDGEMENTS**

I would like to thank my advisor, Dr. Chin-Long Wey, for his guidance and encouragement throughout my graduate studies and this research. I would also like to thank my committee members, Dr. J. Resh, Dr. G. Wierzba, and Dr. J. B. Eulenberg for sharing their time and advice through the course of this dissertation. I am very grateful to my parents, Alamelu and Kalyana Krishnan, and my husband, Venkatesh, for their constant concern and encouragement and direct assistance in the preparation of this manuscript. I would especially like to thank my friend, Sondes, for her continual support and help.

# **TABLE OF CONTENTS**

| LIST OF TA | ABLES      |                                                 | ix |

|------------|------------|-------------------------------------------------|----|

| LIST OF FI | GURES      |                                                 | x  |

| Chapter 1: | Introduc   | tion                                            | 1  |

| •          |            |                                                 | _  |

| 1.1        | Potential  | of Current-mode Signal Processing Circuits      | 2  |

| 1.2        | Importan   | ce of Reliability                               | 6  |

| 1.3        | Dissertat  | ion Organization                                | 8  |

| Chapter 2: | Backgro    | und                                             | 9  |

| 2.1        | J          |                                                 | 9  |

| 2.1        | •          | uisition and Conversion Techniques              |    |

|            | 2.1.1      | Sample-and-hold (S/H) Circuits                  | 9  |

|            | 2.1.2 A    | Analog-to-Digital (A/D) Converters              | 12 |

| 2.2        | Current-   | node Circuits                                   | 18 |

|            | 2.2.1      | Current Mirrors                                 | 18 |

|            | 2.2.2      | Current Copiers                                 | 22 |

|            | 2.2.3 I    | Oynamic Current-mode Signal Processing Circuits | 28 |

|            | 2.2.3.1    | Current-mode Multiplier                         | 28 |

|            | 2.2.3.2    | Current-mode Divider                            | 28 |

|            | 2.2.3.3    | Current-mode A/D Converter                      | 31 |

| 2.3        | Fault-tole | erant and Testable Circuit Design               | 31 |

|            | 2.3.1 F    | Fault Tolerance                                 | 33 |

|            | 2.3.2      | Festability Techniques                          | 34 |

| Chapter 5: | Current-mode Data-acquisition and Data-conversion |     |

|------------|---------------------------------------------------|-----|

|            | Circuits                                          | 40  |

| 3.1        | Bipolar Current Copier                            | 40  |

|            | 3.1.1 Circuit Design and Operation                | 41  |

|            | 3.1.2 Analysis                                    | 43  |

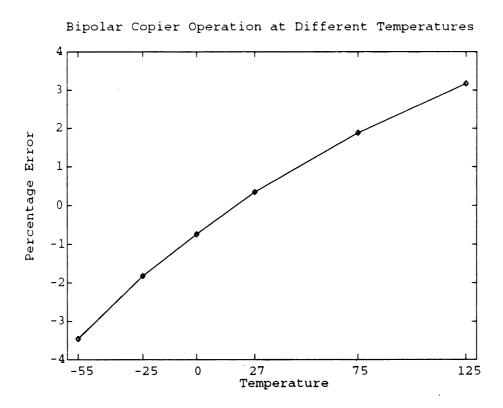

|            | 3.1.3 Experimental Results                        | 44  |

| 3.2        | Current-mode Shift Register                       | 47  |

|            | 3.2.1 Operation Principle                         | 50  |

|            | 3.2.2 Design Considerations                       | 54  |

|            | 3.2.3 Simulation Results                          | 55  |

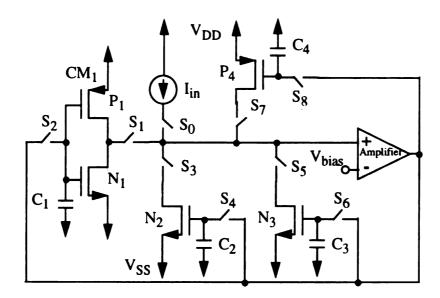

| 3.3        | Current-mode Divider Circuit                      | 61  |

|            | 3.3.1 Method of Operation                         | 61  |

|            | 3.3.2 Performance Estimation                      | 63  |

|            | 3.3.3 Experimental Verification                   | 66  |

| 3.4        | Successive-approximation A/D Converter            | 69  |

|            | 3.4.1 Circuit Description                         | 75  |

|            | 3.4.2 Analysis                                    | 79  |

|            | 3.4.3 Design Evaluation                           | 80  |

|            | 3.4.4 Array Structures                            | 83  |

|            | 3.4.5 Hardware Reduction                          | 85  |

|            | 3.4.6 Implementation                              | 87  |

| 3.5        | Summary                                           | 88  |

|            |                                                   |     |

| Chapter 4: | Testable Current-mode Circuits                    | 89  |

| 4.1        | Testable Current-mode A/D Converter               | 90  |

|            | 4.1.1 Concurrent Error Detection                  | 90  |

|            | 4.1.1.1 Fault Models                              | 93  |

|            | 4.1.1.2 Fault Coverage                            | 94  |

|            | 4.1.2 Test Generation                             | 101 |

|            | 4.1.2.1 Fault Model and Fault Effects      | 101 |

|------------|--------------------------------------------|-----|

|            | 4.1.2.2 Test Generation and Fault Coverage | 104 |

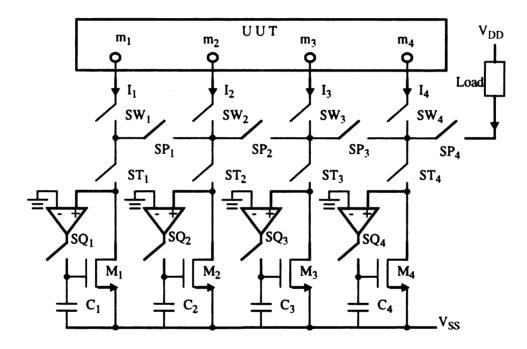

| 4.2        | Testable Data-acquisition Circuits         | 105 |

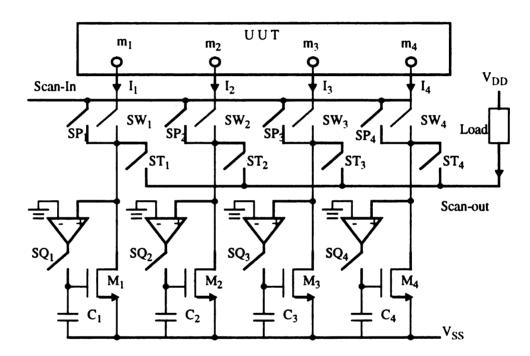

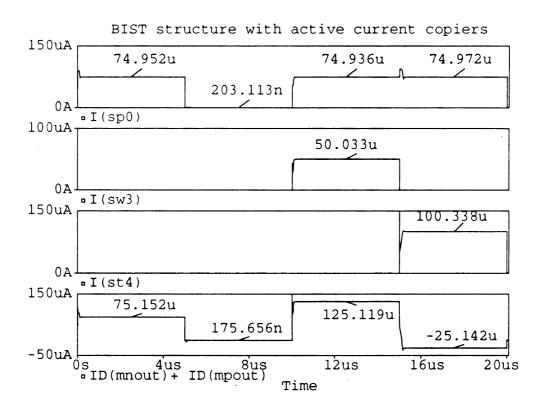

|            | 4.2.1 Built-In Self-Test Structures        | 106 |

|            | 4.2.2 Experimental Results                 | 110 |

| 4.3        | Summary                                    | 112 |

| Chapter 5: | Conclusions                                | 115 |

| 5.1        | Summary                                    | 115 |

| 5.2        | Contributions                              | 118 |

| 5.3        | Future Research                            | 119 |

| APPENDIX   | A: A CMOS Opamp                            | 124 |

| APPENDIX   | B: PSpice Files                            | 126 |

| LIST OF RE | FERENCES                                   | 130 |

# LIST OF TABLES

| Table 2.1 | Comparison of Current Mirror Structures                           | 22  |

|-----------|-------------------------------------------------------------------|-----|

| Table 3.1 | Relationship among $\gamma$ , k and the Corresponding Error Terms | 65  |

| Table 3.2 | Error Terms Obtained from Simulations                             | 71  |

| Table 3.3 | Relationship among γ, k and N                                     | 80  |

| Table 4.1 | Type 1 Errors                                                     | 96  |

| Table 4.2 | Type 2 Errors                                                     | 97  |

| Table 4.3 | Type 3 Errors                                                     | 98  |

| Table 4.4 | Type 4 Errors                                                     | 100 |

| Table 4.5 | Error Detection                                                   | 100 |

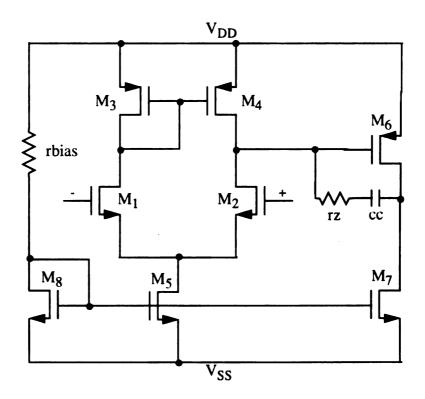

| Table A.1 | Simulated Characteristics of Opamp                                | 125 |

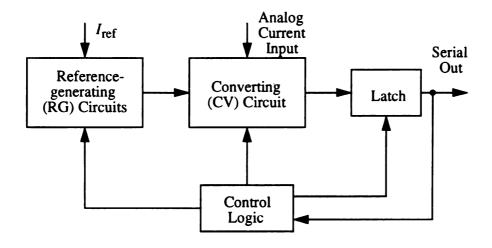

# **LIST OF FIGURES**

| Figure 1.1  | A Sensor Array Implementation                                    | 5  |

|-------------|------------------------------------------------------------------|----|

| Figure 1.2  | Testing of the A/D Converter                                     | 7  |

| Figure 2.1  | A Sample-and-hold Circuit                                        | 10 |

| Figure 2.2  | Block Diagram of a Time Interleaved A/D Converter                | 14 |

| Figure 2.3  | Successive-approximation A/D Converter:                          |    |

|             | (a) Block Diagram; and (b) Voltage Waveform                      | 16 |

| Figure 2.4  | A Simple N-Channel Current Mirror                                | 19 |

| Figure 2.5  | Simple Current Copier: (a) NMOS Copier; and (b) PMOS Copier      | 24 |

| Figure 2.6  | Active NMOS Copier                                               | 27 |

| Figure 2.7  | Current-mode Multiplier                                          | 29 |

| Figure 2.8  | A Highly Accurate Current Divider: (a) Schematic Diagram;        |    |

|             | and (b) Switching Sequence                                       | 29 |

| Figure 2.9  | Current-mode A/D Converter: (a) Schematic Diagram; and           |    |

|             | (b) Switching Sequence                                           | 32 |

| Figure 2.10 | The Concept of Time Redundancy                                   | 38 |

| Figure 3.1  | Bipolar Current Copier: (a) Simple Copier; and (b) Active Copier | 42 |

| Figure 3.2  | Experimental Results of a Bipolar Current Copier                 | 45 |

| Figure 3.3  | Unidirectional Limitation of NMOS and PMOS Copiers               | 46 |

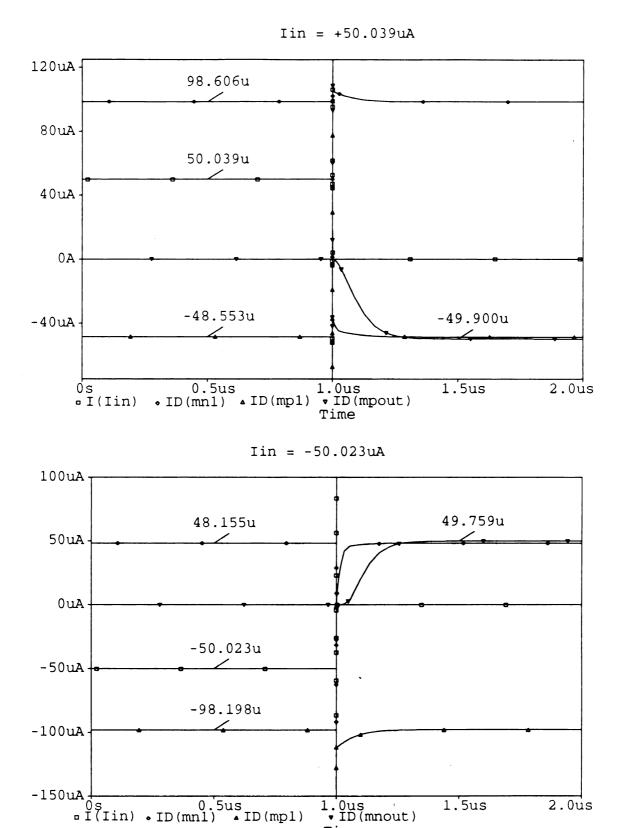

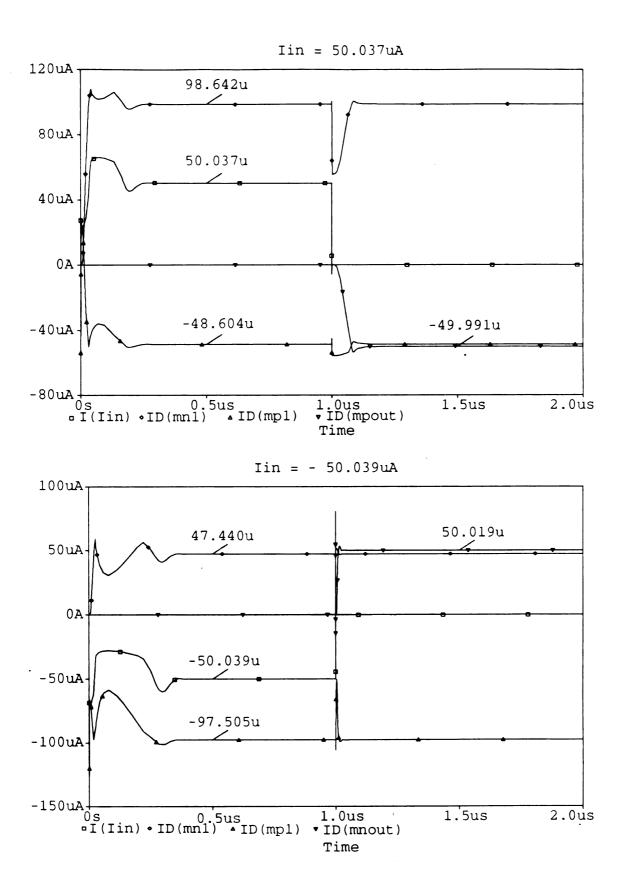

| Figure 3.4  | PSpice Simulation of a Bipolar Current Copier                    | 48 |

| Figure 3.5  | PSpice Simulation of a Bipolar Active Copier                     | 49 |

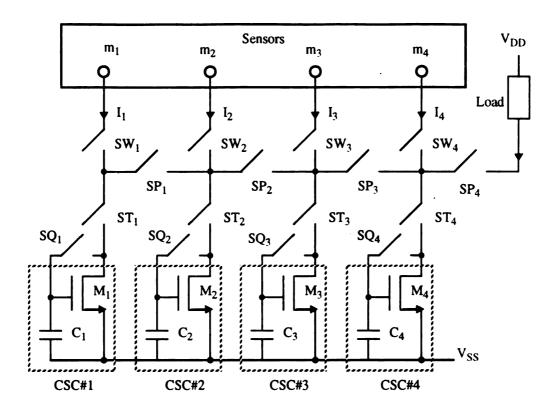

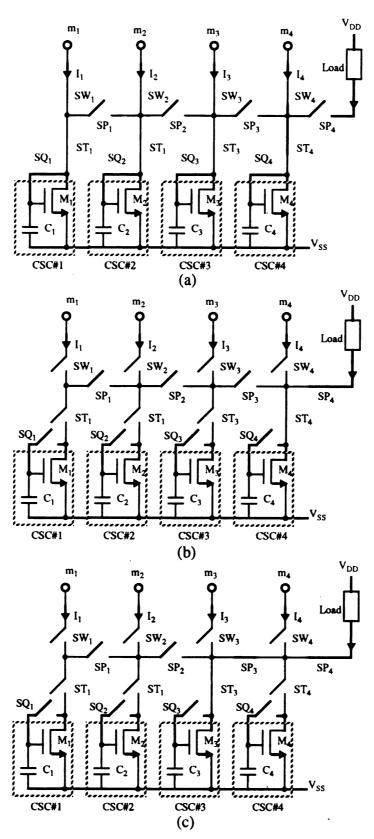

| Figure 3.6  | Current-mode Shift Register Using Simple Current Copiers         | 51 |

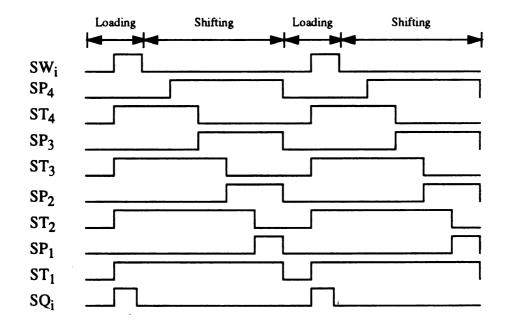

| Figure 3.7  | Switching Sequence for Load/Shift Operation                      | 51 |

| Figure 3.8  | Operation Sequence during Load/Shift:(a) Parallel Loading; and   |    |

|             | (b) & (c) Serial Shifting                                        | 52 |

| Figure 3.9  | A Current-mode Shift Register Using Active Current Copiers            | 53  |

|-------------|-----------------------------------------------------------------------|-----|

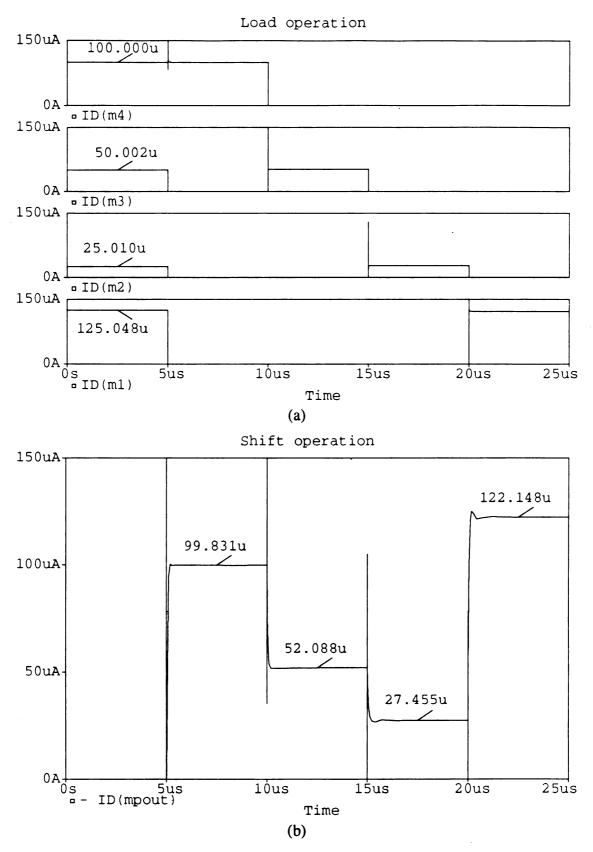

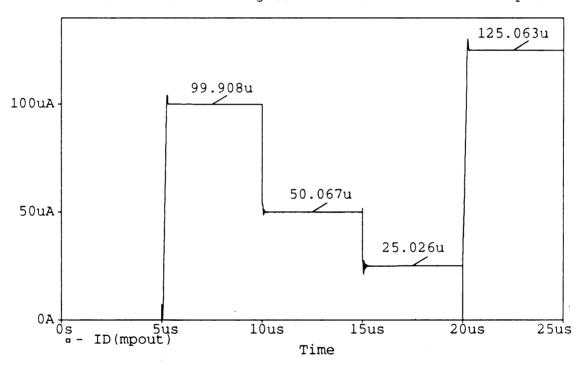

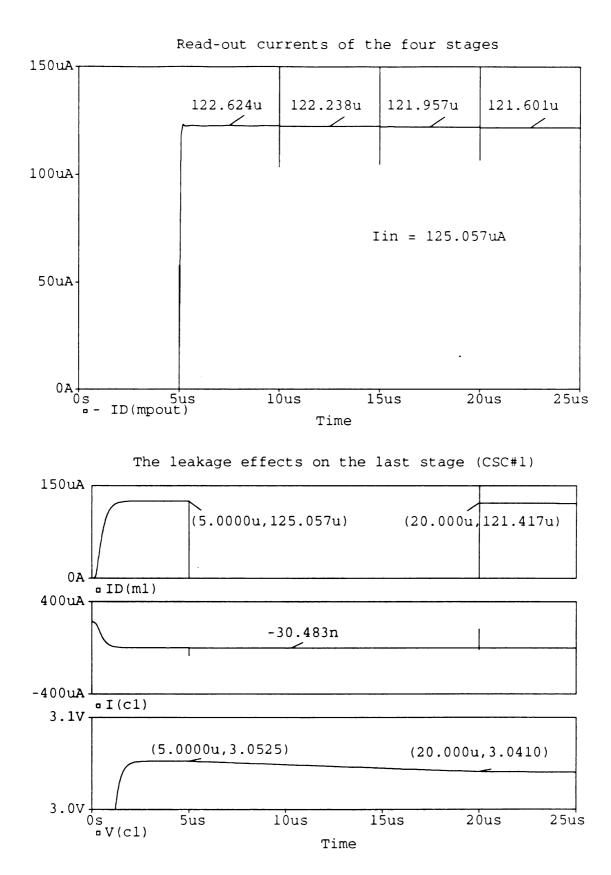

| Figure 3.10 | Simulation of the Current-mode Shift Register: (a) Varied             |     |

|             | Inputs; and (b) Output of the PMOS Copier Load                        | 56  |

| Figure 3.11 | Simulation of the Shift Register with Active Copiers                  | 57  |

| Figure 3.12 | Error Effects of the Sample-and-hold Procedure                        | 59  |

| Figure 3.13 | Improvements to the Acquisition Procedure                             | 60  |

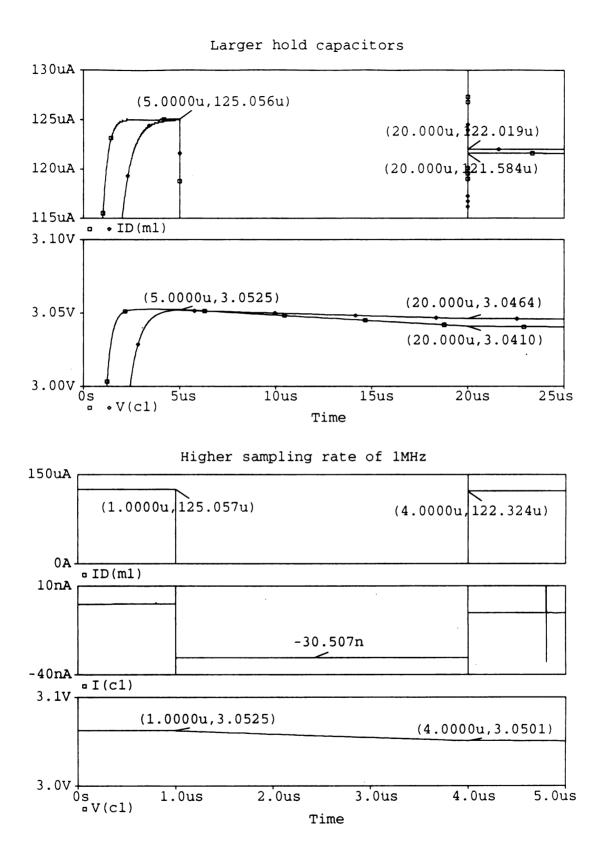

| Figure 3.14 | The Alternative Current-mode Divider                                  | 62  |

| Figure 3.15 | Operational Sequence of Divider                                       | 62  |

| Figure 3.16 | PSpice Simulations of the Current-mode Divider                        | 67  |

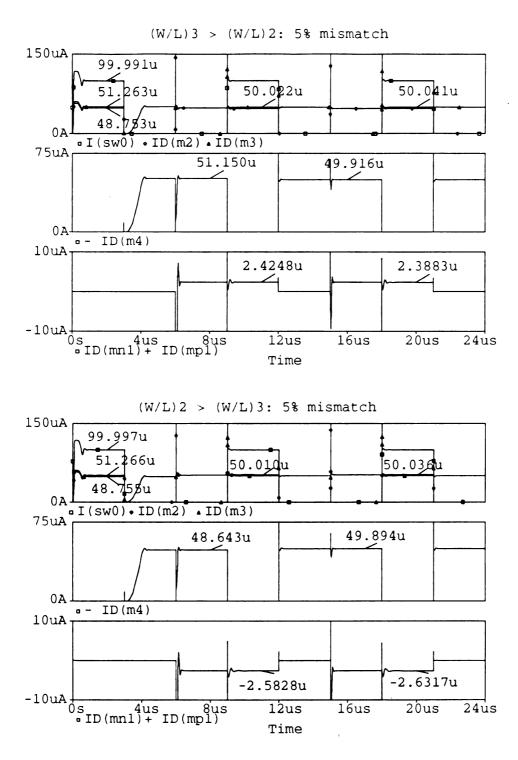

| Figure 3.17 | Divider Operation with 5% Mismatch                                    | 68  |

| Figure 3.18 | Divider Operation with 10% Mismatch                                   | 70  |

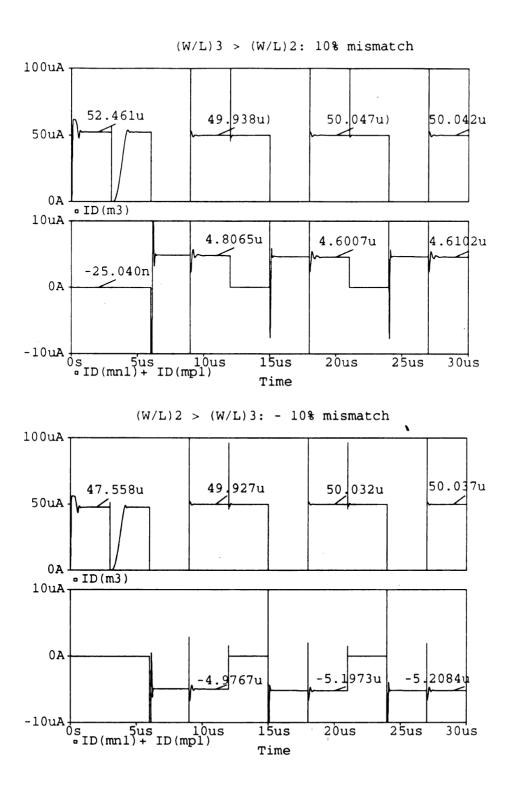

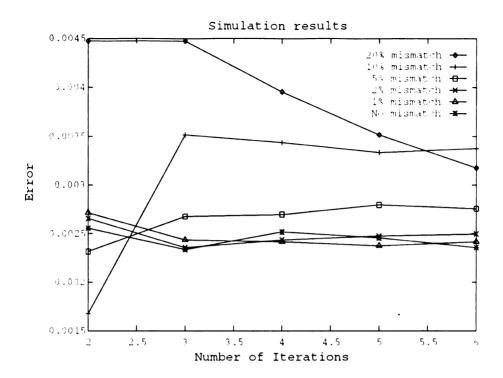

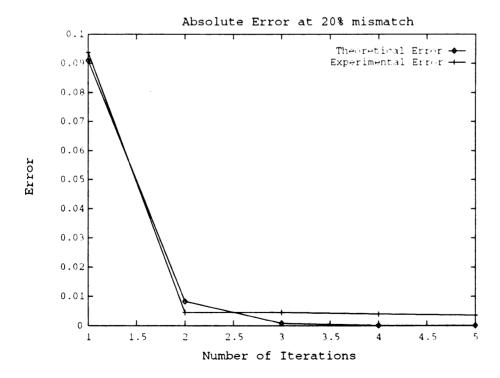

| Figure 3.19 | Experimental Error Terms                                              | 72  |

| Figure 3.20 | Comparison of Error Terms                                             | 72  |

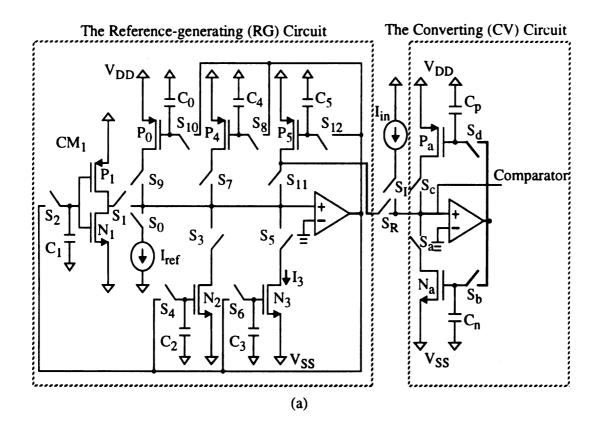

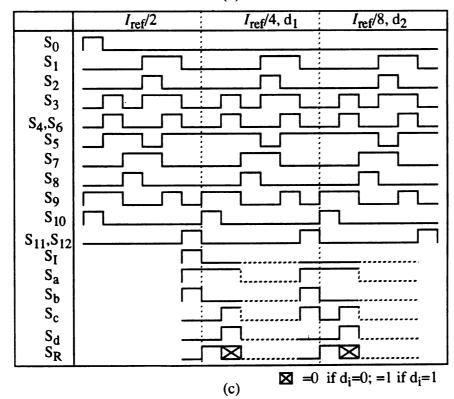

| Figure 3.21 | Block Diagram of a Current-mode Successive-approximation              |     |

|             | A/D Converter                                                         | 74  |

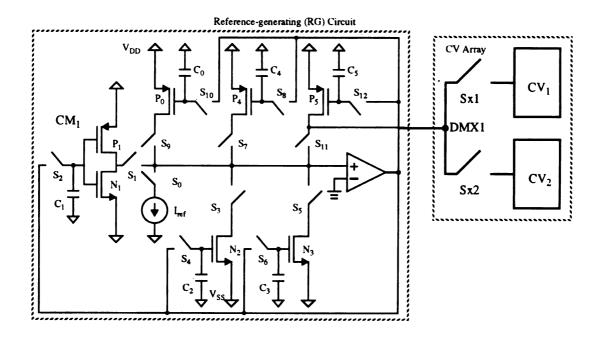

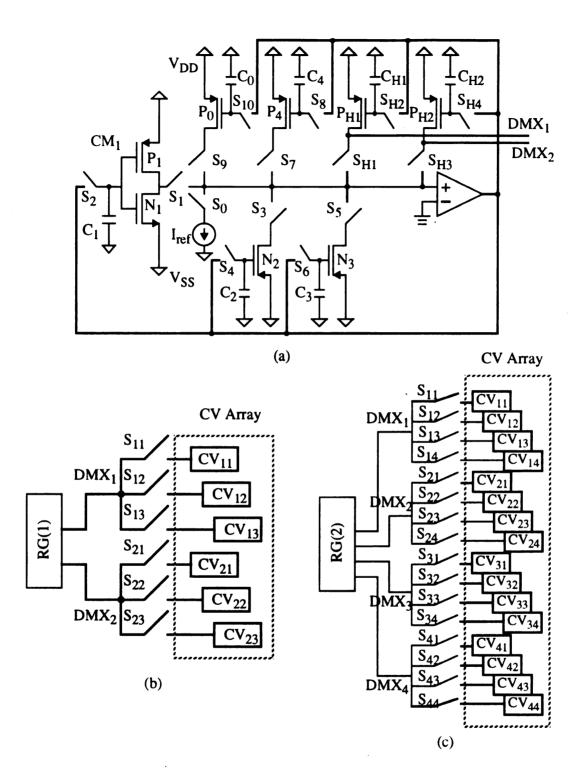

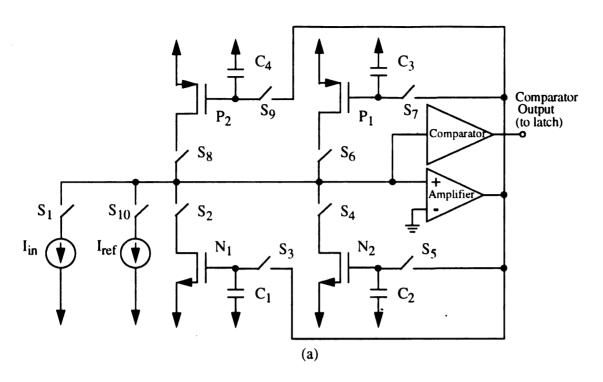

| Figure 3.22 | Proposed Current-mode A/D Converter: (a) Schematic Diagram;           |     |

|             | (b) Current Copying Sequence; and (c) Switching Sequence              | 76  |

| Figure 3.23 | A Converter Array with two CV Circuits                                | 82  |

| Figure 3.24 | Converter Arrays (a) RG(1) Circuit; (b) RG(1) Circuit with            |     |

|             | 2-by-3 CV Array; and (c) RG(2) with 4-by-4 CV Array                   | 84  |

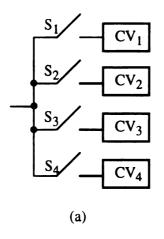

| Figure 3.25 | Hardware Reduction (a) An Array with 4 CV Circuits; and               |     |

|             | (b) Combined CV (CCV) Circuits: CCV <sub>o</sub> and CCV <sub>e</sub> | 86  |

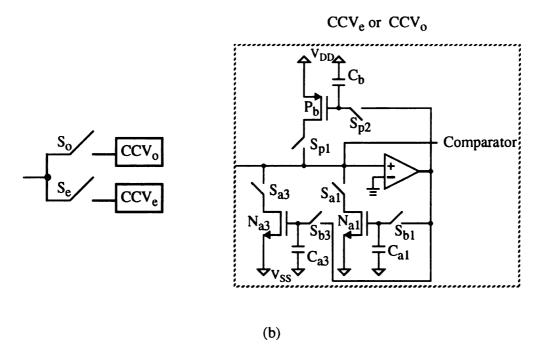

| Figure 4.1  | CED Structure with AL Implementation                                  | 91  |

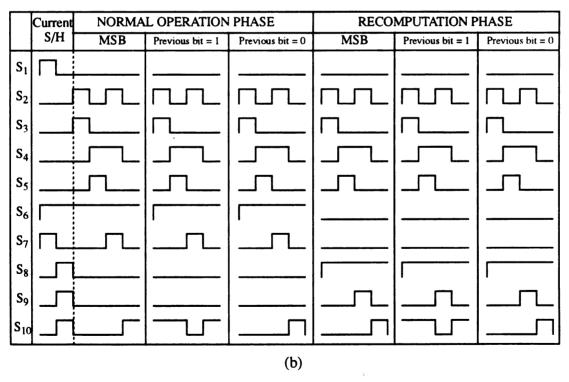

| Figure 4.2  | Proposed Current-mode A/D converter with CED Design:                  |     |

|             | (a) Schematic Diagram; and (b) Switching Sequence                     | 92  |

| Figure 4.3  | Modified Current-mode A/D Converter                                   | 102 |

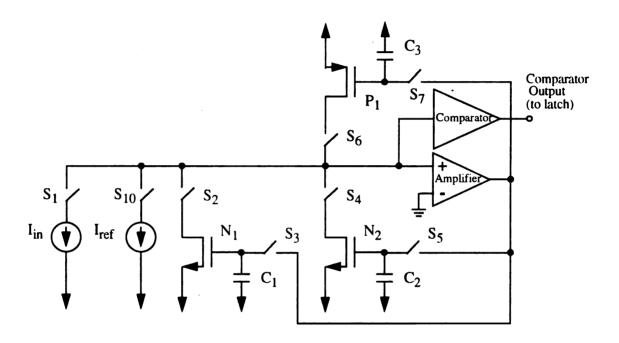

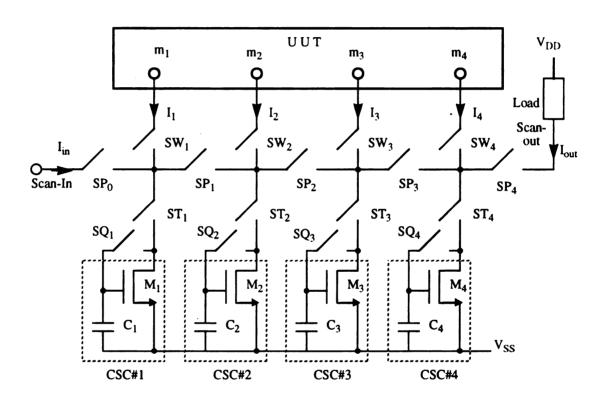

| Figure 4.4  | An BIST Structure Using Simple Current Copiers                        | 107 |

| Figure 4.5  | An Improved BIST Structure with Active Current Copiers                | 111 |

| Figure 4.6  | BIST Tests for Various Faults                                         | 113 |

| Figure 5.1 | A Sensor Array Implementation                      | 121 |

|------------|----------------------------------------------------|-----|

| Figure 5.2 | Temperature Dependence of Bipolar Copier Operation | 123 |

| Figure A.1 | A Two-stage CMOS Opamp                             | 124 |

# **Chapter 1**

## Introduction

The present trend in digital integrated circuits (ICs) towards submicron technologies with 3.3 V power supplies is increasing. The shrinking feature sizes of devices and their increasing density makes it necessary to have reduced supply and operating voltages to help enhance their performance and reliability [1]. The widespread use of MOS technology, with its unique ability to accurately store and transfer voltages or charge packets, led to the development of analog IC techniques in which voltage was used as the signal. These techniques, though quite successful in many applications, have deteriorated in performance due to reductions in the available supply voltage and the move to ever smaller geometries [2]. Thus, there is difficulty in designing high-linearity, wide-dynamic-range and high-speed voltage-mode analog circuits.

Analog circuit design has historically been viewed as a voltage-dominated form of signal processing. This has been apparent in analog IC design where generally current signals are readily transferred into the voltage domain before any analog signal processing takes place. All too often, transistors are assembled into voltage-oriented circuits and systems, and this form of processing is assumed to be most appropriate for the task, although BJTs and FETS are both current-output devices. The electronics engineer will think in voltage terms rather than current simply because of the unavailability of current-mode signal processing circuits such as data-acquisition and data-conversion systems [3].

Sample-and-hold circuits (S/H), analog-to-digital (A/D) converters and digital-to-analog (D/A) converters form an integral part of real-time systems. Validation of the data

generated from these elements for real-time applications is very important. Analog MOS circuits are becoming increasingly sophisticated in terms of checking and correcting themselves [4]. They use self-correcting, self-compensating, or self-calibrating techniques to eliminate errors traditionally associated with analog circuits such as offset, low frequency noise, and non-linearities [5,6,7]. However, these techniques may not be appropriate when a fatal fault occurs during real-time operation. It would be preferable for the circuits to be designed such that they will indicate malfunction during normal operation and will not produce an erroneous result without an error indication.

This study addresses the potential of current-mode circuits for signal processing, and presents their applications and reliability issues for real-time systems.

## 1.1 Potential of Current-mode Signal Processing Circuits

A current-mode circuit may be taken to mean any circuit in which current is used as the active variable in preference to voltage. Current-mode circuits have emerged over the last decade as an important class of analog circuits with properties that enable them to rival their voltage-mode counterparts in a wide range of applications [8]. Recently, a number of novel circuit functions and topologies have been explored on the broader front of current-mode analog circuits, opening up wider areas of interest. Current conveyors and related current-mode circuits such as current converters, amplifiers and current rectifiers are only a few of the circuits that have been successfully constructed using Bipolar, MOS, BiCMOS, GaAs, and optical technologies [8].

There are many advantages to be gained by signal processing embracing current-mode techniques. Due to the nonlinear I-V relationship exhibited by most transistor structures, a small change in input voltage results in a much larger change in the output current [9]. Consequently, for a process with a fixed voltage supply, the usable dynamic range of current-mode signals is significantly larger than that of their voltage-mode counterparts. It has long been recognized that current manipulation is inherently faster than voltage manipulation, since the effects of stray inductances are less severe than those

of stray capacitances [10]. Thus, there is potential for higher operating frequencies in current-mode circuits.

To decrease the costs and increase the performance of electronic circuits, it has become increasingly necessary to integrate both analog and digital circuits on the same IC [11]. The problem is that the most commonly available process, the standard digital CMOS process, does not offer the linear components with which analog design is usually implemented. Until recently the only solution to this problem was to develop more complicated processes that can provide such linear components. Thus, there is a need for circuitry that is compatible with the standard digital CMOS process. Current-mode signal processing circuits generally do not require high precision resistors or capacitors. When capacitors are used to store the signal, they need not display good ratio matching or good linearity. Consequently, these circuits can be designed almost exclusively with transistors making them fully compatible with most digital processes. Generally, current-mode circuits do not require amplifiers with high voltage gains thereby reducing the need for high performance amplifiers [12].

When current is used as the active parameter, the need for matched signals implies a need for matched currents [13]. Matched currents are generally generated using current mirrors which depend on good component device matching. Although the use of laser-trimming technology may result in good component device matching, the fabrication process is costly. Therefore, it is necessary to develop current-mode circuits which achieve their functionality without the need of well-matched components.

The continued growth of mixed analog/digital VLSI systems will ensure the need for small size, high speed analog-to-digital and digital-to-analog converters fabricated using commonly available digital processes. Mixed signal VLSI design is essential to analog and digital interfacing, and the immunity of current-mode circuits to supply noise is an important property in a mixed-mode environment. Also, in large data-acquisition systems there is a preference for the use of current to represent the measurand as it is fairly interference-resistant [14]. This is because of the low probability that DC currents would be induced in data-transmission lines.

The complexity of current-mode circuits is generally less than their voltage-mode counterparts for the same function, as currents may be manipulated to yield more effective and efficient circuit realizations. They have also been found to be a cheaper alternative to voltage-mode circuits for many applications. Another significant advantage rests in the immunity of current signals to deleterious influences such as ground and power supply noise, debiasing, and signal line impedance [15]. These technological reasons form the basis of many commonly used current-mode circuits.

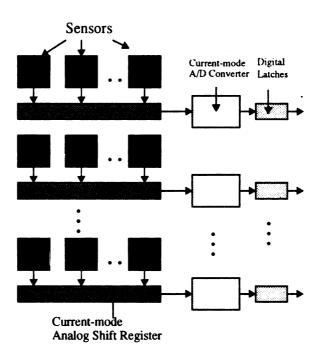

One of the important applications of current-mode signal processing circuits is in the design of integrated sensors. Integrated sensors have the inherent advantages of small size, light weight, high performance, low cost, and high reliability. They provide a better signal-to-noise ratio, improved sensitivity, and a digital output which is less prone to noise. Smart sensor arrays improve overall system performance by changing the system architecture to take advantage of signal processing that is integrated with the sensor [16]. A sensor array chip must include data-acquisition and conversion circuits as well as an array of sensing elements, as shown in the block diagram of Figure 1.1. Each sensing element may include a signal conditioning circuit and/or a simple analog signal processor. When a scan has been completed, each cell in the array will be holding the raw sensing data as either voltages or currents which are read out and converted by either a high-speed current-mode A/D converter, or an array of medium-speed converters. The requirement on speed of the acquisition and conversion circuits is not very high in many such implementations, but the reduction of the size and power consumption is of utmost importance [17].

This dissertation develops a current-mode shift register that can be wound through the array and simultaneously load the data which can then be serially read out to be converted. This dissertation also presents the design of current-mode A/D converter arrays in which each subconverter does not rely on high gain amplifiers or well-matched components to achieve high resolution. Incorporating parallel signal processors into an IC sensor array will increase the overall computation rate significantly.

Figure 1.1 A Sensor Array Implementation

One of the primary motivations of this work, therefore, is to apply the inherent advantages of current-mode techniques to the design of data-acquisition and conversion circuits. The goal of this dissertation is to develop, analyze and construct these current-mode signal processing circuits in MOS technology and to explore the limits of their applications.

## 1.2 Importance of Reliability

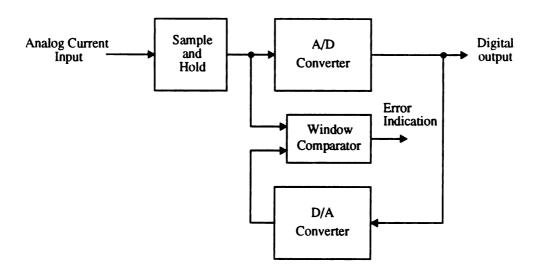

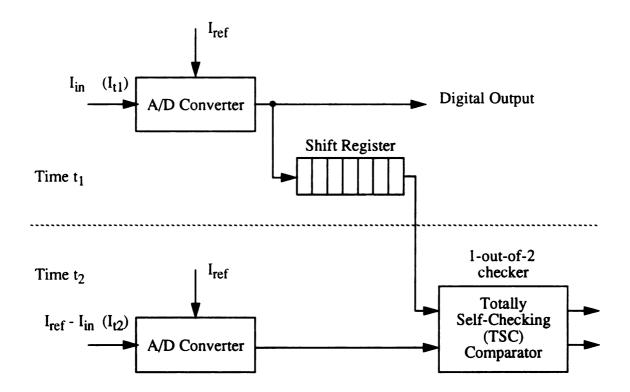

For real-time applications, in general, the validation of data from A/D converters is accomplished by using an extra D/A converter and an analog window comparator [18], as shown in Figure 1.2, where a high-resolution and high-accuracy D/A converter is needed and the comparison is performed in an analog manner. Therefore, the validation must highly depend upon the reliability of both the D/A converter and the window comparator. Although their reliability may be improved by using sophisticated testing schemes to weed out faulty components [19], such off-line or static tests cannot identify the transient faults that occur during on-line operation. Therefore, it is obvious that a mechanism for concurrent error detection (CED) [20-22] must be installed to detect such faults before they cause undesirable results.

One of the objectives of this dissertation is to implement time-redundancy techniques in analog circuit design for reliability enhancement of real-time systems. In this study, an alternative current-mode A/D converter with CED capability is presented in which the Alternating Logic technique [22] is implemented. The fault model considered here is the single stuck-at fault at the switching elements. The A/D converter is capable of detecting all transient faults and most permanent faults.

For more than two decades, the subjects of automatic testing and fault diagnosis of electronic circuits have been of interest to researchers in the area of circuits and systems [23-28]. Recently, with rapidly increasing complexity and size of modern electronic systems, these subjects have become more important and critical. Due to the difficulty of current measurement in an analog circuit, most of the fault diagnosis algorithms have been

Figure 1.2 Testing of the A/D Converter

developed requiring only node voltage measurement [23-26]. However, it has been shown that the use of both current and voltage measurement can simplify the diagnosis process significantly [27,28]. This dissertation presents alternative Built-In Self-Test (BIST) structures in order to allow the voltage and current test data measured at various test points to be shifted out for fault diagnosis.

## 1.3 Dissertation Organization

This dissertation is organized as follows. Chapter 2 presents background knowledge of data-acquisition and conversion circuits in general and existing current-mode signal processing methods specifically. The concepts of reliability and fault testing applied in diagnosable design are also touched upon.

Chapter 3 describes in detail several basic elements developed, followed by descriptions of data-acquisition and conversion systems in which they are used. A bipolar current copier that forms a sample-and-hold building block is first presented. A current-mode shift register used as a data-acquisition system is also discussed. An accurate current-mode divider circuit which does not rely on well-matched components is later described. A successive-approximation A/D converter that can be adapted into a parallel array structure with a common reference unit is finally illustrated. Several design issues are addressed, and simulation results give a thorough understanding of the functioning and performance of these current-mode signal processing circuits.

Chapter 4 describes the incorporation of reliability into these circuits and presents the diagnosable current-mode circuit design methodology. Finally, Chapter 5 summarizes this dissertation and contributions of this study as well as future research topics.

# Chapter 2

# **Background**

This chapter briefly reviews the background knowledge of data-acquisition and conversion circuits in general and existing current-mode signal processing methods. In addition, the concepts of reliability and testability are also discussed.

## 2.1 Data-acquisition and Conversion Techniques

Sample-and-hold circuits are the essential elements in data-acquisition systems and contribute significantly to their performance. Analog-to-digital (A/D) and Digital-to-analog (D/A) converters are the primary components of data-conversion, and they have been implemented using several techniques. The operation principles and characteristics of different sample-and-hold elements and A/D converters are described in this section.

## 2.1.1 Sample-and-hold (S/H) Circuits

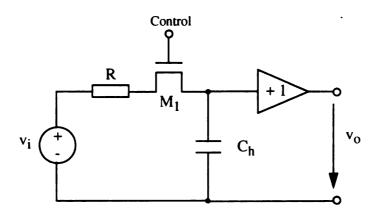

A sample-and-hold (S/H) circuit is an essential building block of sampled data systems and its operation and properties are described in this section. The function of a S/H circuit in its simplest configuration is to take samples from an input signal during the sample mode and then to hold the last value of the input signal for a certain time interval, called the hold mode [29]. An elementary S/H circuit is shown in Figure 2.1. The switch

Figure 2.1 A Sample-and-hold Circuit

$M_1$  is implemented by a single or complementary MOS transistor. During the sample mode the input voltage source  $v_i(t)$ , which has an internal resistance R, is connected to the hold capacitor  $C_h$  via the MOS switch  $M_1$ . The capacitor voltage follows (tracks) the input voltage assuming that the time constant  $RC_h$  is small enough. When the 'hold' mode is selected and the switch is opened, the capacitor voltage remains fixed at the input signal level. To avoid the discharging of the hold capacitor  $C_h$  by an output circuit, a buffer amplifier (voltage follower) is usually used. If necessary, a second voltage follower is used at the input of the S/H stage to avoid loading the input signal source.

In the ideal S/H circuit, tracking is error-free; i.e. the capacitor is immediately charged and the change from the sampling to the hold mode and vice-versa occurs instantaneously. However, there are several factors that determine the performance of practical S/H elements. For example, in the switched capacitor implementation of the elementary S/H circuit, noise and unbalanced charge injection are the major sources of error of the sampled voltage.

The most important S/H circuit parameters are defined as follows [29]:

- (1) Acquisition Time: The time required after receipt of the sample command for the hold capacitor to charge to a specified voltage change and remain within a specified error band.

- (2) Slew-Rate: The maximum rate of change of the output voltage after receipt of the sample command and for a voltage step applied to the input.

- (3) Aperture Uncertainty Time: The time variation or jitter in the opening of the sampling switch.

- (4) Hold-Mode Droop Rate: The output voltage change per unit of time during the hold mode.

- (5) Offset: The extent to which the output deviates from zero for zero input.

- (6) Feedthrough Offset: The step error occurring at the initiation of the hold mode caused by the clock voltage feedthrough through the gate-source or gate-drain overlap capacitances and the unbalanced channel charge stored in the MOS switch.

## 2.1.2 Analog-to-Digital (A/D) Converters

A/D converters are used to transform continuous-time or discrete-time analog signals (typically voltages) to digital data which can then be easily processed, stored, and/ or transmitted digitally. An A/D converter connected between some analog sensors and a digital computer, must be able to accept the outputs from these sensors as its inputs. It should provide its digital outputs to the computer and its complete operation and performance must be tailored to that of the overall system. For example, there is no need for a converter to have 12-bit accuracy if the signals from the sensor are accurate only to 8-bits.

When the input signals to the converter change as a function of time, which is most often the case, it is important to consider all the factors that determine the dynamic behavior of a converter [29]. A/D conversion is ideally considered to take place instantly but in real converters this process takes a finite amount of time for completion during which the output cannot be updated. The dynamic parameters of the converter primarily characterize the speed of converter operation. The most important of these parameters are conversion time, conversion rate (often called throughput rate) and aperture effects (delay, jitter). Conversion time is the amount of time required for an A/D converter to perform one complete conversion under the least favorable conditions. Alternatively, to determine the conversion speed one uses the conversion rate (throughput rate) defined as the maximal number of repetitive analog-to-digital conversions per second. It is calculated as the reciprocal of the total time required for one successful conversion.

Depending upon the structure and the principle of operation, A/D converters can be divided into several different categories such as parallel (direct), serial (or sequential), and serial/parallel. Based on the speed of conversion, A/D converters can be divided into three groups: high-speed, medium-speed, and slow-speed [29]. This categorization is based on the conversion time which is 50nsec for a high-speed converter while the medium-speed and low-speed types convert at 50µsec and 100msec, respectively.

### **High-Speed A/D Converters**

High-speed A/D converters find application in the encoding of composite video signals. Parallel or flash converters are the fastest and largest of this group. Both pipelined and time-interleaved array converters offer a fast conversion rate and a smaller circuit.

In a parallel or flash A/D converter, the reference is divided into 2<sup>N</sup> nominally equal segments, thus generating all possible signal quantization levels. It employs the most straightforward approach to achieve high-speed analog-to-digital conversion by performing 2<sup>N-1</sup> simultaneous voltage comparisons with the 2<sup>N-1</sup> equally spaced reference sources, where N is the number of bits. If the input signal is higher than the quantization level under consideration, an output bit of 1 is generated; otherwise an output bit of 0 is produced. This digital code is then converted to the desired binary code by an encoder circuit. The main advantage of flash A/D converters is their high conversion rate. However the exponential increase in the number of comparators as a function of resolution limits the practicality of such converters.

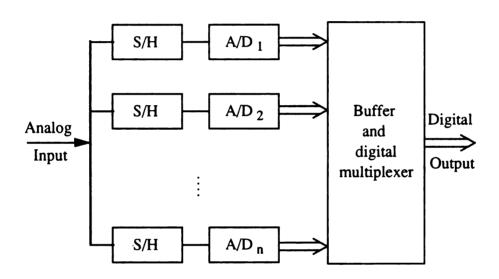

In time interleaved array A/D converters, n identical N-bit A/D converters with S/H stages are connected in n parallel channels as shown in Figure 2.2. In each channel, the input signal is sampled and held and then converted at a rate of 1/nT. By staggering the S/H stages in time such that the sampling in the second channel is T seconds behind that in the first channel and so on, the input signal can be sampled and held each T seconds by a different A/D converter in the structure. Hence, the overall system achieves a conversion rate n times higher than that of the building A/D subconverter. A buffer and a digital multiplexer stage is used at the output to service the conversion channels one at a time. For high-speed input signals very stable and regular sampling intervals are required. Even a small, deviation from the nominal sampling frequency of 1/nT may cause considerable error since it leads to overlapping the input signals. A high-speed analog demultiplexer can be used to relax the sampling accuracy requirement by converting the analog input signal into n lower-speed sampled and held data signals which are fed into the appropriate sample-and-hold stage.

Figure 2.2 Block Diagram of a Time Interleaved A/D Converter

The pipelined A/D converter architecture is such that the pipe consists of m basic stages, each stage consisting of a S/H circuit and a low-resolution low-speed A/D converter. The input signal flows sequentially through successive stages, so the converter produces an N-bit digital word over several sampling periods rather than one period. The main idea of a pipelined A/D converter is to insert S/H structures between the subconverter stages in order to operate all the stages concurrently thus achieving a high conversion rate which is almost independent of the number of stages. The principal disadvantage of pipelining is the requirement of high-speed and high-precision S/H structures.

### **Medium-Speed A/D Converters**

This class of A/D converters commonly employ successive-approximation and cyclic or algorithmic conversion techniques. Both techniques offer a relatively good speed-size performance.

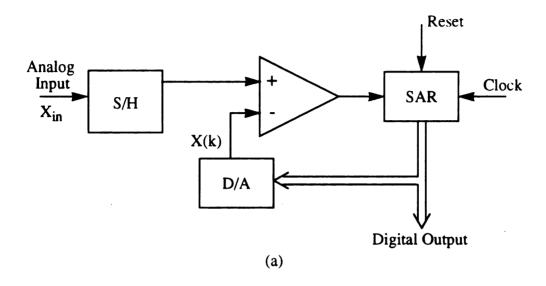

Successive-approximation A/D converters require the use of a S/H stage, a signal comparator, a D/A converter and a successive-approximation register (SAR) as shown in Figure 2.3 (a). The input S/H stage is used to hold the analog input signal constant during the conversion process. The converter operates on the following principle: after the reset in the first conversion step, the SAR sets the D/A output to  $X_r/2$ . Hence, the most significant bit or MSB, d<sub>1</sub>, is assumed to be one whereas all other bits are set to zero. If the input is higher than  $X_r/2$ , the MSB is left at one; otherwise, it is reset to zero. In the next step, the D/A converter output is set to  $X_r/2 \pm X_r/4$  where the plus sign is taken if  $d_1$ = 1 and the minus sign if  $d_1$  = 0. This signal is again compared with the input and the second most significant bit is determined depending on the result of comparison as seen in Figure 2.3(b). In the following step, the output of the D/A is to be incremented or decremented by  $X_r/8$  and a third comparison is performed leading to  $d_3$ . The process continues until all bits of the output word have been determined. Such a converter requires only N clock cycles to complete an N-bit conversion. Mathematically, the algorithm which describes the operation of the successive-approximation A/D can be represented as follows:

Figure 2.3 Successive- Approximation A/D Converter:

(a) Block Diagram; and (b) Voltage Waveform

$$X(k) = X(k-1) - \frac{(-1)^{a_{k-1}}}{2^{k}} X_{r}$$

with  $d_{k} = 1$  if  $X_{in} > X(k)$  and  $d_{k} = 0$  otherwise

for  $k = 1, 2, ..., N$  where  $X(0) = X_{r}$ .

A bipolar A/D conversion can be achieved by introducing a sign bit  $d_0$  to select either  $+X_r$  or  $-X_r$ .

The cyclic or algorithmic A/D converter involves the basic operations of comparison, subtraction and multiplication by two. Conversion is based on holding the reference signal constant and multiplying the signal to be converted by two during each conversion cycle. Conversion begins with sampling the input signal,  $X_{in}$ , doubling it, then comparing it with  $X_r$  in order to generate the MSB  $d_1$ . If  $2X_{in} \ge X_r$  then  $d_1$  is set to 1,  $X_r$  is subtracted from  $2X_{in}$  and the difference is multiplied by two. Otherwise,  $d_1$  is set to 0 and  $X_{in}$  is multiplied by two. This procedure continues according to the algorithm described by the next set of equations until the desired resolution is achieved.

$$X(k) = 2X(k-1) + (-1)^{a_{k-1}}X_r$$

(2.2)

with  $d_k = 1$  if  $X(k) \ge 0$  and  $d_k = 0$  otherwise

for  $k = 1, 2,...,N$  where  $X(0) = X_{in}, d_0 = 1$ .

### **Low-Speed A/D Converters**

High resolution converters can be obtained using one of the described conversion techniques at the expense of costly fabrication technology and/or complicated circuitry. Two alternative techniques achieve high resolution without these burdens but their conversion speed is negatively affected.

The integrating type A/D converter operates with a conversion cycle consisting of two separate integration intervals. In the first interval the analog input signal is integrated up for a fixed and known period of time. In the second interval the negative reference signal is integrated down until the output voltage of the integrator returns to zero. This time period

is then proportional to the input signal. At the start of conversion, the integrator and the counter are both zeroed to guarantee stable timing. The important feature of this result is that the digital output is independent of the integration time constant and of the clock frequency since these parameters affect both the first and the second interval in the same ratio.

In oversampling A/D converters, the input signal is sampled at a rate much higher than the Nyquist rate, then converted to a digital stream in an interpolative modulator. The quantized approximation of the input signal is subtracted from it and the difference is integrated. The integrator in the loop tends to minimize the average difference of the sampled analog input and the quantized approximation. The output of the estimator goes to a digital-low-pass filter which averages and decimates this coarse estimate to get a finer approximation at a lower sampling rate.

## 2.2 Current-mode Circuits

This section reviews some traditional concepts of current-mode circuits. Current-mode signal processing circuits using dynamic techniques and challenges in their design are also described.

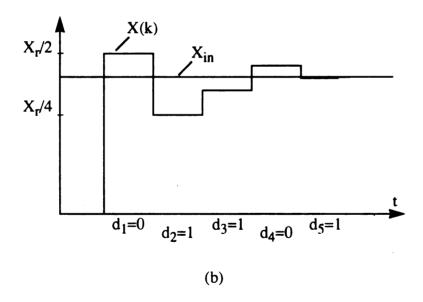

### 2.2.1 Current Mirrors

The current mirror is a very useful and familiar building block in CMOS analog circuit design. Current mirrors use the principle of matched devices such that if the gate-to-source potential of two identical MOSFETS are equal, their currents are equal [30]. Figure 2.4 shows the implementation of a simple n-channel current mirror. The current  $i_I$  is assumed to be defined by a current source or some other means and  $i_O$  is the output or "mirrored" current.  $M_1$  is in saturation because  $V_{DS1}=V_{GS1}$ . In the most general case, the ratio of  $i_O$  to  $i_I$ , is then

Figure 2.4 A Simple N-Channel Current Mirror

$$\frac{i_O}{i_I} = \left(\frac{L_1 W_2}{W_1 L_2}\right) \left(\frac{V_{GS} - V_{T2}}{V_{GS} - V_{T1}}\right)^2 \left(\frac{1 + \lambda V_{DS2}}{1 + \lambda V_{DS1}}\right) \left(\frac{\mu_{o2} C_{ox2}}{\mu_{o1} C_{ox1}}\right)$$

(2.3)

where  $(W/L)_i$  are the aspect ratios,  $V_{Ti}$  is the threshold voltage of the MOSFETs. Normally, the components of a current mirror are processed on the same integrated circuit and thus all of the physical parameters such as  $V_T$ ,  $\mu_O$ ,  $C_{ox}$ , etc., are identical for both devices. As a result, (2.3) simplifies to

$$\frac{i_O}{i_I} = \left(\frac{L_1 w_2}{w_1 L_2}\right) \left(\frac{1 + \lambda v_{DS2}}{1 + \lambda v_{DS1}}\right) \tag{2.4}$$

If  $V_{DS2}$  =  $V_{DS1}$  (not always a good assumption ) then the ratio of  $i_O/i_I$  becomes

$$\frac{i_O}{i_I} = \left(\frac{L_1 W_2}{W_1 L_2}\right) \tag{2.5}$$

Consequently, i<sub>O</sub>/i<sub>I</sub> is a function of the aspect ratios that are under the control of the designer. However, there are three main factors that cause the current mirror to be different than the ideal situation of (2.5). These factors are: (1) channel-length modulation, (2) threshold offset between the two transistors, and (3) imperfect geometrical matching.

Consider the channel-length modulation effect. Assuming all other aspects of the transistor are ideal and the aspect ratios of the two transistors are both unity, then (2.4) simplifies to

$$\frac{i_O}{i_I} = \left(\frac{1 + \lambda V_{DS2}}{1 + \lambda V_{DS1}}\right) \tag{2.6}$$

with the assumption that the modulation parameter  $\lambda$  is the same for both transistors. This equation shows that differences in drain-source voltages of the two transistors can cause a deviation for the ideal unity current gain or current mirroring.

Consider two transistors in a mirror configuration where both have the same drainsource voltage and all other aspects of the transistors are identical except  $V_T$ . In this case, (2.3) simplifies to

$$\frac{i_O}{i_I} = \left(\frac{v_{GS} - v_{T2}}{v_{GS} - v_{T1}}\right)^2 \tag{2.7}$$

It is also possible that the transconductance gain K' of the current mirror is also mismatched. Assume that the W/L ratios of the two mirror devices are exactly equal but that K' and  $V_T$  may be mismatched. (2.3) is then written as

$$\frac{i_O}{i_I} = \frac{\kappa_2 (v_{GS} - v_{T2})^2}{\kappa_1 (v_{GS} - v_{T1})^2}$$

(2.8)

The third nonideal effect of current mirrors is the error in the aspect ratio of the two devices. These are due to mask, photolithographic, etch, and out-diffusion variations. These variations can be different even for two transistors placed side by side. One way to avoid the effects of these variations is to make the dimensions of the transistors much larger than the typical variation one might see. For transistors of identical size with W and L large in value, the errors due to geometrical mismatch will generally be insignificant compared to offset-voltage and  $V_{DS}$  induced errors.

In most current mirror realizations, ideal mirroring is true only for a range of voltages, and there is a minimum voltage,  $V_{MIN}$ , below which the realization will not be a good approximation of the input current. This is because the MOS transistor in the nonsaturation region is not a good current source. Even in the region where it is a good approximation, it deviates due to the resistance  $r_{out}$  which is ideally infinite. Thus, the small signal output resistance of a current mirror is important in determining its performance. Therefore,  $V_{MIN}$  and  $r_{out}$  are the two major aspects by which these mirrors can be characterized.

The advantage of this current mirror is its simple structure. Higher performance current mirrors will attempt to increase the value of  $r_{out}$  and reduce  $V_{MIN}$  further. Several

improvements such as bootstrapped structures or cascode structures have also been implemented. Table 2.1 summarizes the performance of the different types of MOS current mirrors having unity gain from the viewpoint of accuracy (linearity), output resistance, and V<sub>MIN</sub> [31]. Additional considerations include the size of devices where ratio accuracy will be obtained for larger size devices.

Table 2.1 Comparison of Current Mirror Structures

| MOS Current Mirror | Accuracy $(i_O = i_I)$ | r <sub>out</sub>        | V <sub>MIN</sub>       |

|--------------------|------------------------|-------------------------|------------------------|

| Simple             | Poor                   | $r_0 = 1/(\lambda i_0)$ | V <sub>DS</sub> (sat)  |

| Cascode            | Good                   | $g_m r_o^2$             | 2V <sub>DS</sub> (sat) |

| Wilson             | Good                   | $g_m r_o^2/2$           | $V_{GS} + V_{DS}(sat)$ |

| Regulated Cascode  | Good                   | $g_m^2 r_o^3$           | V <sub>DS</sub> (sat)  |

## 2.2.2 Current Copiers

The current mirror uses the principle that if the gate-source potential of two identical MOS transistors are equal, the channel currents should be equal. However, the most important limits of conventional current mirror techniques with respect to their use in high-precision analog circuits are the current errors due to mismatch and the low-frequency 1/f flicker noise. Both of these can be reduced by increasing the gate area WL and the saturation voltage V<sub>Dsat</sub>, but this classical approach cannot eliminate flicker noise or reduce the error much below 1% [1].

Unlike bipolar transistors, MOSFETs do not need any gate current to control their drain current. This property has been recently used to build current copiers or dynamic current mirrors that do not require well-matched components [32-34]. The analog storage capability is exploited to sequentially use the same transistor for copying and read-out. Thus, the very notion of mismatch disappears since there is only one transistor. These

current copiers make practically identical copies of a given current without the need for accurately matched components and are implemented as sampled-current circuits [1].

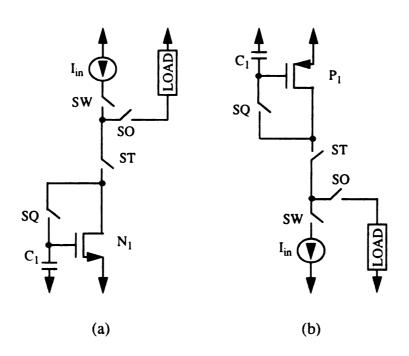

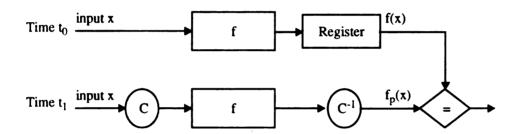

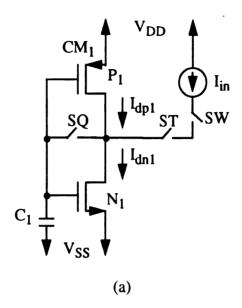

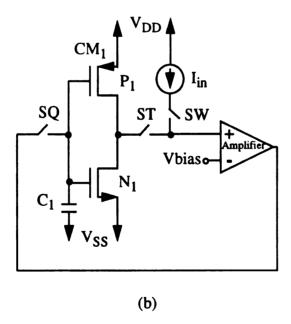

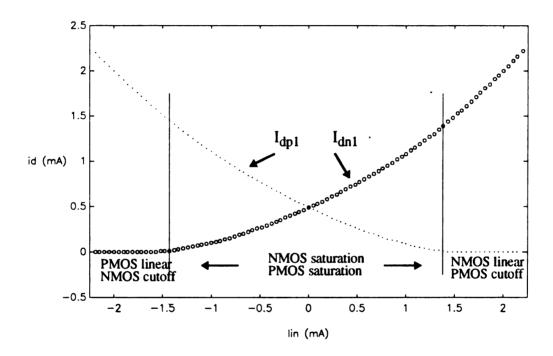

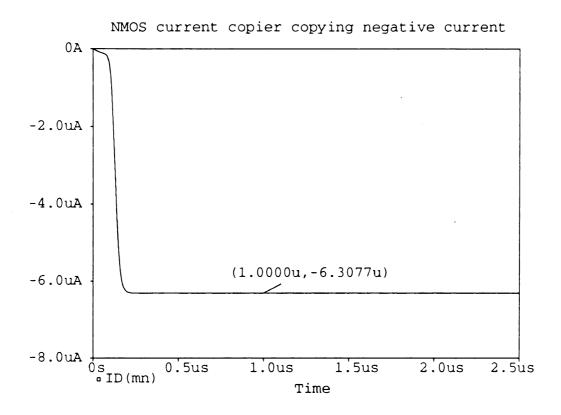

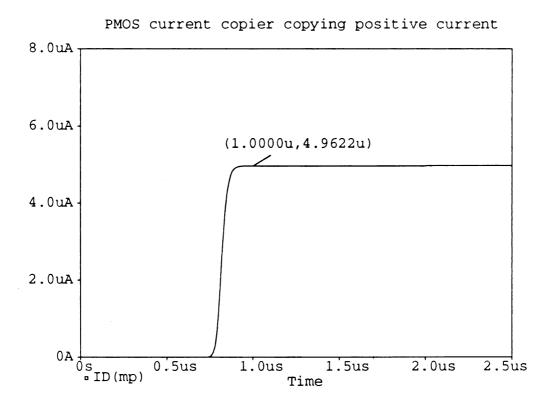

Figure 2.5(a) shows a simple current copier that consists of switches, a non-critical enhancement-mode MOS transistor, and a non-critical capacitor.  $I_{in}$  is copied into the current storage cell by turning on the switches SW, ST and SQ, the capacitor will charge up to the gate voltage needed by the transistor to achieve a drain current equal to  $I_{in}$ . The switches SW and SQ are then turned off to disconnect the cell from the current source; thereafter, the cell is capable of sinking a current  $I_{in}$  when connected to a load. Note that the input current to the NMOS copier cell must be positive. Figure 2.5(b) illustrates a simple PMOS copier which memorizes negative input current.

Many current-mode circuits that utilize dynamic techniques are constructed using current copiers. The error effects of the current copiers will also affect these current-mode circuits. Inevitable circuit non-idealities will cause the current retrieved from a cell to differ from its original copied current. Some of the mechanisms of original-to-copy error include clock feedthrough, leakage and channel length modulation [33,34].

The first important limitation to the precision of the above scheme is *charge* injection or switch charge feedthrough. The various switches are realized by means of transistors. To close the switch, the switching transistor is made conductive by mobile carriers that are attracted into the channel by the gate voltage. When the switch is opened, these carriers are released from the channel in order to block the transistor, and most of them flow to the source or to the drain [32]. Thus, when the switch opens, a fraction  $\Delta q$  of q flows onto the capacitor  $C_1$ , which causes an error  $\Delta V = \frac{\Delta q}{C_1}$  in the stored voltage. This voltage error in turn creates a relative error in the output current equal to  $\frac{\Delta I}{I_0} = \frac{g_m \Delta V}{I_0}$ .

An estimate of the magnitude of this effect for the basic cell of Figure 2.5(a) can be derived as follows. Assume a single n-channel transistor acting as switch SQ. If half of the charge  $Q_{SO}$  on the switch inversion layer is dumped onto  $C_1$ , then

$$\Delta V = \frac{1}{2} \left( \frac{Q_{SQ}}{C_1} \right) = \frac{1}{2} \left( \frac{(WL)_{SQ} C_{ox} (V_{GS} - V_T)_{SQ}}{C_1} \right)$$

(2.9)

Figure 2.5 Simple Current Copier: (a) NMOS Copier; and (b) PMOS Copier

where the assumption that the switch is operated in the linear region and  $N_1$  in the saturation region is taken.  $W_{SQ}$  and  $L_{SQ}$  represent the width and length of switch SQ.  $C_{ox}$  is the gate oxide capacitance per unit area  $(V_{GS}-V_T)_{SQ}$  is the 'on voltage' of the switch and  $\mu$ ,  $W_{N1}$  and  $L_{N1}$  represent the electron mobility, width and length of  $N_1$ , respectively. The resulting relative change in the copier current is

$$\frac{\Delta I}{I_o} = \frac{g_m \Delta V}{I_o} = \left(\frac{\mu C_{ox}^{'}(\frac{W}{L})_{N1}}{2I_o}\right)^{\frac{1}{2}} \left(\frac{(WL)_{SQ} C_{ox}^{'}(V_{GS} - V_T)_{SQ}}{C_1}\right)$$

(2.10)

Simple alternations to the basic current copier cell can help reduce some of the errors. The use of CMOS switches may eliminate the error caused by switch charge feedthrough.  $\Delta V$  can also be decreased by increasing  $C_1$ , with one limit given by the area of the capacitor. It can also be decreased by reducing the total charge q in the channel in order to reduce the fraction  $\Delta q$  that flows onto  $C_1$ . This can be achieved by minimizing the gate area WL and/or by controlling the gate control voltage of the switch in order to adjust its on-conductance to the minimum required value. External gate capacitors can be used to reduce the effects of the charge injection from switches and to allow the transistor and capacitor geometries to be determined independently.

The various approaches to reduce the effect of charge injection on the precision of the dynamic mirror may be combined. It may be pointed out that most of them tend to increase the time needed to achieve equilibrium in the circuit and therefore decrease the maximum frequency of switching. Since the input current is sampled, the bandwidth of the mirror is in turn reduced. Thus, there exists a trade-off between speed and precision.

Another contribution to the error is due to channel length modulation which is represented by the drain-to-source conductance  $g_{ds}$ . As shown in Figure 2.5(a), the drain of  $N_1$  is connected to its gate during the storage phase, thus the two nodes are at the same voltage potential. During the read-out phase, the drain potential will be different and be equal to a value imposed by the load of the mirror. This difference in drain voltage during the two phases produces important additional contributions to the inaccuracy of the mirror.

Because of the change in the effective channel length as  $V_{DS}$  of  $N_1$  changes, the basic current copying circuit of Figure 2.5(a) will supply a slightly different current during retrieval.

These considerations show that an accurate implementation must include some means to keep the drain voltage of N<sub>1</sub> as constant as possible in spite of the difference. An operational amplifier could be used for this purpose, in which case the circuit becomes an active current copier shown in Figure 2.6. Another solution which is more compact is obtained by adding a common gate transistor in series with the main transistor to build a cascode structure, a technique commonly used in current mirrors.

Junction leakage is another error effect to be considered. Even with the switch SQ turned off, a small current will flow through the reversed biased source-substrate junction, drawing charge from  $C_1$ . Over a time interval  $\Delta t$  this leakage current I leak will create a change in voltage  $\Delta V = I_{leak} \frac{\Delta t}{C_1}$  across  $C_1$  with a resulting change in current  $\Delta I = g_m \Delta V$ . However, as is also true for switched capacitor circuits, with usual junction leakage currents and reasonable clock rates, this does not create a severe constraint on circuit operation.

Since both the transconductance element and the switches consist of MOS transistors, the copier inherently contains both thermal and 1/f internal noise sources. As with other sampled data circuits, the resulting output noise current can be separated into two types. Sampled noise, occurring during the period when the current is sampled, resulting in an error in the voltage held across the capacitor C<sub>1</sub> and nonsampled or direct noise, occurring when the copier is sinking current from a load.

Junction leakage and noise can be limited by a careful choice of switch dimensions, capacitor sizes, and loop bandwidth. Note that larger capacitors may reduce the effects of the thermal noises and charge injection from the switches, thus increasing the resolution. However, larger capacitors result in slower settling time. This leads to a significant area/resolution/speed trade-off.

Figure 2.6 Active NMOS Copier

# 2.2.3 Dynamic Current-mode Signal Processing Circuits

Several circuits that use dynamic current-mode techniques are reviewed in this section. These circuits form an essential part of current-mode data converters and utilize current copiers.

### 2.2.3.1 Current-mode Multiplier

One obvious application of current copiers is the integer current multiplier where if the input current  $I_{in}$  is constant, then an output current equal to an integer multiple of  $I_{in}$  can be obtained. Figure 2.7 shows a current-mode multiply-by-two circuit which achieves accurate signal multiplication without the need for well-matched components [9].

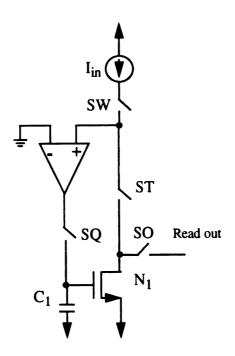

Initially, switches  $S_1$ ,  $S_2$  and  $S_3$  are turned on. After the amplifier has settled,  $I_1$  will equal  $I_{in}$ . When switch  $S_3$  is turned off, the gate capacitance will cause transistor  $N_1$  to "memorize" the current level. The procedure is then repeated for transistor  $N_2$  by turning on  $S_1$ ,  $S_4$  and  $S_5$ . Once  $N_2$  has been "programmed", an output current of  $2I_{in}$  is produced by turning on  $S_2$ ,  $S_4$  and  $S_6$  and providing an appropriate  $V_{out}$  such that  $I_{out}$  is equal to  $(I_1+I_2)$  or  $2I_{in}$ . Ideally, the sum of the outputs of the cells is therefore an integer multiple of  $I_{in}$  achieved without relying on element matching.

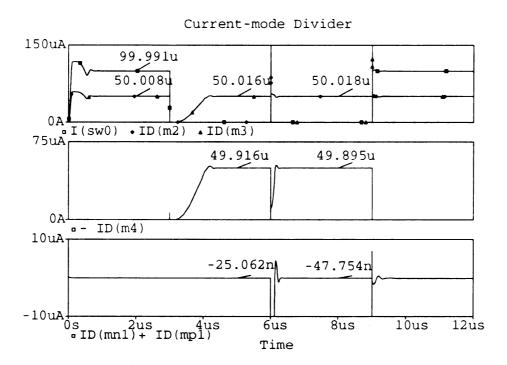

### 2.2.3.2 Current-mode Divider

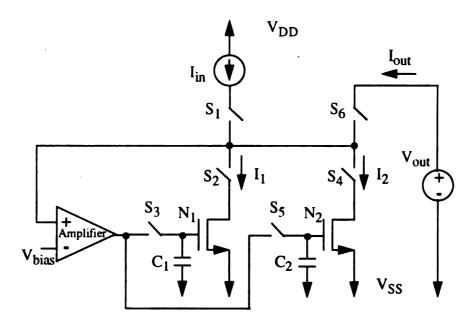

Current dividers are usually implemented by using resistor networks or weighted transistors. The division accuracy of such solutions is limited by device mismatch. An algorithmic method for dividing a given current  $I_{in}$  by an integer factor without depending on device matching or even linearity is depicted in Figure 2.8, for the specific case of division by a factor of 2. The circuit does not require laser trimming, external adjustment, or matched components [35].

Figure 2.7 Current-mode Multiplier

Figure 2.8 A Highly Accurate Current Divider: (a) Schematic Diagram; and (b) Switching Sequence

The basic operation of the current divider is described as follows. (For simplicity of the discussion,  $I_i$ , i=1, 2, or 3, is the memorized current in transistor  $N_i$  and  $I_4$  is the current held in P<sub>4</sub>.) First, the current difference  $(I_{in}-I_1)$  is fed to both transistors N<sub>2</sub> and N<sub>3</sub> by turning on switches S<sub>0</sub>, S<sub>1</sub>, S<sub>3</sub>, S<sub>4</sub>, S<sub>5</sub>, and S<sub>6</sub>, and turning off the others. The currents copied into N<sub>2</sub> and N<sub>3</sub> are determined by the mismatch between them. In order to obtain the difference in their currents, N<sub>3</sub> sources its copied current to P<sub>4</sub>, during the second cycle, by turning on S<sub>7</sub>, S<sub>8</sub>, and S<sub>5</sub>, and turning off the others. Once the current held in P<sub>4</sub> is set, turning on S<sub>3</sub>, S<sub>7</sub>, S<sub>1</sub>, and S<sub>2</sub>, and turning off the others, during the third cycle, will copy the current difference  $(I_4-I_2)$  into  $N_1$ , i.e.,  $I_1=I_4-I_2$ . Thus,  $N_1$  holds the current difference between  $I_2$  and  $I_3$ . This completes an iteration of the division process and thus each iteration takes three clock cycles. During the next iteration, this current difference is removed from  $I_{in}$  and is sourced to  $N_2$  and  $N_3$ . Therefore, through subsequent iterations, the error reduces to a minimal value and the current in  $N_3$  converges to  $I_{in}/2$ . Note that, in order to zero the current remaining in  $N_1$ , only the input current  $I_{in}$  is copied into  $N_2$  and  $N_3$  during the first iteration. The number of iterations necessary to obtain half of the current with certain accuracy depends on the mismatch in N<sub>2</sub> and N<sub>3</sub>. Figure 2.8(b) illustrates the switching sequence of the divider circuit. Let  $\alpha_2$  and  $\alpha_3$  be the mismatch factors of the transistors  $N_2$ and N<sub>3</sub>, respectively, then  $I_2=\alpha_2I_{in}$ ,  $I_3=\alpha_3I_{in}$ , where

$$\alpha_2 = \frac{k_2 (V_{GS} - V_{T2})^2}{k_2 (V_{GS} - V_{T2})^2 + k_3 (V_{GS} - V_{T3})^2}$$

(2.11)

$$\alpha_3 = \frac{k_3 (V_{GS} - V_{T3})^2}{k_2 (V_{GS} - V_{T2})^2 + k_3 (V_{GS} - V_{T3})^2}$$

(2.12)

Note that  $V_{T2}$  and  $V_{T3}$  are the threshold voltages of the transistors  $N_2$  and  $N_3$ , respectively, and the device transconductance  $k_i = k'_i (\frac{W}{L})_i$  where  $(W/L)_i$ , i=1 or 2, is the aspect ratio of the transistor  $N_i$ . Since the sensitivity of  $\alpha_2$  and  $\alpha_3$  to  $V_{GS}$  is small, the values of  $\alpha_2$  and  $\alpha_3$  are considered constant [35].

### 2.2.3.3 Current-mode A/D Converter

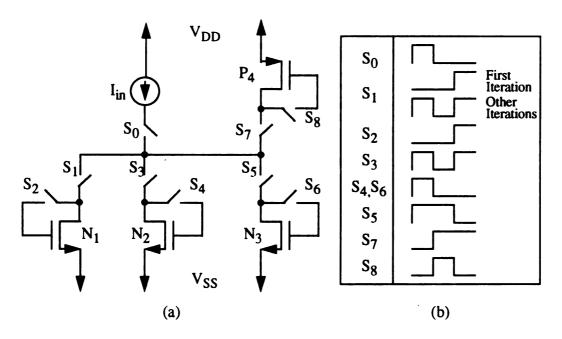

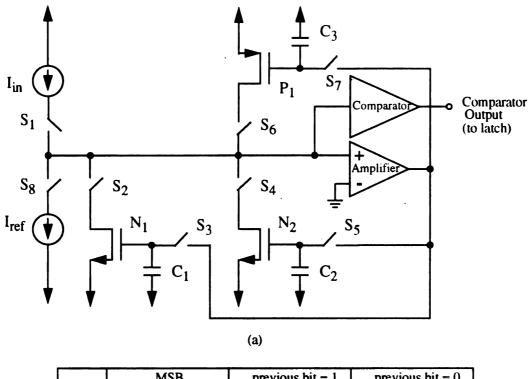

As discussed in (2.2), algorithmic (cyclic) current-mode A/D converters convert an input current to an N-bit digital data word D using a multiply-by-two scheme. The accuracy of these converters is often limited by the mismatching of passive components of the circuits. An algorithmic A/D converter that combines current-mode and dynamic techniques achieves high resolution without the need for high gain amplifiers or well-matched components [13]. The converter, shown in Figure 2.9, starts converting for the most significant bit (MSB) of an input current  $I_{in}$  by turning on switches  $S_1$ ,  $S_2$ , and  $S_3$  to cause the current in  $N_1$  to be set to  $I_{in}$ . Once  $N_1$  is set,  $S_2$  and  $S_3$  are switched off while  $S_4$  and  $S_5$  are on to set  $N_2$  to be  $I_{in}$ . Once the input signal has been stored on  $N_1$  and  $N_2$ , twice the input signal is loaded into  $P_1$  by turning off  $S_1$  and  $S_5$  while switching on  $S_2$ ,  $S_6$ , and  $S_7$ . After  $P_1$  is set,  $S_2$ ,  $S_4$ , and  $S_7$  are turned off while  $S_8$  is turned on, thus allowing the comparator to sense the current imbalance, and hence, determine if the signal,  $2I_{in}$ , is greater than  $I_{ref}$ . If the signal exceeds the reference, the MSB will be a "1" otherwise it will be a "0." This completes the conversion for the MSB.

# 2.3 Fault-tolerant and Testable Circuit Design

During the last few years the theory and practice of testing electronic products have changed considerably. The continuing revolution in electronic circuitry in terms of size and speed has increased the problems of testing. The philosophy of testing has evolved from merely measuring electrical parameters at many points in the device under test to integrating testing in every step of the device design and development. A whole field of testing has emerged. The following section presents a brief introduction to some important testing concepts.

Figure 2.9 Current-mode A/D Converter: (a) Schematic Diagram; and (b) Switching Sequence

### 2.3.1 Fault Tolerance

There are two fundamentally different approaches that can be taken to increase the reliability of computing systems [36]. The first approach is called *fault prevention* (also known as fault intolerance) and the second *fault tolerance*. In the traditional fault prevention approach the objective is to increase the reliability by a priori elimination of all faults. Since this is almost impossible to achieve in practice, the goal of fault prevention is to reduce the probability of system failure to an acceptably low value. Fault tolerance is an attribute that is designed into a system to achieve some design goal. A design must meet many functional and performance goals, it must satisfy numerous other requirements as well. The most prominent of the additional requirements are reliability, availability, safety, performability, dependability, maintainability, and testability. Fault tolerance is one system attribute capable of fulfilling such requirements. Fault tolerance is not a replacement but rather a supplement to the most important principles of reliable system design: (a) use the most reliable components; and (b) keep the system as simple as possible, consistent with achieving the design objectives.

Three fundamental terms in fault-tolerant design are fault, error, and failure [20]. There is a cause-and-effect relationship between faults, errors, and failures. Specifically, faults are the cause of error, and errors are the cause of failures. A fault is a physical defect, imperfection, or flaw that occurs within some hardware or software component. An error is the manifestation of a fault, and it is a deviation from accuracy or correctness. Finally, if the error results in the system performing one of its functions incorrectly, a system failure has occurred. Essentially, a failure or malfunction is the non-performance of some action that is due or expected.

Fault duration specifies the length of time for which a fault is active. A permanent fault remains in existence indefinitely if no corrective action is taken, while a temporary fault occurs for short period of time. Temporary faults have been referred to as "intermittent" or "transient" faults with the same meaning. Transient faults are non-recurring temporary faults. Intermittent faults are recurring faults that reappear on a

regular basis. A major portion of digital system malfunctions are caused by temporary faults. Such faults can occur due to loose connections, partially defective components or poor designs.

In the fault tolerance approach, faults are expected to occur during computation, but their effects are automatically counteracted by incorporating redundancy, i.e. additional facilities, into a system, so that valid computation can continue even in the presence of faults. They are redundant in the sense that they could be omitted from a fault -free system without affecting its operation. Redundancy is achieved simply by the addition of information, resources, or time beyond what is needed for normal system operation [20]. The redundancy can take one of several forms: hardware redundancy, software redundancy, information redundancy and time redundancy. Note that time redundancy uses additional time to perform the functions of a system such that fault detection and often fault tolerance can be achieved.

### 2.3.2 Testability Techniques

The testing of an integrated circuit is extremely vital to the ultimate goal of achieving high reliability, availability, safety, maintainability, fault tolerance or other design requirements [20]. Integrated systems, even when designed with highly reliable components, do not operate forever without developing some faults. When a system ultimately does develop a fault it has to be detected and located so that its effect can be removed. Fault detection means the discovery of something erroneous in a system or circuit. Fault location means the identification of the faults with components, functional modules or subsystems, depending on the requirements. Fault diagnosis includes both fault detection and fault location.

Fault detection in a logic circuit is carried out by applying a sequence of test inputs and observing the resulting outputs. Therefore, the cost of testing includes the generation of test sequences and their application. The test generation process includes fault modeling, test pattern generation, fault simulation and fault coverage evaluation. The first

step consists of developing a fault dictionary for the circuit, i.e. modeling the faults that are assumed. Next, test vectors and/or test patterns are generated to test for the set of faults being considered. One of the main objectives in testing is to minimize the length of the test sequence. The test patterns are then simulated against the faulted circuit, and the fault coverage is evaluated. If the fault coverage is inadequate, the process of test pattern generation and fault simulation is repeated. To be practical and cost effective for large scale integrated circuits, the test generation process should be automated. A test is a means by which the existence and quality of certain attributes within a system are determined.

The testing process attempts to determine if the *unit under test* (UUT) works and if it possesses its complete capability [20]. There are two key concepts in having a testable design: controllability and observability. Controllability refers to the ability to apply test patterns to the inputs of a sub-circuit via the primary inputs of the circuit. Observability refers to the ability to observe the response of a sub-circuit via the primary outputs of the circuit or at some other output point. In general, the easiest way to increase controllability/ observability is to add some control gates and control terminals (controllability) or to add some output terminals (observability) for testing purposes.

#### Fault Model

Fault modeling is very important in developing cost effective test strategies for electronic circuits. In general the effect of a fault is represented by means of a model, which represents the change the fault produces in circuit signals. The selection of adequate fault models is crucial to achieving high quality testing because the efficiency of a test scheme is limited by the accuracy of the chosen fault model. If the model fails to capture the important characteristics of the actual fault, the test based on this model will fail to detect the actual fault [36].

The fault models in use today are Stuck-at faults, Bridging faults and Stuck-open faults. The most common model used for logical faults is the "single-stuck-at fault". It assumes that a fault in a logic gate results in one of its inputs or the output being fixed to either a logic 0 (Stuck-at-0) or a logic 1 (stuck-at-1). Stuck-at-0 and stuck-at-1 faults are

often abbreviated to s-a-0 and s-a-1, respectively. The stuck-at fault model, often referred to as the "classical" fault model, offers good representation for the most common types of failures, e.g. short-circuits ("shorts") and open-circuits ("open") in many technologies.

For circuits containing switching elements, the logical stuck-at model is appropriate, effective and simple to work with. This model is based on the assumption that the basic functionality of the circuit is not affected by the fault. This implies that the circuit continues to behave as expected of it given the existence of the fault.

There exist various testing techniques that can be used to achieve this goal. In general testing techniques use two major approaches: built-in test and external test [20]. External test techniques are typically performed with the UUT removed from its operating environment and various tests applied to it using external equipment. Built-in test techniques usually incorporate testing as part of the design of the device; thus no external testing equipment is needed.

### **Built-In Test**

As digital circuits grow more complex and difficult to test, it becomes increasingly attractive to build some self-testing ability into the circuits under test. Built-in test may be conveniently used to detect and isolate a faulty component in a circuit and thus facilitate its replacement. An important added feature of properly designed built-in test is the ability to simplify off-line testing by taking advantage of the increased controllability and observability made possible by the incorporation of the self-testing capability.

The built-in test strategy can be used to enhance testability of VLSI chips. It is based on the following principles: (1) Test patterns are generated on-chip; (2) Responses to the test patterns are also evaluated on-chip; (3) External operations are required only to initialize the built-in tests and to check the go/no-go tests results from a chip; and (4) Additional pins and silicon area are kept to a minimum.

As the internal complexity of the integrated circuit chip increases, the idea of builtin test becomes more and more attractive as it has many advantages: (1) Test patterns are generated automatically inside chips; (2) Responses to test patterns need not be stored; and (3) Use of expensive test equipment is not necessary. Built-in techniques can follow either a concurrent (on-line) or a nonconcurrent (off-line) approach. Nonconcurrent test techniques require that the operation of the UUT be halted before beginning the test. Concurrent test techniques allow a device to be tested while in normal operating mode. The off-line test techniques suffer from the disadvantage of not being able to detect temporary faults, which are likely to be more important in VLSI systems.

### **Concurrent Error Detection (CED)**

Although reliability of circuits may be improved by using sophisticated testing schemes to weed out faulty components, off-line or static tests cannot identify the transient faults that occur during on-line operation. Therefore, a mechanism for concurrent error detection must be installed to detect such faults before they cause undesirable results [22]. All CED schemes detect errors through conflicting results generated from operations on the same operands. CED can be achieved through space or time redundancy, or space/time hybrid redundancy. Time redundancy employs only one single set of hardware to carry out the repeated operations and can be effectively used in the detection and correction or errors caused by temporary faults. Since the same hardware is used, the repeated operation, in the presence of faults, is liable to produce the same erroneous result as that of the first step. To avoid this problem, the operand must be coded in the repeated cycle, and the result thus obtained must be decoded back to the appropriate form for meaningful comparison.

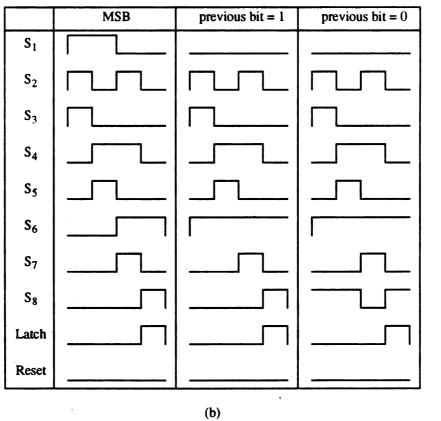

Consider a time redundancy technique shown in Figure 2.10 [21,22]. Let x be the input of the computation unit f, and let  $f_p(x)$  and f(x) be the outputs with and without encoding-decoding operations, respectively. Two fundamental requirements must be satisfied in these operations. First, the coding function c must not interfere with the original function f. In other words, for a selected coding function c, there must exist a decoding function  $c^{-1}$  such that  $f_p(x) = c^{-1}(f(c(x))) = f(x)$  in the absence of faults. This is the concept of mappable correct output [37]. Secondly, for the purpose of fault detection, the coding operation c must transform the input operand(s) x in such a way that when subjected to the same faulty conditions, the output in the repeated step, though still erroneous will be

Figure 2.10 The Concept of Time Redundancy

different from the first step. This is the concept of disjoint error sets. Two simple time redundancy techniques have been reported: RESO (REcomputing with Shifted Operands) [21,37] and AL (Alternating Logic) [22,38]. Among existing CED techniques, both RESO and AL have unique features of transient fault detection and require only a moderate increase in hardware. AL implementation uses the complementation operator as the encoding function while RESO uses the arithmetic shift.

The "alternating logic design" technique achieves its fault detection capability by utilizing a redundancy in time based on the successive execution of a required function and its self-dual [22]. A function for which the normal output is the complement of the output, when complemented inputs are applied, is known as a self-dual function, e.g. a function f(x), where  $x=(x_1, x_2, ....., x_n)$ , is a self-dual if for all x,  $f(\overline{x_1}, \overline{x_2}, ....., \overline{x_n}) = \overline{f}(x_1, x_2, ....., x_n)$ . Thus, the principal characteristic of alternating logic is that it provides a true output in one time period and the complementary output in the next time period. The main disadvantage of the technique is that it requires twice as much time to obtain the verified output.

# **Chapter 3**

# Current-mode Data-acquisition and Data-conversion Circuits

All too often the electronics engineer will think in voltage terms rather than current simply due to the unavailability of current-mode signal processing circuits, thus not taking advantage of the many gains of current-mode techniques [3]. The goal is thus to develop, analyze and construct current-mode data-acquisition and conversion circuits in MOS technology for signal processing and to explore the limits of their applications.

This chapter presents several current-mode circuits and their design and operation. Section 3.1 describes the bipolar current copier, which is a fundamental building block for several current-mode signal processing circuits. A data-acquisition system in the form of a current-mode shift register is discussed in Section 3.2. In Section 3.3 a current-mode divider is described that will form an integral part of a current-mode A/D converter as its reference-generating unit. And, finally, Section 3.4 presents a successive-approximation A/D converter that operates in the current domain.

# 3.1 Bipolar Current Copier

A simple NMOS current copier, consisting of three non-critical components: a switch, an enhancement-mode NMOS transistor, and a capacitor, is generally used to copy a positive current into its cell [39]. It has also been implemented to memorize the current difference  $I_3=I_1-I_2$ , where the current difference  $I_3$  must be positive, i.e.,  $I_1$  is greater than