This is to certify that the

dissertation entitled

Design and Synthesis of On-Line Testable Sequential Circuits

presented by

Chia-Shun Lai

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Electrical Engineering

Major professor

Date 4-30-93

# LIBRARY Michigan State University

PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due.

| DATE DUE | DATE DUE | DATE DUE |

|----------|----------|----------|

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

MSU Is An Affirmative Action/Equal Opportunity Institution c:\circ\dentatue.pm3-p.1

# DESIGN AND SYNTHESIS OF ON-LINE TESTABLE SEQUENTIAL CIRCUITS

By

Chia-Shun Lai

## **A DISSERTATION**

submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

**DOCTOR OF PHILOSOPHY**

**Department of Electrical Engineering**

## **ABSTRACT**

# DESIGN AND SYNTHESIS OF ON-LINE TESTABLE SEQUENTIAL CIRCUITS

By

#### Chia-Shun Lai

With ever-increasing complexity of digital applications, the issue of reliability has become very important in today's VLSI designs. Concurrent error detection schemes using redundancy design approaches have been successfully implemented to enhance chip yield and system reliability. Redundancy design approaches may include hardware redundancy, time redundancy, and information redundancy. The simplest concurrent error detection scheme is the duplication with comparison. Any mismatch between two identical blocks will indicate an error. However, this involves more than a 100% increase in hardware overhead cost.

Information redundancy involves the use of coding techniques that enhance circuit capability for reliable operation. Berger codes are least redundant separable codes, they have been implemented for fault-tolerant, fail-safe, and concurrent error testable digital circuits. The features of high speed and low hardware cost are highly desirable especially for a checker design. In response to these needs, a design methodology using a partitioning and folding scheme is developed for the design of fast, yet low hardware cost, Berger code checkers with self-testing capability.

che tha

is o

des Ex

ma

bec

seq is i

des

layo

Since the hardware cost is increased almost exponentially as the code length of the checker increases, the use of many smaller checkers will require much less hardware cost than that of a larger checker. In this study, an efficient output function partitioning scheme is developed to partition the set of output functions into many smaller subsets so that smaller checkers can be employed. Based on the delay constraint derived from a set of design specification, the checkers which achieve minimal hardware overhead are chosen. Experimental results show that, with the developed partitioning scheme, the hardware cost may be reduced considerably. With such a low hardware cost checker, on-line testability becomes very promising and practical.

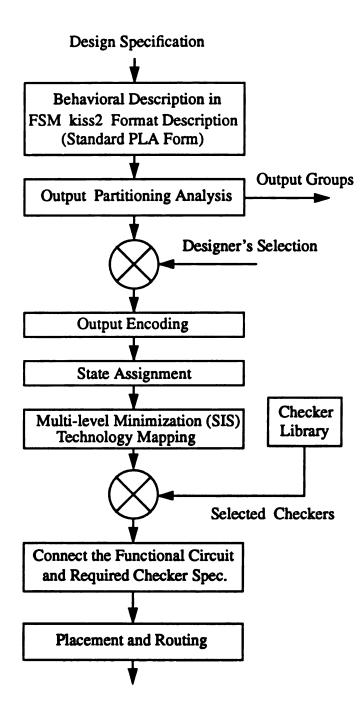

In this research, a system, *SOLiT*, for automated synthesis of on-line testable sequential circuits with multi-level logic implementation has been developed. The system is implemented on Sun/4 workstation in the C-language. The system receives a behavioral description of finite state machines in *kiss2* format and automatically generates the physical layout for a self-checking circuit.

Capyrig 2111-51 1993 Copyright by Chia-Shun Lai 1993 To my wife: Kai-Ling Hsu

,

li M

> id Er

nic

CO:

hel insp

enco

thing

canc

and e

# **ACKNOWLEDGEMENTS**

I would like to thank Professor Chin-Long Wey, my thesis advisor, for his leading me not in the path of ease and comfort but under the stress and spur of difficulties and challenge. I am inspired by his valuable guidance throughout my graduate study. I would like to thank members of my thesis committee, Professors P. David Fisher, Michael Shanblatt, and Jonathan I. Hall, for their meaningful comments and remarkable ideas during the course of my dissertation research. I do very appreciate Professor Erik D. Goodman for his encouragement, support, and assistance. My learning life is richer for having crossed his. I would also like to thank Professor Kun-Mu Chen for his cordial assistance. I am benefited from his provident thinking and effective attitude.

I would like to acknowledge all the faculty member and students who gave me help during my study at Michigan State University, and many friends who showed their inspiration and benevolent feeling.

I am very grateful to my parents and my mother-in-law for their years of concern, encouragement, and support, and to my wife, Kai-Ling, for her wild imagining, significant encouragement and help, and persistent thoughtfulness. She insists in taking care of all things considerately, and keeps learning diligently even though under treatment for her cancer. My latent potentialities have encouraged by her great composure, persevering will, and endless love.

# TABLE OF CONTENTS

| LIST OF TA       | ABLES                                                 | ix  |

|------------------|-------------------------------------------------------|-----|

| LIST OF FIGURES  |                                                       | x   |

| LIST OF SYMBOLSx |                                                       | xii |

| Chapter 1:       | Introduction                                          | 1   |

| 1.1              | Previous Work                                         | 2   |

| 1.2              | Problem Statement                                     | 4   |

| 1.3              | Research Tasks                                        | 5   |

| 1.4              | Thesis Organization                                   | 5   |

| Chapter 2:       | On-line Self-Testable Circuit and System              | 7   |

| 2.1              | Terminology                                           | 7   |

| 2.2              | Self-Testing Circuit Structures                       | 11  |

|                  | 2.2.1 Checker Design                                  | 11  |

|                  | 2.2.2 Functional Circuits                             | 23  |

|                  | 2.2.3 Logic Synthesis Procedure                       | 26  |

| Chapter 3:       | Efficient Self-Testing Berger Code Checker Design     | 29  |

| 3.1              | Maximal Length Berger (MLB) Code Checker Design       | 29  |

|                  | 3.1.1 Berger Code Partitioning Scheme                 | 30  |

|                  | 3.1.2 Partitioning and Folding Scheme                 | 33  |

| 3.2              | Non-Maximal Length Berger Code (NMLB) Checker Design  | 47  |

|                  | 3.2.1 STC Design with Partitioning Scheme             | 47  |

|                  | 3.2.2 STC Design with Partitioning and Folding Scheme | 53  |

| 3.3         | Design Alternative                                 | 62         |

|-------------|----------------------------------------------------|------------|

| 3.4         | Summary                                            | 68         |

| Chapter 4:  | Output Partitioning Algorithm                      | <b>7</b> 0 |

| 4.1         | Problem Statement                                  | 70         |

| 4.2         | Problem Formulation                                | 72         |

| 4.3         | Algorithms                                         | 75         |

| 4.4         | Discussion                                         | 79         |

| 4.5         | Experimental Results                               | 81         |

| 4.6         | Summary                                            | 87         |

| Chapter 5:  | SOLiT: A System for Automated Synthesis of On-Line |            |

|             | Testable Sequential Circuits                       | 89         |

| 5.1         | Synthesis of Self-Checking Functional Circuits     | 90         |

| 5.2         | The Automated Synthesis System SOLiT               | 91         |

| 5.3         | Implementation                                     | 93         |

| 5.4         | Synthesis Example                                  | 95         |

| Chapter 6:  | Summary and Conclusion                             | 107        |

| 6.1         | Summary                                            | 107        |

| 6.2         | Contribution and Future Research                   | 109        |

| Bibliograph | y                                                  | 111        |

I

Ta

Ta Ta

Ta

Tal

Tat

Tab

Tab

Tabi

# LIST OF TABLES

| Table 2.1 | Berger Code B(7,3).                                   | 21 |

|-----------|-------------------------------------------------------|----|

| Table 3.1 | Subsets of B(7,3)                                     | 34 |

| Table 3.2 | B(7,3) with Partitioning Scheme.                      | 36 |

| Table 3.3 | Logic Expressions for Checker in B(7,3).              | 40 |

| Table 3.4 | Berger Code B(6,3).                                   | 45 |

| Table 3.5 | Left-justified Encoding Scheme.                       | 48 |

| Table 3.6 | Berger Code B(11,4)                                   | 54 |

| Table 3.7 | Berger Code Encoding Scheme for B(11,4).              | 55 |

| Table 3.8 | Reduced Check Part for B(31,5).                       | 67 |

| Table 3.9 | Comparisons for Various Checker Designs.              | 69 |

| Table 4.1 | Experimental Results.                                 | 82 |

| Table 4.2 | Experimental Results with Output Partitioning Scheme. | 84 |

| Table 4.3 | Comparisons.                                          | 86 |

Fig Figi Fig Figi Fig Fig

Fig

Fig Fig

Fig Fig

## **LIST OF FIGURES**

| Figure 1.1  | A self-checking circuit.                                                  | 3  |

|-------------|---------------------------------------------------------------------------|----|

| Figure 2.1  | Self-testing and fault-secure circuits.                                   | 8  |

| Figure 2.2  | Totally self-checking circuit.                                            | 9  |

| Figure 2.3  | Typical structure of STC for normal Berger code checker                   | 12 |

| Figure 2.4  | General self-testing checker for m/n checker with $n \neq 2m$             | 14 |

| Figure 2.5  | Test patterns for m/n checker.                                            | 14 |

| Figure 2.6  | Disjoint 2-level realization for C <sub>3/5</sub> .                       | 16 |

| Figure 2.7  | 3-level realization for C <sub>3/5</sub> .                                | 16 |

| Figure 2.8  | m/n code checker.                                                         | 17 |

| Figure 2.9  | 1/n code checker.                                                         | 18 |

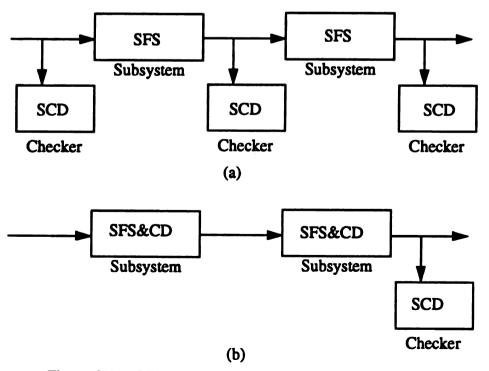

| Figure 2.10 | TSC systems: (a) with TSC subsystems; and (b) with TSC and CD subsystems. | 24 |

| Figure 2.11 | SFS systems: (a) with SFS subsystems; and (b) with SFS and CD subsystems. | 24 |

| Figure 2.12 | A sequential circuit (Moore type).                                        | 26 |

| Figure 2.13 | A logic synthesis example.                                                | 27 |

| Figure 3.1  | Internal structure of a STC design of MLB code B(I,K) (Circuit CH).       | 30 |

| Figure 3.2  | Circuit CS for B(I,K) STC design.                                         | 38 |

| Figure 3.3  | Circuit CH for B(7,3) STC design [30].                                    | 39 |

| Figure 3.4  | Circuit CS for B(7,3) STC design.                                         | 42 |

| Figure 3.5  | STC for modified Berger code with I=2 <sup>K-1</sup> .                    | 46 |

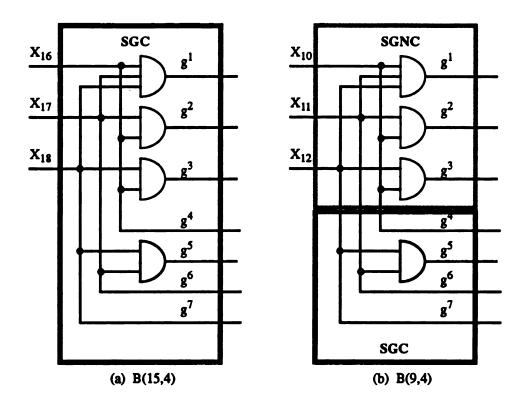

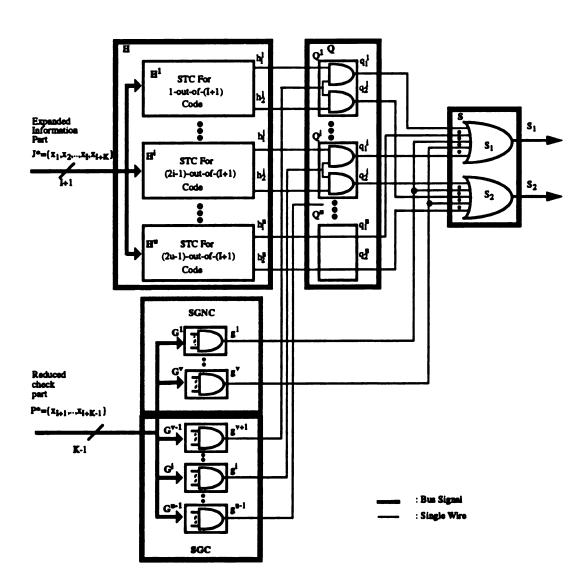

| Figure 3.6  | Function G for B(15,4) and B(9,4) STC designs.                            | 49 |

| Figure 3.7  | Circuit CW for B(I,K) STC design.                                                                        | 50  |

|-------------|----------------------------------------------------------------------------------------------------------|-----|

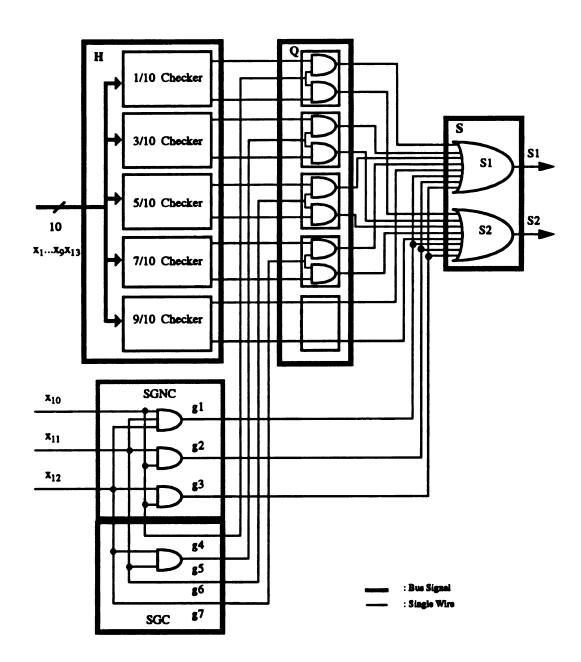

| Figure 3.8  | Circuit CW for B(9,4) STC design.                                                                        | 51  |

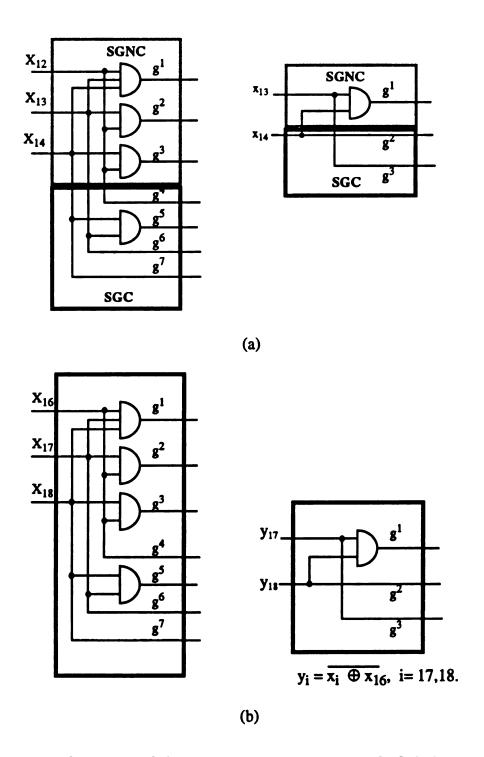

| Figure 3.9  | Function G for (a) B(11,4); and (b) B(15,4) STC design                                                   | 56  |

| Figure 3.10 | Circuit CL for B(I,K) STC design with even u.                                                            | 57  |

| Figure 3.11 | Circuit CL for B(11,4) STC design.                                                                       | 59  |

| Figure 3.12 | Circuit CL for B(I,K) STC design with odd u.                                                             | 61  |

| Figure 3.13 | Circuit CL for B(9,4) STC design.                                                                        | 63  |

| Figure 3.14 | Circuit CS with XOR code complementer.                                                                   | 65  |

| Figure 4.1  | A FSM, ex4.kiss2.                                                                                        | 74  |

| Figure 4.2  | The output matrix and R <sub>j</sub> -sets for ex1.kiss2.                                                | 77  |

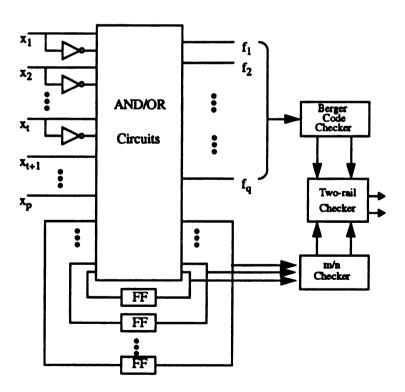

| Figure 5.1  | A Moore-type self-checking sequential circuit.                                                           | 90  |

| Figure 5.2  | Flow chart for SOLiT.                                                                                    | 92  |

| Figure 5.3  | Cell-level implementation of 2/7 code checker.                                                           | 95  |

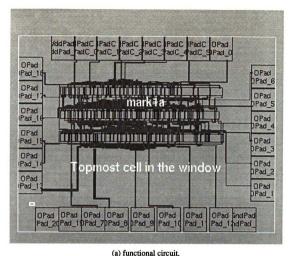

| Figure 5.4  | A FSM example - mark1.kiss2.                                                                             | 96  |

| Figure 5.5  | Output of Procedure out_part.                                                                            | 98  |

| Figure 5.6  | Input file to Procedure out_encode.                                                                      | 98  |

| Figure 5.7  | Encoded output functions.                                                                                | 99  |

| Figure 5.8  | Resultant state encoding with assigner.                                                                  | 100 |

| Figure 5.9  | Resultant optimized network.                                                                             | 101 |

| Figure 5.10 | Netlist generated by sis technology mapper.                                                              | 103 |

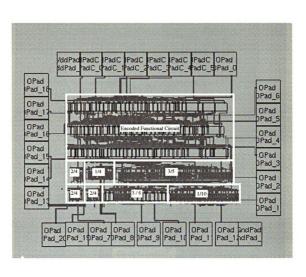

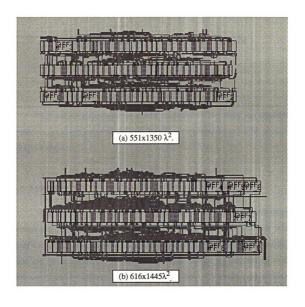

| Figure 5.11 | Physical layouts.                                                                                        | 104 |

| Figure 5.12 | Layout of an on-line testable sequential circuit, mark1.kiss2.                                           | 105 |

| Figure 5.13 | Layout of mark1.kiss2 with (a) the conventional synthesis procedure; and (b) encoded functional circuit. | 106 |

# **LIST OF SYMBOLS**

| symbol                                            | meaning                                                                            |

|---------------------------------------------------|------------------------------------------------------------------------------------|

| Ø                                                 | empty, or null set                                                                 |

| x ∈ A                                             | element x is a member of set A                                                     |

| x ∉ A                                             | element x is not a member of set A                                                 |

| $\exists x \in A$                                 | there exists an element x in set A                                                 |

| $\forall x \in A$                                 | for every element x in set A                                                       |

| $A \cup B$                                        | union of sets A and B; $A \cup B = \{x \mid x \in A \text{ or } x \in B\}$         |

| $A \cap B$                                        | intersection of sets A and B; $A \cap B = \{x \mid x \in A \text{ and } x \in B\}$ |

| $\bigcup_{j=1}^{n} Q_{j}$                         | union of sets $Q_1, Q_2,,$ and $Q_n$                                               |

| $\bigcap_{j=1}^n Q_j$                             | intersection of sets $Q_1$ , $Q_2$ ,, and $Q_n$                                    |

| A - B                                             | difference of sets A and B, $A - B = \{x \mid x \in A \text{ and } x \notin B\}$   |

| IRI                                               | cardinality of set R, the number of elements in set R                              |

| $f: A \rightarrow B$                              | f is a function mapping from A to B                                                |

| {x   x is}                                        | set builder notation                                                               |

| {1,2,}                                            | elements in a set                                                                  |

| $i \in I_v$                                       | index set i = 1, 2,, v                                                             |

| <f<sub>1,f<sub>2</sub>,,f<sub>n</sub>&gt;</f<sub> | ordered sequence containing $f_1, f_2,,$ and $f_n$                                 |

| Σ                                                 | logic OR operation                                                                 |

| <b>⊕</b>                                          | logic exclusive OR operation                                                       |

A bitwise complement of a binary vector A

SXT concatenation of two code, S and T

(010...) code vector

$\binom{n}{m}$  combinations of m out of n;  $\binom{n}{m} = \frac{n!}{(n-m)!m!}$

m/n m-out-of-n

C<sub>m/n</sub> m-out-of-n code

B(I, K) Berger code with I information bits and K check bits

[x] floor function of x; the greatest integer less than or equal to the real

number x

[y] ceiling function of x; the smallest integer greater than or equal to

the real number y

hav

sop sta

me bef

ger

The che

sys tha

uр

sel

ma

## CHAPTER 1

## INTRODUCTION

With ever-increasing complexity of digital applications, the issues of reliability have become very important in today's VLSI designs. Reliability can be improved by sophisticated testing schemes to weed out faulty circuits [1]. However, such off-line or static tests can identify permanent faults, but not transient faults. It is obvious that a mechanism for concurrent error detection (CED) must be installed to detect such faults before they cause undesirable results [2].

All concurrent error detection schemes detect errors through conflicting results generated from operations on the same operands. Concurrent error detection can be achieved through space redundancy, time redundancy, and information redundancy [3]. The conflicting results are compared and errors caused by faults are detected by a hardware check circuit, i.e., the checker. Checkers can no longer be assumed to be error-free in digital systems, because they are constructed from the same types of components as the circuits that perform the operation and hence are subject to the same type of failures. This brings up to the question: Who is checking the checker? The answer is clearly a checker that is self-checking.

It would be preferable for the circuits to be designed such that they will indicate any malfunction during the normal operation and will not produce an erroneous result without

( e

> V P

A

th

1(

ca;

ha m

de

1.

1-10 erro

em

lase

cod

an error indication. In these circuits, any fault from a specified set of faults will cause a detectable erroneous output during normal operation, and each fault must not cause erroneous outputs without also producing an error signal [4,5].

Redundancy design [3] approaches have been successfully implemented in today's VLSI designs for enhancing chip yield and system reliability [6]. However, due to speed performance degradation, time redundancy is not suitable for *on-line* testing. On other hand, for the hardware redundancy, the simplest *concurrent error detection* in multi-level circuits involves duplication of the circuit and comparing the outputs of the two blocks. Any mismatch between them will indicate an error. The equality of two sets of outputs is checked by a totally *self-checking* equality comparator [7,8]. This involves more than 100% redundancy (100% due to the duplicate circuitry and some extra for the checker) in the circuit. This is rather a high cost to pay for fault tolerance.

Information redundancy involves the use of coding techniques that enhance circuit capacity for reliable operation. It has been implemented for fault-tolerant, fail-safe, and concurrent error detection designs of digital circuits. The features of high speed and low hardware cost are highly desirable especially for a checker design. Therefore, this has motivated the development of fast, yet low hardware overhead cost, checker circuits and design methodologies for self-checking circuits or systems.

#### 1.1 PREVIOUS WORK

Extensive research has shown that the errors in VLSI circuits are of a unidirectional error type [9,10]. A unidirectional error model assumes that even though both 0-to-1 and 1-to-0 errors can occur, only one type of error occurs in a particular data word [11]. Such errors have been observed in modern digital devices such as PLAs, ROMs, and compact laser disks [12]. Numerous coding techniques, such as m-out-of-n codes [13-25], Berger codes [26-32], Borden codes [12,33], Burst detecting codes [34,35,36], Residue codes,

con

che

[9,3 pro;

prac

and AN codes [37,38], have been proposed to detect such errors. Among these coding techniques, Berger codes are the least redundant separable codes [26-29] for All-Unidirectional codes.

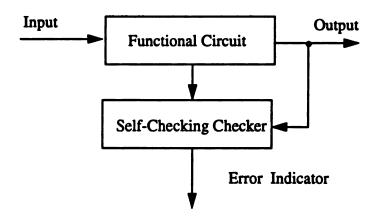

A self-checking circuit [6], as shown in Figure 1.1, consists of a functional circuit and a self-checking checker. The functional circuit can be either a combinational or a sequential circuit. The functional circuit is generally designed such that its primary outputs and some encoded outputs are able to produce an erroneous result in the presence of a fault. The error indicator must be designed to produce an error signal for some normal circuit inputs whenever a fault from a specified set of faults occurs within the circuit.

Figure 1.1 A self-checking circuit.

Considerable research efforts have been devoted to the design of *self-checking* combinational circuits [39-43] and *self-checking* sequential circuits [44-54]. The *self-checking* concept has been applied to microprogram control units and PLAs [9,39,52,55,56]. In addition, numerous *self-checking checker* designs have also been proposed [14,42,49,57,58]. Little emphasis, however, has been devoted to evaluate the practical designs in terms of area overhead and speed performance degradation.

> ac) de)

> > mi

m;

syr ver

or ;

### 1.2 PROBLEM STATEMENT

In general, the code length of a checker grows linearly with the number of outputs of a functional circuit, while the complexity of the checker may grow rapidly. As a result, a self-checking circuit with a large amount of outputs requires a huge checker, and the time required for the checker to detect errors may exceed the clock cycle time of the functional circuit [59]. This results in an increase in the system cycle time required to capture the error signal. To alleviate such a problem, it is highly desirable to develop a checker having the features of high speed and low hardware cost.

Since the hardware cost of the checkers increase almost exponentially as the code length increases, the use of many smaller code length checkers require less hardware cost than that of a larger code length checker. Thus, it is desirable to develop a partitioning scheme which partitions the output of a given circuit into many smaller groups so that smaller checkers can be used to reduce both hardware overhead and performance degradation. The number of smaller checkers can be generally determined based on the performance measurement AT<sup>k</sup>, where A is the gate count, T is the gate delay, and k is a measurement parameter determined by the applications. In this thesis, the optimization is achieved by minimizing the gate count under delay constraint. In other words, based on the delay constraint derived from a set of design specifications, the checkers which achieve minimal hardware overhead are chosen.

As sophisticated techniques for the synthesis of the logic emerge, automated synthesis systems are becoming popular. The synthesis system such as *sis* [60] generates very good results for multi-level logic implementation. It targets optimizing either chip area or speed performance. However, it is also desirable to address the reliability issue, in automated synthesis system.

1.

be

de

a 1 de

0v

ha scl

siz nu

. alg

ob Th

se

1.4

des

#### 1.3 RESEARCH TASKS

Due to the salient feature of least redundant separable codes, Berger codes have been implemented for fault-tolerant and fail-safe designs of digital circuits to detect all unidirectional errors. The features of high speed and lower hardware cost are highly desirable especially in the checker design. Thus, the first task in this research is to develop a fast, yet low hardware cost Berger code checker. A partitioning and folding scheme is developed to design a self-testing checker for Berger codes in which both hardware overhead and speed degradation are improved significantly.

In order to reduce the code lengths of the checkers and to further reduce the hardware cost, the second task of this research is to develop an efficient output partitioning scheme. The scheme partitions the output into many smaller groups which employ small sized checkers. The chromatic partitioning of a graph is used to formulate the problem. The number of groups is equivalent to the chromatic number. In this research, a partitioning algorithm is presented. Finally, in addition to taking the area and speed as design objectives, reliability should be also a design objective of an automated synthesis system. Thus, the third task is to develop a system for automated synthesis of *on-line* testable sequential circuits for multi-level logic implementation.

The three tasks presented in this research are summarized as follows:

- (1) develop a fast, yet low hardware cost, Berger code checker;

- (2) develop an efficient output partitioning algorithm; and

- (3) develop an automated synthesis system for on-line testable circuits.

#### 1.4 THESIS ORGANIZATION

This thesis is organized as follows: Chapter 2 reviews the previous work in the design of both checkers and functional circuits. Chapter 3 describes the developed

partitioning and folding scheme for *Berger code* checkers. An output function partitioning algorithm is presented in Chapter 4 with some experimental results. Chapter 5 illustrates a system, namely, *SOLiT*, for automated synthesis of *on-line* testable sequential circuits with multi-level logic implementation. The system takes a behavioral description as its input and produce a physical layout for chip fabrication. Finally, conclusions and future research are given in Chapter 6.

Ş

Į,

an

## **CHAPTER 2**

# ON-LINE SELF-TESTABLE CIRCUIT AND SYSTEM

This chapter summarizes the terminology used in this thesis, and briefly describes the characteristics of checker and functional circuits for *on-line* testing circuits and systems.

## 2.1 TERMINOLOGY

The following notation and definitions used in this study can be found in [4]:

N: input code space.

S: output code space.

x: an input vector.

f: a fault in the fault set F.

$\lambda$ : an output vector in the correct output space.

Y: mapping function of the circuit.

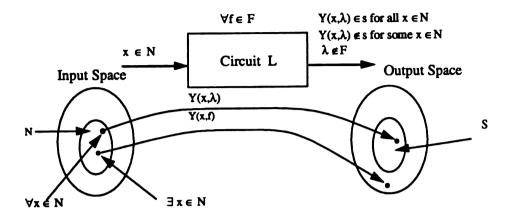

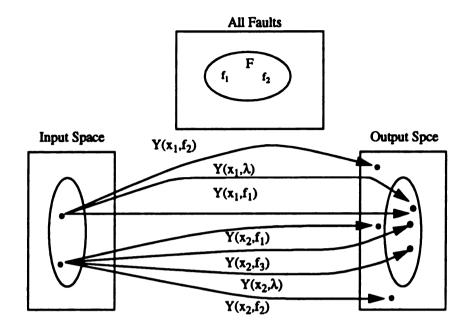

<u>Self-Testing</u>: A circuit L is *Self-Testing* (ST) for an input set N and a fault set F if for every fault f in F there is some input x in N such that Y(x,f) is not in S.

**Fault-Secure:** A circuit L is *Fault-Secure* (FS) for an input set N and a fault set F if for any input x in N and for any fault f in F,  $Y(x,f) = Y(x,\lambda)$ , or  $Y(x,f) \notin S$ .

(a) Self-testing circuit.

(b) Fault-secure circuit.

Figure 2.1 Self-testing and fault-secure circuits.

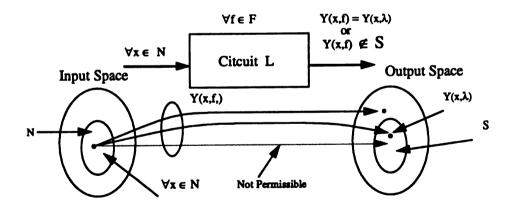

<u>Totally Self-Checking</u>: A circuit is *Totally Self-Checking* (TSC) if it is both *fault-secure* and *self-testing*.

Figure 2.2 Totally self-checking circuit.

<u>Code-Disjoint</u>: A circuit is *Code-Disjoint* (CD) if the input code space maps to the output code space and the input noncode space maps to the output noncode space.

<u>Self-Testing Checker</u>: A checker is a *Self-Testing Checker* (STC) if it is *self-testing* and *code-disjoint*.

Strongly Fault Secure: For a fault sequence  $\langle f_1, f_2, ..., f_n \rangle$ , let k be the smallest integer for which the combination of  $f_i$ ,  $1 \le i \le k$ , does not produce the correct code output for at least one code input in a circuit G. If there is no such k, set k = n. Then G is Strongly Fault Secure (SFS).

5

ei

sea

n:

an

ex

Be che

me

Sys

Sep pres

Īų

f≈ ]

Strongly Code Disjoint: A circuit is Strongly Code Disjoint (SCD) for a fault set F if, for every fault f in F, either

- (1) the circuit is *code-disjoint* and *self-testing* for the fault f, or

- (2) the circuit is *code-disjoint* and if f occurs then the resultant circuit is still SCD for the fault set F excluding the fault f.

<u>Strongly-Self-Checking</u>: A circuit is *Strongly-Self-Checking* (SSC) for a set of faults F if before the occurrence of any fault, the circuit is *code-disjoint*, and for every fault in F, either:

- (a) the circuit is self-testing and fault-secure, or

- (b) the circuit is *fault-secure* and always maps noncode words at the inputs to non-codewords at the outputs,

and if another fault from F occurs, then either property (a) or (b) is true for the fault sequence.

m-out-of-n (m/n) code: In a m-out-of-n (m/n) code, denoted as  $C_{m/n}$ , all code words have exactly m 1's and (n-m) 0's. It is also called m-hot code.

Berger code: A Berger code B(I,K) of length L has an I-bit information part and a K-bit check part, where  $K = \lceil \log_2(I+1) \rceil$  and L = I + K. The check part is the bit by bit complemented binary representation of the number of 1's in the information part.

Systematic: A code is Systematic if it has K check bits appended to I information bits and all the 2<sup>I</sup> possible information I-tuple are assumed to occur.

Separable Code: If all the 2<sup>I</sup> possible I-tuple do not occur and it is known which one is presented, a code derived for this case is referred to as a Separable Code.

<u>True Minterm</u>: A minterm  $m_i$  for a single output function f is called a *True Minterm* if f=1 when  $m_i$  is applied.

4

CC

T

2

Suc a m

The

for beer

leve

**False Minterm:** A minterm  $m_i$  for a multi-output function,  $f_{i, 1} \le i \le n$ , is called a **False Minterm** if all  $f_i = 0$  when  $m_i$  is applied.

Complete Covering: Complete Covering requires the covering of 1-cells as usual, but in addition, each 0-cell must be covered by some product terms.

<u>True Product Term</u>: A product term p<sub>i</sub> is a *True Product Term (False Product Term)* if all the minterms it covered are true minterms (false minterm).

# 2.2 SELF-TESTING CIRCUIT STRUCTURES

A general structure of a totally self-checking (TSC) circuit is shown in Figure 1.1. During the normal operation, code inputs are applied to the functional circuits and the coded outputs are produced. Both the functional circuits and the checkers should possess some special properties. This section reviews some existing STC designs for checkers and TSC design for functional circuits.

#### 2.2.1 CHECKER DESIGN

Two coding techniques, the *m-out-of-n* (*m/n*) code and the *Berger code*, have been successfully implemented in VLSI design for detecting all unidirectional errors. Basically, a *m/n* checker consists of two independent sets of subcircuits, each having a single output. The *m/n* code checker produces the output (0,1) or (1,0) for the application of a *m/n* codeword input, i.e., the number of 1's at the checker input is m, and the output (0,0) or (1,1) for non-codeword inputs. Considerable design alternatives for *m/n* code checkers have been studied in [13-25]. The circuits for the *m/n* checker may be implemented with two-level, three-level, or multi-level logic. Numerous *self-checking checkers* for *Berger codes*

to

A.

side sets

are (

where

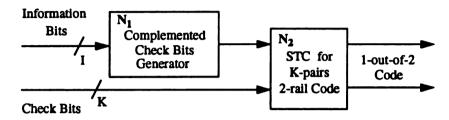

have been presented in [26-32]. The basic design principle for a *Berger code* checker is to generate the replicated check bits of binary value complementary to the original ones and to compare them using a *two-rail* comparator. A general structure is shown in Figure 2.3.

Figure 2.3 Typical structure of STC for normal Berger code checker.

#### A. m/n Checkers

A m/n checker design with two-level logic realization was presented in [15]. Consider a m-out-of-2m code checker, where the 2m bits are partitioned into two distinct subsets  $A = \{x_i \mid 0 \le i \le m-1\}$  and  $B = \{x_j \mid m \le j \le 2m-1\}$ . If the two outputs of the checker are designed as

$$f = \sum_{i=0}^{q} T(\mathbf{k}_a \ge i) \cdot T(\mathbf{k}_b \ge m-i) \qquad i \text{ is odd,}$$

(2.1)

$$g = \sum_{i=p}^{q} T(k_a \ge i) \cdot T(k_b \ge m-i) \qquad i \text{ is even,}$$

(2.2)

where  $p = \max (m-n_{b_1}-1)$ ,  $q = \min(n_a, m+1)$ ,

The jorit

the r

has t

the v

simui (m - i

more

from aratel

larly,

(m - j

**k**<sub>4</sub>+

codev

functi

dant i testin

noma

$n_a$  = the number of bits in group A,

$n_b$  = the number of bits in group B,

m = the number of 1's in the information bits,

$k_a$ ,  $k_b$  = the number of 1's occurring in each group.

The notation  $\Sigma$  represents the OR operation, and  $\bullet$  represents the AND operation. The majority function  $T(k_a \ge i)$  represents the Boolean function that has the value 1 if and only if the number of 1's in subset A is greater than or equal to the value i; similarly,  $T(k_b \ge m - i)$  has the value 1 if and only if the number of 1's in the subset B is greater than or equal to the value m - i.

The term  $T(k_a \ge i) \bullet T(k_b \ge m - i) = 1$  is tested by making  $T(k_a \ge i)$  and  $T(k_b \ge m - i)$  simultaneously be equal to 1. This is done with codewords containing i 1's in subset A and (m - i) 1's in subset B. These codewords exist because  $0 \le i \le m$  and  $n_a = n_b = m$ . Furthermore,  $T(k_a \ge i)$  may be implemented by the AND of each different combination of i bits from the  $n_a$  available; the results are ORed together. Each combination must be tested separately, and this requires  $\binom{n_a}{i} = \binom{m}{i}$  code words, each containing exactly i 1's in A. Similarly,  $T(k_b \ge m - i)$  requires  $\binom{n_b}{m-i} = \binom{m}{m-i} = \binom{m}{i}$  codewords, each containing exactly (m - i) 1's in B. Since the bits in A and B are independent except for the constraint that  $k_a + k_b = m$  for codewords, these factors can be completely tested with the same  $\binom{m}{i}$  codewords. To test all such terms for  $0 \le i \le m$ , it requires a total of  $2^m$  test patterns, i.e., the sum of  $\binom{m}{i}$  for  $0 \le i \le m$ .

If such a test set supplies all  $2^m$  input combinations to A and B, then the majority functions, such as  $T(k_a \ge i)$  or  $T(k_b \ge m - i)$ , are exhaustively tested, and any non-redundant implementation of them is completely diagnosed. Therefore, the checkers are self-testing for single faults or unidirectional faults if these  $2^m$  codewords are given during normal operation.

de

the

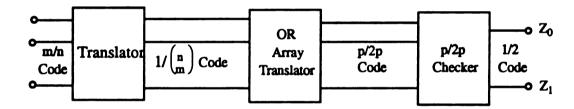

A m/n code checker, with  $n \neq 2m$ , as shown in Figure 2.4, is generally realized by translating the given code to a 1-out-of- $\binom{n}{m}$  (1/ $\binom{n}{m}$ ) code, which is then converted to a p-out-of-2p (p/2p) code via a TSC translator [15]. In this case, p should satisfy the following relation:

$$\binom{2p}{p} \ge \binom{n}{m} \ge 2^p \tag{2.3}$$

The codewords should be selected so that the left-most p bits are complementary to the right-most p bits as shown in Figure 2.5. The two-level realization obtained is indeed a minimum level TSC circuit. However, when the number of inputs become larger, the fan-in of every OR gate grows fast making it impractical for implementing.

Figure 2.4 General self-testing checker for m/n checker with  $n \neq 2m$ .

| $\mathbf{x}_0$             | $\mathbf{x}_1$ | $\mathbf{x}_2$ | $\mathbf{x}_3$ | $\mathbf{x_4}$ | <b>x</b> 5                 |

|----------------------------|----------------|----------------|----------------|----------------|----------------------------|

| <b>x</b> <sub>0</sub><br>0 | 0              | o              | 1              | 1              | <b>x</b> <sub>5</sub><br>1 |

| 1                          | 0              | 0              | 0              | 1              | 1                          |

| 0                          | 1              | 0              | 1              | 0              | 1                          |

| 0                          | 0              | 1              | 1              | 1              | 0                          |

| 1                          | 1              | 0              | 0              | 0              | 1                          |

| 0                          | 1              | 1              | 1              | 0              | 0                          |

| 1                          | 0              | 1              | 0              | 1              | 0                          |

| 1                          | 1              | 1              | 0              | 0              | 0                          |

Figure 2.5 Test patterns for m/n checker.

[] A

all

de (O

Pr

to

tit (2

2-

an

A)

ga 3-

П

3-; m;

An alternative m/n TSC design using a 3-level realization has been presented in [17] for  $n \ge 4$ . For n < 2m and n > 2m, the procedure gives AND-AND-OR and OR-OR-AND 3-level realizations, respectively, while for n = 2m, it results in an AND-OR (or dually OR-AND) 2-level realization which is equivalent to the design provided in [15]. The design procedure consists of the following two stages: (1) Construct two 2-level AND-OR (OR-AND) circuits with no shared gates, which correspond to blocks of the partition. (2) Provide AND (OR) gates, which are shared by two 2-level AND-OR (OR-AND) circuits, to form AND-AND-OR (OR-OR-AND) realization.

Basically, a m/n code is comprised of a set of m/n code vector x, and it can be partitioned into two disjoint subsets  $G_a$  and  $G_b$ , where  $k_a$  and  $k_b$  are defined in Equations (2.1) and (2.2).

$$G_a = \{x \mid x \in m/n, w(k_a) \text{ is odd}\}$$

(2.4)

$$G_b = \{x | x \in m/n, w(k_b) \text{ is even}\}$$

(2.5)

where  $w(k_a)$  and  $w(k_b)$  are the number of 1's in subset  $G_a$  and  $G_b$ , respectively. A disjoint 2-level AND-OR realization based on the partition is a pair of 2-level AND-OR circuits  $g_a$  and  $g_b$  as shown in Figure 2.6, where there exists a one-to-one correspondence between AND gates in circuit  $g_a$  and codewords in  $G_a$ , and between AND gates in circuit  $g_b$  and codewords in  $G_b$ . Exactly m bits of value 1 in codeword x are used as inputs to the AND gates for x. A disjoint two-level OR-AND realization can be defined in a dual way. Such a 3-level configuration with shared gates is illustrated in Figure 2.7. AND gates at the leftmost stage are referred to as shared ANDs and those at the middle stage are called 3-level AND-AND-OR realization (a 3-level OR-OR-AND realization is defined in a dual manner).

Figure 2.6 Disjoint 2-level realization for  $C_{3/5}$ .

Figure 2.7 3-level realization for  $C_{3/5}$ .

Similar to two-level, the three-level implementation also has the large fan-in problem. In order to alleviate this problem, a cost-effective m/n checker design with multi-level logic implementation has been presented for  $m \ge 3$ ,  $4m \ge n > 2m$  [20]. Basically, any m/n code can be represented as a sum of concatenated partitioned codes  $i/n_a$  and  $(m-i)/n_b$ for  $0 \le i \le m$ , and  $n_a + n_b = n$ . Thus, the set of all m/n codes can be formally written with the union operator as

$$C_{m/n} = \bigcup_{i=0}^{m} C_{i/n_{\bullet}} \times C_{(m+i)/n_{\bullet}}$$

(2.6)

where  $\cup$  is a union representation and  $\times$  is a concatenation operator. The set  $C_{m/n}$  can be partitioned into the following three disjoint subsets:

$$C_{AB} = C_{k_{\bullet}/n_{\bullet}} \times C_{k_{\bullet}/n_{\bullet}}; \qquad (2.7)$$

$$C_{A} = \bigcup_{i=0}^{k_{a}-1} C_{i/n_{a}} \times C_{(m-i)/n_{b}};$$

(2.8)

$$C_{B} = \bigcup_{i=0}^{k_{b}-1} C_{(m-i)/n_{a}} \times C_{i/n_{b}}$$

(2.9)

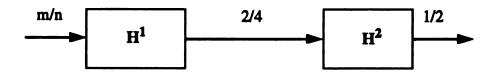

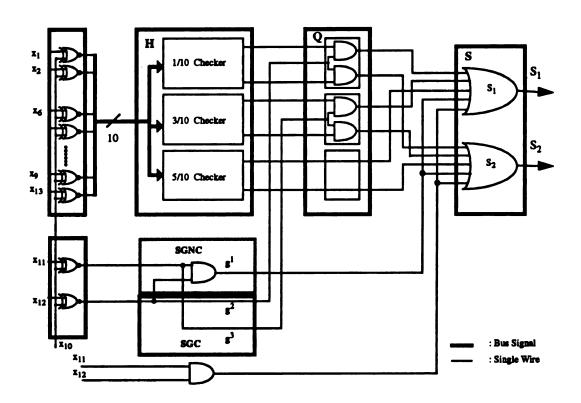

where  $k_a = \lfloor m/2 \rfloor$ ,  $k_b = \lceil m/2 \rceil$ ,  $1 \le k_a \le n_a$ ,  $1 \le k_b \le n_b$ . Both sets  $C_A$  and  $C_B$  can be further partitioned by the same manner. With this partition scheme and algorithm presented in [20], the m/n checkers, as shown in Figure 2.8, can be obtained by using a translator  $H^1$  of the m/n code into 2/4 code, and a TSC 2/4 checker, or  $H^2$ . The block  $H^2$  will produce a 1/2 code as the error signal. For demonstrating this algorithm [20], an example is given below.

Figure 2.8 m/n code checker.

# Example 2.1:

The following equations are used to design a TSC checker for 3/8 code [20].

$$h_{1}^{1} = x_{1} + (x_{2} + x_{3})$$

$$h_{2}^{1} = (x_{4} + x_{5}) + (x_{6} + x_{7})$$

$$h_{3}^{1} = x_{1}(x_{2} + x_{3}) + (x_{4} + x_{5})(x_{6} + x_{7})$$

$$h_{4}^{1} = x_{2}x_{3} + x_{4}x_{5} + x_{6}x_{7}$$

$$h_{1}^{2} = (h_{1}^{1} + h_{3}^{1})(h_{2}^{1} + h_{4}^{1})$$

$$h_{2}^{2} = h_{1}^{1} h_{3}^{1} + h_{2}^{1} h_{4}^{1}$$

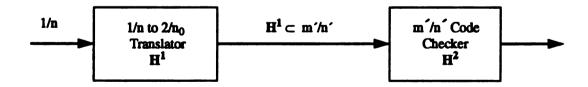

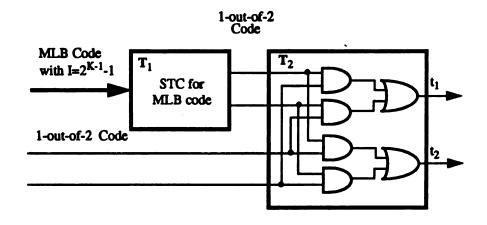

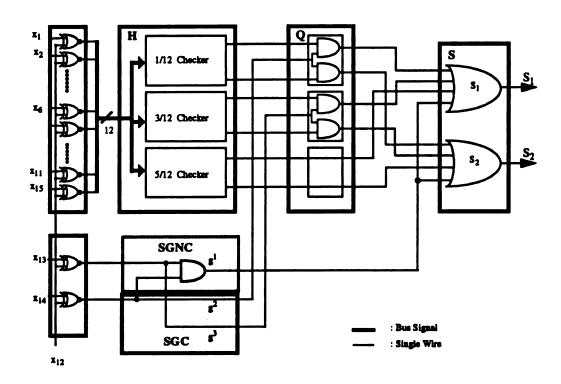

Numerous TSC 1/n code checker designs have been developed [21,22,23]. Similar to Figure 2.8, a 1/n TSC checker, as shown in Figure 2.9, can be obtained by using a translator  $H^1$  to translate the 1/n code into  $2/n_0$  code, then into 1/2 code for indication [20]. At the first stage,  $n_0$  should be selected such that  $\binom{n_0-1}{2} \le n \le \binom{n_0}{2}$  and follow the algorithm in [20] to obtain the partitioned subsets  $h_1^0$ ,  $1 \le i \le n_0$ . A  $2/n_0$  code results. Then, if  $n_0$  is large, a further reduction of  $n_0$  will be necessary to obtain a smaller  $n_1$ , and then a 1/2 two-rail checker is appended to the last stage.

Figure 2.9 1/n code checker.

# Example 2.2: [25]

Consider the design of a 1/20 code checker. It first needs a  $H^1$  translator which translates the 1/20 code to a 2/7 code with the functions  $h_i^0$ ,  $1 \le i \le 7$ , Then the 2/7 code is translated to a 2/4 code as shown in Example 2.1. The following equations summarize the 1/20 code checker design.

$$h_{1}^{0} = x_{1} + x_{7} + x_{8} + x_{14} + x_{15}$$

$$h_{2}^{0} = x_{1} + x_{2} + x_{11} + x_{12} + x_{19} + x_{20}$$

$$h_{3}^{0} = x_{2} + x_{3} + x_{8} + x_{9} + x_{17} + x_{18}$$

$$h_{4}^{0} = x_{3} + x_{4} + x_{12} + x_{13} + x_{15} + x_{16}$$

$$h_{5}^{0} = x_{4} + x_{5} + x_{9} + x_{10} + x_{20}$$

$$h_{6}^{0} = x_{5} + x_{6} + x_{13} + x_{14} + x_{18} + x_{19}$$

$$h_{7}^{0} = x_{6} + x_{7} + x_{10} + x_{11} + x_{16} + x_{17}$$

$$h_{1}^{1} = h_{1}^{0} + (h_{2}^{0} + h_{3}^{0})$$

$$h_{2}^{1} = (h_{4}^{0} + h_{5}^{0}) + (h_{6}^{0} + h_{7}^{0})$$

$$h_{3}^{1} = h_{1}^{0} (h_{2}^{0} + h_{3}^{0}) + (h_{4}^{0} + h_{5}^{0})(h_{6}^{0} + h_{7}^{0})$$

$$h_{4}^{1} = h_{2}^{0} h_{3}^{0} + h_{4}^{0} h_{5}^{0} + h_{6}^{0} h_{7}^{0}$$

$$h_{1}^{2} = (h_{1}^{1} + h_{3}^{1})(h_{2}^{1} + h_{4}^{1})$$

$$h_{2}^{2} = h_{1}^{1} h_{3}^{1} + h_{2}^{1} h_{4}^{1}$$

#### **B. Berger Code Checkers**

Figure 2.3 shows the general structure of a *Berger code* checker. The complemented check bits generator is used to generate the binary value corresponding to the number of 1's in the information bits. In general, a set of full adder modules that add the information bits in parallel and produce the binary number corresponding to the number of 1's in the information bits has been implemented [29]. Recently, based on a completely different

SIT

[30

the

proce

2.1 (

$|x_i|_1$

structure, a *Berger code* partitioning scheme has been presented for the checker design [30].

Consider a *Berger code* checker design [29] using a set of full adder modules for the complemented check bit generator. The design procedure is summarized as follows.

- (1) Let  $s = \{x_i | 1 \le i \le 2^k 1\}$  be the set of all information bits, and set m = k and j = 1.

- (2) Partition the set S into three groups  $A^j$ ,  $B^j$ , and  $E^j$ , which respectively consist of the left-most  $2^{m-1}-1$  bits, the next  $2^{m-1}-1$  bits, and the right-most bit. Let  $a^j = (a^j_{m-1}, a^j_{m-2}, ..., a^j_1)$ ,  $b^j = (b^j_{m-1}, b^j_{m-2}, ..., b^j_1)$ , and  $e^j$  be the binary representations of the number of ones occurring in the information bits of groups  $A^j$ ,  $B^j$ , and  $E^j$ , respectively.

- (3) The binary representation of the number of ones occurring in S,  $g^j = (g^j_m, g^j_{m-1, ..., g^j_n})$  is given by the following addition:

$$a_{m-1}^{j} \quad a_{m-2}^{j} \cdots \quad a_{1}^{j}$$

$b_{m-1}^{j} \quad b_{m-2}^{j} \cdots \quad b_{1}^{j}$

$+ \qquad \qquad e^{j}$

$g_{m}^{j} \quad g_{m-1}^{j} \quad g_{m-2}^{j} \cdots \quad g_{1}^{j}$

A ripple carry adder with m - 1 stages is used to generate the vector g<sup>j</sup>.

- (4) If m > 2, then: (i) m = m 1, L = j; (ii) let  $S = A^j$ , j = j + 1 and repeat steps 2 and 3 to generate the vector  $\mathbf{a}^L = \mathbf{g}^L$ . The vector  $\mathbf{b}^L$  is generated by a circuit identical to that which generates  $\mathbf{a}^L$ .

- (5) End.

Consider the *Berger code* checker based on partitioning scheme in [30]. The design proceeds from the idea that any *Berger code* can be constructed from  $u = \lceil (I+1)/2 \rceil m/n$  codes, where I is the number of information bits, m = 2i-1,  $1 \le i \le u$ , and n = I+1. Table 2.1 (a) lists the B(7,3) codewords. Each subset  $D_i$  consists of seven information bits  $\{x_i|1\le i\le 7\}$  and three check bits  $\{x_8,x_9,x_{10}\}$ . The subset  $D_i$  is a collection of *Berger*

Table 2.1: Berger Code B(7.3).

(a)

| Subset                                 | expanded information part x <sub>1</sub> x <sub>2</sub> x <sub>3</sub> x <sub>4</sub> x <sub>5</sub> x <sub>6</sub> x <sub>7</sub> x <sub>10</sub> | reduced<br>check part<br>x <sub>8</sub> x <sub>9</sub> |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| $egin{array}{c} D_1 \ D_2 \end{array}$ | 0 0 0 0 0 0 0 1 0                                                                                                                                  | 11                                                     |

| D <sub>3</sub><br>D <sub>4</sub>       | $egin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                 | 1 0<br>1 0                                             |

| D <sub>5</sub><br>D <sub>6</sub>       | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                               | 0 1<br>0 1                                             |

| D <sub>7</sub><br>D <sub>8</sub>       | 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                            | 0 0<br>0 0                                             |

(b)

| Subset         | expanded information part x <sub>1</sub> x <sub>2</sub> x <sub>3</sub> x <sub>4</sub> x <sub>5</sub> x <sub>6</sub> x <sub>7</sub> x <sub>10</sub> | reduced<br>check part par<br>x8 x9 | rtitioning                                     |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------|

| E <sub>1</sub> | 0 0 0 0 0 0 0 1                                                                                                                                    | 11 C <sub>1</sub>                  | <sub>1/8</sub> ×(1 1)                          |

| E <sub>3</sub> | 00000111                                                                                                                                           | 10 C                               | <sub>1/8</sub> ×(1 1)<br><sub>3/8</sub> ×(1 0) |

| E <sub>5</sub> | 00011111                                                                                                                                           | 01 C                               | <sub>5/8</sub> ×(0 1)                          |

| E <sub>7</sub> | 0 1 1 1 1 1 1 1                                                                                                                                    | 00 C                               | 5/8×(0 1)<br>1/8×(0 0)                         |

sig

par sets

che

subs

ie., 1

result

effect ber of

gate co

levels

effecti

gale lev

cost eff

codewords in which the number of 1's in the corresponding information part is i - 1, and  $D_i = C_{(i-1)/(I+1)} \times P_i$ , where  $\times$  is a concatenation operator,  $P_i$  is the check part of  $D_i$ . The **Berger code** B(7,3) can be generally represented as a union of eight m/n codes  $C_{i/7}$ ,  $0 \le i \le 7$ , as follows

$$B(7,3) = C_{0/7} \times (111) \cup C_{1/7} \times (110) \cup C_{2/7} \times (101) \cup C_{3/7} \times (100) \cup C_{4/7} \times (011) \cup C_{5/7} \times (010) \cup C_{6/7} \times (001) \cup C_{7/7} \times (000).$$

The partitioning scheme first expands the information part J by adding the least significant bit (LSB) of the check part. Table 2.1 (b) illustrates the expanded information part  $J^* = \{x_1, x_2, ..., x_7, x_{10}\}$  and the reduced check part  $P^* = \{x_8, x_9\}$ . As a result, the subsets  $D_{2i-1}$  and  $D_{2i}$  not only have the same number of 1's, but also have the same reduced check part. Thus, the adjacent pair of subsets  $D_{2i-1}$  and  $D_{2i}$  are grouped and replaced by a subset  $E_{2i-1}$ , as shown in Table 2.1 (b). The Berger code is written as

$$B(7,3) = C_{1/8} \times (11) \cup C_{3/8} \times (10) \cup C_{5/8} \times (01) \cup C_{7/8} \times (00).$$

i.e., the implementation requires only four checkers for  $C_{1/8}$ ,  $C_{3/8}$ ,  $C_{5/8}$ , and  $C_{7/8}$ . This results in reducing the number of checkers by half with the partitioning scheme.

In [30], two design alternatives were presented: a minimal-level design and a costeffective design. The former uses the minimal-level STCs for m/n codes to reduce the number of gate levels, while the latter employs multi-level logic implementation to reduce the

gate count. Results have shown that the STC design for B(7,3), for example, requires 5 gate

levels and 137 gates for minimal-level implementation and 8 levels and 87 gates for costeffective implementation [30]. However, it needs 17 gate levels and 40 gates in [28] and 11

gate levels and 58 gates in [29]. The B(15,4) checker takes 11 gate levels and 315 gates for

cost effective implementation in [30], but requires 35 gate levels and 149 gates in [28] and

1' ps

ev

or

co

2.2

sec exi

Ho

terf

also

mug

(2),

twe

17 gate levels and 150 gates in [29]. Compared to the STC designs presented in [28], the partitioning scheme offers an improvement in delay but with a great cost in hardware. However, it should be mentioned that the implementation of the partitioning scheme is available only for B(I,K) with  $I=2^K-1$  or  $2^K-2$ , i.e., the design is not STC for any other *Berger code* lengths.

#### 2.2.2 FUNCTIONAL CIRCUITS

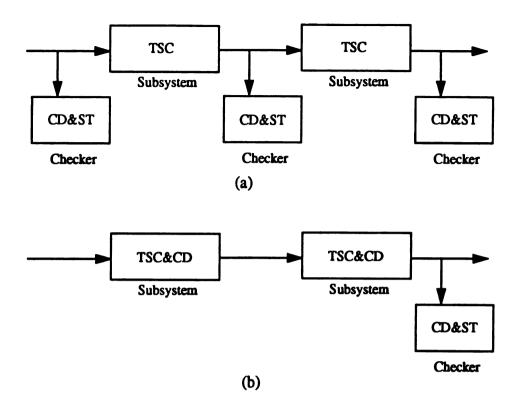

A system may consist of several subsystems which can be either combinational or sequential, interconnected with each other via certain interfaces. Two extreme approaches exist for such a system to be TSC [56].

- (1) If all the subsystems are TSC and all the interfaces are monitored by checkers which are CD and ST, then the system is TSC, as shown in Figure 2.10 (a).

- (2) If all the systems are CD in addition to being TSC, then the system is TSC with no checker used at the embedded interfaces except for the primary output of the system, as shown in Figure 2.10 (b).

A similar argument holds for SFS systems as shown in Figure 2.11 (a) and (b). However, in approach (1), the use of a large number of checkers for embedded partial interfaces may incur not only an intolerable increase in the amount of checker hardware, but also an unacceptable delay in error indication [52]. This is because all the checker outputs must be reduced to a single pair in a *self-testing* manner. On the other hand, in approach (2), it may be difficult for subsystems to be either CD, SCD. Therefore, a trade-off between these two approaches should be made.

Figure 2.10 TSC systems: (a) with TSC subsystems; and (b) with TSC and CD subsystems.

Figure 2.11 SFS systems: (a) with SFS subsystems; and (b) with SFS and CD subsystems.

stat

#### A. Combinational Circuits

The concept of a dynamically checked system was first introduced by Carter and Schneider [61] and later formalized and extended by defining both totally and partially self-checking notions for combinational circuits [50]. Consider the two-level PLA design [39]. The conventional design of PLAs generates all the true product terms in the AND array without considering any false product terms, but the design of SFS PLAs should be done differently. It is proven that if a PLA includes each false minterm in some false product terms in the AND array, then any unidirectional error in the PLA will propagate to the output. If the external output is encoded in an unidirectional error-detecting code and a SFS checker is used to monitor the outputs, the error in the PLA will be detected. Similarly, this concept can be extended to the multi-level combinational circuit. With the algebraic factorization of two-level logic a SC multi-level combination circuit will be obtained.

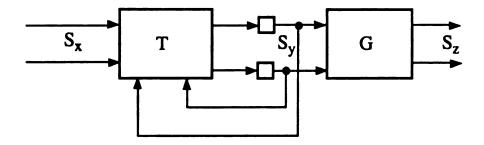

# **B.** Sequential Circuits

Consider a Moore type sequential machine, as shown in Figure 2.12, where Q is the set of states, Z is the set of output vectors, T is the state transition function, and G is the output function. It has been shown that a sequential machine is ST and FS if the following conditions are held [50]: (a) The combinational function T is SC; (b) The combinational function G is SC; (c) G is CD, even in the presence of faults in G; and (d) There exists a sequence i applied during normal functioning such that the next state function goes through all the transitions of the transition diagram (before a second fault occurs), then the sequential machine is SC for a fault set  $E_{\rm f}$ .

Mukai and Tohma [51] have proved that, using a state assignment which leads to monotonic next state equations and output equations with respect to the primary inputs, will cause unidirectional errors at the primary output when a single fault in the circuit occurs. Any code in which the codewords have no ordering among them can be used for the state assignment.

Figure 2.12 A sequential circuit (Moore type).

#### 2.2.3 LOGIC SYNTHESIS PROCEDURE

A logic synthesis procedure for finite-state machines (FSMs) includes three major steps: state assignment, logic optimization, and logic implementation. In order to synthesize FSMs with the tools developed at the University of California at Berkeley, the standard kiss2 format is used to describe the behavior of a FSM, as shown in Figure 2.13 (a), where "i" is the number of inputs; "o" is the number of outputs; "s" is the number of states, "p" is the number of product terms. The state assignment tool, mustang [62], is employed to encode internal state variables, as shown in Figure 2.13(b). The resultant logic is optimized by either espresso [63], for two-level logic minimization, misl1 [63] or sis, for multi-level optimization. Figure 2.13(c) lists the multi-level logic optimization using sis. A test pattern generation tool, stallion [63], can be used to generate test patterns to evaluate the synthesized circuits. Finally, the synthesized circuit can be implemented with either standard cells or gate arrays. Figure 2.13(d) lists the netlist generated by the technology mapper in sis, where standard cells in the sis cell library are used.

|  |  | Г |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

```

.i

6

9

.0

.p 21

.s 14

3 110000000

2 000000000

1---- 3

5 001000000

7 000000000

7 000000000

11---- 7

11 100110000

1---- 11 12 100100000

1-1--- 12

8 000001100

1-0--- 12

8 000000100

1-0--- 8

3 110000000

1-10-- 8

3 110000000

1-11-- 8

4 110000000

1---1- 4

13 000000010

1---0- 4

13 000000000

1---- 13 14 001000010

1---- 14

6 000000000

10---- 6

6 000000000

11---- 6

9 100110000

1---- 9

10 100100000

1----1 10

3 110000101

1---0 10 4 110000100

```

```

.p 21

#STATE ASSIGNED FINITE AUTOMATON

0010 0010

# 1

# 3

1010 1010

1000 1000

2

0110 0110

5

0111 0111

11 0100 0100

12 1011 1011

0000 0000

8

1111 1111

13 1001 1001

14 1100 1100

# 6

0011 0011

# 9

0101 0101

# 10 0001 0001

.i 10

.0 13

.type fr

1---- 0010 1010 110000000

1---- 1010 1000 000000000

1---- 1000 0110 001000000

1---- 0110 0111 00000000

10---- 0111 0111 000000000

11---- 0111 0100 100110000

1---- 0100 1011 100100000

1-1--- 1011 0000 000001100

1-0--- 1011 0000 000000100

1-0--- 0000 1010 110000000

1-10-- 0000 1010 110000000

1-11-- 0000 1111 110000000

1---1- 1111 1001 000000010

1---0- 1111 1001 000000000

1---- 1001 1100 001000010

1---- 1100 0011 000000000

10---- 0011 0011 000000000

11---- 0011 0101 100110000

1---- 0101 0001 100100000

1----1 0001 1010 110000101

1---0 0001 1111 110000100

```

(a) standard kiss2 format.

(b) state assignment with mustang.

Figure 2.13 A logic synthesis example.

1 . [ 1

Figure 2.13 Cont'd

```

INORDER = v0 v1 v2 v3 v4 v5 v6 v7 v8 v9;

OUTORDER = v10.0 v10.1 v10.2 v10.3 v10.4 v10.5 v10.6 v10.7 v10.8 v10.9

v10.10 v10.11 v10.12;

v10.0 = v8*v10.8 + [13] + v10.5;

v10.1 = v9*!v10.0*!v10.10 + !v3*!v9*v10.5 + !v2*!v9*v10.5 + v6*v10.10

+ v7*!v10.7 + [13] + v10.12;

v10.2 = v6*v10.0*!v10.12

v7*!v9*!v10.6 + v8*!v10.0*v10.3 +

!v10.1*v10.5;

v10.3 = !v10.8*[15] + !v7*v10.7 + v6*v9 + v10.6;

v10.4 = v10.7 + v10.5;

v10.5 = !v6*!v7*!v10.10 + !v8*v10.10;

v10.6 = v7*[13];

v10.7 = !v9*!v10.6*[15] + v6*!v7*!v8 + v10.8;

v10.8 = v1*v9*[15]

v10.9 = v2*v8*v10.10;

v10.10 = !v7*v9;

v10.11 = v4*v6*[13] + v6*v10.6;

v10.12 = v5*!v8*v10.10;

[13] = v8*!v9;

[15] = !v6*v7;

```

#### (c) resultant output network from sis.

```

.model ex4.p.esp

.inputs v0 v1 v2 v3 v4 v5 v6 v7

v8 v9

.outputs v10.0 v10.1 v10.2 v10.3

v10.4 v10.5 v10.6 v10.7 v10.8

v10.9 v10.10 v10.11 v10.12

.names v8 v10.5 v10.8 [13] v10.0

-1-- 1

---1 1

1-1- 1

.names v2 v3 v6 v7 v9 v10.0 v10.5

v10.7 v10.10

v10.12 [13] v10.1

-----1- 1

----1 1

---1---0--- 1

--1----1

0---0-1----

-0--0-1----

----10--0-- 1

.names v6 v7 v8 v9 v10.0 v10.1

v10.3 v10.5 v10.6 v10.12 v10.2

----1

--1-0-1--- 1

-1-0---0- 1

1---1---0 1

.names v6 v7 v9 v10.6 v10.7 v10.8

[15] v10.3

---1--- 1

1-1--- 1

-0--1-- 1

----01 1

.names v10.5 v10.7 v10.4

1- 1

-1 1

```

```

.names v6 v7 v8 v10.10 v10.5

--01 1

00-0 1

.names v7 [13] v10.6

11 1

.names v6 v7 v8 v9 v10.6 v10.8

[15] v10.7

----1- 1

100---- 1

---00-1 1

.names v1 v9 [15] v10.8

111 1

.names v2 v8 v10.10 v10.9

111 1

.names v7 v9 v10.10

01 1

.names v4 v6 v10.6 [13] v10.11

-11- 1

11-1 1

.names v5 v8 v10.10 v10.12

101 1

.names v8 v9 [13]

10 1

.names v6 v7 [15]

01 1

.end

```

# **CHAPTER 3**

# EFFICIENT SELF-TESTING BERGER CODE CHECKER DESIGN

This chapter presents the design of self-testing Berger code checkers with the developed partitioning and folding scheme. For a Berger code B(I,K), if  $I=2^k-1$  or  $2^k-2$ , then it is called a maximal length Berger (MLB) code. Otherwise, it is a non-maximal length Berger (NMLB) code. The designs of self-testing checkers for MLB and NMLB codes are respectively discussed in Sections 3.1 and 3.2.

# 3.1 MAXIMAL LENGTH BERGER (MLB) CODE CHECKER DESIGN

This first section more specifically discusses the *Berger code* checker design with the partitioning scheme presented in [30], and then presents an improved version with a partitioning and folding scheme for MLB codes.

#### 3.1.1 BERGER CODE PARTITIONING SCHEME

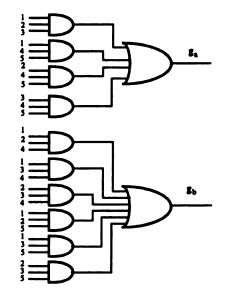

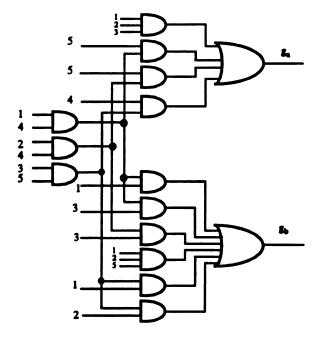

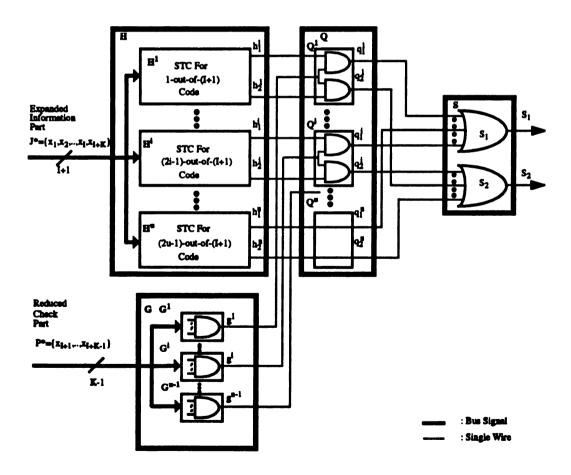

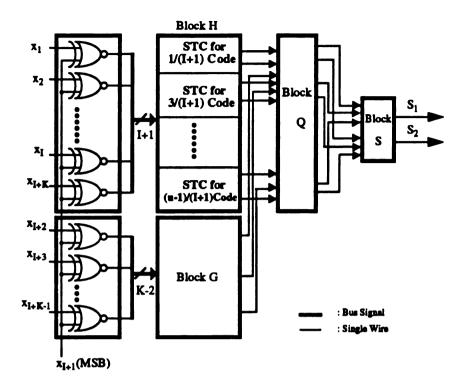

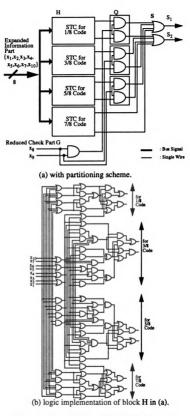

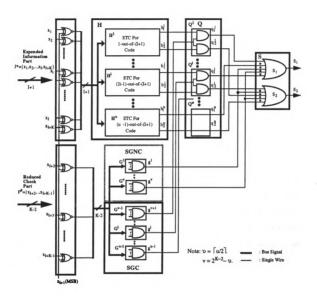

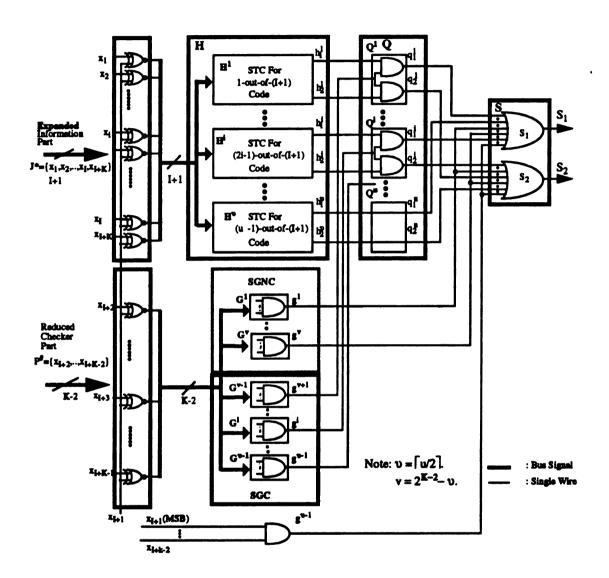

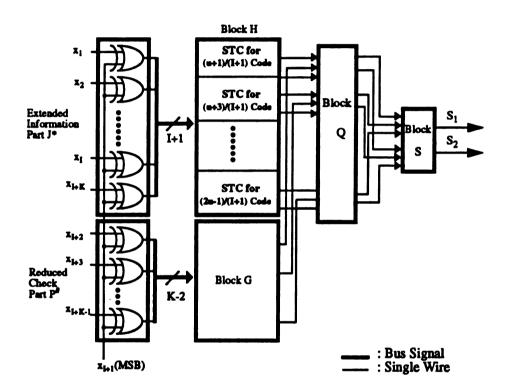

Figure 3.1 shows the internal structure of a STC design of MLB code implemented with the partitioning scheme presented in [30]. The checker, referred to as Circuit CH, is comprised of four major blocks: Block H includes the checkers for  $C_{(2i-1)/(I+1)}$ ,  $1 \le i \le u$ . where  $u = \lceil (I+1)/2 \rceil$ . Each checker takes I+1 bits from the expanded information part  $J^*$  as its input and produces two check output lines; Block G consists of  $(2^{K-1} - K)$  AND gates which have as inputs the check bits from the reduced check part  $P^*$ ; Block Q consists of u-1 pairs of AND gates; and Block S contains two u-input OR gates. The 1-out-of-2 code in the outputs of Block S indicates an error, if it exists.

Figure 3.1 Internal structure of a STC design of MLB code B(I,K) (Circuit CH).

# Theorem 3.1 Circuit CH is a STC Checker.

Prior to proving the properties of self-testing and code-disjoint for Theorem 3.1, the following lemmas are needed.

**Lemma 3.1:** The *totally self-checking checker*  $H^r$  produces the following code output when a code in a subset  $E_{2i-1}$  is applied to Circuit CH.

$$(h_1^r, h_2^r) = \begin{cases} (0 \ 1) \text{ or } (1 \ 0) & \text{if } i = r. \\ (0 \ 0) & \text{if } i < r. \\ (1 \ 1) & \text{if } i > r. \end{cases}$$

**Proof**: Consider the outputs  $h_1^r$  and  $h_2^r$  of the checker  $H^r$ . Let  $N_x$  be the number of 1's in an input codeword. Since  $h_1^r$  and  $h_2^r$  are the majority functions as defined in Equation (2.1) and (2.2) of the inputs, the value of  $(h_1^r, h_2^r)$  is equal to (1,1) if  $N_x > r$ ; (1,0) or (0,1) if  $N_x = r$ ; or (0,0) if  $N_x < r$ . For any code in  $E_{2i-1}$ , its number of 1's is i, i.e.,  $N_x = i$ . Thus, the lemma results.  $\blacklozenge$

Consider the construction of Block G which consists of  $2^{K-1}$  - K AND gates  $G^i$ ,  $1 \le i \le u$ . The output of  $G^i$  is denoted as  $g^i$  and its inputs are the 1-value reduced check bits in  $P_i^*$ . In case of  $N_1(P_i^*) = 1$ , say  $x_j = 1$  in  $P_i^*$  then  $g^i = x_j$  and no AND gate is necessary, where  $N_1(A)$ ,  $(N_0(A))$  denotes the number of 1's (0's) in A. For i = u,  $N_1(P_i^*) = 0$ , it is assumed that  $g^u = 1$  [30]. Let X and Y be two N-tuple. We say that X covers Y if and only if X has 1's everywhere Y has 1's. If neither Y covers X, nor X covers Y, then we say X and Y are unordered.

**Lemma 3.2:** (a)  $P_i^*$  never covers  $P_j^*$  if j < i;

(b) If

$$g^i = 1$$

and  $P_i^*$  covers  $P_i^*$ , then  $g^j = 1$ ; and

(c) If

$$g^i = 1$$

and  $P_i^*$  and  $P_i^*$  are unordered, then  $g^j = 0$ .

**Proof:** (a) If j < i, then  $N_1(J_j) < N_1(J_i)$ , or  $N_1(P_j) > N_1(P_i)$ , i.e.,  $P_j^*$  has more 1's than  $P_i^*$ . Thus,  $P_i^*$  never *covers*  $P_j^*$ ; (b) By definition,  $P_i^*$  covers  $P_j^*$  means that all inputs of  $G^j$  are

L 0

p

P gi If.

Le

un

Pr gei

ind res

> in l **s**/0

> by ;

the ۲,

out

Len Box

also inputs of  $G^i$ . Thus, if  $g^i = 1$ , i.e. the input variables of  $G^i$  are all 1's, then  $g^j = 1$ ; and (c) Since  $P_i^*$  and  $P_j^*$  are unordered, there exists, at least, one input variable of  $G^j$ , say  $x_r$ , which is not an input of  $G^i$ , where  $x_r = 0$  (because  $g^i = 1$ ). Thus  $x_r = 0$  causes the AND gate  $G^j$  to produces  $g^j = 0$ .

**Lemma 3.3:** When a code including the reduced check part  $P_i^*$  is applied to Block G, the outputs are

$$g^j = \begin{cases} 1 & \text{for } j = i; \text{ or } j > i \text{ and } P_i^* \text{ covers } P_j^* \\ 0 & \text{for } j < i; \text{ or } j > i \text{ and } P_i^* \text{ and } P_j^* \text{ are unordered.} \end{cases}$$

**Proof:** When a code including  $P_i^*$  is applied to Circuit CH, the AND gate  $G^i$  produces  $g^i = 1$ , i.e.,  $g^j = 1$  if j = i. For the case of j > i and  $P_i^*$  covers  $P_j^*$ , by Lemma 3.2 (b),  $g^j = 1$ ; If j < i, by Lemma 3.2 (a),  $P_i^*$  never covers  $P_j^*$ , therefore  $g^j = 0$ . Finally, if  $P_i^*$  and  $P_j^*$  are unordered, and j > i, by Lemma 3.2 (c),  $g^j = 0$ .

# Lemma 3.4: Circuit CH is self-testing for all unidirectional faults.

**Proof:** Two types of faults are identified: stuck-at-1 (s/1) and stuck-at-0 (s/0) faults. In general, a noncode output (1,1) in  $Q^i$  results in a noncode output (1,1) in Block S which indicates an error. On the other hand, if all  $Q^i$ 's produce the same noncode output (0,0), this results in a noncode output (0,0) in S that indicates an error. Thus, the application of a code in  $E_{2i-1}$  can detect not only the s/1 fault(s) at the output(s) of  $H^i$ ,  $Q^i$ , and/or S, but also the s/0 faults at the output(s) of  $G^i$ ,  $H^i$ ,  $Q^i$ , and/or S. Finally, the s/1 faults at  $g^i$ 's can be detected by applying a code in  $E_{2u-1}$ . When this code is applied to Circuit CH, all checkers produce the same noncode output (1,1), except that  $H^f$  generates a code output. Since  $g^r = 0$ , for r < u, and  $g^u = 1$  for fault-free circuit, the s/1 faulty  $g^i$  will force  $Q^i$  to produce a noncode output (1,1). Thus, Circuit CH is self-testing for all unidirectional errors.  $\blacklozenge$

#### **Lemma 3.5:** Circuit CH is *code-disjoint*.

**Proof:** When a code in subset E<sub>2i-1</sub> is applied to Circuit CH, the code input produces a

code output in Block S, i.e., all code inputs produce all code outputs. Consider a noncode, without loss of generality, consisting of  $J_q^*$  and  $P_r^*$ , where  $r \neq q$ . When the noncode input is applied to Circuit CH, by Lemma 3.1, the checker  $H^i$  produces a noncode (0,0), for i > q, or (1,1), for i < q. Since  $g^i = 0$ , for i > r, and  $g^r = 1$ , a noncode output (1,1) is produced in  $Q^r$ , if r > q, and further generates a noncode output in Block S. On the other hand, if r < q, all outputs in Block Q are (0,0)'s and result in a noncode output (0,0) in Block S. This concludes that the noncode inputs produce the noncode outputs.  $\bullet$

Proof of Theorem 3.1 Based on Lemmas 3.4 and 3.5, Circuit CH is a STC checker.

#### 3.1.2 PARTITIONING AND FOLDING SCHEME

The basic concept behind the *Berger code* partitioning scheme is that the LSB of the check part is grouped with the information part to reduce the number of checkers used in a STC design. This section presents an alternative structure that further reduces the number of checkers. We first consider the MLB code with  $I = 2^K - 1$ . The same concept can be extended for  $I = 2^K - 2$  and  $2^{K-1}$ .

## A. B(I,K) with $I = 2^{K} - 1$

As defined in Table 2.1(b),  $E_t$ , t = 1, 3, 5, and 7, is a subset of B(I,K) that replaces the adjacent pair of subset  $D_t$  and  $D_{t+1}$  in Table 2.1(a). In general, a B(I,K) is composed of subsets  $E_{2t-1}$ 's,  $1 \le t \le u$ . Note that  $N_1(J_t) = t$  and  $N_0(J_t) = 2u - t$ .

**Definition 3.1:** Let  $E_s$  and  $E_t$  be two subsets of B(I,K), the pair of  $E_s$  and  $E_t$  is *dual* if and only if the bit-complement of any codeword in  $E_s$  is a codeword in  $E_t$  and vice versa. Thus, we say that  $\overline{E}_s = E_t$  and  $\overline{E}_t = E_s$ .

ar

L P

ÇO

im

E<sub>2</sub>

coi pai

car

respe

x<sub>MS</sub>

a bit

Consider the MLB codes B(I,K) with  $I=2^K-1$ , i.e.,  $u=2^{K-1}$ . Let  $E_m$  and  $E_{2u-m}$  be any two subsets of B(I,K). Unless otherwise stated, it is assumed that m < u.

**Lemma 3.6:** The pair of subsets  $E_m$  and  $E_{2u-m}$  is dual.

**Proof:** For any codeword  $c_m$  in  $E_m$ ,  $N_1(c_m) = m$  and  $N_0(c_m) = 2u - m$ . Let  $c_p$  be the bit-complement of  $c_m$ , then we have  $N_1(c_p) = N_0(c_m) = 2u - m$  and  $N_0(c_p) = N_1(c_m) = m$ . This implies that  $c_p$  is a codeword in  $E_{2u-m}$ . Similarly, the complement of any codeword in  $E_{2u-m}$  is a codeword in  $E_{2u-m}$  is dual.  $\blacklozenge$

Since the subset  $J_1^*$  in Table 2.1(b) is a collection of 1-out-of-8 codewords and  $J_7^*$  consists of all 7-out-of-8 codewords, the pair of subsets  $E_1$  and  $E_7$  is dual; Similarly, the pair of  $E_3$  and  $E_5$  is also dual. Without loss of generality, subsets  $E_5$  and  $E_7$  in Table 2.1(b) can be re-written as shown in Table 3.1.

Table 3.1: Subsets of B(7.3).

| Subset         | expanded information part x <sub>1</sub> x <sub>2</sub> x <sub>3</sub> x <sub>4</sub> x <sub>5</sub> x <sub>6</sub> x <sub>7</sub> x <sub>10</sub> | reduced<br>check part<br>x <sub>8</sub> x <sub>9</sub> | partitioning            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------|

| E <sub>5</sub> | 0 0 0 1 1 1 1 1                                                                                                                                    | 0 1                                                    | C <sub>5/8</sub> ×(0 1) |

| E <sub>7</sub> | 0 1 1 1 1 1 1 1                                                                                                                                    | 00                                                     | C <sub>7/8</sub> ×(0 0) |

Let  $J_t^*$  and  $P_t^*$  be the expanded information part and the reduced check part of  $E_t$ , respectively, and  $x_{MSB(t)}$  denotes the MSB of  $P_t^*$ . It is obvious that  $x_{MSB(t)} = 1$  and  $x_{MSB(2u-t)} = 0$ , if t < u; and  $x_{MSB(t)} = 0$  and  $x_{MSB(2u-t)} = 1$ , if t > u. Let A be a set and x be a bit, then we define the set  $A \oplus x = \{y \mid y = z \oplus x, \text{ for all } z \in A\}$ .

**Lemma 3.7:** If  $F_t = E_{2u-t} \oplus x_{MSB(t)}$ , then  $F_t = F_{2u-t}$ .

**Proof:** For t < u, since  $x_{MSB(t)} = 1$  and  $x_{MSB(2u-t)} = 0$ , we have  $F_{2u-t} = E_t \oplus x_{MSB(2u-t)} = E_t$  and  $F_t = E_{2u-t} \oplus x_{MSB(t)} = \overline{E}_{2u-t} = E_t$ , i.e.,  $F_{2u-t} = F_t$ . On the other hand, for t > u, since  $x_{MSB(2u-t)} = 1$  and  $x_{MSB(t)} = 0$ , hence,  $F_t = E_{2u-t}$  and  $F_{2u-t} = \overline{E}_t = E_{2u-t}$ , i.e.,  $F_t = F_{2u-t}$ .

Since, by Lemma 3.6,  $E_{2u-t} = \overline{E}_t$ , the condition in Lemma 3.7 can be written as

$$F_{t} = E_{2u-t} \oplus x_{MSB(t)} = \overline{E}_{t} \oplus x_{MSB(t)} = \overline{E}_{t} \oplus x_{MSB(t)}$$

(3.1)

which is a XNOR (exclusive-NOR) function.

**Theorem 3.2:** If m < u, then any unidirectional errors in a subset  $Z_m = \overline{E_m \oplus x_{MSB(m)}}$  can be detected by the  $C_{m/(l+1)}$  checker.

**Proof:** Since m < u,  $x_{MSB(m)} = 1$  implies  $Z_m = \overline{E}_m$ . By Lemma 3.6,  $Z_m = E_{2u-m}$ . Obviously, the checker  $C_{(2u-m)/(I+1)}$  detects all unidirectional errors in  $E_{2u-m}$ , or  $Z_m$ . Similarly, for (b),  $Z_m = E_m$ , any unidirectional errors in  $Z_m$  can be detected by  $C_{m/(I+1)}$  checker.  $\blacklozenge$

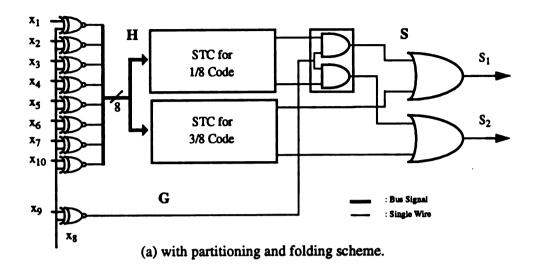

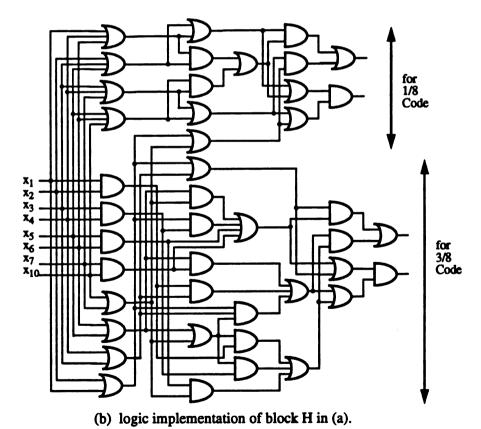

Table 3.2 (a) is the same as Table 2.1 (b) except  $E_5$  and  $E_7$  are reordered, where  $x_{MSB(1)} = x_{MSB(3)} = 1$  and  $x_{MSB(5)} = x_{MSB(7)} = 0$ . By Lemma 3.7,  $F_1 = F_7$  and  $F_3 = F_5$ . As illustrated in Table 3.2 (c),  $Z_1$  replaces the pair of identical subsets  $F_1$  and  $F_7$ , while  $Z_3$  substitutes the pair of  $F_3$  and  $F_5$ . Tables 3.2(c) and 3.2(d) list two possible partitions. By Theorem 3.2, the code B(7,3) can be written as

$$B(7,3) = C_{1/8} \times (1) \cup C_{3/8} \times (0)$$

(3.2)

The number of m/n checkers in the STC design for B(7,3) is reduced from four to two.

Table 3.2: B(7.3) with Partitioning Scheme.

(a)

| Subset         | Expanded information part x <sub>1</sub> x <sub>2</sub> x <sub>3</sub> x <sub>4</sub> x <sub>5</sub> x <sub>6</sub> x <sub>7</sub> x <sub>10</sub> | Reduce<br>check<br>part<br>x8x9 | partitioning             |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------|

| E <sub>1</sub> | 00000001                                                                                                                                           | 1 1                             | $C_{1/8} \times (1 \ 1)$ |

| E <sub>3</sub> | 00000111                                                                                                                                           | 10                              | C <sub>3/8</sub> ×(1 0)  |

| E <sub>5</sub> | 11111000                                                                                                                                           | 0 1                             | C <sub>5/8</sub> ×(0 1)  |

| E <sub>7</sub> | 1111110                                                                                                                                            | 00                              | C <sub>7/8</sub> ×(0 0)  |

(b)

| Subset         | Expanded information part x <sub>1</sub> x <sub>2</sub> x <sub>3</sub> x <sub>4</sub> x <sub>5</sub> x <sub>6</sub> x <sub>7</sub> x <sub>10</sub> | Reduce<br>check<br>part<br>x <sub>9</sub> | x <sub>MSB</sub> |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------|

| F <sub>1</sub> | 00000001                                                                                                                                           | 1                                         | 1                |

| F <sub>7</sub> | 11111110                                                                                                                                           | 0                                         | 0                |

| F <sub>3</sub> | 00000111                                                                                                                                           | 0                                         | 1                |

| F <sub>5</sub> | 1 1 1 1 1 0 0 0                                                                                                                                    | 1                                         | 0                |

(c)

| Subset                | Expanded information part $x_1x_2x_3x_4x_5x_6x_7x_{10}$ | Reduce<br>check<br>part<br>x <sub>9</sub> | partitioning          |