This is to certify that the

dissertation entitled

VLSI Smart Logic Modeling and Design For Optimum Chip Feature Characterization

presented by

Hsien-Hui Tseng

has been accepted towards fulfillment of the requirements for

Ph.D. degree in <u>Electrical</u> Engineering

Lajor professor

Date  $\frac{6}{30/93}$

# LIBRARY Michigan State University

PLACE IN RETURN BOX to remove this checkout from your record.

TO AVOID FINES return on or before date due.

| O AVOID FINES return | on or below sum |                         |

|----------------------|-----------------|-------------------------|

| DATE DUE             | DATE DUE        | DATE DUE                |

| FEB 1 0 2001         |                 |                         |

|                      |                 |                         |

|                      |                 |                         |

|                      |                 |                         |

|                      |                 |                         |

|                      |                 |                         |

|                      |                 |                         |

|                      |                 | Opportunity Institution |

MSU Is An Affirmative Action/Equal Opportunity Institution c:/circ/datedus.pm3-p.1

## VLSI SMART LOGIC MODELING AND DESIGN FOR OPTIMUM CHIP FEATURE CHARACTERIZATION

By Hsien-Hui Tseng

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

**DOCTOR OF PHILOSOPHY**

Department of Electrical Engineering

#### **ABSTRACT**

## VLSI SMART LOGIC MODELING AND DESIGN FOR OPTIMUM CHIP FEATURE CHARACTERIZATION

#### By

#### Hsien-Hui Tseng

Because the transportation and handling of agricultural products can result in various degrees of damage due to impacts, a 38 mm (1.5 in.) diameter self-contained Instrumented Sphere (IS) was designed to record the impacts it experiences while being handled with like-sized commodities (plums, tomatoes, peaches, strawberries). Compared with the 89 mm (3.5 in.) diameter sphere previously reported by Zapp et al., 1990, this miniaturized unit contains a composite smart logic chip with the same 32K of memory, approximately 1/12 the volume, smaller batteries, and a smaller triaxial accelerometer.

Spatial optimization was performed by computer to investigate the practical minimum volume configuration that can be realized using commercially available components. The saving in power consumption for the smart logic configuration was also investigated. The combination of reduced power, small circuit elements and optimum packaging produce a feasible sphere of 38 mm (1.5 in.) diameter.

The overall objectives accomplished in this research report are: 1) development of a general design rule for a n-Dimensional (n-D) data acquisition system with m restrictions (m or more of the input signals from each of the n independent sources are above some threshold for signal acceptance); 2) design of a 3-D smart logic data acquisition system with one restriction (This latter system replaces a  $\mu$ -P circuit and other supporting logic of an operational data acquisition system. Essentially a single chip data acquisition system replaces a circuit board system of 5 chips); 3) demonstration of a VTI smart logic simulation to verify the single chip performance, and; 4) assessment of the size, power consumption, and cost compared to the operational  $\mu$ -P based system.

Copyright by

Hsien-Hui Tseng

1993

To my family

#### **ACKNOWLEDGMENTS**

I would like to express my greatful appreciation and gratitude to the members of my Dissertation Committee: Dr. H. Roland Zapp, Dr. Mohammad Aslam, Dr. Galen K. Brown, Dr. Bong Ho, and Dr. David Yen. Their constructive comments and guidance were invaluable to the completion of this thesis.

A special appreciation goes to Dr. H. Roland Zapp and Dr. Mohammad Aslam, my advisors, for serving as chairs of my dissertation committee. Their encouragement, advice, support and friendship helped each step along the way and their excellent dedication provided continuous inspiration.

I wish to acknowledge Dr. Galen K. Brown for providing an assistantship during the course of this project.

I also wish to express my gratitude to Dr. Paul R. Armstrong for his assistance.

At last I wish to express my love and gratitude to my family for their support.

#### TABLE OF CONTENTS

| LIST OF TABLES                                                    | ix       |

|-------------------------------------------------------------------|----------|

| LIST OF FIGURES                                                   | <b>x</b> |

| 1. INTRODUCTION                                                   | 1        |

| 2. BACKGROUND                                                     | 4        |

| 2.1 Historical Perspective                                        | 4        |

| 2.2 Previous μ-P Based Data Acquisition Units                     | 8        |

| 2.3 Criteria for 3-D Data Acquisition                             | 10       |

| 2.4 VTI and CMOS VLSI Design Considerations                       | 11       |

| 3. SYSTEM DESIGN STRATEGIES                                       | 13       |

| 3.1 A Review of the μ-P Based IS                                  | 13       |

| 3.2 Smaller Size and Reduced Power Consumption by Smart Logic     | 14       |

| 3.2.1 General Design Rules for n-D Data Acquisition with m        |          |

| Restrictions                                                      | 14       |

| 3.2.1.1 Clock Design                                              | 15       |

| 3.2.1.2 Binary Code Development                                   | 18       |

| 3.2.1.3 Signal Latching                                           | 18       |

| 3.2.1.4 Comparison of Input Signal with a Threshold               | 18       |

| 3.2.1.5 Memory Address Counting                                   | 18       |

| 3.2.2 Flow Chart for System Operation                             | 25       |

| 3.3 The Algorithm                                                 | 26       |

| 3.4 Special Case (Clock Count Per Burst Less Than Data Dimension) | 28       |

| 3.5 Application (Design of a Smart Logic 3-D Data Acquisition System      |     |

|---------------------------------------------------------------------------|-----|

| with One Restriction)                                                     | 28  |

| 3.5.1 CSC Design                                                          | 28  |

| 3.5.2 CTB Design                                                          | 30  |

| 3.5.3 LATCH Design                                                        | 30  |

| 3.5.4 COMP Design                                                         | 44  |

| 3.5.5 COUNTER Design                                                      | 44  |

| 3.6 Software Program                                                      | 51  |

| 4. VARIATION IN SIZE, POWER AND HEAT DISSIPATION WITH                     |     |

| SPECIFICATION REQUIREMENTS                                                | 53  |

| 4.1 Estimation of Size, Power and Heat Dissipation for a μ-P Based IS     | 53  |

| 4.1.1 Estimation of Power Dissipation in a 3.5 Inch μ-P Based IS          | 53  |

| 4.1.2 Estimation of Power Dissipation in a 2.5 Inch μ-P Based IS          | 54  |

| 4.1.3 Estimation of Power Dissipation in a 2.0 Inch $\mu$ -P Based IS     |     |

| Multichip Housing                                                         | 55  |

| 4.2 Estimation of Size, Power and Heat Dissipation for a Smart Logic Chip |     |

| Based IS                                                                  | 55  |

| 4.2.1 Estimation of the Size                                              | 56  |

| 4.2.2 Estimation of the Power and Heat Dissipation                        | 57  |

| 4.3 Ultimate Size, Power and Heat Sink Consideration                      | 58  |

| 4.4 Variation of Power and Size vs Specification Changes                  | 60  |

| 5. SIMULATION RESULTS                                                     | 79  |

| 5.1 Architecture for IS Smart Logic Chip                                  | 80  |

| 5.2 Simulation Results                                                    | 80  |

| 5.3 Discussion                                                            | 83  |

| 6. CONCLUSIONS AND DIRECTIONS FOR FUTURE WORK                             | 95  |

|                                                                           | 0.5 |

| 6.2 Directions for Future Work | 96  |

|--------------------------------|-----|

| APPENDICES                     | 97  |

| RIRLIOGRAPHY                   | 125 |

#### LIST OF TABLES

| Table 1 - Software program for synthesizing the n-D with m restrictions data                  |

|-----------------------------------------------------------------------------------------------|

| acquisition system52                                                                          |

| Table 2 - Maximun μ-P current consumption for different models from two                       |

| manufacturers62                                                                               |

| Table 3 - Current and power consumption for the conventional μ-P circuit                      |

| (89 mm or 3.5 in. IS) and the composite smart logic chip                                      |

| Table 4 - IS dimensions for different geometrical configurations64                            |

| Table 5 - CMOS current consumption values for various quad gates at T <sub>A</sub> =25 °C for |

| different manufacturers65                                                                     |

| Table 6 - Minimum IS dimensions for different geometrical configurations66                    |

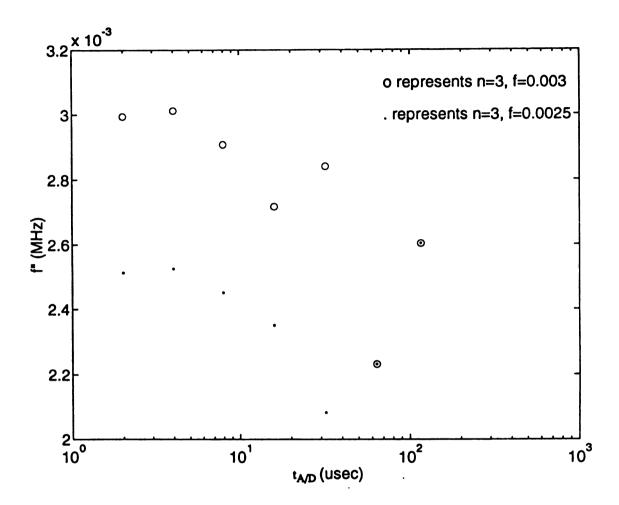

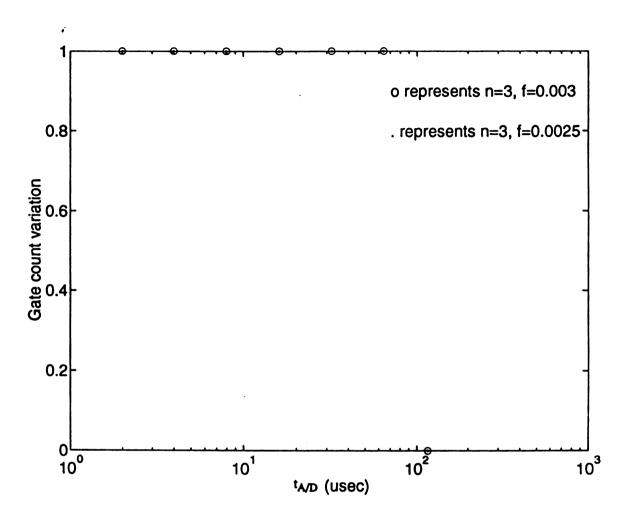

| Table 7.a - Gate count variation vs different specifications relative to $t_{A/D} = 116$      |

| µsec and maintaining $t_1$ =0.125 µsec, f=0.003 MHz, and n=3 conditions67                     |

| Table 7.b - Gate count variation vs different specifications relative to $t_{A/D} = 116$      |

| $μsec$ keeping $t_1$ =0.125 $μsec$ , $f$ =0.0025 MHz, and $n$ =3 fixed68                      |

| Table 8 - Power variation vs different specifications relative to t <sub>A/D</sub> =116 μsec  |

| maintaining t <sub>1</sub> =0.125 μsec, f=0.003 MHz, and n=3 fixed69                          |

#### **LIST OF TABLES**

| Table 1 - Software program for synthesizing the n-D with m restrictions data                  |           |

|-----------------------------------------------------------------------------------------------|-----------|

| acquisition system                                                                            | 52        |

| Table 2 - Maximun $\mu$ -P current consumption for different models from two                  |           |

| manufacturers                                                                                 | 62        |

| Table 3 - Current and power consumption for the conventional $\mu$ -P circuit                 |           |

| (89 mm or 3.5 in. IS) and the composite smart logic chip                                      | 63        |

| Table 4 - IS dimensions for different geometrical configurations                              | 64        |

| Table 5 - CMOS current consumption values for various quad gates at T <sub>A</sub> =25 °C for |           |

| different manufacturers                                                                       | 65        |

| Table 6 - Minimum IS dimensions for different geometrical configurations                      | 66        |

| Table 7.a - Gate count variation vs different specifications relative to $t_{A/D} = 116$      |           |

| μsec and maintaining $t_1$ =0.125 μsec, $f$ =0.003 MHz, and $n$ =3 conditions                 | 67        |

| Table 7.b - Gate count variation vs different specifications relative to $t_{A/D} = 116$      |           |

| μsec keeping t <sub>1</sub> =0.125 μsec, f=0.0025 MHz, and n=3 fixed                          | 58        |

| Table 8 - Power variation vs different specifications relative to $t_{A/D} = 116 \mu sec$     |           |

| maintaining t <sub>1</sub> =0.125 μsec, f=0.003 MHz, and n=3 fixed                            | <b>59</b> |

#### **LIST OF FIGURES**

| Figure 1 - A t μsec clock with f MHz frequency forms the waveform SWC              | 20 |

|------------------------------------------------------------------------------------|----|

| Figure 2 - Block diagram for the n-D data acquisition system with m restrictions   | 21 |

| Figure 3 - The detailed circuit diagram for the CSC (counter & switch clock)       |    |

| generator for n=3                                                                  | 22 |

| Figure 4 - The waveform SWC, with 3 pulses of 2 µsec at a 0.003 MHz                |    |

| repetition frequency                                                               | 23 |

| Figure 5 - The detailed circuit diagram for the CTB (clock-to-binary) generator    |    |

| for n=3                                                                            | 24 |

| Figure 6 - A t µsec clock with f MHz frequency forms the waveform SWC              |    |

| (for the special case n=4)                                                         | 32 |

| Figure 7 - The schematic circuit diagram for the CSC (counter & switch clock)      |    |

| generator for the special case n=3                                                 | 33 |

| Figure 8 - The detailed circuit diagram for the CSC (counter & switch clock)       |    |

| generator for the special case n=3                                                 | 34 |

| Figure 9 - The simulation results of the CSC (counter & switch clock)              |    |

| generator circuit for the special case n=3                                         | 35 |

| Figure 10 - The waveform SWC, with 3 pulses of 128 µsec at a 0.002604 MHz          |    |

| repetition frequency for the specific smart logic case                             | 37 |

| Figure 11 - The simulation results of the CTB (clock-to-binary) generator          |    |

| circuit for n=3                                                                    | 38 |

| Figure 12 - The simulation results for the latch circuit for the special case n=3, |    |

| m=1, t'=125 nsec, $t_{A/D}$ =116 µsec, f=0.003 MHz39                                 |

|--------------------------------------------------------------------------------------|

| Figure 13 - The detailed circuit diagram for a two stage latch with n=3, m=142       |

| Figure 14 - One impact force which contains five sampled data43                      |

| Figure 15 - The simulation results for an 8 bit comparator with predetermined        |

| thresholds45                                                                         |

| Figure 16 - The detailed circuit diagram for an 8 bit comparator with                |

| predetermined thresholds46                                                           |

| Figure 17 - The simulation results for a 16 bit counter which is divided into        |

| four parts47                                                                         |

| Figure 18 - The detailed circuit diagram for a 16 bit counter49                      |

| Figure 19 - Block diagram for the smart logic chip50                                 |

| Figure 20 - Patterned silicon substrate to support the SLIC, RAM, A/D                |

| and Op Amp dice in order to form the composite smart logic chip70                    |

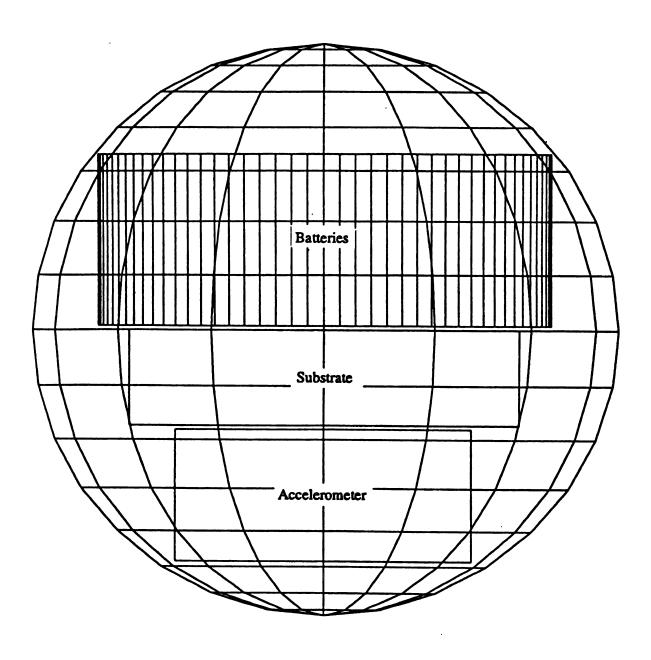

| Figure 21 - The front view of the typical configuration for the sphere of 30 mm      |

| (1.18 in.) diameter. Not included: rigid foam, beeswax, and epoxy71                  |

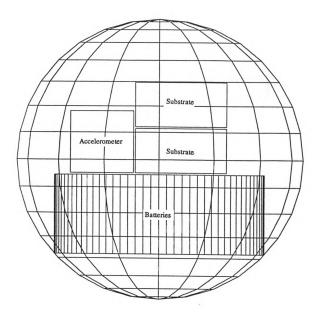

| Figure 22 - The side view of the typical configuration for the sphere of 31.62 mm    |

| (1.25 in.) diameter. Not included: rigid foam, beeswax, and epoxy72                  |

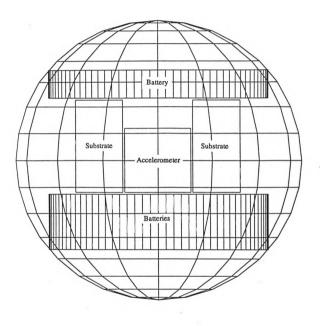

| Figure 23 - The front view of the typical configuration for the sphere of 30.24 mm   |

| (1.19 in.) diameter. Not included: rigid foam, beeswax, and epoxy73                  |

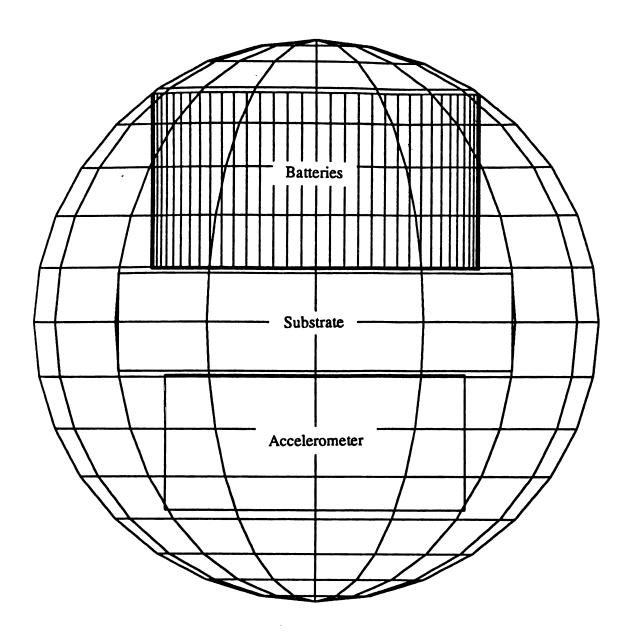

| Figure 24 - The front view of the typical configuration for the sphere of 28.72 mm   |

| (1.13 in.) diameter. Not included: rigid foam, beeswax, and epoxy74                  |

| Figure 25 - The front view of the typical configuration for the sphere of 24.58 mm   |

| (0.97 in.) diameter. Not included: rigid foam, beeswax, and epoxy75                  |

| Figure 26 - The front view of the typical configuration for the sphere of 28.28 mm   |

| (1.12 in.) diameter. Not included: rigid foam, beeswax, and epoxy76                  |

| Figure 27 - f vs different specifications as given in Table 7.a77                    |

| Figure 28 - Gate count variation vs different specifications as given in Table 7.b78 |

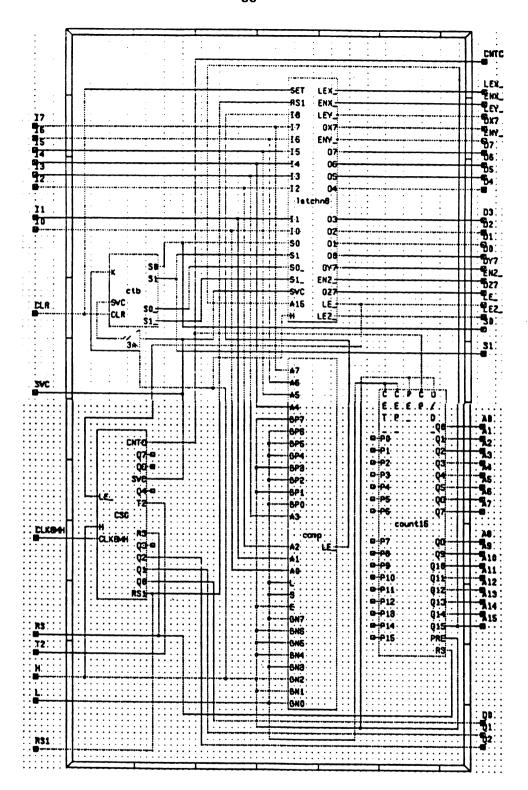

| Figure 29.a - The detailed circuit diagram for the data acquisition system  |    |

|-----------------------------------------------------------------------------|----|

| with n=3, m=1                                                               | 85 |

| Figure 29.b - The detailed circuit diagram for the smart logic chip         |    |

| (special case of n=3, m=1)                                                  | 86 |

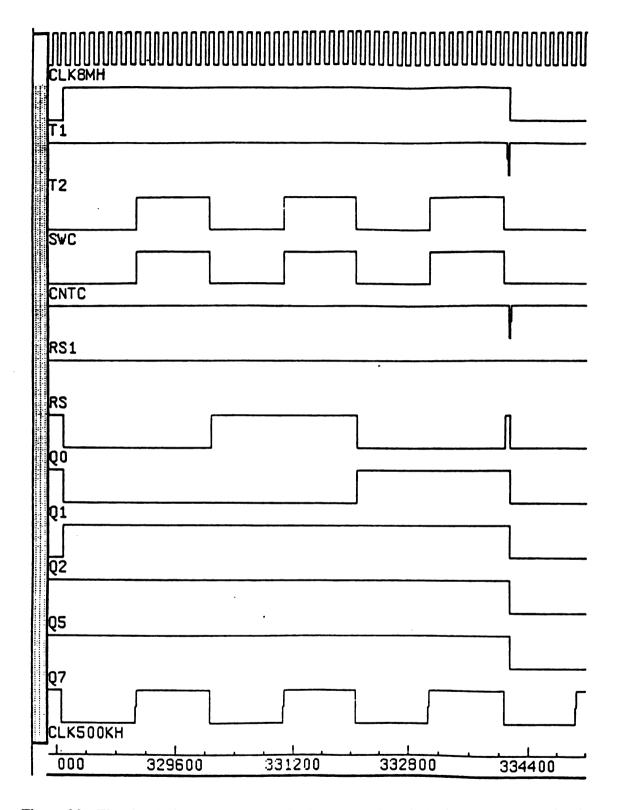

| Figure 30 - The simulation results of the CSC (counter & switch clock)      |    |

| generator circuit for n=3                                                   | 87 |

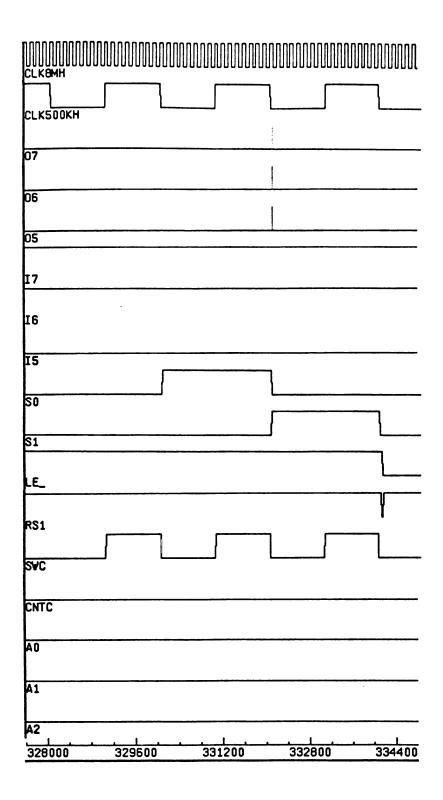

| Figure 31 - The simulation results of the data acquisition system with n=3, |    |

| m=1, t'=125 nsec, t=2 μsec, f=0.003 MHz                                     | 88 |

| Figure 32 - The typical simulation results of the smart logic chip          |    |

| (special case of n=3, m=1)                                                  | 91 |

| Figure 33 - Two impact forces which contain ten sampled data                | 94 |

#### **CHAPTER 1**

#### INTRODUCTION

Agricultural products, sensitive electronic equipment, glass and bottled goods are among the many items which can be damaged by impact or shock. To identify the sources of damage, instrumentation mounted to the item or substitution of the item by an electronic clone have been proposed. For example, an Instrumented Sphere (IS) accompanying apples during mechanical handling operations has provided the monitoring required to identify locations and magnitudes of significant impacts which cause bruise damage to apples [1],[2]. This IS [3] had a diameter of 89 mm (3.5 in.), which was adequate for measurements with apples, potatoes, cucumbers and other medium sized produce.

The 89 mm (3.5 in.) IS has been very useful for identifying damage causes; impact locations and impact magnitudes. A smaller IS is essential to accomplish similar results in smaller size produce such as strawberries, plums, mushrooms, peaches, eggs, etc.. One method to achieve a size reduction was to re-package the electronics in a 63.5 mm (2.5 in.) diameter IS [4], probably the smallest size possible without the use of very large scale integration (VLSI). A second approach is to develop a multichip housing [5] which replaces four standard integrated circuit (IC) chip with four dice mounted on a single substrate with pinouts compatible to those of the microprocessor ( $\mu$ -P). A piggyback sandwich type configuration results which has dimensions of just the  $\mu$ -P. Operational power reduction is necessary to accommodate smaller batteries for the much smaller size IS. Heat sinking must be considered because of the high circuit density in the reduced size. These conflicting

requirements suggest a CMOS smart logic VLSI design [6],[7] to achieve the simultaneous objectives of small size and low power consumption.

A CMOS smart logic chip approach should produce the smallest size IS. The approach to chip miniaturization is to eliminate the  $\mu$ -P and replace it with a "smart logic" low power consuming chip. The motivation here is to simplify the electronics by using a smart logic integrated circuit (SLIC) for performing the system operation instead of the  $\mu$ -P since the  $\mu$ -P is highly underutilized in the presently available IS. Thus, by developing dedicated logic, which should be compatible with VLSI technology, the size [8],[9], power consumption [9]~[12] and cost [13] of the miniaturized IS is substantially reduced. In the previous IS designs, the  $\mu$ -P was the major power consumer. A factor of two in power reduction is realized using smart logic without a  $\mu$ -P.

A smaller IS which consumes less power than the previous 89 mm (3.5 in.) diameter IS and present 63.5 mm (2.5 in.) diameter is a design objective. A final size of less than 38 mm (1.5 in.) diameter, or about 1/12 the volume of the earlier 89 mm (3.5 in.) model, results. The miniature IS uses a smaller triaxial accelerometer, a SLIC, operational amplifier (Op Amp), analog-to-digital conversion (A/D) and the same 32K of external random access memory (RAM). The final design eliminates the circuit board by incorporating the circuit in a single IC package which contains four IC dice. These dice are mounted on a patterned silicon substrate that fits in the package. After bonding the dice [14]~[17], the package is sealed using standard IC package processing. The completed electronic package is encased in rigid foam and cast in beeswax to provide structural hardness for the IS. After adequate testing, an epoxy casing will be utilized. An optimization routine shows that a 38 mm (1.5 in.) diameter is feasible using commercially available elements. A number of element packaging arrangements were configured with the optimization routine. The results of these optimization configurations are presented. The power and heat dissipation analysis for the smart logic configuration is included.

Chapter 2 gives a review of some researchers' efforts in detecting and explaining

bruising in fruit during harvesting and handling. Criteria for 3-Dimension (3-D) data acquisition, VTI and CMOS VLSI design considerations and previous μ-P based data acquisition units are also addressed in that Chapter. Chapter 3 presents system design strategies which include system operation, general design rules and algorithms for n-D data acquisition with m restrictions, special cases and applications and the software listing. Chapter 4 provides the analysis of size, power and heat dissipation for the μ-P based IS, the composite smart logic chip based IS and the absolute size limit for an IS. Power and size are substantially reduced from the commercially available unit and heat dissipation represents no problem for size reduction related to multichip housing. The variation of power and size vs specification changes is also provided. Chapter 5 presents simulation results and discussion. Chapter 6 discusses the general results and conclusions and provides some ideas for future studies.

#### **CHAPTER 2**

#### **BACKGROUND**

#### 2.1 Historical Perspective

During the past two decades many researchers tried to detect and explain bruising in fruit during harvesting and handling. Rider [18], developed a pseudo-fruit to measure the forces involved in the collisions and to relate these forces to the generation of bruises. In this pseudo-fruit, three separate accelerometers were mounted in a 57-mm diameter steel shell covered with 9.5 mm of Ensolite material. This pseudo-fruit was capable of recording the maximum acceleration and the time duration of an impact by using cables to transfer acceleration signals to a chart recorder. Rider showed that acceleration can be used to predict internal shear stress, if the modulus of elasticity and the radius of the surface impacted by the pseudo-fruit were known. Although physical properties of the Rider pseudo-fruit were similar to those of a peach, the duration of impact did not agree with the values obtained from the Hertz theory. He attributed this to the "bottoming out" of the covering material at relatively high impact values. Rider et al. [19] also studied the pseudo-fruit's calibration and how it would correlate to bruise damage in fruit. The previous other researchers had showed that the probability that a peach will be bruised by impact can be related to the internal shear stress developed in the fruit, based upon the assumption that the fruit behaves elastically. So Rider calibrated the accelerometer outputs to the shear stress experienced by the pseudo-fruit. Thus the shear stresses experienced by the pseudo-fruit were supposed to correlate directly to bruise damage. All of Rider's formulas assumed perfectly elastic impacts. In order to test the mathematical relationships, a 76.2 mm (3.0 in.) diameter, 204 gm (0.45 lb) pseudo-fruit which contained a piezoelectric triaxial accelerometer was constructed. The small flexible coaxial cables were connected between this encased sensor and a tape recorder. The shell of the pseudofruit was a 1.52 mm (0.06 in.) thick 57.15 mm (2.25 in.) diameter steel sphere covered with a layer of 9.53 mm (3/8 in.) thick type AH Ensolite<sup>R</sup> over which three layers of 3M\* Fastbond-10<sup>R</sup> contact cement were applied. The accelerometer was rigidly mounted inside the shell. The unit had a coefficient of restitution of 0.42 when dropped 152.4 mm (6 in.) onto concrete. The modulus of elasticity of the pseudo-fruit, 489 kPa (71 psi), was determined both by measuring the area of contact during impact and by using a quasi-static compression test. In Rider's calibration procedure the only externally supplied variable. was the modulus of elasticity of the impacted surface. From the data, he only made use of the peak acceleration and impact duration. In order to make the theoretical calibration procedure correspond to experimental data however, the impact duration time had to be multiplied by an unexplained factor of 2 before being used in the calibration procedure.

Pullen and Diener [20] developed a low cost FET triaxial accelerometer. The advantages of this system were the vector summing capabilities, using long cables without cable noise or cross talk, high power gain and low impedance output. Three cables were required to transmit the impact data to a recorder. This accelerometer approach was subsequently duplicated by others in recent telemetry systems. Another approach was to use telemetry in a pseudo-fruit to transmit the variation in accelerations via a FM transmitter. The objective was to remove any sensing cables from the pseudo-fruit in order to enable the pseudo-fruit to simulate the free movement of a fruit.

O'Brien et al. [21] developed a telemetry system which contained three miniature and separate FM transmitters with antennas, one for each axis and a triaxial accelerometer. The accelerometer and electronics were enclosed in a 50.8 mm (2 in.) hollow fiber glass

sphere covered by 10.2 mm (0.4 in.) thick layer of resilient material. A standard FM receiver was used to pick up the pseudo-fruit signal and store this signal on a multi-channel analog tape recorder. Because of low transmitter power, the receiver's antenna had to be placed very close to the pseudo-fruit. The calibration accuracy was estimated to be ±5%. The pseudo-fruit was not sensitive to accelerations below 0.5 g (gravitational force), or to frequency response down to 2 Hz, because these were believed unimportant for bruise formation.

Aldred and Burch [22] developed an electronic shock-sensing device for detecting amplitudes and frequencies of acceleration of peaches during harvesting and handling. A microcomputer and an analog vector summing circuit were added to this impact detection system. This impact detection system still consisted of a sensing unit and receiving station. Instead of transmitting 3 channels of data, only one transmitter (for the resultant acceleration) was placed inside a 67 mm (2.64 in.) sphere for transmitting one channel of data. Data from the sensor were telemetered to a microcomputer, then processed, stored and retrieved later as a direct readout of maximum impact or as a curve on a strip chart recorder. Approximately 2 sec of data at a 1 kHz sampling rate were stored and processed for each impact. It was stated that additional experimentation was necessary to insure that the pseuso-fruit resembles a real fruit and to correlate output of the pseudo-fruit with the actual bruise. No attempts were made to calibrate the output of this system.

Jenkins and Humphries [23] developed a new technique to assess impact damage. They used a fluid filled bladder with slit valves to meter fluid flow during impact. This bladder was a hollow vinyl sphere (toy ball) approximately 76 mm (3 in.) in diameter with a 3 mm (0.12 in.) wall fitted with six equally spaced one-way slit valves. According to the relationship between water loss and impact velocity, this system resulted in good correlation between drop height on a hard surface and water loss. The only drawback was the lack of an automated recording system.

Halderson et al. [24] developed their first generation impact detection telemetry sys-

tem to predict impact bruises to potatoes. They used a triaxial accelerometer configuration with three miniature transmitters which operated in the commercial FM band and a three channel FM receiver. The unit operated up 30 m (100 ft.) from the receiver but was too directional. This research, however, lacked both a true calibration procedure and a field test performance analysis. Their second generation impact detection device had a single transmitter system with three subcarriers. The most efficient and non-directional antenna for the unit were two wire loops of approximately 6 cm (2.4 in.) diameter which oriented 90 degrees to each other. A special three channel FM telemetry receiver was used to receive the transmitted signal. During impact tests, the correlation of the enclosed accelerometer voltage with decorder voltage was slightly better than 80%. By 1986 Halderson et al. [25] had built and tested a third generation impact detection device. The main changes from his previous device were in the packaging. The new unit enclosed all of the electronics in a 40 mm x 40 mm x 57mm aluminum box. Three small LC antenna were mounted on the outside of the three perpendicular planes of the box. The aluminum box was molded in silicone (Dow Corning RTV-3110) to form a cylindrical package that was 100 mm (4 in.) in length and 84 mm (3.3 in.) in diameter, weighed 654 gm (1.44 lb), and had an overall specific gravity of 1.18. The device was tested under impact conditions by dropping a 1054 mm (41.5 in.) in length, 286.7 gm (0.63 lb) in weight metal rod, with a spherical hard rubber tip (36.5 mm (1.44 in.) in diameter), onto the device which was supported by a 75 mm (3 in.) thick foam pad with a force-deflection rate of 275 (gm/cm<sup>2</sup>)/cm (9.93 (lb/in.<sup>2</sup>)/in.). Ten replications of 0.2 J (1.9 x 10<sup>-4</sup> BTU) of energy were used for each axial direction. Coefficients of variation were 8.3%, 8.4% and 5.2% respectively for the X. Y and Z axes. The transmission distance was evaluated around a potato harvester, but no range distances were reported.

Anderson and Parks [26] developed two impact detection devices (two physical units) using a pressure sensor transducer in one and a single axis accelerometer in the other. The pressure version was packaged by mounting the electronic assembly inside a hollow rub-

ber ball which was then sealed, thus containing air at atmosphere pressure. The accelerometer version is built up by surrounding the electronic assembly with cushioning foam and an outer shell. Both devices used telemetry to transmit data to a receiver with an attached tape recorder. A two channel tape recorder was used so that data could be recorded on one channel and voice commentary on the other. Both devices used the same FM transmitter design and battery configuration which could operate for eight hours. The pressure version was calibrated by compressing it between two plates with a known force, while the accelerometer version was calibrated by dropping it from known heights. The acceleration data was used to generate an "equivalent drop height number". These devices were used to test potato handling equipment.

Kerr and Wilkie [27] described a triaxial accelerometer and telemetry system, as an automated data collection system, for use on a potato harvester to provide an immediate indication of damage. This unit included a computer on-board the harvester which stored the acceleration, temperature and other critical data for further analysis. No calibration, accuracy or performance results were discussed, however.

More recent work was performed by Siyami [28], Zapp and Armstrong [3], Sober [2] and Brown [1]. The strong continuing interest is due to the recent developments in VLSI design and implementation techniques and the continuing development of miniaturized accelerometers and batteries. The recent technical advances have also reduced the power consumption of most components.

#### 2.2 Previous µ-P Based Data Acquisition Units

The application of the  $\mu$ -P based system to data acquisition systems has been common.

Lowther et al. [29] designed a general purpose dual-microprocessor data acquisition system. The hardware allowed data capture at speeds of up to 600 kHz and the software provided the user with a simple but powerful interface for setting up test requirements. These requirements included a certain amount of real time control for retrieving and

examining the data. This system has been used to investigate the penetration of magnetic fields into nonlinear laminated media under transient and steady state conditions and also to study an electromagnetic suspension system and linear motor drive for advanced ground transportation research.

Hill et al. [30] developed a  $\mu$ -P based digital wattmeter which can measure power in the frequency range dc to 1 kHz with a full scale accuracy of better than 0.5%. First, the  $\mu$ -P measured the voltage waveform period and then computed the sampling interval and number of samples. The measurement of average power must be taken over an integer number of cycles. Second, it is necessary to multiply together the samples of the voltage and current waveforms, accumulate the products over the measurement period, and then divided by the number of samples. Finally, we can read out as a 4-digit display of the scaled average power.

Wallingford [31] designed a simple data acquisition scheme which was implemented on a 16-bit microcomputer. This system can simultaneously acquire and store the output of two independent 8-bit A/D at a 115 kHz rate with a 3 MHz clock. This high speed data acquisition is made possible by configuring the interface to respond to two separate non-flicting parallel processes. The simultaneous conversion of two A/D's made this data acquisition scheme well suited for FFT signal processing systems.

Sridharan [32] developed a synchronous multichannel (8-channel) data acquisition system by using a separate A/D converter for each channel. The synchronous sampling became very desirable when the data was required for system identification studies, or when fast data conversion of a large number of analog channels was involved. For a microcomputer clock period of 330 nsec, the program took only 93 µsec of CPU time to convert and store the results of 8 channels in RAM.

Adam [33] made a telemetric seismic data acquisition system which sampled transducers continuously but stored data only when a threshold was exceeded. This system consisted of remote encoding stations and data acquisition stations. Each remote station consisted of up to three seismic sensors operating at sampling rates of 60 samples/sec. The highest single sensor sampling rate was 240 samples/sec. If any of 24 possible encoder stations registered above the threshold for a predetermined time, all of the encoder stations were recorded. If all of the signals were below the threshold for a short period of time, recording was terminated. In order to make the threshold process immune to nonseismic disturbance such as rain and eliminate the need for threshold adjustments, it is necessary to divide the short term average by the long term average.

Ahrens et al. [34] developed a multi-channel microcontroller-based data acquisition unit for logging the activity of cattle on the range which was small enough to be carried by cattle without bothering them. The chewing and walking habits of the cattle were of primary interest to the researchers. Significant motion from these habits produced 5 volt pulses out of the sensor and conditioning circuits which could be sent to the microcontroller.

Negro [35] designed a low power  $\mu$ -P controlled data acquisition system which used nonvolatile bubble memory cartridges for mass data storage. The system was battery powered. By chosing magnetic bubble memory, the period of unattented operation in the field can increase from 2 weeks to about 2 months and improve reliability. The input voltage to the data acquisition system is derived from the output of a gamma-ray ionization chamber that uses a temperature-compensated electrometer, or other moderately high output transducer. CMOS technology and power switching techniques were used in this system achieving very low power consumption (less than 10 mW).

#### 2.3 Criteria for 3-D Data Acquisition

The need for data acquisition is very common in industrial applications. Some examples of user needs have already been introduced in Section 2.2. For a n-D data acquisition system, in order to save memory by recording only useful data, some restrictions or thresholds for data acceptance are predetermined. For example, in a 3-D data acquisition

system for measuring and storing impact accelerations along 3 orthogonal axis, a vector threshold or a single axis threshold can be set in order to efficiently utilize the available memory. The single axis restriction is more easily implemented than a vector restriction. The n-D and m restrictions on a data acquisition system means discarding n data components if less than m of these components are above some threshold where n $\geq$ m. For example, if n=4, and m=2, with each threshold=5, any 2 or more of the 4 dimensions which have absolute values above 5 results in storing all four components. If less than 2 components are above 5, all four components are discarded. The criteria for the 3-D and 1 restriction data acquisition system include the capability of recording and saving 3 data components if any 1 or more of these components are greater than some threshold, for instance  $\pm 10$  g acceleration. This algorithm can be realized as follows: if  $|x(n)| \geq 10$  or  $|y(n)| \geq 10$  or  $|z(n)| \geq 10$ , then output=x, y, z, otherwise, output=0, 0, 0. This provides a transfer function given by H(z)=1 when  $|x(n)| \geq 10$  or  $|y(n)| \geq 10$  or  $|z(n)| \geq 10$ , otherwise H(z)=0.

#### 2.4 VTI & CMOS VLSI Design Considerations

VTI is a comprehensive VLSI design technique [36]~[48] from VLSI Technology, Inc. It covers a broad range of chip design tasks, including behavioral modeling, schematic entry, simulation, symbolic layout, hand-crafted layout, analysis, and test description.

Complementary Metal Oxide Silicon (CMOS) technology has played an increasingly important role recently because of the very low power consumption by this design configuration. Two types of MOS field effect transistors (FET) are produced by this technology, an n-channel MOSFET (NMOS) and a p-channel MOSFET (PMOS). The NMOS transistor consists of n diffusion, polysilicon, metal and insulating layers, while the PMOS transistor consists of p diffusion and the remaining similar materials.

The CMOS inverter, which uses an NMOS transistor as the driver and a PMOS transistor as the load, is characterized by low power consumption in the quiescent state, since

one of the two series transistors is always off except during a switching transition from one logic level to the other. Since power dissipation is a concern for VLSI NMOS chips, CMOS is an attractive alternative for VLSI application. For this reason we use VTI tools, which include CMOS standard cells, to design the smart logic chip.

#### **CHAPTER 3**

#### SYSTEM DESIGN STRATEGIES

#### 3.1 A Review of the $\mu$ -P Based IS

The existing  $\mu$ -P based IS consists of one circuit board. The main electronic components consist of an 8-bit CMOS Motorola  $\mu$ -P (XC68HC11) which has an integral 8-channel A/D converter, 8K byte ROM (which stores the monitor program), and a RS232 serial communication port. The other electronic components include 32 K RAM, latch, multiplexer and Op Amp.

The analog signal flow originates from a triaxial piezoelectric accelerometer (Columbia model 512TX) and adjacent conditioning circuits. The conditioning circuits provide impedance matching, voltage range scaling and noise filtering before input to the 0-5 Vdc A/D on-board the  $\mu$ -P. The  $\mu$ -P provides a multiplexed 8-channel 8-bit A/D converter with sample and hold.

The IS power supply consists of a rechargable, 7.2 V NiCad battery (Eveready CH22) chosen because of its availability, reliability, cost and size. The charge capacity is about 80 mA-h. Voltage regulation to 5 Vdc is accomplished with a high efficiency low differential regulator from National Semiconductor (LM2931AZ5). When the IS is in operation the current drain is less than 14 mA, which corresponds to approximately 6 h of battery power. At lower sampling rates or in a "sleep" mode the current can be reduced substantially (down to 2 mA in the sleep mode).

The entire design is enclosed in a 89 mm (3.5 in.) diameter sphere cast in wax to reduce the construction interface problem.

## 3.2 Smaller Size and Reduced Power Consumption by Smart Logic

The application of digital electronics to data acquisition systems is common. A sophisticated  $\mu$ -P based data acquisition system for agricultural damage monitoring has been proposed and demonstrated. But the  $\mu$ -P occupies a relatively large volume and demands the most system power. Thus, a new design idea using smart logic without a  $\mu$ -P and other auxiliary components such as a latch and a multiplexer would be desirable. The new design concept should accommodate a number of desired features, such as small size and long operation time. The design incorporates a suitable clock, a selection algorithm to choose the correct analog signals, and a threshold filter. A memory address counting scheme to store desired digital data is also required. The absence of the  $\mu$ -P assures a reduction in power consumption by a factor of 2. However, without the  $\mu$ -P, the system will suffer some flexibility; for example, the sampling rates will not be changable, the data dimensions and thresholds can not be altered and the programability is lost. These features are not critical for a dedicated data acquisition device. Each new application will require custom designed acquisition features.

## 3.2.1 General Design Rules for n-D Data Acquisition with m Restrictions

A general data acquisition unit allowing n data lines and m restrictions is developed. This general design can be reduced to the specific case to be realized in hardware. The n-D and m restrictions means saving n data components if any m or more of these components are greater than some threshold where n≥m. For example, n=4, m=2, threshold=5, if

any 2 or more of the 4 components have absolute values greater than 5 all 4 data components are recorded otherwise these components are ignored. The design concept requires developing a suitable clock, latch and other auxiliary circuits to realize a low cost, low power consumption single chip data acquisition system. In order to get a suitable clock, as the specification requires, it is necessary to develop a clock design. After obtaining the desired clock, it is still necessary to choose the correct analog input signals for the A/D, so that the appropriate binary code development is necessary to multiplex the correct input signal. It is also necessary to threshold the signals from the A/D, to provide signal latching and to generate a comparison circuit with a threshold, to identify the desirable signals. Finally, we need a 16-bit counter for address counting of the memory. The design specification is divided into the following five main parts:

#### 3.2.1.1 Clock Design

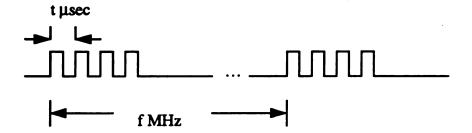

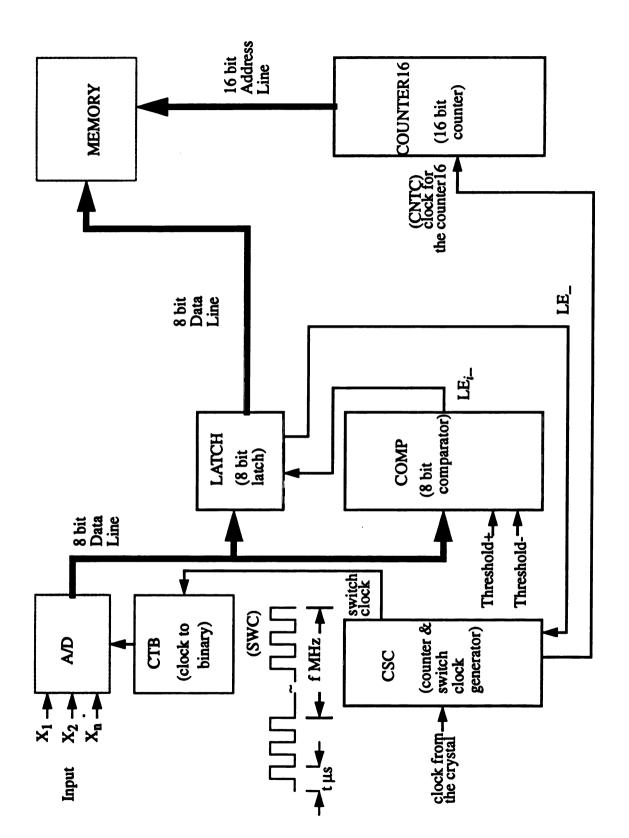

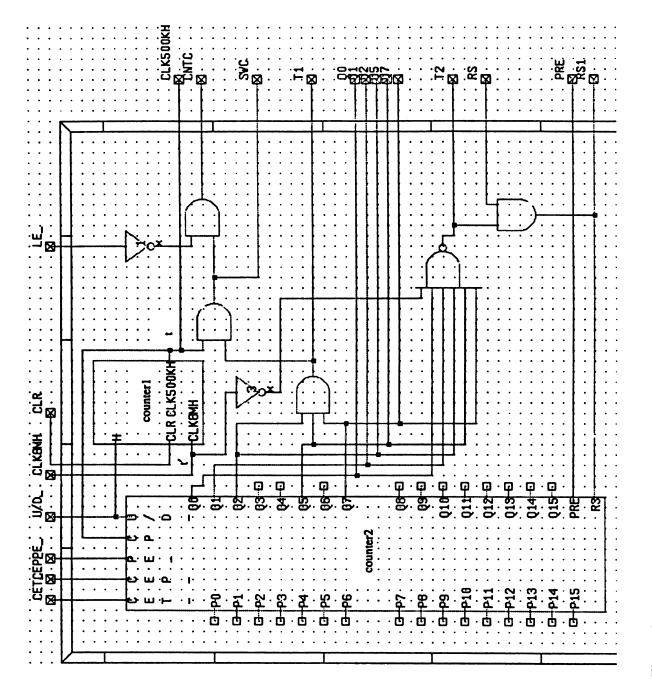

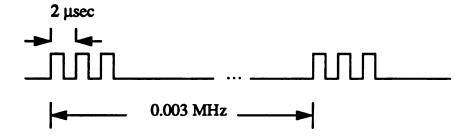

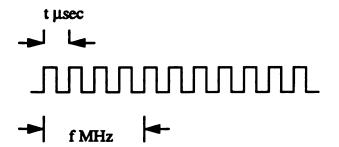

A CSC (Counter & Switch Clock generator) circuit can generate a t µsec clock burst (t represents the µsec duration of the clock pulses in the burst) with f MHz frequency (f represents the frequency of the burst), see Figure 1, for input to the CTB (clock-to-binary generator), as shown in Figure 2. In addition, the CSC generates a similar signal, when latch enable (LE\_) is low, for input to a 16-bit counter, identified as counter16.

Assuming that the crystal provides a clock period of t', and considering the A/D specifications, we can choose t such that

$$t/t'=p=2^q$$

where q is an integer. Thus we need a q bit counter, identified as counter1, which converts an input clock period t' from the crystal into an output period t, see Figure 3. Every f MHz cycle, we will keep n (data dimension) clock pulses of t µsec duration each and ignore the (1/tf) - n remaining clock pulses. We will call this waveform SWC (switch clock), as shown in Figures 1 and 2. The waveform SWC is generated as follows:

Express 1/tf (clock pulses count per sampling frequency) as a binary code d<sub>15</sub>d<sub>14</sub>

... $d_2d_1d_0$ . If 1/tf is not an integer, it should be rounded off to form an integer. Define  $f'=(1/t)\cdot(1/(d_{15}d_{14} \dots d_l d_{l-1}d_{l-2}\dots d_1d_0))$ , so that if 1/tf is an integer then f'=f, otherwise f'=f.

In our circuit design, we need the lower l bits of the sequence  $d_{15}d_{14} \dots d_l d_{l-1}d_{l-2} \dots d_1 d_0$  equal to n in order to get n clock pulses of t  $\mu$ sec duration per f MHz cycle as shown in Figure 1, where n is the data dimension and l=round-off of  $\log_2 n + 1$ .

Define  $s_{l-1}...s_0=n$  where n, the data dimension, equals the decimal equivalent to the binary sequence. If  $d_{l-1}d_{l-2}...d_1d_0$  equals  $s_{l-1}...s_0$ , let f, the real frequency in the SWC waveform, be equal to  $(1/t) \cdot (1/(d_{15}d_{14}...d_2d_1d_0))$  or f = f'. In the general case where  $d_{l-1}$   $d_{l-2}...d_1d_0$  does not equal  $s_{l-1}...s_0$ , we can replace  $d_{l-1}d_{l-2}...d_1d_0$  by  $s_{l-1}...s_0$  according to the following round off rules:

If

$$d_{l-1}d_{l-2}...d_1d_0 > s_{l-1}...s_0$$

,

or  $s_{l-1}...s_0 - d_{l-1}d_{l-2}...d_1d_0 \le 2^{l-1}$ , then  $f''=(1/t)\cdot(1/(d_{15}d_{14}...d_l s_{l-1}...s_0))$ ;

whereas, if  $s_{l-1}...s_0 - d_{l-1}d_{l-2}...d_1d_0 > 2^{l-1}$ , then  $f''=(1/t)\cdot(1/(d_{15}d_{14}...d_l s_{l-1}...s_0-2^l))$ .

The above rules will result in a minimun error of f'-f" where f" is the real frequency in the SWC waveform and f' is approximately equal to f. If f'=f and f'-f" gives zero, the actual frequency will be the ideal specified frequency.

In order to generate the SWC signal a second counter, identified as counter2, is necessary to accept clock t and output  $Q_{15}Q_{14}...Q_1Q_0$ , see Figure 3. From the  $Q_{15}Q_{14}...Q_l$  sequence choose those which have a value of 1 when the corresponding modified values (consistent with previously discussed requirements) of  $d_{15}d_{14}...d_l$  has a 1 and connect these Q values to an AND gate. After (1/f) - tn  $\mu$ sec the output of the AND gate, T1, will go high to enable the SWC. Similarly, from the  $Q_{15}Q_{14}...Q_1Q_0$  sequence choose those which have a value of 1 when the corresponding modified values of  $d_{15}d_{14}...d_2d_1d_0$  has a 1 and connect these lines to a NAND gate. For this latter case, we need to add an extra t' to the NAND gate input to avoid a transient spike. After 1/f  $\mu$ sec the output of the NAND gate, T2, goes low, which sends a low reset, RS1, to counter2 to reset  $Q_{15}Q_{14}...Q_1Q_0$ .

This allows T1 to go low, so that the total high time is tn. The resulting T1 and t generate the SWC used in the CTB. From SWC and LE\_, we can get CNTC (counter clock) for counter addressing. See Figure 3 for the sequence described above.

#### Example:

Assume n=3, m=1, t=2  $\mu$ sec and t'=125 nsec. Then t/t'=16=2<sup>4</sup>. As seen in Figure 3, counter1 receives input from the clock with t'=125 nsec and sends out a clock with t=2  $\mu$ sec. In the design considered here, n=3, f=0.003, so every 0.003 MHz we keep 3 clock pulses and ignore the remaining 164 clock pulses in order to obtain 3 clock pulses per 0.003 MHz, each of 2  $\mu$ sec duration. This waveform is shown in Figure 4, and is called SWC.

The waveform SWC is generated as follows:

The number of pulses per cycle is expressed by its binary representation:

$1/tf=1/(2 \mu sec \times 0.003 MHz)=167=10100111=d_7d_6...d_2d_1d_0$

Since n=3, or  $s_1s_0=11$ , and  $d_1d_0$  is the same as  $s_1s_0$ , the sequence  $d_7d_6...d_2d_1d_0$  =10100111 remains unchanged.

The counter2, shown in Figure 3 receives 2 µsec clock pulses and outputs  $Q_7Q_6$ ... $Q_1Q_0$ , from which  $Q_7Q_5Q_2$  can be choosen for input to an AND gate. After 328 µsec (2 µsec x ( $2^7+2^5+2^2$ )), T1 (the output of the AND gate) will go high to enable the SWC. Similarly, from the  $Q_7Q_6$ ... $Q_1Q_0$  sequence choose  $Q_7Q_5Q_2Q_1Q_0$  and connect to a NAND gate. For this latter case, we need to add an extra 125 nsec clock pulse to the NAND gate in order to avoid a transient spike. Without this delay clock pulse, the output from the NAND gate will induce a 4.1 nsec spike due to a timing conflict with counter2. This spike will produce a 3.0 V signal at RS1, which will incorrectly enable counter2 and will generate an ambiguous output  $Q_7Q_6$ ... $Q_1Q_0$ . Assuming correct timing, after 334 µsec (2 µsec x ( $2^7+2^5+2^2+2^1+2^0$ )), T2, the output from the NAND gate, will go low and send this low, RS1, to reset all output  $Q_7Q_6$ ... $Q_1Q_0$  of counter2, so that T1 goes low giving a total high time of 6 µsec. Using T1 and a 2 µsec clock, we can generate SWC to be used in the CTB. From SWC and LE\_, we can get CNTC for counter addressing.

#### 3.2.1.2 Binary Code Development

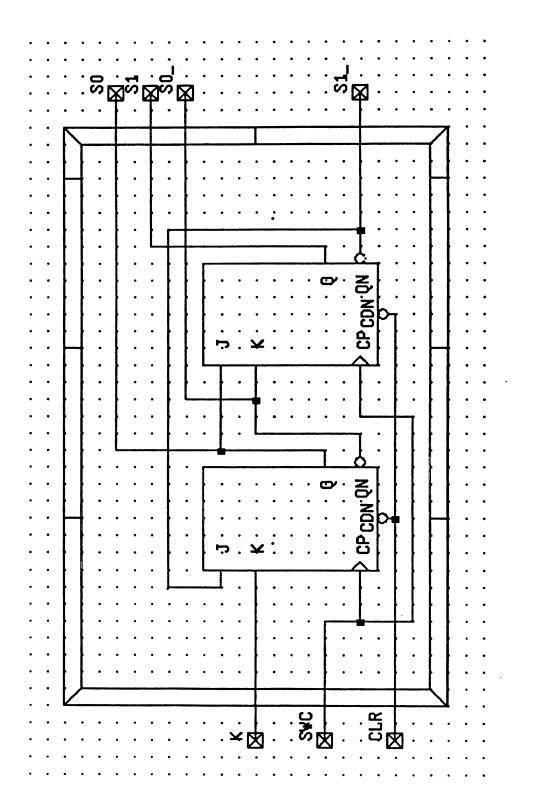

The A/D has n channels (for example, the National Semiconductor ADC0808 data sheet shows 8 channels), which are multiplexed by analog switches to choose the appropriate analog input. It is necessary to develop the binary code for correct A/D addressing. This is accomplished by the CTB circuit, as shown in Figure 5, which accepts the pulse sequence SWC from the output of the CSC, and generates the binary code  $s_{l-1}...s_0$ , where l=round-off of  $log_2n + l$  and n is the data dimension for A/D addressing.

#### 3.2.1.3 Signal Latching

Because we need to threshold filter the signals from the A/D, a latch is necessary to store these signals in a buffer memory. The latch operates in two stages; First, we need to store n parallel input signals from the A/D into a pre-latch every f MHz cycle in order to investigate m constraints. Second, if m or more constraints are satisfied, a low LE\_ is sent to the CSC to control the clock for the counter16 and pass the n signals into the post-latch. The data is stored in memory during the next f MHz cycle. If the constraints are not satisfied, the LE\_ will remain high and the post-latch will block the signal.

#### 3.2.1.4 Comparison of Input Signal with a Threshold

The signal from the A/D is threshold filtered in order to save memory. Thus, we require an 8 bit comparator circuit to compare the signals from the A/D with predetermined thresholds (both positive and negative thresholds). If a signal satisfies the threshold, a low  $LE_{i}$  ( $1 \le i \le n$ ) is sent to the latch. If the thresholds are not satisfied, the  $LE_{i}$  will remain high. Thus only interesting data will be latched into memory.

#### 3.2.1.5 Memory Address Counting

The memory has a 16-bit address bus, so a 16-bit counter is necessary to receive the clock pulses from the CSC and send the 16 bit count signal to memory for address count-

ing.

The block diagram for this n-D data acquisition with m restrictions circuit is shown in Figure 2.

Figure 1 - A t  $\mu$ sec clock with f MHz frequency forms the waveform SWC. (n=4, l=round-off of  $\log_2 n + 1 = 3$ ,  $s_{l-1} ... s_0 = s_2 s_1 s_0 = 100 = n$ )

Figure 2 - Block diagram for the n-D data acquisition system with m restrictions.

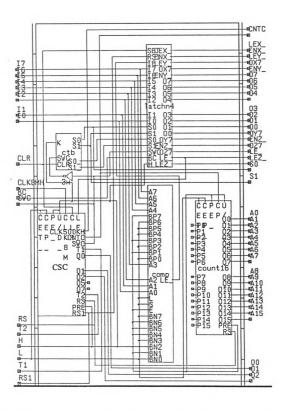

Figure 3 - The detailed circuit diagram for the CSC (counter & switch clock) generator for n=3.

Figure 4 - The waveform SWC, with 3 pulses of 2  $\mu$ sec at a 0.003 MHz repetition frequency.

Figure 5 - The detailed circuit diagram for the CTB (clock-to-binary) generator for n=3.

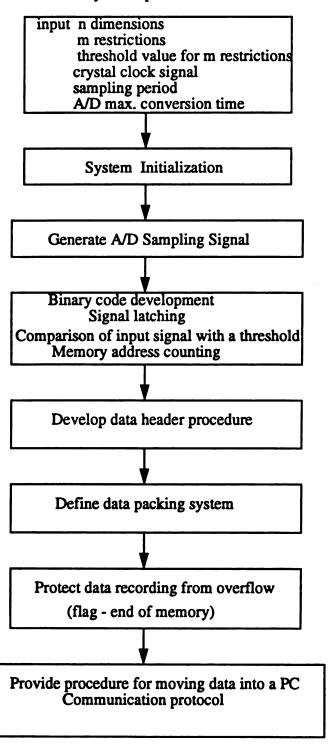

#### 3.2.2 Flow Chart for System Operation

An overall flow chart for system operation is shown as follows:

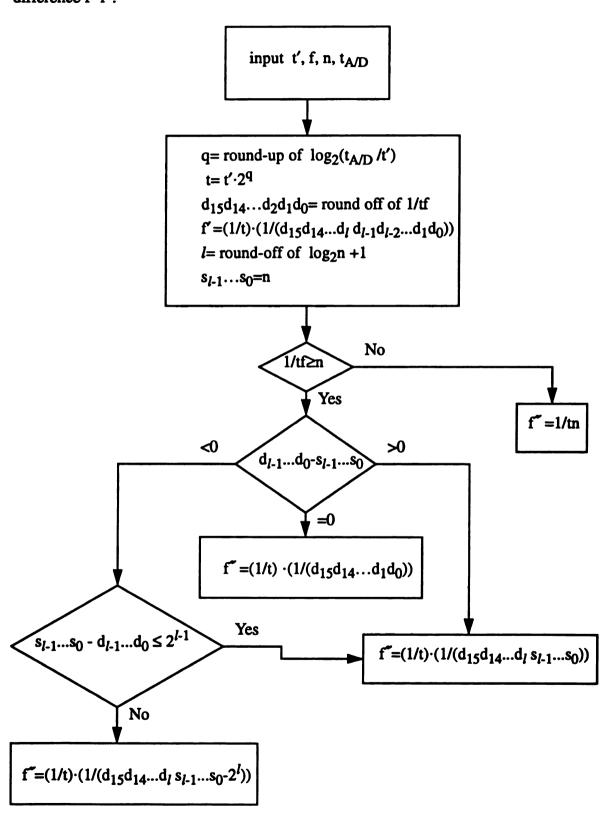

#### 3.3 The Algorithm

Develop a new design methodology [49]~[53] to synthesize a n-dimension with m restrictions data acquisition system which includes the previously defined CSC, CTB, latch, comparator and counter16 for optimum power and size features.

The development of the overall data acquisition signals will procede as outlined below. The design methodology follows the flow graph attached below to develop the actual sampling frequency f, with minimum error in the difference f-f.

Flow graph for developing the actual sampling frequency f with minimun error in the difference f- f.

# 3.4 Special Case (Clock Count Per Burst Less Than Data Dimension)

When 1/tf < n where t, f, and n were previously defined, and  $t/t' = p = 2^q$  (with q an integer and t' as previously defined), we still need a q+l bit counter, counter1, which receives an input clock period t' from the crystal and generates the waveform SWC, see Figure 6. For f''=1/tn, the actual frequency from the SWC is generated as follows:

From the  $Q_{q+l-1}Q_{q+l-2}...Q_q$  sequence choose those which have a value of 1 when the corresponding values of  $d_{q+l-1}d_{q+l-2}...d_q$  has a 1, where  $d_{q+l-1}d_{q+l-2}...d_q$  is the binary code of n, and connect these lines to a NAND gate. Again, we need to add an extra t' to the NAND gate input to avoid a transient spike. After 1/f µsec the output of the NAND gate, T2, goes low, which sends a low reset, RS1, to counter1 to reset  $Q_{q+l-1}Q_{q+l-2}...Q_qQ_{q-1}...Q_1Q_0$ . The  $Q_{q-1}$  (t'x2<sup>q</sup>=t) is the SWC used in the CTB. From SWC and LE\_, we can get CNTC for counter16 addressing, see Figure 7 for this sequence.

# 3.5 Application (Design of a Smart Logic 3-D Data Acquisition System with One Restriction)

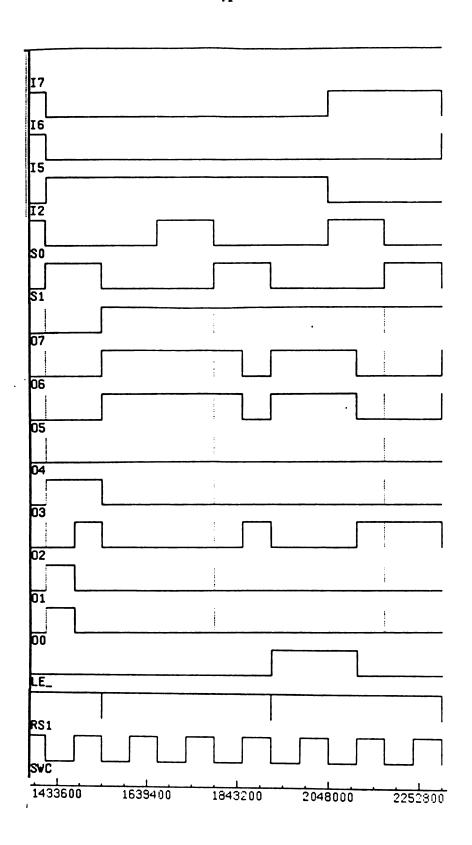

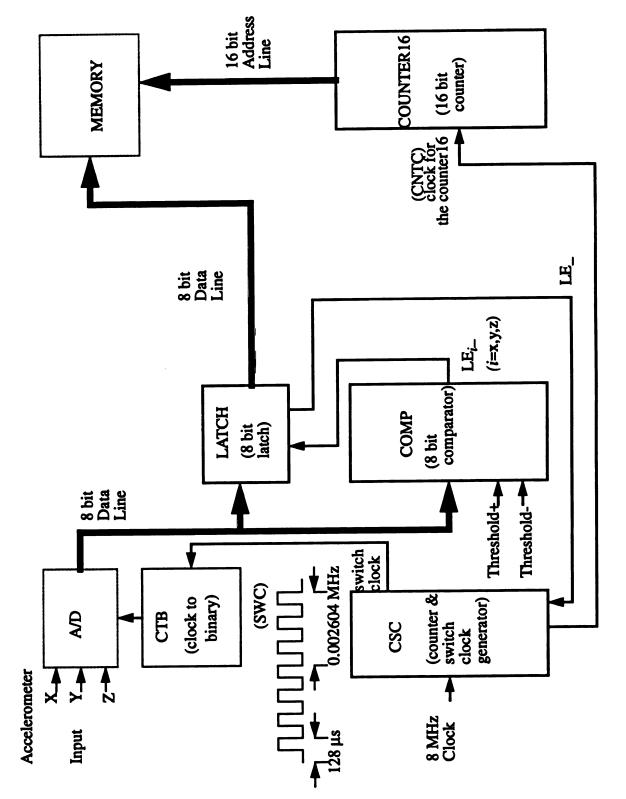

According to the general design rules, with n=3, and m=1, we can achieve the design of a smart logic circuit to replace an operational  $\mu$ -P based system. The design will contain the following five main blocks: CSC, CTB, LATCH, COMP, COUNTER. The design procedure follows the techniques outlined for the n-D data acquisition with m restrictions. The five required blocks are as follows:

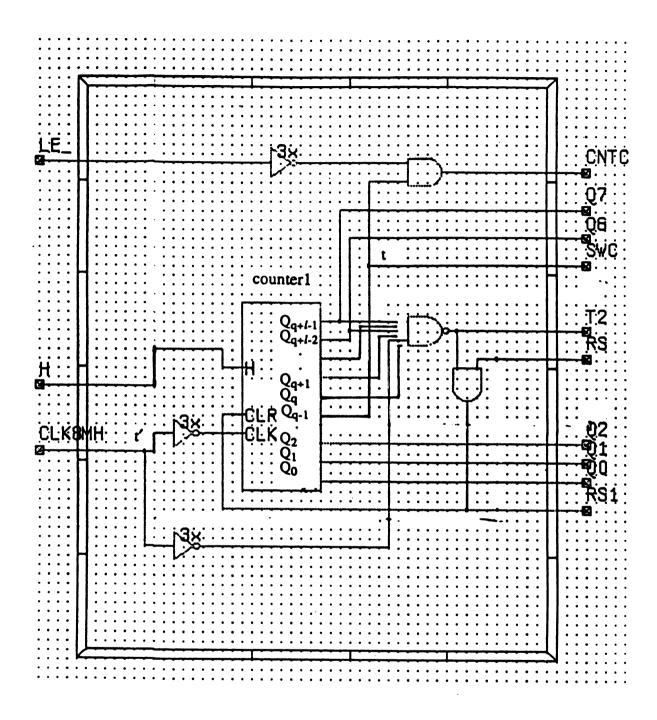

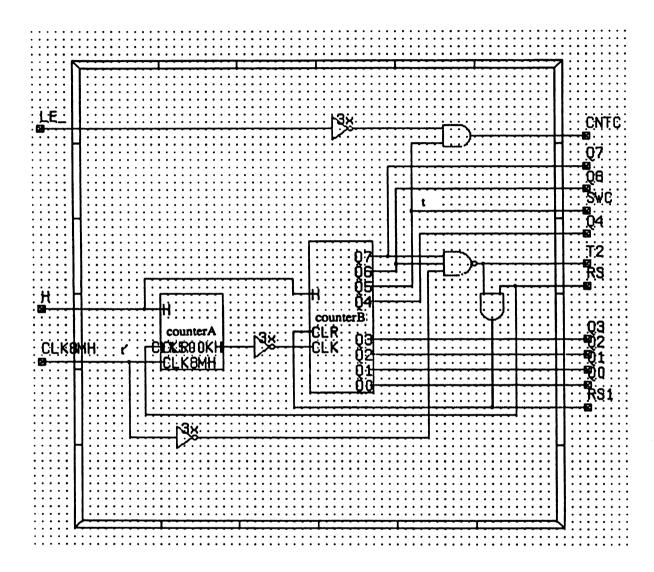

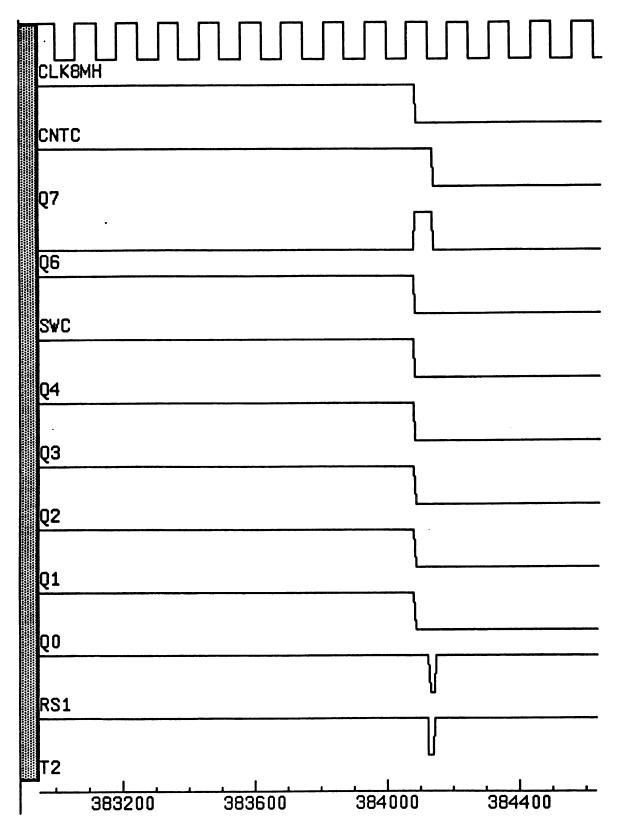

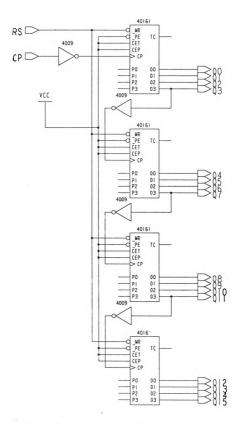

#### 3.5.1 CSC Design

The counter and switch clock generator generates the desired signals for the CTB and for the counter16. In our case, the input clock t' from the crystal is 125 nsec. According to the A/D specification the maximum conversion time is 116 µsec (National Semiconductor

ADC0808). In the design considered here, n=3, f=0.003, so that 1/tf=1/(116x0.003) =2.87<3=n, which indicates that these conditions belong to the special case design considered in Section 3.4 above. If we choose t=128  $\mu$ sec, then  $t/t'=128/0.125=1024=2^{10}$ , or q=10, and with t=round-off of  $\log_2 3 + 1 = 2$ , we need a 12-bit counter (q+t), counter1, which can be the cascade of a first stage 4-bit counter, counterA, and a second stage 8-bit counter, counterB. CounterA receives its input from the clock with period 125 nsec (from the crystal) and generates an output Q<sub>3</sub> of period 2  $\mu$ sec. CounterB receives the 2  $\mu$ sec clock signal from Q<sub>3</sub> of CounterA and generates the waveform SWC, see Figure 8. If we define f'=1/tn=1/(128x3) =0.002604 as the real frequency for the SWC, the waveform for SWC is generated as follows:

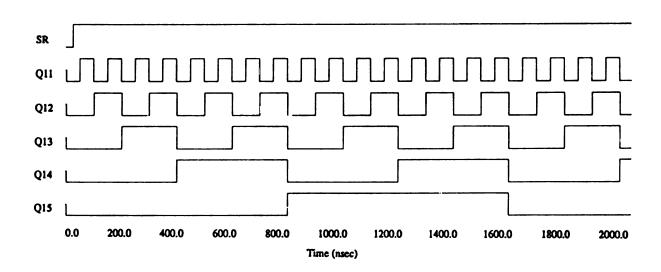

From the  $Q_7Q_6...Q_1Q_0$  sequence of counterB choose  $Q_7Q_6$  (2  $\mu$ sec x (2<sup>7</sup>+2<sup>6</sup>)=384  $\mu$ sec= 128  $\mu$ sec x3) and connect these lines to a NAND gate along with an extra 125 nsec clock pulse in order to avoid a transient spike. After 384  $\mu$ sec the output of the NAND gate, T2, goes low, which sends a low reset, RS1, to counterB to reset  $Q_7Q_6...Q_1Q_0$ . The  $Q_5$  (2  $\mu$ sec x 2<sup>6</sup>=128  $\mu$ sec) of counterB is the SWC used in the CTB. From SWC and LE\_, we can get CNTC for counter16 addressing, see Figure 8 for this sequence.

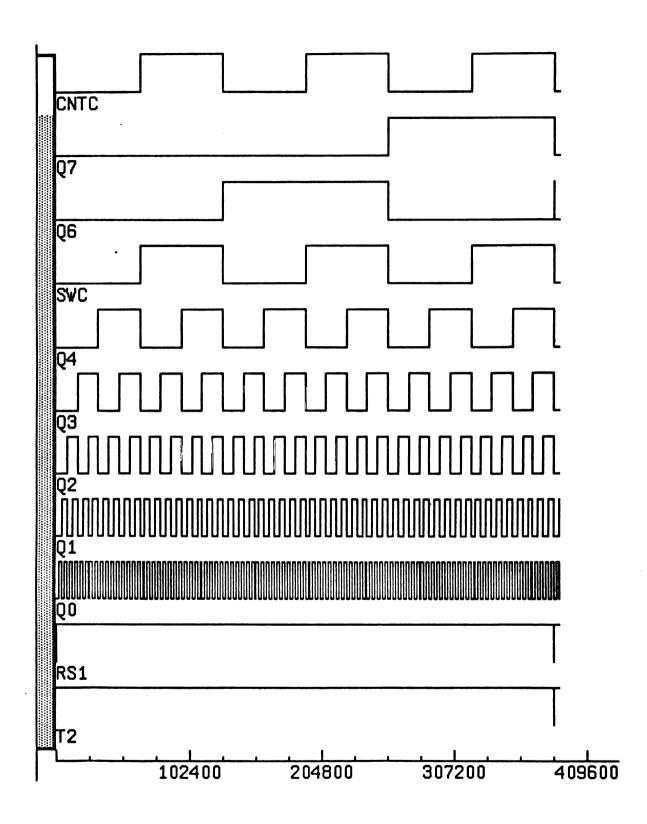

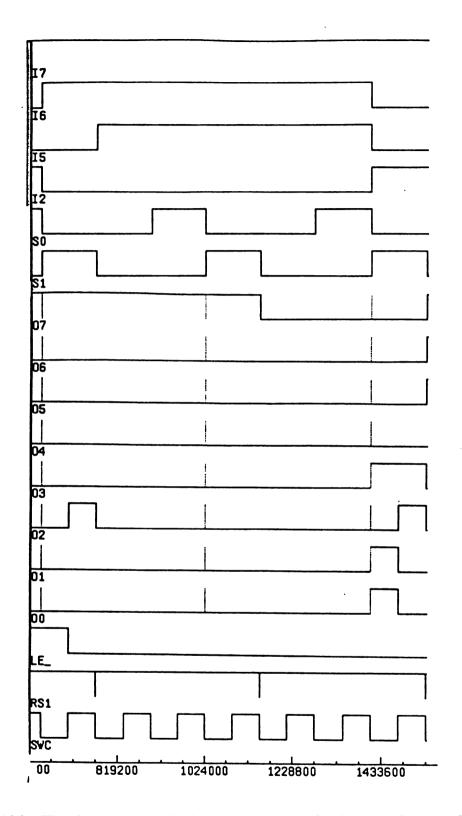

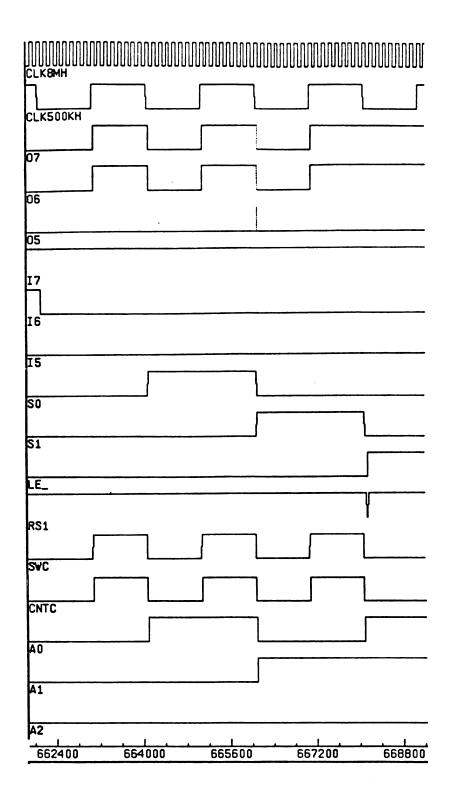

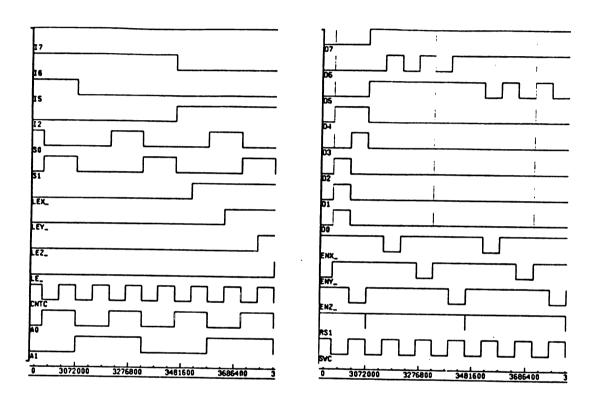

The simulation results of the CSC generator circuit for the special case n=3, m=1, t'=125 nsec,  $t_{A/D}$  =116 µsec, f=0.003 MHz are shown in Figure 9. Each of the monitoring nodes can refer to the circuit diagram shown in Figure 8. The SWC and CNTC are expected signals. CLK8MH (t') and LE\_ are input signals. At first LE\_=0, RS is set to low to clear counterA and forces RS1 to 0 which clears  $Q_7Q_6...Q_1Q_0$  of counterB. Then RS is set to high and forces RS1 to 1, counterA and  $Q_7Q_6...Q_1Q_0$  of counterB counts step by step according to the clock sequence of CLK8MH and the output of counterA, respectively. T2 is an important signal, which is initially high and after 384 µsec (2 µsec x  $(2^7+2^6)$ =384 µsec= 128 µsec x3) goes low and sets RS1=0 in order to reset  $Q_7Q_6...Q_1Q_0$  of counterB. The  $Q_5$  (cycle time of one pulse=2 µsec x  $2^6$ =128 µsec) of counterB is the SWC (contains 3 pulses of Q5) used in the CTB. From SWC and LE\_, we can get CNTC for counter16

addressing. Then T2 goes high and sets RS1=1 to continue a new cycle of SWC.

#### 3.5.2 CTB Design

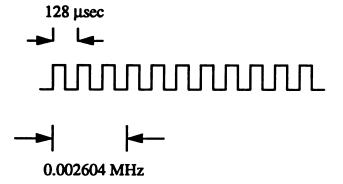

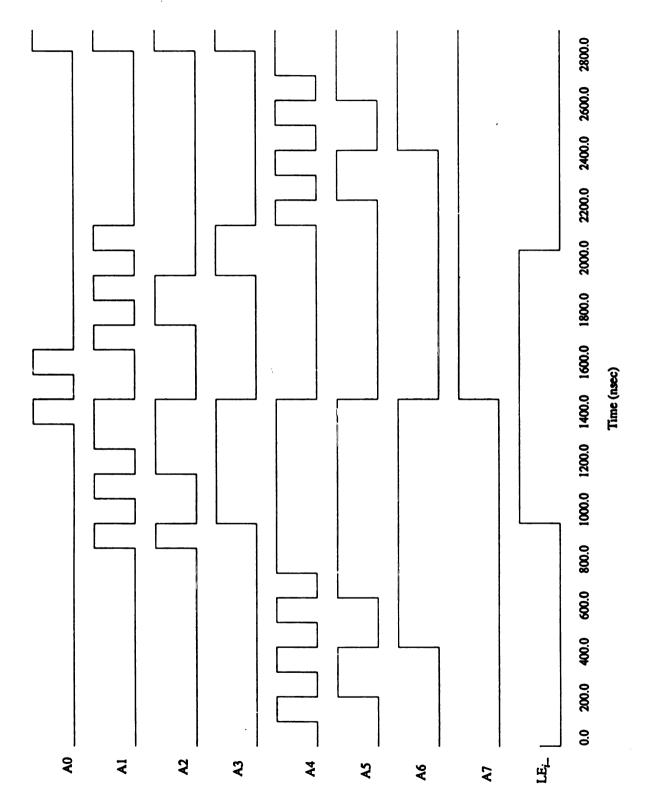

The A/D has 8 channels (National Semiconductor ADC0808) for multiplexing different analog inputs. The clock-to-binary circuit accepts 3 pulses of 128  $\mu$ sec signals at 0.002604 MHz repetition frequency, see Figure 10, converts these to binary codes  $s_1s_0$  and sends these codes to the A/D for choosing x, y, z axis analog inputs.

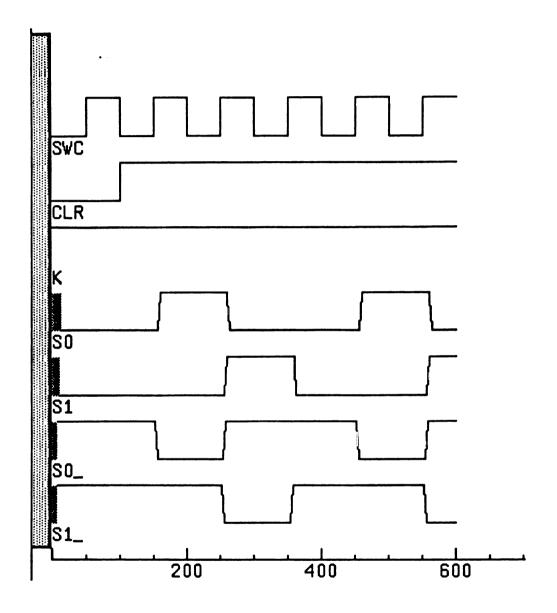

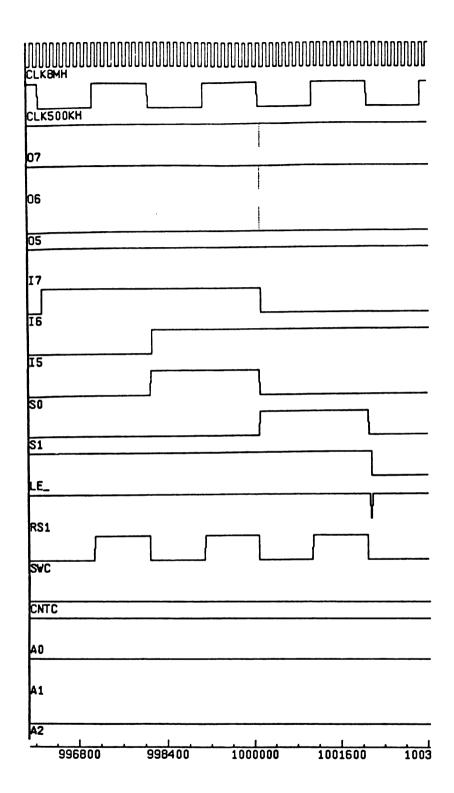

The simulation results of the CTB generator circuit for n=3 are shown in Figure 11. Each of the monitoring nodes can be referred to the circuit diagram shown in Figure 5. The S1 and S0 are CTB output control signals for choosing respectively the x, y, z axis analog A/D input signals. The SWC is an input signal representing a series of bursts from the CSC. The system initialization is as follows: the K of the JK Flip Flop is always set high, the CLR (clear) is set low in order to set S1 and S0 to 00, after which CLR is set high. The S1 and S0 change from 00, 01, 10 to correctly select the x, y, z axis analog inputs respectively and return to 00 according to the clock count of the SWC. The cycle continues in order to choose the desired signal. Each cycle needs three pulses from the SWC. S1\_ and S0\_ are the complements of S1 and S0, respectively, and these four signals are used in the latch for selecting digital signals from three different axes.

#### 3.5.3 LATCH Design

The latch circuit accepts three signals from the A/D at a 0.002604 MHz rate, and generates a LE\_ (latch enable low true) signal which is sent to the CSC to control the CNTC. For each 0.002604 MHz cycle, if one or more of the received signals are above the threshold, the low enable latch will strobe the signals into memory. For signals below the threshold, the LE\_ will remain high and the latch will block these signals from memory.

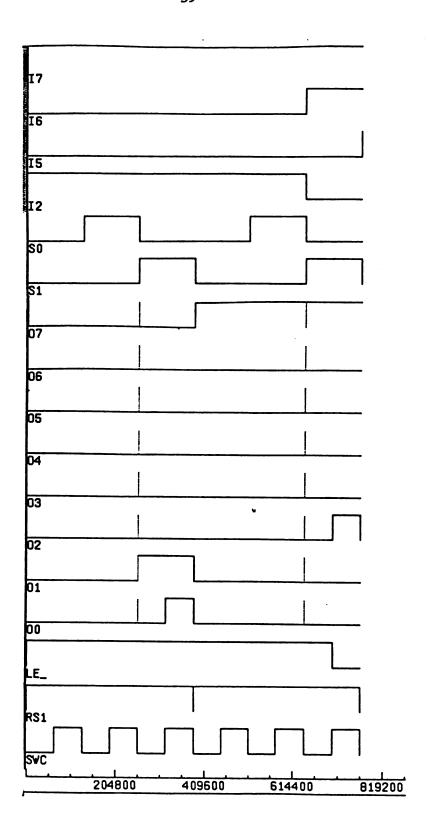

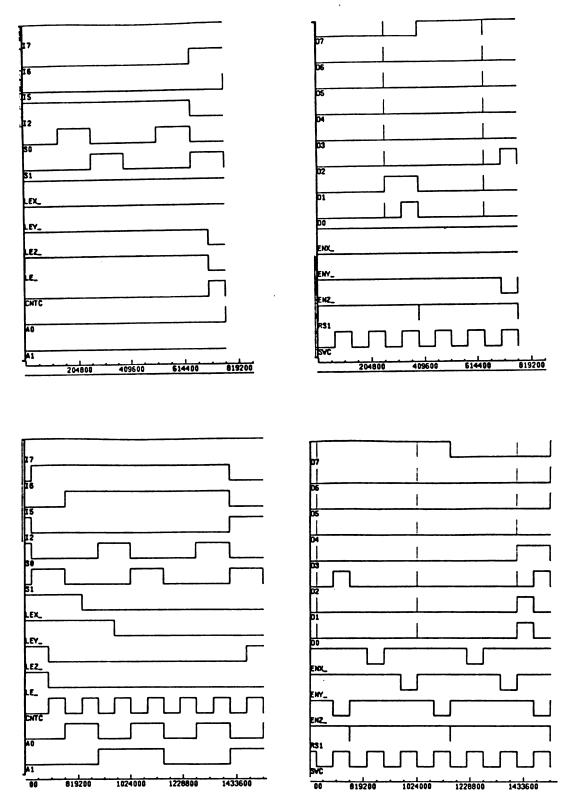

The simulation results for the latch circuit for the special case n=3, m=1, t'=125 nsec,  $t_{A/D} = 116 \mu sec$ , f=0.003 MHz are shown in Figure 12. Each of the monitoring nodes are

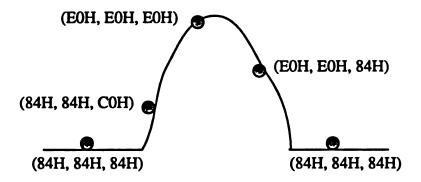

shown in the circuit diagram of Figure 13. The O7,O6,.....,O0 and LE\_ are output signals. The former is sent to memory as input data and the latter is send to the CSC to control the CNTC. The  $LE_{i-}$  (i=x,y,z, referred to as I8 in the simulation), I7,I6,....,I0 are input signals representing the latch enable signal of a single axis and digitalized impact force, respectively. The signals shown on Figure 12, namely, SWC, RS1, S1 and S0 are control signals. The input signal used to run a simulation is an impact force similar to that shown in Figure 14. The output signals are delayed one time unit (384  $\mu$ s) and the first two data values are replaced by a heading and time of occurrence for any significant impact pulse. The output signals are updated only when SWC is high. S1 and S0 are used to choose the input signals from the x, y, z axis, where S1,S0=00 chooses the x axis, S1,S0=01 chooses the y axis, and S1,S0=10 chooses the z axis. The S1,S0 control signals continue to cycle in order to select the desired signal from the data sequence.

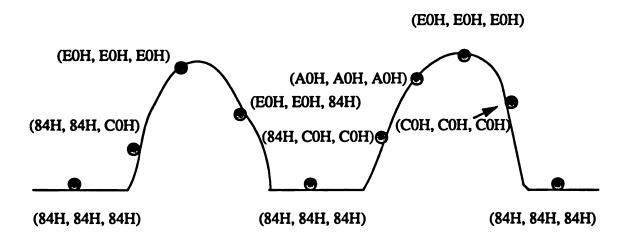

In Appendix 1 and Figure 14, the first input data to the latch for the three axes is 84H, 84H, 84H, which is below the threshold. The relative output data which is delayed one time unit is undefined, and in particular resulted in the sequence: 80H, 80H, 84H for our simulation. The second input data is 84H, 84H, C0H, which is above the threshold. The relative output data, which is delayed one time unit, is 80H, 80H, 80H, which represents heading. The third input data is E0H, E0H, E0H, which is also above the threshold. The relative output data, which is delayed one time unit, is 00H, 00H, 0CH, which represents the real time clock count. The fourth input data is E0H, E0H, 84H, which is above the threshold. The relative output data, which is delayed one time unit, is E0H, E0H, 84H, the same as input data. The fifth input data is 84H, 84H, 84H, which is below the threshold. The relative output data, which is delayed one time unit, is arbitrary for example E0H, 84H, 84H in the simulation performed in this thesis.

Figure 6 - A t  $\mu$ sec clock with f MHz frequency forms the waveform SWC. (for the special case and n=4)

Figure 7 - The schematic circuit diagram for the CSC (counter & switch clock) generator for the special case n=3.

Figure 8 - The detailed circuit diagram for the CSC (counter & switch clock) generator for the special case n=3.

Figure 9.a - The simulation results of the CSC (counter & switch clock) generator circuit for the special case n=3.

Figure 9.b - The simulation results of the CSC (counter & switch clock) generator circuit for the special case n=3, continued.

Figure 10 - The waveform SWC, with 3 pulses of 128 µsec at a 0.002604 MHz repetition frequency for the specific smart logic case.

Figure 11 - The simulation results of the CTB (clock-to-binary) generator circuit for n=3

Figure 12.a - The simulation results for the latch circuit for the special case n=3, m=1, t'=125 nsec,  $t_{A/D}=116$  µsec, f=0.003 MHz.

Figure 12.b - The simulation results for the latch circuit for the special case n=3, m=1, t'=125 nsec,  $t_{A/D}=116$  µsec, f=0.003 MHz, continue.

Figure 12.c - The simulation results for the latch circuit for the special case n=3, m=1, t'=125 nsec,  $t_{A/D}=116$  µsec, f=0.003 MHz, continue.

Figure 13 - The detailed circuit diagram for a two stage latch with n=3, m=1.

Figure 14 - One impact force which contains five sampled data.

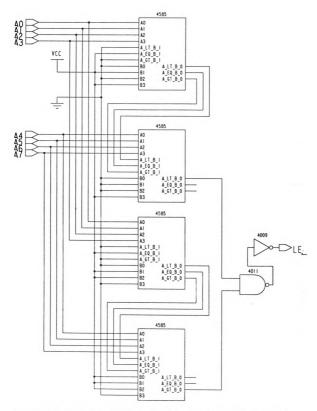

#### 3.5.4 COMP Design

The 8-bit comparator circuit compares the output signal from the A/D with preprogrammed thresholds (8AH and 76H, for +10 g and -10 g, respectively) and generates a latch enable signal,  $LE_{i}$  (latch enable  $LE_{i}$  low true, i=x,y,z). If the signal magnitude is above the threshold,  $LE_{i}$  will go low, otherwise,  $LE_{i}$  will remain high.

The simulation results of the comparator circuit are shown in Figure 15. Each of the monitoring nodes can be referred to the circuit diagram shown in Figure 16. The input signals are placed on the lines A7,A6, ....,A0 (data lines) and the output signal appears as  $LE_{i-}$ . The first set of input data is the sequence 00H, 10H, 20H, 30H, 40H, 50H, 60H, 70H which is above the threshold, so that  $LE_{i-}$  goes low. The second set of input data is chosen as 90H, A0H, B0H, C0H, D0H, E0H, F0H, FFH which again is above the threshold so that  $LE_{i-}$  again goes low. Finally the set of input data 76H, 78H, 7AH, 7CH, 7EH, 7FH, 80H, 81H, 82H, 84H, 86H, 88H, 8AH is applied which is below or at the threshold so that  $LE_{i-}$  goes high.

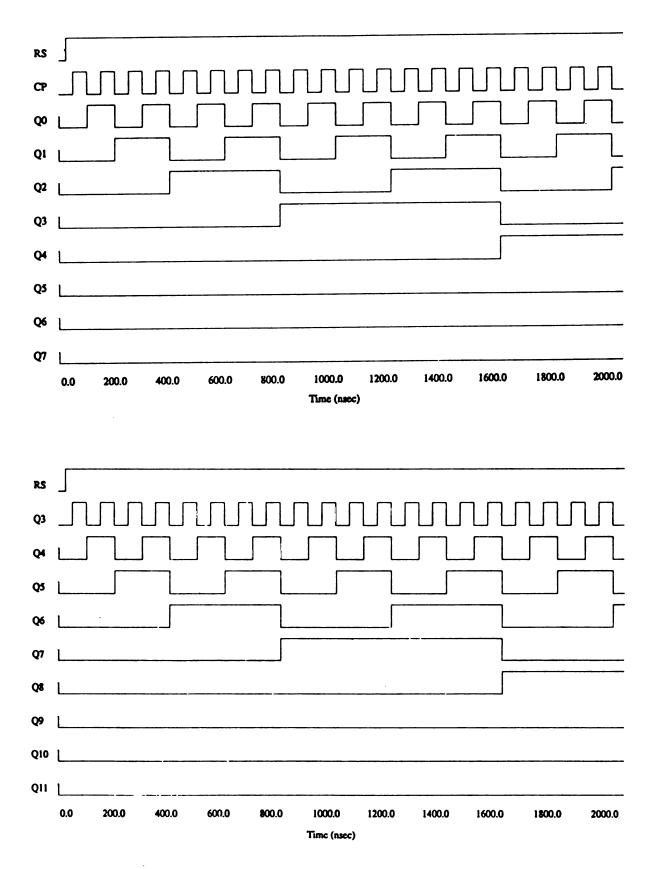

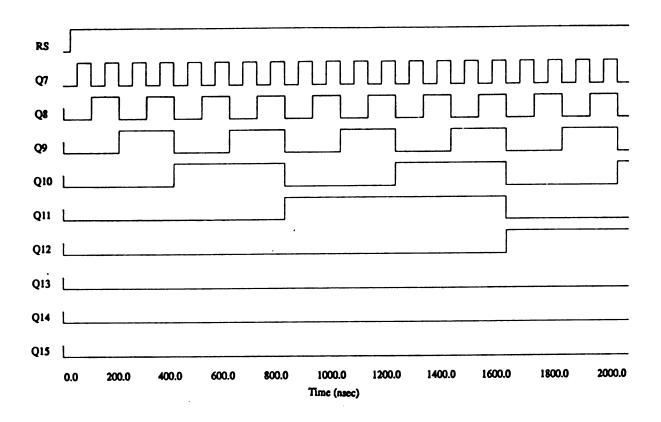

#### 3.5.5 COUNTER Design

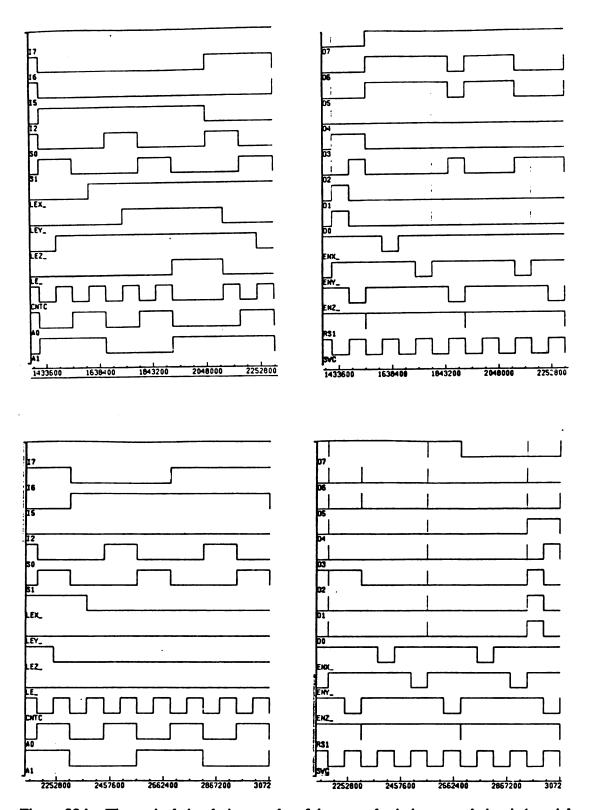

The 16-bit counter circuit receives the clock signal from the CSC and sends a 16-bit word to memory for address pointing. The simulation results for the counter16 circuit are shown in Figure 17. Each of the monitoring nodes can be referred to the circuit diagram shown in Figure 18. The output signals appear on the  $Q_{15}Q_{14}...Q_1Q_0$  lines. The input signal is CP (CNTC). We divide the counter16 into four parts to simulate the individual circuits since simulating the whole counter16 requires 65536 clock counts which would expend to much time and paper. For each individual part the 16 clock counts are sufficient to verify counter simulation performance. Initially, RS=0 in order to clear  $Q_{15}Q_{14}...Q_1Q_0$ . When RS=1,  $Q_{15}Q_{14}...Q_1Q_0$  will count each pulse from the clock which generates the signal CP (CNTC). This process is repeated for the other 3 four bit parts of the counter.

The block diagram for this SLIC is shown in Figure 19.

Figure 15 - The simulation results for an 8-bit comparator with predetermined thresholds.

Figure 16 - The detailed circuit diagram for an 8-bit comparator with predetermined thresholds.

Figure 17.a - The simulation results for a 16-bit counter which is divided into four parts.

Figure 17.b - The simulation results for a 16-bit counter which is divided into four parts, continue.

Figure 18 - The detailed circuit diagram for a 16-bit counter.

Figure 19 - Smart logic integrated circuit (SLIC) functions interfaced to memory and A/D.

#### **3.6 Software Program**

A software program based on the flow graph shown in Section 3.3 has been developed for synthesizing the n-D with m restrictions data acquisition system according to the design methodology developed in Section 3.2. The flow chart for the software to accomplish this objective is shown in Section 3.3. This program develops the actual sampling frequency f, with minimum error in the difference f- f. The detailed software listing is included in Table 1.

```

#include <math.h>

#include <stdio.h>

main()

{ /* The program for synthesizing the n-dimension with m restrictions data acquisition

system */

float t1,t,f,tad,q1,f1,f2;

int n,q,d,l,s,d1;

printf("enter the t1 value with nsec:"):/*internal clock period generated from the crystal*/

t1=getnum()/1000.;

printf("enter the f value with Hz:"); /* sampling frequency */

f = getnum()/1000000.;

printf("enter the tad value with usec:"); /* A/D maximum conversion time */

tad=getnum():

printf("enter the n value:"); /* data dimension */

n=getnum();

q1=log10(tad/t1)/log10(2.0); /* q=round-up of log_2(tad/t1) */

if (q1-(int) q1==0)

q=q1;

else q=++q1;

t=t1*pow(2.0,(float) q); /* μsec duration of the clock pulses in the burst */

if ((1/(t+f))-(int)(1/(t+f))<0.5) /* d=round off of 1/tf */

d=1/(t+f);

else d=1+1/(t+f);

f1=(1/t)*(1/(float) d);

l=\log 10((float) n)/\log 10(2.0)+1; /* l=round-off of log<sub>2</sub>(n) +1 */

d1=d&((int) pow(2.0,(float) l) -1); /* d1 = the least l bit of d */

if (1/(t+f)< n

/* special case: clock count per burst less than data dimension */

/* f2 represents actual frequency of the SWC waveform */

f2=(1/(t*n));

else if (d1==n)

f2=(1/t)*(1/(float) d);

/* f1=f2 */

else if (d1>n)

/* minimize f1-f2 */

f2=(1/t)*(1/(float)(d-d1+n));

else if ((n-d1) <= (int) pow(2.0, (float) l-1.0))

f2=(1/t)*(1/(float)(d-d1+n));

else f2=(1/t)*(1/(float) (d-d1+n-(int) pow(2.0, (float) l)));

printf("q=%d t=%f d=%d f1=%f l=%d d1=%d f2=%f", q,t,d,f1,l,d1,f2);

getnum()

char s[80];

gets(s);

return(atoi(s));

Table 1 - Software program for synthesizing the n-D with m restrictions data acquisition

```

system.

#### **CHAPTER 4**

### Variation in Size, Power and Heat Dissipation with Specification Requirements

It is important to estimate the size, power and heat dissipation of the  $\mu$ -P based IS, of the composite smart logic chip based IS and of the absolute limit for an optimum design in order to compare the improvement for each step of the smart logic implementation. A general analysis of power versus size for multichip housing configurations and high density VLSI will aid in the design of compact data acquisition devices.

# 4.1 Estimation of Size, Power and Heat Dissipation for a $\mu$ -P Based IS

The size, power and heat dissipation of the  $\mu$ -P based IS are analyzed in order to compare the power and size saving achievable with a composite smart logic chip based IS.

### 4.1.1 Estimation of Power Dissipation in a 89 mm (3.5 in.) $\mu$ -P Based IS

A 89 mm (3.5 in.) IS previously reported by Zapp, et al. (1990) has a 13.804 mA total current consumption from a 7.2 V battery which includes 9 mA for the  $\mu$ -P (the power consumption data of some typical single chip  $\mu$ -P are listed in Table 2 for reference), 1.2

mA for the 32 K RAM, 0.004 mA for the latch and multiplexer, 0.6 mA for the Op Amp, and 3 mA for the regulator biased at 7.2 V. Thus the total power consumption is P=IV=13.804 mA x 7.2 V = 99.39 mW. The current and power consumption for the conventional  $\mu$ -P circuit in the 89 mm (3.5 in.) IS are shown in Table 3.

According to the data sheets for the MC68HC11A8  $\mu$ -P (Motorola Semiconductor Products, Inc.), the average chip-junction temperature,  $T_J$ , in  ${}^{\circ}$ C can be obtained from:

$$T_{J}=T_{A}+(P_{D} \times \theta_{JA}) \tag{4.1}$$

where T<sub>A</sub>= Ambient Temperature, °C

$\theta_{JA}$  = Junction-to-Ambient Package Thermal Resistance, °C/W

$P_D = P_{INT} + P_{I/O}$

$P_{INT}$  = Chip internal power Icc x Vcc, W

$P_{I/O}$  = Power dissipation on input and output pins

For most applications  $P_{I/O} < < P_{INT}$  and can be neglected.

For the 89 mm (3.5 in.) IS, the estimated  $\mu$ -P current consumption based on total system current requirements gives Icc=9 mA, at Vcc=5 V, so that P<sub>D</sub>= Icc x Vcc= 9 mA x 5 V = 45 mW if P<sub>I/O</sub> is neglected. Thus T<sub>J</sub>-T<sub>A</sub>= 45 mW x 50 °C/W (The  $\mu$ -P MC68HC11A8, Plastic 52-pin Quad Pack, Thermal Resistance is given as  $\theta_{JA}$ =50 °C/W) = 2.25 °C. Such a small temperature increase is allowable in the 89 mm (3.5 in.) IS.

### 4.1.2 Estimation of Power Dissipation in a 63.5 mm (2.5 in.) $\mu$ -P Based IS

A 63.5 mm (2.5 in.) IS previously reported by Techmark, 1991, has a 10.244 mA total current consumption which includes 9 mA for the  $\mu$ -P, 1.2 mA for the 32 K RAM, 0.004 mA for the latch and multiplexer and 0.04 mA for the Op Amp at Vcc=5 V. This gives a total power consumption of P=IV=10.244 mA x 5 V = 51.22 mW.

For the 63.5 mm (2.5 in.) IS, using Eq. 4.1, and the estimated  $\mu$ -P current consumption (based on total system current requirements) of Icc=9 mA, at Vcc=5 V, gives  $P_D$ = Icc x

Vcc= 9 mA x 5 V = 45 mW if  $P_{IO}$  is neglected. This results in  $T_J$ - $T_A$ = 45 mW x 50 °C/W = 2.25 °C. This temperature increase is allowable in the 63.5 mm (2.5 in.) IS.

## 4.1.3 Estimation of Power Dissipation in a 50.8 mm (2.0 in.) $\mu$ -P Based IS Multichip Housing

A 50.8 mm (2.0 in.) multichip housing IS, has a 10.804 mA total current consumption which include 9 mA for the  $\mu$ -P, 1.2 mA for the 32 K RAM, 0.004 mA for the latch and multiplexer and 0.6 mA for the Op Amp at Vcc=5 V, giving a total power consumption of P=IV=10.804mA x 5 V = 54.02 mW.

For the 50.8 mm (2.0 in.) IS, using Eq. 4.1, and a  $\mu$ -P current consumption of Icc=9 mA, at Vcc=5 V, gives P<sub>D</sub>= Icc x Vcc= 9 mA x 5 V = 45 mW if P<sub>I/O</sub> is neglected. Thus T<sub>J</sub>-T<sub>A</sub>= 45 mW x 50 °C/W = 2.25 °C which is allowable in the 50.8 mm (2.0 in.) IS.

Comparing section 4.1.1, 4.1.2 and 4.1.3 for the three different sizes of  $\mu$ -P based IS, the  $T_J$ - $T_A$  (the temperature difference between chip-junction and ambient) is the same because we use the same  $\mu$ -P and the  $\mu$ -P dominates the power consumption.

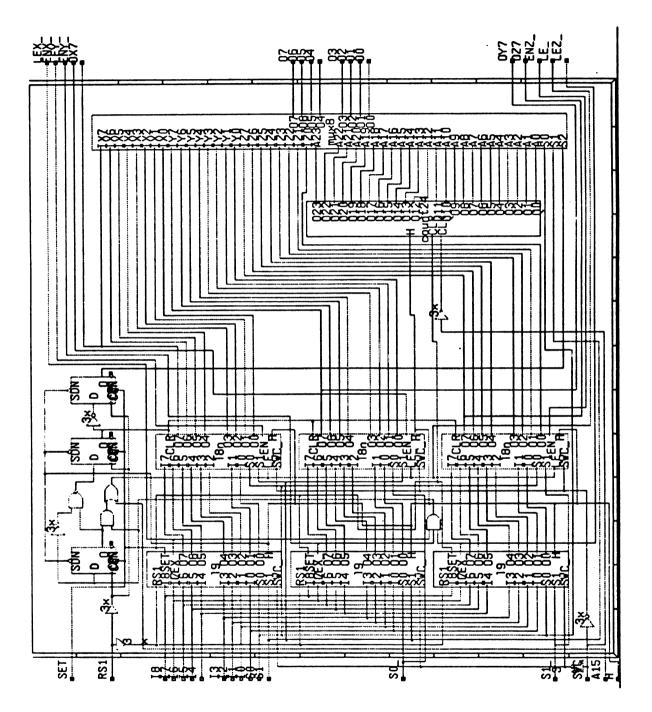

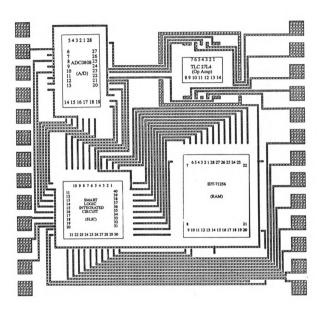

# 4.2 Estimation of Size, Power and Heat Dissipation for a Composite Smart Logic Chip Based IS

The SLIC, A/D, Op Amp and RAM dice are housed together on a single substrate without circuit board and connected to form what we call the composite smart logic chip. Figure 20 depicts the smart logic substrate layout, showing the 4 subsets, RAM, Op Amp, SLIC and A/D. The dimensions of the single housing unit are  $20 \times 20 \text{ mm}$  (0.787 x 0.787 in.). The composite smart logic chip will save power compared to the previous 89 mm (3.5 in.) IS since SLIC replaces the  $\mu$ -P which dominates the total power consumption. It is necessary to estimate the size and power for a composite smart logic chip based IS to verify the specification requirements of smaller size and lower power consumption than

for the previous 89 mm (3.5 in.) IS.

#### 4.2.1 Estimation of the Size

Three different configurations for the smart logic chip based IS are considered:

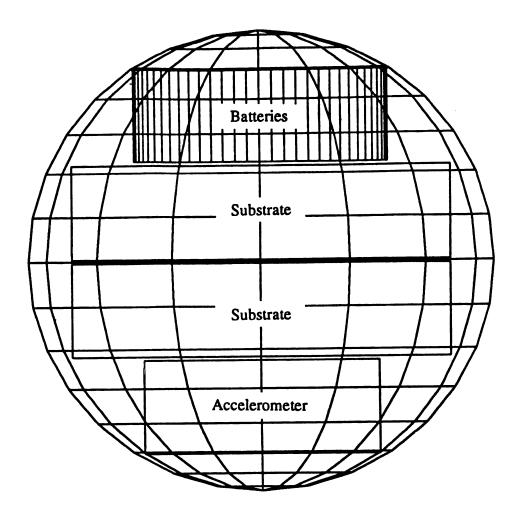

For a one substrate composite smart logic chip configuration, the volume of the substrate is 20 mm x 20 mm x 5 mm (0.787 in. x 0.787 in. x 0.197 in.), the volume of the triaxial piezoelectric accelerometer (Vibrametrics model 3130HT) is 7 mm x 7 mm x 15.2 mm (0.275 in. x 0.275 in. x 0.6 in.), and the volume of the smallest battery (Panasonic model PZ2330) of which 3 are needed has a 23.2 mm diameter and a 3.0 mm height (0.91 in. diameter, 0.12 in. height). Using Autocad an optimal volume configuration has been developed as shown in Figure 21. The components are contained in a spherical volume which has a sphere diameter of 30 mm (1.18 in.). If a utilization rate (minimum element volume divided by minimum sphere space) of 46.33% is assumed and the remainder of the sphere is filled with heat sink, rigid foam, beeswax, and epoxy walls of 3.81 mm (0.15 in.) thickness, the IS diameter becomes 37.62 mm (1.48 in.). The disadvantage of this configuration is that the accelerometer is not located in the center of the sphere.

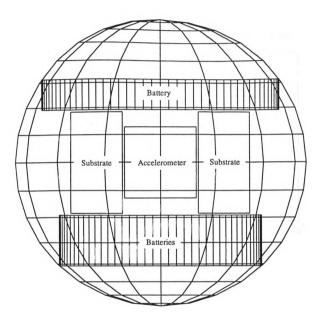

For two half-substrate configurations, the volume of each substrate is 20 mm x 10 mm x 5 mm (0.787 in. x 0.394 in. x 0.197 in.). Using the same accelerometer and battery as previously, the Autocad software provides two possible configurations. The sphere diameter for one is 31.62 mm (1.25 in.) which for a utilization rate of 39.57% gives an IS diameter of 39.24 mm (1.55 in.) as shown in Figure 22. The advantage of this configuration is that the accelerometer is located near the center of the sphere.

The sphere diameter for the third configuration is 30.24 mm (1.19 in.) which using a utilization rate of 45.24% gives an IS diameter of 37.86 mm (1.49 in) as shown in Figure 23. The advantage of this configuration is that the accelerometer is located in the sphere center. The disadvantage is that the separating distance between the two half-substrates is larger than that of the previous configuration, so that longer wire connections are neces-

sary.

The detailed IS dimensions for the three different configurations are shown in Table 4.

#### 4.2.2 Estimation of the Power and Heat Dissipation

Replacement of the  $\mu$ -P with a composite smart logic chip results in a substantial power reduction. The expected power reduction can be calculated using the known power consumption of individual gates comprising the composite smart logic chip. Specifically, the gate count for the SLIC is approximately 1500 gates. According to the National Semiconductor CMOS Logic Databook, Application Note 303, Kenneth Karakotsios [54], the CMOS Logic Databook [55], the Texas Instruments CMOS Logic Databook [56], and the Samsung CMOS Logic Databook [57], as summarized in Table 5, the average HCMOS current consumption for one gate is 0.5  $\mu$ A at  $T_A=25$  °C, at a bias voltage of Vcc= 6 V. Thus the current consumption of the smart logic circuit is less than 1 mA at Vcc= 5 V. The current consumption of the 32 K RAM (IDT 71256, Integrated Device Technology, Inc., Santa Clara, CA) is approximately 1.2 mA at Vcc= 5 V. The current consumption of the A/D (ADC 0808/ADC 0809, National Semiconductor) is approximately 3 mA at Vcc= 5 V. The current consumption of the Op Amp (TLC 27L4, Texas Instruments Inc., Dallas, TX) is approximately 0.04 mA at Vcc= 5 V (A recent modification incorporated in the IS by Techmark Inc. of Lansing uses this type of Op Amp to provide a reduced current consumption of 0.04 mA and achieve a smaller size for the IS of 63.5 mm (2.5 in.) diameter.), so that the total current consumption of the composite smart logic device during operation is about 5.24 mA at Vcc= 5 V. This is less than half the current consumption of the conventional μ-P based circuit. The better than 2.0 reduction in power consumption allows the use of smaller volume batteries to achieve the same results as for the existing larger IS. The current and power consumption for the composite smart logic IS chip are shown in Table 3.

According to R. C. Eden [58], the maximum temperature rise, T<sub>m</sub>, above the heat sink

temperature is given by:

$$T_m - T_0 = (P/2\pi kz)[\ln(R_0/R_1) + 1/2]$$

(4.2)