LIBRARY Michigan State University

PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due.

| DATE DUE | DATE DUE    | DATE DUE |

|----------|-------------|----------|

|          |             |          |

|          | <del></del> |          |

|          |             |          |

|          |             |          |

|          |             |          |

|          |             |          |

|          |             |          |

MSU Is An Affirmative Action/Equal Opportunity Institution etcirc/datedus.pm3-p.;

# DESIGN AND EVALUATION OF A HIERARCHICAL BUS MULTIPROCESSOR

By Carl Burton Erickson

## A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Electrical Engineering 1991

## Abstract

Design and Evaluation of a Hierarchical Bus Multiprocessor

### By Carl Burton Erickson

This thesis describes the design and evaluation of the protocol and controllers which maintain memory coherence in a hierarchical bus multiprocessor. The architecture studied represents a natural step in the evolution of bus-based shared memory multiprocessors. Extending the scalability of these machines beyond the current single bus limit of 20 processors preserves the inherent advantages and familiarity of the bus interconnect and the shared memory programming paradigm.

Cache memory is vitally important in bus-based multiprocessors for reducing memory latency and for conserving bus bandwidth. A new cache coherence protocol, designed for hierarchical buses, is used to solve the attendant problem of cache and memory coherence. A design and debugging tool based on Petri net simulation was developed to evaluate detailed models of the controllers implementing the cache coherence protocol. The Petri net simulator is completely general, but is particularly adept at representing concurrency and synchronization; a necessity for modeling parallel computer architectures.

Performance evaluation of the architecture under study was accomplished with object-oriented discrete event simulation. The overall performance of a bus-based multiprocessor is heavily dependent on the performance of cache memory, since the system buses are potential bottlenecks. Two simulation models were developed. The first, a purely probabilistic model, can be used to quickly explore a wide range of system configurations and parameters. A second, more detailed, trace-driven model accurately represents the activities and state of a single cluster of processors. Trace-driven simulation is necessary in evaluating the hierarchical bus multiprocessor since

the performance of cache memory is highly dependent on the pattern of memory accesses. A method of gathering architecture independent multiprocessor address traces on a conventional uniprocessor was developed to facilitate trace-driven simulation.

Simulation indicates the hierarchical bus architecture increases the ultimate size of bus-based multiprocessors by nearly an order of magnitude to approximately 200 processors. Detailed Petri net modeling and simulation suggests the feasibility of the controllers and the correctness of the cache coherence protocol.

To my parents, and Mary Caroline O'Neill

## Acknowledgments

This research and the degree it represents would not have been possible were it not for my dual thesis advisors, Dr. Mani Azimi and Professor Lionel Ni. The time spent with Mani in front of workstations, at the chalk board, and over numerous dinners has been distilled into this thesis. For all the knowledge I have absorbed, both technical and non-technical, and for our friendship, I am most grateful. Dr. Ni has been most generous with his time in the final year and a half of my degree; I have benefited in many ways from his considerable experience and knowledge.

I also appreciate the assistance and interest of my other committee members, Dr. Richard Enbody, Dr. Erik Goodman Dr. John Kreer, Dr. Habib Salehi and Dr. Anthony Wojcik. As chairman of the Electrical Engineering department when I started at Michigan State, Dr. Kreer helped me in many ways, the last being to serve on my thesis committee. Erik gave generously of his time in reviewing my research, and provided financial support through my long and pleasant association with the Case Center.

Working with the numerous people who have been a part of the Case Center for the last five years has been an enjoyable and educational experience. In particular Jackie Carlson, Leslie Hoppensteadt, and Homayoun Torab have made Michigan State a happier place for me.

This research has been supported by the National Science Foundation under grant MIPS 8811815 and by the College of Engineering.

Finally, as the most important people in my life, I acknowledge with love the support of my extended family and in particular my wife, Mary Caroline.

## **Table of Contents**

| Li | List of Tables |          |                                    | x   |

|----|----------------|----------|------------------------------------|-----|

| Li | st of          | Figure   | es                                 | xii |

| 1  | Introduction   |          | on                                 | 1   |

|    | 1.1            | Need f   | or Parallel Processing             | 1   |

|    | 1.2            | Elemen   | nts of Parallel Computers          | 2   |

|    |                | 1.2.1    | Processors                         | 3   |

|    |                | 1.2.2    | Interconnection network            | 3   |

|    |                | 1.2.3    | Memory                             | 4   |

|    | 1.3            | Cache    | Coherence                          | 5   |

|    | 1.4            | Single   | Bus Multiprocessor                 | 5   |

|    | 1.5            | Hierar   | chical Bus Multiprocessor          | 6   |

|    | 1.6            | Perform  | mance Evaluation                   | 8   |

|    |                | 1.6.1    | Queuing networks                   | 8   |

|    |                | 1.6.2    | Discrete event simulation          | 10  |

|    | 1.7            | Thesis   | Outline                            | 11  |

|    |                | 1.7.1    | Guide to chapters                  | 12  |

| 2  | Cac            | he Col   | nerence                            | 16  |

|    | 2.1            | Definit  | ion of Cache Coherence Problem     | 16  |

|    | 2.2            | Examp    | ble of Cache Coherence Problem     | 18  |

|    | 2.3            | Solution | ons to the Cache Coherence Problem | 20  |

|    |                | 2.3.1    | Software solutions                 | 20  |

|    |                | 2.3.2    | Hardware solutions                 | 21  |

|    |                | 2.3.3    | Single bus snoopy protocols        | 22  |

| 3 | Arc        | chitecture of the HBSM Multiprocessor | 25         |  |

|---|------------|---------------------------------------|------------|--|

|   | 3.1        | Introduction                          | <b>2</b> 5 |  |

|   | 3.2        | System Controllers                    | 28         |  |

|   |            | 3.2.1 Cache Controller (CC)           | <b>3</b> 0 |  |

|   |            | 3.2.2 Memory Controller (MC)          | <b>3</b> 0 |  |

|   |            | 3.2.3 Cluster Cache Controller (CCC)  | 31         |  |

|   |            | 3.2.4 Cluster Memory Controller (CMC) | 33         |  |

|   |            | 3.2.5 CCC/CMC state mapping           | <b>3</b> 5 |  |

|   | 3.3        | Interference Events                   | <b>3</b> 6 |  |

|   |            | 3.3.1 Collision events                | 37         |  |

|   |            | 3.3.2 Benign events                   | 38         |  |

|   |            | 3.3.3 Coherence events                | <b>3</b> 8 |  |

|   |            | 3.3.4 CMC and interference events     | <b>3</b> 9 |  |

|   |            | 3.3.5 CCC and interference events     | <b>3</b> 9 |  |

|   | 3.4        | Bus Arbitration                       | 41         |  |

| 4 | СО         | COGI Cache Coherence Protocol         |            |  |

|   | 4.1        | Design of COGI Protocol               | 42         |  |

|   | 4.2        | COGI Protocol Tables                  | 43         |  |

|   | 4.3        | Example of COGI Protocol              | 53         |  |

|   | 4.4        | Other Protocols                       | 57         |  |

| 5 | Mu         | ltiprocessor Address Traces           | 58         |  |

|   | 5.1        | Introduction                          | 58         |  |

|   |            | 5.1.1 Tracing techniques              | 60         |  |

|   | 5.2        | The Traced Application                | 61         |  |

|   | <b>5.3</b> | Trace Generation                      | 64         |  |

|   |            | 5.3.1 Expanding assembly language     | 64         |  |

|   |            | 5.3.2 Compile and execute             | 67         |  |

|   |            | 5.3.3 Filter raw traces               | 67         |  |

|   | 5.4        | Extension of Tracer                   | 70         |  |

| 6 | Pet        | ri Net Model                          | 73         |  |

|   | 6.1        | Petri Net Modeling                    | 73         |  |

|   |            | 6.1.1 Extensions                      | 75         |  |

|   |      | 6.1.2  | Software packages             |

|---|------|--------|-------------------------------|

|   | 6.2  | High I | Level Timed Petri Nets        |

|   |      | 6.2.1  | Places                        |

|   |      | 6.2.2  | Directory places              |

|   |      | 6.2.3  | Transitions                   |

|   |      | 6.2.4  | Connectivity                  |

|   | 6.3  | HLTP   | N Simulator                   |

|   | 6.4  | HBSM   | Multiprocessor Model          |

|   |      | 6.4.1  | Processors                    |

|   |      | 6.4.2  | Synchronization               |

|   |      | 6.4.3  | Bus arbitration               |

|   |      | 6.4.4  | Directories                   |

|   | 6.5  | Design | and Debugging                 |

|   |      | 6.5.1  | Correctness                   |

| 7 | Disc | rete E | Event Simulation 94           |

|   | 7.1  | Introd | uction                        |

|   | 7.2  | Simula | ation Environment             |

|   |      | 7.2.1  | Multiprocessor models         |

|   |      | 7.2.2  | System parameters             |

|   |      | 7.2.3  | Measures of performance       |

|   |      | 7.2.4  | Correctness                   |

|   | 7.3  | Proba  | bilistic Model                |

|   |      | 7.3.1  | Single cluster                |

|   |      | 7.3.2  | Multiple cluster              |

|   | 7.4  | Trace- | driven Model                  |

|   |      | 7.4.1  | Intercluster activity         |

|   |      | 7.4.2  | Benchmark parallel merge sort |

|   |      | 7.4.3  | Results for 8×8 system        |

|   |      | 7.4.4  | Cache geometry                |

|   |      | 7.4.5  | Coherence traffic             |

|   | 7.5  | Summ   | arv                           |

| 8  | Conclusions and Future Research |                                      |     |  |  |

|----|---------------------------------|--------------------------------------|-----|--|--|

|    | 8.1                             | HBSM Multiprocessor Architecture     | 143 |  |  |

|    |                                 | 8.1.1 Performance improvements       | 145 |  |  |

|    |                                 | 8.1.2 System requirements            | 146 |  |  |

|    | 8.2                             | High Level Timed Petri Net Simulator | 147 |  |  |

|    | 8. <b>3</b>                     | Simulation Methodology               | 148 |  |  |

| Bi | bliog                           | graphy                               | 150 |  |  |

## List of Tables

| 2.1 | Important stages in the evolution of snoopy cache coherence protocols.  | 23  |

|-----|-------------------------------------------------------------------------|-----|

| 3.1 | The state of blocks in the CC.                                          | 31  |

| 3.2 | The state of blocks in the CCC                                          | 32  |

| 3.3 | The state of blocks in the CMC                                          | 34  |

| 3.4 | Mapping of CMC states to CCC and CC                                     | 36  |

| 3.5 | Mapping of CCC states to CMC and CC                                     | 36  |

| 3.6 | Coherence events detected by the CCC and their resolution               | 41  |

| 4.1 | Transaction types on the cluster bus and processor events               | 44  |

| 4.2 | Transaction types on the global bus.                                    | 44  |

| 4.3 | Actions of CC in response to processor requests                         | 46  |

| 4.4 | Actions of CC in response to cluster bus transactions                   | 47  |

| 4.5 | Actions of CMC in response to cluster bus transactions                  | 48  |

| 4.6 | Actions of CMC in response to global bus transactions                   | 49  |

| 4.7 | Actions of CCC in response to cluster bus transactions                  | 50  |

| 4.8 | Actions of CCC in response to global bus transactions                   | 51  |

| 4.9 | Actions of MC in response to bus transactions                           | 52  |

| 5.1 | Tracer library functions for barrier synchronization and tracing        | 63  |

| 7.1 | Technology dependent system parameters for simulation model             | 101 |

| 7.2 | Probabilistic representation of memory accesses                         | 102 |

| 7.3 | Techniques of increasing confidence in correctness of models            | 106 |

| 7.4 | Probabilistic parameters for simulation of first model                  | 108 |

| 7.5 | Effect of hit ratio on multiprocessor cycles per instruction (MCPI) for |     |

|     | single cluster multiprocessor Experiment 1                              | 112 |

| 7.6  | Multiprocessor cycles per instruction (MCPI) for ideal application Ex- |     |

|------|------------------------------------------------------------------------|-----|

|      | periment 5                                                             | 118 |

| 7.7  | Multiprocessor cycles per instruction (MCPI) for non-ideal application |     |

|      | Experiment 6                                                           | 120 |

| 7.8  | Cases of intercluster transactions in COGI protocol                    | 125 |

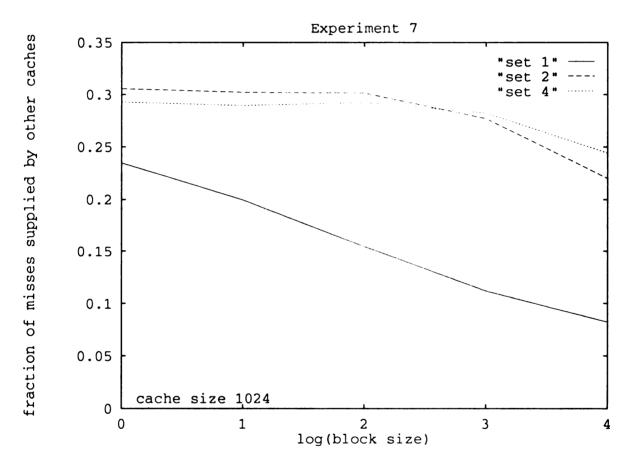

| 7.9  | Experiment 7 multiprocessor cycles per instruction (MCPI) data for     |     |

|      | set size 2                                                             | 133 |

| 7.10 | Experiment 7 distribution of cluster bus busy time                     | 139 |

## List of Figures

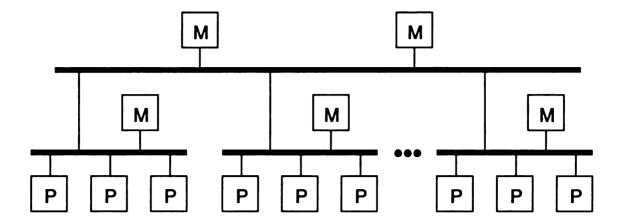

| 1.1        | Generalized two-level hierarchical bus multiprocessor                                | 7  |

|------------|--------------------------------------------------------------------------------------|----|

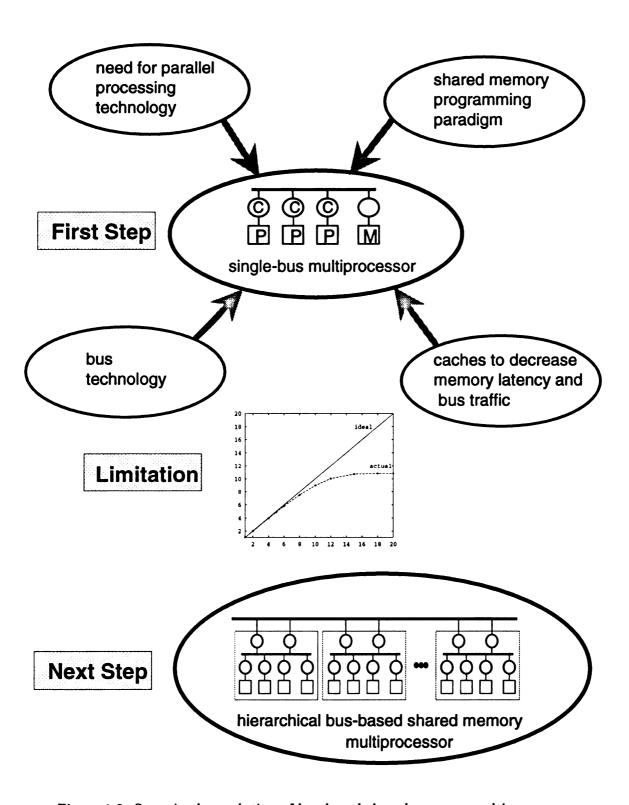

| 1.2        | Steps in the evolution of bus-based shared memory multiprocessors                    | 13 |

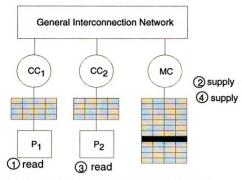

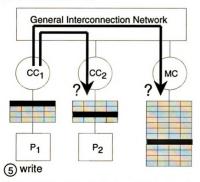

| 2.1        | Simple multiprocessor scenario to demonstrate cache coherence problem.               | 19 |

| 3.1        | Components of the Hierarchical Bus Shared Memory (HBSM) multi-                       |    |

|            | processor architecture                                                               | 27 |

| 3.2        | Detail of the CCC dual-bus snoop device showing the two active por-                  |    |

|            | tions of the controller, cluster snoop and global snoop, sharing access              |    |

|            | to the single cache directory                                                        | 29 |

| 3.3        | Meaning of the block states of the CCC                                               | 32 |

| 3.4        | Meaning of the block states of the CMC                                               | 34 |

| 4.1        | Basic scenario of intracluster sharing of locally resident block. Pro-               |    |

|            | cessor $P_1$ reads block, $P_10$ reads then writes block, passing updated            |    |

|            | version of data word to $P_1$                                                        | 54 |

| 4.2        | Continuation of the COGI protocol example transaction. Processor                     |    |

|            | $P_{2,1}$ reads then writes the same block that is shared with Cluster 1             | 56 |

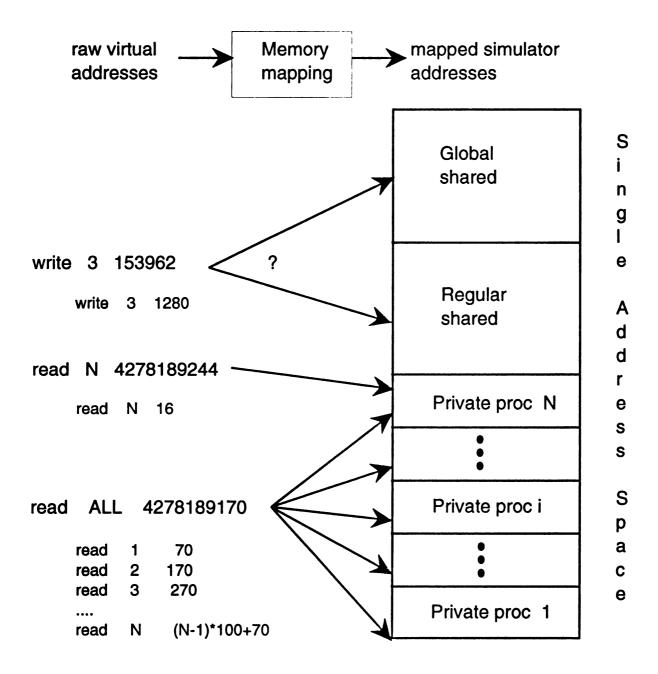

| 5.1        | Traced multiprocessor address space. Raw virtual references are shown                |    |

|            | with resulting filtered references below them and indented                           | 62 |

| <b>5.2</b> | C template for process creation and synchronization                                  | 65 |

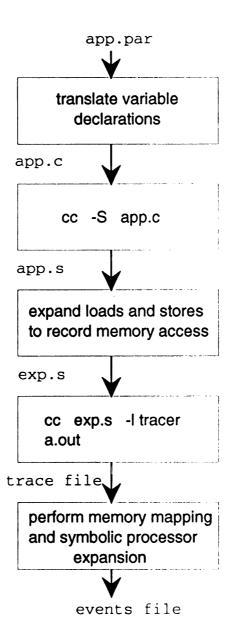

| 5.3        | The steps of the Tracer technique                                                    | 66 |

| 5.4        | Expanded assembly code (in two columns) shown below original assembly code fragment. | 68 |

| E          |                                                                                      | UO |

| 5.5        | Problem of extending Tracer to general synchronization and task allo-                | 71 |

|            | cation paradigm.                                                                     | 71 |

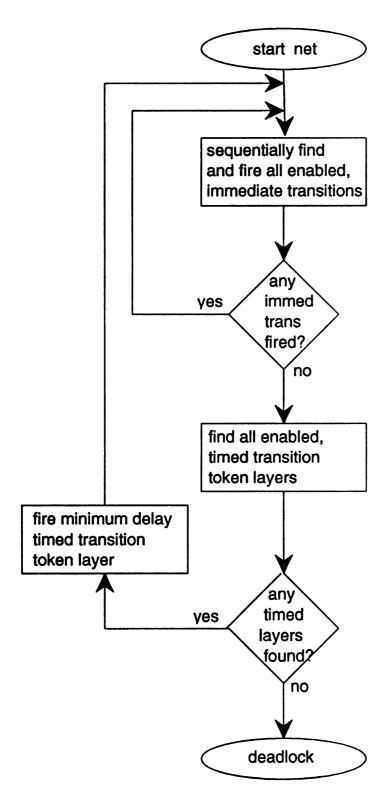

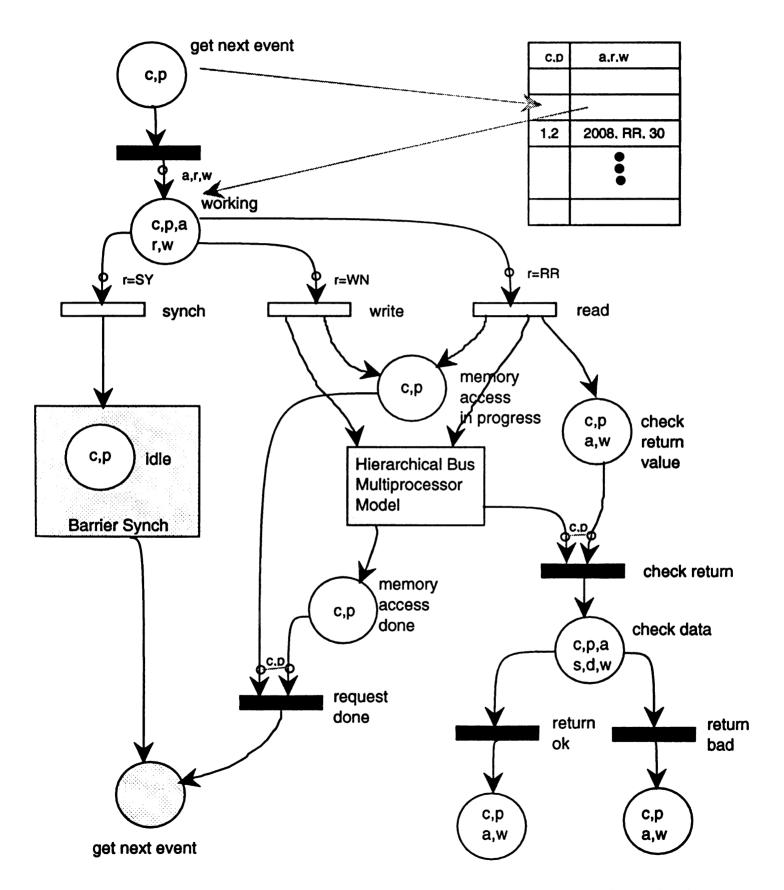

| 6.1        | Main loop of HLTPN simulator                                                         | 82 |

| 6.2  | HLTPN model representing the actions of processors in the hierarchical      |      |

|------|-----------------------------------------------------------------------------|------|

|      | bus multiprocessor                                                          | 84   |

| 6.3  | HLTPN subnet of barrier synchronization in the hierarchical bus mul-        |      |

|      | tiprocessor model                                                           | 86   |

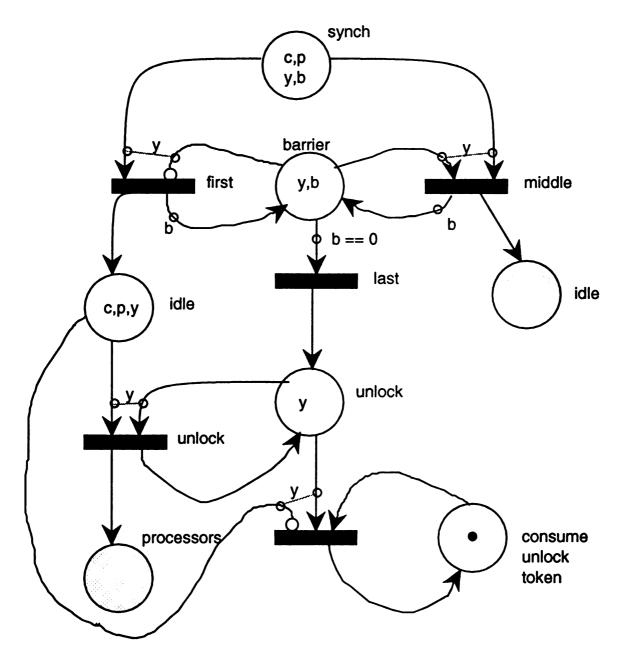

| 6.4  | HLTPN subnet of bus arbitration for HBSM multiprocessor                     | 88   |

| 6.5  | Set associative and direct mapped directories for a 2 cluster, 2 proces-    |      |

|      | sor/cluster hierarchical cache system model                                 | 89   |

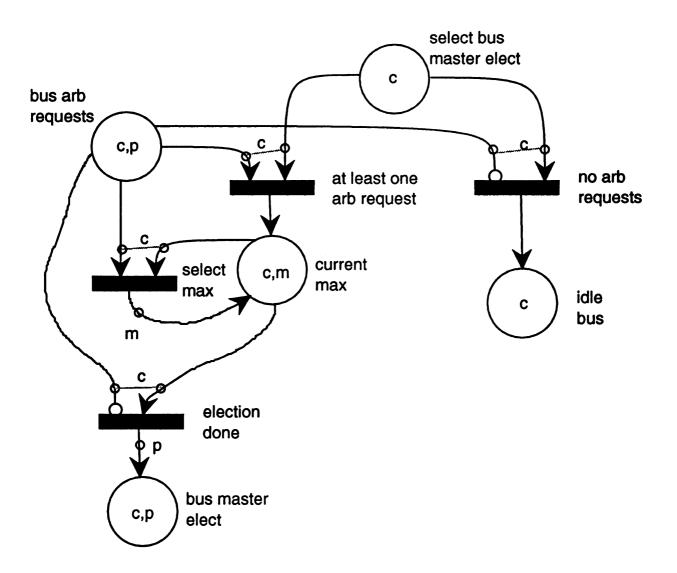

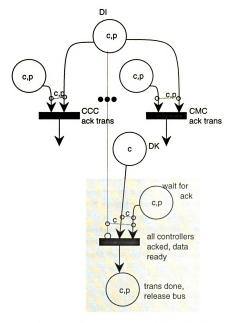

| 6.6  | Bus handshaking signals DI and DK in Petri net model                        | 92   |

| 7.1  | Simulation loop for event scheduled DES using C-like pseudo code            | 96   |

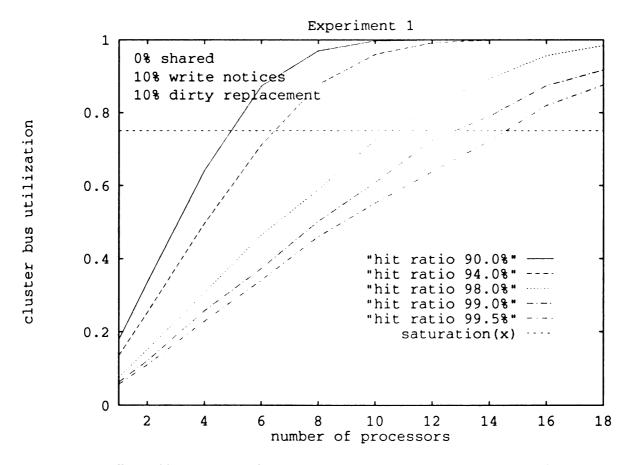

| 7.2  | Effect of hit ratio on cluster bus utilization for single cluster multipro- |      |

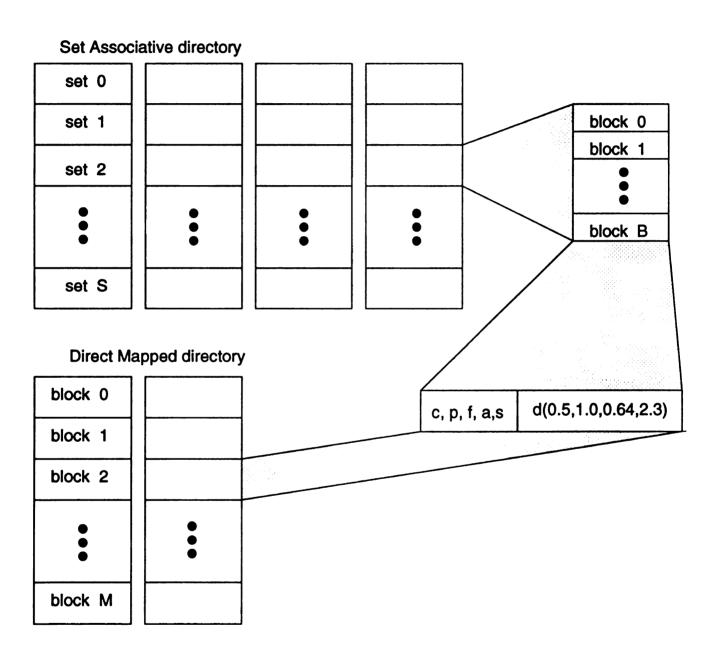

|      | cessor                                                                      | 109  |

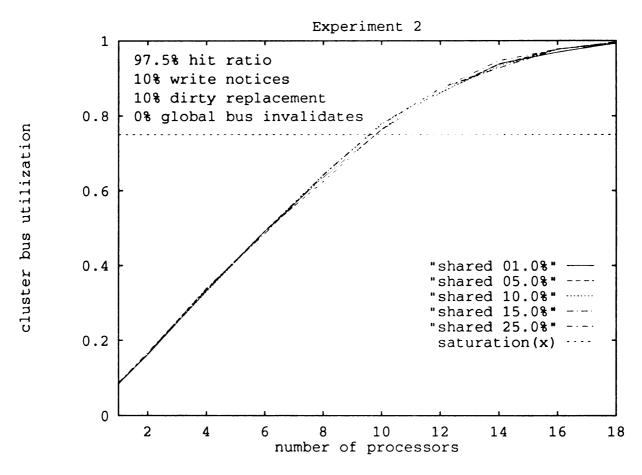

| 7.3  | Effect of global accesses on cluster bus utilization for single cluster     |      |

|      | multiprocessor                                                              | 111  |

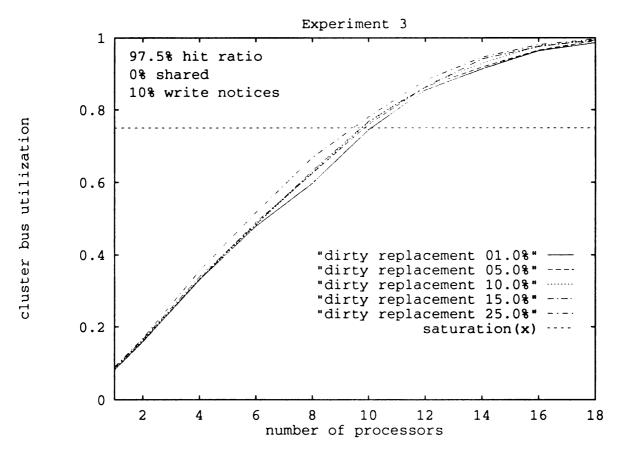

| 7.4  | Effect of dirty write-back probability on cluster bus utilization in single |      |

|      | cluster multiprocessor                                                      | 113  |

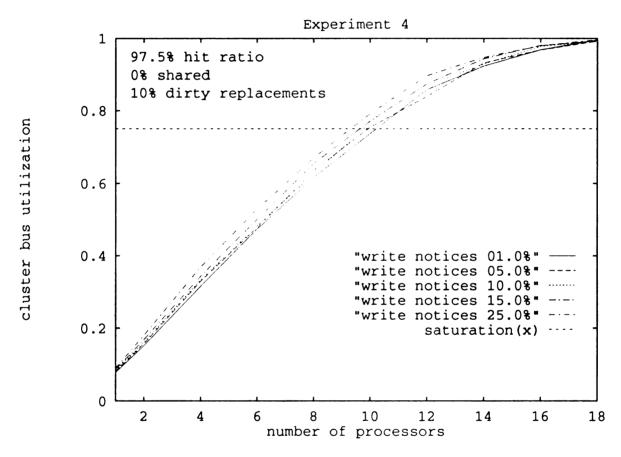

| 7.5  | Effect of write notice probability on cluster bus utilization in single     |      |

|      | cluster multiprocessor                                                      | 114  |

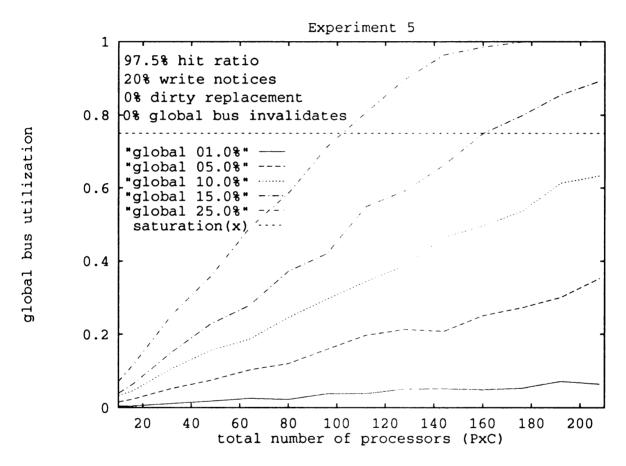

| 7.6  | Global bus utilization in ideal application                                 | 116  |

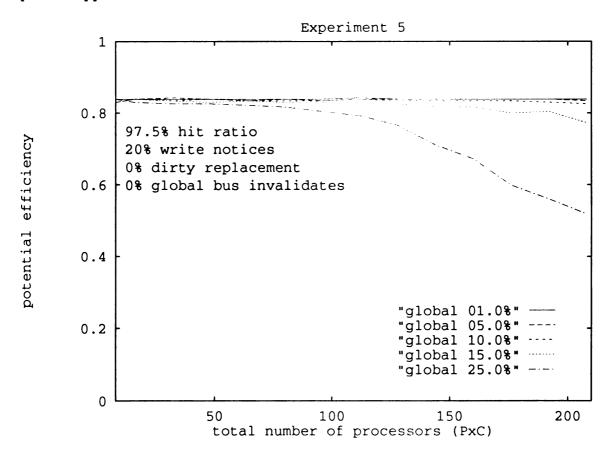

| 7.7  | Potential efficiency for ideal application                                  | 117  |

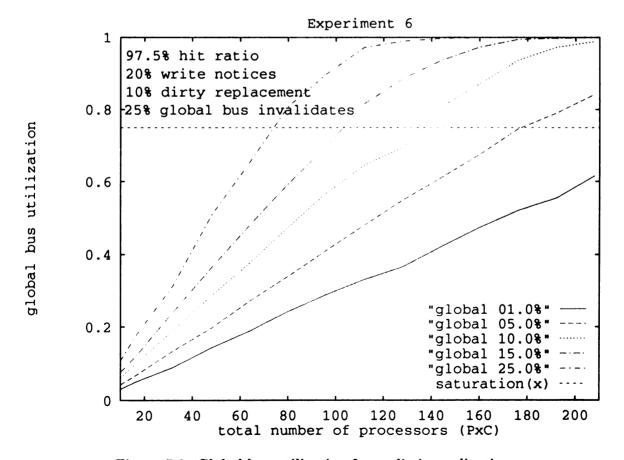

| 7.8  | Global bus utilization for realistic application                            | 119  |

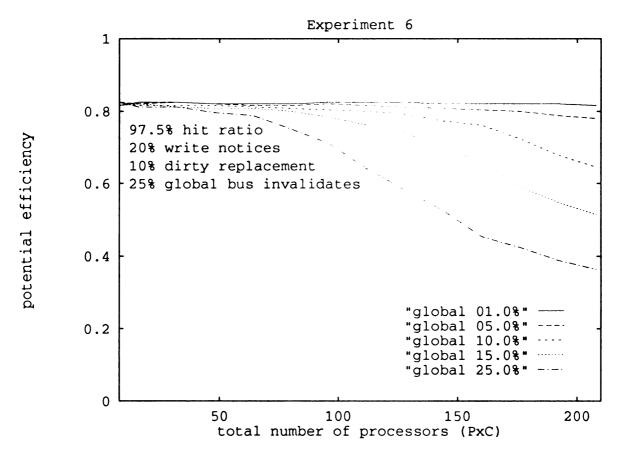

| 7.9  | Potential efficiency for realistic application                              | 121  |

| 7.10 | The benchmark parallel merge sort used for traces in the hybrid model       | 128  |

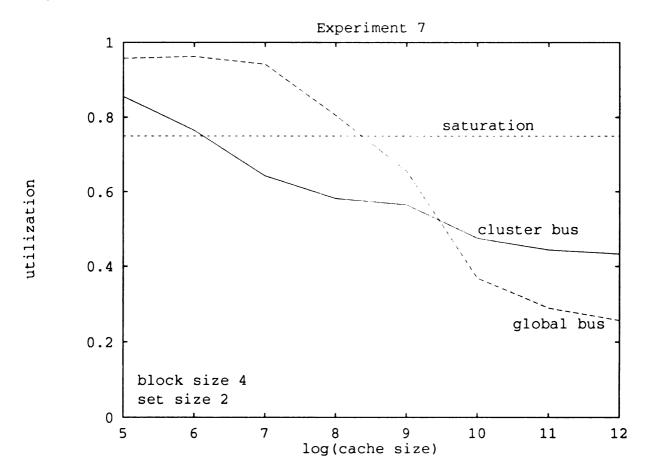

| 7.11 | Bus utilizations in typical configuration of block size 4, set size 2       | 129  |

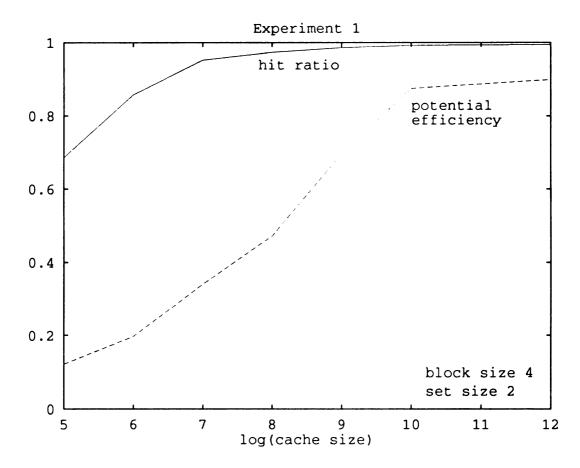

| 7.12 | Hit ratio and potential efficiency in typical configuration of block size   |      |

|      | 4, set size 2                                                               | 130  |

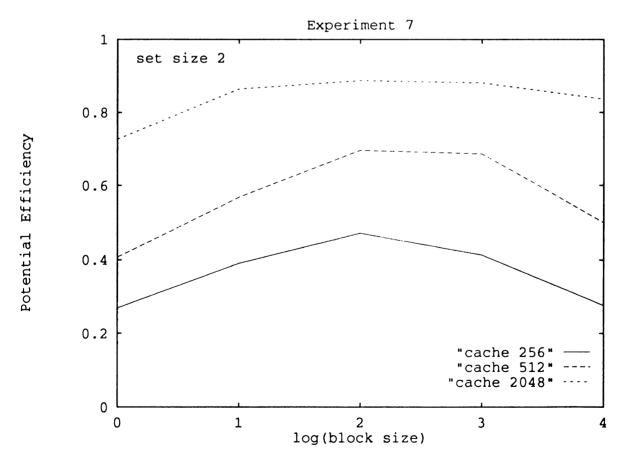

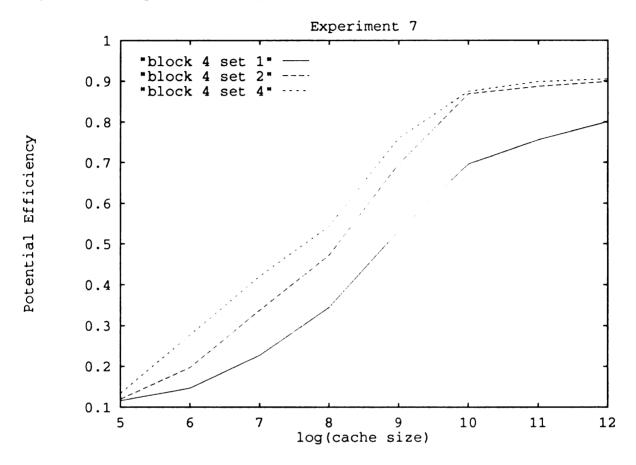

| 7.13 | Effect of block size on potential efficiency for set size 2                 | 133  |

| 7.14 | Effect of set size on potential efficiency for optimal block size           | 134  |

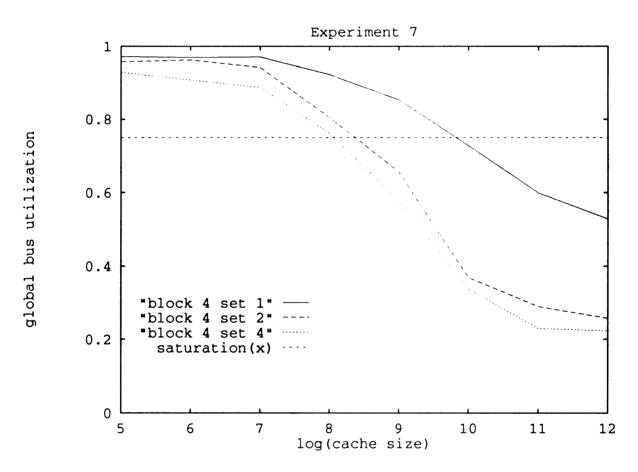

| 7.15 | Effect of set size on global bus utilization for block size 4               | 135  |

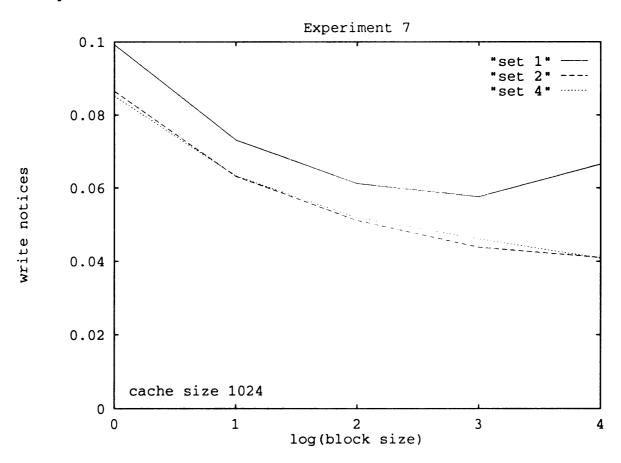

| 7.16 | Fraction of cache writes which generate a cluster bus write notice          | 136  |

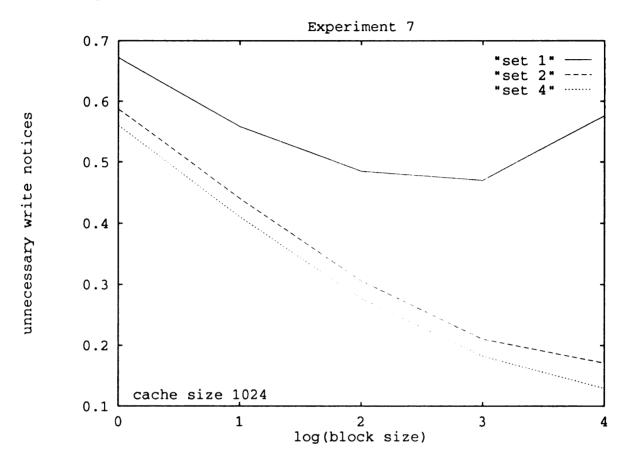

| 7.17 | Fraction of write notices to blocks which are not shared by other caches    | .137 |

| 7.18 | Fraction of read misses which are serviced by another cache with a          |      |

|      | dirty copy of the block                                                     | 138  |

## Chapter 1

## Introduction

This thesis describes the design and performance of the hardware controllers and cache coherence protocol which together comprise the memory subsystem of a hierarchical bus shared memory multiprocessor. The architecture studied represents a logical evolutionary step in the inevitable ascendancy of parallel processing in computationally intensive application domains such as scientific computing. The inevitable need for parallel computers and the basic elements of these machines is outlined in this introductory chapter. The first generation of single bus multiprocessors are considered, and the natural extension of a hierarchical bus architecture is described. The contributions of this thesis are a solution to the problem of cache coherence in a hierarchical bus multiprocessor and performance evaluation techniques for trace-driven simulation. The final section summarizes the strategy underlying this work and the contents of the remaining chapters.

### 1.1 Need for Parallel Processing

The eventual use of parallel processing technology is assured by the limitless need for computational power and the inherent physical limits of sequential computers. The areas of research that could benefit from faster, more efficient computers is as large as the number of fields being studied with computers. Classic examples of applications which are limited by available computing power include numerical weather forecasting, computational fluid dynamics, finite element analysis, and image processing. The future will undoubtedly bring uses for the computer which are as yet unimagined, and which will require vast computational power.

The computational power of traditional von Neumann architecture uniprocessor computers is limited by the speed of light. Signal transmission speed in silicon is actually ten times slower than the speed of light in a vacuum  $(3 \times 10^8 m/sec)$  [18]. At this rate, a signal can only propagate 3 cm in  $10^{-9}sec$ . As the clock rate of the fastest supercomputers [15] approaches  $10^{-9}sec$ , practical constraints on packaging and cooling

will begin to limit their computational power. If such supercomputers were restricted to purely sequential architectures, then executing one floating-point operation per clock cycle would imply a limit of 1000 MFLOPS (millions of floating-point operations per second). In fact, extant supercomputers, and those announced for the near future, rely on low-level parallel processing techniques known as pipelining and vector processing to increase their maximum potential speed beyond 1000 MFLOPS. Materials more exotic than silicon (such as gallium arsenide) may have a smaller propagation time, but are nevertheless eventually limited by the speed of light.

Where will computer engineers of the future find the performance improvements necessary to satisfy the voracious appetite for computational power of scientific applications? Whatever the technology, if the speed at which information can be processed is limited, then the only method of processing a constant amount of information in less time is to perform multiple operations simultaneously. Coordinated, simultaneous work by multiple processors is the essence of parallel processing. Implementations of parallel computers range from large numbers of slow processors to small numbers of fast processors. Hennessy and Patterson [30] refer to the El Dorado¹ of parallel processing as large numbers of powerful processors in the same computer. The two distinct roads to this El Dorado are exemplified by the 8 processor Cray Y-MP from Cray Research and the 65,536 bit-serial processor CM-2 from Thinking Machines.

The key to parallel architectures which follow the Cray Y-MP path is scalability. In practical terms, scalability is usually judged over a range. For example, binary hypercube multicomputers may scale well over the range of 10 to 10,000 processors, but packaging, cooling, and other mundane constraints may make hypercubes impractical outside of this range. Parallel computers which rely on a shared bus as an interconnection network have shown very limited scalability. Such computers are limited by bus bandwidth to around 30 processors; in other words, single bus parallel computers are scalable over less than an order of magnitude.

## 1.2 Elements of Parallel Computers

The fundamental elements of parallel computers are processors, memory, and an interconnection network. The interconnection network serves to connect processors

<sup>&</sup>lt;sup>1</sup>El Dorado refers to a city of fabulous riches in South America for which Spanish explorers of the 16th century searched in vain.

to other processors as well as to memory modules.

#### 1.2.1 Processors

Processing elements in parallel computers range from the most powerful pipelined vector processors (Cray Y-MP, IBM 3090) made with expensive, fast bipolar semi-conductor technology, to the bit-serial, slow, CMOS processing elements of the CM-2. In between these extremes are the high performance RISC microprocessors, such as the Intel i860, Motorola 88000, Sun Microsystems SPARC, and MIPS R3000. Supercomputer processors are designed to be as fast as possible with almost no regard for expense. They are heavily pipelined and support vector instructions. Clock cycle times in such machines are now around  $4 \times 10^{-9} sec$ , with sustained performance around 20–30 MFLOPS. Such processors often require elaborate packaging and cooling support, and are never made in large quantities. Most of the supercomputers offered today, and all that are being planned, are available in models with multiple processors [15].

The single chip, VLSI microprocessors with around  $10^6$  transistors offer the most economical method of building powerful parallel computers with hundreds to thousands of processors. They often include one or more of on-chip data and instruction caches, floating point and integer processors, and memory management units. Mass production of these off-the-shelf components reduces their price, and they generally do not require any special cooling or packaging. Their clock cycle times range from  $12.5 \times 10^{-9}$  to  $40 \times 10^{-9} sec$ , and their sustained performance ranges between 2-8 MFLOPS.

#### 1.2.2 Interconnection network

Of the three elements of any parallel computer, the interconnection network is likely the hardest to make scalable. The methods proposed for connecting processors and memories are numerous. Some common interconnection networks include bus, ring, star, tree, mesh, torus, crossbar, and hypercube. Each of these (and the many other possibilities) can be classified by their connectivity, degree, and cost. The bus and crossbar are fully connected with respect to memory; each processor is directly connected to every memory module. The bus has lower cost and lower performance than the crossbar, since each processor node has only one connection (degree one)

and all processors share the same path to all memory modules. With a crossbar, on the other hand, each processor has a direct connection to each memory module, thereby increasing the degree of each node, the cost, and hopefully the performance. In general, increasing the connectivity or the degree of the interconnection network increases the potential performance of the system at the expense of greater complexity and cost.

#### **1.2.3** Memory

Parallel processors can be described by two views of memory: hardware and software. Physically, memory in a parallel processor can be distributed or centralized. Centralized memory may become the bottleneck of the entire computer, limiting the scalability of the architecture. From a software perspective, memory can either be shared or non-shared. Shared memory is seen as the more desirable programming paradigm, since interprocessor communication can take place within the single, shared address space. Non-shared memory programming involves explicit forms of communication (message passing) and can be efficiently emulated on a shared memory machine. Gordon Bell coined the terms multiprocessor to refer to shared memory parallel processors and multicomputer to refer to non-shared memory parallel processors [7]. Bell termed bus-based multiprocessors built from powerful microprocessors multis and predicted that these machines would represent the fifth generation of computing.

The disparate progression of memory and processor technology has resulted in a memory latency problem [30]. The speed of dynamic random access memory (RAM) has grown steadily at a 7% annual rate since 1980. Over the same time period, processor speed has increased at a rate of 19–26% before 1985 and 50–100% rate after 1985. The solution to this mismatch in speed has been a memory hierarchy. Small, fast static random access memories known as caches are placed close to the processor, and serve as a buffer to the larger, slower dynamic RAMs used in main memory. Computer programs generally exhibit both spatial and temporal locality, that is, the memory locations that will be accessed in the near future have a high probability of being physically close in the address space (or the identical) to those accessed in the recent past. The principles of locality assure that a large proportion of memory accesses will be satisfied by the faster but smaller cache, thus decreasing the overall memory latency.

#### 1.3 Cache Coherence

Computers with cache memories may have multiple copies of the same block of memory existing at the same time. These multiple copies of a memory block lead to the problem of cache coherence. A scheme for preserving the correctness of the system in the face of multiple copies of memory blocks is known as a cache coherence protocol. On a uniprocessor, a cache coherence protocol may be as simple as requiring that blocks in the cache which have been modified be written back to main memory before they are replaced in the cache. Input/output operations may also affect cache coherence in a uniprocessor. Cache coherence in a multiprocessor is more complicated, because copies of blocks may exist in multiple caches as well as main memory. The actions of all processors must be coordinated to maintain memory and cache coherence.

Centralized solutions to the multiprocessor cache coherence problem (e.g. a single table and controller) are undesirable because the centralized resource is likely to become a system bottleneck. A distributed solution to the cache coherence problem requires that each processor know what actions every other processor is taking, and respond accordingly. A major advantage of the bus-based multiprocessor class identified by Bell is that it admits a distributed, hardware solution to the cache coherence problem. The set of snoopy cache coherence protocols hinges on the ability of each processor to react to the transactions of every other processor by monitoring the bus. By snooping on the bus, each processor receives the same information at the same time, and can take actions to preserve coherence based on this information and the cache coherence protocol. The bus serves to serialize access to the memory assuring that no more than one transaction can take place at any given time, and that all processors have the same knowledge of the system.

### 1.4 Single Bus Multiprocessor

The single shared bus was a natural choice of interconnection network for the first multiprocessors. The shared bus was inexpensive, fully connected, and a known technology. Computer engineers were familiar with existing bus standards and interfacing techniques. Multiprocessors built on shared buses could be sold in small configurations and later upgraded by adding processors. The full connectivity of the

bus allowed for simpler, centralized memories. Centralized memories, in turn, made the shared memory software paradigm easier to implement. Early commercial multiprocessors built on a single bus include the Symmetry and Balance from Sequent Computer Systems, the Multimax from Encore Computer, the N+1 from Synapse Computer, FX/80 from Alliant Computer Systems, the Sequoia from Sequoia Systems, and the System 64000 from ELXSI. More recently, shared memory bus-based multiprocessors have been used in powerful graphics workstations from Stardent and Silicon Graphics, and as compute and file servers by MIPS, Solbourne, Compaq Computer, and Digital Equipment Corporation.

In addition to reducing memory latency, cache memory plays an equally important role in bus-based multiprocessors by reducing accesses to memory. Single bus multiprocessors without caches would be limited in size to only a few processors. If every memory access by every processor had to go across the single shared bus, the bus would soon become the system bottleneck. Instead, by buffering the bus from every memory access, caches allow the available bus bandwidth to be shared among more processors. Even with cache, the ultimate size of single bus multiprocessors is between 20 and 30 processors. Scalability after this point is limited by the bandwidth of the bus.

### 1.5 Hierarchical Bus Multiprocessor

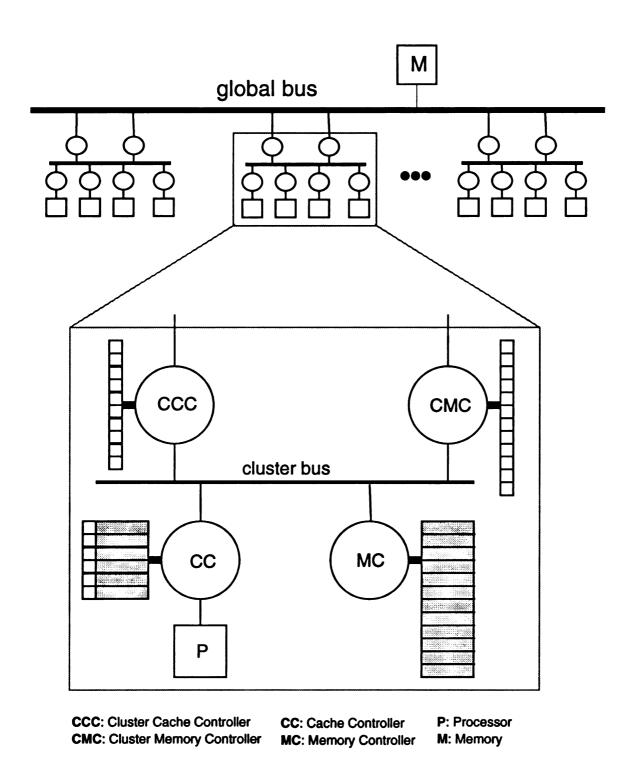

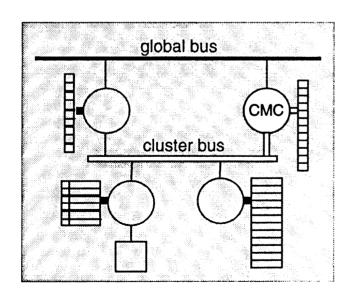

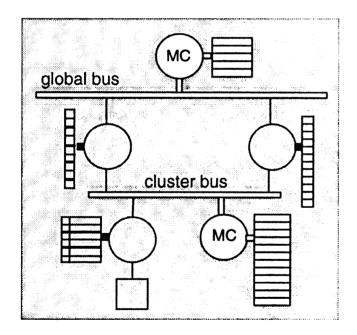

The use of caches to reduce traffic on the bus increased the ultimate size of single bus multiprocessors an order of magnitude, from 2-3 processors to 20-30 processors. A logical means of further increasing the scalability of bus-based multiprocessors is to form a hierarchy of single bus multis. A two level hierarchical bus multiprocessor would have several clusters of processors joined by a single global bus. Each cluster would be equivalent to a single bus multiprocessor. Memory could be either distributed among clusters or centralized on the global bus. Figure 1.1 shows the general arrangement of processors and memory in a two-level hierarchical bus shared memory (HBSM) multiprocessor. Processors are gathered into clusters organized around a single bus; memory is distributed throughout the entire system. Such a machine should be able to scale into the hundreds of processors, thus increasing the ultimate size of bus-based multiprocessors an additional order of magnitude.

The Cm\* multiprocessor developed at Carnegie Mellon in the 1970s is the most

Figure 1.1: Generalized two-level hierarchical bus multiprocessor.

historically significant hierarchical bus architecture. The Cm\* was made up of clusters of up to 14 processor/memory modules sharing a single bus and a custom controller. Clusters were joined to one another with two global buses. The custom controller maintained the illusion of a single shared memory address space. Any of the DEC LSI-11 processors could access any other processor's memory module, but the memory latency ratio of 1:3:9 (local:same cluster:different cluster) placed a premium on intercluster accesses. A 50 processor, 5 cluster Cm\* machine was built and operated.

Cm\* showed the feasibility of a bus architecture which was designed to take advantage of locality of reference by attaining linear speed-up on such clusterable applications as partial differential equations. The lack of cache memory simplified the role of the custom controller and eliminated the need for a cache coherence protocol. Amortizing the cost of the custom controller across the 10-14 processors in a cluster allowed it to be more powerful and expensive than if each processor were required to have its own controller. A buffered, packet switching bus protocol was used to avoid deadlocks over bus allocation. Not having to worry about a cache coherence problem made implementation of such a split-transaction protocol feasible.

Two ongoing research projects featuring hierarchical bus multiprocessor architectures have been reported in the literature. In a project known as the Ultramax [8, 56], Encore Computer, with DARPA funding, has made the logical extension to their Multimax architecture by joining single bus clusters of 16 processors with a global bus. The Ultramax uses large caches between the clusters and the global bus, and memory that is physically distributed among clusters.

The Data Diffusion Machine [29], from the Swedish Institute of Computer Science, is built around a multi-level hierarchical bus architecture. Processor caches at the lowest level of the hierarchy form the only system memory in the DDM. Caches at higher levels hold only status information, not data. The most novel aspect of the DDM is that shared memory data blocks are not considered to have a particular home location. Instead, data blocks migrate to where they are needed, living in caches at all times, without a home memory module for permanent residence.

#### 1.6 Performance Evaluation

To be credible, a proposal for a new computer architecture must be accompanied by evidence of realistic requirements for and correct operation of system components. To be of interest, new computer architectures must show promise of increased performance. Two strategies were pursued to evaluate the HBSM multiprocessor architecture. Detailed Petri net models were used to design and debug the cache coherence protocol and controllers. Discrete event simulation of purely probabilistic and tracedriven models provided estimates of broad measures of performance of the protocol and the architecture.

### 1.6.1 Queuing networks

The main advantage of queueing networks is the balance between accuracy and efficiency which they provide. The close correspondence between certain aspects of computer systems and networks of queues eases the task of developing a queuing network model. Algorithms such as Mean Value Analysis are available for which the analysis of queuing network models is computationally proportional to the product of the number of queues and the number of customer classes. Use of such economical algorithms depends on being able to accurately represent the system under study with a class of models known as product form queuing networks. A further advantage is the fact that the number of parameters which must be obtained to characterize a system being modeled with product form queueing networks is relatively small. Queuing network models have been successfully applied to the analysis of high level computer system models where questions of capacity planning and overall system performance must be addressed.

If the system under study can not be adequately represented by product form networks, then a general network of queues can be employed. Unfortunately, analysis of such general networks is computationally very expensive; the amount of work required for analytical solutions rises exponentially with the size of the model. Simulation of queueing network models is an alternative in such cases, but is also computationally intensive and requires very careful characterization of the system under study to determine model parameters. For approximately the same investment in model development and simulation time, a more general discrete event simulation of the system under study can be made.

The main difficulty in using queuing networks for performance evaluation is that exact solutions to models exist only for product form, or separable, networks. Product form networks must be composed solely of first-come-first-served queues with exponential, class-independent service times. FCFS queues with exponential service times are not sufficient for accurately modeling the memory subsystem of a multiprocessor. As a result, approximate solutions to non-product form networks (those with a wider range of service times and disciplines) must be found. Sauer and Chandy [45] outline two approaches to this problem. The first is to simply apply the product form solutions to the non-product form model. In some cases, Reiser has shown that this approach can yield results close to the exact solutions [43]. The conditions under which this strategy yields results close to the exact solution are for queuing networks with large populations of customers. This requirement is not met for a model of the HBSM multiprocessor, since the number of customers in the entire model would simply be the number of processors being modeled. On average, most queues would never see more than one customer enqueued at a time.

The second approach to solution of non-product form networks is known as aggregation. While no known bounds exist for the error incurred by using aggregation, Lazowska, et al claim that a large body of empirical evidence exists to show that results from aggregation are usually close to the exact results [35]. The empirical evidence cited comes from the field of computer systems modeling and capacity planning. Unfortunately, the number of customers in a queuing network model of the HBSM multiprocessor would be so small, compared to the computer system models mentioned, that the error involved with aggregation is much more uncertain.

Queuing networks are unable to represent some common aspects of computer system behavior such as simultaneous holding of resources. The representation of concurrency is an unfortunate limitation when using queuing networks to model parallel computer systems. Since queuing network models are concerned with average flows in a network of queues, it is difficult to represent resources which must be used exclusively. For example, consider a snooping cache controller competing with a processor for exclusive access to the cache directory. This competition (and the likely locking that accompanies it) has ramifications for the performance of the cache memory subsystem. In a queuing network model of such a cache controller, the use of the cache directory can only be represented as an average flow through the directory queue; competition and locking can not be directly represented.

Modeling with queuing networks is an entirely stochastic approach; the actual memory references recorded in address traces can not be used directly as input to a queuing network model. Increased availability of computer power at decreased cost has boosted the popularity of simulation as the performance evaluation tool of choice. More popular in the past, technological trends and the availability of sophisticated modeling and simulation software have largely displaced queuing networks as a performance evaluation tool for detailed computer architecture studies.

#### 1.6.2 Discrete event simulation

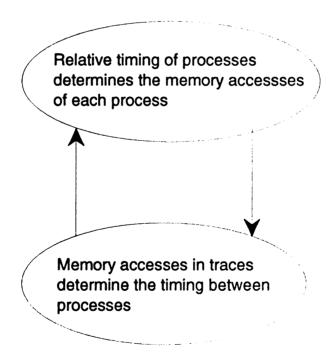

The overall performance of a shared memory multiprocessor depends heavily on the performance of the memory hierarchy. In turn, the performance of the memory hierarchy depends on the memory reference patterns of an application. Interconnection network traffic attributable to the maintenance of cache coherence in particular is very sensitive to the distribution and timing of memory references both within a single processor and between processors. To be accurate, performance evaluation of a cache coherence system (protocol and controllers) must be done with trace-driven simulation. The difficulties of obtaining traces for multiprocessors provided the impetus for the development of a multiprocessor trace gathering technique that can be run on a uniprocessor. A major advantage of the traces generated in this manner are their architectural independence. Address traces are taken at the process level, so the traces are independent of the architecture of the machine generating them. Synchronization artifacts in the traces are avoided by recording the presence of barrier synchronization points in the traces themselves. The simulators that are fed with the traces determine the actual timing of the read, write, and synchronization events

recorded in the traces.

To demonstrate reasonable hardware requirements and to provide some degree of confidence in the correctness of the cache coherence protocol, detailed modeling was performed with high-level, timed Petri nets. The Petri net model accurately represents the complete state of the system controllers, buses, caches and memory modules. Developing this model and running it with multiprocessor address traces was crucial to the design and debugging of the proposed cache coherence protocol. However, the level of detail in the Petri net model precludes its use for trace-driven simulations of adequate length to accurately estimate the potential performance of the HBSM multiprocessor architecture.

Estimates of bus and controller utilization, the chief performance metrics of interest in bus-based multiprocessors, are made using an object-oriented, event scheduled, discrete event simulation developed in the C++ programming language. The C++ simulation is a hybrid approach combining trace-driven simulation and probabilistic models. For applications which are symmetric with respect to clusters, the cache activity on one cluster can be taken to be representative of the activity of all clusters. Simulation time is reduced by simulating the activities of only one cluster. The effect of the interaction between clusters is represented probabilistically in the simulation by pre-processing the address traces and estimating the amount of intercluster activity for each phase of the application.

### 1.7 Thesis Outline

The evolution of bus-based shared memory multiprocessors is depicted in Figure 1.2. The first step taken was to join several processors and a central memory to a single bus via private caches. This first step was motivated by the ever present need for increased computing power, the desirability of the shared memory programming paradigm, and the familiarity of computer engineers with bus technology. The scalability limit of the single bus multiprocessors is the bandwidth of the bus; this unique resource becomes the system bottleneck when the number of processors exceeds about 20. The graph in the middle of Figure 1.2 shows the behavior of speed-up or total compute power of single bus multiprocessors when the bus becomes a system bottleneck. Actual performance saturates at a limit determined by the bus bandwidth, the memory reference patterns, and the size, geometry and speed of caches and memory. Further

additions of processors at this saturation point does not result in further speedup. The natural next step to extend the scalability of bus-based multiprocessors is to form a hierarchy of buses, as shown in the bottom of Figure 1.2.

This thesis describes the design and performance of the hardware controllers and cache coherence protocol of a hierarchical bus shared memory multiprocessor. The first four chapters constitute the background of the problem and the paper design work. The final four chapters represent the work done to evaluate the HBSM multiprocessor architecture.

The cache coherence protocol and controllers developed for the hierarchical bus shared memory architecture are complex entities. Verification of the correctness of such complex, interrelated hardware/software systems remains an open research topic. Trace-driven simulation with an accurate and detailed Petri net model was performed to gain confidence in the correctness of the memory subsystem. The Petri net simulator used to develop and debug the protocol and hardware controllers is a powerful, general tool for the study and performance evaluation of concurrent systems. However, the level of detail of the Petri net model required to be useful for studying the correctness of the system precludes its use in performance evaluation of the system for trace files of realistic lengths. An object-oriented discrete event simulator was developed to study the higher level performance of the memory subsystem. Both strategies of this two-pronged approach, detailed Petri net models and higher level discrete event simulation, are trace-driven approaches. The goal of the first strategy is to gain confidence in the correctness of the protocol and the realizability of the hardware controllers. The goal of the second strategy is to demonstrate the feasibility of increasing the scalability of bus-based multiprocessors by an order of magnitude, from 10–20 processors to 100–200 processors.

#### 1.7.1 Guide to chapters

This chapter outlines the need for parallel processing technology to bring to bear increased computational power on a wide range of computer applications. A brief review of the elements of parallel computer architectures and the method of applying caches to bridge the processor/memory speed gap was provided as background. The first cache-based single bus multiprocessors were described. The natural extension

Figure 1.2: Steps in the evolution of bus-based shared memory multiprocessors.

of the hierarchical bus as a means of increasing the ultimate size of bus-based multiprocessors was outlined. Performance evaluation strategies were described which produce confidence in the correctness of the proposed cache coherence protocol and broad measures of performance for the hierarchical architecture.

The problem of cache coherence is considered in Chapter 2. Possible solutions to the cache coherence problem are described, with specific attention being paid to a class of hardware solutions for single bus multiprocessors.

The components of the hierarchical bus shared memory multiprocessor studied in this thesis are described in Chapter 3. The responsibilities and the design criterion of each controller are explained. The description in this chapter includes a section analyzing the hazards inherent in a controller which monitors two asynchronous buses and how each of these hazards is resolved.

The cache coherence protocol developed for the hierarchical bus multiprocessor is described in Chapter 4. A complete description of the states of the protocol, the required bus transactions, and the tables defining the protocol are found here.

Chapter 5 describes a method developed to generate multiprocessor address traces for detailed performance evaluation of multiprocessors. The chief advantages of this method are the lack of reliance on a real multiprocessor and the architectural independence of the address traces.

The detailed Petri net models used to design and debug the hardware controllers and the cache coherence protocol are discussed in Chapter 6. The models were used in a Petri net simulator developed for the purpose of studying concurrent systems. The simulator supports many extensions to Petri nets which increases the modeling power or expressiveness of the tool.

Discrete event simulation is used to estimate the performance of the hierarchical bus multiprocessor. The object-oriented simulation tools and the models used for performance evaluation are described in Chapter 7. A purely probabilistic model of the complete HBSM multiprocessor is used to explore the scalability of the hierarchical architecture. A trace-driven extension of this model is used to verify the purely probabilistic simulation model, and to study in more detail the effects of cache geometry and coherence traffic in the HBSM multiprocessor. This simulation model provides increased detail with acceptable speed by accurately capturing the state of a single cluster and representing intercluster activity probabilistically with parameters measured from address traces.

The final chapter draws conclusions about the scalability of the hierarchical bus architecture and considers directions for future research in several areas.

## Chapter 2

## Cache Coherence

A hierarchical bus multiprocessor has the potential of increasing the ultimate size of bus-based multiprocessors into the range of a few hundred processors. The critical role of caches in bus-based architectures and the obvious need for correct and deterministic operation of the multiprocessor means that a satisfactory solution to the cache coherence problem is necessary. As shall be seen, the performance of the system for maintaining cache coherence will be crucial to the performance of the overall system.

#### 2.1 Definition of Cache Coherence Problem

The cache coherence problem arises from the simultaneous existence of multiple copies of the same block of memory. Physical memory of a computer can be thought of as a collection of memory blocks. Each block of memory is associated with a home memory module. Copies of each memory block may exist in zero or more caches in a multiprocessor. The correct and deterministic operation of the multiprocessor depends on managing the multiple copies of data blocks, or solving the cache coherence problem.

An intuitive requirement for a solution to the cache coherence problem is that any read to a memory location should return the value last written to that memory location. In a multiprocessor the meaning of last written value may very well depend on the point of view of each processor. As a result, this intuitive definition of coherence is not rigorous enough to use for evaluating solutions to the cache coherence problem, but does indicate a desired behavior for a solution.

A more rigorous requirement for correct operation is known as sequential consistency. Sequential consistency requires that a system produce the same result as long as the memory accesses of each processor are kept in order, while the memory accesses of different processors may be interleaved in arbitrary order. This is a common expectation among programmers, no doubt because uniprocessors execute in this fashion,

and the semantics of sequential and parallel programming languages encourage this model. Scheurich and Dubois define a sufficient condition for a multiprocessor to be sequentially consistent in terms of global performance of memory accesses. A store is globally performed when it is performed with respect to all processors, that is, no load issued by any processor can return an old value which was valid before the store. A load is globally performed when it is performed with respect to all processors, and the store which is the source of the value returned has been globally performed.

Sequential consistency is satisfied in *any* system if an access may not be performed with respect to any processor until the previous access by the same processor has been globally performed and if accesses of each individual processor are globally performed in program order [46].

Enforcing sequential consistency via the cache coherence system may be too costly. For example, if multiple caches in the hierarchical bus architecture held copies of the same block, sequential consistency would require that a processor writing to this block be held until the effect of the write operation had been recorded in every cache holding the block. Even if the effect of the write were to simply invalidate other copies of the shared block, stalling the processor until all invalidations were performed (and until acknowledgments had been received) would severely degrade performance.

Alternatives to sequential consistency are known as weak ordering models. Systems which do not enforce sequential consistency (or strong ordering) may still execute correctly if proper synchronization is followed. Coherence in a weakly ordered system is only enforced at necessary synchronization points. The advantage of weak ordering models is that by allowing inconsistency when it does not matter, the performance of the system may be improved. To continue the example used above, a processor would only need to be delayed on a write to a shared block until it broadcast its write intention on its cluster bus, knowing that invalidations would eventually be received by all caches holding a copy of the block.

The cache coherence maintenance system (protocol and controllers) described in this thesis implements a form of weak ordering known as processor consistency. Processors are released after a write to a shared block once the transaction has been issued on the bus; a processor is free to issue further memory accesses before the write is seen by all processors in the system. Accesses by any given processor occur in sequential order with respect to that processor, but nothing is guaranteed about memory accesses relative to other processors. Not guaranteeing sequential consistency

eliminates the only published method of proving a cache coherence protocol correct [46]. The issue of correctness is addressed in later chapters. Processor consistency requires that access to shared variables be protected with synchronization constructs such as semaphores and monitors.

The expectations of a good solution to the cache coherence problem are that it not allow violations of the cache coherence protocol, that it maintain coherence with minimal impact on the performance of the system, that it be transparent to programmers, and that the cost and complexity of the solution are reasonable. A solution to the cache coherence problem does not eliminate the need for proper use of synchronization in parallel programming.

### 2.2 Example of Cache Coherence Problem

To understand the cache coherence problem, imagine a small multiprocessor with two processors each with private caches and a single system memory, joined by an arbitrary interconnection network, as shown in Figure 2.1a. The first event (step 1) in the scenario depicted is when processor  $P_1$  does a read to a block which misses in the cache. The cache miss is satisfied by the cache controller  $CC_1$  requesting that the block be supplied to it. The memory module responds to this request (step 2), and the block is loaded into the cache of  $P_1$ . Processor  $P_2$  proceeds to also read from this block (step 3), find it missing in the cache, load the block from memory (step 4), until the situation is as shown in Figure 2.1b. The next event in the system is a write by processor  $P_1$  to the block. At this point, the question of updating the other copies of the block that exist in memory and cache arises. If the write to the block is passed over the interconnection network, thus keeping the copy of the block in memory up-to-date with the latest copy in  $P_1$ 's cache, then the cache coherence protocol is classified as write-through. If memory is left inconsistent with the latest cache copy, then the protocol is said to be write-back. A write-back protocol requires that caches take responsibility for blocks for which they hold the latest value. The actions taken for the copy of the block in  $P_2$ 's cache distinguishes the cache coherence protocol as either a write-invalidate or write-update protocol. Write-invalidate protocols simply invalidate copies of the block held in other caches. Write-update protocols transfer the new data value of the block to the other caches holding copies of the block. The memory update policy and the cache update policy are orthogonal.

a) Reads by P<sub>1</sub> and P<sub>2</sub> load copies of block into their respective caches.

Block of interest shown in black.

b) Write by  $\mathbf{P}_1$  forces choice of policy for updating memory and cache copies of block.

Figure 2.1: Simple multiprocessor scenario to demonstrate cache coherence problem.

#### 2.3 Solutions to the Cache Coherence Problem

The strategies for solving the cache coherence problem can be broadly classified into hardware solutions or software solutions. The policies which can be implemented efficiently depend on the architecture of the multiprocessor, particularly of the interconnection network. For example, if all cache controllers can monitor broadcasts from all other cache controllers, then a write-update policy can be more efficiently implemented, since the writing processor need not know in advance the list of other processors holding copies of the block in their cache. Access to the same information at the same time gives the shared bus an advantage over more general forms of interconnection networks, such as multistage switching networks, since it allows for a distributed hardware solution to the cache coherence problem.

#### 2.3.1 Software solutions

Software solutions to the cache coherence problem rely on intelligent compilers to generate instructions to the cache controllers which will ensure that coherence is maintained [12]. In the most extreme case, the compiler may simply mark all variables shared between two or more processors to be uncacheable. Accesses to share variables would bypass the cache and go directly to memory every time. A more sophisticated approach is to classify shared variable memory accesses by their coherence requirements, and issue instructions to the cache controller to maintain coherence for the shared variables but still allow caching. For example, shared variables that are used read-only by multiple processors can always be cached, and no special action need be taken to maintain coherence. Shared variables which are read by many processors and written by just one processor must be made uncacheable on the reading processors and can be cached for the writing processor if the cache protocol specified a write-through memory update policy.

Software solutions to the cache coherence problem do not require complex cache controllers, but do require that a processor be able to issue commands to the cache controller to turn the cache on and off, and to selectively invalidate cache blocks. Performance of software solutions can not be as high as a properly implemented hardware solution to the coherence problem, since compilers cannot know the relative timing between accesses to the same block by multiple processors. In other words, if

a block is accessed read/write by two processors, but those accesses do not overlap in time, then hardware support for cache coherence will allow greater cache accesses to occur with only small overhead, while a software solution enforces no caching of the block.

#### 2.3.2 Hardware solutions

Placing the burden of cache coherence on hardware makes the actions necessary to maintain coherence transparent to both the programmer and the compiler writer. The solutions that have been proposed can be classified into directory schemes, snoopy controllers, and coherent networks. Directory schemes use state information held in either a centralized directory [54] or distributed among the memory modules [10]. In both cases, the directory holds state information which enables the cache controllers to take actions necessary for preserving coherence. Centralized directories may become a system bottleneck, as every memory reference must be checked against the directory. Stenström has proposed a directory scheme where the state information is distributed among the caches [50].

Full-map directories contain state information for every instance of a block in the system, allowing invalidates or updates to be sent only to those caches holding the block. The size of full-map directories has prompted methods of limiting how many caches can hold a block at the same time. These limited directories [11] either force invalidations when the requested number of blocks exceeds their capacity or resort to broadcasting invalidates and update information. The main advantage of directory schemes is they do not require a single source of information which all cache controllers can monitor; they can be used with general interconnection networks.

A second class of hardware solutions are the snooping schemes designed for single bus multiprocessors. When a single shared bus is used to interconnect all processors and memories, broadcast from one cache to all other caches is readily and inexpensively achieved. Snooping on (monitoring) the bus gives all cache controllers information about what is happening in the system simultaneously. A single invalidate bus transaction can invalidate all cached copies of the block at the same time. In addition, the bus acts to serialize accesses to memory, since the bus is the only path for all processors to memory, whereas in a generalized interconnection network there

may be multiple paths to memory which can be used concurrently. The characteristics which make the bus desirable from a standpoint of cache coherence act as a fundamental limitation to the ultimate size of bus-based multiprocessors. Because the bus is a unique resource shared by all processors to communicate with each other and memory, it will inevitably become the system bottleneck as the size (number of processors) of the multiprocessor is increased.

Limitations in the scalability of bus-based multiprocessors have led to proposals for cache coherent networks. These machines are multiprocessors built around interconnection networks designed to maintain cache coherence while at the same time not limiting the scalability of the overall system. Hierarchical bus architectures have been proposed by several researchers. Wilson [56] describes a two-level hierarchical bus machine which uses large second level caches to hold copies of the blocks held in caches in the cluster below them. These second level caches hold both status and data. The system memories are concentrated on the highest level (global) bus. The cache coherence protocol used is an extension of a simple invalidation protocol with write-back.

The Data Diffusion Machine [29] being built at the Swedish Institute of Computer Science uses large low-level caches attached to each processor and a hierarchy of buses connected by status-only caches at each hierarchical level. A novel feature of the DDM is the absence of traditional memory. The large caches at the processors act as a distributed memory for the entire system.

The Wisconsin Multicube [28] is based on a two dimensional grid of buses with memory modules for each column, and large caches at the intersection of rows and columns. Each cache controller snoops on both its column and row bus. A simple write-invalidate/write-back protocol is used together with the information of all modified blocks in all column caches held in each cache controller. A novel feature of the Multicube cache coherence scheme is that read requests can be handled by the closest cache containing a copy of the block, even if the block has not been modified. Normally system memory handles requests for blocks which have not been modified.

#### 2.3.3 Single bus snoopy protocols

The protocol and cache coherence system developed in this thesis have their roots in single bus multiprocessor solutions to the cache coherence problem. Table 2.1

summarizes the characteristics of several of the important evolutionary steps made in snoopy cache coherence protocols.

| Protocol   | Memory policy | Cache policy     | Comment                                                                   |

|------------|---------------|------------------|---------------------------------------------------------------------------|

| Write Once | dynamic       | write-invalidate | first write to memory, subsequent writes to cache                         |

| Synapse    | write-back    | write-invalidate | first implemented snoop pro-<br>tocol, introduced concept of<br>ownership |

| Dragon     | write-back    | write-update     | used bus line to support cache-to-cache sharing                           |

Table 2.1: Important stages in the evolution of snoopy cache coherence protocols.

Goodman's Write Once protocol [27] was the first write-invalidate protocol and also used a dynamic memory update policy. In Write Once, the first write to a cache block was passed on through to memory (write-through memory update policy) while subsequent writes to the same block were kept in the cache (write-back). The Synapse protocol [25] was used in the Synapse N+1 fault tolerant multiprocessor and represents the first implementation of a snooping protocol. The ownership concept, in which every block has a distinct and unique owner at all times, either memory or a cache controller, was introduced by Synapse. The ownership concept was taken the next logical step by the Dragon protocol [39], in which write-updates are performed to keep caches up-to-date with each other when a block is being written to by multiple caches. A cache is an owner of a modified block, and hence is responsible for supplying that block to read requests, until it either replaces the block and writes it back to memory, or until another cache writes to the block and assumes ownership. Dragon uses a bus line, called the Shared Line, for cache controllers to indicate whether a block is being shared among multiple caches. The shared line obviates the need to broadcast every write-update on the bus when it is known that no other caches have copies of the block. This effectively splits the modified state into two states, a modified-shared state, and a modified-private state.

Archibald and Baer [2] studied the performance of published snoopy protocols (including those in Table 2.1) for single bus multiprocessors with probabilistic workload models. Their results indicate that cache coherence protocols which allow dirty

sharing of blocks (true of Dragon) have significantly better performance, particularly when the degree of sharing is high, than do simpler invalidation protocols.

## Chapter 3

# Architecture of the HBSM Multiprocessor

Several strategies for solving the cache coherence problem were discussed in the previous chapter. The solution proposed for the hierarchical bus shared memory multiprocessor studied in this thesis is comprised of hardware controllers and a cache coherence protocol. This chapter describes the HBSM architecture and specifies the responsibilities of the hardware components of the memory system. The possible states of a memory block in each controller are described in anticipation of the definition of the cache coherence protocol in Chapter 4.

### 3.1 Introduction

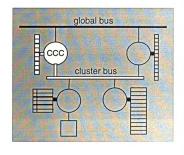

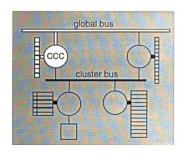

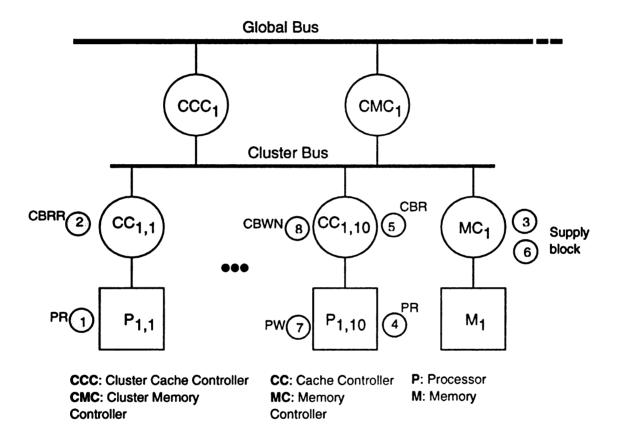

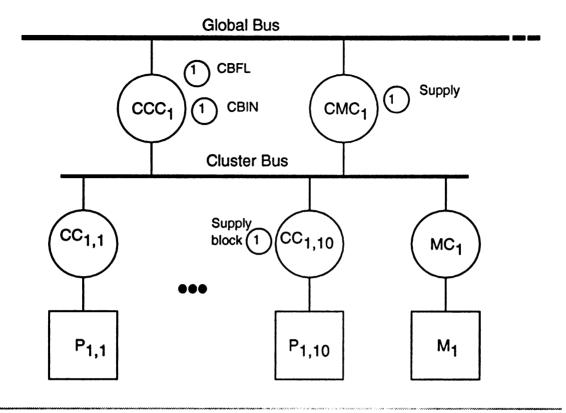

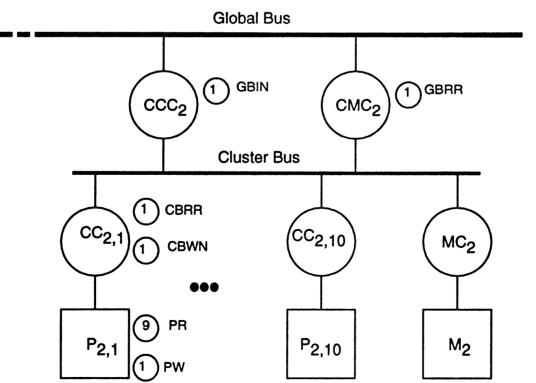

The Hierarchical Bus Shared Memory (HBSM) multiprocessor consists of a two-level hierarchical bus interconnect with physically distributed memory and private processor caches. A cluster consists of multiple processors sharing a single cluster bus. Multiple clusters are joined by a single global bus. The interface between the global bus and the cluster buses consists of two devices: a memory controller and a status-only cache controller. Providing the illusion of a single, flat virtual address space in the presence of physically distributed memory is an important characteristic of the HBSM multiprocessor both for performance and ease of programming.

The main components of the HBSM multiprocessor are shown in Figure 3.1. Caches in the system are shown as boxes attached to controllers. Each row of the boxes corresponds to a memory block. Data in caches are gray, status information is white. Groups of blocks separated by thicker lines indicate set associative caches. Each cluster consists of Processors P with private caches CC and a dumb Memory Controller MC on a cluster bus joined to the global bus by the dual-bus snoop controllers, the Cluster Memory Controller CMC and the Cluster Cache Controller CCC. In order to support the illusion of a single shared address space, the CMC maintains

a directory of status information for every block in the cluster memory module. The CCC keeps a set-associative status-only cache containing an entry for every block held in a CC cache on the CCC's cluster. The CCC acts to maintain coherence between caches on different clusters.

The architecture of the HBSM multiprocessor is similar to other hierarchical bus multiprocessors. The HBSM architecture differs from the Ultramax by physically distributing the memory modules throughout the system, rather than concentrating them on the global bus [8]. Additionally, the role of the second level cache is different. The Ultramax second level caches are traditional caches that hold the both the data and status of memory blocks found in the processor caches below them. The HBSM multiprocessor CCC caches only the *status* of the memory blocks found in the lower level caches, and not their data values.

The paper design of new multiprocessors is a time honored tradition for doctoral degrees in the field of parallel processing. Novel methods of connecting processors with memories are not difficult to propose; whether the new architecture has any merit is more difficult to ascertain. As with any complex system, the performance of a large multiprocessor depends on the interaction of its many subsystems. To study all of these subsystems is both necessary for complete understanding of the whole, as well as impossible for anything but a large team of researchers. This chapter, along with Chapters 4 and 6 attempts to compromise between a purely academic exercise and a useful investigation of a practical multiprocessor architecture. Some aspects of the HBSM multiprocessor are not modeled, or are represented only implicitly. For example, the role of the operating system in a real multiprocessor cannot be understated, but is completely ignored here. The model used for processors is very simple.

The main components of the memory subsystem are described in this chapter; Chapter 6 is devoted to a detailed Petri net model of these controllers. The Petri net model captures the state of each controller and each memory block in the system. Trace driven simulation and the level of detail found in the models uncovered problems that would be faced in actually building a multiprocessor similar to the one studied here. The goal of the design portion of this effort was to confirm the practicality of the protocol and the memory subsystem controllers. For example, a protocol transaction which required instantaneous information available only on other clusters is not practical. Modeling the HBSM multiprocessor in detail has verified that each

Figure 3.1: Components of the Hierarchical Bus Shared Memory (HBSM) multiprocessor architecture.

controller can act to maintain system coherence with information which would be readily available to it in a real system.

An additional achievement of detailed study of the cache coherence protocol and memory subsystem controllers is the knowledge of the phenomenon of state-space explosion which occurs in a complex, asynchronous system. Cache coherence protocols are often judged practical or impractical based on the number of states they utilize. What is not often discussed in research papers is the large increase in states and possible situations when the interactions of real controllers and asynchronous buses are considered. For example, when two processors on different clusters write to a common block at nearly the same time, the corresponding write notice transactions will collide at one of the dual-bus snoop controllers (CCC and CMC) What is represented by a single box in a protocol table has now become a complex event of aborting one of the transactions, resetting the states of various controllers and restarting the aborted cache write. If each of the many possible interactions on one cluster and between clusters is considered a state of the system, then the formal states of the cache coherence protocol mushroom into system states which must be properly handled.

A fundamental assumption underlying the design of the system controllers was the clustered nature of the architecture, and the expectation that computations performed on such a multiprocessor would exhibit clustered memory access patterns. The protocol and controllers were designed to be completely general, *i.e.* they will support any sort of memory access patterns. High performance is predicated on a bias of each processor to access memory locations found in their respective cluster memory module. The design objectives of the system were three-fold. First, the delay associated with intracluster memory accesses should be minimized since the system is aimed at applications with clusterable memory access patterns. Second, protocol traffic on the global bus should be minimized, since the global bus represents a possible system bottleneck. And third, the communication costs for intercluster accesses should be within an acceptable range to allow sharing of data amongst clusters.

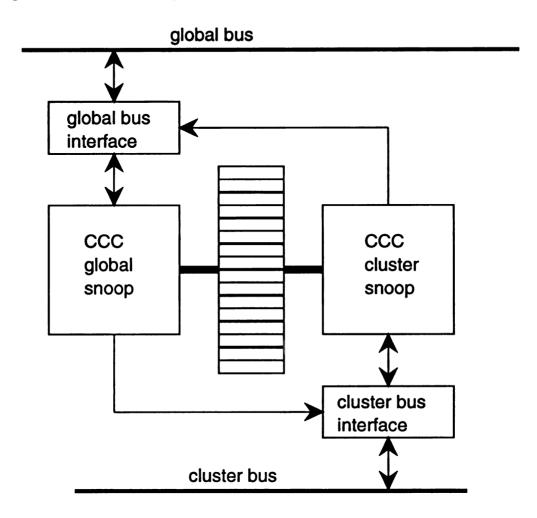

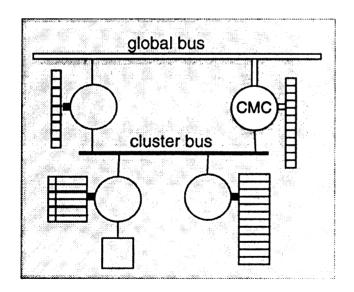

## 3.2 System Controllers

The two dual-bus snoop devices, the Cluster Memory Controller CMC and the Cluster Cache Controller CCC each have two snooping parts; the cluster snoop (Csnoop) monitors a cluster bus, and the global snoop (Gsnoop) monitors the global bus.

Dual-ported memory could be used to implement a single directory to which both the Csnoop and the Gsnoop of these devices refer. Most of the complexity of the design of the HBSM memory controllers is found in the dual-bus snoop devices.

Figure 3.2: Detail of the CCC dual-bus snoop device showing the two active portions of the controller, cluster snoop and global snoop, sharing access to the single cache directory.

Explanation of a few key terms and concepts used will aid in understanding the HBSM multiprocessor and the cache coherence protocol. A block of memory corresponds to a contiguous group of memory locations, generally between 2 and 32 words. All blocks in the shared memory address space reside either in one of the cluster memory modules or in the global memory module. A block is remote with respect to a given cluster if it resides in the memory module of another cluster, or in global memory. A block is local with respect to a given cluster if it resides in the