## This is to certify that the

## dissertation entitled

## ALGORITHM IMPLEMENTATION AND DESIGN OF RECONFIGURABLE MIXED SYSTOLIC ARRAYS

presented by

Anwar Khurshid

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Electrical Engineering

Major professor

P. David Fisher

Date June 4, 1985

MSU is an Affirmative Action/Equal Opportunity Institution

0-12771

RETURNING MATERIALS:

Place in book drop to remove this checkout from your record. FINES will be charged if book is returned after the date stamped below.

MAR 0,5 2002

# ALGORITHM IMPLEMENTATION AND DESIGN OF RECONFIGURABLE MIXED SYSTOLIC ARRAYS

Ву

Anwar Khurshid

## A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Electrical Engineering and Systems Science

#### ABSTRACT

## ALGORITHM IMPLEMENTATION AND DESIGN OF RECONFIGURABLE MIXED SYSTOLIC ARRAYS

By

#### Anwar Khurshid

One drawback of systolic architectures is their fixed-flow structure for data streams, which limits the type of algorithms or applications that can effectively be supported by such architectures. This thesis presents a methodology for algorithm implementation and design of a class of reconfigurable multiprocessor architectures called the mixed systolic array (MSA). In the MSA architecture, switching cells are mixed with computation cells to achieve flexibility in the data-flow patterns. This architecture broadens the scope of systolic arrays by achieving reconfigurability, algorithmic flexibility and fault tolerance. The level sensitive scan design (LSSD) technique is employed to load and implement the distributed control structure required to establish a desired interconnection pattern on the MSA. The control structure for a particular configuration is loaded into the array as a binary vector in a bit serial fashion. This approach enhances testability and incorporates fault tolerance in the MSA structures.

Efficient implementation of algorithms on VLSI structures requires exploitation of parallelism in the algorithm and mapping of the algorithm communication structure into the processor interconnection structure. thesis presents a general mathematical model for formally representing reconfigurable MSA architectures and a step-by-step procedure for implementing a given algorithm into the MSA structure by generating the control code required to reconfigure the array. The mapping procedure is based on time and space transformations of the data dependence vectors of the algorithm. These transformations provide a description of the data-flow and timing, and dictate the interconnection structure required to implement the algorithm on the array. The procedure presented in this work, will provide a useful tool in the design automation of reconfigurable MSAs. To illustrate the methodology and explain the reconfiguration procedure, two sample algorithms, the finite impulse response (FIR) filtering algorithm and the priority queue algorithm, are mapped into a linear reconfigurable systolic array. A computer-aided design (CAD) facility is also presented, for modeling and simulating mixed systolic arrays. This CAD facility serves as a high-level design tool which supports the design of MSA architectures, and provides the designer of MSAs with a facility to interactively develop an MSA structure for a given set of user-specified attributes and simulate the execution of algorithms on MSA processors at the register-transfer level.

To

MOTHER AND FATHER

## **ACKNOWLEDGEMENTS**

I would like to express my deepest gratitude to my advisor, Dr. P.D. Fisher, for his continuous moral and professional support and guidance throughout my doctoral program. He was a rich source of inspiration, and Ι gratefully acknowledge the encouragement and motivation provided by him which made possible the successful conclusion of my Ph.D. work. I also would like to thank Dr. Michael Shanblatt for his valuable suggestions and evaluation of this research. I am very thankful to Dr. Lionel Ni for his professional advice and review of this work. The interest and encouragement provided by Dr. S.R. Crouch is gratefully acknowledged. Appreciation is extended to Dr. M.A.P. Jayasumana for his help during this research. I am thankful to Mr. B. MacArthur for his skillful drawings. The support provided by the National Science Foundation (Grant No. MCS 79-09216) for this research is gratefully acknowledged. I shall always be grateful to my parents for their unending support and encouragement through the years. Finally, I am specially thankful to my wife, Nadira, for her patience and understanding in awaiting the completion of this dissertation.

## TABLE OF CONTENTS

| Ch | hapter Pa |                                                                                                                                                               | Page                 |

|----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1. | INTR      | ODUCTION                                                                                                                                                      | 1                    |

| 2. | BACK      | GROUND                                                                                                                                                        | 7                    |

|    | 2.1       | Systolic Arrays                                                                                                                                               | 7                    |

|    |           | 2.1.1 Systolic Array Architectures and Algorithms 2.1.2 Systolic and Semisystolic Design                                                                      | 7<br>16              |

|    | 2.2       | Reconfigurable Mixed Systolic Arrays                                                                                                                          | 18                   |

|    | 2.3       | Algorithm Transformation and Mapping into VLSI Structures                                                                                                     | 23                   |

|    | 2.4       | Fault Tolerance in Systolic Arrays                                                                                                                            | 26                   |

|    | 2.5       | Level Sensitive Scan Design (LSSD) Techniques                                                                                                                 | 28                   |

| 3. | A LI      | NEAR RECONFIGURABLE SYSTOLIC ARRAY (LRSA) ARCHITECTURE                                                                                                        | 33                   |

|    | 3.1       | Structure of the Linear Reconfigurable Systolic Array                                                                                                         | 34                   |

|    |           | 3.1.1 The Computation Cells Array 3.1.2 Function-Select Array 3.1.3 Data Flow Control Array                                                                   | 34<br>38<br>38       |

|    | 3.2       | Systolic Algorithms Implemented on the LRSA                                                                                                                   | 42                   |

|    |           | 3.2.1 Systolic Filtering Array 3.2.2 Systolic FIR Filtering Array 3.2.3 Pattern Matching Systolic Array 3.2.4 Discrete Fourier Transform (DFT) Systolic Array | 42<br>46<br>48<br>50 |

|    | 3.3       | Summary and Discussion                                                                                                                                        | 52                   |

| 4. | DESI      | GN OF A MULTIPURPOSE RECONFIGURABLE ARRAY PROCESSOR (MRAP)                                                                                                    | 55                   |

|    | 4.1       | Structure of the Multipurpose Reconfigurable Array Processor                                                                                                  | 56                   |

|    |           | 4.1.1 The Computation Cell 4.1.2 The Switching Cell 4.1.3 Data-Flow and Timing 4.1.4 Programming Data-Flow Control                                            | 59<br>61<br>61<br>66 |

| Chapter |                                                                   | Page |

|---------|-------------------------------------------------------------------|------|

| 4.2     | Implementation of Algorithms on the MRAP                          | 69   |

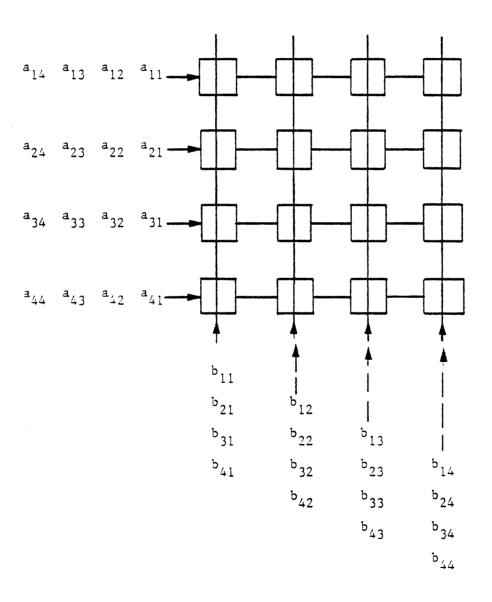

|         | 4.2.1 Dense-Matrix/Dense-Matrix Multiplication                    | 71   |

|         | 4.2.2 Band-Matrix/Dense-Matrix Multiplication                     | 73   |

|         | 4.2.3 Band-Matrix/Band-Matrix Multiplication                      | 75   |

|         | 4.2.4 Recursive Filtering                                         | 77   |

| 4.3     | Performance Analysis and Comparison                               | 79   |

|         | 4.3.1 Dense-Matrix/Dense-Matrix Multiplication                    | 82   |

|         | 4.3.2 Band-Matrix/Dense-Matrix Multiplication                     | 83   |

|         | 4.3.3 Band-Matrix/Band-Matrix Multiplication                      | 86   |

| 4.4     | Fault Tolerance                                                   | 87   |

| 4.5     | Summary and Discussion                                            | 89   |

| 5. ALGO | RITHM IMPLEMENTATION ON MIXED SYSTOLIC ARRAYS                     | 93   |

| 5.1     | A Model for Reconfigurable Mixed Systolic Arrays                  | 94   |

| 5.2     | A Model for Algorithms                                            | 98   |

| 5.3     | Mapping Algorithms into Mixed Systolic Arrays                     | 104  |

|         | 5.3.1 Procedure for Mapping Algorithms into Mixed Systolic Arrays | 108  |

| 5.4     | Examples                                                          | 112  |

|         | 5.4.1 Finite Impulse Response (FIR) Filtering Algorithm           | 113  |

|         | 5.4.2 Priority Queue                                              | 119  |

| 5.5     | Summary and Discussion                                            | 1 22 |

| 6. SUMM | MARY AND CONCLUSIONS                                              | 126  |

| APPENDI | X A - A COMPUTER-AIDED DESIGN FACILITY FOR MIXED SYSTOLIC ARRAYS  | 132  |

| A.1     | Description of the System                                         | 134  |

| A.2     | Discussion                                                        | 145  |

| BIBLIOG | RAPHY                                                             | 147  |

## LIST OF FIGURES

| Figure |                                                                                                                                                                                  | Pag |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1    | Linearly connected systolic array for computing the product of band-matrix A and vector X.                                                                                       | 10  |

| 2.2    | Two geometries for the inner-product step processor.                                                                                                                             | 11  |

| 2.3    | Hex-connected systolic array for computing the product matrix C, of matrices A and B [44].                                                                                       | 12  |

| 2.4    | Some common interconnection schemes for systolic arrays: (a) two-dimensional systolic arrays, (b) degenerate two-dimensional systolic array, (c) one-dimensional systolic array. | 15  |

| 2.5    | A semisystolic system can implement broadcasting by Mealy machines [41].                                                                                                         | 17  |

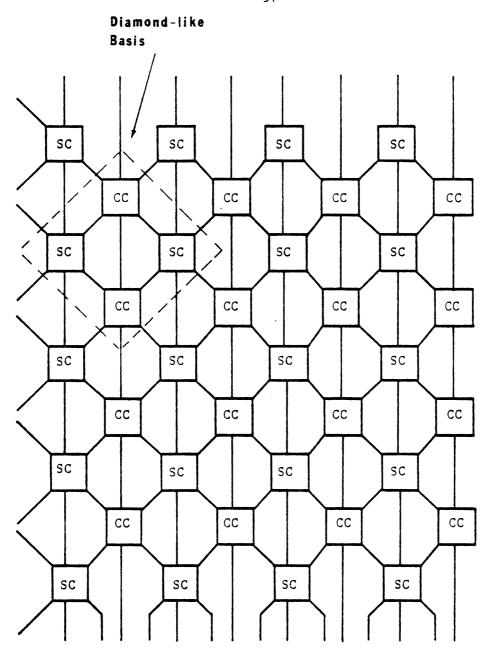

| 2.6    | A mixed systolic array constructed from a diamond-like basis.                                                                                                                    | 21  |

| 2.7    | Block diagram representation of a shift register latch.                                                                                                                          | 29  |

| 2.8    | Interconnections of SRLs on an integrated circuit [57].                                                                                                                          | 30  |

| 2.9    | General structure of an LSSD subsystem with two system clocks.                                                                                                                   | 32  |

| 3.1    | General system diagram of the Linear Reconfigurable Systolic Array.                                                                                                              | 3 5 |

| 3.2    | Block diagram representation of a Computation Cell.                                                                                                                              | 36  |

| 3.3    | SRLs are used in the function-select array.                                                                                                                                      | 39  |

| 3.4    | Four interconnection states of an interchange box.                                                                                                                               | 40  |

| 3.5    | Logic diagram of a two-function interchange box.                                                                                                                                 | 41  |

| 3.6    | Structure of the Linear Reconfigurable Systolic Array.                                                                                                                           | 43  |

| 3.7    | One-dimensional systolic array for filtering: (a) basic cells used in the array, (b) the systolic filtering array.                                                               | 45  |

| Figure |                                                                                                                                                  |     |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

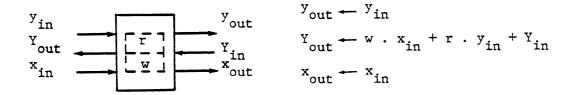

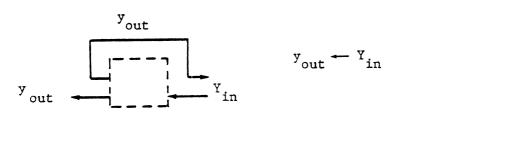

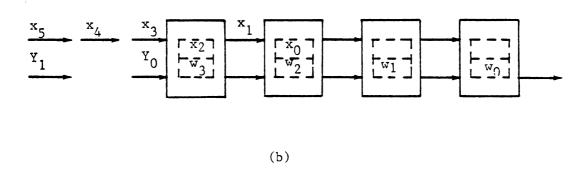

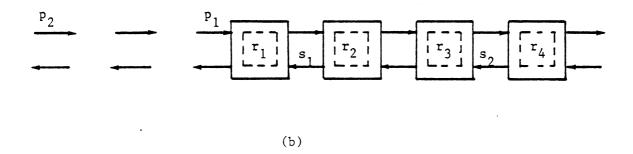

| 3.8    | One-dimensional systolic array for FIR filtering: (a) basic cells used in the array, (b) the systolic FIR filtering array.                       | 47  |

| 3.9    | One-dimensional systolic array for pattern matching: (a) basic cells used in the array, (b) systolic pattern matching array.                     | 49  |

| 3.10   | Linear systolic array for DFT algorithm: (a) basic cells used in the array, (b) the systolic DFT array.                                          | 51  |

| 3.11   | LSSD scan path within a computation cell incorporating testing and register initialization.                                                      | 53  |

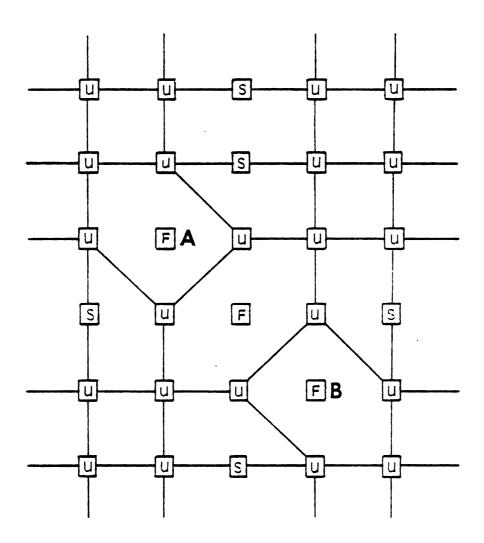

| 4.1    | The structure of the Multipurpose Reconfigurable Array Processor (MRAP).                                                                         | 57  |

| 4.2    | Scan path for loading the control vectors.                                                                                                       | 58  |

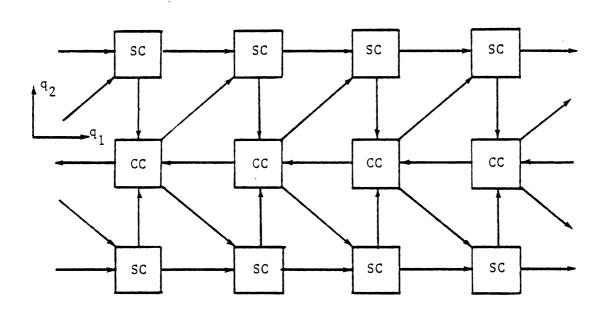

| 4.3    | General system diagram of the MRAP.                                                                                                              | 60  |

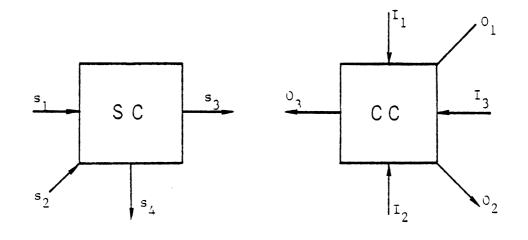

| 4.4    | The computation cell.                                                                                                                            | 62  |

| 4.5    | A gate-level logic implementation of the switching cell.                                                                                         | 63  |

| 4.6    | A timing diagram for inter-processor communication.                                                                                              | 65  |

| 4.7    | A computation cell CC <sub>i,j</sub> and its neighbors.                                                                                          | 67  |

| 4.8    | (a) Dense-matrix/dense-matrix multiplication.                                                                                                    | 72  |

| 4.8    | (b) Band-metrix/dense-matrix multiplication.                                                                                                     | 74  |

| 4.8    | (c) Band-matrix/band-matrix multiplication.                                                                                                      | 76  |

| 4.8    | (d) One-dimensional arrays for filtering.                                                                                                        | 78  |

| 4.9    | (a) The MRAP with one faulty computation cell, (b) spare cells are used for fault masking.                                                       | 88  |

| 4.10   | Fault tolerance in the MRAP for 2-dimensional algorithms.                                                                                        | 90  |

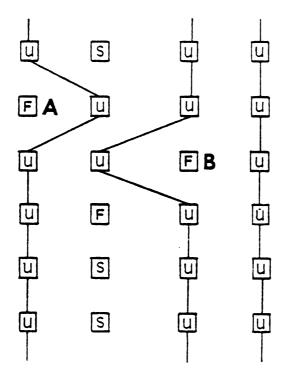

| 5.1    | The Linear Reconfigurable Systolic Array (LRSA) architecture: (a) structure of the LRSA, (b) a switching cell (SC), (c) a computation cell (CC). | 97  |

| 5.2    | Structure of the Multipurpose Reconfigurable Array Processor                                                                                     | 99  |

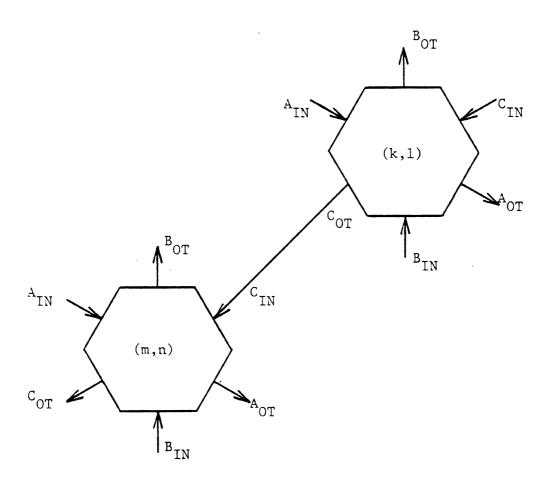

| 5.3    | A computation cell with communication links.                                                                                                     | 107 |

| 5.4    | LSSD scan path sequence in an LRSA.                                                                                                              | 114 |

| 5 5    | A linear systolic array for ETR filtering                                                                                                        | 118 |

| Figure |                                                                                               | Page |

|--------|-----------------------------------------------------------------------------------------------|------|

| 5.6    | A systolic priority queue.                                                                    | 1 23 |

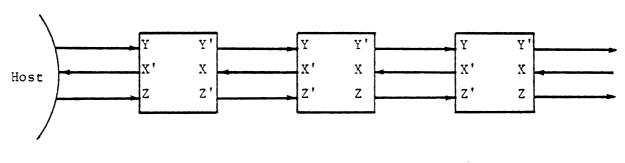

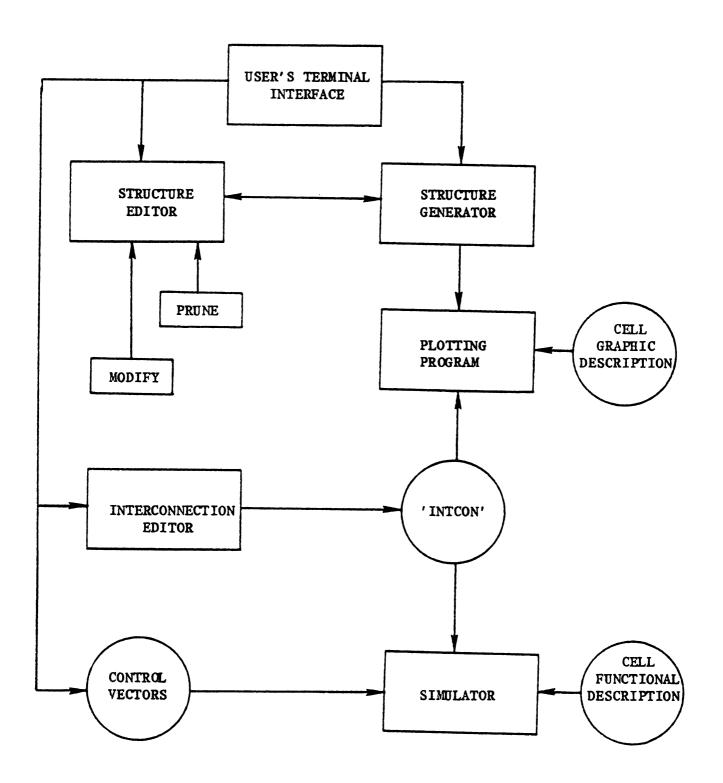

| A.1    | The system diagram.                                                                           | 136  |

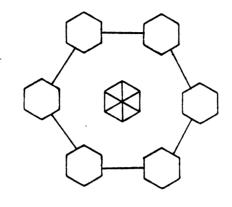

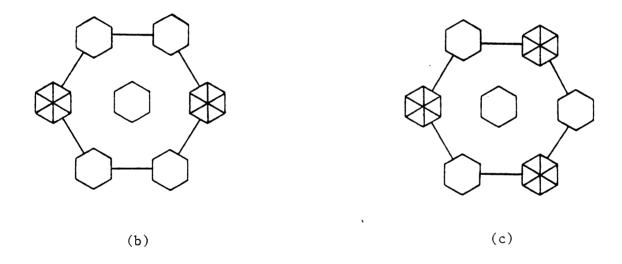

| A.2    | Hexagonal array bases with (a) $\rho_b = 1/7$ , (b) $\rho_b = 3/7$ , and (c) $\rho_b = 3/7$ . | 141  |

| A.3    | An arc indicating a connection between two neighboring cells.                                 | 144  |

#### CHAPTER 1

#### INTRODUCTION

VLSI Rapid advancements in technology demand innovative computational algorithms and hardware structures which fully exploit the technology to achieve high throughput rates and efficient resource Efficient implementation of algorithms on VLSI structures utilization. requires exploitation of parallelism in the algorithm and mapping of the communication structure into pipeline, vector or array algorithm processor interconnection structures. The main issues in VLSI design are those of modularity, simplicity of communication and control, and extensibility. A modular design with a large number of identical modules organized in a simple regular fashion is an ideal structure for VLSI.

In recent years, systolic arrays have been at the focus of attention of many researchers as pipelined multiprocessor structures suitable for solving a variety of computation-intensive and real-time problems requiring high throughput [2,4,31,32,41]. In the systolic concept, VLSI devices consist of arrays of interconnected primitive processors with distributed control and a high degree of modularity. Each processor operates on a string of data that flows regularly and rhythmically through the array. Systolic arrays feature the important properties of modularity, regularity, locality of interconnection and highly pipelined

multiprocessing. However, one drawback of systolic architectures is their fixed-flow structure for data streams, which limits the type of algorithms or applications that can effectively be supported by such architectures. Therefore, it is desirable to have reconfigurability in the data-flow structure and flexibility in the algorithm implementation to make more general purpose arrays.

The mixed systolic array (MSA) is a class of reconfigurable multiprocessor architectures, introduced by Chang and Fisher [6-8]. In this architecture, control elements are mixed with computing elements according to a certain mixing profile and the data-flow patterns are determined by the distributed control structure stored in the control elements. Classes of algorithms with similar data requirements may be executed on the same array by merely presetting the control elements at load time. MSA architectures broaden the scope of systolic arrays and at the same time preserve VLSI design attributes such as locality of communication, modularity, extensibility and simplicity of control. While Chang and Fisher developed, characterized, and evaluated the basic computing model for MSAs [6], they did not present procedures for loading and implementing the distributed control structure required to establish desired interconnection pattern on the MSA. Also, no formal methodology was presented for implementing a given algorithm into the MSA structure by systematically generating the control code required for its reconfiguration.

The goal of this research is to investigate structured methodologies for mapping parallel algorithms into reconfigurable MSA architectures,

and implementing the distributed control structure required for the algorithm implementation. Another goal is to exploit the emerging VLSI and Wafer-Scale Integration (WSI) technologies by designing computer architectures, which employ modularity in structure, simplicity and regularity in communication and control paths, and extensibility in design. From a more general standpoint, this research broadens the scope and enhances the applicability of special-purpose VLSI array processors, and at the same time contributes to the understanding of the problems and nature of a parallel processing approach to computation. The specific tasks are outlined as follows:

- Investigate the procedures for loading and implementing the distributed control structure required to establish a desired interconnection pattern on the MSA structure.

- 2. Relate the MSA's architectural model with the parallel algorithms implemented on the array and investigate the procedures for implementing algorithms into MSA structures by systematically generating the required control code for reconfiguration.

This research investigates structured methodologies for designing and implementing mixed systolic arrays. The Level Sensitive Scan Design (LSSD) technique [12,25,57] is employed to load and implement the distributed control structure required to establish a desired interconnection pattern on the MSA. The control structure for a particular configuration is loaded into the array as a binary vector in a bit-serial fashion. This approach enhances testability and incorporates

fault tolerance in the MSA structure. This thesis presents a general mathematical model for formally representing reconfigurable architectures and a step-by-step procedure for implementing a given algorithm into the MSA structure by generating the control code required to reconfigure the array. The mapping procedure is based on time and space transformations of data dependence vectors of the algorithm. These transformations provide a description of the data-flow and timing, and dictate the interconnection structure required to implement an algorithm on the array. A computer-aided design facility for modeling and simulating MSAs is designed and partially implemented. This facility helps the designer of MSAs to interactively develop an MSA structure for a given set of user-specified attributes, such as mixing density and array geometry, and to simulate the execution of algorithms on MSA processors at the register-transfer level.

The procedures presented in this thesis, for mapping algorithms onto MSAs and for implementing the control structure necessary for reconfiguration, provide a useful tool in the automated design of reconfigurable MSAs. For instance, in order to design an MSA to implement a set of algorithms, one can start with a high-level language description of algorithms and use the approach presented in this thesis to find a suitable MSA which can implement these algorithms. Usually, many valid time and space transformations are generated in the procedure, providing the designer flexibility to choose the ones which map easily on the array. The procedures are especially useful during the application of an MSA processor. Whenever a new configuration of the MSA is desired

for a new algorithm, the host computer can use the procedure to generate the reconfiguration control vector for the algorithm to be implemented. This control vector can be loaded into the MSA processor to reconfigure the array on—the—fly. The procedure can also be used to determine whether or not an algorithm can be implemented on a given mixed systolic array.

Throughout, we use symbols I and Z to denote the set of all natural numbers and the set of all integers, respectively. An denotes the nth cartesian power of a given set A, i.e., the set of all possible n-tuples of elements of A. Chapter 2 reviews some background information and related research work regarding systolic architectures, parallel algorithms. and LSSD techniques. In Chapter 3, design of a one-dimensional MSA architecture, called the Linear Reconfigurable Systolic Array (LRSA), is presented which employs LSSD techniques to achieve reconfigurability and multifunctionality. This approach is extended to two-dimensional arrays in Chapter 4, which describes a Multipurpose Reconfigurable Array Processor (MRAP) architecture for implementing various systolic and semisystolic algorithms. performance of the MRAP is analyzed in Chapter 4, for various matrix-multiplication algorithms based on their Space-Time-Bandwidth complexity. Chapter 5 presents a mathematical formalism for modeling reconfigurable MSA architectures and a methodology for reconfiguring the array by mapping the communication structure of an algorithm into the interconnection structure of the array. Two sample algorithms, the finite impulse response (FIR) filtering algorithm and the priority queue algorithm, are mapped into a linear reconfigurable systolic array in order to illustrate the reconfiguration procedure. Chapter 6 contains a summary of this research work and some thoughts for future research possibilities. Finally, a computer-aided design facility for modeling and simulating MSAs is described in Appendix A.

## CHAPTER 2

#### BACKGROUND

#### 2.1 SYSTOLIC ARRAYS

Several types of VLSI architectures have been proposed in recent years, such as the systolic arrays [31-35], the Wavefront Array Processor [39], mixed systolic arrays [6-8] and the Configurable Highly Parallel (CHiP) computer [53,54]. Most of these parallel architectures attempt to match the underlying hardware to specific algorithms for fast and efficient execution. Systolic array architectures are particularly attractive for VLSI implementation because of their regular, short and simple communication geometry [44,45]. This section discusses the characteristics of systolic array architectures, systolic algorithms, and semisystolic design.

## 2.1.1 SYSTOLIC ARRAY ARCHITECTURES AND ALGORITHMS

Systolic array architectures are multiprocessing systems in which data is pipelined among processors by using next-neighbor communication. Systolic algorithms are defined as mathematical algorithms which are implementable with systolic architectures. A number of special purpose systolic arrays, suitable for VLSI and wafer-scale integration (WSI), have been proposed for solving various computation-intensive problems

[4,18,35,38]. Their applications range from numerical problems, such as signal and image processing and matrix arithmetic, to non-numerical tasks, such as searching and sorting, graph algorithms and relational databases.

A sytolic array comprises a network of interconnected cells, where each cell is capable of performing a small set of operations and has some local memory and control logic. Strictly next-neighbor type of connections constitute the interprocessor communication structure and data moves through the architecture in a synchronous pipelined manner. Communication with the outside world takes place only at the array boundary, possibly through some special I/O processors. The following design criteria for systolic arrays have been suggested: First, the design should use only a small number of different types of simple cells. Second, these cells should be interconnected by a network with short, regular connections. Third, multiple use of each input data item should be made in order to achieve high computation rate and throughput without requiring high memory to array bandwidth. And, finally, computational algorithms should be employed which exploit both data pipelining and parallel execution.

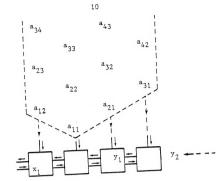

The principles of systolic array design are illustrated here by considering two examples of systolic arrays. A linearly connected systolic array, shown in Figure 2.1 [31], uses W processing elements to multiply an NxN band-matrix, with bandwidth W by a vector of N elements. The basic processing element is called the inner-product step processor (see Figure 2.2), and consists of three internal registers RA, RB and RC. This processing element performs the inner-product operation

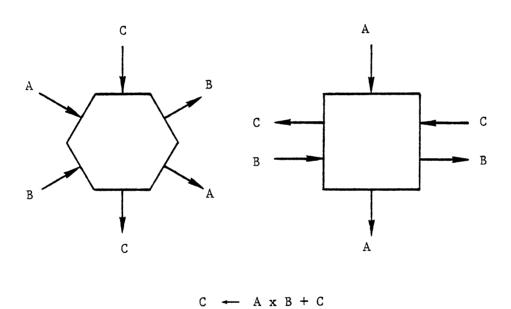

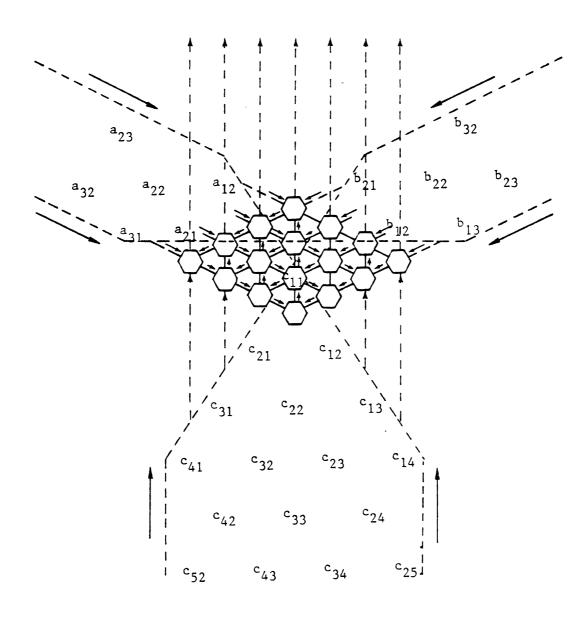

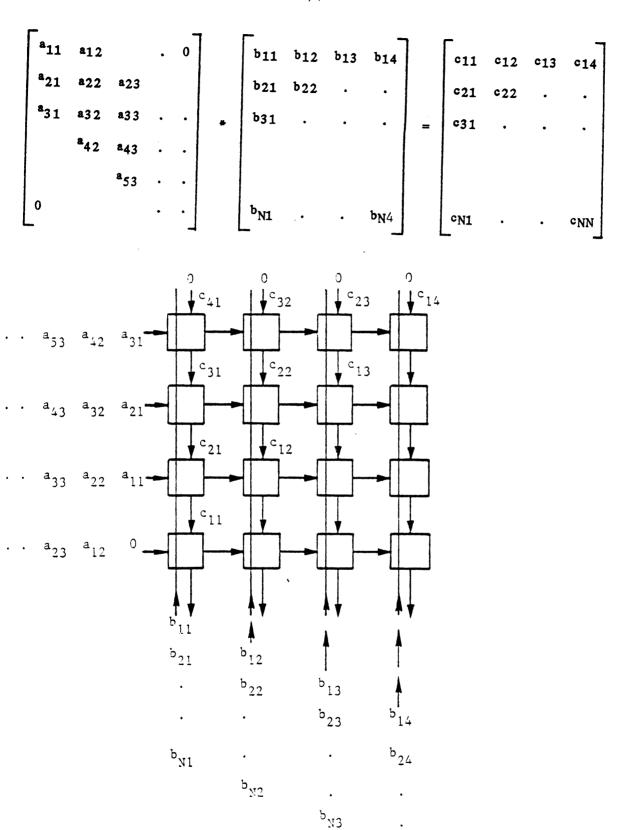

$C \leftarrow C + A * B$ ; where A, B and C are the contents of the registers RA, RB and RC, respectively. The time to compute the entire multiplication is 2N+W time units. The input and output vector elements march in opposite directions, so that each input vector element meets all the output vector elements before it leaves the array. The same inner-product step processor is used in a hexagonal systolic array to implement band-matrix multiplication. Figure 2.3 illustrates the multiplication algorithm for two NxN band-matrices with bandwidths  $W_1$  and  $W_2$ , respectively [31]. This algorithm requires  $W_1 x W_2$  inner-product step processors and takes  $3N+\min(W_1,W_2)$  units of time for the computation. Several other computation-intensive algorithms can be solved on systolic arrays such as LU decomposition, triangular linear systems, convolution, filter, and discrete Fourier transforms.

Many implementation alternatives exist for systolic array processors providing different interconnection topologies and degrees of flexibility. According to their degree of flexibility, systolic array processors can be classified as follows [34]:

- 1. Single-purpose systolic arrays [2,4,38]. In this approach, a systolic array is built to implement only one algorithm and a different array needs to be designed for each new algorithm. This approach is reasonable if the performance of the processor is of ultimate importance and the processor is to be used in large quantities despite the fact that it is single-purpose.

- 2. Multi-purpose systolic arrays [58]. A systolic array processor

$$\begin{bmatrix} a_{11} & a_{12} & & & & 0 \\ a_{21} & a_{22} & a_{23} & & \\ a_{31} & a_{32} & a_{33} & a_{34} \\ & & a_{42} & a_{43} & a_{44} \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \\ x_3 \\ x_4 \\ \vdots \end{bmatrix} \begin{bmatrix} y_1 \\ y_2 \\ x_3 \\ x_4 \\ \vdots \end{bmatrix}$$

Figure 2.1. Linearly connected systolic array for computing the product of band-matrix A and vector X.

Figure 2.2. Two geometries for the inner-product step processor.

Figure 2.3. Hex-connected systolic array for computing the product matrix C, of matrices A and B [44].

of this type can implement a predefined set of algorithms. The control overhead for providing necessary flexibility should be kept small and the VLSI attributes, such as modularity and locality of communication, should be preserved in the design.

- 3. Non-programmable building blocks [29]. Building-block processors are constructed which can execute a few predefined commonly used functions. These blocks are connected to form a variety of systolic array processors of different sizes and shapes.

- 4. Programmable building blocks [14]. The building block is a programmable processor which can be programmed to implement a large family of systolic cells. This approach is not very efficient because of the overhead for supporting the programmability. However some systolic algorithms involving complicated data dependencies, such as greatest common divisor computation [2], can be effectively implemented on this type of arrays.

- 5. Programmable systolic arrays [3,7]. In this approach, programmable processing elements are mixed with other control units in a certain manner. These arrays are more flexible than the multi-purpose systolic arrays in the sense that the processing elements are programmable and their interconnections can be configured by software control before a computation

starts.

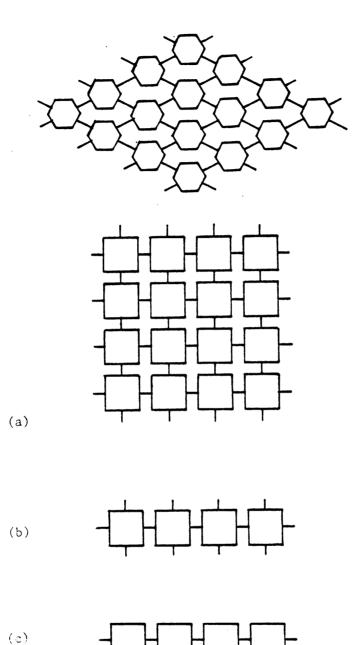

Various interconnection topologies for systolic arrays can be defined according to the number of computations performed for each input/output operation. First, for two-dimensional systolic arrays shown in Figure 2.4(a), O(n) processing elements perform computations in each cycle, whereas  $O(\sqrt{n})$  boundary cells perform input/output Thus the computation over input/output ratio is  $O(\sqrt{n})$ . operations. Systolic arrays for matrix arithmetic algorithms are included in this class [37]. Second interconnection topology can be defined as degenerate two-dimensional systolic arrays shown in Figure 2.4(b), in which O(n) processing elements perform computations and O(n) elements perform input/output operations. So the computation over input/output ratio is O(1) in this case. Systolic arrays for solution of triangular linear systems and orthogonal transformations are examples degenerated two-dimensional arrays [19,37]. Finally, linear or one-dimensional systolic arrays shown in Figure 2.4(c), perform the input/output via the two processing elements at the ends of the array, and thus the computation over input/output ratio is O(n) for an array of size n. Systolic arrays for filtering or pattern matching come under be this category [32,37]. Linear arrays may preferred two-dimensional arrays in situations where the input/output bandwidth, between the host system and the systolic array, is a major limiting factor for achieving high performance.

Figure 2.4. Some common interconnection schemes for systolic arrays:

- (a) two-dimensional systolic arrays,

- (b) degenerate two-dimensional systolic array,

- (c) one-dimensional systolic array.

## 2.1.2 SYSTOLIC AND SEMISYSTOLIC DESIGN

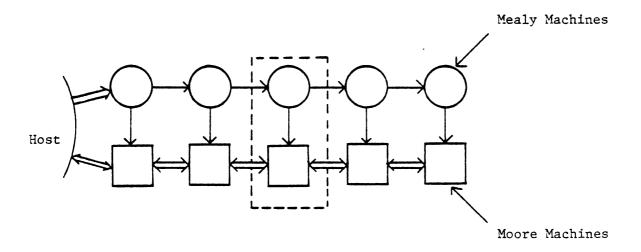

Systolic array architectures do not allow any global data communication and all communication between processing elements is clocked through a register. Semisystolic array architectures, on the other hand, allow global data communication and a data item may be broadcast to many processing elements simultaneously. Mathematically, the structure of a systolic system S(n) is given by a machine graph G = (V, E) of n interconnected Moore machines, where the vertices in Vthe machines and the directed edges in E represent represent interconnections between the machines [41]. The machines operate synchronously by means of a common clock, and time in the system is measured as the number of clock cycles. A semisystolic system is similar to a systolic system except that some of the machines may be Mealy machines with the condition that the output edges from Mealy machines may not form a cycle in the machine graph [41]. Mealy machines can implement data broadcasting, whereas Moore machines can not. Figure 2.5 shows an example of a semisystolic array which can implement data broadcasting. In this example, the combinational logic for Mealy machines is a simple wire from input to output. The exclusion of Mealy machines in systolic systems makes the clock period independent of the system size.

Semisystolic systems do not meet the design criterion of extensibility as systolic systems do. That is, many semisystolic arrays can not be cascaded together to form an arbitrarily large array, because the clock cycle time, which depends upon the delay due to broadcasting or rippling of logic, may asymptotically become arbitrarily large. In

Figure 2.5. A semisystolic system can implement broadcasting by Mealy machines [41].

general. there are two main disadvantages associated with data broadcasting. First, large broadcasts can not be implemented in a single communication cycle, because the broadcast delay can dominate the execution time of an algorithm. Second, large drivers are required for broadcasting in order to drive the combined load of all the cells connected to the broadcasting bus. Two techniques, retiming and slowdown, are described in [41] and [42] for converting a semisystolic design into a systolic one by eliminating broadcasting. For many systolic algorithms, some fraction of the processors are always idle at a given time. For example, in FIR filtering, half of the processors are idle at each clock tick and in band-matrix multiplication, two third of the processors are idle at each clock tick [44]. Leiserson proposed coalescing and interlacing techniques for improving processor utilization [41]. For specific algorithms, introduction of broadcast concept results in more efficient parallel algorithms and better processor utilization [9,10,21]. Huang and Abraham [21] have compared the efficiencies of systolic and semisystolic arrays for matrix multiplication algorithms. They concluded that, for specific computations, semisystolic arrays perform better than systolic arrays according to the Space-Time-Bandwidth complexity criterion.

## 2.2 RECONFIGURABLE MIXED SYSTOLIC ARRAYS

The mixed systolic array (MSA) is a class of reconfigurable multiprocessor architectures, first introduced by Chang and Fisher [6-8]. In this architecture, control elements are mixed with computing

elements according to a certain mixing profile and the data-flow patterns are determined by the distributed control structure stored in the control elements. The computing elements are programmable multifunctional arithmetic and logic processors, whereas the control elements are programmable interconnection networks which establish the communication structure of the array. Classes of algorithms with similar data requirements may be executed on the same array by merely presetting the control elements at load time. In this thesis, we refer the computing element and the control element as the computation cell and the switching cell, respectively.

The mixed systolic array provides programmable interconnection structure by way of mixing switching cells with computation cells in a systolic fashion. Its main objective is to broaden the scope of systolic arrays by achieving reconfigurability, algorithmic flexibility and fault tolerance. Another objective is to preserve the design attributes of modularity, uniformity, locality of communication and simplicity of control, in order to exploit the very large scale integration (VLSI) and wafer scale integration (WSI) technologies. The computation cells, in the MSA, are programmable multifunctional arithmetic and logic processors, which process the incoming data according to the control codes stored in their control registers. switching cells are programmable interconnection networks which establish the interprocessor communication structure in the array to meet the communication requirements of the algorithms implemented. A switching cell directs the data-flow among its neighboring computation cells according to the interconnection configuration defined by its

control code register. An MSA executes a specific algorithm according to the control codes stored in individual cells. The control code registers of computation cells determine the computational structure of the MSA and their contents are determined by the basic computational requirements of the algorithm. The control code registers of switching cells establish the communication structure of the MSA, and their contents are determined by the communication requirements of the algorithm. In order to configure an MSA to implement a specific algorithm, the control code corresponding to that particular algorithm is loaded into the array, and the array performs the execution in a synchronous manner. Whenever a new application of the same MSA is needed, a new control code can be loaded into the array for its reconfiguration.

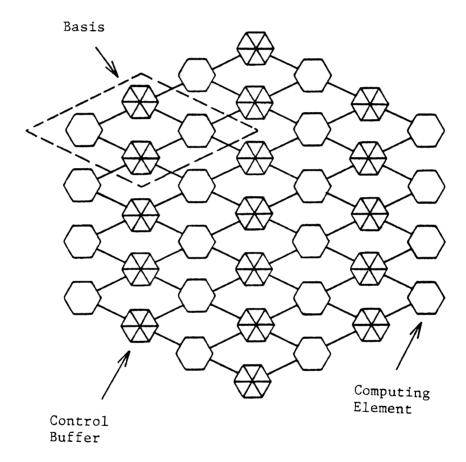

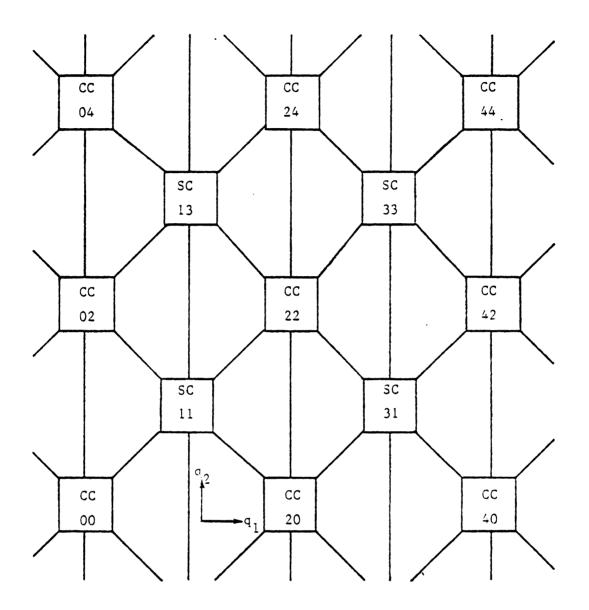

Basically, the structure of an MSA is determined by its mixing profile, which establishes the possible frames of data-flow patterns within the array. An MSA structure is called a regular structure, when there is a basis or a subarray from which the MSA can be constructed. Figure 2.6 shows an MSA constructed from a diamond-like basis. Other possible MSA structures with irregular and partially regular mixing, are discussed in [6]. In this thesis, we are concerned only with the regular MSA structures, mainly because programming and mapping algorithms into irregular arrays are too complex, and most of the existing synchronous parallel algorithms map into regular array structures [4.35].

The mixing profile of an MSA is determined by its mixing density and boundary conditions. The mixing density,  $\rho$ , is defined as

Figure 2.6. A mixed systolic array constructed from a diamond-like basis [6].

$$\rho = \frac{N_{sc}}{N_{sc} + N_{cc}}$$

(2.1)

where  $N_{SC}$  and  $N_{CC}$  are the number of switching cells and the number of computation cells, respectively. An MSA with high mixing density is suitable for implementation of algorithms which require more complex data routing and less computing. On the other hand, an array with low mixing density can be applied to algorithms which have simple data routing but require large amount of computing. When  $\rho=0$ , the MSA reduces to a fixed structure single-purpose systolic array, and when  $\rho=1$ , the MSA reduces to a reconfigurable interconnection network with no computing power. The boundary conditions in an MSA are represented by a boundary condition function,  $\Omega$ , which is defined as

$$\rho = \frac{N_{sc'}}{N_{sc}}$$

(2.2)

where N<sub>SC</sub> is the number of control buffers placed on the MSA boundary.

Various other general purpose reconfigurable VLSI architectures have been proposed such as Configurable Highly Parallel (CHiP) computer by Snyder [53], and the Programmable Systolic Chip by Fisher and Kung [14]. In the CHiP architecture, a lattice structure of programmable switches is incorporated, into which processing elements are placed at regular intervals. This architecture can implement various special purpose parallel architectures such as mesh structures and tree structures, under the supervision of a master controller. The controller broadcasts commands to all the switches to invoke a

particular configuration setting. This master controller may be undesirable for failure critical applications. In MSA architecture, neither a broadcasting of command signals nor a master controller is required; instead, the control structure is distributed among the switching cells and the computation cells of the array. While Chang and Fisher developed, characterized, and evaluated the basic computing model for MSAs [6], they did not present procedures for loading and implementing the distributed control structure required to establish a desired interconnection pattern on the MSA structure. Also, no formal methodology was presented for implementing a given algorithm into the MSA structure by systematically generating the control code required to reconfigure the array. The main motivation for this research work came from the above mentioned issues regarding algorithm design and implementation of MSAs.

### 2.3 ALGORITHM TRANSFORMATION AND MAPPING INTO VLSI STRUCTURES

Efficient implementation of algorithms on VLSI structures requires exploitation of parallelism in the algorithm and mapping of the communication structure algorithm into the array processor interconnection structure. An approach to design VLSI algorithms based on recurrences was first suggested by Cohen in [11] and later expanded by Johnnson and Cohen in [22], and Weiser and Davis in [56]. This approach is adopted from z-transforms in signal processing and uses delay operators (Z-operators) for specifying and representing sets of data as wavefront entities in the mathematical expressions.

Mathematical formulas are manipulated to obtain different expressions that correspond to different computational networks. The drawback with this approach is that the notation gets difficult to manage for complex computations. Leiserson and Saxe presented a general theory for optimizing a synchronous circuit by adjusting the number of register delays in the data paths [43]. This theory justifies some transformations used to eliminate broadcasting from semisystolic designs, but does not offer a methodology for systematically designing systolic arrays starting from a high-level language description of an algorithm.

Kuhn introduced the idea of exploiting parallelism in loops with multiple levels of nesting by reindexing the loop computations [30]. He used the concept of program dependence for detection and exploitation of parallelism in programs. He defined dependence as an arc in the dependence graph directed from the source occurrence of a variable to the destination occurrence of the same variable. Both the source and destination nodes are labeled by the values of the loop indices at which the generation and use of a variable occur, and the dependence arc is labeled by the difference vector of the source and destination labels. mapped several specific algorithms into SIMD computers with Нe single-stage interconnection networks and illustrated how the design of certain VLSI systolic arrays could be done automatically by reindexing algorithms. Moldovan [45-47] and Fortes [15] extended the approach of Kuhn, and formalized the procedure for mapping algorithms into VLSI architectures by transforming dependencies of the original algorithm by a reindexing transformation. Algorithm transformations comprise a time transformation which dictates the order of execution of computations and a space transformation which determines the data movement, and the array size and geometry. Necessary and sufficient conditions for the existence of a certain type of transformation are given in [45]. This approach is best suited to algorithms described by programs with loops or by recurrence equations.

Some other related work on formalizing the design process of algorithmically specialized devices has been reported by Cappello and Steiglitz [5], Quinton [49], and Lam and Mostow [40]. methodology is based on geometric transformations for mapping nested-loop algorithms into systolic arrays. The computation is modeled as a lattice in which nodes represent operations and edges represent data dependencies. Different systolic designs can be derived by applying geometric transformations to the lattice. Quinton's approach finds a uniform recurrent system of equations that is equivalent to the problem to be solved and maps this system of equations into a finite architecture. The methods given in [5] and [49], regarding the formalizing of systolic array design, are suitable for algorithms described by recurrence equations. Lam and Mostow described a design model, in which software transformations are first applied to put the algorithm to be implemented into a regular form conducive to systolic implementation. The algorithm is then mapped into a systolic design described by a structure and a driver. The structure describes the hardware cells and the driver defines data streams in terms of the original variables in the algorithm. This approach can process algorithms with simple FOR-loops and BEGIN-END blocks, but cannot deal

with conditional execution, computed iteration bounds and array indices.

A survey of systematic approaches to the design of algorithmically specified systolic arrays can be found in [16].

# 2.4 FAULT TOLERANCE IN SYSTOLIC ARRAYS

Fault-tolerant systems are capable of performing correctly even in the presence of one or more faulty components. Fault-tolerant systems require some form of redundancy incorporated in their design. This redundancy could be either physical or temporal, or a combination of the two [51]. Physical redundancy is provided by replicating resources and may involve the use of extra gates, memory cells or functional modules. A taxonomy of fault-tolerance techniques and various stages of response to a system-failure in a fault-tolerant system are described in [51].

Fault tolerance in a pipeline architecture is very critical because a single fault in any segment would cause a total failure of the pipeline. Physical redundancy can be incorporated in pipeline architecture either at the pipeline level or at the segment (module) level. Reconfigurable parallel pipelines can be utilized to implement fault tolerance and achieve better performance in terms of average throughput, mean time to failure (MTTF), and mean computation before failure (MCBF)[24]. Initially the system utilizes all the pipelines in parallel, but as soon as one segment in a pipeline fails, the pipeline containing the failed segment ceases operation resulting in a degradation in performance. The other segments in the ceased pipeline become available as spares to mask subsequent faults in adjacent

pipelines. In this way, whenever the system fails, it does it with graceful degradation.

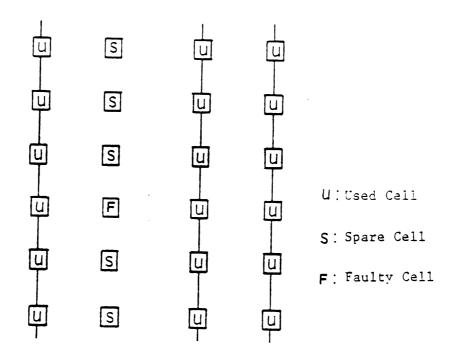

Although systolic array processing is a very efficient method of gaining increased system performance, this architecture is highly susceptible to faults. As a systolic array consists of many parallel pipelines, a single fault in any processing cell will propagate down the pipeline causing the system to fail. In two-dimensional systolic arrays, a single processing cell is shared by more than one pipelines, so the fault can propagate in multiple directions which makes the situation even worse. The above makes clear that the application of fault tolerance to a systolic array-based architecture is very critical. A fault-tolerant design of systolic arrays should enable an array to withstand one or more faults without total failure. This extends the life of the system and increases the mean time to failure (MTIF) and mean computation before failure (MCBF) for the system. Fault tolerance, of course, will require that redundancy be incorporated in the design of systolic arrays [20]. Temporal redundancy is not suitable because it adversely affects the system speed and throughput, which is not desirable if high performance is required. Physical redundancy can be introduced in the systolic array designs at the processing cell level or at the pipeline level. In response to a fault, the faulty cell or pipeline is discarded and replaced by another working one.

One method of designing fault-tolerant systolic arrays uses modular redundancy at the processing cell level. Triple modular redundancy (TMR) and N-modular redundancy will mask out the faulty outputs from a bad processing cell, but these are very costly techniques and their

application is limited to only critical short term uses [50]. Another fault-tolerant scheme, proposed in [36], enhances the yield of wafer-scale integration implementation of systolic arrays by replacing defective cells with clocked delays. This allows data to flow through the array with faulty cells at the original clock speed. Reconfigurable parallel pipelines for fault tolerance can be utilized in systolic arrays in order to achieve graceful degradation property. In case of no fault, all the pipelines are utilized and contribute to increased system performance. In case of faults, however, some pipes will shut down degrading the system performance. This makes many processing cells available to be used to mask out any further faults.

# 2.5 LEVEL SENSITIVE SCAN DESIGN (LSSD) TECHNIQUES

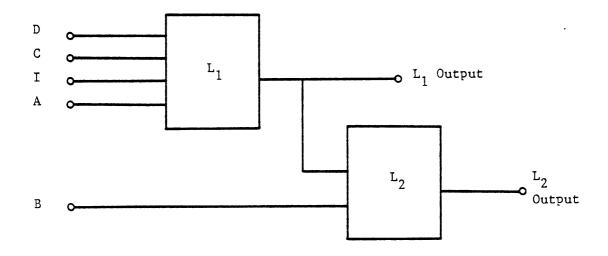

LSSD is IBM's discipline for structural design for testability [12]. In this concept, the memory elements or latches in an IC can be threaded together to form a serial-in, serial-out shift register. This provides an efficient means for "controlling" and "observing" the internal states of a machine with only three or four additional pinouts.

A key element in this design is the "shift register latch" (SRL) as shown in Figure 2.7 [57]. Since IBM has used the LSSD technique extensively, considerable attention has been given to the efficient implementation of LSSD latches such that the overhead due to complexity of SRLs is substantially reduced [13]. The lines D and C form the normal mode memory function while lines I, A, B and L2 comprise circuitry for the shift register function. The shift registers are

Figure 2.7. Block diagram representation of a shift register latch.

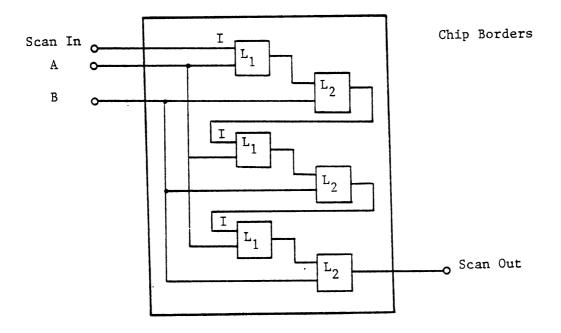

Figure 2.8. Interconnections of SRLs on an integrated circuit [57].

threaded by connecting I to L2 and operated by clock lines A and B in two phase fashion. Figure 2.8 illustrates how four SRLs can be threaded together for shift register action, and Figure 2.9 shows general structure of an LSSD subsystem with two clocks. Specific design rules and constraints concerning gating of clocks, etc., are given in [12].

LSSD techniques are employed in reconfigurable systolic architectures for loading and implementing the control structure required for reconfiguration [25]. The main advantage of using the LSSD technique is that overhead due to additional pinouts does not exceed three or four pins regardless of the size of the array. Shift register latches (SRLs) hold the control information. All SRLs are threaded together in a chain of shift registers in a manner such that a control vector entered in a bit-serial fashion sets up the array configuration for a particular algorithm.

Figure 2.9. General structure of an LSSD subsystem with two system clocks [57].

#### CHAPTER 3

# A LINEAR RECONFIGURABLE SYSTOLIC ARRAY (LRSA) ARCHITECTURE

The Level Sensitive Scan Design (LSSD) technique is employed in mixed systolic arrays to load and implement the distributed control structure required to configure the array for a desired algorithm implementation. To illustrate the concepts, this chapter presents the design of a one-dimensional linear reconfigurable systolic array (LRSA). This array structure is statically reconfigurable to realize any of the following: a filtering array, an FIR filtering array, a pattern matching array, and a Discrete Fourier Transform (DFT) array. What's more, the array structure is partitionable and can be divided into two or more independent subarrays, each capable of executing a preprogrammed algorithm. Shift register latches (SKLs) hold the control information for setting up the interconnections configuration and selecting the functional mapping of computation cells. Both the data flow through the array and the functions executed in the computational cells are established by inputting a control vector in a bit-serial fashion, using a two-phase clock. The next section describes the structure of the LRSA, and Section 3.2 characterizes four systolic algorithms which can be implemented on this structure.

#### 3.1 STRUCTURE OF THE LINEAR RECONFIGURABLE SYSTOLIC ARRAY

The linear reconfigurable systolic array can be configured to implement one or more of the following types of systolic arrays: 1) a general filtering array, 2) a FIR filtering array, which has better resource utilization than the general filtering array, 3) a pattern matching array, and 4) a Discrete Fourier Transform (DFT) array. The systolic algorithms for the above mentioned arrays are described in Section 3.2. The LRSA architecture is configured, by simply loading a binary control vector through the LSSD scan input line, such that the computational and the data-flow structures of the algorithm are implemented on the array architecture. Once the array is configured, the architecture matches the algorithm structure exactly. Structure of the LRSA can be divided into three parts, the computation cells array, the function-select array and the data flow control array. Figure 3.1 illustrates a system block diagram of this structure, and each part is described in the remainder of this section.

#### 3.1.1 THE COMPUTATION CELLS ARRAY

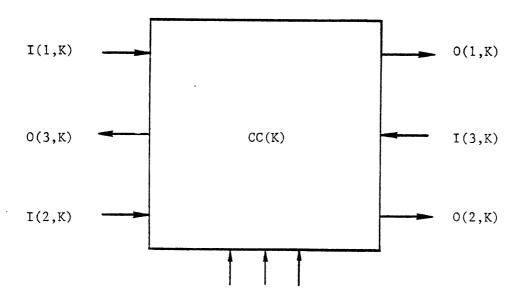

All computation cells are identical so the modularity is preserved in the design. This, of course, is an important factor in the efficient design and implementation of systolic arrays [22]. Each computation cell has three input data ports and three output data ports. These are all local ports except for the cells at the extreme ends of the array, where global I/O ports are used. Due to the local I/O ports the interconnections are regular, simple and short. Three control bits select the functionality of the computation cell. Figure 3.2 shows a

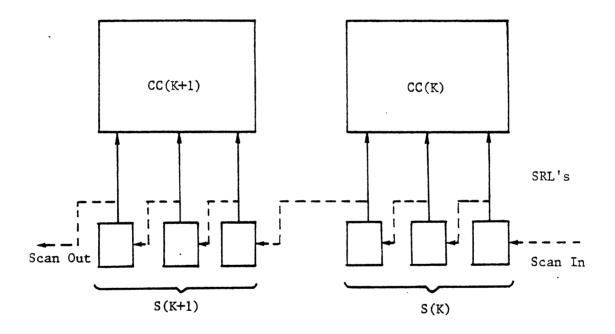

Figure 3.1. General system diagram of the Linear Reconfigurable Systolic Array.

Function-Select Lines

Figure 3.2. Block diagram representation of a Computation Cell.

computation cell at K'th position in the array. The control input lines will be referred to as function-select lines. For a computation cell CC(K), the input ports are referred to as I(1,K), I(2,K) and I(3,K), whereas the output ports are O(1,K), O(2,K) and O(3,K). Each cell contains two operand register buffers A(K) and B(K), which hold the filter coefficients loaded by the host, prior to start of computation.

Let set of function-select lines for cell CC(K) be called S(K). Then, functions of the computation cell can be described as follows:

Begin

$O(1,K) \leftarrow I(1,K)$

$O(2,K) \leftarrow I(1,K)*I(2,K)+A(K)$

end if

end

R(K) is a flip flop in each computation cell which is used in the pattern matching algorithm. A(K) and B(K) are two registers in each CC(K) which hold the coefficients loaded from the host or main memory.

# 3.1.2 FUNCTION-SELECT ARRAY

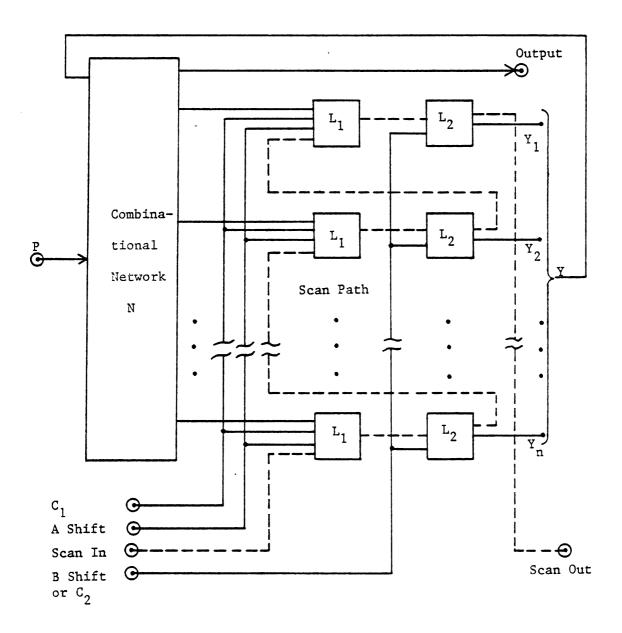

The function-select array contains a three-bit element for each computation cell; the contents of this array select the function performed by the computation cell. Each computation cell can be programmed to perform a selected primitive arithmetic or logic operation by setting its function-select array element. All elements of the function-select array consist of SRLs which are all threaded together to form a shift register. The control information can be entered in a bit-serial fashion using two phase clock via Scan In input line, as shown in Figure 3.3.

# 3.1.3 DATA FLOW CONTROL ARRAY

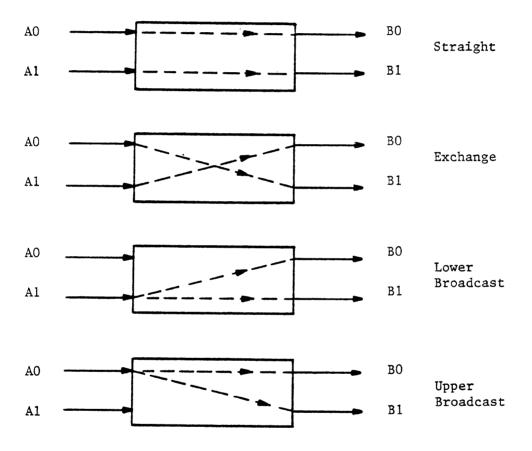

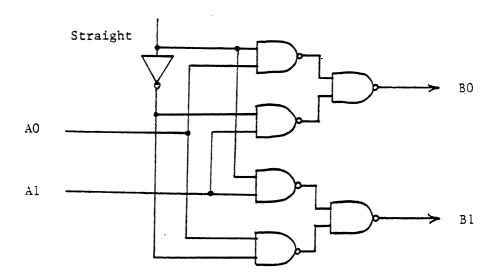

The data flow control array contains the control information for the interconnection network configuration. Data flow control is achieved by employing interchange boxes which are devices with two inputs and two outputs. Figure 3.4 shows the four legitimate states of an interchange box. Two-bit control is required for each box and the control bits for each box are stored in an SRL. All SRLs are threaded together as in case of the function-select array. Figure 3.5 shows a hardware implementation

Figure 3.3. SRLs are used in the function-select array.

Figure 3.4. Four interconnection states of an interchange box.

Figure 3.5. Logic diagram of a two-function interchange box.

of an interchange box.

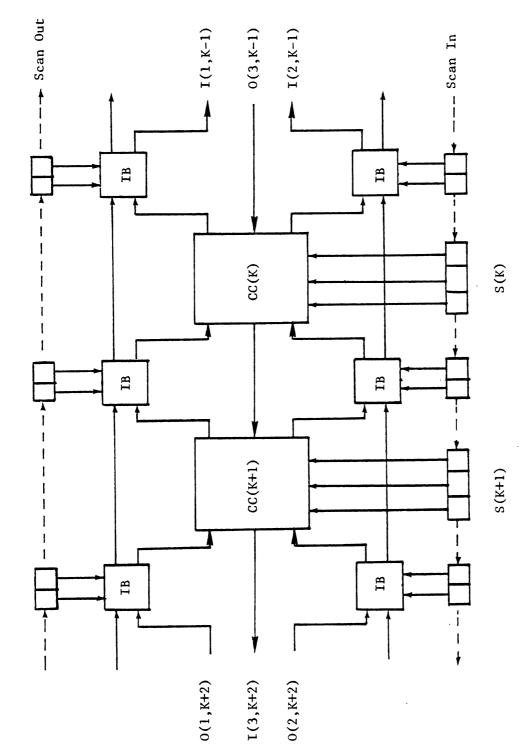

Figure 3.6 illustrates how two adjacent cells in the LRSA are connected together with interchange boxes and function—select elements. Although the computation cells are multifunctional, yet various functions are computationally not much different from each other. By employing some data selection logic in an inner product step processor, computation cells for LRSA could be obtained. So, the overhead because of introducing complexity in the computation cell by making it multifunctional should be small. All the control information is entered through one pin in a bit-serial fashion, so overhead because of additional pinouts is minimal.

#### 3.2 SYSTOLIC ALGORITHMS IMPLEMENTED ON THE LRSA

This section describes four systolic algorithms implemented on the LRSA. These algorithms include general filtering, Finite Impulse Response (FIR) filtering, pattern matching and Discrete Fourier Transform (DFT).

# 3.2.1 SYSTOLIC FILTERING ARRAY

The general filtering problem is defined as follows [49]:

Given the weighting coefficients  $\{w_0, w_1, \dots, w_h\}$ ,  $\{r_1, r_2, \dots, w_h\}$

,  $x_k$ , the initial values  $\{y_{-k}, y_{-k+1}, \dots, y_{-1}\}$ , and the input sequence  $\{x_{-h}, x_{-h+1}, \dots, x_0, x_1, \dots, x_n\}$ ,

compute the output sequence  $\{y_0, y_1, \dots, y_n\}$  defined by

Figure 3.6. Structure of the Linear Reconfigurable Systolic Array.

$$y_i = \sum_{j=0}^h w_j x_{i-j} + \sum_{j=1}^k r_j y_{i-j}.$$

(3.1)

A systolic array to implement the above filtering problem is shown in Figure 3.7 [49]. This array computes a new output  $y_i$  every two cycles, where a cycle is the time to perform two multiplications and two additions. The weighting coefficients  $w_i$ 's and  $r_i$ 's are preloaded into the array. The filtering computation starts by loading the  $x_i$ 's from the host to the systolic array. When the array has received all the  $x_i$ 's for  $-h \le i < 0$ , it starts outputting the computed  $y_i$ 's at the rate of one every two cycles.

The two types of basic cells used are shown in Figure 3.7(a). The systolic array for filtering is a linear array and consists of m type-1 cells and one type-2 cell, where m = max(h+1,k). Each  $y_i$  is initialized as zero as entering the array from the right-most cell. It accumulates terms as it travels along the array towards left and eventually achieves its final value  $y_i$  when reaching the left-most cell. The output  $y_i$  is fed back into the array for use in other computations.

In order to implement the above filtering algorithm on an LRSA consisting of (m+1) computation cells, the function-select elements should be as follows:

$$S(K) = 001, 1 \le K \le m$$

:

$$S(K) = 011, K = m+1$$

The switching cells in the array should be used in straight configuration. It can be easily seen from Figure 3.6, that exchange and broadcast configurations of the switching cell can be used to partition

# TYPE-1 CELL:

# TYPE-2 CELL:

(a)

m TYPE-1 CELLS

y<sub>i</sub>'s

x<sub>i</sub>'s

Figure 3.7. One-dimensional systolic array for filtering:

- (a) basic cells used in the array,

- (b) the systolic filtering array.

(b)

the LRSA into subarrays, or to bypass faulty computation cells.

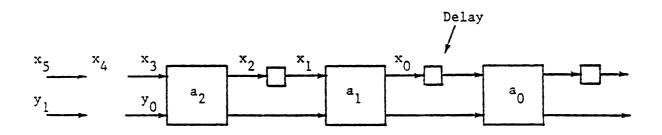

# 3.2.2 SYSTOLIC FIR FILTERING ARRAY

The general filtering problem described in the previous subsection realizes systems having Infinite-duration Impulse Response (IIR). Such systems involve a recursive computational algorithm. In the case of Finite-duration Impulse Response (FIR) systems [49], realization generally takes the form of a nonrecursive computational algorithm. FIR filtering problem is a special case of the general filtering problem given in Subsection 3.2.1 where  $r_{i=0}$  for all 1  $\leq$  i  $\leq$  k. The dedicated throughput of the systolic array for filtering described in the previous subsection is one half, i.e. only one half the cells in the array are active at any given time. Figure 3.8 shows a systolic array for FIR filtering algorithm [24]. Data streams move in the same direction at two different speeds in the systolic array and all the cells are used all the time. The basic cell used in the design is shown in Figure 3.8(a). The Wi's are preloaded in the array during the initialization phase. the xi's and yi's travel towards right but yi's travel twice as fast as x<sub>i</sub>'s. Each y<sub>i</sub> accumulates terms as travelling towards right and achieves its final value as it leaves the right-most cell. The FIR filtering problem is mathematically identical to the convolution problem, so the systolic array described here also applies to convolution computations.

In order to implement the FIR filtering algorithm on the LRSA, the function-select elements for all the computation cells in the array, should contain 010, i.e.,

$$x_{in}$$

$y_{out}$

$x_{in}$

$y_{out}$

$x_{in}$

$y_{out}$

$x_{in}$

$y_{in}$

$y_{out}$

$y_{out}$

(a)

Figure 3.8. One-dimensional systolic array for FIR filtering:

- (a) basic cells used in the array,

- (b) the systolic FIR filtering array.

$S(K) = 010, 1 \le K \le h$

# 3.2.3 PATTERN MATCHING SYSTOLIC ARRAY

A systolic array design for pattern matching problem is shown in Figure 3.9 [24]. The pattern matching problem can be defined as follows:

Given a text string  $(s_1, s_2, \ldots, s_n)$  and a pattern string  $(p_1, p_2, \ldots, p_m)$ , with n much larger than m,

compute positions of all occurrences of the pattern within the text

string.

For example, if the text string is DBABBFBABABB and the pattern is BAB, then the result is 010000101000, where each '1' indicates the beginning position of an occurrence of the pattern inside the text string. Let the resulting Boolean string be  $\{r_1, r_2, \dots, r_{n-m+1}\}$ , such that  $r_i=1$  if and only if  $(s_i, s_{i+1}, ..., s_{i+n-1}) = (p_1, p_2, ..., p_m)$ . Then the systolic array shown in Figure 3.9, using the basic cell as shown, can compute the ri's by comparing the characters of the pattern with the characters of the text string. Each ri is initialized to be a '1'. A pattern character pk and a text string character si are compared at the cell where they meet and the cell updates the value of r; such that  $r_i \leftarrow r_i$  AND  $(p_k=s_j)$ . In case of a mismatch, the value of  $r_i$  is reset to '0'. The pattern string travels towards right and the text string travels towards left, such that each pattern character meets each text The value of ri at a cell finalizes when the last character in the pattern string passes through that cell. This systolic array with m cells can solve the pattern matching problem in time n, whereas a sequential software solution takes time proportional to men.

(a)

Figure 3.9. One-dimensional systolic array for pattern matching:

- (a) basic cells used in the array,

- (b) the systolic pattern matching array.

In order to implement the pattern matching algorithm on an LRSA consisting of m computation cells, the function-select elements for all the computation cells in the array should contain 100, i.e.,

$$S(K) = 100, 1 \le K \le m$$

# 3.2.4 DISCRETE FOURIER TRANSFORM (DFT) SYSTOLIC ARRAY

An n-point Discrete Fourier Transform (DFT) is defined as follows: Given  $\{a_0, a_1, \ldots, a_{n-1}\}$  be n samples of a time function, compute  $\{y_0, y_1, \ldots, y_{n-1}\}$  defined by

$$y_i = \sum_{j=0}^{n-1} a_j * w_{ij},$$

(3.2)

where  $w = e^{2\pi k/n}$  and k = -1.

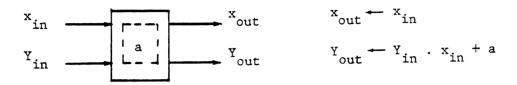

The straightforward method for computation of n-point DFT requires  $O(n^2)$  operations and the Fast Fourier Transform (FFT) algorithm requires  $O(n\log n)$  operations for the same computation. The linear systolic array shown in Figure 3.10 [48] with (n-1) basic cells can compute an n point DFT in O(n) time. However, the communication scheme for the systolic array is much simpler compared to the complicated data communication requirements for the FFT algorithm. The basic cell used in the DFT systolic array is essentially a multiplier-accumulator cell and is shown in Figure 3.10(a). The array consists of (n-1) basic cells and the input samples  $a_{n-2}$  to  $a_0$  are preloaded in the array cells. The inputs  $Y_{in}$  and  $x_{in}$  to the left-most cell are  $a_{n-1}$  and some power of w, respectively. The output  $x_{out}$  from the right-most cell is always ignored. Each  $y_i$ ,

(a)

Figure 3.10. Linear systolic array for DFT algorithm:

- (a) basic cells used in the array,(b) the systolic DFT array.

initialized as a<sub>n-1</sub>, accumulates its terms as travelling towards right, and reaches its final value as it leaves the right-most cell.

In order to implement an n-point discrete Fourier transform algorithm on the LRSA, the function-select elements for all the computation cells in the array, should contain 101, i.e.,

$S(K) = 101, 1 \le K \le n-1$

# 3.3 SUMMARY AND DISCUSSION

This chapter presented the architecture and design of a one-dimensional Linear Reconfigurable Systolic Array. This design approach illustrates how the level sensitive scan design technique can be employed in mixed systolic arrays, to load and implement the distributed control structure required to configure the array for a desired algorithm implementation. The control structure for a particular configuration is loaded into the array through the LSSD scan path as a binary vector in a bit-serial fashion. This approach has the advantage that overhead in terms of additional pinouts is limited to only three or four pins. Also, serial loading of the control structure reduces the overhead in terms of additional interconnections on the chip due to the control hardware.

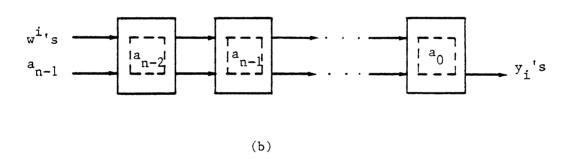

The major incentive for employing the LSSD technique in the design of the LRSA is to load the configuration control code in the array. This approach, in addition, enhances testability, incorporates fault tolerance, and provides capability for initializing the internal data registers of individual cells. In order to achieve testability and data

Figure 3.11. LSSD scan path within a computation cell incorporating testing and register initialization.

register initialization capability, the LSSD scan path must pass through the data registers and the input/output ports of each cell. Figure 3.11 shows one possible arrangement for a scan path within a computation cell. Registers X, Y and Z are the local output ports; S is the control register which selects the function performed by the computation cell; A and B are the data registers for holding the preloaded coefficients and R is a flip-flop used to save the result of a Boolean operation in pattern matching algorithm. This arrangement provides capability for testing the functionality of the individual cells, initializing the registers and preloading the coefficients. During test mode, a desired bit-vector is loaded into the array through LSSD scan path. This vector contains the control information required for each cell as well as the test data for data registers. After the vector has been loaded, one system clock is applied so that each cell can perform its required function. The results in the local output ports are scanned out using LSSD shift clock. This vector contains results of the operations performed by all the cells. A comparison of this vector with the expected results helps identify the faulty cells which may be bypassed by reconfiguring the chip. Fault tolerance in mixed systolic arrays employing LSSD techniques is discussed in more detail in Chapter 4, where this approach is extended to two-dimensional mixed systolic arrays.

#### CHAPTER 4

# DESIGN OF A MULTIPURPOSE RECONFIGURABLE ARRAY PROCESSOR (MRAP)

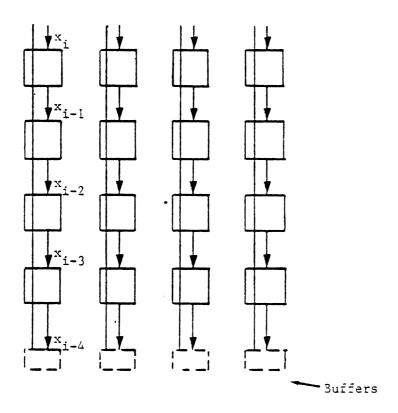

Chapter 3 presented a design approach for mixed systolic arrays, which employs the level sensitive scan design technique for configuring the array architecture to match the structure of the algorithm to be This chapter extends the same approach to two-dimensional implemented. mixed systolic array architectures, and discusses the issues of fault tolerance, performance analysis and algorithm implementation. We present the design of an MSA-based processor, called the multipurpose reconfigurable array processor (MRAP). This architecture implements both systolic and semisystolic algorithms, and incorporates fault tolerance in its design. The performance of MRAP, taking into account the total computation time and the data-transfer bandwidth, is analyzed for specific algorithms. Also, it is demonstrated, by way of examples, how the MRAP can efficiently implement different systolic and semisystolic algorithms. Structure of the MRAP is a two-dimensional array type, which can be configured to implement a number of systolic and semisystolic algorithms involving two-dimensional linear recurrences such as matrix manipulations. This two-dimensional array could also be partitioned into many independent linear arrays to implement independent algorithms involving one-dimensional linear recurrences such as finite impulse response (FIR) filtering.

The next section describes the structure of the MRAP, the design of basic functional cells and the data flow in the array at register-transfer level. Section 4.2 illustrates, by way of examples, how the MRAP can be configured to implement different parallel algorithms. In Section 4.3, performance of the MRAP is analyzed and compared with other existing systolic structures. Section 4.4 investigates fault tolerance capabilities inherent in the MRAP design. Finally, a summary and discussion is presented in Section 4.5.

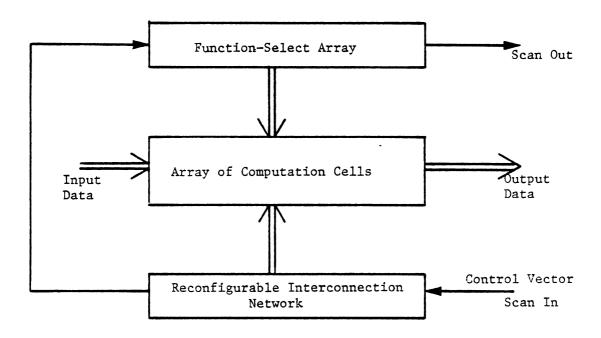

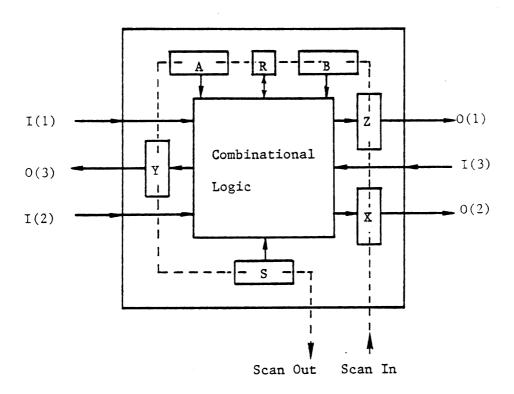

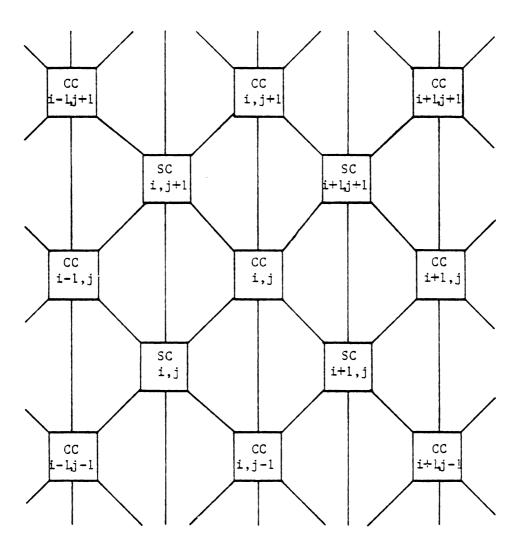

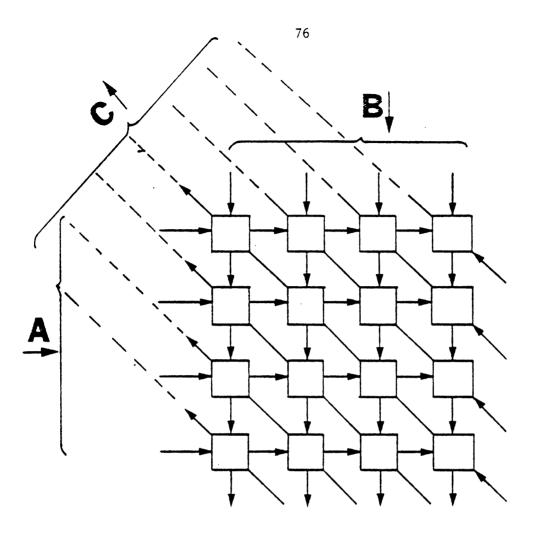

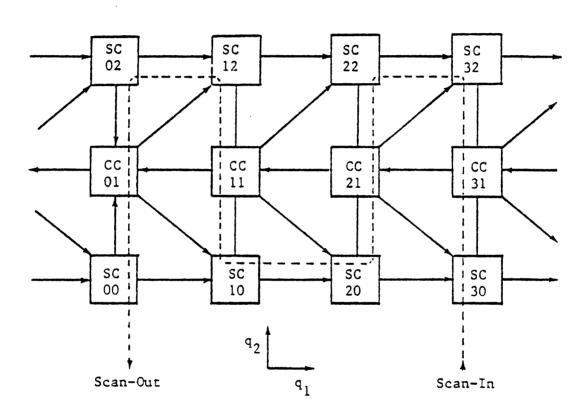

#### 4.1 STRUCTURE OF THE MULTIPURPOSE RECONFIGURABLE ARRAY PROCESSOR

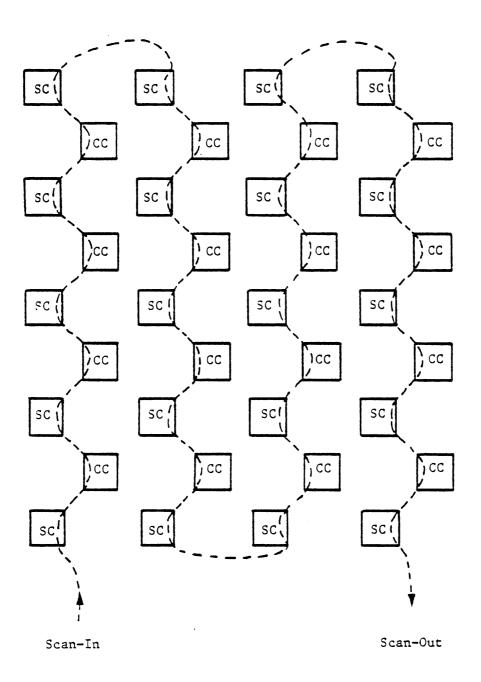

The multipurpose reconfigurable array processor (MRAP) employs two types of basic elements, computation cells and switching cells, as shown in Figure 4.1. In general, the computation cells and the switching cells are mixed according to a certain mixing profile which determines the possible frames of data-flow patterns within the array. Mixing profile is specified by the mixing density and the basis of the array [6]. The MRAP designed here, is constructed from a diamond-like basis with a mixing density of 1/2, i.e., switching cells and computation cells are equally represented in the basis. The control structure communication and computation is embedded in both types of cells in form of control registers. We employ the LSSD technique to realize this control structure. All the control registers are threaded together through a Scan-In line as shown in Figure 4.2. For a particular configuration the control structure is realized by loading a binary vector through the Scan-In line in a bit-serial fashion. In the next

CC : Computation Cell

SC : Switching Cell

Figure 4.1. The Structure of the Multipurpose Reconfigurable

Array Processor (MRAP).

Figure 4.2. Scan Path for Loading the Control Vectors.

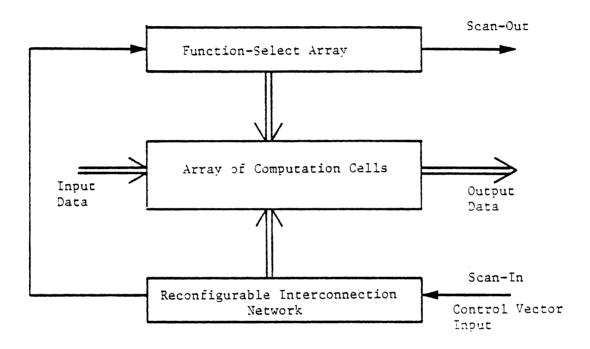

section, we provide some examples of how the control vectors can be generated for implementing different algorithms. Figure 4.3 shows the system block diagram of the array and each part of the structure is described later in this section. The array can be configured in various topologies depending upon the application, such that a variety of algorithms can be efficiently implemented. Various configurations obtained from this structure are discussed in Section 4.2. In the remainder of this section, we describe the design of the computation cell and the switching cell. Also, a register-transfer level data-flow description and a timing diagram for the computation cell are given.

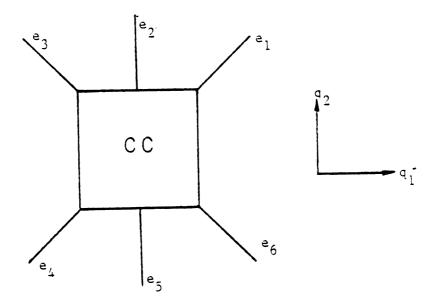

#### 4.1.1 THE COMPUTATION CELL

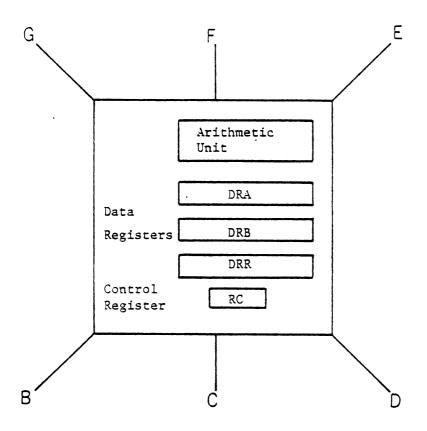

The computation cell is basically an inner product step processor with some extra control logic added into it. All computation cells are identical so the modularity is preserved in the design. This, of course, is an important factor in the efficient design and implementation of structures for VLSI computation. Each computation cell has six data ports, which are all local ports except for the cells at the boundary of the array, where global I/O ports are used [6,8]. Due to local I/O ports the interconnections are simple, regular and short. Three control bits are used to select the functionality of the computation cell. There are three dedicated data registers DRA, DRB and DRR which can be used to hold the preloaded coefficients or the results of a local computation. There is a three-bit control register, comprising of shift-register latches and threaded into the Scan-In line. We shall refer to this control register as RC and the three latches in it as RCO, RC1 and RC2. The input-output

Figure 4.3. General System Diagram of the MRAP.

functional mapping of a cell is determined by the contents of RC. Figure 4.4 shows a computation cell and describes some of its functions for different control vectors. A register-transfer level description of various operations is given later in this section.

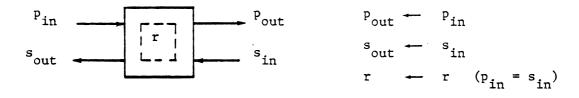

# 4.1.2 THE SWITCHING CELL

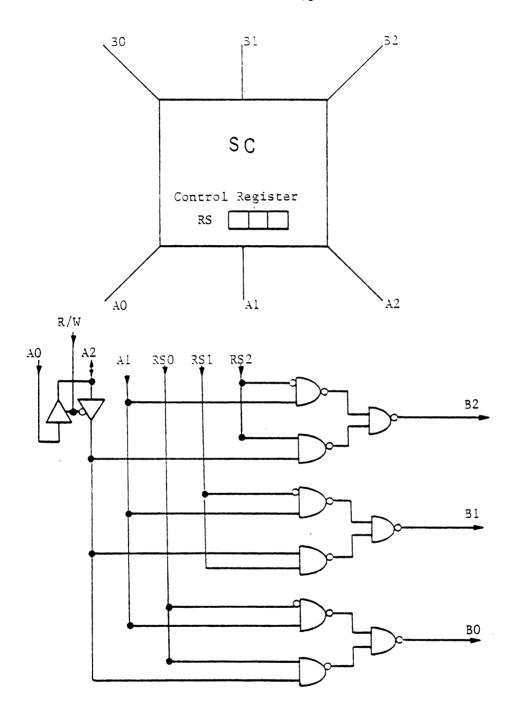

The switching cell used in this array is an extension of the two-by-two interchange box [52] and is shown in Figure 4.5. When the R/W control line is low, this switching cell acts as a single-stage, nonblocking SIMD interconnection network which requires three-bit control to realize all possible connections from input lines A1, A2 to the output lines B0, B1 and B2, without resulting in a conflict. When R/W line is high, A2 acts as an output line which is connected to the input A0. R/W is a local I/O control provided by the neighboring computation cell at line A2. The control bits are held in the three-bit control register RS associated with each switching cell. Figure 4.5 shows a logic implementation of the switching cell. A function table for the switching cell is given in Table 4.1, where RSO, RS1 and RS2 are the bits in the control register RS.

## 4.1.3 DATA-FLOW AND TIMING

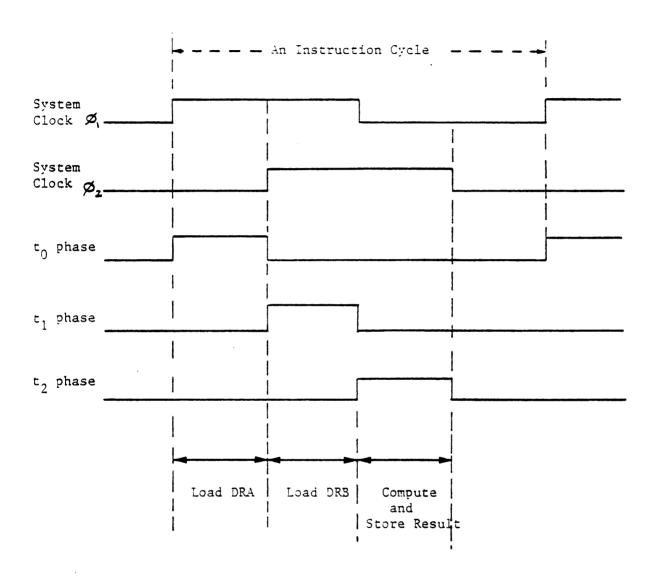

This section describes a register-transfer level description of data-flow in the array. Figure 4.6 shows a timing diagram for the instruction cycle of the computation cell, when a two-phase system clock is used. There are three phases in the instruction cycle, as shown in Figure 4.6. Phases  $t_0$  and  $t_1$  are used to latch input data from the

```

Begin

DRA →  − G

if RC=001 then

elseif RC=010 then

E ← − − DRA