#### This is to certify that the

#### dissertation entitled

# AN INTELLIGENT MICROSENSOR FOR MONITORING ROLLING ELEMENT BEARINGS

presented by

Mark B. Chuey

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Elect. Engr.

Milliel Shavellet

Date \_\_\_\_11/11/93\_\_\_\_\_

MSU is an Affirmative Action/Equal Opportunity Institution

10 to 20 0

0-12771

## LIBRARY Michigan State University

PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due.

|       | DATE DUE | DATE DUE |

|-------|----------|----------|

| EN 25 |          |          |

|       |          |          |

|       |          |          |

|       |          |          |

|       |          |          |

|       |          |          |

|       |          |          |

MSU is An Affirmative Action/Equal Opportunity Institution c\circ\data\u00e4a.pm3-p.1

AN I MONITO

# AN INTELLIGENT MICROSENSOR FOR MONITORING ROLLING ELEMENT BEARINGS

By

Mark D. Chuey

#### **A DISSERTATION**

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

**DOCTOR OF PHILOSOPHY**

Department of Electrical Engineering

1993

The ability to examined by designing post suspended mass in This is converted to an by a temperature-complete temove any offset order. 256-times over aciel first-stage deciminationing. The outpleasure is a resolution to a resolution.

programmable sixth-ord

compared to a program

when the threshold is e

extraction logical

some element in a plan-

A simulation of stateters. The programmes as well as the sign

#### **ABSTRACT**

## AN INTELLIGENT MICROSENSOR FOR MONITORING ROTATING ELEMENT BEARINGS

by

#### Mark D. Chuey

The ability to monitor rolling element bearings with an intelligent microsensor is examined by designing key elements of the device. The intelligent sensor contains a four-post suspended mass microaccelerometer to sense bearing housing acceleration vibrations. This is converted to an electrical signal through a half-active piezoresistive bridge driven by a temperature-compensated supply. The voltage output is amplified, high-pass filtered to remove any offset signal, and low-pass filtered. The result is digitized in a second-order, 256-times oversampling sigma- delta modulating analog-to-digital converter. A novel first-stage decimator, located on-chip, provides a minimum resolution of 9 bits for monitoring. The output of the decimator can be transmitted off-chip for second-stage decimation to a resolution suitable for diagnostic purposes or it can be put into on-chip feature extraction logic. Feature extraction is accomplished by filtering the signal in a programmable sixth-order IIR filter then extracting the mean squared value. This value is compared to a programmable threshold value. An alarm signal is transmitted off-chip when the threshold is exceeded a programmable number of times. The sensor is to serve as one element in a plant-wide multisensor monitoring system.

A simulation of bearing housing vibrations is developed to examine monitoring parameters. The program simulates different types of point defects and random noise sources as well as the signal transmission path through the housing. Comparisons between

peak value, mean so frequencies. The effor features are also exam-

The on-chip s

Ext-stage decimation

generator accumulator

require less circuit are

aministing A classific

peak value, mean squared, crest and kirtosis measures are made for various sampling frequencies. The effects of sampling resolution on mean squared and spectral monitoring features are also examined.

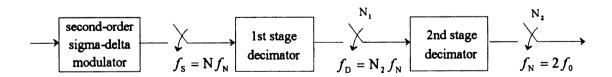

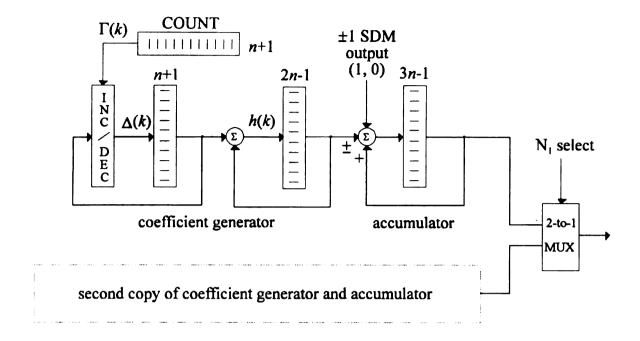

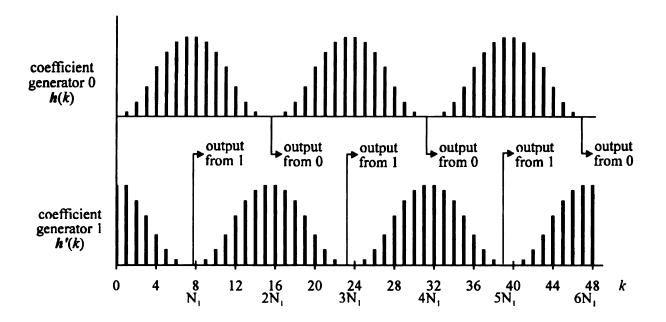

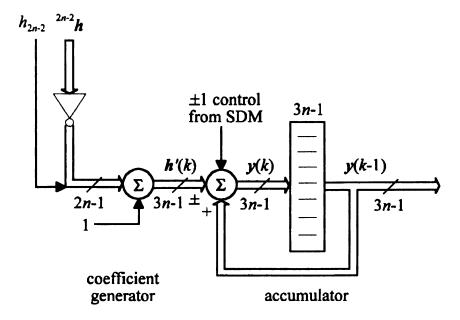

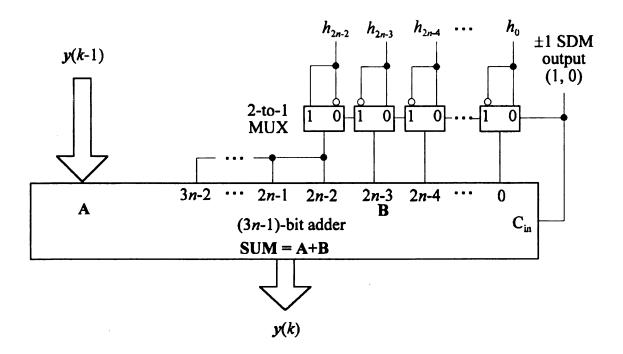

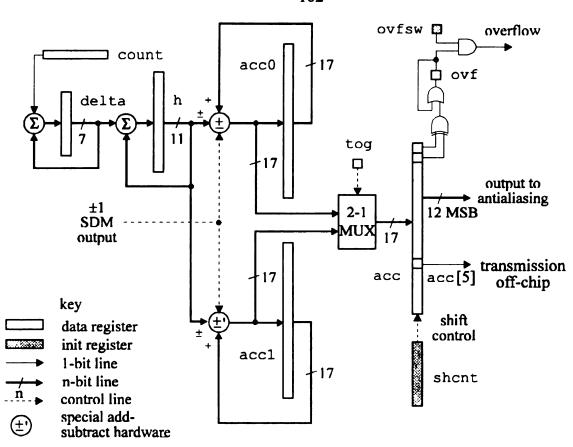

The on-chip sigma-delta modulating analog-to-digital converter employs a novel first-stage decimation filter. The sinc<sup>3</sup> FIR filter uses two coefficient generator/accumulator pairs, each alternately producing an output. The filter is shown to require less circuit area than previous designs at a cost of reduced noise rejection and antialiasing. A classification scheme for sinc<sup>3</sup> filters is also provided.

No project of people Abrief listing

I would first

Fisher, Dr. J. Hall, Dr.

D. M. Shanblan

I would also

Eigneering Departmer

thoughout the past e

diring this period. Fred

ण leaching schedule t

Many thanks to

Dr Jeff Abell for pro-

Burgett for his suggest

traliable strategic advis

The support and friends has be

la: Furkioti for her pati

A special thank

Position have been positions

#### **ACKNOWLEDGMENTS**

No project of this size can be completed without the help and support of many people. A brief listing of some of those people is provided here.

I would first like to thank the members of my doctoral committee: Dr. P. D. Fisher, Dr. J. Hall, Dr. M. Nayeri, Dr. R. Tonda, Dr. C. L. Wey and the committee chair, Dr. M. Shanblatt.

I would also like to acknowledge the faculty of the Electrical & Computer Engineering Department at GMI Engineering and Management Institute for their support throughout the past eight years. Special thanks is extended to the department heads during this period, Fred Cribbins and Dr. Dave Leffen, for their cooperation in arranging my teaching schedule to accommodate the requirements of the doctoral program.

Many thanks to Pat Irish for producing some of the figures in Chapters 3 and 4, Dr. Jeff Abell for proofreading the technical chapters of this dissertation, Dr. Scott Burgett for his suggestions in the area of signal processing, and Gerald Vossler for invaluable strategic advice.

The support and understanding of my parents, Donald and Rosemary Chuey, my family and friends has been invaluable throughout this project. I would also like to thank Jean Furkioti for her patience.

A special thank you is extended to Dr. Richard Tonda for his help with the mechanical design of the microaccelerometer. Without Rick's assistance this project would not have been possible.

LIST OF TABLES

LIST OF FIGURES

CEAPTER 1 INTRO:

11 MACHINES

12 Marian

13 PROJECTS

14 Acc 3277

141 K

142 Te

143 V.

15 OVERVEW

CHAPTER 2 BEARING

11 BEASTALL

22 BEAUNG VI

23 VERATIONS

231 Tra:

232 Sign

23.3 Sign

234 Fea:

24 BEARING Visit

24.1 Béar

242 Simu

## **TABLE OF CONTENTS**

| LIST OF TABLESx                              |    |

|----------------------------------------------|----|

| LIST OF FIGURESxi                            | ii |

| CHAPTER 1 INTRODUCTION 1                     |    |

| 1.1 MACHINERY MONITORING 1                   |    |

| 1.2 Intelligent Sensor Monitoring System     |    |

| 1.3 Project Scope 6                          |    |

| 1.4 ASSUMPTIONS8                             |    |

| 1.4.1 Knowledgeable User                     |    |

| 1.4.2 Temperature Range                      |    |

| 1.4.3 Vibration Signal Ergodicity9           |    |

| 1.5 OVERVIEW10                               | 0  |

| CHAPTER 2 BEARING VIBRATIONS 12              | 2  |

| 2.1 BEARING LIFE AND FAILURE 13              | 3  |

| 2.2 BEARING VIBRATIONS                       | 5  |

| 2.3 VIBRATION SIGNALS AND FEATURE EXTRACTION | 8  |

| 2.3.1 Transducer Type and Location           | 9  |

| 2.3.2 Signal Frequency Range 20              | 0  |

| 2.3.3 Signal Magnitude Range and Resolution  | 0  |

| 2.3.4 Feature Extraction Methods 22          | 2  |

| 2.4 BEARING VIBRATION SIMULATION 20          | 6  |

| 2.4.1 Bearing Vibration Model                | 6  |

| 2.4.2 Simulator Input                        | 7  |

243

244

25 SMCTAT

251

252

26 M NT 4

CHAPTER 3 TRAN

31 \$1500 C

311

312 3131

32 F.N.T. E. .

3211

322 S

323 E

324 F

33 PEZORENI

3.3.1 7

332 P

333 P

3.3.4 P.

34 PERFORMS

3.4.1 R

3,4,2 Re

| 2.4.              | 3 Simulator Operation Details   | . 30 |

|-------------------|---------------------------------|------|

| 2.4               | 4 Simulator Example             | . 31 |

| 2.5 SIMUL         | ATION RESULTS                   | . 36 |

| 2.5.              | 1 Feature Extraction Simulation | . 36 |

| 2.5.              | 2 Quantization Simulation       | . 40 |

| 2.6 <b>M</b> ONIT | OR SYSTEM SPECIFICATIONS        | . 42 |

| CHAPTER 3 TRA     | ANSDUCER                        | . 44 |

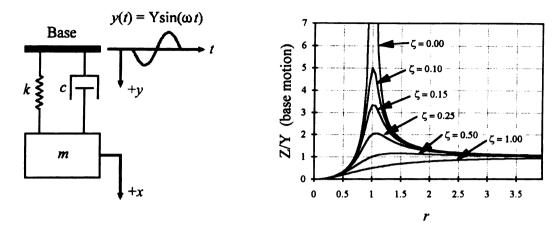

| 3.1 SUSPE         | NDED MASS ACCELEROMETER THEORY  | . 44 |

| 3.1.              | 1 Mass-Spring-Damper System     | . 44 |

| 3.1.              | 2 Transducer Geometry           | . 46 |

| 3.1.              | 3 Isotropic Beam Theory         | . 47 |

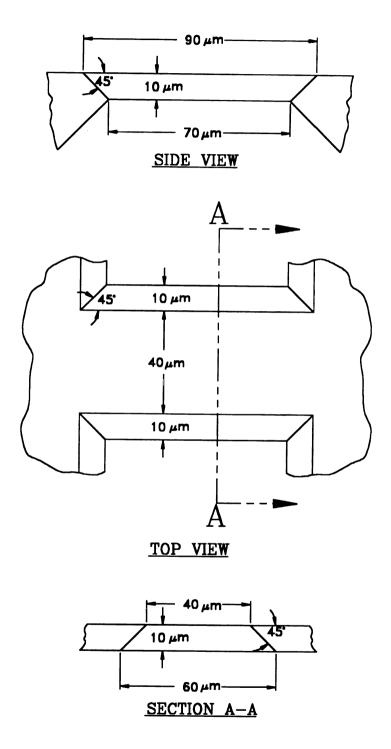

| 3.2 FINITE        | ELEMENT ANALYSIS                | . 53 |

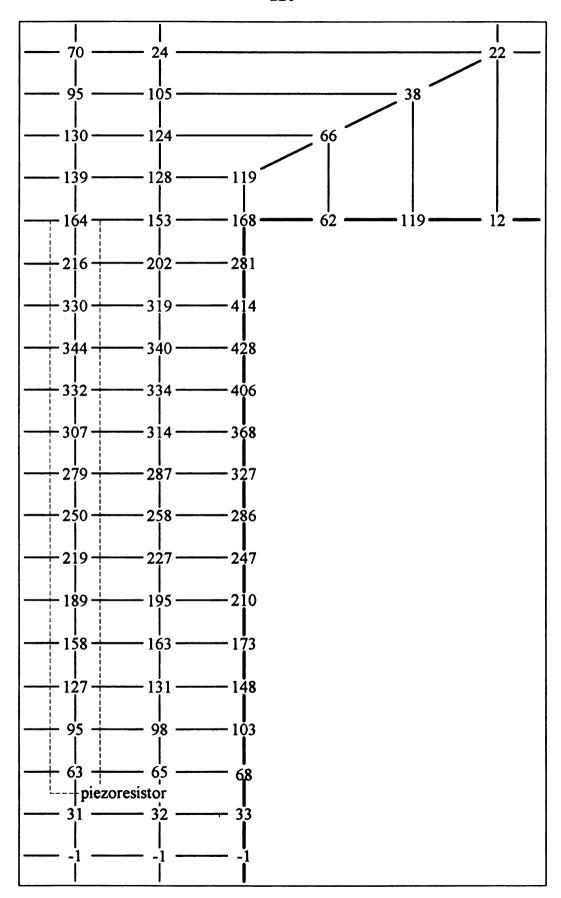

| 3.2.              | 1 Finite Element Model          | . 53 |

|                   | 3.2.1.1 Element type            | . 54 |

|                   | 3.2.1.2 Material properties     | . 54 |

|                   | 3.2.1.3 Element size            | . 56 |

| 3.2.              | 2 Static Analysis               | . 59 |

| 3.2.              | 3 Eigenvalue Analysis           | . 62 |

| 3.2.              | 4 Frequency Analysis            | . 63 |

| 3.3 PIEZOF        | RESISTOR                        | . 66 |

| 3.3.              | 1 Transduction Methods          | . 66 |

| 3.3.              | 2 Piezoresistance               | . 67 |

| 3.3.              | 3 Piezoresistor Type            | . 69 |

| 3.3.              | 4 Piezoresistor Bridge          | . 70 |

| 3.4 Perfo         | RMANCE CHARACTERISTICS          | . 70 |

| 3.4.              | 1 Resistor Dimensional Effects  | . 75 |

| 3.4               | 2 Resistor Temperature Effects  | 79   |

3.4

3 4

35 DEVICE

3 5

3.5.2

3 5 3

36 Electe

361

362

363

CHAPTER 4 OVER

41 SEECT

42 BANG SE

421

422

423

424

43 TRANNOT 44 DECIMAN

44.1

442

| 3.4.3 Beam Thickness Effects                                  | 81         |

|---------------------------------------------------------------|------------|

| 3.4.4 Nonlinearity, Hysteresis and Repeatability              | 83         |

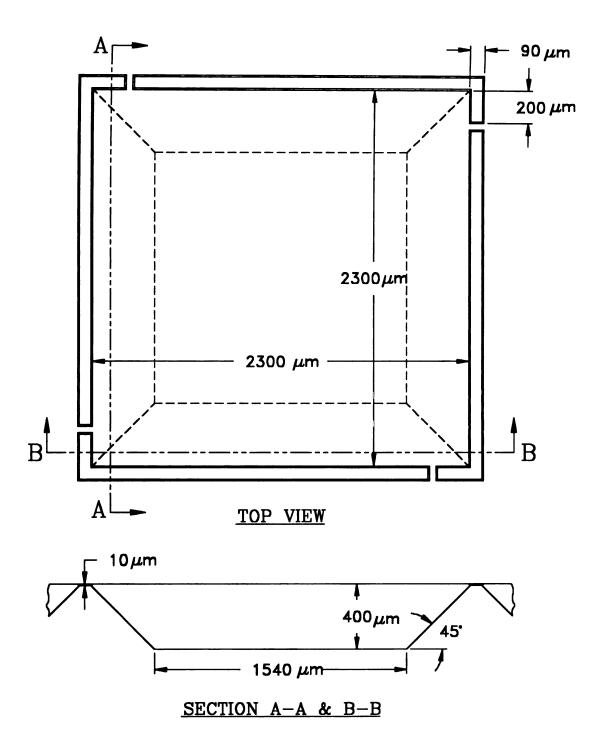

| 3.5 DEVICE CONSTRUCTION                                       | 85         |

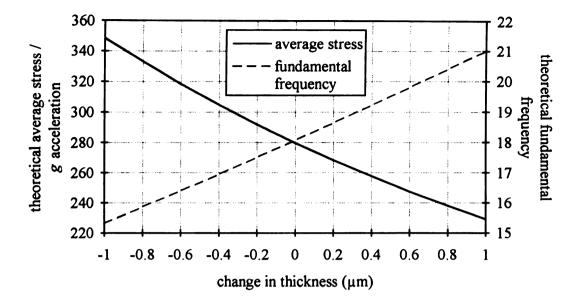

| 3.5.1 Beam Micromachining                                     | 85         |

| 3.5.2 Process Compatibilities                                 | 87         |

| 3.5.3 Packaging Benefits                                      | 88         |

| 3.6 ELECTRONIC CONSIDERATIONS                                 | 89         |

| 3.6.1 Temperature Compensation                                | <b>8</b> 9 |

| 3.6.2 Noise Effects                                           | 94         |

| 3.6.3 Amplification and Offset Reduction                      | 97         |

| CHAPTER 4 OVERSAMPLING A/D CONVERTER                          | 100        |

| 4.1 SELECTION OF A/D CONVERTER TYPE                           | 101        |

| 4.2 BASIC SDM CONVERTER OPERATION                             | 102        |

| 4.2.1 Single-loop SDM                                         | 104        |

| 4.2.2 Double-loop SDM                                         | 106        |

| 4.2.3 Decimator                                               | 108        |

| 4.2.4 Regions of Operation                                    | 109        |

| 4.3 TRANSDUCER SIGNAL AMPLIFICATION AND OSR CALCULATION       | 112        |

| 4.4 DECIMATOR DESIGN                                          | 117        |

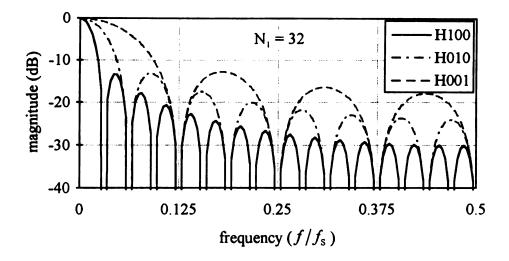

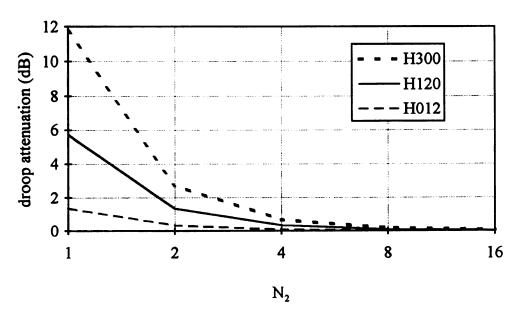

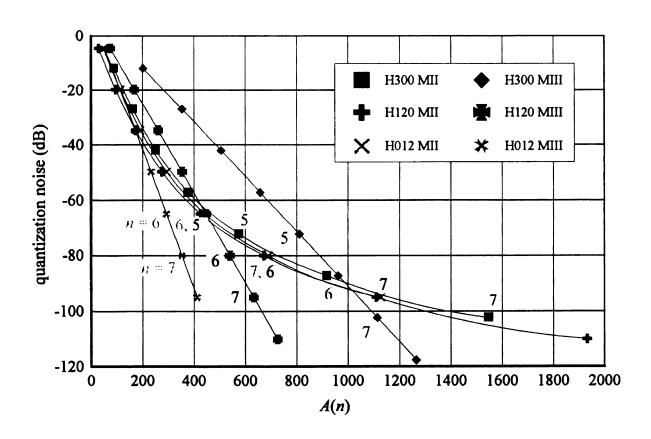

| 4.4.1 Sinc <sup>3</sup> Filter Classification and Performance | 118        |

| 4.4.1.1 In-band noise                                         | 121        |

| 4.4.1.2 Antialiasing                                          | 124        |

| 4.4.1.3 Droop                                                 | 124        |

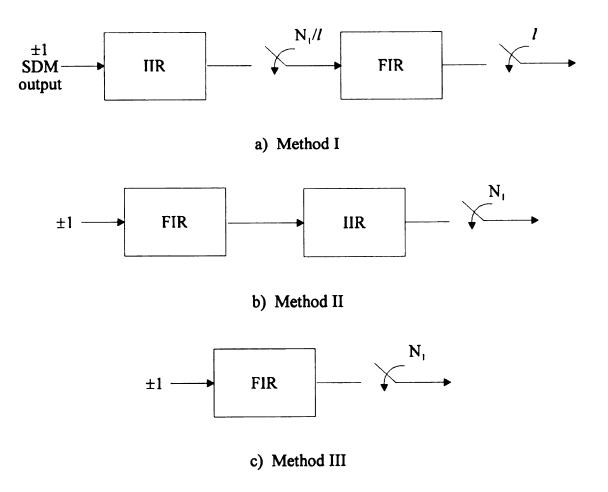

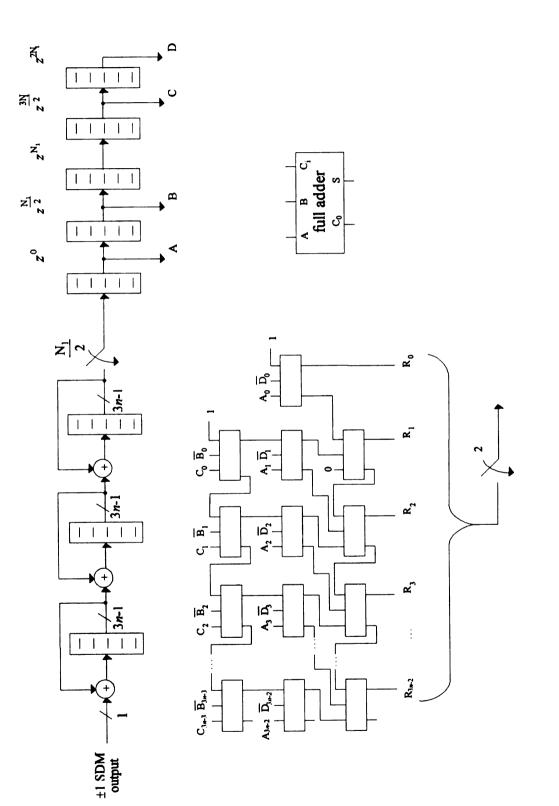

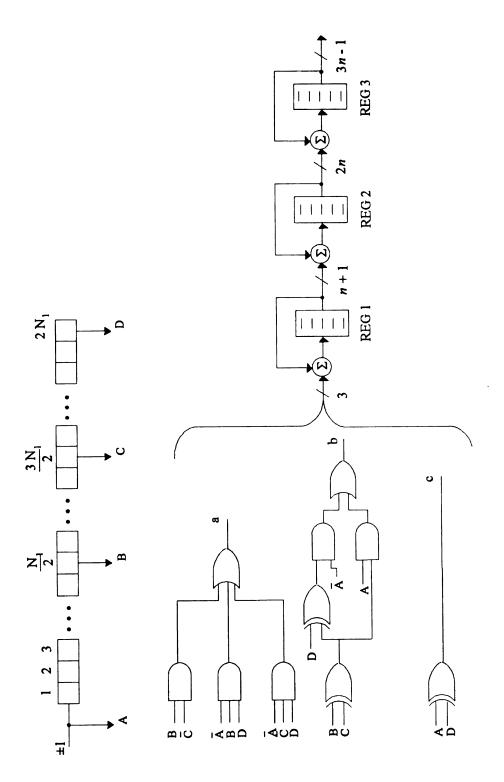

| 4.4.2 Sinc <sup>3</sup> Filter Architecture                   | 127        |

| 4.4.2.1 Method I architecture                                 | 129        |

| 4.4.2.2 Method II architecture                                | 131        |

| 4.4.2.3 Method III architecture                               | 135        |

451

452

453 454

CHAPTER 5 FEAT

51 Distract 9

52 DECIMAL

S3 ANTALIS

54 IIR FILTS

5.5 MS CALC

56 CONTROL

5.7 SIMPLATE

CHAPTER 6 SYSTE

61 SW. ZA

62 SIMPLAT

CHAPTER 7 CONT

7.1 CONTREE

7.111

7.12 H

71.3

7.14 F

71.5 [

72 FRITTER H

| 4.4.2.3.1 H120 coefficients                             | 137 |

|---------------------------------------------------------|-----|

| 4.4.2.3.2 H120 second coefficient generator             | 139 |

| 4.4.3 Filter Type and Architecture Selection            | 144 |

| 4.5 ADDITIONAL ADC SYSTEM ISSUES                        | 148 |

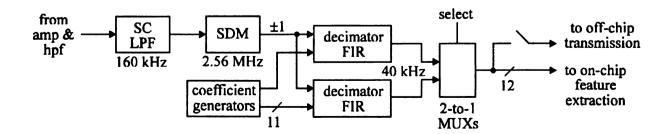

| 4.5.1 ADC System Review                                 | 148 |

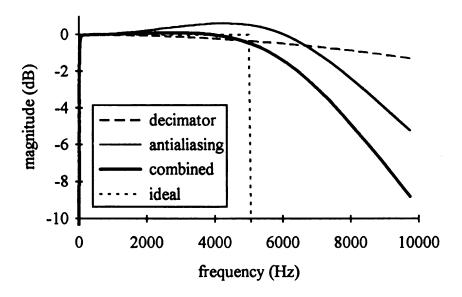

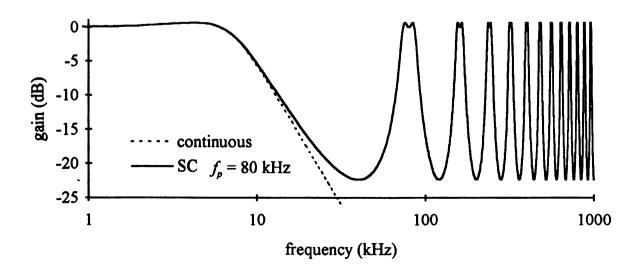

| 4.5.2 Antialiasing filter                               | 149 |

| 4.5.3 Sigma-Delta Modulator                             | 153 |

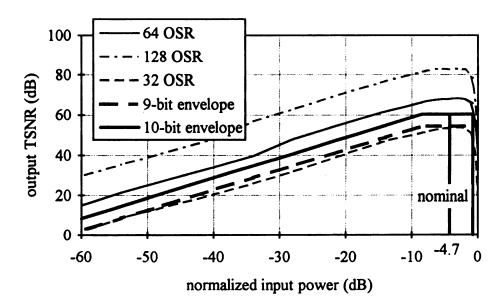

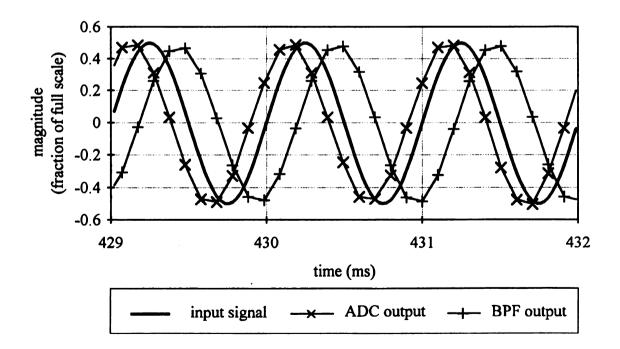

| 4.5.4 System Simulation Results                         | 154 |

| CHAPTER 5 FEATURE EXTRACTION AND DECISION LOGIC         | 157 |

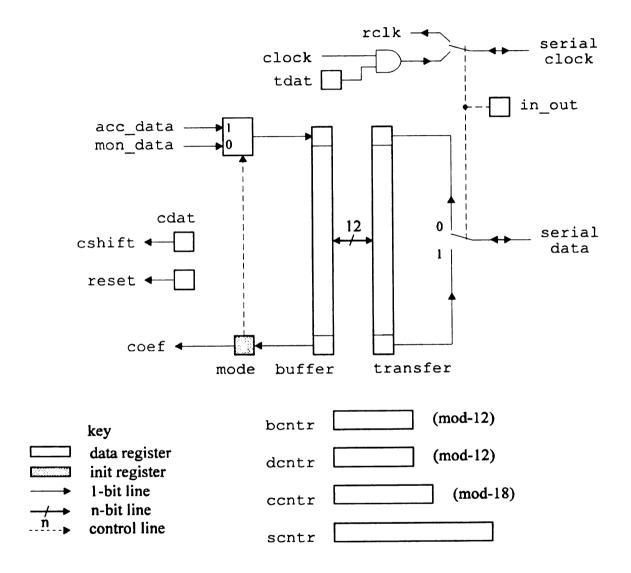

| 5.1 DIGITAL SYSTEM OVERVIEW                             | 157 |

| 5.2 DECIMATOR TIMING AND CONTROL                        | 161 |

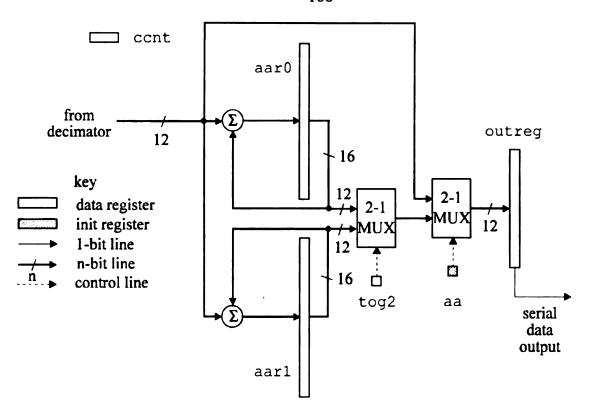

| 5.3 Antialiasing Filter                                 | 163 |

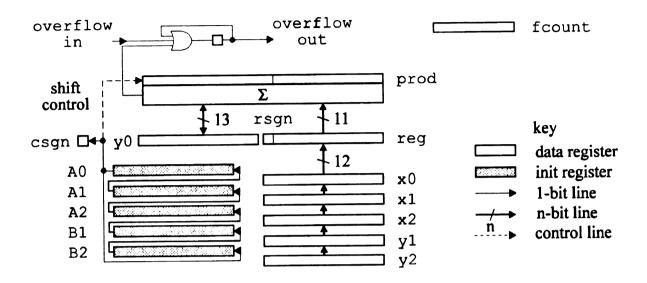

| 5.4. IIR FILTER                                         | 170 |

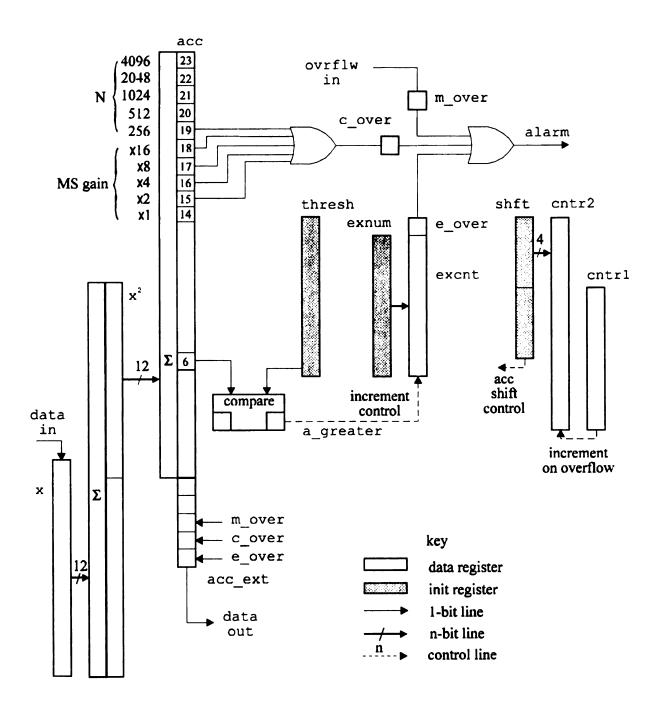

| 5.5 MS CALCULATION AND THRESHOLDING                     | 174 |

| 5.6 CONTROL UNIT                                        | 180 |

| 5.7 SIMULATION                                          | 183 |

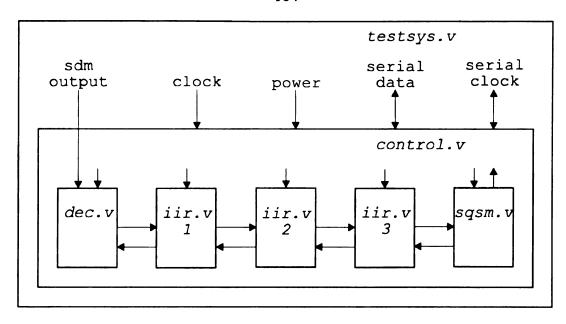

| CHAPTER 6 SYSTEM SIMULATION                             | 187 |

| 6.1 SIMULATOR COMPONENTS                                | 187 |

| 6.2 SIMULATION RESULTS                                  | 189 |

| CHAPTER 7 CONTRIBUTIONS AND FURTHER RESEARCH            | 197 |

| 7.1 CONTRIBUTIONS                                       | 197 |

| 7.1.1 Intelligent Microsensors and Machinery Monitoring | 198 |

| 7.1.2 Bearing Simulator and Simulation Results          | 199 |

| 7.1.3 Microaccelerometer                                | 200 |

| 7.1.4 First-Stage Decimation Filter                     | 202 |

| 7.1.5 Differing Monitoring and Diagnostic Precisions    | 203 |

| 7.2 FURTHER RESEARCH                                    | 203 |

APPENDIX A BE

APPENDIX B

BI STSPEN

B2 ISCR

B3 RAYLEI

B4 MATER

B.5 STRIKE

. . .

B6 P37.4

B7 BEAMT

APPENDIX C

C1 DECIMA

C2 USE 4 F

C3 472(90)

C4 SATICE

C.5 W(35.5)

Ce Zoze b

C7 TSNR

APPENDIX D DIC

BBLIOGRAPHY.

| APPENDIX A BEARING MODEL PARAMETERS            | 206 |

|------------------------------------------------|-----|

| APPENDIX B                                     | 208 |

| B.1 SUSPENDED MASS                             | 208 |

| B.2 ISOTROPIC BEAM THEORY                      | 209 |

| B.3 RAYLEIGH'S PRINCIPLE FUNDAMENTAL FREQUENCY | 213 |

| B.4 MATERIAL COEFFICIENTS                      | 215 |

| B.5 STRESS AVERAGE                             | 218 |

| B.6 PIEZORESISTANCE COEFFICIENTS               | 222 |

| B.7 BEAM THICKNESS VARIATIONS                  | 222 |

| APPENDIX C                                     | 224 |

| C.1 DECIMATOR FILTER REGISTER WIDTHS           | 224 |

| C.2 USE OF RIPPLE-CARRY ADDERS                 | 230 |

| C.3 Antialiasing Filter Characteristics        | 232 |

| C.4 SWITCHED CAPACITOR FILTER                  | 234 |

| C.5 Worst-Case Antialiasing                    | 239 |

| C.6 Noise Power                                | 240 |

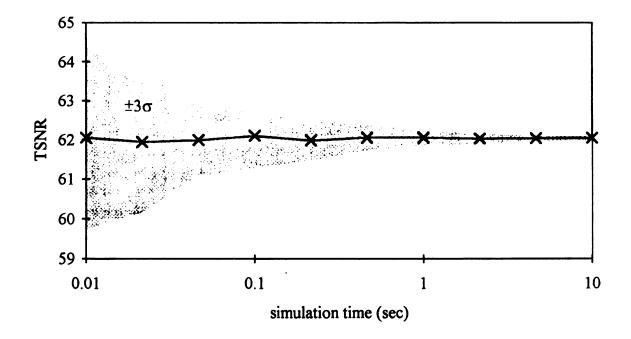

| C.7 TSNR SIMULATION                            | 241 |

| APPENDIX D DIGITAL BUTTERWORTH FILTERS         | 247 |

| BIBLIOGRAPHY                                   | 253 |

Table 1 Vibration s

Table 2 Actual vs : Table 3 Actual Win

Table 4 Natural fre

Table 5 Piezoresist...

Table 6 Offset sour

Table 7. Input signa

Table 8 Hardware: Table 9 Method II I

Table 10 Method II

Table II Method II

Table 12 Method III

Table 13 Hardware:

Table 14. Relative ar-

Table 15 SC filter c!

Table 16. Programma

Table 17 Decimator

Table 18 Antialiasing

Tible 19 Antialiasing

Table 20 IIR filter ties

Table 21. First multip

## **LIST OF TABLES**

| Table 1. Vibration signal ranges for different bearings            | 21  |

|--------------------------------------------------------------------|-----|

| Table 2. Actual vs. model bearing damage indexes for no defect.    | 34  |

| Table 3. Actual vs. model bearing damage indexes for an OR defect. | 36  |

| Table 4. Natural frequencies and modal masses                      | 63  |

| Table 5. Piezoresistance coefficients [49].                        | 69  |

| Table 6. Offset sources.                                           | 97  |

| Table 7. Input signal deviation factors                            | 115 |

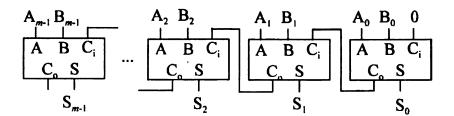

| Table 8. Hardware for Method I implementation                      | 132 |

| Table 9. Method II H <sub>N</sub> 120 logic                        | 134 |

| Table 10. Method II accumulator sizes.                             | 134 |

| Table 11. Method II hardware implementation.                       | 135 |

| Table 12. Method III H120 coefficient generation, $N_1 = 8$        | 138 |

| Table 13. Hardware for Method III Implementation.                  | 143 |

| Table 14. Relative area figures, $A(n)$ .                          | 146 |

| Table 15. SC filter characteristics                                | 152 |

| Table 16. Programmable init register values.                       | 160 |

| Table 17. Decimator control signals.                               | 162 |

| Table 18. Antialiasing filter control signals                      | 168 |

| Table 19. Antialiasing FIR coefficients.                           | 169 |

| Table 20. IIR filter timing.                                       | 171 |

| Table 21. First multiply/accumulate operation timing.              | 172 |

Table 22 Accumula

Table 23 MS and th

Table 24 Effects of

Table 25 Effects of

Table 26 Maximum

Table 27 Bearing ge

Table 28 Bearing h.

Table 29 Bearing h.

Table 30 Bearing co

Table 31 Data gene

Table 32 NISA mat

Table 33 P-type Tag

Table 34 Method I r

Table 35 Method II

Table 36 Band-pass

| Table 22. | Accumulation cycle timing.                                                     | 176 |

|-----------|--------------------------------------------------------------------------------|-----|

| Table 23. | MS and threshold timing.                                                       | 176 |

| Table 24. | Effects of shft[7:4]                                                           | 178 |

| Table 25. | Effects of shft[3:0]                                                           | 178 |

| Table 26. | Maximum average MS values for band-pass filter                                 | 193 |

| Table 27. | Bearing geometry parameters.                                                   | 206 |

| Table 28. | Bearing housing resonance parameters.                                          | 206 |

| Table 29. | Bearing housing high-pass parameters.                                          | 207 |

| Table 30. | Bearing contact noise parameters.                                              | 207 |

| Table 31. | Data generation parameters                                                     | 207 |

| Table 32. | NISA material coefficients                                                     | 219 |

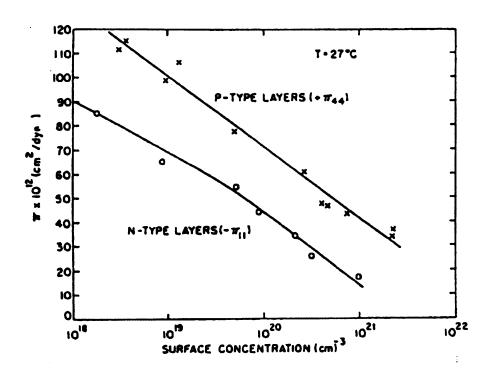

| Table 33. | <i>P</i> -type $\pi_{44}$ vs. temperature for $9 \times 10^{18}$ concentration | 224 |

| Table 34. | Method I register widths.                                                      | 229 |

| Table 35. | Method II register widths.                                                     | 230 |

| Table 36. | Band-pass filter coefficients                                                  | 250 |

Figure 2 Intelligent Figure 3 Bearing vib Figure 4 Bearing life Figure 5 Average be Figure 6 Bearing vii Figure 7 NSK NT Figure 8 Actual [27] Figure 9 Actual [27] Figure 10 Defect incl Figure 11 Compariso Figure 12 Quantizati Figure 13 Quantizati Figure 14 Mass-sprin Figure 15. Overall tra Figure 16. Beam geor Figure 17 Loaded be Figure 18. Test beam Figure 19 Element siz Figure 20. Beam top a Figure 21. First six ac

Figure 22 Longitudir

Figure 1. The monity

## LIST OF FIGURES

| Figure 1. The monitoring hierarchy [1].                                     | 2  |

|-----------------------------------------------------------------------------|----|

| Figure 2. Intelligent monitoring system.                                    | 4  |

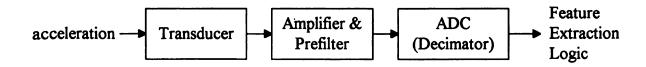

| Figure 3. Bearing vibration monitor.                                        | 7  |

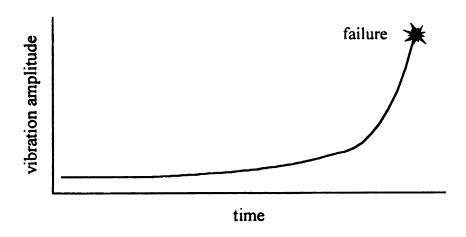

| Figure 4. Bearing lifetime wear rate [13]                                   | 14 |

| Figure 5. Average bearing vibration level vs. time [10]                     | 16 |

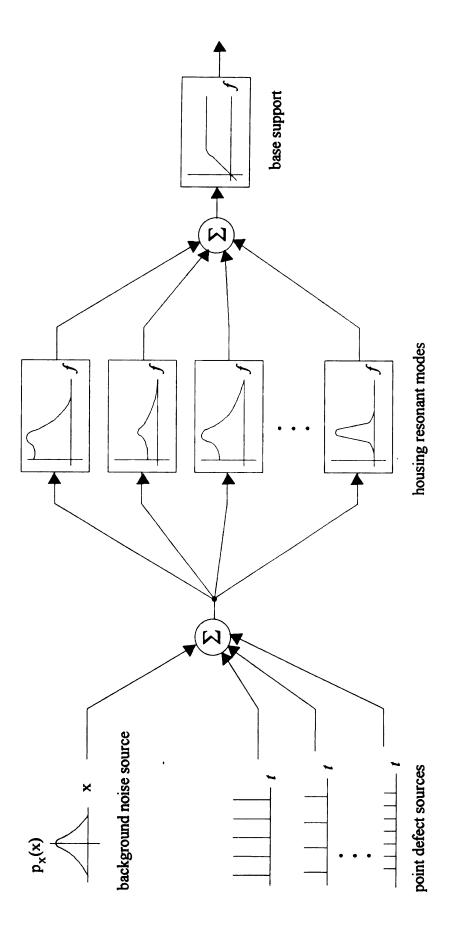

| Figure 6. Bearing vibration model                                           | 28 |

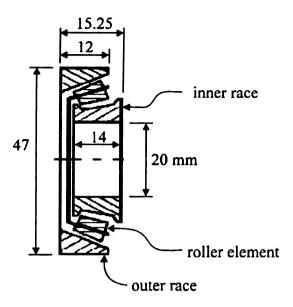

| Figure 7. NSK / NTN 30204 bearing section [27].                             | 32 |

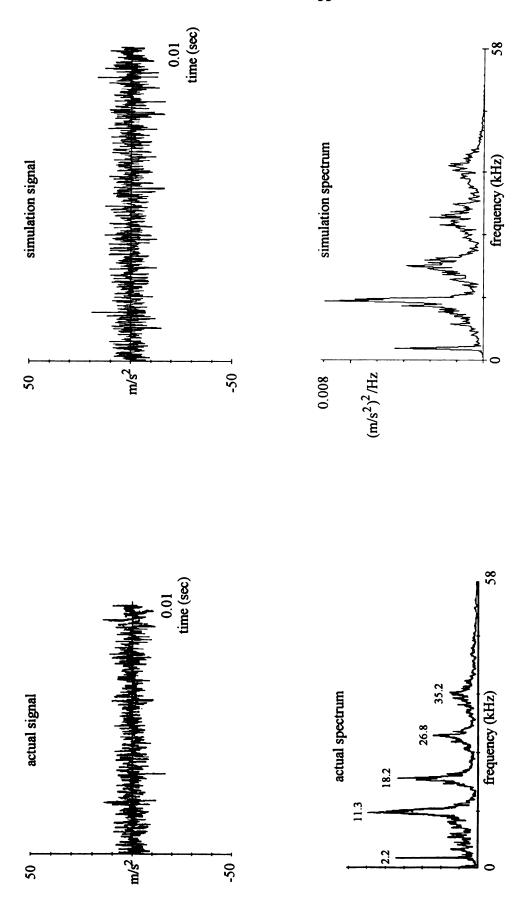

| Figure 8. Actual [27] and simulated zero-defect bearing signals and spectra | 32 |

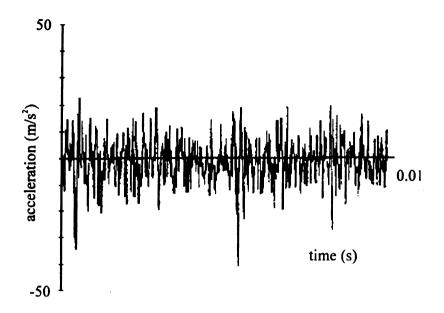

| Figure 9. Actual [27] and model defective bearing signals.                  | 35 |

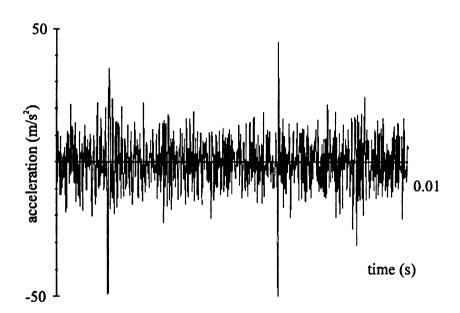

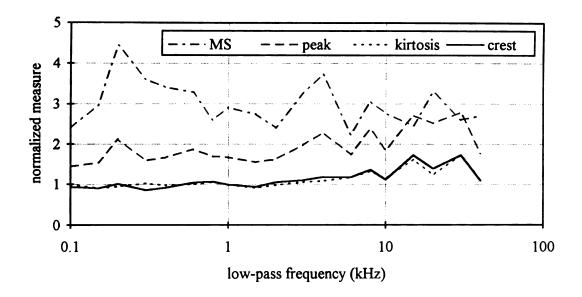

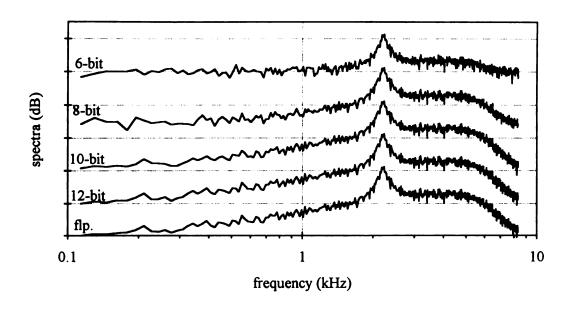

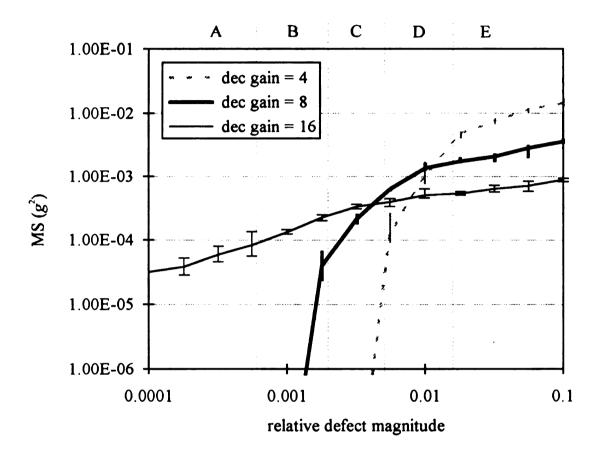

| Figure 10. Defect indexes vs. frequency.                                    | 37 |

| Figure 11. Comparison of normalized defect indexes                          | 39 |

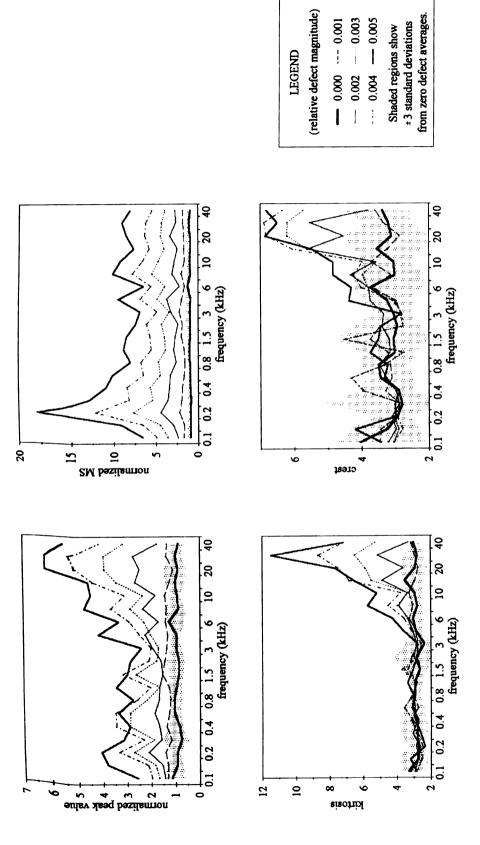

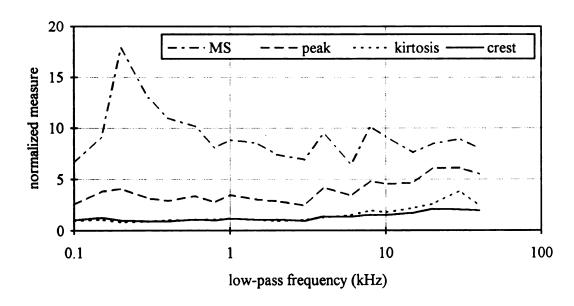

| Figure 12. Quantization effects on MS.                                      | 41 |

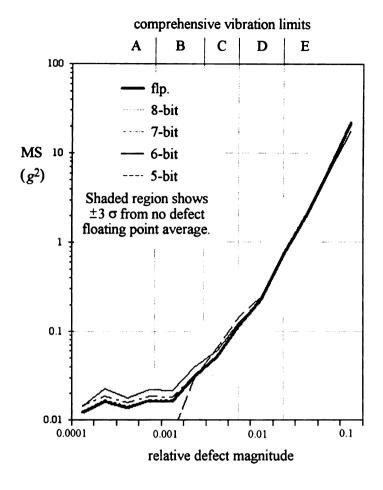

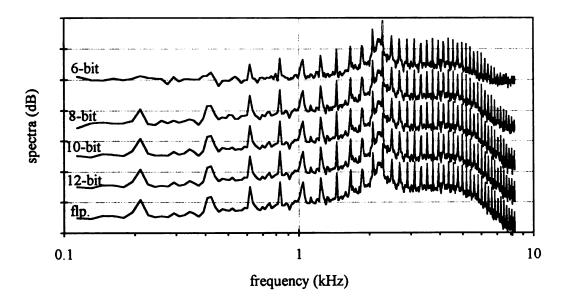

| Figure 13. Quantization effects on spectrum.                                | 43 |

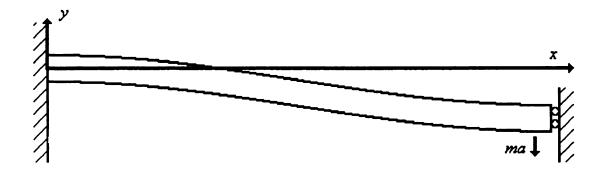

| Figure 14. Mass-spring-damper system [35]                                   | 45 |

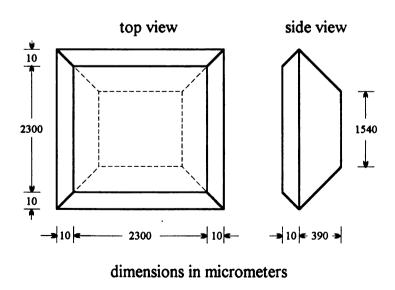

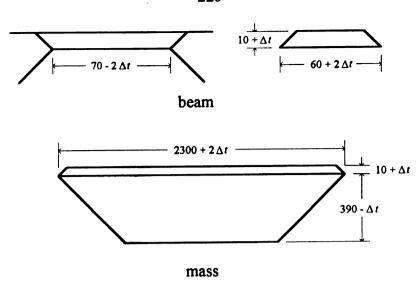

| Figure 15. Overall transducer geometry.                                     | 48 |

| Figure 16. Beam geometry                                                    | 49 |

| Figure 17. Loaded beam in the four-beam accelerometer                       | 50 |

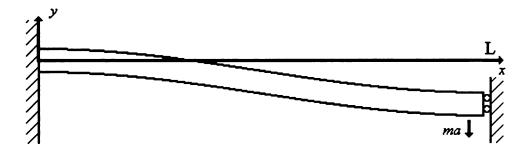

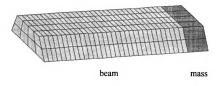

| Figure 18. Test beam.                                                       | 57 |

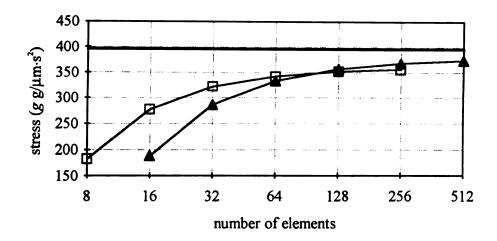

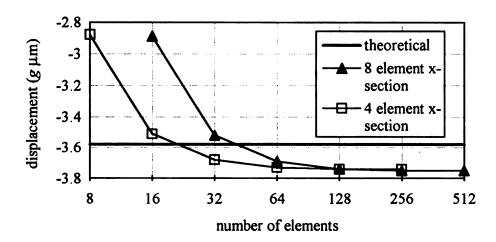

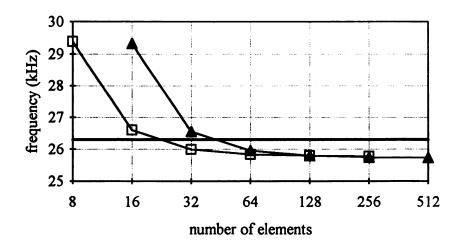

| Figure 19. Element size effects                                             | 58 |

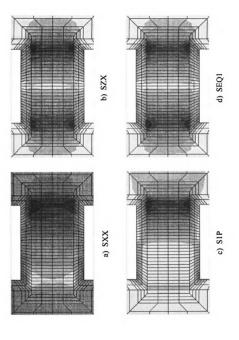

| Figure 20. Beam top stress distributions                                    | 60 |

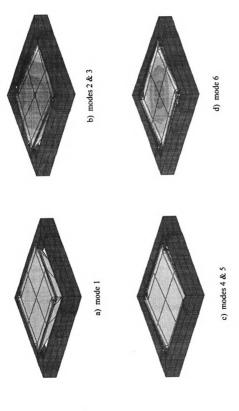

| Figure 21. First six accelerometer modes.                                   | 64 |

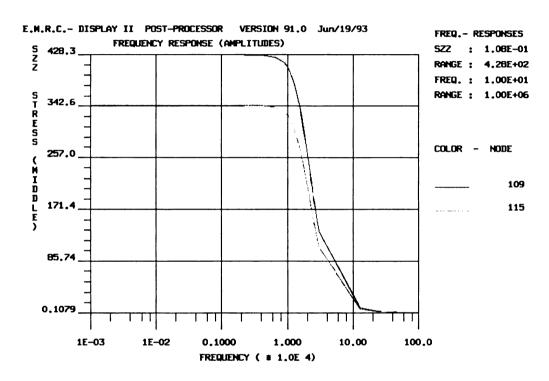

| Figure 22 Longitudinal stress frequency response                            | 65 |

Figure 23 Piezoresi Figure 24 Piezoresi Figure 25 Bridge ou Figure 26 Bridge ou Figure 27. Dimensio Egure 28 nu vs. ter Figure 29 Temperat Figure 30. Temperat Figure 31 Beam th. Figure 32 Etch-stop Figure 33 Accelera-Figure 34 Temperat Figure 35 Temperat Figure 36 Approxim Figure 37 Offset red Figure 38. Tradition. Figure 39. Single-loc Figure 40 Conversion Figure 4] Effect of ( Figure 42 Double-le Figure 43 Conversion Figure 44 Conceptua Figure 45. OSR effect Figure 46 Signal gain Figure 47 OSR and g Figure 48 Standard St Egute 49 H100, H01

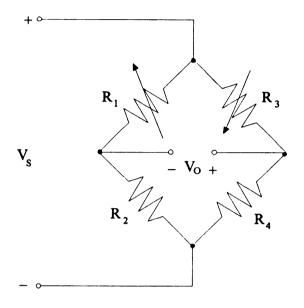

| Figure 23. | Piezoresistor bridge.                                      | 71  |

|------------|------------------------------------------------------------|-----|

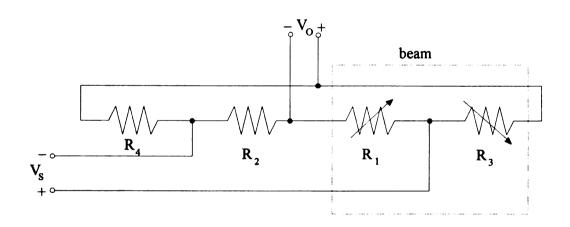

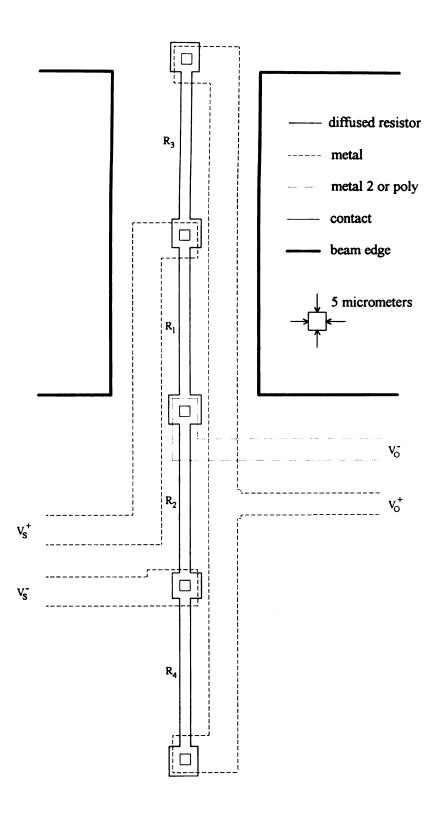

| Figure 24. | Piezoresistor placement.                                   | 72  |

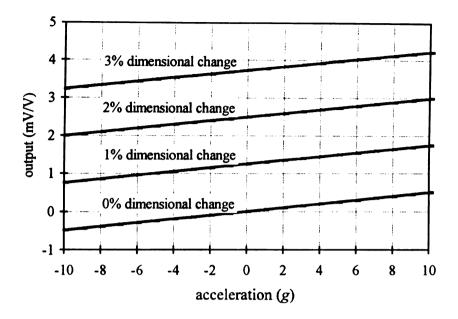

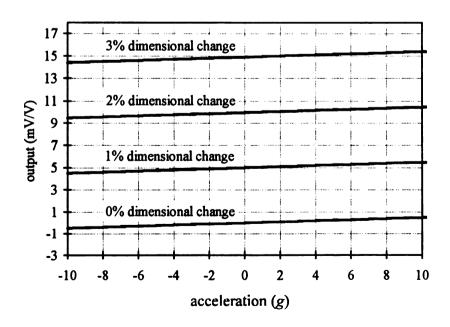

| Figure 25. | Bridge output for dimensional changes in R <sub>1</sub>    | 76  |

| Figure 26. | Bridge output for dimensional changes in all resistors     | 76  |

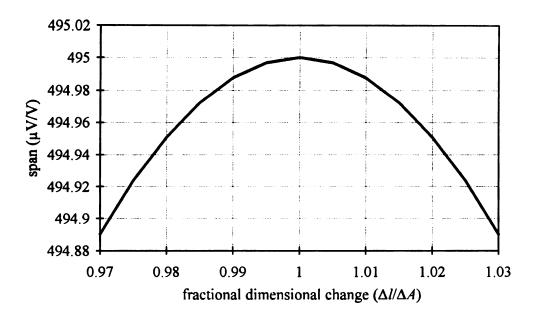

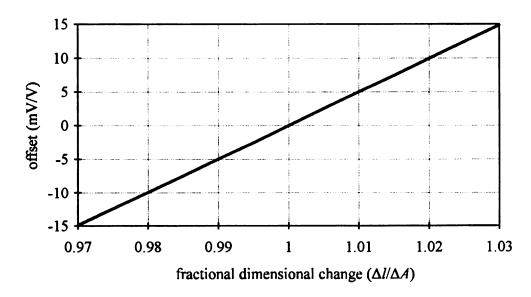

| Figure 27. | Dimensional effects on the span and offset.                | 78  |

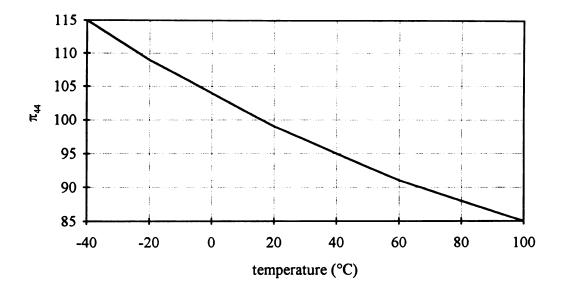

| Figure 28. | $\pi_{44}$ vs. temperature                                 | 80  |

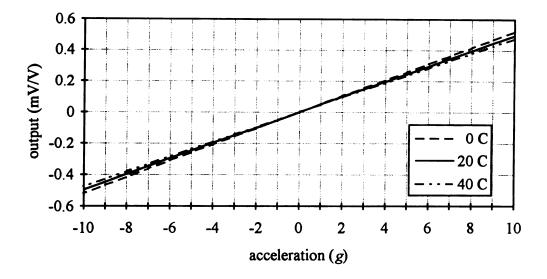

| Figure 29. | Temperature effects on the bridge output                   | 81  |

| Figure 30. | Temperature effects on the span.                           | 82  |

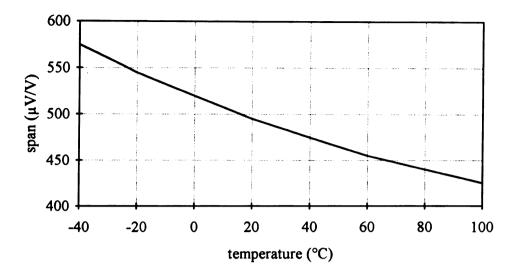

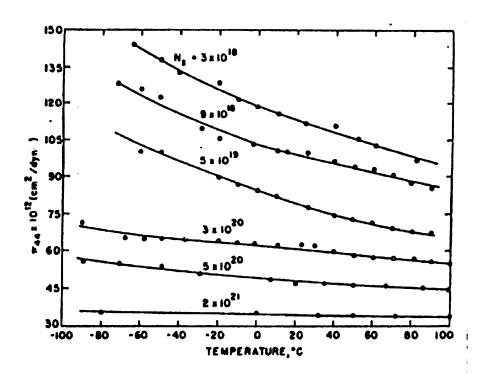

| Figure 31. | Beam thickness effects on stress and fundamental frequency | 83  |

| Figure 32. | Etch-stop apparatus [60]                                   | 86  |

| Figure 33. | Accelerometer package cross-section [55].                  | 88  |

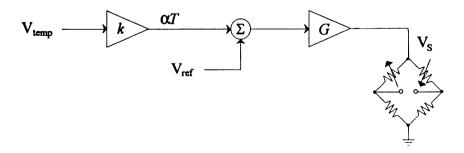

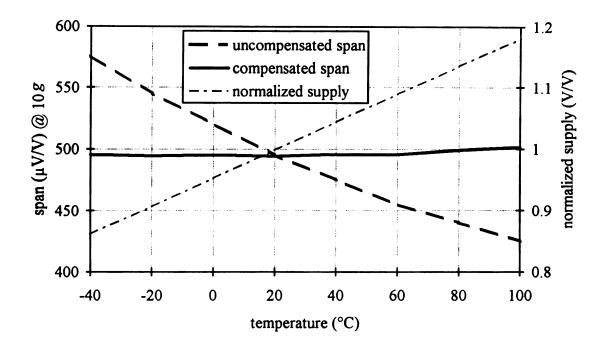

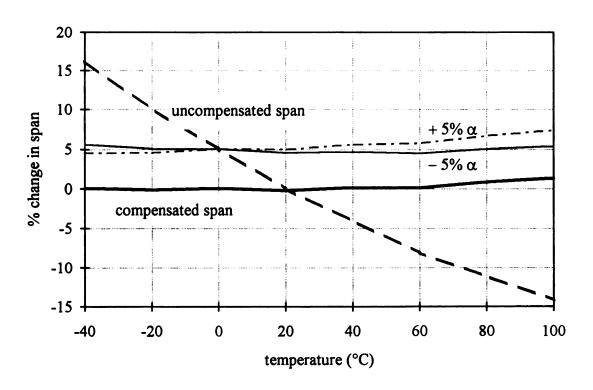

| Figure 34. | Temperature compensating bridge supply                     | 91  |

| Figure 35. | Temperature compensation of the span.                      | 93  |

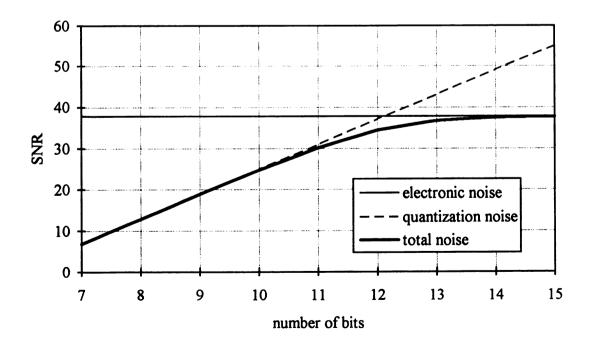

| Figure 36. | Approximate system noise effects                           | 96  |

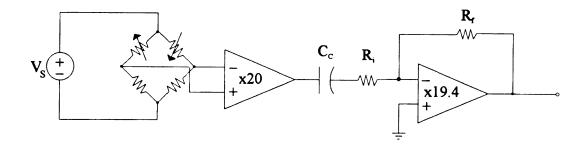

| Figure 37. | Offset reduction and amplification.                        | 99  |

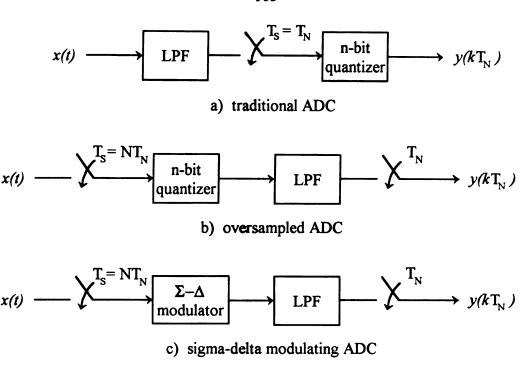

| Figure 38. | Traditional and oversampling ADC models.                   | 103 |

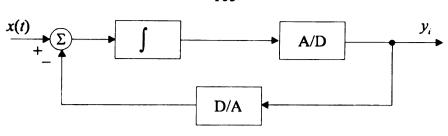

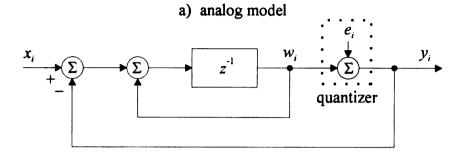

| Figure 39. | Single-loop SDM.                                           | 105 |

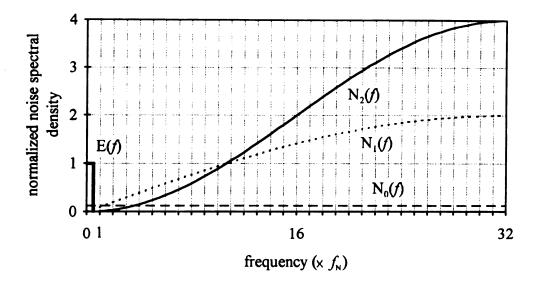

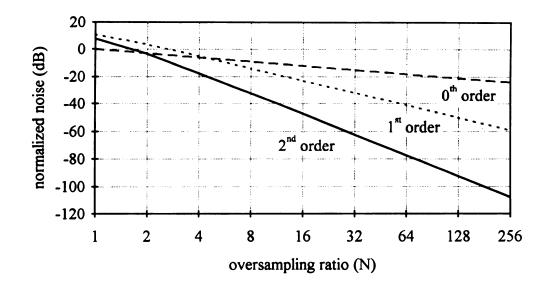

| Figure 40. | Conversion noise spectral density.                         | 106 |

| Figure 41. | Effect of OSR on quantization noise.                       | 107 |

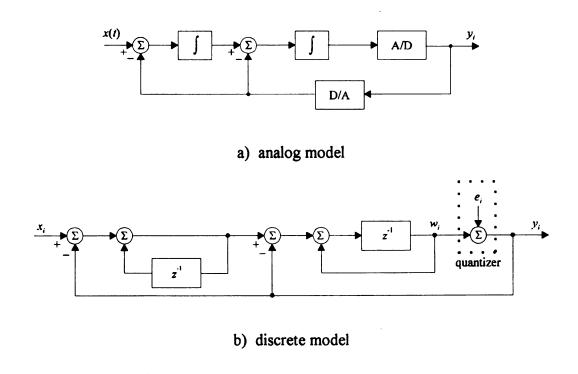

| Figure 42. | Double-loop SDM.                                           | 107 |

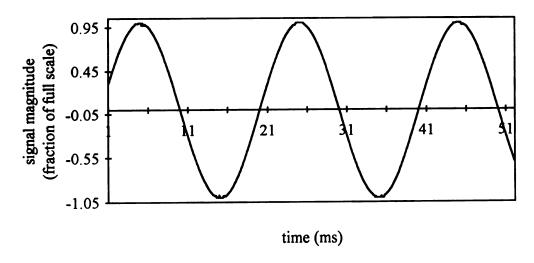

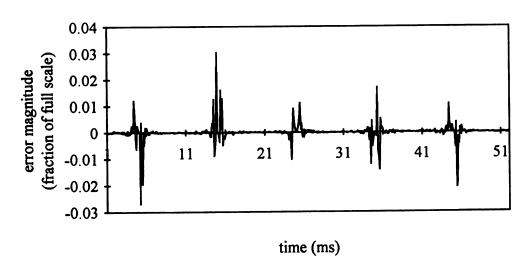

| Figure 43. | Conversion of a rail-to-rail sinusoid.                     | 110 |

| Figure 44. | Conceptualized TSNR vs. input power                        | 112 |

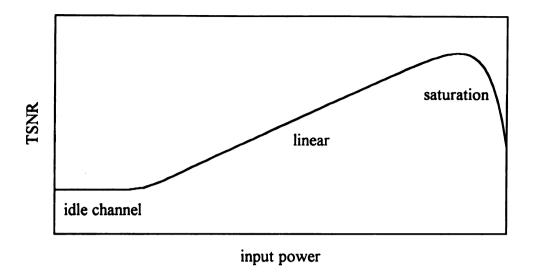

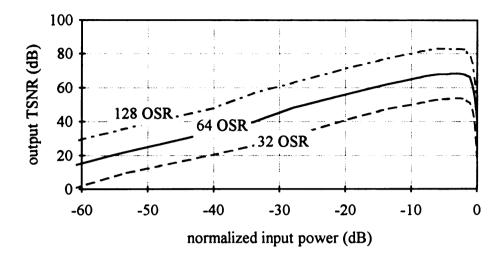

| Figure 45. | OSR effects on TSNR                                        | 114 |

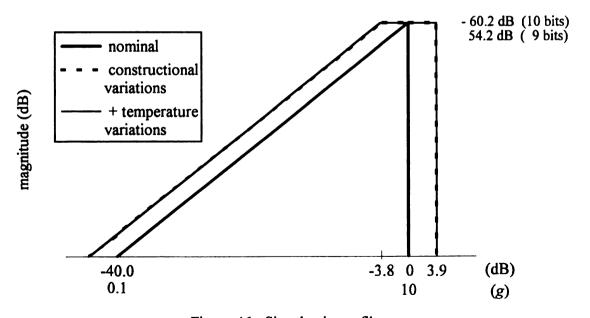

| Figure 46. | Signal gain profile.                                       | 114 |

| Figure 47. | OSR and gain determination.                                | 116 |

| Figure 48. | Standard second-order SDM ADC                              | 118 |

| Figure 49. | H100, H010 and H001 spectra                                | 120 |

- Figure 58 Method II Figure 68 TSNR vs Figure 69 TSNR 1/3 Figure 70 Digital log Figure 73 Frequency Figure 74 Spectral fi

- Figure 50 Six High

- Figure 51 In-band r

- Figure 52 Worst-ca

- Figure 53 Worst-ca

- Figure 54 Worst-ca

- Figure 55 High archi

- Figure 56 Method I

- Figure 57 Method II

- Figure 59 Dual coef

- Flatte 60 Coefficier

- Figure 61 Improved

- Figure 62 A(n) vs c

- Figure 63 ADC 55.50

- Figure 64 Antialias...

- Figure 65 Continuo

- Figure 66 Sampling

- Figure 67 Simulated

- Figure 71 Decimator

- Figure 72 Decimator

- Figure 75 Antialiasin

- Fere of IIR filter b

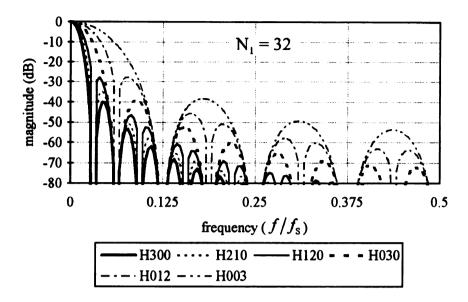

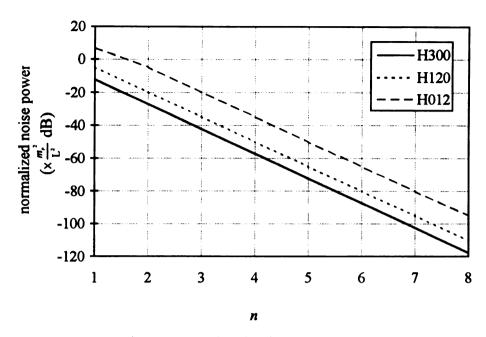

| Figure 50. | Six Hijk spectra                                          | . 121 |

|------------|-----------------------------------------------------------|-------|

| Figure 51. | In-band noise power vs. n.                                | . 123 |

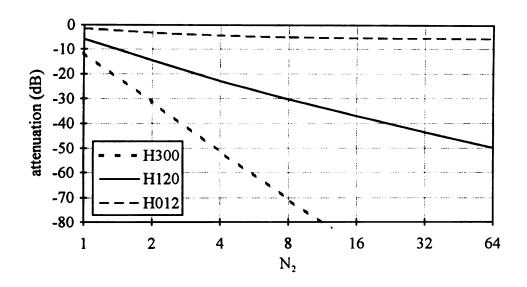

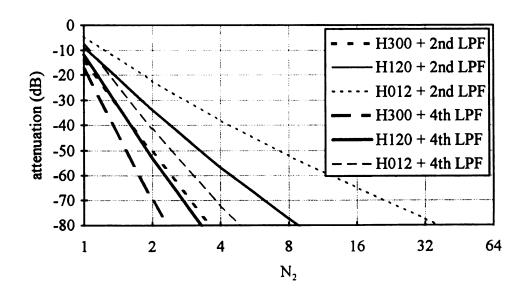

| Figure 52. | Worst-cast antialiasing                                   | 125   |

| Figure 53. | Worst-case aliasing with low-pass filters.                | 125   |

| Figure 54. | Worst-case droop, N <sub>1</sub> = 64.                    | 126   |

| Figure 55. | Hijk architectures.                                       | 128   |

| Figure 56. | Method I H120 architecture.                               | 123   |

| Figure 57. | Method II H120 architecture                               | 131   |

| Figure 58. | Method III H120 architecture                              | 139   |

| Figure 59. | Dual coefficients vs. time.                               | 140   |

| Figure 60. | Coefficient generator 1 circuit                           | 141   |

| Figure 61. | Improved coefficient generator 1 circuit                  | 142   |

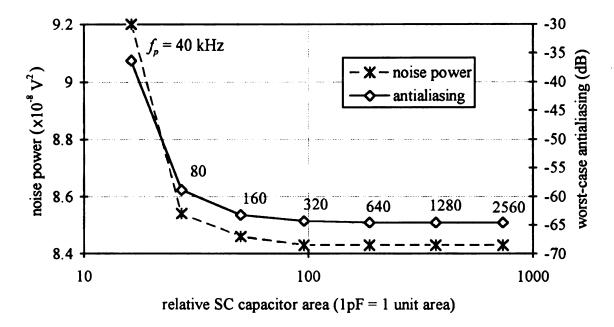

| _          | A(n) vs. quantization noise power.                        |       |

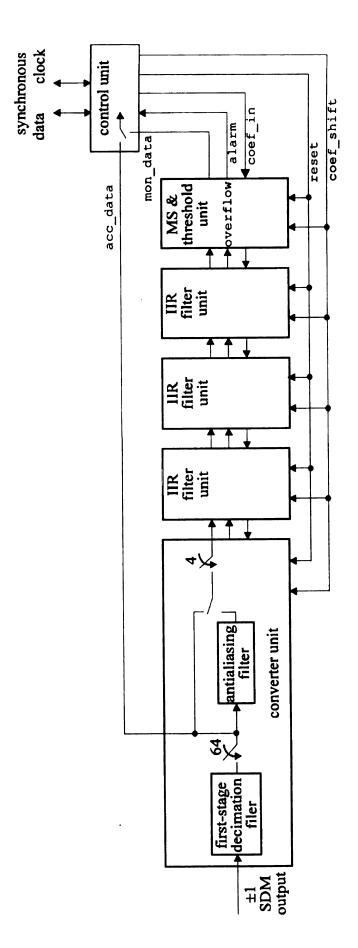

| Figure 63. | ADC system block diagram.                                 | 148   |

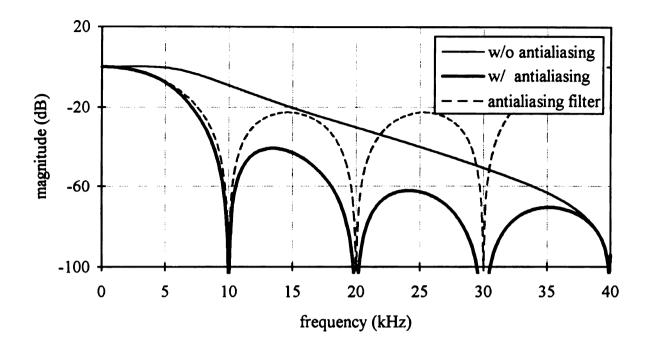

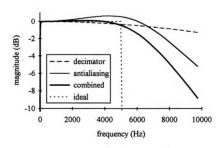

| Figure 64. | Antialiasing filter spectrum.                             | 150   |

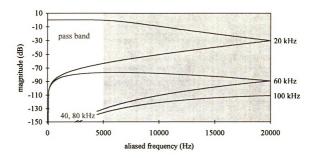

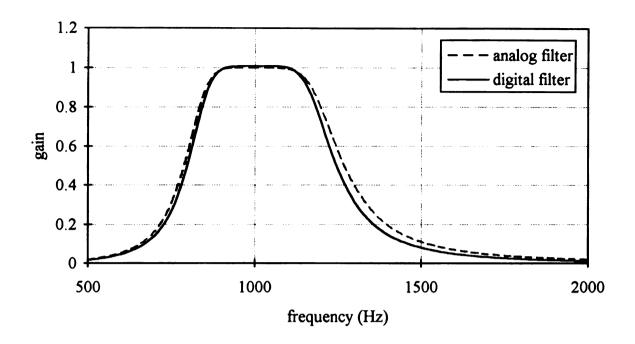

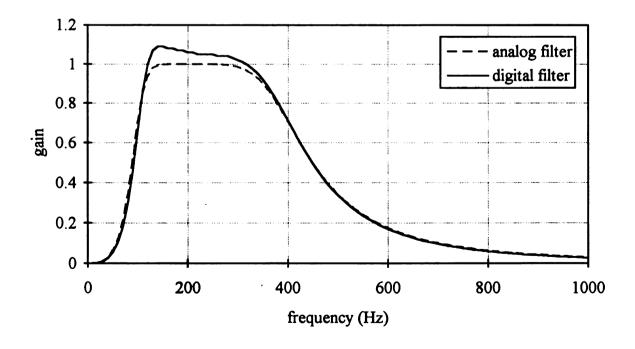

| Figure 65. | Continuous and SC filter frequency response               | 152   |

| Figure 66. | Sampling rate effects on SC filter parameters.            | 153   |

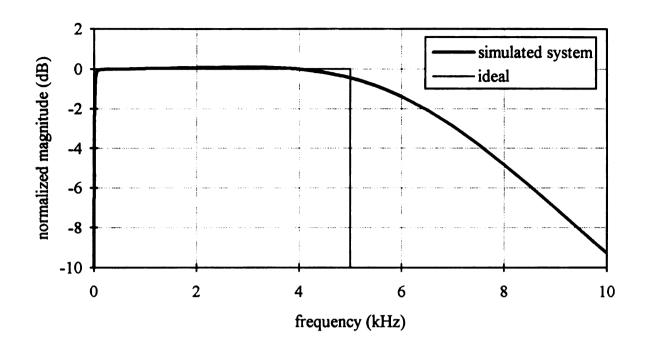

| Figure 67. | Simulated frequency response.                             | 155   |

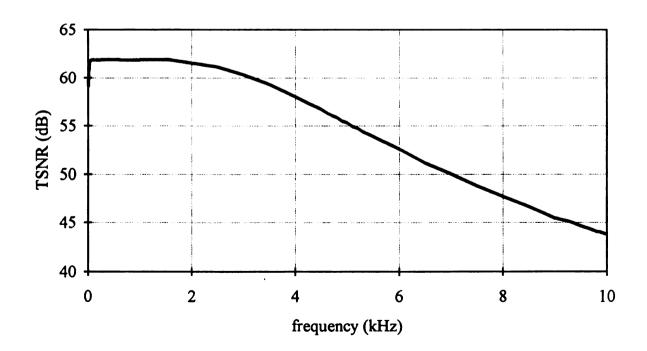

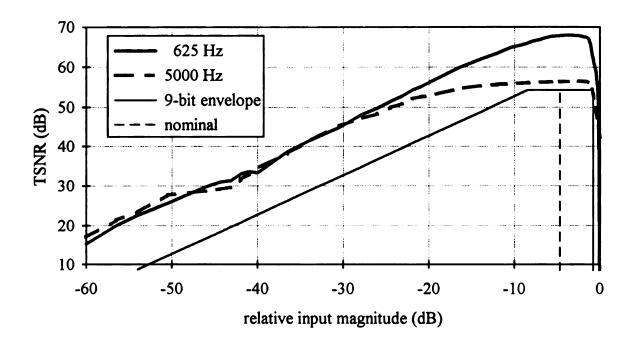

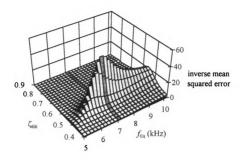

| Figure 68. | TSNR vs. frequency.                                       | 155   |

| Figure 69. | TSNR vs. input power.                                     | 156   |

| Figure 70. | Digital logic block diagram.                              | 158   |

| Figure 71. | Decimator logic diagram.                                  | 162   |

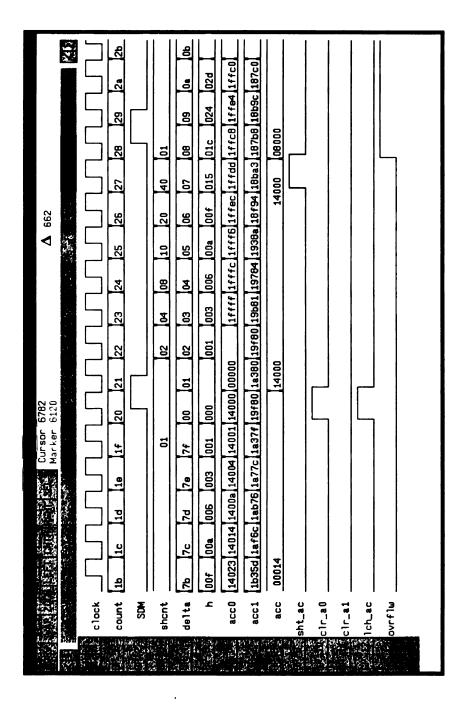

| Figure 72. | Decimator timing diagram.                                 | 164   |

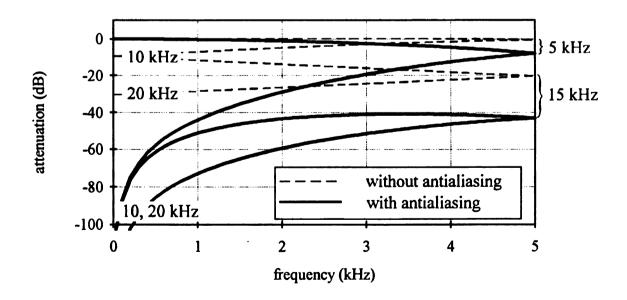

| Figure 73. | Frequency response with and without antialiasing          | 167   |

| Figure 74. | Spectral folding with and without the antialiasing filter | 167   |

| Figure 75. | Antialiasing filter logic diagram.                        | 168   |

| Figure 76. | IIR filter block diagram.                                 | 171   |

Figure 77. MS calci Figure 78 Control Figure 79 Simulatio Figure 80 Digital si Figure 81 Simulatic Figure 82 Compani Figure 83 Compani Figure 84 Range of Figure 85 Range of Figure 86 Acceleror Figure 87 Suspende. Figure 88 Clamped-Figure 89 Crystally 2 Flaire 90 Quarter No Figure 91 Piezoresis Figure 92 744 V3 tem Figure 93 Beam thick Figure 94 Sinc filter Figure 95. Register w Figure 96 Ripple-can Figure 97 Ripple-can Figure 98 System con Ferre 99 Antialiasing Face 100 System f Fare 191 Second-c Figure 102 Switched Este 193 Second-co

| Figure 77. | MS calculation and thresholding unit circuit.         | . 175 |

|------------|-------------------------------------------------------|-------|

| Figure 78. | Control unit diagram.                                 | . 181 |

| Figure 79. | Simulation model hierarchy                            | 184   |

| Figure 80. | Digital simulation output.                            | 185   |

| Figure 81. | Simulation modules.                                   | 187   |

| Figure 82. | Comparison of feature extraction parameters.          | 190   |

| Figure 83. | Comparison of computed MS for various decimator gains | 192   |

| Figure 84. | Range of MS values for band-pass filter, N = 512.     | 195   |

| Figure 85. | Range of MS values for band-pass filter, N = 2048     | 196   |

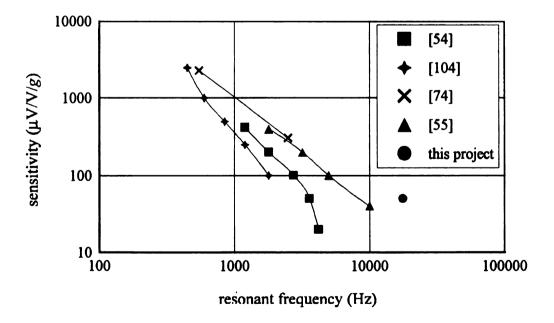

| Figure 86. | Accelerometer sensitivity vs. resonant frequency.     | 200   |

| Figure 87. | Suspended mass                                        | 208   |

| Figure 88. | Clamped-sliding beam.                                 | 210   |

| Figure 89. | Crystallographic-to-model axes transformation         | 216   |

| Figure 90. | Quarter beam longitudinal stress values.              | 221   |

| Figure 91. | Piezoresistance vs. dopant concentration [52].        | 223   |

| Figure 92. | $\pi_{44}$ vs. temperature for p-type silicon [52].   | 223   |

| Figure 93. | Beam thickness variations.                            | 225   |

| Figure 94. | Sinc filter.                                          | 227   |

| Figure 95. | Register width simulation results.                    | 230   |

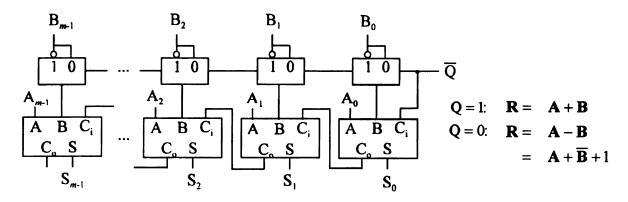

| Figure 96. | Ripple-carry adder.                                   | 232   |

| Figure 97. | Ripple-carry adder/subtractor                         | 234   |

| Figure 98. | System components that affect frequency response      | 235   |

| Figure 99. | Antialiasing filter parameter relationships.          | 237   |

| Figure 100 | System frequency response.                            | 237   |

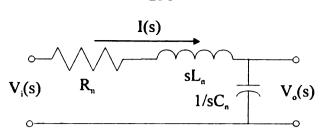

| Figure 101 | . Second-order low-pass network                       | 238   |

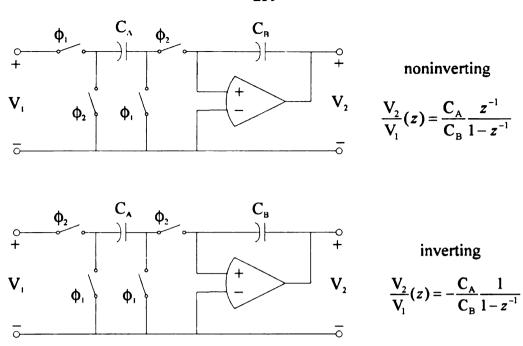

| Figure 102 | Switched capacitor integrators.                       | 239   |

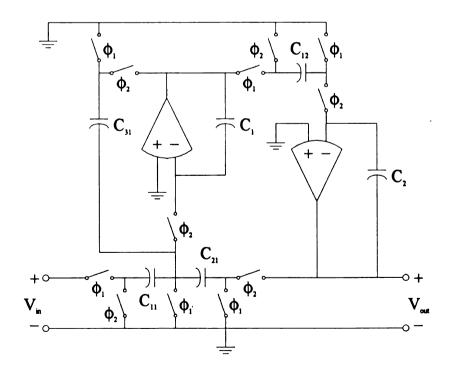

| Figure 103 | Second-order switched capacitor filter                | 239   |

Figure 104 First-s:

Figure 105 TSNR

Figure 106 Freques

Figure 107 Freque:

### xvi

| Figure 104. | First-stage spectral folding. | 242 |

|-------------|-------------------------------|-----|

| Figure 105. | TSNR vs. simulation time      | 245 |

| Figure 106. | Frequency response of BPF 1.  | 252 |

| Figure 107. | Frequency response of BPF 2.  | 252 |

The purpose merosensors to me through the design conditioning circuitry thresholding and ala-

This chapter monitoring bearings problem. Section 1.2 a system employing scope of this project. 14 lists the assumption of this difference working of this difference working the second of the second of this difference working the second of this difference working the second of the second of

# II MACHINERY M

The purpose militarce future deci-

Machinery madecisions about the or decisions range from complex issues such a state possibilities of the decisions of the decisions about the or decisions range from the complexity of the decisions about the order of the o

# CHAPTER 1 INTRODUCTION

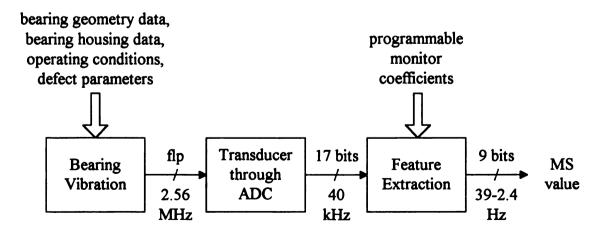

The purpose of this project is to examine the feasibility of using intelligent microsensors to monitor the health of rolling element bearings. This is accomplished through the design of a device that incorporates a microaccelerometer, analog conditioning circuitry, a novel analog-to-digital converter, and logic for feature extraction, thresholding and alarm generation, all on the same substrate.

This chapter provides introductory and supporting material for a discussion of monitoring bearings using microsensors. Section 1.1 describes the general monitoring problem. Section 1.2 defines an intelligent microsensor and discusses the configuration of a system employing these devices for machinery monitoring. Section 1.3 describes the scope of this project within the general framework provided in the first sections. Section 1.4 lists the assumptions used throughout the design process. Finally, Section 1.5 presents an overview of this dissertation.

## 1.1 MACHINERY MONITORING

The purpose of monitoring is to obtain information. This information is used to influence future decisions concerning the monitored system. The amount and type of information required from monitoring depends on the kind of decisions to be made.

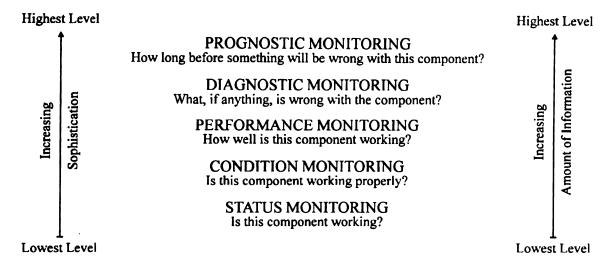

Machinery monitoring refers to the gathering of information required to make decisions about the operating conditions and relative health of mechanical systems. These decisions range from simple inquiries as to whether a device is operating or not to complex issues such as quantitative predictions about future operating parameters and failure possibilities. The precise definition of machinery monitoring, therefore, differs depending on the context. Figure 1 shows different levels of meaning based on the complexity of the decision under consideration. The figure is modified from Brawley [1].

Monitoring recondition of ball and these devices that had however, on many pconsequences due to addition to the cost of to other equipment as

Condition monitoring

Condition monitoring

Condition monitoring

Condition monitoring

Condition feature of the

Condition feature level to a the

Figure 1. The monitoring hierarchy [1].

Monitoring rolling element bearings involves gathering information about the condition of ball and roller bearings. Status monitoring checks for failed bearings, or those devices that have seized. This requires very simple data and little data reduction. However, on many pieces of machinery the sudden seizure of a bearing has catastrophic consequences due to the force created by the rapid deceleration of rolling masses. In addition to the cost of the bearing, there are the costs that may be incurred by the damage to other equipment and by the unscheduled equipment down time. This makes status monitoring a virtually useless technique for monitoring most bearings.

Condition monitoring determines if a bearing is performing at some level or within a set of specifications. Because of the monotonic nature in which damage is accumulated in a bearing, condition monitoring can be used to estimate the health of the device. Condition monitoring requires extracting a sufficient amount of information to obtain a relevant feature of the bearing, reducing the data to extract the feature, then comparing the feature level to a threshold value.

Performance monit health

Diagnostic n the bearing. This performance monite diagnosed through ; [2,3].

Prognostic in bearing or, more specim bearing life expectantacting surfaces in available.

In addition to Continuous monitor dedicated data collected meters are permeters may perform analysis. A compresental monitoring inaccuracies introducted deenorating condition.

An ideal solu:

low-level, low-resolu:

and for periodic vericentral computer for in

a mechanism for realize

Performance monitoring is similar to condition monitoring in its data requirements.

Performance monitoring differs in that it provides a quantitative measure of the bearing's health.

Diagnostic monitoring is used to determine the cause of any defect discovered in the bearing. This generally requires data that is more detailed than is necessary for performance monitoring. Further, research indicates that different bearing defects are best diagnosed through the use of various types of data reduced using a variety of techniques [2, 3].

Prognostic monitoring attempts to predict the future operating conditions of the bearing or, more specifically, exactly when the bearing will fail. Due to the wide variance in bearing life expectancy and the difficulty in obtaining direct information about the contacting surfaces inside the bearing, no prognostic monitoring systems are commercially available.

In addition to the level of monitoring, the frequency of monitoring is important. Continuous monitoring requires sensors permanently attached to the machine and dedicated data collection, reduction and analysis hardware. At the other extreme, handheld meters are periodically connected to machinery by maintenance personnel. The meters may perform condition monitoring on location or may record data for future analysis. A compromise technique uses permanently attached sensors connected to a central monitoring processor via multiplexed cables. This method removes the inaccuracies introduced by hand-held devices but may result in a delay in detecting deteriorating conditions if the degree of multiplexing is high.

An ideal solution would employ small processors at the sense point to perform low-level, low-resolution continuous condition monitoring. When a problem is detected and for periodic verification of operation, the sensor signal could be transmitted to a central computer for in-depth processing on high-resolution data. Intelligent sensors offer a mechanism for realizing such a monitoring system.

# 12 INTELLIME

As mir

parameter of information ab

A monitory of the Attached to the type of machine vibration, acoust and particulate

and affect chan

#### 1.2 INTELLIGENT SENSOR MONITORING SYSTEM

As minimum requirements, an intelligent sensor is capable of measuring some parameter of its environment, reducing the effects of cross-parameters and transmitting information about the parameter. Additionally, it may perform signal conditioning and format conversion, extract parameter features, make decisions based on these features, and affect changes either directly or by communicating the results.

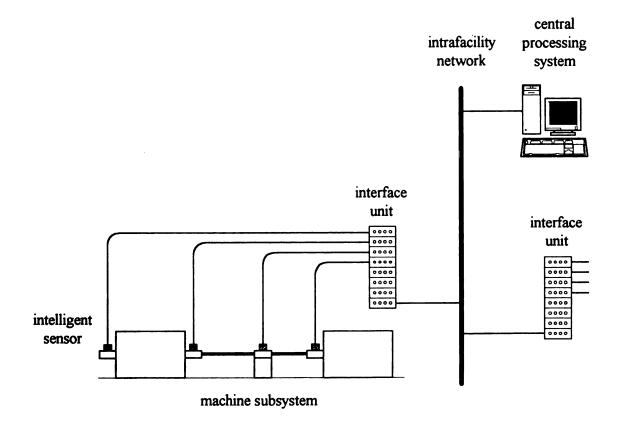

A monitoring system that employs intelligent sensors is pictured in Figure 2. Attached to the machinery being examined is a group of smart sensors. Depending on the type of machinery, the sensed parameters may include temperature, voltage, current, vibration, acoustic emissions, speed, torque, force, chemical makeup, radiation, pressure and particulate size. A group of sensors is connected to an interface unit through

Figure 2. Intelligent monitoring system.

dedicated cables T well as initialization

Once initial performing data gard condition is detected smart sensor can be digitized data to the data reduction, performed sensors with computer for further

The central pleasement the monit minalization, and responses or via a plant Alternation Protocol

Many of the mentioning system, simplemented [6, 7] imaligent sensors

In order to miscommon electronics common buffers

are used to carry massimity in silicon based

dedicated cables. The interface unit provides each sensor with power and clock signals as well as initialization parameters on startup.

Once initialized, the intelligent sensors are capable of operating autonomously, performing data gathering, reduction and condition monitoring functions. If a change in condition is detected, an alarm is transmitted to the interface unit. Additionally, each smart sensor can be placed in a transducer mode, allowing it to transmit conditioned, digitized data to the interface unit. The interface unit may collect this data, implement data reduction, perform multivariate condition monitoring or diagnostics, reinitialize the intelligent sensors with new parameters, and forward the data to the central processing computer for further analysis.

The central processing system provides advanced data manipulation, coordination between the monitoring of different machine subsystems, overall plant monitoring initialization, and report generation. The interface units are connected to the central processor via a plant-wide communication network, such as the MAP (Manufacturing Automation Protocol) network [5].

Many of the high-level components required for the intelligent sensor based monitoring system, such as the interface units and the central processor, have been implemented [6, 7]. A major set of components that have not been designed is the intelligent sensors.

In order to minimize the cost of the system, each intelligent sensor should contain common electronics for connecting to the interface unit. These electronics provide communication buffering, power supply regulation and signal separation if common wires are used to carry multiple signals. Since temperature is the major source of cross-sensitivity in silicon based microsensors [8, 9], a temperature sensing circuit should also be included.

As a bear

localized metal fati plis. The pitting accumulation of dafailure or seizes due

No technique accumulated contact varying success, including success, including the success and the success acceleration. Three typesceleration. Acceleration.

accelerometers A disprovided in Chapter 2

This project of

the sensor system is so by the bold boxes in

The common

provides a voltage our

A possible scheme for combining the clock at

to the monitor on stations operation

#### 1.3 Project Scope

As a bearing ages, the contact between races and rolling elements produces localized metal fatigue. This fatigue produces small subsurface cracks that may grow into pits. The pitting of the surfaces increases contact stresses, further accelerating the accumulation of damage. This damage progresses until the bearing suffers a component failure or seizes due to excessive friction.

No technique has been developed for direct, in situ measurement of the accumulated contact surface damage. Several indirect measures have been used with varying success, including housing vibration, housing temperature, lubricant temperature, lubricant metal analysis, and acoustic emission. Of these, the most widely used is housing vibration. Three types of housing vibrations can be measured: displacement, velocity and acceleration. Acceleration is most often used due to the frequency range and cost of accelerometers. A detailed description of rolling element bearings and their monitoring is provided in Chapter 2.

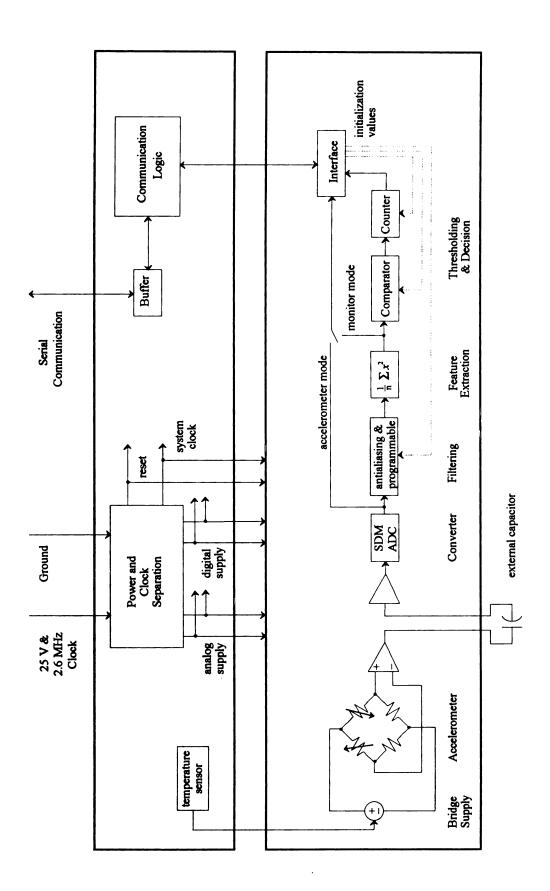

This project concentrates on the design of critical elements unique to an intelligent microsensor for monitoring the vibrations of rolling element bearings. A block diagram of the sensor system is shown in Figure 3. The system is divided into two portions, signified by the bold boxes in the figure. The top portion represents electronics common to all intelligent sensors. The bottom portion is unique to the vibration monitor.

The common portion contains three subsystems, a temperature sensor, communication logic, and power and clock separation circuitry. The temperature sensor provides a voltage output used to adjust the bridge supply for cross-parameter correction. A possible scheme for connecting an intelligent sensor to the interface unit uses 3 wires, combining the clock and power supply on a single cable. This requires separation circuitry at the sensor. Communication logic passes initialization parameters from the interface unit to the monitor on startup and passes data from the monitor back to the interface unit during operation.

Сонтинизация Huffer Serud Communication reset / p..... Power and Clock 25 V W 2 Clark

Figure 3. Bearing vibration monitor.

The s

micromachine

amplification

digital convert

mean squared

logic. The de

compensated, conventions

14 ASS 3.5 TO

programmable i

Three a monitor. These operating temper

141 Knowledge

Although knowledgeable

consguration of inelligent sensor

the correct place

Prace prace

With regard

determine approp

understanding of

The sensor components unique to the bearing vibration monitor include a micromachined accelerometer incorporating a half-active piezoresistive bridge, amplification and conditioning electronics, a novel sigma-delta modulating analog-to-digital converter, programmable digital filters, feature extraction logic for calculating the mean squared value of the filtered acceleration signal, thresholding logic, and control logic. The device is capable of operating as either a smart accelerometer, transmitting compensated, digitized vibration acceleration values back to the interface unit, or as an autonomous condition monitor, comparing filtered mean squared vibration values to a programmable threshold.

#### 1.4 ASSUMPTIONS

Three assumptions were used in the development of the intelligent vibration monitor. These assumptions concern the availability of a knowledgeable user, the range of operating temperatures, and the ergodicity of the bearing vibration signals.

## 1.4.1 Knowledgeable User

Although the bearing monitor is considered an intelligent device, it still requires a knowledgeable user. The user must first make decisions regarding the overall configuration of the monitor system. Once this is accomplished, the appropriate types of intelligent sensors must be chosen to match the needs of the machinery subsystem. Next, the correct placement of each sensor is critical to maximizing the sensing of the desired parameter and minimizing the effects of cross-parameters.

With regard to the intelligent vibration monitor, a knowledgeable user must determine appropriate initialization parameters for the sensor. This requires an understanding of the bearing configuration and potential failure modes as well as the

knowledgeab! deteriorates gra assume the signa the correlation

limitations of the vibration In the

142 Temper

The or

This range is

located in man

The rea simple tempera

range is desired

143 Vibration

The vib since a change

deteriorating he

$D_{espite}$

assumed to be s

assumption allow

In addition

[il] Ergodicity

esemble average

limitations of the sensor. The user must also be able to interpret the results produced by the vibration monitor to determine an appropriate course of action.

In the future, it may be possible to replace the functions provided by the knowledgeable user with an expert system.

# 1.4.2 Temperature Range

The operating temperature range assumed for this device is  $20 \pm 20$  °C ( $68 \pm 36$  °F). This range is reasonable for bearings mounted on motors, fans, pumps or transmissions located in manufacturing facilities designed for human workers.

The reason for this choice for the range of temperatures is to allow for the use of a simple temperature compensation scheme in the intelligent bearing monitor. If a greater range is desired, a more complicated scheme may be employed.

# 1.4.3 Vibration Signal Ergodicity.

The vibration signal over the life of the bearing is nonstationary. This is apparent since a change in the signal's statistical properties over time provides an indication of deteriorating health.

Despite the long-term nonstationary quality of the vibration signal, it is always assumed to be stationary over short intervals [10]. This is because the bearing normally deteriorates gradually over an extended period of time, often many years. This assumption allows the calculation of power spectral densities for frequency analysis.

In addition to assuming the vibration signal is locally stationary, it is common to assume the signal is locally ergodic as well. This assumption is reported to be valid due to the "correlation between machinery vibration and defects for similar pieces of equipment" [11]. Ergodicity allows signal statistics to be calculated from time averages instead of ensemble averages. Hence the major reason for the ergodic assumption is the

impracticality of operating condition

15 OVERVIEW

The rema

discusses the natu and defect-free ho monitoring featu

requirements for o

Chapter 3 mass accelerome

riezoresistive bri

new The charge

electronics

A second

Chapter 4. The

the area than

quantization noi Tay be routed o

Chapter

programmable i

and control log

discussed.

The re presented in Ci

bearing vibratio

impracticality of obtaining data from identical pieces of machinery under identical operating conditions.

#### 1.5 OVERVIEW

The remainder of this dissertation is divided into seven chapters. Chapter 2 discusses the nature of bearing vibrations and presents a simulator for generating defective and defect-free housing acceleration signals. These signals are used to examine condition monitoring feature extraction methods and to determine frequency and resolution requirements for condition and diagnostic monitoring.

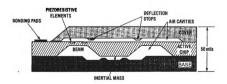

Chapter 3 describes the microaccelerometer. The design of a four-post suspended mass accelerometer is followed by finite element analysis results. The half-active piezoresistive bridge that transduces acceleration into a change in voltage is presented next. The chapter also includes discussions on transducer construction issues and support electronics.

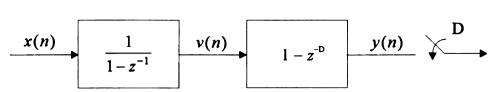

A second-order sigma-delta modulating analog-to-digital converter is designed in Chapter 4. The converter incorporates a novel first-stage decimation filter requiring less chip area than conventional designs. The first-stage decimator provides sufficient quantization noise reduction for on-chip condition monitoring. Output from the first-stage may be routed off-chip for further diagnostic processing.

Chapter 5 discusses the design of the on-chip second-stage decimator, sixth-order programmable IIR digital filter, mean squared value calculation logic, thresholding logic, and control logic. A register transfer level simulation of the digital hardware is also discussed.

The results of a functional simulation of the intelligent vibration monitor are presented in Chapter 6. The simulator consists of 3 modules written in C representing the bearing vibration source, transducer and conditioning electronics, and digital logic.

Chapter 7:

further research

Four appen

bearing simulation

Chapters 3 and 4 re

programmable IIR

Chapter 7 lists the contributions resulting from this project and presents areas for further research.

Four appendixes are provided. Appendix A lists the parameters used in the bearing simulation of Chapter 2. Appendixes B and C provide supporting material for Chapters 3 and 4 respectively. Appendix D contains the design of digital filters used in the programmable IIR section of the monitor.

A bearing mechanism. The the friction between the inner race, attach to the recess, separation and rotating conteedie, tapered inner and outer provides balance surrounds, and

Bearings

The of rolling

Another method

Self-aligning bear

dissertation, the

do not A third

bearing princips

(thrust) bearing

Regardie they age and we surface of the be

the health of the Bearing:

# **CHAPTER 2 BEARING VIBRATIONS**

A bearing interfaces a rotating shaft to a stationary support or another rotating mechanism. The goal of a good bearing is to sufficiently distribute the load and minimize the friction between the two elements. Rolling element bearings consist of five basic parts: the inner race, outer race, rolling elements, cage and housing. The inner and outer races attach to the rotating shaft and the stationary support. The rolling elements fit into the races, separating the two races and providing the transfer of load between the stationary and rotating components. Rotating elements may be balls (spheres), or may be cylindrical, needle, tapered or barrel rollers. Most rolling element bearings contain a cage between the inner and outer races. The cage maintains proper spacing between the rolling elements, provides balance, and prohibits contact between the rotating elements. The housing surrounds and protects the bearing assembly. Throughout the remainder of this dissertation, the term bearings will imply rolling element bearings only.

Bearings can be classified using criteria based on their construction and use. The type of rolling element used in the bearing divides them into ball and roller bearings. Another method of classification considers the technique for guiding the shaft, yielding self-aligning bearings that allow for shaft misalignment and non self-aligning bearings that do not. A third method of classifying bearings uses the supported load direction. A radial bearing principally supports a load perpendicular to the shaft and an angular contact (thrust) bearing supports load along the axis of rotation as well as radially.

Regardless of the type, all bearings tend to exhibit similar deterioration patterns as they age and wear. This wear produces vibrations that can be detected on the outside surface of the bearing housing. A monitoring system detects these vibrations to determine the health of the bearing.

Bearing life and failure modes, and the vibrations these modes produce are covered

obtaining vibration signals. Section used throughout 25. Section 2.6 material presented

21 BEARNOLI

One of:

the effective life magnitude differ bearings will fai

avoid catastrop

the other extrem

The var

failure modes as due to material

the rate of wear

bearing should

One pri

Progress to the Following the

feed particles

in Sections 2.1 and 2.2. Section 2.3 contains a discussion of the issues associated with obtaining vibration signals and the techniques for extracting salient features from these signals. Section 2.4 presents a bearing vibration simulator and the specific bearing model used throughout this dissertation. The results of the simulation are presented in Section 2.5. Section 2.6 develops a set of specifications for the monitor system based on the material presented.

## 2.1 BEARING LIFE AND FAILURE

One of the difficulties in using rolling element bearings is the large discrepancy in the effective life of identical bearings under similar loads. This is reflected in the order of magnitude difference between the  $B_{10}$  life (length of time during which 10% of all bearings will fail) and the  $B_{90}$  life. Therefore, it is important to monitor the bearing to avoid catastrophic failure and the subsequent costly unscheduled downtime, and to avoid the other extreme of replacing perfectly useful bearings [12].

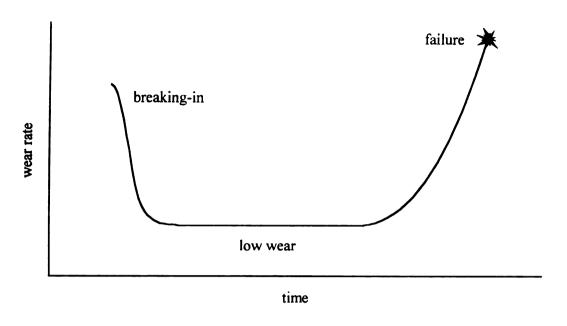

The variance in expected bearing life is partially due to the number of possible failure modes and their varying effects. Under optimal conditions, a bearing will wear out due to material fatigue based on the load, speed and service time. The function describing the rate of wear for a bearing throughout its life has a bathtub shape, as shown in Figure 4. Initially, the bearing will accumulate wear rapidly during a short breaking-in period. The bearing should then experience a long period of low wear accumulation and low fatigue.

One principal failure mode begins as the bearing ages. Metal fatigue causes small cracks to form below the surface of the races and/or rolling elements. These cracks progress to the surface, breaking free small pieces of material and producing pits. Following the initial pitting, wear accumulates rapidly due to the damage caused by the freed particles and due to rolling surfaces impacting the pits.

electrical currents, temperatures. The Under cert.

distributed indental electric current), coor more of the su

defect, also accelet

Figure 4. Bearing lifetime wear rate [13].

This may create additional pitting on other surfaces and may enlarge the pits already present, both in depth an in surface area, further increasing the wear rate. The damage progresses until the bearing suffers a component failure or seizes due to excessive rubbing friction.

The formation of bearing surface damage and subsequent bearing failure can be accelerated due to several factors including lubrication failure, contamination, corrosion, electrical currents, excessive preloading, vibration, incorrect mounting and excessive temperatures. These factors tend to produce point or local defects [12, 14].

Under certain conditions, factors such as lubrication failure, brinelling (regularly distributed indentations in the races due to excessive vibration or shock, static loading or electric current), contamination and corrosion may cause somewhat even damage over one or more of the surfaces simultaneously [15]. This damage, classified as a distributed defect, also accelerates wear and greatly reduces bearing life.

pattern around eccentric races

> source of study temperature, ac examined as po: commercial use

Anoth

The de

installed beam

22 BEARING VIII

ease of implemen

Contacts | Vibrations from v they can be used ! sources of vibrati

resulting from inte Vibrations

conditions, the ma with the races S functions of the su

properly lubricated

amplitude, zero me

results from contact

though the shaft c staff rotational vibra

Another set of difficulties includes distributed defects due to faulty or improperly installed bearings. These problems produce unusual loading distributed in a symmetrical pattern around the bearing. Factors producing these defects include misaligned races, eccentric races, off-size rolling elements and out-of-round components [14].

The detection of the damage and wear level suffered by a bearing has been a source of study since the invention of the bearing. Various bearing parameters, including temperature, acoustic emissions, lubricant debris and housing vibrations, have all been examined as potential sources for health monitoring. Currently, the majority of systems in commercial use are based on the analysis of housing vibrations due to the effectiveness, ease of implementation and relatively low cost of vibration-based systems.

## 2.2 BEARING VIBRATIONS

Contacts between elements in a bearing produce forces that result in vibrations. Vibrations from within the bearing are transmitted to the surface of the housing where they can be used to determine the type and extent of damage. This section examines the sources of vibrations in rolling element bearings and the characteristics of vibrations resulting from internal defects.

Vibrations from new bearings generally arise from three sources. Under optimal conditions, the main source of vibrations is the normal contact of the rotating elements with the races. Since this contact involves rolling surfaces, the vibrations produced are functions of the surface smoothness and, since these surfaces are quite smooth on new, properly lubricated bearings, the vibration produced have the form of relatively low amplitude, zero mean Gaussian noise [12, 16, 17]. A second source of housing vibrations results from contacts in other machinery. The vibrations are transmitted to the bearing through the shaft or the mountings. These sources include fundamental and harmonic shaft rotational vibrations, gear mesh vibrations, cavitation noise from pumps, blade noise

from turbines, and results from implement on the s

As the bear

Throughout most point, however, the continues to deterior

The basic of depending on the factoristics is to the magnitude at 4 to 1 kHz contains contacting other electronic approximately 500 I in the contacting stapproximately 10 k in the bearing [12]

from turbines, and impacts from reciprocating equipment. A third source of vibrations results from improperly installed or defective bearings, with the type of vibration dependent on the specific problem.

As the bearing ages, the average level of vibration increases, as shown in Figure 5. Throughout most of the bearing's life, the vibration level growth is gradual. At some point, however, the bearing experiences a defect that accelerates the rate of increase. As it continues to deteriorate, the vibration level climbs until failure occurs.

The basic characteristics of these vibrations change, as does their magnitude, depending on the failure mode, loading and bearing usage. One method of examining the characteristics is to consider the magnitude frequency spectrum of the bearing vibrations. The magnitude at 0 Hz must be zero if the bearing is stationary. The range from above 0 to 1 kHz contains the repetition frequencies corresponding to defective components contacting other elements and most vibrations from connected machinery. The range from approximately 500 Hz to 20 kHz shows the random vibrations produced by the roughness in the contacting surfaces and harmonics of the defect frequencies. The range above approximately 10 kHz includes the vibrations resulting from excitation of the resonances in the bearing [12]. These ranges vary depending on bearing type and running conditions.

Figure 5. Average bearing vibration level vs. time [10].

The defect calculated if the best face or inner race. The frequencies of the defect is on a The frequency of frequency (f<sub>b</sub>) 1 frequencies [13, 1]

Ntere

$f_r$   $f_l$

$f_{o}$

$f_b$

$f_l$

n

D

$D_{l}$

¢

The defect repetition rates for point defects on rolling elements or races can be calculated if the bearing geometry and shaft speed are known. If the defect is on the outer race or inner race, each rolling element will strike the defect once per cage revolution. The frequencies of the sum of the impacts due to all rolling elements are known as the ball pass frequency of the outer race  $(f_0)$  and the ball pass frequency of the inner race  $(f_i)$ . If the defect is on a rolling element, it contacts both the inner and outer races alternately. The frequency of contact with one of the races (outside) is referred to as the ball spin frequency  $(f_0)$ . Below are the formulas for calculating the point defect repetition frequencies [13, 18].

$$f_{i} = \frac{n}{2} f_{r} \left( 1 + \frac{D_{b}}{D_{p}} \cos \phi \right),$$

$$f_{o} = \frac{n}{2} f_{r} \left( 1 - \frac{D_{b}}{D_{p}} \cos \phi \right),$$

$$f_{b} = \frac{D_{p}}{2D_{b}} f_{r} \left( 1 + \frac{D_{b}^{2}}{D_{p}^{2}} \cos \phi \right),$$

$$f_{i} = \frac{1}{2} f_{r} \left( 1 - \frac{D_{b}}{D_{p}} \cos \phi \right).$$

where

$f_r$  = rotating unit frequency (shaft speed) (Hz),

$f_i$  = inner race element pass frequency (Hz),

$f_o$  = outer race element pass frequency (Hz),

$f_b$  = rotating element spin frequency (Hz),

$f_t$  = fundamental train frequency (Hz),

n = number of rotating elements,

$D_b$  = rotating element diameter (mm),

$D_p$  = pitch diameter (mm),

$\phi$  = contact angle.

The fundamental training revolve around the ax

The magnitude function of the bearing defect contacts another. The detected vibration the housing surface exponentially damped as

If the defect of

through regions of vary period the inverse of the the fundamental train from the fundamental train from the fundamental train from the fundamental train from the attenuation conditions are the attenuation of the attenuatio

groove, causing the vibra

Due to the comp features are extracted for with obtaining a signal an of the transducer, frequen featuring, and the type in

<sup>23</sup> VIBRATION SIGNALS

The fundamental train frequency is the speed at which the rotating elements and the cage revolve around the axis of rotation.

The magnitude and shape of the vibrations produced by the point defect are a function of the bearing geometry, loading, and defect location and size. When a point defect contacts another surface, the resulting shock can be approximated as an impulse. The detected vibration is dependent on the transmission path from the defect location to the housing surface. A good approximation of the resulting acceleration is an exponentially damped sinusoid [13].

If the defect occurs on the outer race, each rolling element impact will cause a decaying pulse of similar magnitude. If the defect is on the inner race, it may rotate through regions of varying load. This produces a series of decaying pulses, each with a period the inverse of the inner race pass frequency and with the magnitude modulated by the fundamental train frequency. If the defect is on a rolling element, it will alternately strike the inner and outer races, passing the inner race induced vibrations at a weaker level due to the attenuation caused by the signal passing through the rolling elements. Since the defective element is rotating through areas of different loading, the magnitudes will be modulated by the fundamental train frequency. If the rolling elements are balls, there is the additional possibility of having the defect spin partially or completely out of the race groove, causing the vibrations to intermittently fade or disappear.

## 2.3 VIBRATION SIGNALS AND FEATURE EXTRACTION

Due to the complex and random nature of bearing vibration signals, descriptive features are extracted for use in monitoring and diagnostics. Several issues are associated with obtaining a signal and extracting the salient features, including the type and location of the transducer, frequency range of the transduced signal, magnitude range and signal resolution, and the type and amount of data reduction to obtain an indication of the

bearing health velocity, and a desired, with Industr frequencies,

23.1 Transdu

Three t

acceleration at

required for g

housing mass

housing surface

Indust

vibrations and

[19]. Veloci

limited frequ

sinusoidal c

Indus a frequency

most prevale

choice in a n

The

limitations re

The transdu

area of high

bearing health.

## 2.3.1 Transducer Type and Location

Three types of vibration signals have been used to monitor bearings: displacement, velocity, and acceleration. The selection is primarily dependent on the frequency range desired, with displacement showing the greatest sensitivity at low frequencies and acceleration at high frequencies.

Industrial displacement transducers are useful to about 1 kHz, below the minimum required for general bearing monitoring. They find use on large, slow machines where the housing mass is significantly greater than the rotating mass resulting in vibrations at the housing surface that may not be representative of the internal condition [19].

Industrial velocity transducers tend to be bulky, to be sensitive to cross-axis vibrations and magnetic interference, and to have a useful frequency range up to 2 kHz [19]. Velocity transducers have been successfully used to monitor bearings despite their limited frequency ranges. They are reported to have a flatter frequency response to a sinusoidal contact force than displacement transducers, which accentuate lower frequencies, and acceleration sensors, which accentuate higher frequencies [20].

Industrial acceleration transducers have good insensitivity to cross-parameters and a frequency range from 0 to above 10 kHz [19]. Acceleration appears to be by far the most prevalent transduction method in the field, and has been selected as the method of choice in a number of research articles that compare velocity and acceleration [12, 21, 22].

The location of the transducer is important in detecting defects. One of the limitations required by most bearing designs is that the transducer must be non-intrusive. The transducer should be located on the housing surface at a point corresponding to the area of highest loading inside the bearing [20].

$^{6001}$  8 to  $_{1000}$   $_{8}$

amount beyond t

their own work, 1

A survey acceleration valu bearings under di

### 2.3.2 Signal Frequency Range

The optimum range of frequencies for bearing vibration acceleration signals depends on the type of bearing, application and feature extraction method used. Two basic ranges have been identified, low frequency monitoring and high frequency monitoring.

Low frequency monitoring extends up to between 2 and 10 kHz [23]. This range is designed to encompass the defect repetition frequencies and their significant harmonics. Various reports indicate that this range is suitable for extracting salient information about the health of a bearing [17, 24, 25].

High frequency monitoring extends to 20 kHz and beyond. This range includes the vibrations that arise when housing resonances are excited by point defect impacts. Several studies report greater success in the high frequency range, particularly if there is significant noise from external sources [19, 21, 22].

The current available research is inconclusive as to the best range of frequencies to use in bearing monitoring. If the bearing is operating in a relatively quiet environment or filtering is used to remove extraneous signals, the low frequency range is appropriate. This also fits into the present technological constraints for microaccelerometer frequency ranges.

#### 2.3.3 Signal Magnitude Range and Resolution

Xistris et al. claim that vibration monitors should ideally operate in the range of 0.001 g to 1000 g measured to 10 kHz [23]. This would require 20 bits of resolution, an amount beyond the capability of most industrial-grade analog-to-digital converters. In their own work, 12-bit accuracy was used [23].

A survey of research was conducted to obtain a range for RMS and peak acceleration values. Table 1 presents the starting and maximum values for different bearings under different conditions.

Table 1 Vibration signal ranges for different bearings.

| Bearing Load/ | Frequency Bearing | Frequency Bearing  | Peak (g) Frequency Bearing    | Frequency Bearing             |

|---------------|-------------------|--------------------|-------------------------------|-------------------------------|

| Type          | Kange (Kriz)      | aximum Kange (KTZ) | No defect Maximum Kange (KTZ) | No defect Maximum Kange (KTZ) |

| double row    | 0 - 20 double row | 500 0 - 20         | 0 - 20                        | 500 0 - 20                    |

| ball          | ball              | ball               | ball                          | ball                          |

| double row    | 0 - 20            | 50 - 500 0 - 20    | 0 - 20                        | 50 - 500 0 - 20               |

| ball          | ball              | ball               | ball                          | ball                          |

| tapered       | 0 - 20            | 28 - 69 0 - 20     | 1-2 28-69 0-20                | 28 - 69 0 - 20                |

| roller        | roller            | roller             | roller                        | roller                        |

| tapered       | 0 - 5 tapered     | 0-5                |                               | 0-5                           |

| roller        | roller            |                    | 0.63 roller                   |                               |

| 1100 - 2000   | 2.5 - 5           |                    |                               |                               |

|               |                   |                    |                               |                               |

| tapered       | 3 - 5 tapered     |                    |                               |                               |

| roller        | roller            | roller             | roller                        | roller                        |

| tapered       | 3 - 5 tapered     | 3.0 3-5            | 3-5                           | 3.0 3-5                       |

| roller        | roller            | roller             | roller                        | roller                        |

|               |                   |                    |                               |                               |

to cover this range Appropriate quantiz Many techn indicate that more 16] and trending The fequencies. An al tange exceeds the

Two facts ca variation between th test conditions Th satisfy the needs for The second i Amongst the RMS v maximum for any or the RMS values (11 from 24 to 40 dB

> The range be required to represer

234 Feature Extra

These include the a single-value indexe trending, and time

Probably th

over a set period o

Spectral ter

Two facts can be obtained from an examination of the table. First, there is a large variation between the no defect and maximum values for different bearings under different test conditions. This implies that it is highly unlikely that any one type of device will satisfy the needs for all monitoring situations.

The second item concerns the magnitude range required for a given bearing signal. Amongst the RMS values, there is no more than a 31 dB variation between no defect and maximum for any one type of bearing and test. This indicates that 6 bits are required for the RMS values (11 bits for mean squared values). The spread of peak amplitudes varies from 24 to 40 dB. Assuming the signal is symmetric, between 5 and 8 bits are necessary to cover this range.

The range between no defect and maximum levels does not consider the resolution required to represent the signal. Unfortunately, this area is not covered in the literature.

Appropriate quantization levels must be obtained through experimentation or simulation.

#### 2.3.4 Feature Extraction Methods

Many techniques have been developed for monitoring the health of bearings. These include the areas of spectral analysis, statistical analysis, low frequency time-domain single-value indexes, high frequency time-domain single-value indexes, frequency-domain trending, and time-domain trending. Several reports that compare different methods indicate that more than one method may be required to detect impending failures [12, 15, 16].

Probably the most prevalent technique in industry is power spectrum windowing and trending. The person implementing this technique sets maximum limits over ranges of frequencies. An alarm is raised when a magnitude value at a frequency within a specified range exceeds the "window" threshold value. The maximum level within each window over a set period of time may be saved for trending analysis [15, 26].

Spectral techniques yield very good sensitivity to changes in the bearing's health,

but possereduction

near-futu

computa

single-va

I

sensor.

defective

Variance.

I

time rang

where a

calculate

derelope five qua

moniton

but possess a high degree of computational complexity and may produce very little data reduction. These disadvantages eliminate spectral methods from consideration for use in near-future smart sensor monitors due to the silicon area required to perform the computations and to store and process the large amounts of data produced.

In contrast, time-domain statistical indexes have simple algorithms and produce single-valued outputs for a given time range, making them better suited to a self-contained sensor. Their main detraction is that they generally are not as accurate at detecting defective bearings. Four techniques were considered for use in the monitor: peak, variance, crest and kirtosis values.

The peak value,  $A_p$ , is the maximum vibration acceleration value over the given time range. Expressed mathematically,

$$A_{p} = \max_{n} (a_{i}),$$

where  $a_i$  is the i<sup>th</sup> acceleration value over n samples. The peak value is the easiest to calculate, and has been studied extensively [4, 15, 16, 22, 26, 28]. Comprehensive limits on peak levels have been determined for use as guides when examining bearings. One set, developed at the Southwest Research Institute, partitions possible bearing conditions into five quality grades [28]:

$$A_p < 0.9 g$$

No fault

$0.9 < A_p < 1.8 g$  Acceptable

$1.8 < A_p < 3.6 g$  Marginal

$3.6 < A_p < 7.2 g$  Failure probable

$7.2 < A_p$  Danger of immediate failure.

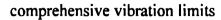

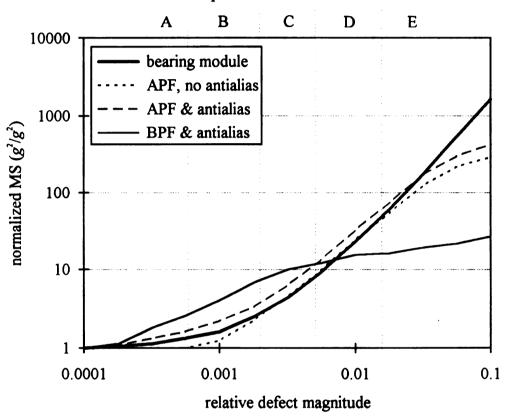

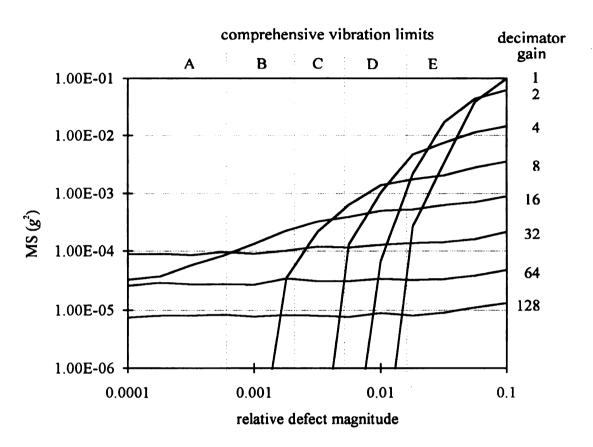

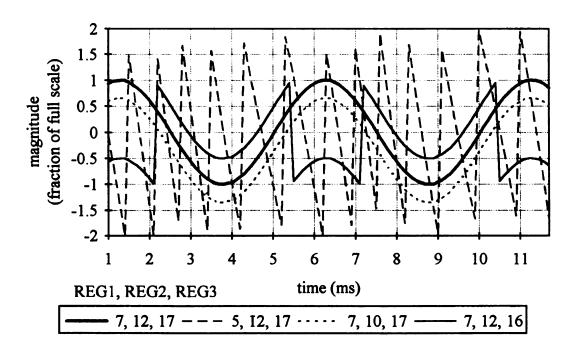

The precise acceleration levels for each grade depend on the type of bearing being monitored, equipment mounting, vibration frequencies and monitoring equipment.