# LIBRARY Michigan State University

PLACE IN RETURN BOX to remove this checkout from your record.

TO AVOID FINES return on or before date due.

| DATE DUE | DATE DUE | DATE DUE |

|----------|----------|----------|

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

MSU is An Affirmative Action/Equal Opportunity Institution ctcircletedus.pm3-p.1

# A CONFLICT-FREE MEMORY DESIGN FOR MULTIPROCESSORS

$\mathbf{B}\mathbf{y}$

Honda Shing

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Computer Science

1992

#### **ABSTRACT**

# A CONFLICT-FREE MEMORY DESIGN FOR MULTIPROCESSORS

By

#### Honda Shing

Multiprocessors have been widely used in achieving high performance computation. In a multiprocessor, applications are implemented with processes executing on multiple processors and cooperating with each other. It is hoped that, by using multiple processors, multiplied performance improvement can be obtained. Ideal speedup, however, can hardly be achieved due to several factors. In a shared-memory multiprocessor, memory conflicts and interconnection network contention are two of the most important performance degradation factors.

This dissertation proposes a conflict-free memory architecture, a new architecture based on block accesses, which solves the memory and network contention problems in shared-memory multiprocessors. With a synchronously coordinated memory access pattern and a contention-free interconnection network, memory conflicts and network contention can be eliminated. In addition, the tree saturation problem that results from the hot spot problem is solved. Possible extensions to the architecture and performance issues are also discussed in this dissertation.

An invalidation-based write-back cache coherence protocol is introduced for the conflict-free memory architecture. The new cache protocol preserves the advantages of both conventional snoopy protocols and directory-based protocols. With this cache coherence protocol, efficient synchronization operations can be implemented to support the weak memory consistency model. Furthermore, high level process synchronization mechanisms can be implemented with low overhead and low latency. The scalability of both the conflict-free memory architecture and the cache coherence protocol are demonstrated.

This dissertation also introduces the new parallel programming paradigm, resource binding, which can be efficiently implemented on the conflict-free memory architecture. With simple primitives, the programming paradigm handles shared data protection and process synchronization in a flexible and consistent way. In addition, the resource binding paradigm can be implemented in other shared-memory and distributed-memory systems, which allows programmers to write portable parallel programs that are easy to understand and to debug.

Copyright © by Honda Shing 1992 To my parents

#### ACKNOWLEDGEMENTS

I wish to thank my advisor, Dr. Lionel M. Ni, who has guided me throughout the academic and research years of my Ph.D. program. Without his patient instruction and imaginative enlightening, this dissertation would have been impossible.

I would also like to thank Dr. Anthony S. Wojcik for his valuable suggestions and comments on this dissertation and careful reviewing of the manuscript. I appreciate Dr. Richard Enbody, who has always been willing to answer my questions and to spend time on discussions. I am grateful to Dr. R. V. Ramamoorthy for his encouragement and support.

A person cannot accomplish anything without the help and encouragement of others. I would like to thank all the people who helped me during my stay at Michigan State University. In particular, I wish to acknowledge my friends Ten Hwan Tzen, Arun Nanda, and brothers and sisters in the Michigan State University Chinese Christian Fellowship.

Finally, I thank my parents for their continuous support, patience, and love.

# TABLE OF CONTENTS

| L | LIST OF TABLES |        |                                                    | x  |

|---|----------------|--------|----------------------------------------------------|----|

| L | ST (           | OF FI  | GURES                                              | хi |

| 1 | INT            | rod    | UCTION                                             | 1  |

|   | 1.1            | Distri | buted-Memory Multiprocessors                       | 2  |

|   | 1.2            |        | d-Memory Multiprocessors                           | 3  |

|   | 1.3            | Disser | rtation Outline                                    | 5  |

| 2 | SH.            | ARED   | -MEMORY DESIGN CONSIDERATIONS                      | 8  |

|   | 2.1            | The C  | Contention Problem and Solutions                   | 8  |

|   |                | 2.1.1  | The NYU Ultracomputer and the IBM RP3              | 9  |

|   |                | 2.1.2  | The BBN Butterfly and Monarch                      | 10 |

|   |                | 2.1.3  | The OMP multiprocessor                             | 11 |

|   |                | 2.1.4  | The Cedar Project                                  | 12 |

|   | 2.2            | Memo   | ory Consistency Models                             | 13 |

|   |                | 2.2.1  | Sequential Consistency                             | 13 |

|   |                | 2.2.2  | Processor Consistency                              | 14 |

|   |                | 2.2.3  | Weak Consistency                                   | 15 |

|   |                | 2.2.4  | Release Consistency                                | 16 |

| 3 | CO             | NFLIC  | CT-FREE MEMORY                                     | 18 |

|   | 3.1            | The C  | CFM Architecture                                   | 18 |

|   |                | 3.1.1  | The $AT$ -Space and Block Accesses                 | 19 |

|   |                | 3.1.2  | Designing the CFM with AT-Space Partitioning       | 21 |

|   |                | 3.1.3  | Constructing the CFM with Longer Memory Bank Cycle | 23 |

|   |                | 3.1.4  | The CFM Configurations and Parameters              | 26 |

|   | 3.2            | Conte  | ention-Free Interconnection Networks               | 29 |

|   |                | 3.2.1  | Synchronous Omega Networks                         | 30 |

|   |                | 3.2.2  | An Extension for Large Scale Multiprocessors       | 33 |

|   | 3.3            | Other  | CFM Extensions                                     | 36 |

|   | 3.4 | The C                                  | CFM Performance                                 | 37         |  |  |

|---|-----|----------------------------------------|-------------------------------------------------|------------|--|--|

|   |     | 3.4.1                                  | Efficiency of Conventional Memory Systems       | 37         |  |  |

|   |     | 3.4.2                                  | Efficiency of the CFM Architecture              | <b>3</b> 9 |  |  |

|   |     | 3.4.3                                  | Overhead of Interconnection Networks            | 42         |  |  |

|   |     | 3.4.4                                  | Latencies of Memory Accesses                    | 44         |  |  |

| 4 | DA  | TA CO                                  | DNSISTENCY AND ATOMIC OPERATIONS                | 45         |  |  |

|   | 4.1 | Data                                   | Consistency                                     | 46         |  |  |

|   |     | 4.1.1                                  | Inconsistency Problem Caused by the CFM         | 46         |  |  |

|   |     | 4.1.2                                  | Ensuring Data Consistency with Address Tracking | 47         |  |  |

|   | 4.2 | Imple                                  | menting Atomic Operations with Address Tracking | 54         |  |  |

|   |     | 4.2.1                                  | The Atomic Swap Operation                       | 55         |  |  |

|   |     | 4.2.2                                  | Implementing Lock/Unlock with Swap              | 57         |  |  |

| 5 | CA  | CACHE COHERENCE AND SYNCHRONIZATION 59 |                                                 |            |  |  |

|   | 5.1 | Cache                                  | Coherence Protocol Review                       | 60         |  |  |

|   |     | 5.1.1                                  | Snoopy Cache Protocols                          | 60         |  |  |

|   |     | 5.1.2                                  | Directory-Based Cache Protocols                 | 61         |  |  |

|   | 5.2 | The C                                  | CFM Cache Protocol                              | 63         |  |  |

|   |     | 5.2.1                                  | Hardware Configuration                          | 63         |  |  |

|   |     | 5.2.2                                  | Invalidation-Based Write-Back Protocol          | 65         |  |  |

|   |     | 5.2.3                                  | Primitive Operations                            | 67         |  |  |

|   |     | 5.2.4                                  | Autonomous Access Control                       | 69         |  |  |

|   | 5.3 | Synch                                  | ronization Supports                             | 71         |  |  |

|   |     | 5.3.1                                  | Synchronization Operations                      | 72         |  |  |

|   |     | 5.3.2                                  | Simple Lock/Unlock                              | 73         |  |  |

|   |     | 5.3.3                                  | Atomic Multiple Lock/Unlock                     | 76         |  |  |

|   | 5.4 | Scalab                                 | oility of the CFM Cache Protocol                | 78         |  |  |

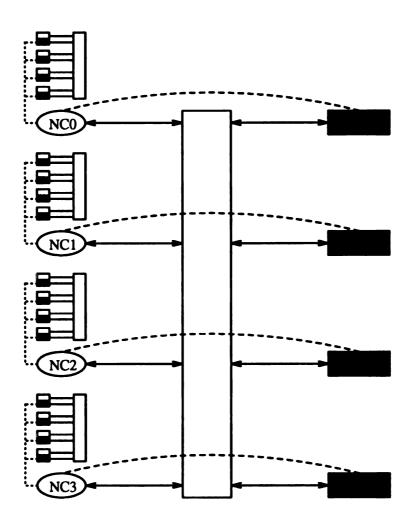

|   |     |                                        | A Hierarchical CFM Architecture                 | 78         |  |  |

|   |     | 5.4.2                                  | Scalable Write-Back Cache Protocol              | 80         |  |  |

|   |     | 5.4.3                                  | Other Issues of the Scalable Cache Protocol     | 82         |  |  |

|   |     | 5.4.4                                  | Performance of Hierarchical CFM Architectures   | 84         |  |  |

| 6 | тн  | E RE                                   | SOURCE BINDING PARALLEL PROGRAMMING             |            |  |  |

|   | PA: | RADIO                                  | GM                                              | 87         |  |  |

|   | 6.1 | Parall                                 | el Programming Paradigm Review                  | 88         |  |  |

|   |     | 6.1.1                                  | Locking Semaphores and Monitors                 | 88         |  |  |

|   |     | 612                                    | Message Passing                                 | an         |  |  |

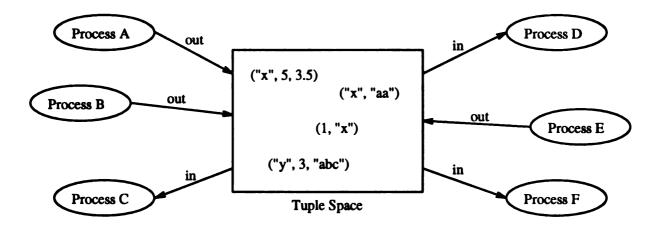

|   |      | 6.1.3  | Linda                                                    | 90  |

|---|------|--------|----------------------------------------------------------|-----|

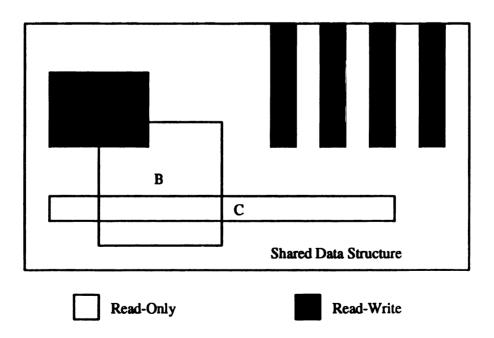

|   | 6.2  | The C  | Concept of Resource Binding                              | 92  |

|   |      | 6.2.1  | Managing Shared Resources in Parallel Processing Systems | 93  |

|   |      | 6.2.2  | The Fundamental Operations—Bind and Unbind               | 94  |

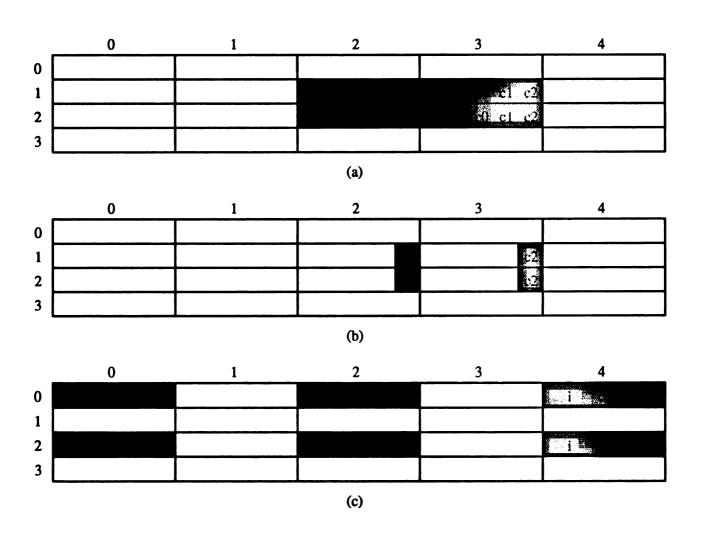

|   | 6.3  | Mana   | ging Shared Data Structures with Data Binding            | 97  |

|   |      | 6.3.1  | The Dining Philosophers Problem                          | 99  |

|   |      | 6.3.2  | Accessing Highly Overlapped Data Regions                 | 100 |

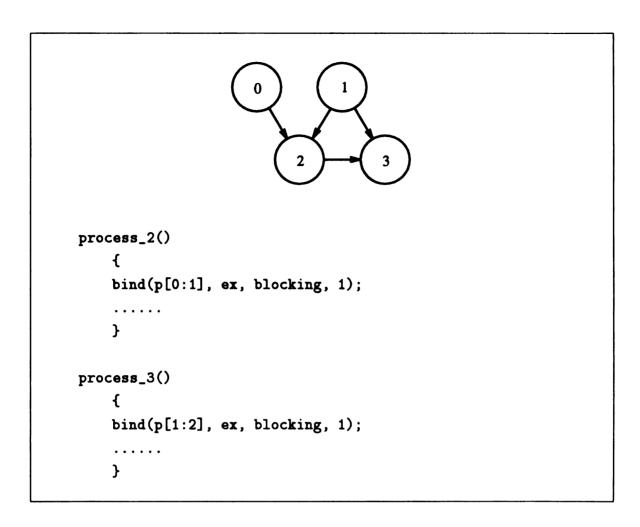

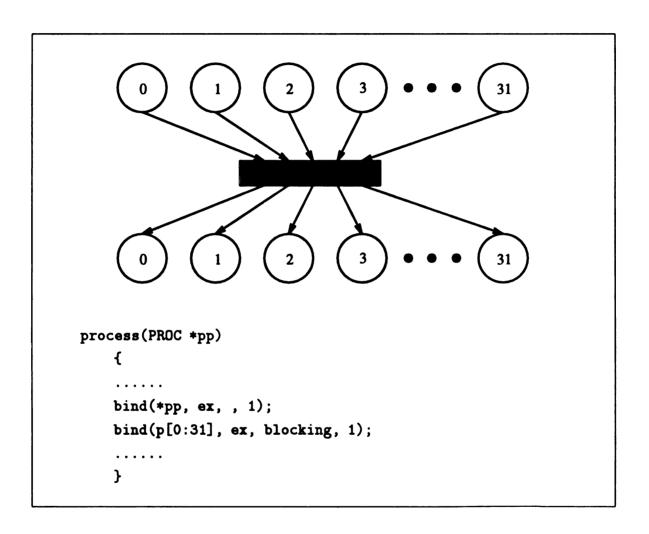

|   | 6.4  | Synch  | ronizing Processes with Process Binding                  | 103 |

|   |      | 6.4.1  | An Abstract Data Type for Concurrent Processes           | 105 |

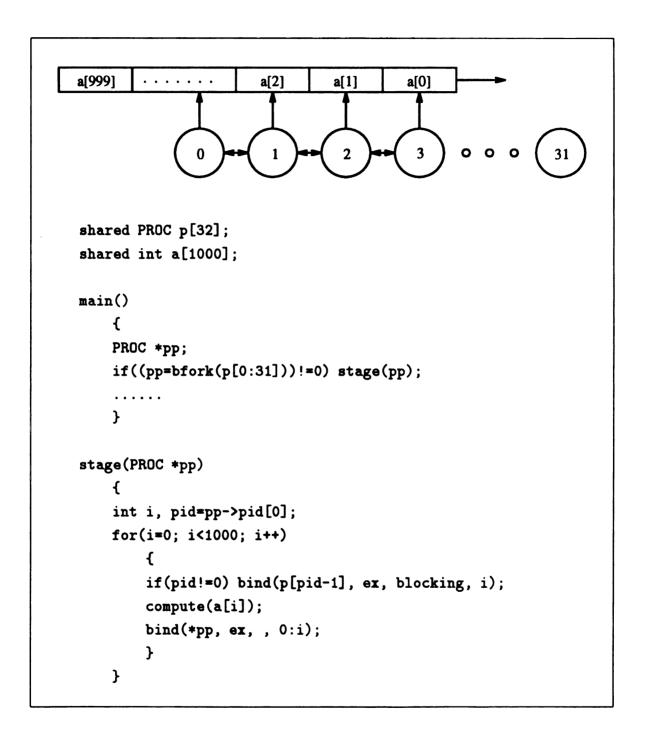

|   |      | 6.4.2  | Defining Process Dependency with Process Binding         | 106 |

|   |      | 6.4.3  | Illustrative Examples—Barrier and Pipelining             | 108 |

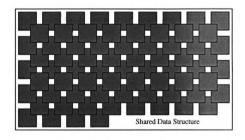

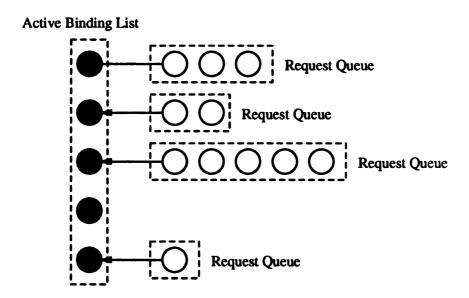

|   | 6.5  | Imple  | mentation Issues                                         | 111 |

|   |      | 6.5.1  | Shared-Memory Multiprocessors and the CFM Architecture . | 112 |

|   |      | 6.5.2  | Distributed-Memory Multiprocessors                       | 113 |

| 7 | СО   | NCLU   | SION AND FUTURE WORK                                     | 115 |

|   | 7.1  | Summ   | nary                                                     | 115 |

|   | 7.2  | Future | e Work                                                   | 118 |

| B | IBLI | OGRA   | PHY                                                      | 120 |

# LIST OF TABLES

| 3.1 | Address path connections                                        | 25 |

|-----|-----------------------------------------------------------------|----|

| 3.2 | Definition of notations                                         | 27 |

| 3.3 | Trade-off in the CFM configurations. $(\ell=256,c=2)$           | 28 |

| 3.4 | States of switches in an $8 \times 8$ synchronous omega network | 32 |

| 3.5 | Different configurations of a 64-bank multiprocessor            | 35 |

| 5.1 | Cache hits, misses, and corresponding actions                   | 67 |

| 5.2 | Access control among primitive operations                       | 69 |

| 5.3 | States of corresponding cache lines                             | 81 |

| 5.4 | Event priority in a network controller                          | 83 |

| 5.5 | Read latency of CFM and DASH                                    | 85 |

| 5.6 | Read latency of CFM and KSR1                                    | 86 |

# LIST OF FIGURES

| 1.1  | A typical distributed-memory multiprocessor                                   |

|------|-------------------------------------------------------------------------------|

| 1.2  | A typical shared-memory multiprocessor                                        |

| 2.1  | Tree saturation caused by a hot spot                                          |

| 2.2  | The Cedar architecture                                                        |

| 3.1  | AT-space and the accessible subset                                            |

| 3.2  | Mechanisms for non-stall block accesses                                       |

| 3.3  | Mutually exclusive subsets in AT-space                                        |

| 3.4  | A 4 × 4 synchronous switch box                                                |

| 3.5  | The CFM with memory bank cycle equal to 2 CPU cycles 24                       |

| 3.6  | The timing diagram of a read operation                                        |

| 3.7  | An 8 × 8 omega network                                                        |

| 3.8  | States of an 8 × 8 synchronous omega network                                  |

| 3.9  | Message headers of memory access requests                                     |

| 3.10 | Message headers of partially synchronous omega networks                       |

| 3.11 | Partially synchronous omega networks                                          |

| 3.12 | A system with two conflict-free clusters                                      |

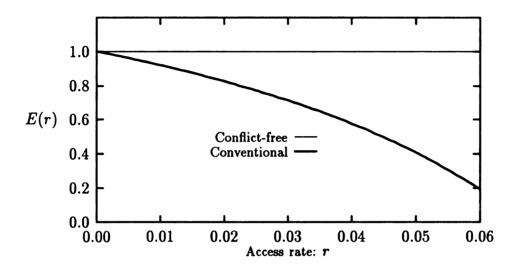

| 3.13 | Memory access efficiency. $(n = 8, m = 8, block size=16, \beta = 17)$ 39      |

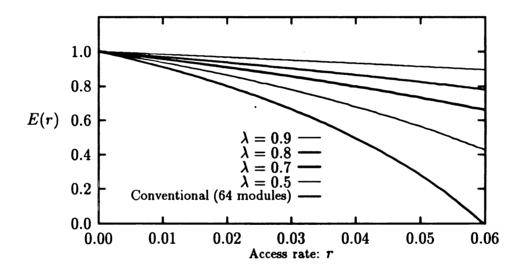

| 3.14 | Memory access efficiency. $(n = 64, m = 8, block size=16, \beta = 17)$ 41     |

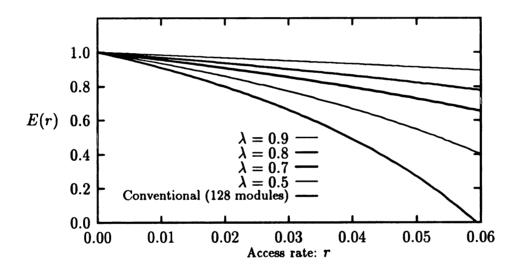

| 3.15 | Memory access efficiency. $(n = 128, m = 16, block size=16, \beta = 17)$ . 42 |

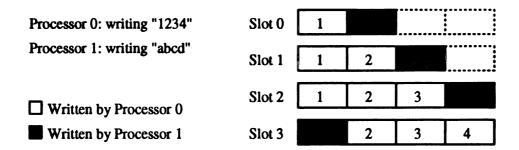

| 4.1  | A data inconsistency caused by the CFM architecture 46                        |

| 4.2  | The address tracking hardware configuration                                   |

| 4.3  | Write access control with address tracking                                    |

| 4.4  | Solving simultaneous same-address write problem                               |

| 4.5  | Read access control with address tracking                                     |

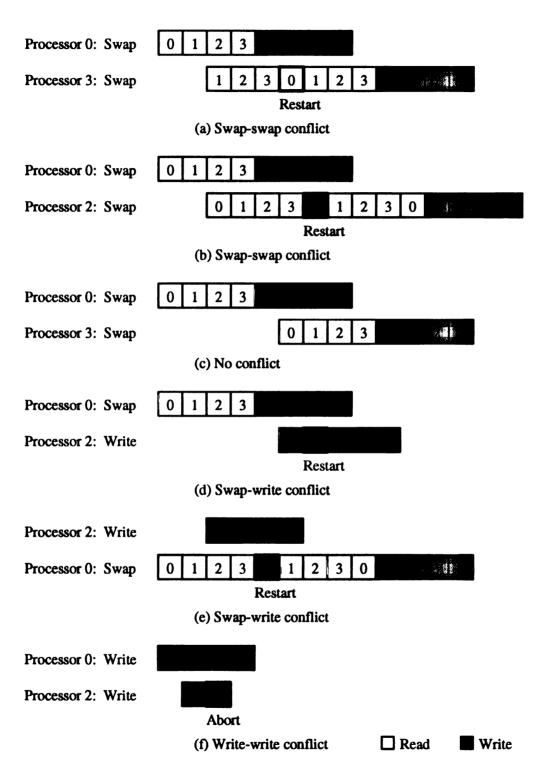

| 4.6  | Interaction among swap operations and write operations                        |

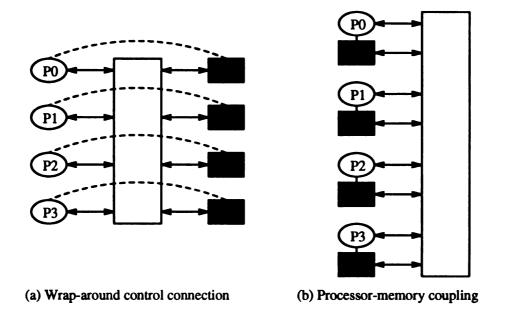

| 5.1  | Wrap-around control connection and processor-memory coupling 64               |

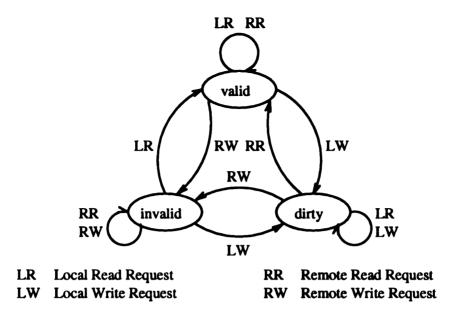

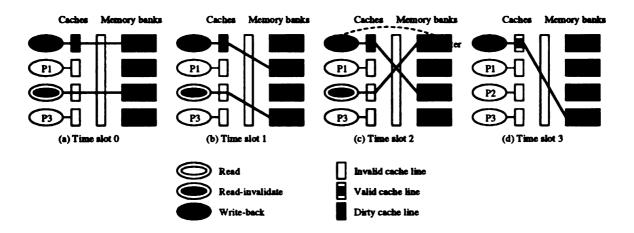

| 5.2  | Invalidation-based write-back protocol 65                                     |

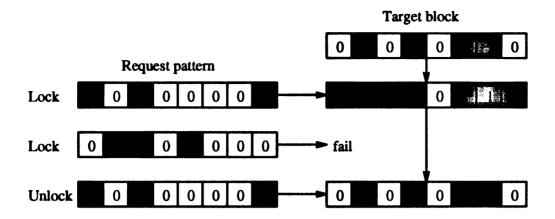

| 5.3  | Access control between a write-back and a read-invalidate              | 71   |

|------|------------------------------------------------------------------------|------|

| 5.4  | Lock transfer                                                          | 75   |

| 5.5  | Atomic multiple lock/unlock                                            | 76   |

| 5.6  | A hierarchical CFM architecture                                        | 79   |

| 6.1  | Linda processes and tuple space                                        | 91   |

| 6.2  | Shared data regions                                                    | 95   |

| 6.3  | Shared data regions in a structure type array                          | 98   |

| 6.4  | Solving dining philosophers problem with Linda                         | 101  |

| 6.5  | Solving dining philosophers problem with data binding                  | 102  |

| 6.6  | Highly overlapped data regions                                         | 102  |

| 6.7  | Accessing shared data regions with locking semaphores and data binding | .104 |

| 6.8  | Process dependency and process binding                                 | 107  |

| 6.9  | Barrier and process binding                                            | 109  |

| 6.10 | Pipelining processes                                                   | 110  |

| 6.11 | Resource binding implementation on a shared-memory multiprocessor.     | 112  |

## CHAPTER 1

# INTRODUCTION

Computer performance has dramatically progressed over the past decades, yet computer scientists have never stopped seeking new technologies for more performance improvement. Rapid IC technology improvements have increased both the number of components per chip and the circuit speed [1], which in turn have had a great impact on computer architecture designs. New technologies have not only enabled larger main memory sizes, but also allowed more powerful processors to be built. Processors have been designed with faster clock rates, more functional units, and higher degrees of pipelining. Furthermore, in order to compensate for the growing gap between processor speed and memory speed, caches have been widely used in improving memory access performance. Powerful processors with high bandwidth memory systems have become a common way of achieving high performance computation.

Besides powerful processors, multiprocessing is another approach to achieving high performance. Multiprocessors have been widely used in application areas which have high demand for computation performance. In a multiprocessor, applications are implemented with processes executing on multiple processors and cooperating with each other. It is hoped that, by using multiple processors, multiplied performance improvement can be obtained; however, ideal (or linear) speedup can hardly be achieved due to a number of performance degradation problems. The purpose of

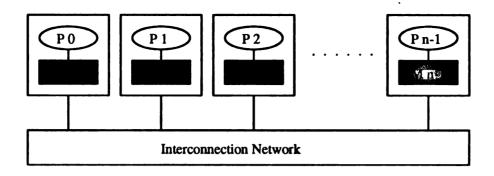

Figure 1.1. A typical distributed-memory multiprocessor.

this dissertation research is to improve multiprocessor performance by solving some of the most important performance degradation problems. This chapter first defines the basic categories of multiprocessors, namely, distributed-memory multiprocessors and shared-memory multiprocessors; states some performance degradation problems observed in these multiprocessors, and then gives an overview of the dissertation.

#### 1.1 Distributed-Memory Multiprocessors

Multiprocessor architectures can basically be divided into two categories, namely, distributed-memory systems and shared-memory systems. On a distributed-memory multiprocessor, the memory system is distributed among processors. Since there is no common memory directly accessible by more than one processor, processors communicate with each other through message-passing. Figure 1.1 presents a typical distributed-memory multiprocessor. As can be seen, each processor has a local memory module physically associated with it. Messages between processors are transferred through the interconnection network. The Intel iPSC [2] and the nCUBE [3] are two well-known examples of distributed-memory multiprocessors.

Distributed-memory multiprocessors have the advantage of scalability. Large scale systems can be built by replicating processor nodes, including their local memo-

ries, and increasing the interconnection network bandwidth. The performance of a distributed-memory multiprocessor, however, is dependent on the interconnection network latency. Modern distributed-memory multiprocessors employ network protocols, such as wormhole routing, which allow the network latency to be independent of the distance between two processor nodes. This enables large scale distributed-memory systems to be constructed without imposing too much penalty on network latencies. Performance degradation, however, can still result from contention in the interconnection network.

The major disadvantage of distributed-memory multiprocessors is in its programming difficulty. In a distributed-memory multiprocessor, messages must be passed back and forth among large numbers of processors. This increases programming complexity and severely limits efficient use of processor resources. In order to solve the problem, some approaches support shared-memory environments on top of physically distributed memory architectures. In such a system, shared memory accesses are handled by underlying network controllers and network switches through message-passing. Examples include the BBN Butterfly [4, 5], the NYU Ultracomputer [6], and the IBM RP3 [7]. These architectures are referred to as "logically shared-memory multiprocessors", and together with "physically shared-memory multiprocessors", which are to be discussed in the following section, are the focus of this dissertation.

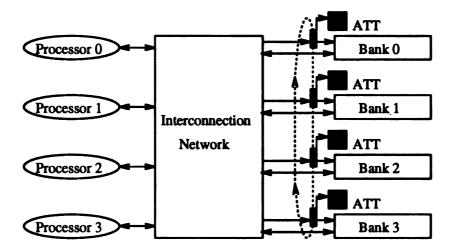

### 1.2 Shared-Memory Multiprocessors

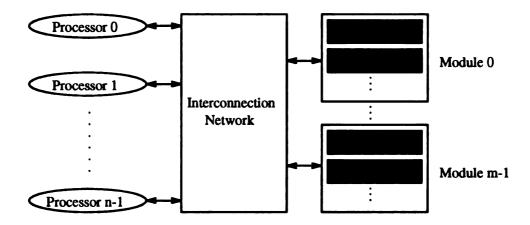

In a shared-memory multiprocessor, processes interact with each other through shared physical address space. Figure 1.2 shows a typical shared-memory multiprocessor, where a number of memory modules are equally accessible from all processors. The processors access the shared memory modules through an interconnection network. Accessing shared memory can cause contention, both in memory modules and in the

Figure 1.2. A typical shared-memory multiprocessor.

interconnection network, and decrease system performance. Additional overhead can also be introduced by network latency. Because of the comparatively long memory access latency in a multiprocessor, memory accesses are usually in blocks. Each memory block contains a number of memory words. In order to efficiently support block accesses, a memory module is usually composed of several memory banks. A memory word in this dissertation is defined as the data unit retrieved from or stored in a memory bank within one memory access, which can be one byte, two bytes, or other sizes.

In order to hide the long memory latency, there is usually a local cache installed with each processor. When accessing shared memory, processors usually talk to caches only, instead of directly accessing main memory modules. Blocks of data or instructions are transferred between caches and memory modules. In order to maintain cache coherence among processors, however, there may be some exceptions. While some multiprocessor designs force shared data to be non-cacheable and transferred in words instead of blocks, others employ the write-through protocol for cache coherence. Both approaches degrade system performance because of increased memory accesses and contention. Most recent approaches make everything cacheable and use

the write-back cache protocol. In such systems, memory accesses are always in blocks.

In order to distribute workload and reduce memory conflicts, addresses may be arranged in an interleaved fashion. For a block access, however, if the address assignment is interleaved across memory modules, a processor needs to access multiple modules. Accesses to the memory modules have to go through different paths, which further increase the network traffic and latency. In practical multiprocessor designs, the address assignment within each memory module is sequential; while, in order to increase performance, each module has multiple banks organized in an interleaved fashion. Either way, however, there is still network and memory contention.

As mentioned, memory access contention and interconnection network latency are two factors that degrade shared-memory multiprocessor performance. In addition to those, synchronization among concurrent processes can further decrease the performance. Consider the commonly used synchronization mechanism, lock/unlock. Multiple processors may concurrently and repeatedly access the same lock variable and create intensive memory and interconnection network contention. This results in the "hot spot" problem described in [8]. The contention problem and the hot spot problem will be discussed further in Section 2.1.

This dissertation focuses on the design, implementation, and other issues related to the physically shared-memory multiprocessors described in this section as well as the logically shared-memory multiprocessors mentioned in the previous section. From this point, the term "shared-memory multiprocessors" will be used to denote both logically and physically shared-memory multiprocessors.

#### 1.3 Dissertation Outline

This dissertation introduces the Conflict-Free Memory (CFM) architecture for multiprocessors [9]. Most memory system designs are based on word accesses. In contrast, the CFM architecture is based on block accesses. For multiprocessors within a certain scale range, the architecture eliminates memory and network contention as well as the hot spot problem without increasing latency and overhead. For large scale systems, the architecture improves system performance by reducing memory and network contention and increasing effective memory bandwidth and resource utilization. Moreover, it reduces the setup time and propagation delay caused by message routing in multiprocessors using MINs, such as the BBN Butterfly, the NYU Ultracomputer, and the IBM RP3. With an invalidation-based write-back cache protocol, the CFM architecture also efficiently supports high level process synchronization.

Chapter 2 addresses shared-memory design considerations for multiprocessors. It describes the contention problem found in shared-memory multiprocessors. A number of well-known multiprocessors are illustrated to demonstrate and evaluate several approaches to reducing or tolerating the contention problem. In addition, this chapter describes various memory consistency models that can be applied in multiprocessor designs.

In Chapter 3, the basic concept of the CFM architecture is introduced and a contention-free interconnection network that can be used in implementing the CFM architecture is presented. This chapter discusses various CFM configurations with different system parameters and their tradeoffs. In addition, it introduces a partially conflict-free extension to the basic CFM architecture for implementing larger scale multiprocessors. This chapter briefly analyzes the memory access efficiencies of partially conflict-free systems. A comparison between the efficiencies of conventional memory systems and partially conflict-free systems under different access rates and data localities is made. This chapter also discusses other performance issues, such as interconnection network overhead and memory access latency.

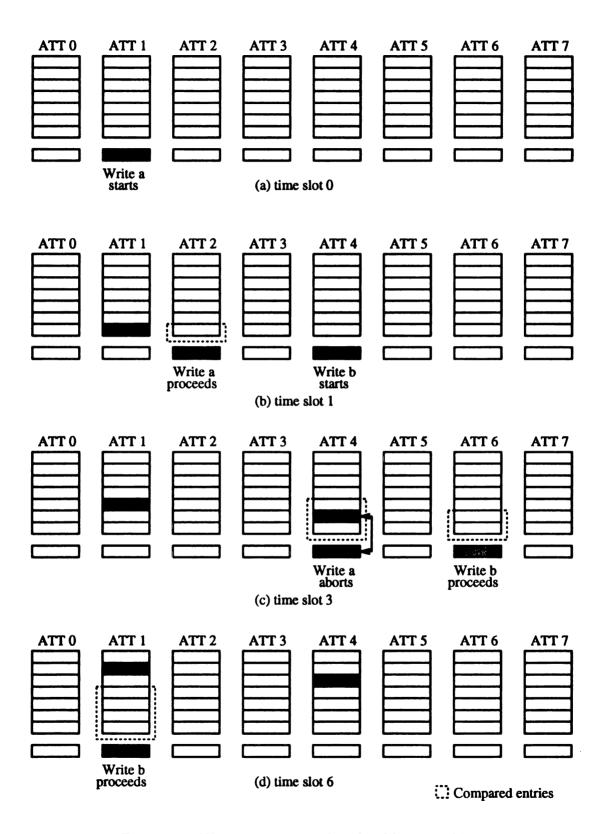

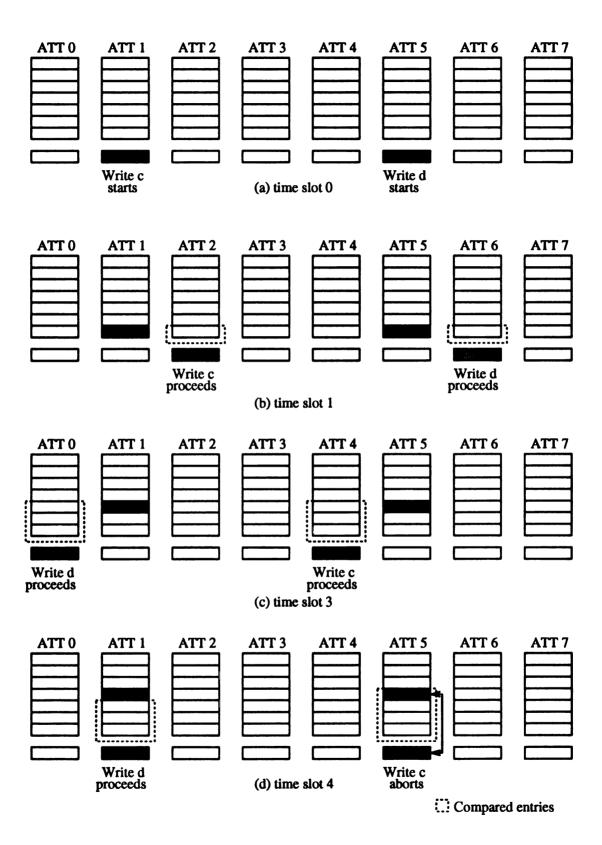

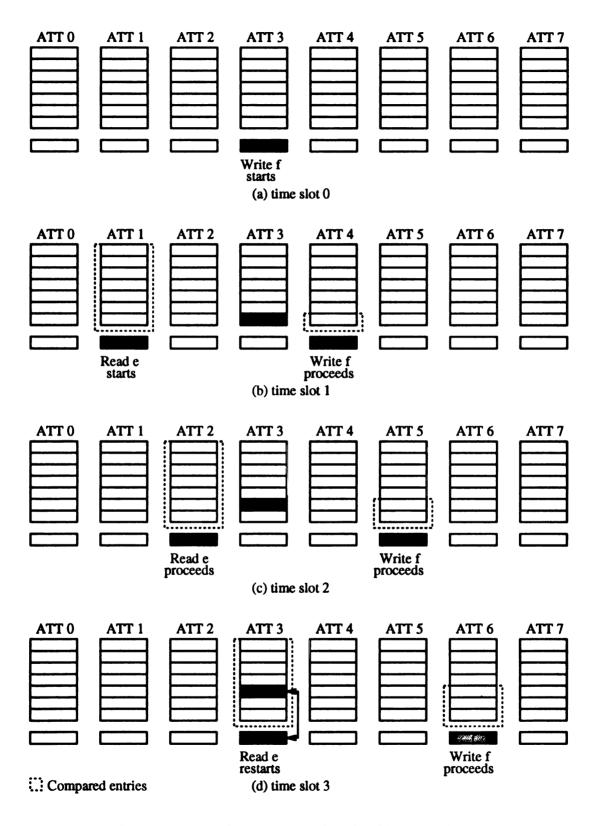

Chapter 4 presents a data inconsistency problem in the CFM architecture. It introduces an address tracking mechanism, which maintains data consistency among

concurrent accesses to the same memory block. The mechanism is also used to implement atomic operations, which in turn support higher level process synchronization.

Chapter 5, after reviewing some existing cache protocols, introduces the CFM cache coherence protocol. The new cache protocol is an invalidation-based write-back protocol. Based on the CFM cache protocol, synchronization operations can be implemented and can support weak consistency. Simple lock/unlock as well as atomic multiple locks can be implemented using the busy-waiting scheme with low overhead. Furthermore, the CFM cache protocol can be recursively scaled for large scale CFM extensions. This chapter demonstrates a hierarchical extension to both the CFM architecture and the cache coherence protocol.

Parallel programming is an important issue in achieving high performance computation in a parallel processing environment. Chapter 6 presents the portable parallel programming paradigm, resource binding [10], which can be efficiently implemented on the CFM architecture. The programming paradigm supports a flexible environment for parallel programming in various computation models. Moreover, the paradigm manages both data sharing and process synchronization in a consistent manner.

Chapter 7 is a summary of this dissertation. Major contributions of the research presented is highlighted. This chapter also lists interesting topics for future work.

## CHAPTER 2

# SHARED-MEMORY DESIGN CONSIDERATIONS

Resource contention and memory consistency models are two important issues in designing a shared-memory multiprocessor. The contention problem not only occurs in shared memory modules, but also in interconnection networks. Serious performance degradation can happen when the contention rate increases. In order to reduce or tolerate the effect of contention, various approaches have been applied by some multiprocessors and are reviewed in this chapter. Different memory consistency models explore parallelism from different perspectives. They can be implemented with various hardware complexity. This chapter also discusses several memory consistency models used in multiprocessor designs.

#### 2.1 The Contention Problem and Solutions

Shared-memory multiprocessors suffer memory conflicts when several processors access the same shared-memory module simultaneously. In a shared-memory multiprocessor, contention also occurs in the interconnection network. Examples include multiprocessors with *Multistage Interconnection Networks* (MIN) [4, 5, 11, 6, 7]. Both

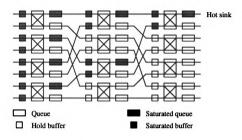

Figure 2.1. Tree saturation caused by a hot spot.

memory conflicts and interconnection network contention cause higher overhead and degrade system performance. Furthermore, the hot spot problem occurs when many processors try to access data in the same memory module or through the same network switch at a high rate [8]. This may be observed, for example, when several processors execute spin-lock on a single semaphore variable. In a MIN multiprocessor, the hot spot problem may result in the "tree saturation" effect, as shown in Figure 2.1. The highly contended hot sink can block its neighboring network switch buffers. The affected network switches can, in turn, block other network switches. Eventually, all memory accesses may incur considerable delays due to contention. This section presents several well-know multiprocessors and their approaches to solving the contention problem.

#### 2.1.1 The NYU Ultracomputer and the IBM RP3

The prevention or reduction of memory and network contention becomes a very important issue in achieving high speedup in multiprocessors. Numerous approaches have been implemented or proposed in order to solve the contention problem. For example, the NYU Ultracomputer and the IBM RP3, MIN-based multiprocessors, employ a combining network to reduce memory and network contention [6, 7]. They implement atomic fetch-and-add operations that can be combined at any switch of the interconnection network. In case two fetch-and-add operations from two different processors accessing the same memory location arrive at a switch about the same time, they can be combined, and only one memory access need to be completed at the memory location. Combining, however, can be applied only among operations that access the same memory location. This restriction limits the usage of the combining technique, as there may be accesses to different locations in the same memory module or accesses to the same location but several clocks apart in their arrival times. In either case, network or memory contention remains.

#### 2.1.2 The BBN Butterfly and Monarch

The Butterfly GP1000 and TC2000, built by BBN, are two other MIN-based multiprocessors [4, 5]. Both multiprocessors use circuit-switching in their interconnection networks. When a memory access request encounters memory or network contention, it is aborted and retried later rather than buffered at switches. This solves the tree saturation problem mentioned earlier. Since each memory access holds an entire path during its execution, the probability of network contention is increased. In order to reduce memory and network contention, the multiprocessors may provide alternative paths for memory accesses. Severe performance degradation due to contention, however, can still occur when shared memory access rate is high. Moreover, the circuit-switching network requires each conflicting memory access request to be retransmitted, which also increases the network overhead.

A variety of memory interleaving, skewing, and random mapping schemes have been developed to reduce contention in shared memory accesses. Some of these provide conflict-free access for a limited set of access patterns [12, 13], while others improve the average access performance [14, 15, 16]. The Monarch, a massively parallel processing computer being developed by BBN, is an example which applies random mapping on memory addresses to reduce memory and network contention [11]. The Monarch also employs read combining to reduce contention. In order to support the read combining, all memory accesses execute synchronously. Accessing requests are sent to memory banks in one cycle, and data returned in another. As a consequence, when a memory access is issued in a wrong cycle, a stall is required. The Monarch uses dual memory banks and double interconnection networks to increase memory bandwidth, which results in higher hardware cost.

#### 2.1.3 The OMP multiprocessor

Another example of a shared-memory multiprocessor is OMP, a RISC-based multiprocessor using orthogonal-access memories and multiple spanning buses [17]. In an n-processor OMP,  $n^2$  memory banks are arranged as an  $n \times n$  2-D mesh with the processors connected to the n diagonal locations. Memory access cycles are divided into two modes, row and column. All processors and memory banks are synchronized, so that they are all either in the row mode or in the column mode. The synchronous row and column access style prevents processors from interfering with each other, thus, no memory conflict may occur. The scheme, however, introduces long delays when a processor attempts a row or column access during a column or row mode, respectively. Furthermore, due to the long latency of an orthogonal memory access, each processor requires a local memory as well as a large register file and accesses the orthogonal memory in a DMA interrupt fashion. This causes the orthogonal memory to be more like a RAM-disk instead of a shared main memory. In order to support n processors, the multiprocessor requires  $n^2$  memory banks, which is also considered to be too expensive.

#### 2.1.4 The Cedar Project

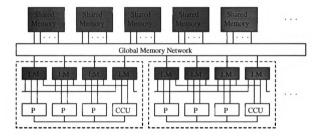

Cedar is a research project on parallel processing at the University of Illinois. The project has great emphasis on parallel software development techniques and tools, and a goal of developing a multigigaflops machine supporting a wide application range [18]. Figure 2.2 shows the Cedar architecture. Processors are grouped into clusters. Each processor has its local memory and can access the local memories of other processors in the same cluster through a high-speed switching network. Furthermore, there are global memories shared by processors in all clusters. Each processor can directly access global memories for data that are not in local memory through the global memory network.

Figure 2.2. The Cedar architecture.

As can be seen, the Cedar architecture allows a memory to be local to each processor, some memories to be shared within each cluster, and other memories to be globally accessible. This reduces memory latency for accesses that can be served locally or within a cluster, which also eliminates the traffic that can otherwise be introduced to the global memory network. Conflicts in the global memory and contention in

the global memory network can thus be reduced. The reduced memory latency and memory contention improve the overall performance, however, contention can still occur both within clusters and in the global memories and network.

#### 2.2 Memory Consistency Models

In order to bridge the growing gap between processor cycle times and memory cycle times, caches have been widely used in current multiprocessors. In cache-based multiprocessors, a protocol is required to maintain data consistency among replicated copies of shared writable data. Furthermore, memory accesses may be buffered and pipelined to reduce the effect of long memory access latencies. Without proper programming practice, these architectural optimizations can cause memory accesses to be executed in an order different from what the programmer expects. The set of allowable memory access orderings forms the memory consistency model for an architecture [19]. This section describes several memory consistency models, which include sequential consistency [20], processor consistency [21], weak consistency [22], and release consistency [19]. Chapter 5 will further introduce a cache coherence protocol which implements the weak consistency model.

#### 2.2.1 Sequential Consistency

Sequential consistency [20] requires the execution of a parallel program to appear as some interleaving of the execution of the parallel processes on a sequential machine. Before defining the sufficient conditions for sequential consistency, two definitions from Dubois et al. [22, 23] are presented below. In the following,  $P_i$  refers to processor i.

Definition 2.1 (Performing a Memory Request) A load by  $P_i$  is considered performed with respect to  $P_k$  at a point in time when the issuing of a store to the

same address by  $P_k$  cannot affect the value returned by the load. A store by  $P_i$  is considered performed with respect to  $P_k$  at a point in time when an issued load to the same address by  $P_k$  returns the value defined by this store (or a subsequent store to the same location). An access is performed when it is performed with respect to all processors.

Definition 2.2 (Performing a load Globally) A load is globally performed if it is performed and if the store that is the source of the returned value has been performed.

In the following discussion, the phrase "previous accesses" is used to denote accesses in the program order that is before the current access. Condition 2.1 presents sufficient conditions of sequential consistency [19].

#### Condition 2.1 (Conditions for Sequential Consistency)

- 1. before a load is allowed to perform with respect to any other processor, all previous load accesses must be globally performed and all previous store accesses must be performed, and

- 2. before a store is allowed to perform with respect to any other processor, all previous load accesses must be globally performed and all previous store accesses must be performed.

Sequential consistency imposes stricter limitation than the other consistency models discussed later. This prohibits some hardware optimizations for performance improvements that are allowed by those models.

#### 2.2.2 Processor Consistency

Processor consistency, introduced by Goodman [21], requires that stores issued from a processor must be observed in their issued order. It does not, however, require

stores from two processors to be observed in the same order by themselves or other processors. Processor consistency relies on programmers to use explicit synchronization rather than the memory system to guarantee strict event ordering. Conditions to satisfy processor consistency is shown in Condition 2.2 [19].

#### Condition 2.2 (Conditions for Processor Consistency)

- 1. before a load is allowed to perform with respect to any other processor, all previous load accesses must be performed, and

- 2. before a store is allowed to perform with respect to any other processor, all previous accesses (loads and stores) must be performed.

Processor consistency explores additional parallelism and improves performance by allowing a load access to perform before previously issued **store** accesses have been performed.

#### 2.2.3 Weak Consistency

Based on the assumption that critical memory accesses are regulated by programmers through synchronization points and critical sections, a weaker consistency model is defined. The weak consistency model requires that all synchronization accesses must be identified by programmers or compilers. With this reasonable programming requirement, weak consistency permits multiple memory accesses to be pipelined. The weak consistency model requires the following conditions to be satisfied [22, 19].

#### Condition 2.3 (Conditions for Weak Consistency)

1. before an ordinary load or store access is allowed to perform with respect to any other processor, all previous synchronization accesses must be performed, and

- 2. before a synchronization access is allowed to perform with respect to any other processor, all previous ordinary load or store accesses must be performed, and

- 3. synchronization accesses are sequentially consistent with respect to one another.

Weak consistency allows ordinary loads and stores within a critical section to be pipelined, which improves the performance of a multiprocessor.

#### 2.2.4 Release Consistency

Release consistency further relaxes the ordering requirements of memory events by dividing synchronization accesses into acquire and release accesses [19]. An acquire synchronization access is performed to gain access to a set of shared locations. A release synchronization access grants this permission. An acquire is accomplished by reading a shared location until an appropriate value is read. Thus, an acquire is always associated with a read synchronization access. Similarly, a release is always associated with a write synchronization access. Condition 2.4 lists the conditions to satisfy release consistency.

#### Condition 2.4 (Conditions for Release Consistency)

- 1. before an ordinary load or store access is allowed to perform with respect to any other processor, all previous acquire accesses must be performed, and

- 2. before a release access is allowed to perform with respect to any other processor, all previous ordinary load or store accesses must be performed, and

- 3. synchronization accesses are processor consistent with respect to one another.

In comparison to weak consistency, release consistency allows additional overlapping among ordinary accesses and synchronization accesses. First, ordinary load and store accesses following a release access do not have to wait for the release to complete. Second, an acquire synchronization access needs not be delayed for previous ordinary load and store accesses to be performed. Furthermore, synchronization accesses are only required to be processor consistent rather than sequentially consistent. One disadvantage of the release consistency model is the higher hardware complexity it requires. As an example, counters are required to maintain statuses of outstanding ordinary accesses and synchronization accesses.

# CHAPTER 3

# CONFLICT-FREE MEMORY

#### 3.1 The CFM Architecture

A memory module can be roughly characterized in three different dimensions, namely, address space, word width, and number of memory banks. Throughout this dissertation, the term, address space, refers to physical address space, which defines the total number of addressable elements in a memory module. It is limited by physical memory chips, address bus width, and interfacing schemes. A processor retrieves or stores a number of bits in one memory access. The number of bits processed in one access is defined as word width. In order to keep up with the fast speed of more and more powerful processors, multiple-bank memory modules have been developed and widely used. The number of memory banks defines the maximum number of memory addresses that can be accessed at one time, which along with other parameters specify the total bandwidth of a memory module. Due to conflicts in memory accesses, however, the effective memory bandwidth is usually lower. The rest of this section shows how the CFM architecture is designed to increase the effective memory bandwidth.

#### 3.1.1 The AT-Space and Block Accesses

Each of the three dimensions mentioned above characterizes the function or improves the performance of a memory device. One may start to wonder: can a fourth dimension be defined, and will it bring any new advantages to memory performance? The answers to both of these questions are "yes". As in most physics subjects, the fourth dimension of a memory device can be defined as the "time dimension". With the introduction of this new degree of freedom, conflicts among shared memory accesses in multiprocessors can be eliminated.

A conventional interleaved memory module can be viewed as a function, M, mapping from its address space A to the range of data elements D. A read operation in the memory module can be depicted by the function  $d = M(a \cdot b)$ , where d is the data retrieved, and  $a \cdot b$  denotes the memory address being accessed. The components a and b represent the address offset in a memory bank and the bank number, respectively. In case of two or more memory accesses to the same memory bank, there are memory conflicts, even if they are not to the same location.

As in a conventional interleaved memory module, an address in the CFM consists of its offset in a memory bank and the bank number. The bank number, however, is not part of the input to a memory access. Instead, it is defined by the time slot number in which the data is accessed. A time slot is usually the length of a CPU cycle. A constant number (usually the number of memory banks) of time slots compose a time period which characterizes the fourth dimension of the CFM architecture. The new memory function is now defined as a mapping from its address-time space AT to the range of data elements D. A read operation in this model can be described by the function  $d = M(a \cdot t)$ , where d is the content at the address offset a in the memory bank defined by the time slot t in which the data is accessed.

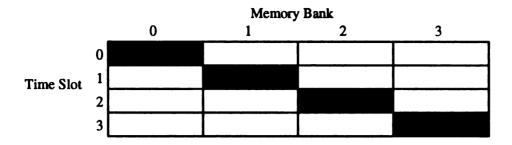

Figure 3.1 shows an AT-space with an address space distributed in four memory

Figure 3.1. AT-space and the accessible subset.

banks and a time period of four slots. Each shaded area denotes the memory bank defined by each time slot in the period. As can be seen, only a subset of the AT-space can be accessed within the time period. The blank areas simply represent the idle time slots of the memory banks. These may not be attractive to a single processor system with only one path between the CPU and the memory device. To a multi-processor with shared memory, however, the AT-space model offers an efficient way of eliminating shared memory conflicts among the processors. This will be explained later.

In this dissertation, each set of memory locations with the same offset in all the memory banks of a memory module is defined as a block, whose size is determined by cache line size. (Relationship or tradeoffs among block size, number of memory banks, and memory word width are discussed in Section 3.1.4.) Memory accesses in the CFM architecture are in blocks, each of which involves retrieving or storing words with the same offset from all memory banks. To simplify the discussion here, let us assume that the memory bank cycle is the same as the CPU cycle. Suppose that there are b memory banks, each block access takes b time slots. In a real case, the memory cycle is usually longer than the CPU cycle. The CFM design in such a case is explained later in this section.

It is important to note that a block access can start at any time slot. There is no delay required before starting a block access. This is because that a block access does

Figure 3.2. Mechanisms for non-stall block accesses.

not have to start at the first bank, instead, each access starts at the bank defined by the time slot in which the access request is received by the memory module. This avoids unnecessary stalls, which occur in the Monarch and the OMP when a memory access arrives at a memory bank in a wrong time phase. Figure 3.2 shows the mechanism which implements the block access style. The CPU and the memory banks are fully synchronized to ensure that each word of a block is transferred between its memory bank and the corresponding section of a CPU line buffer.

#### 3.1.2 Designing the CFM with AT-Space Partitioning

In a shared-memory multiprocessor with a single memory module, the processors share a single address space. Assume the memory module is composed of a number of memory banks. Memory conflicts occur when two or more processors access the same memory bank at the same time. Most of the memory conflicts are unnecessary and undesirable, since they are caused by processors accessing different locations in the same memory bank. These memory conflicts need to be eliminated in order to increase effective memory bandwidth. Some researchers have attempted to reduce memory conflicts by memory skewing or random mapping. In contrast, the CFM scheme presented here is based on a deterministic and highly synchronized model of

Figure 3.3. Mutually exclusive subsets in AT-space.

#### block accessing style.

With an appropriate partitioning of the AT-space, as shown in Figure 3.1, four mutually exclusive subsets of the space can be formed and assigned to four different processors in a multiprocessor. It is easy to show that, with such an assignment, the architecture guarantees conflict-free accesses to the shared memory. Figure 3.3 demonstrates a partitioning and an assignment of the AT-space. It is shown that, at time slot t, processor p can only access memory bank  $((t+p) \mod 4)$ , for  $0 \le t, p \le 3$ . With the mapping of the processor number p and the time slot t to the accessible memory bank b, each processor occupies an independent subset of the AT-space for a block access, and thus, the memory architecture is guaranteed to be conflict-free.

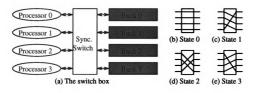

The above AT-space partitioning and mapping scheme can be implemented with a simple synchronous switch box. Figure 3.4a shows such a switch box with four input/output ports on each side, connecting four processors and four memory banks. The switch box is similar to an ordinary crossbar, but much simpler as it requires neither address decoding nor setup delay for routing decisions. Its four routing states, shown in Figures 3.4b, c, d and e, are driven by the system clock. At time slot t, input port i is connected to output port  $((t+i) \mod 4)$ , for all  $0 \le t, i \le 3$ . Every four CPU cycles, it completes a time period, which is totally deterministic. This mechanism implements the mutually exclusive partitioning and assignment of the

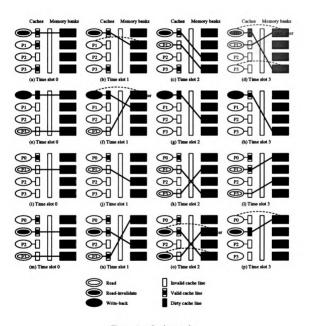

Figure 3.4. A  $4 \times 4$  synchronous switch box.

AT-space shown in Figure 3.3, which guarantees conflict-free block accesses. For example, at time slot 0, block accesses issued by processor 0 and 1 start retrieving or storing data in bank 0 and 1, respectively, without contention. During the middle of the accesses, at slot 2, a write operation issued by processor 3 can start storing data in bank 1 without interfering with the two accesses issued earlier. Section 3.2 shows how the synchronous switch can be extended to support larger and more complicated interconnection networks for conflict-free memory accesses.

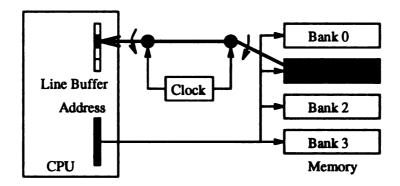

# 3.1.3 Constructing the CFM with Longer Memory Bank Cycle

The time required to complete a memory word access in a memory bank is defined as a memory bank cycle. In practical multiprocessors, a memory bank cycle is usually longer than a CPU cycle. Under such circumstances, designing the CFM architecture with the AT-space partitioning and assignment becomes infeasible. Since memory bank access cannot be finished within one time slot, the cost of a block access becomes too high. Consider a conventional memory module with multiple banks. The memory banks can be interleaved and accessed in a pipelined fashion. When an access is received by the memory module, the input address can be used by each of the memory banks. The memory banks start to process the request of continuous

Figure 3.5. The CFM with memory bank cycle equal to 2 CPU cycles.

addresses at different times. Eventually, the data from or to different banks will be piped through the interconnection network. The same concept can be applied to the CFM architecture.

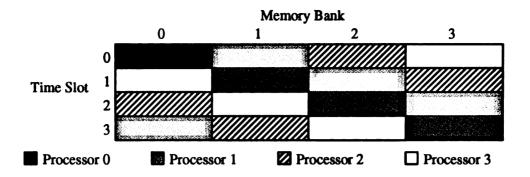

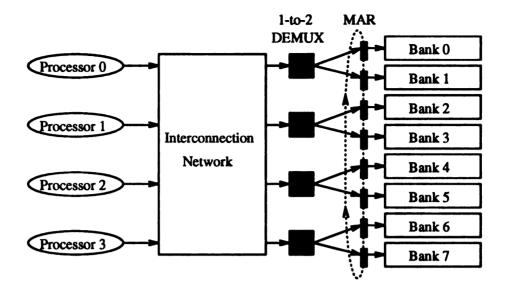

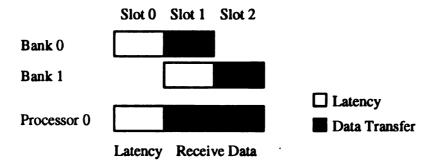

Figure 3.5 presents the organization of the CFM with memory bank cycle equal to two CPU cycles. For better readability, only address paths are shown in the figure. Data transfer can share a complicated bi-directional network with the address paths or be handled by a separate network. In order to reduce the speed gap between the processors and the memory banks, there are twice the number of memory banks as the number of processors. Besides the synchronous switch, there are a column of one-to-two demultiplexers between the switch and the memory banks. Like the switch, the demultiplexers are also driven by the system clock. The switch and the demultiplexers divide each time period into eight time slots for the four processors and the eight memory banks. The state transitions of the switch and the demultiplexers are arranged appropriately, so that, at time slot t, processor p is connected to memory bank ( $(t + 2p) \mod 8$ ), for all  $0 \le t \le 7$  and  $0 \le p \le 3$ . Table 3.1 presents the

address paths connected to the memory banks at different time slots. The data path connections are similar but shifted by one time slot.

Table 3.1. Address path connections.

|        | B0 | B1 | <b>B2</b> | <b>B3</b> | <b>B4</b> | <b>B</b> 5 | <b>B6</b> | B7 |

|--------|----|----|-----------|-----------|-----------|------------|-----------|----|

| Slot 0 | P0 |    | P1        |           | P2        |            | P3        |    |

| Slot 1 |    | P0 |           | P1        |           | P2         |           | P3 |

| Slot 2 | P3 |    | P0        |           | P1        |            | P2        |    |

| Slot 3 |    | P3 |           | P0        |           | P1         |           | P2 |

| Slot 4 | P2 |    | P3        |           | P0        |            | P1        |    |

| Slot 5 |    | P2 |           | P3        |           | P0         |           | P1 |

| Slot 6 | P1 |    | P2        |           | P3        |            | P0        |    |

| Slot 7 |    | P1 |           | P2        |           | P3         |           | P0 |

It can be seen that, at each time slot, an accessed memory bank is at least two banks away from any other accessed memory bank. The input address of each access can be shifted directly between the MARs (memory address registers) of the memory banks, instead of retransferred from the processors, as presented in Figure 3.5. These allow a memory access to be processed in a pipelined fashion, where a memory bank processing the second CPU cycle stage of an access can have its successor processing the first CPU cycle stage of the same access. The result is also transferred from or to the memory banks in a pipelined fashion which starts one time slot later than the access being issued. For example, if processor 0 issues a read operation at time slot 0, it will receive the retrieved data from memory banks 0 and 1 at slots 1 and 2, respectively. The timing diagram of this example is shown in Figure 3.6.

The concept can be extended to memory banks with longer cycles. Basically, for memory banks with an access cycle equal to c, the number of memory banks must be c times the number of processors. One-to-c demultiplexers are used with

Figure 3.6. The timing diagram of a read operation.

the synchronous interconnection network to connect the processors and the memory banks. For the purpose of simplicity, in the discussion of the following sections, the memory bank cycle is assumed to be identical to the CPU cycle. The number of memory banks is also assumed to be equal to the number of processors. The concept explained here, however, can be extended to all the examples mentioned later for practical situations.

#### 3.1.4 The CFM Configurations and Parameters

With respect to system parameters, the CFM architecture can be implemented in different configurations. These parameters include numbers of processors and memory banks, block size, memory word width, and memory bank cycle. Word width is defined as the number of bits retrieved or stored in one memory bank access. Table 3.2 shows the definition of a list of notations to be used in the following discussion.

Consider a system with n processors and b memory banks containing w-bit memory words. Since each block contains a memory word from each memory bank, the block (and cache line) size,  $\ell$ , can be defined as follows.

Table 3.2. Definition of notations.

| Notation       | Definition                            |

|----------------|---------------------------------------|

| n              | Number of processors                  |

| b              | Number of memory banks                |

| m              | Number of memory modules              |

| l              | Block (and cache line) size (in bits) |

| $oldsymbol{w}$ | Memory word width (in bits)           |

| c              | Memory bank cycle (in CPU cycles)     |

| β              | Block access time (in CPU cycles)     |

Assume each memory bank access takes c CPU cycles. In order to support conflict-free accesses, the number of memory banks needs to be c times the number of processors, as shown below.

$$b = cn$$

As a consequence, the number of processors that can be supported in the CFM system is

$$n = \frac{b}{c} = \frac{\ell}{cw}$$

It is shown that, with more memory banks and larger blocks, more processors can be supported for conflict-free accesses. Since the block size is defined to be identical to the cache line size, systems with larger cache lines can support more processors. Detailed study of the tradeoff between cache line size and system performance can be found in [24]. Some advanced processors have the tendency using large cache lines. For example, the cache line size in the Intel i860 processor is 32 bytes (256 bits), while the cache line size in the IBM RS/6000 is 128 bytes.

In order to retrieve or store a block of memory words, the memory banks cooperate in a pipelined fashion. The latency of a block access in the CFM architecture is the same as that of a conventional memory block access. The block access time,  $\beta$ , can

be computed as follows.

$$\beta = b + c - 1$$

As can be seen, when the number of memory banks increases, the block size and the block access time also increase. The number of memory banks needs to be limited in order to maintain appropriate cache line size and efficient conflict-free memory access. This presents a tradeoff between the memory latency and the number of processors that can be supported in the conflict-free system.

Table 3.3. Trade-off in the CFM configurations. ( $\ell = 256, c = 2$ )

| Memory banks | Word width | Memory latency | Processors |

|--------------|------------|----------------|------------|

| 256          | 1          | 257            | 128        |

| 128          | 2          | 129            | 64         |

| 64           | 4          | 65             | 32         |

| 32           | 8          | 33             | 16         |

| 16           | 16         | 17             | 8          |

| 8            | 32         | 9              | 4          |

To get a clearer idea about the tradeoff among the CFM configurations, let us define the block size  $\ell$  and the memory bank cycle c as constants. By decreasing the number of memory banks b and increasing the memory word width w, the memory latency for each block access can be reduced. The number of processors supported for conflict-free memory accesses, however, is reduced. Table 3.3 demonstrates the tradeoff observed in a system with cache line size  $\ell$  equal to 256 bits and memory bank cycle c equal to two. It is shown that, with smaller memory word width, more processors can be supported for conflict-free accesses. This is adequate for the practical situation since, in larger scale systems, data paths tend to be narrower due to higher connectivity between processors and memory banks. For example,

the Monarch with 64K processors uses one-bit serial data paths for shared memory accesses.

Although memory latency places a limitation on the number of processors that can be supported in the CFM configurations, there are ways to compensate the problem. First, cache line prefetching techniques implemented in some parallel compilers can be employed to reduce the effect of a long memory latency. The NYU Ultracomputer is an example of this approach [25]. Second, a partially conflict-free approach using the CFM concept can be used to support large scale multiprocessors without increasing memory latency. This approach groups memory banks into a number of memory modules with smaller blocks. Processors are also divided into several "contention sets". Each contention set is assigned a particular AT-space division for accessing the memory modules. A "conflict-free" cluster can be formed by selecting one processor from each of the contention sets. Processors in the cluster do not conflict with each other in accessing the memory modules as they are from different contention sets and use different AT-space divisions. With proper processor allocation and memory locality, this partially conflict-free approach can reduce memory and network contention to a minimum. The implementation issues of this approach is described in Section 3.2.2.

#### 3.2 Contention-Free Interconnection Networks

The synchronous switch box shown in Figure 3.4 serves as the interconnect between processors and memory banks for synchronous block accesses. Like all crossbar switches, however, it has a limitation on the number of I/O ports that can be connected to other devices. Crossbar interconnections are used on supercomputers and multiprocessors that have a limited number of processors and memory banks. For a system with a large number of processors, a more sophisticated interconnection

Figure 3.7. An  $8 \times 8$  omega network.

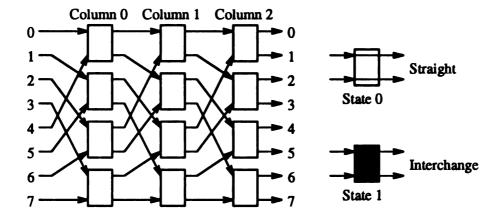

scheme is needed. Multistage Interconnection Network (MIN) is one of the widely used interconnection schemes in large scale multiprocessors [4, 5, 7]. The network is built by connecting a number of crossbar switches in a number of layers. Figure 3.7 shows an omega network, which is an example of MIN, and the possible states of its switches. Through circuit switching, messages can be routed and transferred by the intermediate switches between processors and memory banks. Memory accesses implemented with message passing in a MIN introduce routing and message header overhead. Moreover, contention encountered in switches also degrades effective memory bandwidth. To solve these problems, this section presents a synchronous interconnection network based on the omega network topology, which eliminates all possible switch contention as well as message passing overhead.

#### 3.2.1 Synchronous Omega Networks

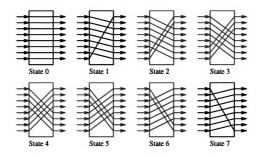

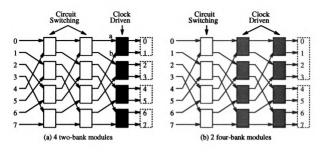

Like building circuit-switching omega networks with crossbar switches for conventional multiprocessors, synchronous omega networks can be built with synchronous switches for supporting contention-free interconnections. For example, an  $8 \times 8$  synchronous omega network can be built with  $12.2 \times 2$  synchronous switches arranged in

Figure 3.8. States of an  $8 \times 8$  synchronous omega network.

3 columns, as shown in Figure 3.7. The goal of building such a synchronous omega network is to support block accesses just as an ordinary  $8 \times 8$  synchronous switch does. The network should have a similar state transition pattern as a single switch, that is, at time slot t, input port p is mapped to output port  $((t + p) \mod 8)$ , for all  $0 \le t, i \le 7$ . It has been shown by Lawrie [26] that such mappings can be done with no contention.

Figure 3.8 presents the states of the  $8\times 8$  synchronous omega network. The connection state of the synchronous omega network fully depends on the state of each synchronous switch. The switches have two connection states: "straight" and "interchange", denoted by state 0 and 1, respectively. Table 3.4 shows the states of the switches at each time slot. Note that, since all the switches are synchronous, correct connection states for all switches can be set simultaneously for each time slot. There is neither setup time nor propagation delay required for the switches on a path. This is unlike the situations in the BBN Butterfly [4, 5] and the RP3 [7], where setup time and propagation delay are needed for routing and flow control.

Table 3.4. States of switches in an  $8 \times 8$  synchronous omega network.

| Column | 0 |   |   |   | 1 |   |   | 2 |   |   |   |   |

|--------|---|---|---|---|---|---|---|---|---|---|---|---|

| Switch | 0 | 1 | 2 | 3 | 0 | 1 | 2 | 3 | 0 | 1 | 2 | 3 |

| Slot 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Slot 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| Slot 2 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| Slot 3 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| Slot 4 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Slot 5 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| Slot 6 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| Slot 7 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

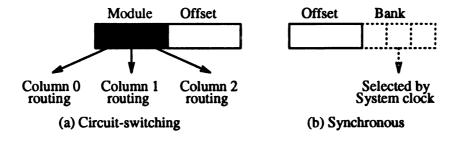

In a circuit-switching omega network, a memory address is represented by a memory module number and an offset. The memory module number is used by each switch column as routing information and required to be included in the header of each memory access request. While in a synchronous omega network, a memory address is composed of an offset and a memory bank number. Since all the switch routings are driven by the system clock, only the offset is required in the header of a memory access request. Figure 3.9 shows a comparison between the message headers used by a circuit-switching omega network and a synchronous omega network. It is clear that the new scheme reduces communication overhead by decreasing the message size of each memory access request.

Figure 3.9. Message headers of memory access requests.

#### 3.2.2 An Extension for Large Scale Multiprocessors

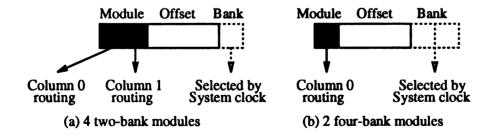

When the number of memory banks becomes larger, the block access style mentioned is no longer appropriate. Imagine a system with 64K processors and the same number of memory banks such as the Monarch [11], a block becomes too large to be efficient. By modifying the synchronous omega network mentioned above, however, memory banks can be grouped into a number of conflict-free memory modules with smaller blocks. Each memory module contains a continuous physical address space. Within each module, memory addresses are interleaved among memory banks and mutually exclusive AT-space division is maintained. This modified synchronous omega network supports partially conflict-free memory accesses.

In such a system, a memory address can be represented by a module number, an offset, and a bank number. Only the module number is used for routing, and only the module number and the offset are required in the message header of a memory access request. The bank number of a memory access is selected automatically by the system clock. Figures 3.10a and b show the memory addresses and message headers of a system with 4 two-bank memory modules and a system with 2 four-bank memory modules, respectively. The two-bank memory module system has two-word blocks, while the four-bank module system has four-word blocks.

Figure 3.10. Message headers of partially synchronous omega networks.

Figure 3.11. Partially synchronous omega networks.

To construct a system with 4 two-bank memory modules using  $2 \times 2$  switches, an omega network can be configured so that the first two columns are implemented with crossbars and the third column implemented with clock-driven synchronous switches. Figure 3.11a presents such a partially synchronous omega network. The first and second columns of the network are routed by circuit-switching, while the last column is controlled by the system clock. As can be seen, requests being sent to ports a and b can access memory banks 0 and 1 synchronously without contention, thus, banks 0 and 1 form a conflict-free memory module. The same concept applies to memory banks 2 and 3, 4 and 5, and 6 and 7. Since processors 0, 2, 4 and 6 always access banks 0 and 1 through port a and access other memory modules also through particular ports, they form a contention set. Likewise, processors 1, 3, 5 and 7 form another contention set. A conflict-free cluster can be formed by selecting one processor from each of the contention sets. This clustering mechanism reduces the block size into two words and supports partially conflict-free memory accesses.

Figure 3.11b shows another partially synchronous omega network which has only its first column switches routed by circuit-switching. Both the second and the last columns are controlled by the system clock. The network groups the memory banks into two conflict-free modules. The first module includes memory banks 0, 1, 2 and 3. The second module contains banks 4, 5, 6 and 7. According to access paths to these conflict-free memory modules, processors are divided into four contention sets: (0, 4), (1, 5), (2, 6), (3, 7). A conflict-free cluster can easily be formed by selecting one processor from each of the sets. The configuration reduces the block size into four words. It can be seen that, there is a tradeoff between the block size and the degree of conflict-free access. By adjusting the numbers of circuit-switching columns and clock-driven columns of the omega network, a multiprocessor can be configured with different block sizes. Table 3.5 illustrates possible configurations of a 64-bank multiprocessor implemented with  $2 \times 2$  switches.

Table 3.5. Different configurations of a 64-bank multiprocessor.

| Module | Bank | Block size | Circuit-switching | Clock-driven | Remark       |

|--------|------|------------|-------------------|--------------|--------------|

| 1      | 64   | 64 words   | 0 column          | 6 columns    | CFM          |

| 2      | 32   | 32 words   | 1 column          | 5 columns    |              |

| 4      | 16   | 16 words   | 2 columns         | 4 columns    |              |

| 8      | 8    | 8 words    | 3 columns         | 3 columns    |              |

| 16     | 4    | 4 words    | 4 columns         | 2 columns    |              |

| 32     | 2    | 2 words    | 5 columns         | 1 column     |              |

| 64     | 1    | 1 word     | 6 columns         | 0 column     | Conventional |

It is worth mentioning that, in some large scale multiprocessors, the CFM architecture can even be applied to memory word access. In an extremely large scale multiprocessor, due to the high connectivity between processors and memory banks, wide data paths are unlikely to be implemented in the interconnection network. Usually, a wide memory word is divided into several sections and transferred in several CPU cycles. In such a system, a block can be defined as identical to a memory word,

which is composed of data stored in a number of memory banks. The number of memory banks form a conflict-free memory module. For example, the Monarch uses bit-serial data paths in its interconnection network to transfer 64-bit memory words [11]. With the CFM architecture, each memory module can be composed of 64 memory banks, where each bank provides one-bit data, to support partially conflict-free memory word access with shorter latency than the Monarch.

#### 3.3 Other CFM Extensions

In addition to the omega network scheme, there are other solutions to extending the CFM concept for large scale multiprocessing. The CFM architecture mentioned have assumed the same or proportional number of processors, memory banks and time slots. In the CFM architecture, however, the number of processors can be less, leaving free slots for other purposes such as DMA and remote memory accesses.

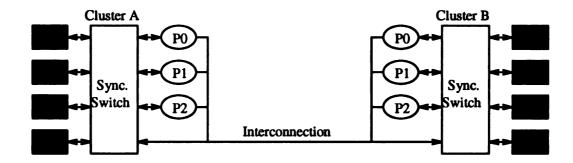

Figure 3.12 presents two CFM clusters connected to each other. Each CFM cluster has three processors and four memory banks supporting four time slots for conflict-free memory accesses. Since each cluster has one free time slot, the slot can be used to serve remote memory access requests from each other. For example, processor 0 in cluster A makes an access request to memory banks in cluster B. The request is sent to cluster B through a memory-mapped I/O port and the interconnection between the clusters. Upon receiving the request, cluster B serves as if it is an ordinary memory access from a local processor. The service does not introduce network and memory contention to cluster B, since it uses the free time slot. To processor 0, the remote memory access can be considered as just a "slower" regular memory access. Contention on the interconnection between clusters, however, is still possible.

The multiple-cluster connection scheme can be used to extend the CFM architecture for constructing multiprocessors with various scales, connectivity, and topologies.

Figure 3.12. A system with two conflict-free clusters.

These include hypercube, 2-D mesh, etc. Furthermore, A hierarchical extension approach will be presented in Chapter 5.4 after the introduction of a new cache coherence protocol for the CFM architecture.

#### 3.4 The CFM Performance

Performance of a multiprocessor is influenced by numerous factors. These factors include the nature of applications, computation models, and hardware architectures. From the architecture point of view, speedup can be limited by effective memory bandwidth, interconnection network overhead, and other parameters. The CFM architecture improves system performance by increasing effective memory bandwidth as well as reducing interconnection network overhead. This section gives a brief discussion about the impact of the CFM architecture on the performance of a multiprocessor.

#### 3.4.1 Efficiency of Conventional Memory Systems

Consider a conventional multiprocessor with n processors and m memory modules. Assume each processor uniformly generates memory accesses to the memory modules at a rate of r accesses per CPU cycle. All memory accesses are in blocks. Each memory module may consist of multiple banks to support pipelining for block accesses. Each block access takes  $\beta$  CPU cycles, where the value of  $\beta$  is dependent upon the block size and  $nr\beta \leq m$ . To a memory access, the probability that the target memory module is busy serving another access can roughly be computed as  $P(r) = \frac{(n-1)r\beta}{m}$ . Without considering interconnection network contention, a memory access request being sent to a memory module has the probability P(r) of conflict with other memory accesses. The expected number of retries is given below.

Expected number of retries

$$=\frac{1}{1-P(r)}-1=\frac{P(r)}{1-P(r)}$$

To simplify the model, assume each failed memory access consumes an average of  $\frac{\beta}{2}$  CPU cycles before a possibly successful retry. The expected time, M(r), it takes to complete a memory access can be approximated as follows:

$$M(r) = \beta + \frac{P(r)}{1 - P(r)} \times \frac{\beta}{2} = \frac{2 - P(r)}{2 - 2P(r)} \times \beta$$

The efficiency of memory accesses can be depicted by the following formula.

$$E(r) = \frac{\beta}{M(r)} = \frac{2 - 2P(r)}{2 - P(r)} = \frac{2m - 2(n-1)r\beta}{2m - (n-1)r\beta}$$

For example, suppose a multiprocessor has 8 processors and 8 memory modules. Each memory block contains 16 words. A block access takes 17 CPU cycles to complete. Figure 3.13 shows the efficiency of memory accesses under different memory access schemes and rates. In the case of conventional memory, as the access rate increases, the efficiency of memory accesses drops due to increased memory conflicts. Note that, because of interconnection network contention, the actual efficiency of the conventional memory is even lower than depicted in the figure. While in the CFM architecture, since both memory conflicts and network contention are eliminated, the

efficiency of memory accesses can roughly be thought of as 100%. It is clear that, when memory access rate is expected to be high, the CFM architecture is preferable.

Figure 3.13. Memory access efficiency.  $(n = 8, m = 8, block size=16, \beta = 17)$

### 3.4.2 Efficiency of the CFM Architecture