Ent we

LIBRARY

Michigan State

University

This is to certify that the

dissertation entitled

# APPLICATIONS OF LOGICAL CIRCUIT EXPRESSIONS TO CMOS VLSI DESIGN AUTOMATION presented by

Ching-Farn Eric Wu

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Computer Science

Major professor

Date 9/21/87

# APPLICATIONS OF LOGICAL CIRCUIT EXPRESSIONS TO CMOS VLSI DESIGN AUTOMATION

By

Ching-Farn Eric Wu

#### **A DISSERTATION**

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

**DOCTOR OF PHILOSOPHY**

Department of Computer Science Michigan State University East Lansing, MI 48824

#### **ABSTRACT**

# APPLICATIONS OF LOGICAL CIRCUIT EXPRESSIONS TO CMOS VLSI DESIGN AUTOMATION

By

Ching-Farn Eric Wu

CMOS technology has been recognized as a leading contender for existing VLSI systems, and is projected by industry analysts as being the dominant technology for the next decade. In this thesis, a novel approach for representing CMOS logic circuit networks at the transistor level is proposed. Unlike traditional device listing approaches which represent only circuit structures, this representation combines structural data with behavioral information, and thus illustrates a way to reduce the difficulty of information transformation between behavioral and structural representations for CMOS circuits.

Functional recognition of logic components is an important issue in circuit verification. A new method based on functional expansion and logical circuit expressions is proposed, and recognition rules are described. The success of logic component recognition can help other processes such as reverse engineering, which deals with extracting logic-level components from layouts of unknown-function circuits, and the comparison of CMOS transistor schematic networks. Functional recognition enhances the schematic comparison process in that it brings the comparison up to higher levels.

Traditional approaches which use graph matching algorithms for CMOS schematic comparison have difficulty in matching circuits with the same function but different topologies. Other approaches dealing with schematic

comparison such as switch-level simulation need to exercise all possible input patterns, require a large amount of time, and thus are not practical for medium-or large-sized circuits. The approach in this thesis for CMOS schematic comparison is to represent a CMOS transistor network by a set of logical circuit expressions, so that the comparison process is not as rigid as graph matching approaches and yet is efficient enough to compare two functionally isomorphic circuits. The shift from graph connectivity to logical circuit expressions allows schematics comparison for matching functionally isomorphic structures, while most graph-based approaches can handle only topologically isomorphic circuits.

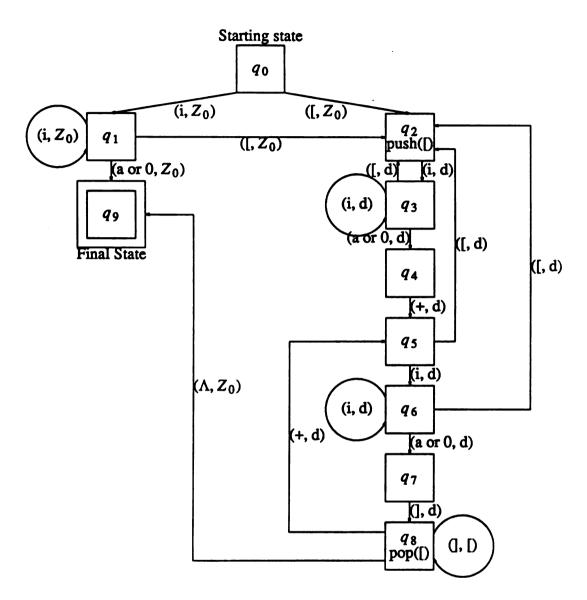

Automated CMOS design and verification using predicates is also described in this thesis. A context-free grammar and a pushdown automata are proposed so that the synthesis and verification processes for series-parallel networks can be done in linear time. ITP, an interactive theorem prover developed at Agonne National Laboratory, is used to demonstrate the capability of the approach.

To my parents and my wife

#### **ACKNOWLEDGEMENTS**

I would like to thank my advisor, Professor Lionel M. Ni, for his patient advice, guidence, inspiration, and continuing support which made this thesis possible. I am in debt to Professor Anthony S. Wojcik for providing me many ideas and valuable discussions of the ITP reasoning system. I am also grateful to other members of my Ph.D. committee, Professors George C. Stockman, Michael A. Shanblatt, and Shui-Nee Chow, for their valuable suggestions, encouragement, and comments.

My thanks are due to many other people in the department for indirectly contributing to this thesis through friendship and support throughout my stay in Michigan. Special thanks are due to my colleagues and friends, who have contributed in various ways to my graduate education here at Michigan State University. In particular, I would like to express my gratitude to Dr. T. B. Gendreau, now at Vanderbilt University, C. T. King, B. McMillin, T. Znati, J. Liao, and S. W. Chen, for their personal support, friendship, and concern.

Finally, I would like to thank my wife, Yew-Huey, for her support and everlasting love over the years.

The work described here was supported in part by the National Science Foundation under grants ECS-83-04967, DCR-86-96044, and in part by the State of Michigan REED Project.

### TABLE OF CONTENTS

| List of Tables                                    |    |

|---------------------------------------------------|----|

| List of Figures                                   | ix |

| Chapter 1 Introduction                            | 1  |

| 1.1. Y-Chart for VLSI Design                      | 2  |

| 1.2. Design Starting Point                        | 5  |

| 1.3. Motivation and Thesis Organization           | 9  |

| Chapter 2 CMOS Logic Structures and Design Styles | 11 |

| 2.1. Fully Complementary CMOS Logic               | 14 |

| 2.2. Clocked CMOS Logic                           | 18 |

| 2.3. Pseudo-nMOS Logic                            | 18 |

| 2.4. Dynamic CMOS Logic                           | 20 |

| 2.5. Domino CMOS Logic                            | 22 |

| 2.6. Cascade Voltage Switch                       | 24 |

| 2.7. Pass Transistor Logic                        | 26 |

| 2.8. Differential Pass Transistor Logic           | 27 |

| 2.9. Zipper CMOS                                  | 31 |

| 2.10. Design Styles                               | 37 |

| Chapter 3 Logical Circuit Expressions             | 42 |

| 3.1. Levels of Abstraction                        | 43 |

| 3.2. Series-Parallel Network                      | 46 |

| 3.3. Logical Circuit Representation               | 49 |

| 3.4. Generating Logical Circuit Expressions       | 58 |

| 3.4.1. Separating Nodes                           | 59 |

| 3.4.2. Nonseparable Components                                  | 66         |

|-----------------------------------------------------------------|------------|

| Chapter 4 Functional Recognition of Static CMOS Circuits        | 71         |

| 4.1. Previous Work                                              | <b>7</b> 3 |

| 4.2. Functional Expansion and Recognition Rules                 | 76         |

| 4.3. Static Logic Component recognition                         | 83         |

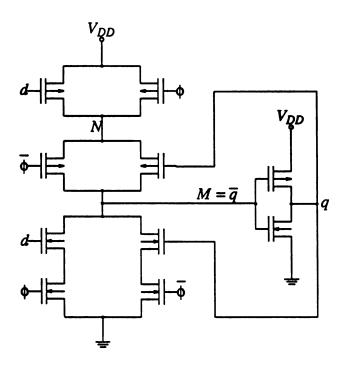

| 4.4. Recognition of Storage Cells                               | 86         |

| Chapter 5 Comparison of CMOS Transistor Schematic Networks      | 91         |

| 5.1. Functional Isomorphism                                     | 93         |

| 5.2. Comparison of Boolean Expressions                          | 99         |

| 5.3. Comparison Beyond Logic Structures                         | 101        |

| 5.4. Comparison Hierarchy and Binding                           | 102        |

| Chapter 6 CMOS Design and Verification Using Logical Predicates | 106        |

| 6.1. Using Logical Predicates                                   | 108        |

| 6.2. Formal Representation of CMOS Circuits                     | 113        |

| 6.3. Deterministic Pushdown Automata                            | 116        |

| 6.4. Automated Circuit Verification                             | 119        |

| 6.5. Automated Circuit Design                                   | 127        |

| Chapter 7 Conclusions                                           | 134        |

| 7.1. Summary                                                    | 134        |

| 7.2. Future Work                                                | 137        |

| Appendix                                                        | 139        |

| Pibliography                                                    | 1 4 4      |

## LIST OF TABLES

| Tabel 6.1. | A set of five logic predicates for CMOS circuit representation | 109 |

|------------|----------------------------------------------------------------|-----|

| Table 6.2. | State transition table for recognizing n-type networks         | 118 |

| Table 6.3. | Verification rules for FCMOS circuits                          | 121 |

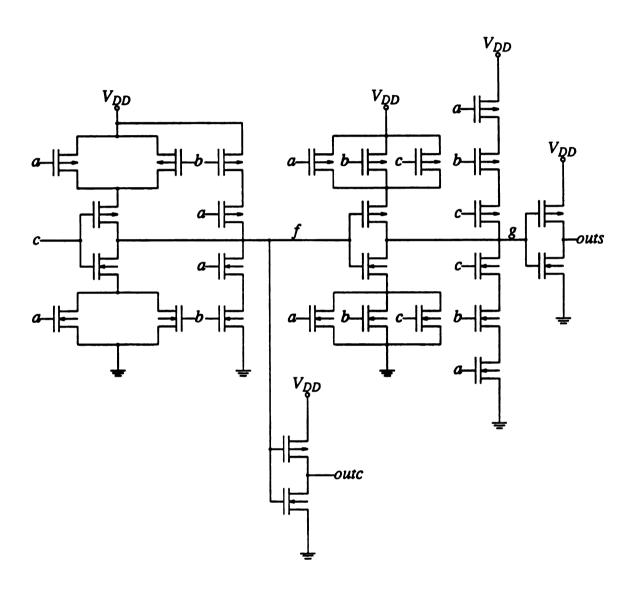

| Table 6.4. | ITP predicate statements of the circuit in Figure 6.6          | 124 |

| Table 6.5. | Demodulator list for the circuit in Figure 6.6                 | 125 |

| Table 6.6. | Metrics for verification of the one-bit full adder             | 126 |

## LIST OF FIGURES

| Figure 1.1.  | Y-chart representation of various design levels                                                                       | 3  |

|--------------|-----------------------------------------------------------------------------------------------------------------------|----|

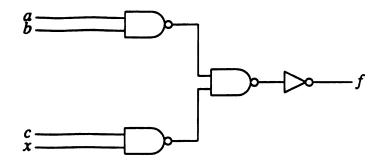

| Figure 1.2.  | Intuitive restricted gate-level design for function f                                                                 | 7  |

| Figure 1.3.  | Intuitive gate-level design for function f                                                                            | 7  |

| Figure 1.4.  | Minimized gate-level design for function f                                                                            | 8  |

| Figure 1.5.  | Compound gate design for function f                                                                                   | 8  |

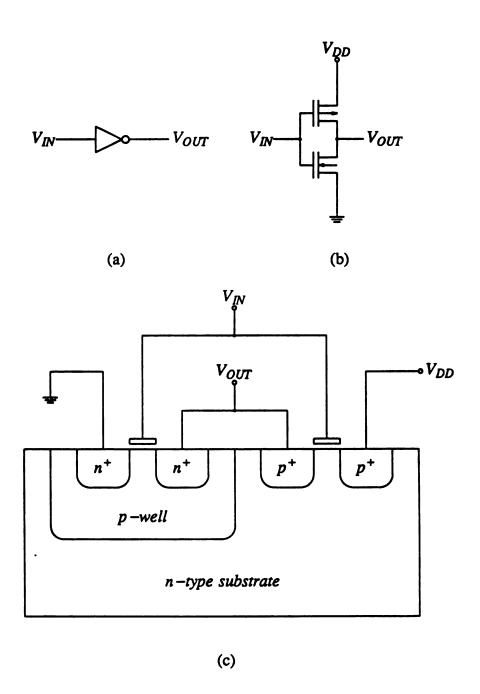

| Figure 2.1.  | A typical P-well CMOS inverter: (a) logic diagram, (b) transistor schematics, and (c) a simplified cross-section view | 13 |

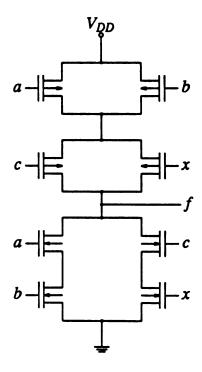

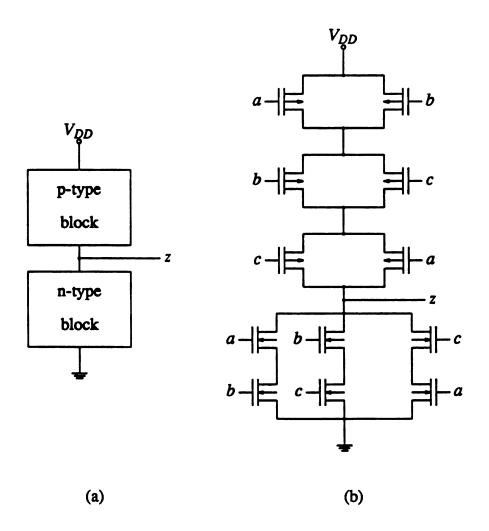

| Figure 2.2.  | Fully complementary CMOS logic: (a) block diagram, and (b) a CMOS gate implementing $z = \overline{ab + bc + ca}$     | 15 |

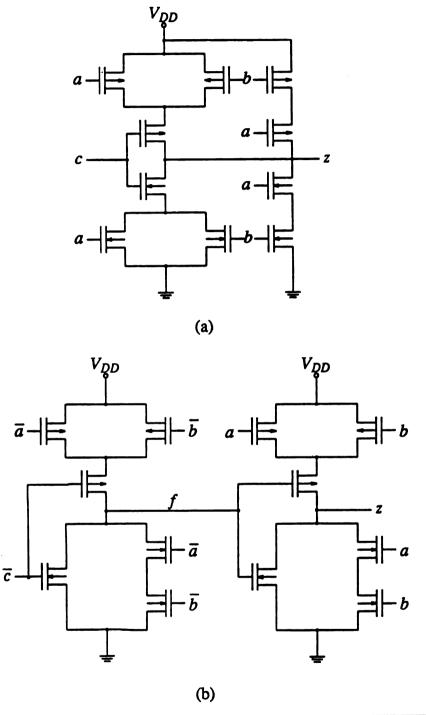

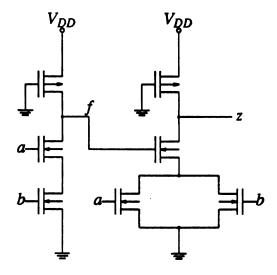

| Figure 2.3.  | (a) Non-complementary CMOS structure for $z = \overline{c(a+b) + ab}$ , and                                           |    |

|              | (b) multistage CMOS gates for $z = \overline{f + ab}$ , where $f = \overline{c} + \overline{ab}$                      | 17 |

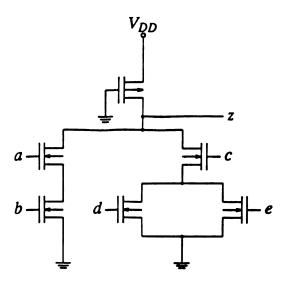

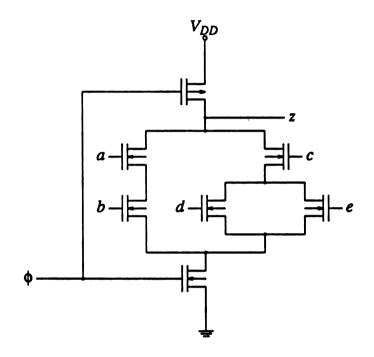

| Figure 2.4.  | A CMOS gate using clocked CMOS logic                                                                                  | 19 |

| Figure 2.5.  | A CMOS gate using pseudo-nMOS logic                                                                                   | 20 |

| Figure 2.6.  | A dynamic CMOS logic gate with clock signal φ                                                                         | 21 |

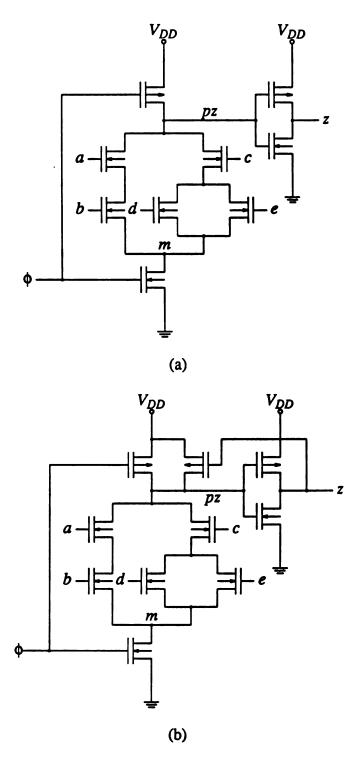

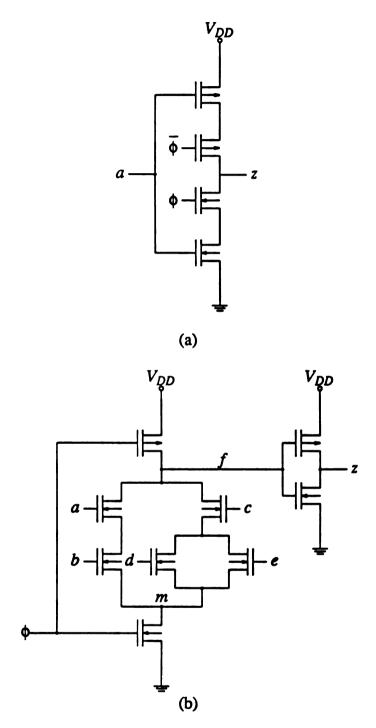

| Figure 2.7.  | Domino CMOS logic: (a) basic version, and (b) latching version                                                        | 23 |

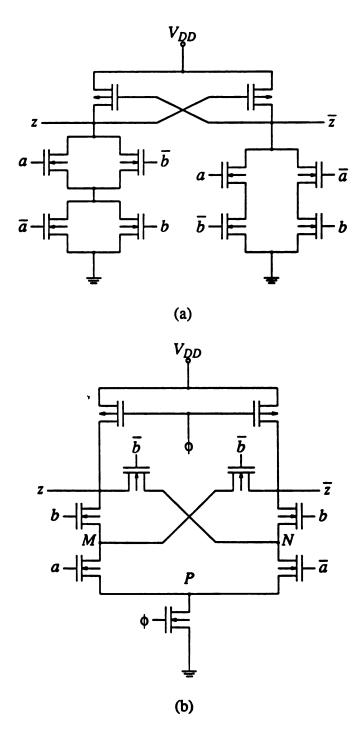

| Figure 2.8.  | Two-input DCVS XOR/XNOR circuits: (a) static and (b) clocked version                                                  | 25 |

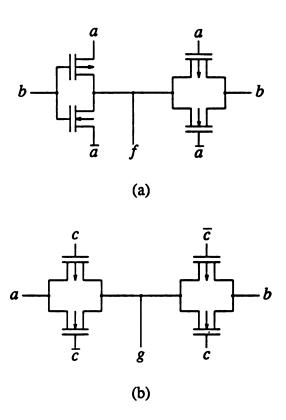

| Figure 2.9.  | Pass transistor logic: (a) a two-input CMOS XOR gate, and (b) a two-input CMOS multiplexer                            | 27 |

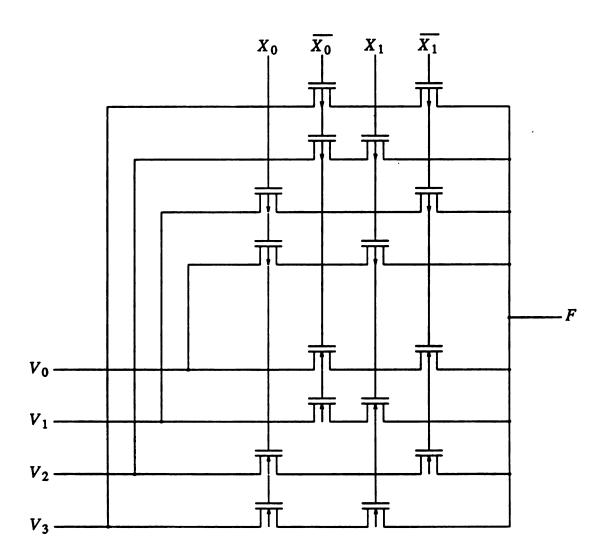

| Figure 2.10. | Conventional CMOS pass-transistor 4-to-1 selector circuit diagram                                                     | 29 |

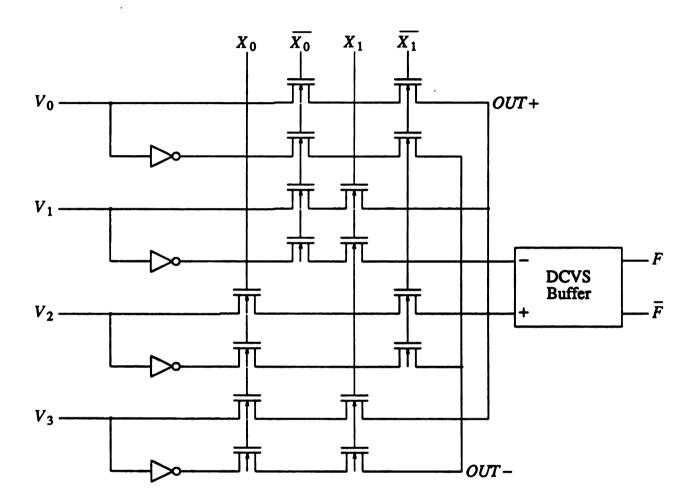

| Figure 2.11. | Differential pass-transistor 4-to-1 selector circuit diagram                                                          | 30 |

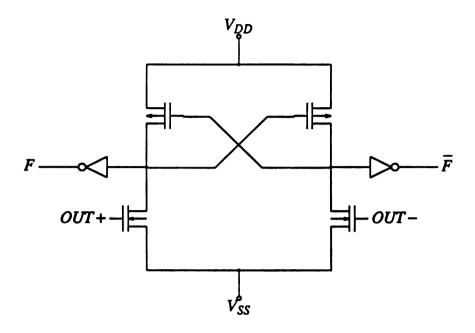

| Figure 2.12. | DCVS buffer used in differential pass transistor logic                                                                | 31 |

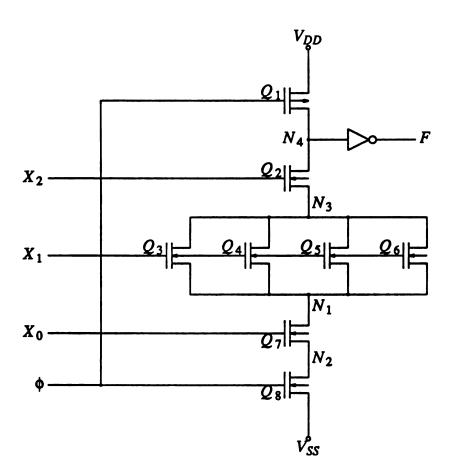

| Figure 2.13. | Charge sharing problem in dynamic CMOS and Domino CMOS logic                                                          | 33 |

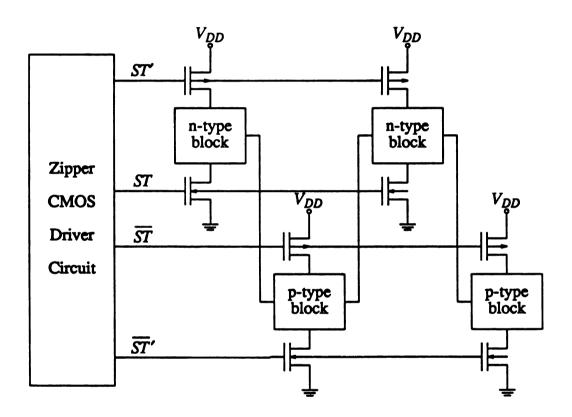

| Figure 2.14. | Zipper CMOS circuit structure                                                                                         | 35 |

| _            | Two stages in a (a) ZCMOS (b) FCMOS ripple carry chain                                                                | 36 |

| Figure 2.16. Semi-custom design styles: (a) gate array, (b) standard cell, and (c) macrocell                            | 38 |

|-------------------------------------------------------------------------------------------------------------------------|----|

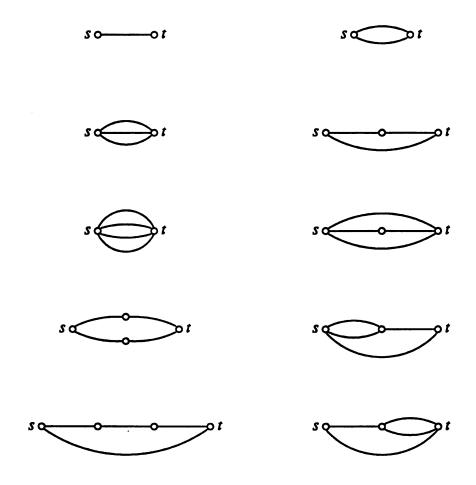

| Figure 3.1. A circuit with a Wheatstone bridge                                                                          |    |

|                                                                                                                         | 4  |

| Figure 3.2. Circuits with incomplete logic property: (a) a clocked CMOS inverter, and (b) a Domino CMOS gate            | 5  |

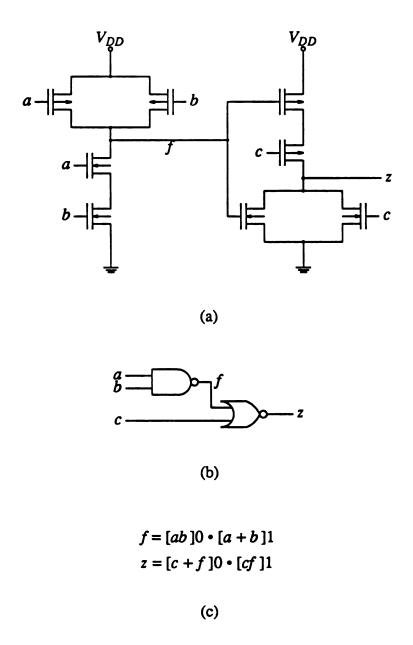

| Figure 3.3. A two-stage CMOS circuit: (a) transistor schematics, (b) logic diagram, and (c) logical circuit expressions | 5  |

| Figure 3.4. A CMOS decision-making circuit                                                                              | 5  |

| Figure 3.5. The virtual partitioning diagram of the circuit in Figure 3.3                                               | 6  |

| Figure 3.6. The virtual partitioning diagram of the circuit in Figure 3.4                                               | 6  |

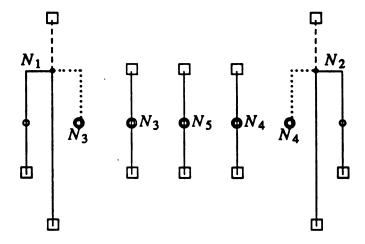

| Figure 3.7. A two-input asynchronous arbiter design                                                                     | 6  |

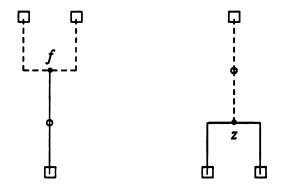

| Figure 3.8. Separating nodes for nonseparable components                                                                | 6  |

| Figure 3.9. Possible structures for a 2-terminal nonseparable component with less than 5 elements                       | 6  |

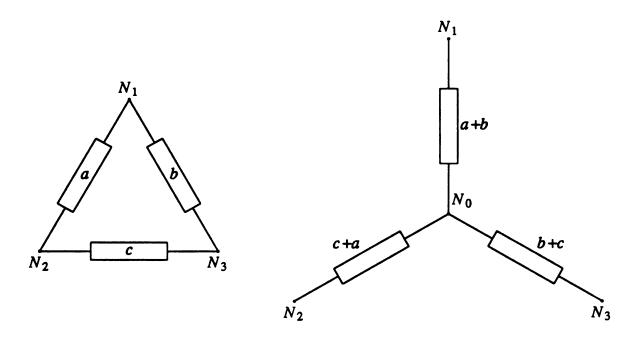

| Figure 3.10. Delta-to-wye (Δ-to-Y) transformation                                                                       | 6  |

| Figure 3.11. Wye-to-delta (Y-to-Δ) transformation                                                                       | 6  |

| Figure 3.12. Equivalent network by means of transformations                                                             | 7  |

| Figure 4.1. A pseudo-nMOS XNOR circuit                                                                                  | 8  |

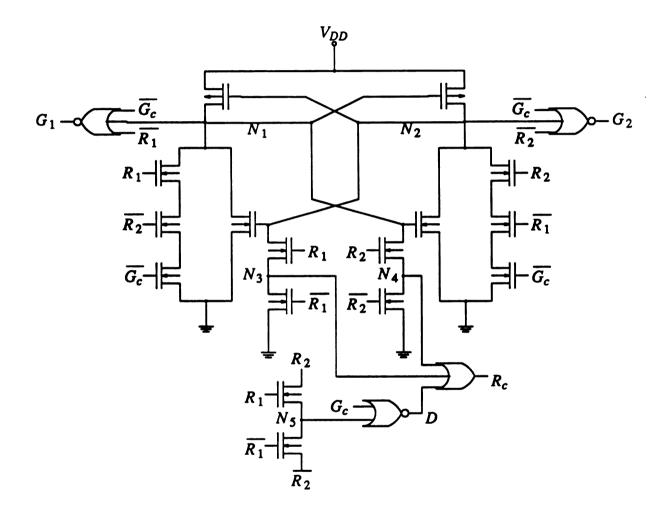

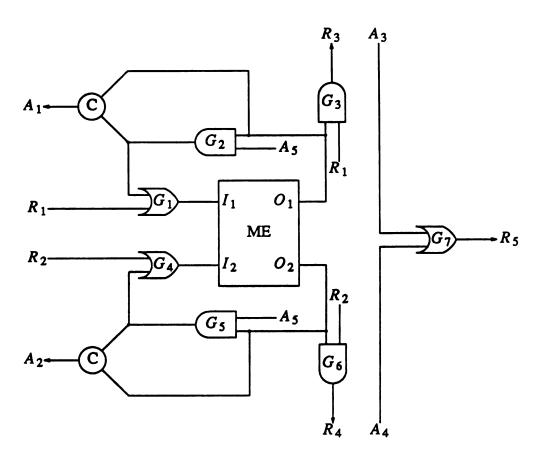

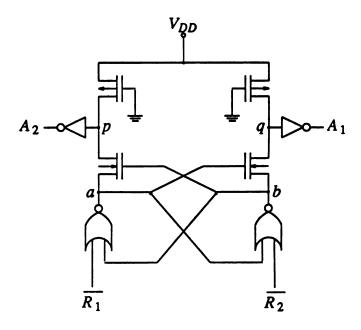

| Figure 4.2. A mutual exclusion element                                                                                  | 8  |

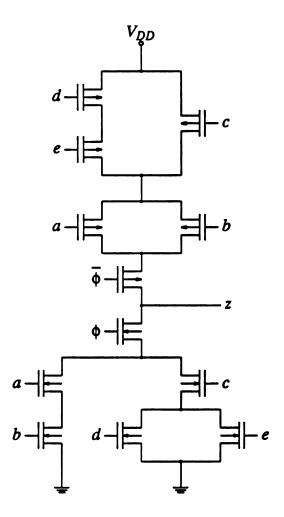

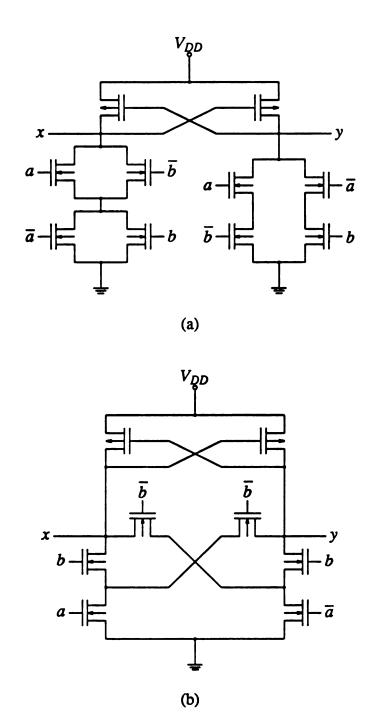

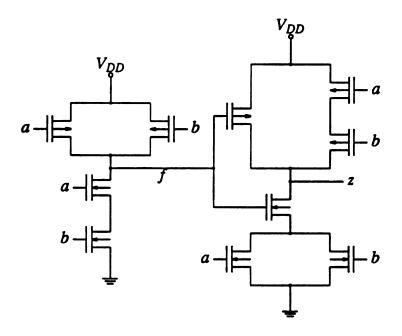

| Figure 4.3. Two 2-input DCVS XOR/XNOR gates with the same logical circuit expressions                                   | 8  |

| Figure 4.4. A pseudo-nMOS Muller-C element                                                                              |    |

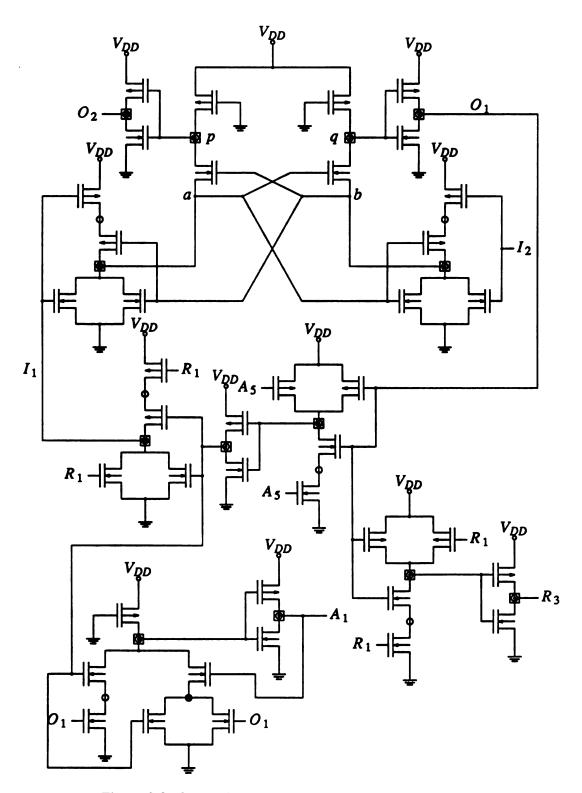

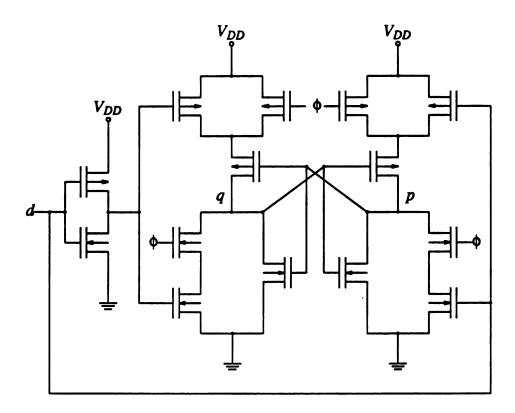

| Figure 4.5. Transistor schematics of a static CMOS D flip-flop                                                          |    |

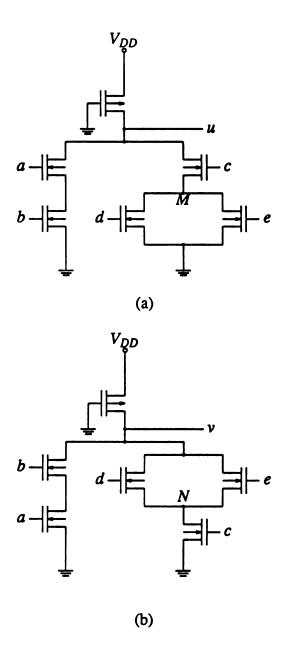

| Figure 5.1. Pseudo-nMOS gates through subcircuit permutation                                                            |    |

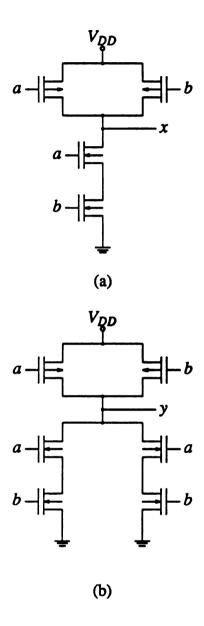

| Figure 5.2. Static CMOS NAND gates through subcircuit repetition                                                        | 9  |

| Figure 5.3. Pseudo-nMOS XOR gates through functional transformation                                                     | 9  |

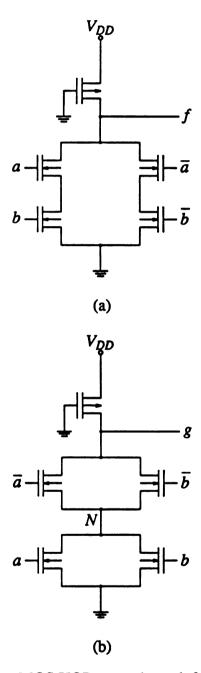

| Figure 5.4. A two-stage static CMOS XNOR gate                                                                           | 10 |

| Figure 5.5. A two-stage pseudo-nMOS XNOR gate                                                                           | 10 |

| Figure 6.1. An FCMOS gate implementing $z = \overline{ab + bc + ca}$                                                    |    |

| Figure 6.2. A pseudo-nMOS gate realizing $z = \overline{ab + cd}$                                                       |    |

| Figure 6.3. A Domino CMOS circuit with a clock signal \$\phi\$                                                          |    |

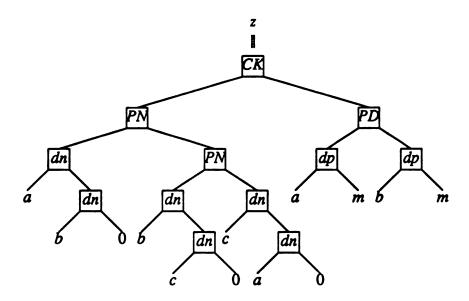

| Figure 6.4. The parse tree of node z in Figure 6.1                                                                      |    |

| Figure 6.5. State transition diagram for recognizing n-type transistor networks                                         |    |

| Figure 6.6. | Transistor schematics of a one-bit full adder                  | 123 |

|-------------|----------------------------------------------------------------|-----|

| Figure 6.7. | Alternative D flip-flop design using basic synthesis procedure | 132 |

#### **CHAPTER I**

#### INTRODUCTION

Recent advances in integrated circuit fabrication technology have increased the complexity of integrated circuits to such an extent that it is possible to fabricate a VLSI chip containing hundreds of thousands of transistors [Youn86]. The growth of IC complexity has had a dramatic impact on the time needed to design a circuit. The design methods which were adequate in the MSI and LSI periods require extensive improvement. In the early days of IC design, almost unlimited freedom was used in order to achieve the most compact results. This approach is no longer possible because the time complexity for solving the design and layout problems grows exponentially as the number of gates increases.

To tackle the complexity, automated design methods have become an indispensable tool for designing chips in a reasonable time frame. Many efforts have been devoted to various aspects of automated design and verification to reduce the design time and cost. Given that the process of designing a system on silicon is complicated, the role of VLSI design aids is to reduce this complexity and raise the level of confidence for the correctness of the design. Recently, VLSI design tools have been used in many ways to help reduce high design costs. VLSI design tools not only assist an engineer in circuit design, simulation, testing, and layout, but also help alleviate human errors caused by the manual design process. The average turn-around time has decreased significantly in the past ten years due to the use of automated tools.

On the other hand, in order to reduce the VLSI design burden and make the whole design process manageable, hierarchical design methods [Nies83] are usually considered

as a means of dealing with the VLSI design problem. The hierarchy, when properly implemented, is the self-evident implementation of the "divide and conquer" principle. The use of hierarchy involves dividing a chip into modules and repeating this operation on the modules until the complexity of a submodule is at an appropriate and comprehensible level of detail [Sequ83]. For instance, a chip may be decomposed into several modules with the I/O pads residing around the boundaries, and modules can be further decomposed into a number of cells.

In addition to hierarchical design methodology, circuit representation also plays an important role. Once a high-level specification is available, the design process can be viewed as a translation process from a higher-level description into a lower one.

#### 1.1. Y-Chart for VLSI Design

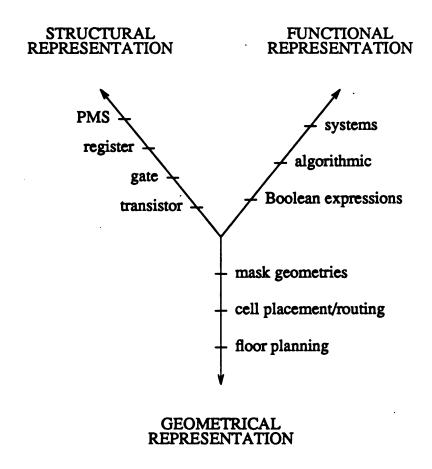

A tripartite representation for moving a design from a high-level specification to the low-level mask data has been proposed by Gajski and Kuhn [GaKu83]. The representation is partitioned into three sub-domains, namely, the functional (or behavioral) representation, the structural representation, and the geometrical representation. Multiple levels of detail are represented along each of the three axes. The levels of abstraction are increasing as one moves away from the vertex.

In the functional (or behavioral) domain one is interested in what the chip does and not how it is built. The design is treated as a black box with a specified set of inputs, a set of outputs and a set of functions describing the behavior of each output as a function of inputs and time. For example, the Boolean expression  $z = \overline{ab} + \overline{cd}$  indicates only the function of the design whose inputs are a, b, c, and d, and whose output is z. It does not say anything about the implementation or the structure of the cell. The functional representation of a design may be captured at several levels, such as systems,

Figure 1.1. Y-chart representation of various design levels

algorithmic, and Boolean expressions. The system or architectural description defines gross operational characteristics with performance specifications without being concerned about how data is manipulated or what algorithm is used. At the algorithmic level, the system may be represented using state transition diagrams. Variables or data structures are not bound to registers or memories at this level, and operations are not bound to any functional units or control state. For the logic level, Boolean expressions are chosen to represent the circuit function.

The structural representation is the bridge between the functional representation and

the geometrical representation. It is a mapping of a functional representation onto a set of components and connections under constraints such as cost, area, and time. This representation does not specify any physical parameters, such as the locations of circuit components and their sizes. In fact the structural representation specifies the connectivity among various components. The most commonly used levels of structural representation can be identified with the basic structural elements used. At the transistor level the basic elements are transistors, while gates and flip-flops are at the logic level. ALUs, registers, RAMs and ROMs can be used to represent structures at the register level, in which the communication among the components is of more concern than the implementation of each individual component. Processors, memories, and switches are used at the system level.

At the lowest level in this hierarchy, the geometrical representation deals with physical layout design. The geometrical representation ignores, as much as possible, what the design is supposed to do and binds its structure in space or to silicon. Components in the structural representation are built, placed, and interconnected using provided primitives. The structure-to-geometry mapping can be defined as a two step process. The first step, usually called symbolic or topological layout, determines relative or approximate positions for all structural elements. The absolute positions are determined in the second step after substitution of layouts for symbols and compaction. The most commonly used levels in geometric representation are mask geometries, cell placement/routing and floor planning with arbitrary size blocks. Cell placement/routing deals with the location of each individual cell and connections among those cells within a block, while floor planning is concerned with the placement of rectangular modules of varying sizes and shapes such that the required electrical performance can be achieved and the total area occupied by the modules and the interconnections is minimized.

#### 1.2. Design Starting Point

Based on the Y-chart representation, hierarchical design is an efficient approach to reduce the high design cost of a VLSI circuit. The design procedure for developing a chip can be entered at various starting points. In other words, it is the designer's responsibility to decide the entry point of the design process, which is an important factor in the tradeoff between the performance and design cost of the chip [VaSh85]. Since complementary metal oxide semiconductor (CMOS) technology has played an increasingly important role in the integrated circuit industry over the past several years, CMOS technology is selected in the following example to illustrate different starting points for designing a logic circuit.

Given a function f with a control signal C, assume  $f = \overline{ab}$  if C = 0 and  $f = \overline{x + ab}$  if C = 1. There are several different ways to implement the circuit using the prevalent CMOS technology.

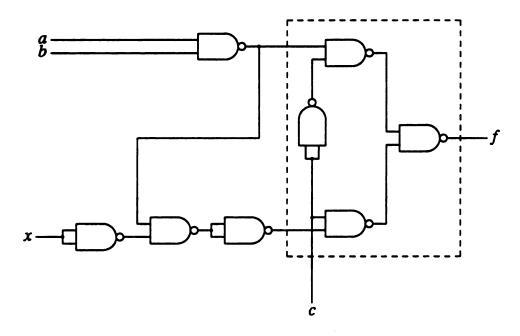

Intuitively one can use a two-input multiplexer and simple logic gates to implement the function f. However, in order to simplify the automated synthesis process, one might have only a limited number of available components, such as two-input NAND gates or four-input multiplexers. Thus the basic problem of circuit design becomes finding a way to connect those primitives so that the overall circuit behaves in the desired way [WoOL84]. Figure 1.2 shows a logic circuit with eight two-input NANDs, in which the two-input multiplexer is formed by four two-input NAND gates and the longest path contains five stages. A total of thirty-two transistors are used. Note that the logic circuit is not minimized.

By increasing the number of available components, one may be able to improve the design. If two-input multiplexers and simple logic gates are available in the designer's cell library, a simplified version of the same design can be obtained. Figure 1.3 shows

the circuit with one two-input multiplexer using pass transistor logic, one NAND, one NOR and one inverter. A total of sixteen transistors are used, and the number of stages along the longest path is three. If the chip area is proportional to the device count and the delay time of a circuit is proportional to the number of gates along the longest path [Hwan79], then the chip performance  $AT^2$  is improved by a factor of 5.5.

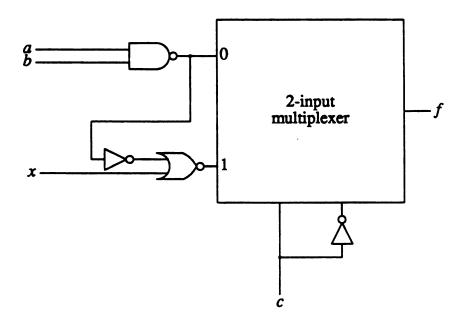

Logic minimization is another way to improve the circuit. Applying simple logic simplification rules, one notices that the function f is actually defined by  $\overline{ab + Cx}$ . Thus three NAND gates and one inverter are sufficient to build the circuit. Figure 1.4 shows the logic diagram of the simplified circuit. Fourteen transistors are used, and the number of stages along the longest path is only three. Thus, the chip performance is improved by another factor of 1.14.

If the transistor level is selected instead of the gate level as the entry point of the design, significant improvement can be achieved. Expertise at the transistor level is useful in realizing a better circuit structure. A compound gate whose output is f using true CMOS technology is shown in Figure 1.5. Only eight transistors are used. Since compound gates are basically one-level circuits, they also have significant improvement in terms of delay times. The delay time of such a circuit, estimated from SPICE [Oklo82], is about 1.5 times that of a standard 2-input CMOS NAND gate. Thus, the chip performance  $AT^2$  is further improved by a factor of 7.

In the best case, simple logic gates available in a VLSI standard cell library are locally optimized. Even with logic minimization at the gate level, a large number of transistors in a circuit are usually wasted because of the lack of a global viewpoint.

The key to moving beyond this local minimum is the expertise of lower level design, namely, transistor level expertise. The use of transistor level expertise significantly improves the chip performance. Knowledge at the transistor level is usually

Figure 1.2. Intuitive restricted gate-level design for function f

Figure 1.3. Intuitive gate-level design for function f

Figure 1.4. Minimized gate-level design for function f

Figure 1.5. Compound gate design for function f

used mainly inside the designers' cell library. This is true especially when standard cell design is used. In order to speed up the design process in the conventional design environment, designers usually use those cells they need from the cell library and interconnect them to form new custom circuits in spite of the sacrifice in the chip performance. The tools a designer might have are merely a collection of programs that perform logic minimization at the gate level, placement of selected components on the floor plan, and routing of the interconnections.

#### 1.3. Motivation And Thesis Organization

Since the designs at the transistor level usually result in smaller area and better performance, CMOS logic circuits are considered at the transistor level as the target area. The goal of this thesis is to find a CMOS circuit representation which combines both functional and structural information, so that the difficulty associated with information transformation between these two design domains can be reduced or released.

Once this representation is available, a practical problem which deals with CMOS schematic comparison becomes evident. Traditional approaches use either direct graph-matching algorithms or indirect switch-level simulation. As graph-matching algorithms suffer from rigid graph isomorphism checking, switch-level simulation suffers from tremendous computation overhead due to exhaustive exercises of input patterns and usually does not provide any information for error location. From the representation, an alternative is proposed and a better solution for CMOS schematic comparison may be obtained. One would also like to be able to recognize the logic functions of CMOS logic elements, so that the comparison can be performed at the Boolean level, and thus logic circuits with the same function but different topology may still be matched. In order to provide solutions for these problems, one needs a circuit partitioning scheme, and that is

where the idea for the logical circuit expressions arises.

In this thesis, a circuit representation for CMOS transistor networks is proposed and its applications to CMOS VLSI design automation is examined. After this introductory chapter, various CMOS logic structures and circuit design methodologies such as standard cell, gate array, and full-custom designs are described in Chapter 2. The approach to CMOS circuit representation, the Logical Circuit Expressions, is described in Chapter 3, along with approaches for generating logical circuit expressions. In Chapter 4, a novel approach to functional recognition for CMOS logic circuits based on logical circuit expressions and functional expansion is proposed. In addition to the contribution of recognizing logic functions of CMOS circuits, this approach also enhances the schematic comparison process in that it brings the comparison process up to the gate, or even, block level, provided that function recognition for individual or consecutive stages is successful. Chapter 5 shows how logical circuit expressions can be used for CMOS schematic comparison. Although it is different from the conventional direct and indirect approaches, it is shown that this approach gives more freedom when compared with the rigid graph-matching algorithms, and provides much more information when compared to switch-level simulation approaches. In Chapter 6 a rule-based system for automating CMOS design and verification using predicates is described. A context-free grammar and a pushdown automata are proposed so that the synthesis and verification processes for series-parallel networks can be done in linear time. ITP (Interactive Theorem Prover), which was developed at Agonne National Laboratory and written in Pascal, is used to demonstrate the capability of the approach. Finally, Chapter 7 concludes the thesis with a summary and directions for future research.

#### **CHAPTER II**

# CMOS LOGIC STRUCTURES AND DESIGN STYLES

Basically this chapter serves as common background for CMOS VLSI designs. The general characteristics of CMOS technology are described, various CMOS logic structures are examined, and several VLSI design styles are discussed. Both advantages and disadvantages of various CMOS logic structures and design styles are illustrated.

The technology of semiconductor devices is advancing at a rapid rate. Bipolar devices have been widely used for a long time. In general, bipolar transistors are characterized by lower ON resistances and higher current capabilities for a given size of device than are MOS devices. The most widely used semiconductor technology was TTL (Transistor-Transistor Logic). ECL (Emitter-Coupled Logic) and  $I^2L$  (Integrated Injection Logic) are also popular in some applications. To date, for most high-speed and low-noise applications, such as high-speed mainframe processors, bipolar technology is still used. However, the heat dissipation in bipolar circuits is rather large and requires an elaborate cooling arrangement for its operation.

The fastest growing technology has been MOS since the last decade. MOS transistors are known as FETs (Field-Effect Transistors) and are also referred to as MOSFETs. The MOS technology is growing dramatically fast because of high-volume commercial applications. The minimum feature size of MOS technology is decreasing rapidly, resulting in high-density complex custom chips with proven reliability of the two MOS technologies, nMOS and pMOS. CMOS is comprised of both n-type and p-type MOSFETs. To fully appreciate CMOS, it is necessary to understand the properties of MOS in general.

Detailed descriptions of MOS technology can be found in [MeCo80, HoJa83, GlDo85].

The nMOS technology has had some advantages in terms of size or area of silicon needed to produce equivalent functionality, but with decreasing feature size for CMOS, that advantage is rapidly evaporating. The past several years have seen a rapid shift in the technology of choice for high-complexity digital microelectronics from nMOS to CMOS. This shift has occurred because CMOS offers high performance at low power and scales extremely well to small feature size. The greatest advantage of CMOS over nMOS is its static power consumption, which is an order of magnitude smaller than nMOS static power requirements. CMOS technology has been recognized as a leading contender for existing VLSI systems, and is projected by industry analysts as being the dominant technology for the next decade [Mukh86]. It provides an inherently low power static circuit technology that has the capability of providing a lower power-delay product than comparable design-rule nMOS or pMOS technologies.

CMOS technology provides two types of transistors, an n-type transistor and a p-type transistor. These transistors are fabricated in silicon by using negatively doped silicon that is rich in electrons and positively doped silicon that is rich in holes, respectively. For the n-transistor, the structure consists of a section of p-type silicon separating two diffused areas of n-type silicon. The area separating the n regions is capped with a sandwich consisting of an insulator and a conducting electrode called a gate. Similarly, for the p-transistor, the structure consists of a section of n-type silicon separating two p-type diffused areas. Each transistor has two additional connections which are designated the drain and the source. In fact, the drain and source may be viewed as two switched terminals. The terminals are physically equivalent, and the name assignment depends on the direction of current flow [WeEs85]. Figure 2.1 shows a CMOS inverter with its logic diagram, transistor schematics, and a simplified cross-section view.

Figure 2.1. A typical P-well CMOS inverter: (a) logic diagram, (b) transistor schematics, and (c) a simplified cross-section view.

The use of both polarity devices on the same substrate creates various types of CMOS circuits. Many designers prefer to use static logic whenever possible to simplify their designs. On the other hand, dynamic CMOS circuits in which dynamic charges play an important role in circuit behavior usually results in significant area savings. In this chapter alternative CMOS logic configurations are examined and various approaches by which CMOS circuits are constructed are illustrated. The CMOS logic structures covered in this chapter are by no means complete; but through this chapter, one should be able to understand how a CMOS circuit works and how it is constructed.

#### 2.1. Fully Complementary CMOS Logic

Fully complementary CMOS (also referred to as FCMOS or true CMOS) logic is the most common logic structure. An FCMOS gate consists of a network of p-type transistors called the *load circuit* and a network of n-type transistors called the *driver circuit*. If an input combination for which the function realized by an FCMOS gate is to be 1 is applied, a path from  $V_{DD}$  to the output node of the gate is established through conducting p-type transistors, and all paths from output to  $V_{SS}$  through the n-type transistor network are cut off. Similarly, if an input combination for which the output of the gate is 0 is applied, a path from  $V_{SS}$  to the output is established through conducting n-type transistors, and all paths from output to  $V_{DD}$  are disconnected. Consequently, there is no static current path between  $V_{DD}$  and  $V_{SS}$ , and fully complementary CMOS ICs dissipate power only to charge and discharge circuit capacitance. Figure 2.2(a) shows the block diagram of a CMOS gate with p-type and n-type transistor networks, and Figure 2.2(b) shows a fully complementary CMOS gate which is used as the carry generator of a full adder.

Basically there are three different physical structures of fully complementary

Figure 2.2. Fully complementary CMOS logic: (a) block diagram, and (b) a CMOS gate implementing  $z = \overline{ab + bc + ca}$

CMOS combinational gates. Complementary CMOS structure refers to FCMOS gates whose p-type and n-type transistor networks are complementary in physical structure. Parallel n-type devices in the driver circuit imply serial p-type devices with the same gate signals in the load circuit, and serial n-type devices in the driver circuit imply parallel p-type devices with the same gate signals in the load circuit. The complementary CMOS structure is simple and has been widely used in many designs, especially for simple logic functions. The CMOS gate in Figure 2.2(b) which implements z = ab + bc + ca is a typical example.

Non-complementary CMOS structure refers to FCMOS gates whose p-type and n-type networks are not complementary in physical structure. Since both p-type and n-type transistor networks are separated from each other, they can be implemented independently in order to compact the physical layout. Thus, unnecessary long serial structures may be avoided. Figure 2.3(a) shows a fully complementary CMOS realization of the function  $z = \overline{ab + bc + ca}$ , in which p-type and n-type networks are symmetric instead of complementary in physical structure.

The third approach to implement Boolean functions using FCMOS logic is the use of multistage design. Compound gates are basically one-stage circuits. As the complexity of a logic function increases, the delay time of the gate also increases. Figure 2.3(b) shows two CMOS gates concatenated in series to implement the same function as the one in Figure 2.2(b). The output node z implements the function  $\overline{f+ab}$ , where  $f=\overline{ab}+\overline{c}=c(a+b)$ . Although it becomes a two-stage circuit with both true and complementary input signals, its first stage can be easily shared by other functions.

Figure 2.3. (a) Non-complementary CMOS structure for  $z = \overline{c(a+b) + ab}$ , and (b) multistage CMOS gates for  $z = \overline{f + ab}$ , where  $f = \overline{c} + \overline{ab}$

#### 2.2. Clocked CMOS Logic

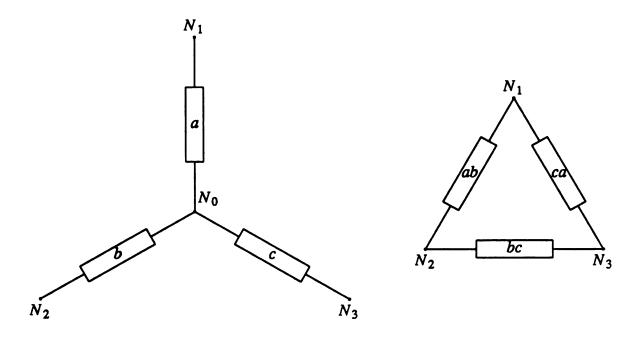

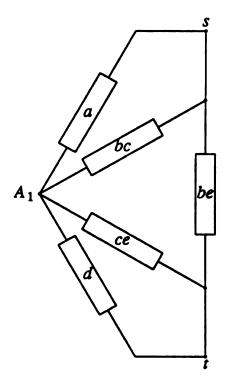

Clocked CMOS logic is a variant of the fully complementary CMOS logic. It was originally used to build low power dissipation CMOS circuits [SuOA73]. Since only part of a circuit is active at a time, it is not necessary to enable all logic gates all the time. By introducing a clock signal in the circuit, gates not in use can be cut off to reduce dynamic power consumption. Figure 2.4 shows a clocked CMOS compound gate which implements the function  $z = \overline{ab + c(d + e)}$ .

Gates using clocked CMOS logic have the same input capacitance as fully complementary CMOS gates but larger rise and fall times due to the series clocking transistors.

#### 2.3. Pseudo-nMOS Logic

A common criticism of CMOS is that equivalent CMOS circuits have more transistors than nMOS circuits. As a point of reference, CMOS designs are commonly quoted as being 20-30 percent larger than the nMOS equivalent designs [WeEs85]. This increase results from "logical redundancy" [MyIv85] — the need in fully complementary CMOS for evaluating the logic function and its complement to maintain good logic levels. Thus, circuits need two devices per logic variable in use, leading to area wasteful interconnections and a consequent degradation in performance.

Pseudo-nMOS is a CMOS variation which uses a p-type transistor to mimic an nMOS pull-up. The load device is a single p-type transistor, with the gate connected to  $V_{SS}$ . This structure is equivalent to a conventional nMOS gate except that the depletion nMOS load is replaced by a p-device. The design of this style of gate thus involves ratioed transistor sizes to ensure correct switching.

A typical pseudo-nMOS gate is shown in Figure 2.5, which performs the same func-

Figure 2.4. A CMOS gate using clocked CMOS logic

Figure 2.5. A CMOS gate using pseudo-nMOS logic

tion as the one in Figure 2.4, except that it is a static circuit. There is a definitive gain in area, but its low-to-high transition is slower and the static power consumption cancels the main advantage of CMOS technology. One possible advantage of the pMOS load is that it does not suffer from body effect as the nMOS depletion load does. Thus in a CMOS process it gives a method of emulating nMOS circuits.

### 2.4. Dynamic CMOS Logic

Dynamic CMOS gates require a precharge interval to generate dynamic charges at internal nodes. A basic dynamic CMOS gate is shown in Figure 2.6. It consists of an n-transistor logic structure whose output node is precharged to  $V_{DD}$  by a p-transistor in the precharge phase and conditionally discharged by an n-transistor connected to  $V_{SS}$  during the evaluate phase. Input signal  $\phi$  is a single phase clock. The precharge phase occurs when  $\phi = 0$ . The path to  $V_{SS}$  supply is closed via the n-transistor "ground switch"

during the evaluate phase when  $\phi = 1$ . The input capacitance of this gate is the same as the pseudo-nMOS gate shown in Figure 2.5. Its pull-up time is improved by virtue of the active switch, but the pull-down time is increased due to the ground switch.

Figure 2.6. A dynamic CMOS logic gate with clock signal  $\phi$

Precharged logic requires a clocking scheme which implies the need for some extra global control and communication. The inputs of a gate must remain steady once the precharge phase is finished. Simple single-phase dynamic CMOS gates, therefore, cannot be cascaded due to the conditional discharge at the output of the previous gate during the evaluate phase. A possible modification of dynamic CMOS logic is presented in [KrLL82], which leads to Domino CMOS logic.

Friedman and Liu [FrLi84] proposed another dynamic CMOS logic structure based on the direct interconnection of p-type logic and n-type logic dynamic gates. Adjacent

dynamic CMOS gates utilize complementary clock signals and complementary logic networks so that cascaded structures are allowed. Further improvements to dynamic CMOS logic use the forms of two and four phase logic that have been developed for earlier types of MOS design [MyIv85, WeEs85].

#### 2.5. Domino CMOS Logic

One of the best known approaches to the design of combinational logic in CMOS that avoids logical redundancy without suffering from the side effect of increased power dissipation is Domino CMOS logic. Domino CMOS circuits share some characteristics with dynamic circuits. In particular, each output is precharged high while the path to ground is opened, and the precharge is stopped while the path to ground is activated. Transitions from precharge to evaluation are accomplished by means of a single clock edge applied simultaneously to all gates in the circuit. This simplifies the clocking scheme and permits utilization of the full inherent speed of the gates.

A single Domino CMOS gate is depicted in Figure 2.7(a). It consists of a single phase dynamic gate and a static CMOS buffer. During precharge ( $\phi = 0$ ), the output node of the dynamic gate is precharged high and the output of the buffer is low. As subsequent logic stages are fed from this buffer, transistors in subsequent logic blocks will be turned off during the precharge phase. In addition, during evaluation, a Domino gate can make only a single transition ( $0 \rightarrow 1$ ). Because of the nature of the dynamic gate which drives it, it is impossible for the buffer to go from high to low. As a result there can be no glitches at any nodes in a cascaded set of logic blocks. Each stage evaluates and causes the next stage to evaluate in the same manner that a stack of dominos fall.

The Domino CMOS gate may be made static for low frequency circuits by including a weak p-transistor. A weak p-transistor is one that has a small W/L ratio. The ratio

Figure 2.7. Domino CMOS logic (a) basic version, and (b) latching version

is chosen small enough so that there is no significant impact on the pull-down current and so that the power consumed during the evaluation phase is tolerable. If the time between evaluation phases is relatively long, the clocked precharged p-transistor can be eliminated, and precharge can be accomplished by the weak static pull-up transistor. Charge redistribution in Domino CMOS can be reduced by placing a weak p-type feedback transistor or increasing the capacitance of the precharge node [OkMo86]. Figure 2.7(b) shows a circuit with a weak p-type feedback transistor which leads to the latching version of Domino CMOS gates, and increasing the capacitance of a precharge node can be accomplished by making the size of the transistors in the output inverter larger.

### 2.6. Cascade Voltage Switch

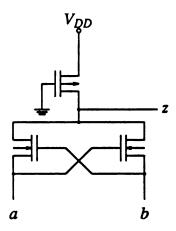

Cascade voltage switch (CVS) is a circuit implementation technique for complex single or dual output switching functions formed by cascading n-type MOS transistors. The CVS circuits yielding a dual output are called differential CVS (DCVS) circuits [HeGD84], whereas the other CVS circuits are called single-ended CVS (SCVS) circuits [BrCM84]. The differential style of logic usually requires both true and complement signals to be routed to gates. Both static and dynamic circuits can be generated. DCVS circuits are obtained by realizing the complement function with another set of n-type transistors. The two n-type networks are connected to the positive supply voltage node by a pair of cross-coupled p-type transistors.

Figure 2.8(a) shows a two-input static DCVS XOR circuit with complementary ntype networks. The static version is usually slower than a conventional complementary gate employing a p-tree and n-tree, since during the switching action, the pull-ups have to "fight" the n pull-down trees. Note that this is not a very efficient implementation of this gate.

Figure 2.8. Two-input DCVS XOR/XNOR circuits (a) static and (b) clocked version

Further refinement leads to a clocked version of the DCVS gate, as shown in Figure 2.8(b). A dynamic DCVS circuit is formed simply by adding one discharge n-type transistor and substituting the two cross-coupled p-type transistors with two precharge p-type transistors. The logic tree is minimized from the full differential form using logic minimization. Logic minimization results in a n-type network with only six transistors rather than eight. Outputs from dynamic DCVS circuits are usually buffered using static CMOS inverters, which are not shown in Figure 2.8(b). This DCVS structure can be easily expanded for multiple-input parity generator and other complex switching circuits. A four-way DCVS XOR gate [HeGD84], for instance, needs only fourteen transistors in its n-type network. Significant area saving is therefore achieved.

### 2.7. Pass Transistor Logic

One form of logic that is popular in nMOS circuits is pass transistor logic. Pass transistor realizations using fewer transistors usually result in area savings and higher operating speed when compared with the corresponding gate logic realizations. CMOS transmission gates used in many CMOS designs such as XOR gates and multiplexers are simple examples. A CMOS XOR gate and a two-input CMOS multiplexer are depicted in Figure 2.9. In total, four transistors are used for both the two-input CMOS XOR gate and the two-input multiplexer. If they are implemented using gate-level design, four two-input CMOS NAND gates are required for a two-input XOR gate, and three CMOS NAND gates are required for a two-input multiplexer.

CMOS pass-transistor gates are composed of nMOS and pMOS transistors. Since the transistor gate controls the passage of current between the drain and source, a simplified scheme [MeCo80, Brya81] which allows the MOS transistors to be viewed as simple on/off switches is proposed. In an n-transistor, for instance, the switch is closed,

-

Figure 2.9. Pass transistor logic (a) A two-input CMOS XOR gate; and (b) a two-input CMOS multiplexer

or "ON", when there is a "1" on the gate. Formal methods for deriving pass-transistor logic have been presented using this model [Whit83]. Basic design procedures for pass transistor logic using modified Karnaugh map and modified Quine-McCluskey tabular approach can be found in [RaWM85].

# 2.8. Differential Pass Transistor Logic

In traditional CMOS pass transistor logic, a p-type transistor is used to pass logic one efficiently, while the n-type transistor is used to pass logic zero efficiently. Besides

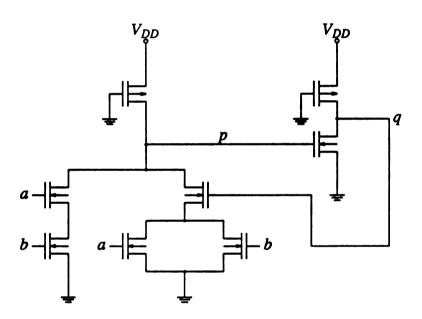

using both p- and n-type transistors, substantial p-to-n plane interconnects and the required well-to-device channel spacing reduce area efficiency. Furthermore, the number of drain-source connections at the network output is doubled, hence doubling the output capacitance and making conventional CMOS pass transistor networks inherently slow. Pasternak et. al. [PaSS87] proposed a new logic design structure called differential pass transistor logic by encoding the pass variables differentially, passing this signal through a differential pass network, and then decoding the output to normal logic levels. The differential signal can be restored to normal logic levels by using a static differential buffer, which is typically a cascade voltage switch logic inverter. Thus, both true and complementary values of the function can be obtained due to the differential buffer.

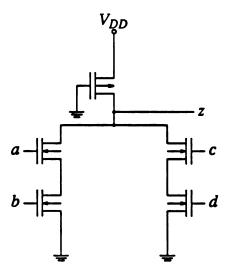

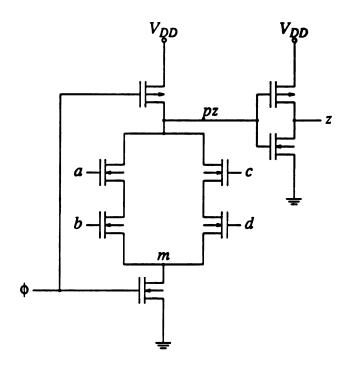

The differential pass logic element consists of two n-type transistors, controlled by the same gate signal, to pass the input and its complement to the output. Since n-type transistors pass logic zero efficiently, one of these values will be zero. The other output voltage level will be the maximum output voltage of an n-type transistor  $V_{DD}$  -  $V_{TH}$  where  $V_{TH}$  is the ON threshold voltage of the transistor. A conventional CMOS pass-transistor four-to-one selector circuit diagram and a differential pass-transistor four-to-one selector network are depicted in Figure 2.10 and Figure 2.11, respectively.

Note that in Figure 2.11 all the positive row outputs are connected together to form the signal OUT+, and all the negative row outputs are connected together to form the signal OUT-. The differential signal pair, OUT+ and OUT-, is then restored to normal logic levels by using a static differential buffer, which is simply a cascade voltage switch logic (DCVS) inverter and is depicted in Figure 2.12. In addition to replacing the p-type transistors of conventional CMOS pass transistor logic with smaller n-type transistors, differential pass transistor logic eliminates the p-to-n plane interconnect, and effectively halves the output capacitance. This results in increased area efficiency and operating speed.

Figure 2.10. Conventional CMOS pass-transistor 4-to-1 selector circuit diagram

Figure 2.11. Differential pass-transistor 4-to-1 selector circuit diagram

Figure 2.12. DCVS buffer used in differential pass transistor logic

Both DCVS logic and differential pass transistor logic structures have substantial area savings over fully complementary CMOS. However, when compared with corresponding DCVS circuits which suffer from longer rise time and fall time due to the fact that the p-type pull-ups have to fight the bigger n-type pull-down trees, differential pass transistor logic has shorter delay by using a fixed-size DCVS inverter.

# 2.9. Zipper CMOS

Charge-sharing is a prevalent problem in dynamic CMOS and Domino CMOS circuits. The problem arises due to the fact that not all internal nodes in the logic block are fully precharged. Figure 2.13 shows a Domino CMOS circuit for implementing a Boolean function f with clock signal  $\phi$  to illustrate the charge sharing problems. During the precharge phase of the clock, the p-type transistor  $Q_1$  is ON while the n-type

transistor  $Q_8$  is OFF. Node  $N_4$  is charged to  $V_{DD}$  and the output from the inverter is at the voltage level close to 0 V. This situation occurs at that time at every logic block including those whose outputs are connected to the inputs  $X_i$  of this particular block. As a consequence, the inputs  $X_i$  and those of all other blocks are close to 0 V during the precharge phase. Therefore there is no electrical path from node  $N_4$  to node  $N_1$ . When the clock turns to the evaluation phase, transistor  $Q_8$  is ON conditionally creating the path from the node  $N_4$  through the switch network to the ground, which in turn makes the output of the inverter F the logic ONE. This value is the input to the subsequent logic blocks and can cause the output of those blocks to switch to ONE in the "domino" fashion.

Obviously, the charge is stored at the node  $N_4$  during the precharge phase. The nodes  $N_3$ ,  $N_2$ ,  $N_1$  might have been discharged during the previous cycle and thus have no charge. Therefore, during the evaluation phase, there may be an electrical path to several discharged nodes without an electrical path to the ground, causing so-called charge redistribution problems. If the capacitance at the storage node  $N_4$  is  $C_s$  and the uncharged capacitance internal to the switching network is  $C_i$ , it is possible that the resulting voltage at the node  $N_4$  is reduced below the inverter threshold  $I_{TH}$ ; i.e.

$$V_{DD} \times \frac{C_s}{C_i + C_s} \le I_{TH}$$

where the maximum original voltage  $V_{DD}$  at the node  $N_4$  is assumed. This charge redistribution will cause the inverter at the output of the switching network to falsely switch, thus placing the incorrect value on the line causing other circuits to discharge falsely.

All dynamic CMOS and Domino CMOS circuits suffer from signal degradation caused by charge redistribution and leakage current. In contrast to these circuits, Zipper CMOS (ZCMOS for short) is inherently immune to the problems of instability and charge-sharing. ZCMOS is proposed by Lee and Szeto [LeSz86], and the basic ZCMOS

Figure 2.13. Charge sharing problem in dynamic CMOS and Domino CMOS logic

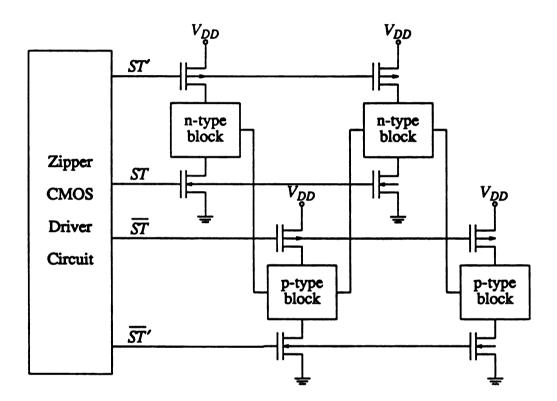

structure is depicted in Figure 2.14. The major components in a ZCMOS circuit are the Zipper Driver circuit and the alternate n-type and p-type logic blocks. The Zipper Driver generates four strobe signals, ST,  $\overline{ST}$ , ST', and  $\overline{ST'}$ , at various voltage levels based on a single clock to drive subsequent dynamic blocks.

During precharge, the output of every n-type block is high and that of every p-type block is low. This ensures that the transistors driven by the output of each dynamic stage will be off. During evaluation, strobe signal ST' is at its "poor 1" voltage level, and  $\overline{ST'}$  is at its "poor 0" voltage level. The precharge transistors are, therefore, partially on to produce a residual current for sustaining the precharged value of the internal nodes and overcoming the charge redistribution problem. The output of each n-stage can make at most one transition from high to low, and the output of each p-stage can undergo only one transition from low to high. This "staggered" fashion in which signals propagate through n-type and p-type blocks gives rise to the name "Zipper CMOS".

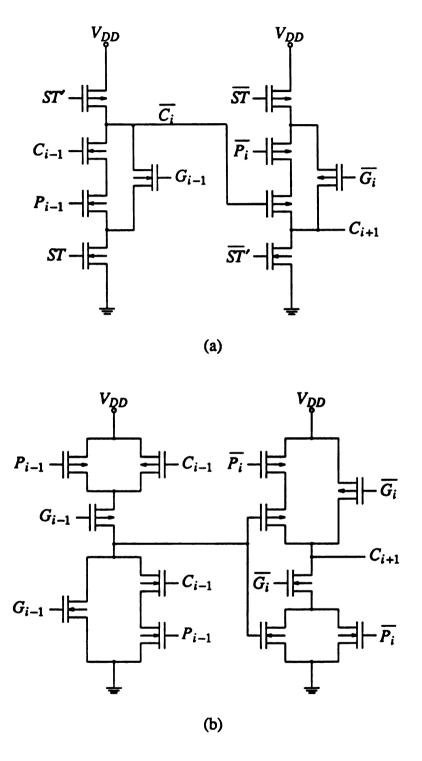

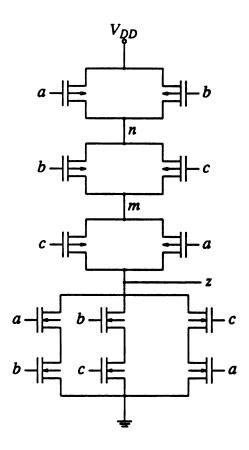

Figure 2.15(a) shows the ZCMOS implementation of two stages of a ripple carry chain. A static FCMOS implementation of the same circuit is shown in Figure 2.15(b).  $P_i$  and  $G_i$  represent the propagation and generation terms at the *i*th stage. The carry-in  $(C_i)$  and carry-out  $(C_{out})$  signals at the *i*th stage are related by

$$C_i = P_{i-1}C_{i-1} + G_{i-1}$$

.

Generally speaking, ZCMOS circuits lead to the use of multivalued logic due to various levels of clock signals. It improves the delay time of a CMOS circuit at the expense of increasing its dynamic power consumption. Thus, design tradeoffs exist for various logic structures, and the selection of an appropriate logic structure is basically a choice among a number of factors such as area, power dissipation, speed, noise margin, and even fault susceptibility.

In general, pseudo-nMOS, dynamic CMOS, and pass transistor logic provide sub-

Figure 2.14. Zipper CMOS circuit structure

Figure 2.14. Zipper CMOS circuit structure

Figure 2.15. Two stages in a (a) ZCMOS (b) FCMOS ripple carry chain

stantial savings in terms of area, which can be estimated to a first order by the number of transistors and also affected by routing considerations. Note that dynamic gates require a precharge interval, and this may or may not impact performance. As a rule of thumb, small logic blocks are usually implemented statically while large logic cascaded structures might be implemented with dynamic or domino CMOS logic.

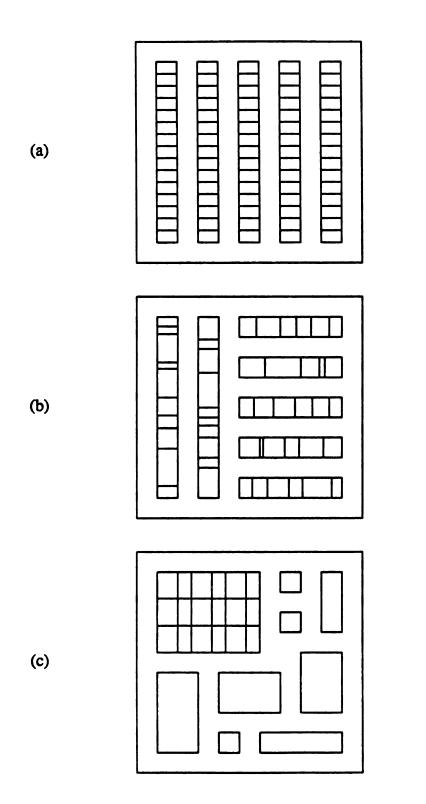

### 2.10. Design Styles

VLSI design styles are undergoing rapid evolution. As the density and the number of devices on a VLSI chip increase, methods of dealing with complex design problems have to be developed. Several different methodologies have been developed for designing integrated circuit chips, ranging from full-custom approach, in which the entire IC is designed from scratch, to semi-custom approaches, in which the designer builds the chip from a collection of pre-designed components. One of the advantages with various design styles is to allow system designers the option of implementing high performance systems directly in silicon. Figure 2.16 illustrates three semi-custom approaches -- gate array, standard cell, and macrocell.

The standard cell approach provides a cell library for functions to be interconnected. The cells in a design are arranged in rows with area for making interconnect between the rows. Usually the cells are constrained to be of uniform height but variable width, and the designer retains the flexibility of both placement and interconnect.

The macrocell approach can be treated as an extension of the standard cell approach, with the additional feature that designers can either use their own local cells or circuits generated from automatic tools. Some macrocells generated from automatic tools are parameterizable, rectilinear blocks that are customized from a library of templates. These cells are either connected by abutment or by automatic routing.

Figure 2.16. Semi-custom design styles (a) gate array, (b) standard cell, and (c) macrocell

Obviously, designs using macrocells offer still more flexibility than standard cell designs.

Gate arrays are semi-custom integrated circuits, which are mostly made ahead of time and which are customized to the user's needs by defining one or more layers of metal on the die itself. This method provides macros with predefined placement on the chip. The interconnection of these macros is customized for specific applications. Because the gate array is mostly made ahead of time, it offers significant savings in both cost and time. On the other hand, in the standard cell approach the wafers are not built ahead of time. Therefore, in the standard cell approach, the designs of all the mask levels of each cell have to be stored in a computer, in contrast to typically one or two such mask levels for gate array macros. This implies that the tooling cost for a standard cell library is considerably higher than that of a similar library of macros for gate arrays. It is true that the die cost of a gate array is higher than that of a full custom die. However, in lowvolume applications, the nonrecurring development costs are the dominating factors, not the differential piece-part costs. It is here that the gate array approach has a clear edge over the full-custom and standard cell approaches. At the end of 1985, gate arrays outsold standard cell ICs by a four-to-one margin. By 1990 it is estimated [Holl87] that more than half of all semiconductors sold will be semi-custom designs of which gate arrays and standard cell ICs are a major part.

There are also a number of major arguments in favor of the standard cell approach compared with gate arrays. The ability to put an extra 20 to 30% or more of functionality on a die using the standard cell approach often enables the system to be partitioned in such a way as to minimize the connections to the world outside the chip. Because the bulk of the power dissipated is often in the I/O buffers, minimization of their numbers can drastically cut the power dissipated by the chip. Speed will also be enhanced by the elimination of the capacitance associated with the no-longer-needed I/O buffers. Thus, given a standard cell library and gate array macros, some researchers are working on

converting gate arrays to standard cell designs.

Today, standard cells and gate arrays sometimes compete for a given customization project. However, due to the shrinking feature sizes and larger die sizes, there is nothing to prevent standard cells from incorporating gate arrays. One or more of the standard cells in the library could simply be a gate array cell of a given size. Such an arrangement has the advantage of permiting a chip to be designed so as to accommodate a rapidly changing market or to accommodate a low-entry-cost product. In the future, one will see combinations of customization techniques on one chip.

The *full-custom* design style incorporates maximum flexibility, and a full-custom IC is completely made with no interruption in the manufacturing cycle. Theoretically, a full-custom IC is one in which every transistor is designed, sized and placed appropriately for the function that particular IC performs. However, in the VLSI era with as many as two million or more transistors on a chip, a relatively small number of transistor designs are usually used over and over again, and groups of circuitry are replicated where possible. Because of its flexibility, full-custom design offers a number of advantages. Full-custom chips can often be made denser and faster than their semi-custom counterparts, as well as offering better yield and lower power consumption. Sadly, these advantages are frequently offset by the greater time it takes to design custom chips. A survey of the IC industry [ReSS85] shows that even moderately small (2,000 gates) full-custom chips take approximately three times as long to design as comparable semi-custom chips. For larger chips, the differences are even more extreme.

Chips designed using the full-custom approach take longer to design mainly because more aspects of their layout are under designer control, and the verification of layout pieces is much more difficult. The designer creates each circuit transistor-by-transistor, rather than from a collection of logic gates. The layout of a given circuit is not standard, but depends on where that circuit is used on the chip. Components are often

connected by abutment or local hand-routing to compact the design, instead of through standard routing channels by an automatic router. The lack of automatic tools for full-custom design make these cells time-consuming to enter, and even more time-consuming to verify or change.

From the above introductory sections, it is clear that there exist many logic structures and various design methodologies by which a VLSI design can be implemented. To automate a design or verification process, one needs to have a base, namely a design representation, to represent and record the design. Many design representations have been proposed in the literature and actually used at different levels. In the next chapter, a brief discussion on how a design can be represented at various levels, followed by the logical circuit expressions at the switch level, will be given.

### **CHAPTER III**

# LOGICAL CIRCUIT EXPRESSIONS

In this chapter, the essence of abstraction and several levels of abstraction that various VLSI design representations use are discussed. The representation scheme proposed in this thesis, namely the *logical circuit representation*, is described in detail. Approaches for generating logical circuit expressions are proposed. Unlike traditional device listing approaches, which represent only circuit structures, logical circuit expressions combine structural data with behavioral information, and thus illustrate a way to reduce the difficulty of information transformation between bahavioral and structural representations of CMOS circuits.

The VLSI design process spans a broad spectrum of disciplines in many different fields. Because of the diversity of tasks and design issues, a systematic approach to breaking the design process into a number of design levels and subtasks is essential. While the design of single chips with the complexity of a microprocessor is a relatively recent phenomenon, people have been designing software systems of similar complexity for many years. Thus, one might naturally wonder whether the experience and tools used in software design could be carried over directly to the world of VLSI. Certainly there are several factors in common. In both the circuit world and program world, the problem can be characterized as one of implementing algorithms [Ullm84]. For example, the Least-Recently Used (LRU) processing unit designed for hierarchical memory systems [WuNi86] is principally a hardware design for the LRU algorithm. Both large hardware and large software designs can be carried out by several designers, and coordinating pieces of a project is always a difficult job. Another important similarity between

software design and the world of VLSI is that designers are much more productive when they are given high-level languages in which to express their designs. For example, programmers almost never work in machine code, and they generally prefer higher level languages such as C and Pascal. Similarly, working at a higher-level circuit representation will relieve the designer's burden, and therefore improve the designer's productivity and reduce the turn-around time of the design. Of course, it is a dangerous practice to oversimplify the abstractions of electronic circuit behavior. Thus, the selection of an appropriate abstraction level for individual projects is basically a trade-off between accuracy and productivity, and is a matter of art.

#### 3.1. Levels of Abstraction

The virtue of abstraction is data reduction. It is a method to replace an object by a simplified one that defines the interactions of the object with its environment, while deleting the internal organization of the object. There are a number of different levels of symbolic representation for MOS VLSI circuits. In order to understand the overall design system, it helps to be aware of the many levels of abstraction that various design representations use. The principal sorts of design representations that appear are the following.

#### Geometry Representation

Geometry languages, such as the popular layout description languages CIF (Caltech Intermediate Form) [MeCo80] and Calma GDS II, use colored rectangles or colored shapes as their primitives. Once a layout has been drawn it can then be digitized, or translated into some machine-readable form. Silicon foundries take designs expressed in

these languages as inputs to fabricate the chips.

#### Stick Representation

In a stick diagram, transistors and vias are represented by points of a grid, and wires are represented by widthless lines. Such stick diagrams may be annotated with important circuit parameters such as length-to-width ratios, if needed. Information regarding the thickness of wires and the exact positions of the points is supplied by the compiler that translates the stick representation into geometry. A typical language can be found in [MaNE82]. One of the significant advantages of this sort language is that it is almost impossible to make a design rule error, since it is the responsibility of the compiler to position elements and wires due to the higher-level abstraction.

#### Switch-Level Representation

Switch-level primitives are transistors and nodes, which are points connected to one of the three terminals of one or more transistors. These three terminals are generally called the source and drain, which are the two ends, and the gate, which separates the source and drain. ESIM [BaTe80], a switch-level language for event-driven switch-level simulations, is a typical example at this level. The *Logical Circuit Expressions* representation to be proposed later in this chapter falls into this category.

#### PLA Personalities and Logic Representation

The programmable logic array, or PLA, is a specialized layout style for implementing switching logic and sequential machines. Truth tables and tiles are usually used to generate PLAs in various styles [KaVa81, OuSM85]. This representation leads to regular layouts and allows design to be carried out at a relatively high level. Similar to PLA per-

sonalities, the logic level of the design process uses an abstraction of the underlying electrical circuit in which the currents and voltages are limited to discrete levels. In digital circuits, the two levels of signals that are permissible are those that represent logic ZERO and logic ONE. Thus, ordinary Boolean logic, while augmented with a notion of sequentiality such as using the key word "LAST" in LGEN [John83] so one can refer to the "current" and "previous" values of a variable, also forms a high-level way to specify designs. However, with a language at the logic level, the designer has lost all control over the layout and relative positioning of circuit elements.

#### Finite State Machine Languages

Finite state machine languages such as SLIM [Henn81] and PEG [Hama83] are designed to specify the control of a microprocessor or similar chips. They can be compiled into logic or PLA personalities, for example. While a PLA is often a fast approach for implementing a sequential machine, the compiler for the language must decide on the coding of states for the machine in a way that minimizes the area of the PLA.

#### Procedure Languages

The extreme of high-level design languages is an ordinary programming language, in which the algorithm to be performed by the circuit is written. The sequencing rules for statements of the program are embedded into the control of the chip, while the variables are represented by registers. An attempt at compiling Pascal programs into silicon can be found in [Tric85]. Procedural languages that are somewhat more specialized to circuit design than are ordinary programming languages also exist. These languages, often called register transfer languages, deal with registers and specify the sequencing of actions involving these registers in terms of events at the inputs and events at other registers.

Generally speaking, it is important to simplify the model of integrated circuitry, so as to more quickly and easily analyze or explain the function of a given circuit, and more easily visualize and invent new circuit structures without drifting too far away from physically realizable and workable solutions. An extremely simple model based on transistor "switches" is proposed in [MeCo80], in which transistors are treated as valves or switches. Many switch-level simulators such as ESIM [BaTe80, Term83] and MOSSIM [Brya81] have similar models for analyzing circuit behavior.

#### 3.2. Series-Parallel Network

The focus in this chapter is on circuit representation at the transistor level. Not only are switch-level simulators based upon transistor networks, but also symbolic layout systems such as TOPOLOGIZER [KoWe85] use a transistor connection description as input to generate geometric layouts. As far as circuit connectivity is concerned, one of the first attempts to list all electrical networks meeting certain specified conditions was made in 1892 by P. A. MacMahon [MacM92] who investigated combinations of resistances. Among various switching circuits, the simplest structure is the so-called series-parallel network.

A series-parallel network is a simple type of connection which occurs frequently in both theoretical and applied electrical engineering. The concept of series-parallel connection is intuitive, but this type of network plays a prominent role in Shannon's well known application of Boolean algebra to switching circuits [Shan38]. One reason for the importance of series-parallel networks stems from the fact that the joint resistance is easily evaluated by the following two rules due to Ohm:

#### (1) Resistance is additive for resistors in series, and

(2) Reciprocal resistance is additive for resistors in parallel.

The following inductive definition of a series-parallel network is given in [RiSh42]:

**Definition:** A single element is a series-parallel network. A network N is series-parallel if it is either a series or a parallel connection of two series-parallel networks.

There are also several alternative definitions of series-parallel networks [Duff65]:

- (1) A network is series-parallel if it is a direct construction of the series operation and the parallel operation.

- (2) Two edges x and y are said to be *confluent* if there do not exist two closed curves  $C_1$  and  $C_2$  such that  $C_1$  meets x and y in the same direction but  $C_2$  meets x and y in the opposite direction. A network is series-parallel if it is confluent; i.e., every pair of its edges is confluent.

- (3) A network is series-parallel if it does not have an embedded Wheatstone bridge.

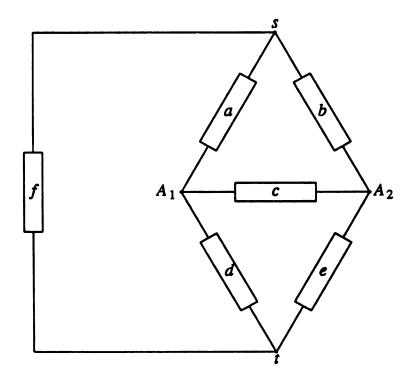

Figure 3.1 shows a circuit with a Wheatstone bridge [Nils83]. Suppose that the directions of f and c are chosen so that they have the same sense relative to the loop (f, b, c, d). It then results that f and c have opposite sense relative to the loop (f, a, c, e).

The series-parallel combinations do not exhaust the possible networks since they exclude all bridge arrangements like the Wheatstone bridge, but they are an important class because of their simplicity. When the number of elements is less than five, all networks are series-parallel. When the number of elements is exactly five, there is only one bridge-type network, the Wheatstone bridge [RiSh42]. As the number of elements rises, both series-parallel and bridge-type networks increase.

The series-parallel networks are interesting in themselves in another setting, namely the design of switching circuits. In fact, most switching circuits are series-parallel in structure, and all existing low-level synthesis tools use series-parallel networks to implement logic functions. Another property of a series-parallel network is that the direction

Figure 3.1. A circuit with a Wheatstone bridge

of the current flow through a given edge is independent of the resistance of the edges of the network [Duff65]. In Figure 3.2, the edges f and c can be replaced by a battery and a meter, respectively, to measure the current flow through c so as to estimate the resistance of the resistors. Since the circuit is not series-parallel in structure, the measurement obtained from the meter might be either positive or negative, indicating the direction of the current flow through the edge.

A series-parallel CMOS switching network can be described using a symbolic representation. Such a circuit is represented by a set of expressions, the terms of the expressions corresponding to the various n-channel and p-channel devices in the circuit. As far as the circuit function is concerned, a calculus is used for manipulating these expressions by simple mathematical processes, most of which are similar to rules in the

ordinary algebra. This calculus associated with *logical circuit expressions* is analogous to the calculus of propositions used in the symbolic study of logic. Once a symbolic representation is available, the desired functions of a synthesis problem can be written as a system of expressions, and the expressions are then manipulated into the form representing the simplest circuit. The circuit may then be immediately drawn from the expressions.

Based on series-parallel networks, a CMOS switching circuit can be partitioned into a number of components, most of which are series-parallel in structure. The notation to be used is taken chiefly from symbolic logic, and will be shown in the following sections.

### 3.3. Logical Circuit Representation

In terms of representing transistor connectivities, traditional approaches for low-level circuit representation are mainly device listing approaches, in which circuit elements are listed one by one using nodes. For example, the commonly used circuit simulator SPICE [Nage75] uses nodes and circuit elements to perform nodal analysis. The switch-level event-driven simulator ESIM uses statements in the form of

to represent transistors, where  $\langle type \rangle$  can be either p or n for p-type transistor and n-type transistor, respectively.

Device listing approaches used at either circuit level or transistor level are really simple, but are not suitable for describing system functions merely because they do not supply any information about how a circuit works. In fact, the difficulty of information transformation among various representations makes design automation systems for VLSI circuits less mature. Much unnecessary effort is spent in transforming information from one representation to another. In order to overcome this difficulty, we need a

representation which combines both structural and functional information so that circuit functionality can be easily extracted from geometric layouts and/or transistor schematics.