This is to certify that the

dissertation entitled

# Scalable Data Redistribution Services for Distributed Memory Machines

presented by

Edgar T. Kalns

has been accepted towards fulfillment of the requirements for

<u>Doctoral</u> <u>degree in <u>Computer Sci</u>ence</u>

Major professor

Date May 19, 1995

0-12771

# LIBRARY Michigan State University

PLACE IN RETURN BOX to remove this checkout from your record.

TO AVOID FINES return on or before date due.

| TO ATOID FINES retur  | TO AVOID FINES return on or before date due. |          |  |  |  |

|-----------------------|----------------------------------------------|----------|--|--|--|

| DATE DUE              |                                              | DATE DUE |  |  |  |

| C <u>T 1 3 1999</u>   |                                              |          |  |  |  |

|                       |                                              |          |  |  |  |

|                       |                                              |          |  |  |  |

|                       |                                              |          |  |  |  |

|                       |                                              |          |  |  |  |

|                       |                                              |          |  |  |  |

|                       |                                              |          |  |  |  |

|                       |                                              |          |  |  |  |

|                       |                                              |          |  |  |  |

|                       |                                              |          |  |  |  |

|                       |                                              |          |  |  |  |

| MSU is An Affirmative | A-01                                         |          |  |  |  |

MSU is An Affirmative Action/Equal Opportunity Institution ctoirclasses.pn3-p.1

## SCALABLE DATA REDISTRIBUTION SERVICES FOR DISTRIBUTED-MEMORY MACHINES

$\mathbf{B}\mathbf{y}$

Edgar T. Kalns

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Computer Science

#### ABSTRACT

# SCALABLE DATA REDISTRIBUTION SERVICES FOR DISTRIBUTED-MEMORY MACHINES

By

#### Edgar T. Kalns

Run-time data redistribution can effect higher algorithm performance in distributed-memory machines. Redistribution of data can be performed between algorithm phases when a different data decomposition is expected to deliver increased performance for a subsequent phase of computation. Data-parallel Fortran languages, e.g., HPF (High Performance Fortran), support run-time data redistribution. Data redistribution can be invoked explicitly with primitives or may occur implicitly. One type of implicit data redistribution occurs when the distribution of actual parameters to a subprogram do not match the distribution of the dummy arguments in the subprogram interface. Typically, with distributed-memory machines, redistribution causes data exchange among processor memories resulting in interprocessor communication overhead. Consequently, there is a performance tradeoff between the higher efficiency of a new data distribution for subsequent computation and the time required to establish it.

This dissertation investigates the pertinent issues that affect the performance of data redistribution on distributed-memory machines, focusing on four primary areas. First, we address the partitioning (or mapping) of data onto processor memories. A technique that facilitates the minimal amount of data exchange among processor memories during redistribution between HPF's regular patterns is proposed. Second, we present the design of a portable and communication-efficient data redistribution library whose implementation is portable among a large class of distributed-memory machines. Portability is enhanced through MPI (Message Passing Interface) communication primitives. Third, we develop a framework for quantifying the scalability of parallel algorithms together with the machines upon which they execute. Fourth, we apply the framework to quantify the scalability of the data redistribution library for a large range of processor configurations and data set sizes on selected distributed-memory machines.

© Copyright 1995 by Edgar T. Kalns All Rights Reserved To my parents

#### ACKNOWLEDGMENTS

My deepest gratitude to my parents whose continual love and encouragement helped me achieve my academic goals. For as long as I can remember, they have told me, and shown me by example, that life's most gratifying accomplishments require industriousness, perseverance, tenacity, and an ability to find enjoyment not only in the achievement itself, but in the progression toward the goal.

To my dissertation advisor, Professor Lionel Ni, I extend my warmest thanks for his guidance, inspiration, and patience. His door was always open to me, his consultation forthcoming whenever I asked for it. With his help, I honed my abilities to think critically as a researcher, and I heightened my satisfaction of pursuing solutions to difficult problems in Computer Science. I will always be indebted to him for his contribution to my professional development. Additionally, I would like to thank the remaining members of my Ph.D. guidance committee: Professors Li, McKinley, Mutka, and Rover for their numerous helpful comments and suggestions.

I would like to thank a number of fellow graduate students with whom I have developed close friendships. I am particularly grateful to Barbara Birchler, who with her love, kindness, and encouragement, helped me immensely. She critiqued my ideas and proofread my technical reports and dissertation chapters. With her ever-present smile and cheerful nature, she helped me through the inevitable ups and downs. To my "lunch crowd" friends: Reid Baldwin, Barb Birchler, Kevin Bradtke, Eddie Burris, Dave Chesney, Marie-Pierre Dubuisson, Jon Engelsma, Maureen Galsterer, Dan Meyers, Michele Morin, Tim Newman, Ron Sass, Steve Turner, Christian Trefftz, and Steve Walsh I extend my thanks for many fond, and oftentimes boisterous, noon-time get-togethers. A special thanks to Ron Sass, for his careful preparation of the document style used to format this dissertation in compliance with the Graduate School's regulations.

To Frank Northrup and to all the past and present Computer Science systems administrators with whom I have worked, I extend my gratitude for the camaraderie and team spirit we shared in managing one of the largest computing facilities in the country. I would especially like to thank Frank for his understanding and friendship.

Lastly, I extend my gratitude to the Michigan State University as a whole for providing me the highest quality graduate education. As a Michigan native, I have been extremely fortunate that this institution, attended by students the world over, exists in "my backyard."

#### TABLE OF CONTENTS

| LIST OF TABLES                                          | Х  |

|---------------------------------------------------------|----|

| LIST OF FIGURES                                         | хi |

| 1 Introduction                                          | 1  |

| 1.1 HPF Example                                         | 4  |

| 1.2 Motivation                                          | 6  |

| 1.3 Organization of Dissertation                        | 9  |

| 2 Data Decomposition                                    | 11 |

| 2.1 Static: Align and Distribute                        | 12 |

| 2.2 Dynamic: Realign and Redistribute                   | 16 |

| 2.3 Example of Redistribution in HPF                    | 18 |

| 2.4 Rudimentary Operation of Data Redistribution        | 20 |

| 2.4.1 Determination of Processor Send and Receive Sets  | 21 |

| 2.4.2 Data Exchange with Message-Passing                | 23 |

| 2.5 Implicit Redistribution                             | 25 |

| 2.6 Redistribution Optimizations                        | 28 |

| 3 Data Mapping Optimization                             | 32 |

| 3.1 One-dimensional Logical Processor Mapping           | 33 |

| 3.1.1 Processor Mapping Technique                       | 35 |

| 3.1.2 Mapping Function                                  | 38 |

| 3.1.3 Optimality of Mapping Function                    | 39 |

| 3.2 Multidimensional Logical Processor Mapping          | 46 |

| 3.2.1 m-dimensional Redistribution                      | 46 |

| 3.2.2 Two-dimensional to One-dimensional Redistribution | 48 |

| 3.2.3 One-dimensional to Two-dimensional Redistribution | 53 |

| 4 Data Redistribution Library                           | 59 |

| 4.1 Library Design Issues                               | 60 |

| 4.1.1 Advantages of Software Libraries                  | 60 |

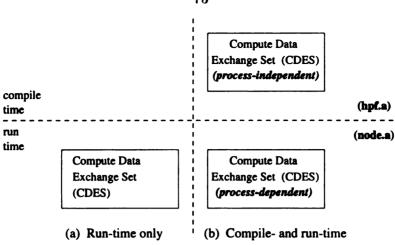

| 4.1.2 Role of HPF Compiler                              | 61 |

| 4.1.3 Use of MPI for Libraries                          | 63 |

| 4.1.4 Scalability                                       | 64 |

| 4.2 DaReL Design Overview                               | 65 |

| 4.2.1 DaReL Interface                                   | 65 |

| 4.2.2 Compute Data Exchange Sets (CDES)                 | 69 |

| 4.2.3 Partitioning CDES Functionality                            | <br>72  |

|------------------------------------------------------------------|---------|

| 4.2.4 Exchange Data (ED)                                         | <br>73  |

| 4.2.5 Standard and Derived Datatypes                             |         |

| 4.2.6 Scalability                                                | <br>80  |

| 5 Quantifying Scalability                                        | 82      |

| 5.1 Examples of Ambiguity in Scalability                         | <br>84  |

| 5.2 Goal-directed Scalability Metrics                            |         |

| 5.3 Metrics for Quantifying Scalability                          |         |

| 5.3.1 Taxonomy of Scalability Measures                           |         |

| 5.4 Mathematical Framework                                       |         |

| 5.4.1 Algorithm and Machine Parameterization                     |         |

| 5.4.2 Fixed-work Problems                                        |         |

| 5.4.3 Scaled-work Problems                                       |         |

| 5.4.4 Deriving AM Pair Parameters                                |         |

| 5.5 A Three-dimensional Illustration of AM Pair Scalability      |         |

| 5.6 Case Study: Matrix Multiplication                            |         |

| 5.6.1 Algorithm-Machine Pair $a_1M$                              |         |

| 5.6.2 Algorithm-Machine Pair $a_2M$                              |         |

| 5.6.3 Algorithm-Machine Pair $a_3M$                              | <br>108 |

| 5.6.4 Computing AM Pair Parameters                               |         |

| 5.6.5 Scalability Quantification of $a_1M$ , $a_2M$ , and $a_3M$ |         |

| 5.7 Inclusion of Other Scalability Models                        |         |

| 6 Performance and Scalability                                    | 120     |

| 6.1 Processor Mapping Technique Analysis                         | <br>    |

| 6.1.1 Effect of Optimal Mapping on the Programmer                |         |

| 6.1.2 Effect of Optimal Mapping on the Compiler                  |         |

| 6.1.3 Performance Comparison with Traditional Technique          |         |

| 6.2 DaReL Performance and Scalability                            |         |

| 6.2.1 CDES and ED Execution-time Performance                     |         |

| 6.2.2 Algorithm Choices for ED                                   |         |

| 6.2.3 Scalability                                                |         |

| 7 Conclusion and Future Work                                     | 147     |

| 7.1 Research Contribution                                        |         |

| 7.2 Future Work                                                  |         |

| BIBLIOGRAPHY                                                     | 152     |

#### LIST OF TABLES

| 4.1 | MPI Communication Primitive Choices            | 77  |

|-----|------------------------------------------------|-----|

|     | AM parameters for $a_1M$ , $a_2M$ , and $a_3M$ |     |

| 6.1 | Redistribution test cases for DaReL            | 129 |

#### LIST OF FIGURES

| 1.1  | HPF Linear System Solver                                                                                           |

|------|--------------------------------------------------------------------------------------------------------------------|

| 2.1  | Example of HPF alignment                                                                                           |

| 2.2  | One- and two-dimensional HPF data distributions                                                                    |

| 2.3  | Example of !HPF\$ REDISTRIBUTE                                                                                     |

| 2.4  | Redistribution from (*,BLOCK,CYCLIC) to (CYCLIC,CYCLIC,BLOCK) 19                                                   |

| 2.5  | Collective communication patterns                                                                                  |

| 2.6  | Realignment of x causes redistribution                                                                             |

| 2.7  | Redistribution at subprogram interface                                                                             |

| 3.1  | Data Distribution and Redistribution onto physical nodes                                                           |

| 3.2  | Logical processor to data mapping alternatives                                                                     |

| 3.3  | Mapping lpids to place holders                                                                                     |

| 3.4  | lpid; is mapped to first element of its data block                                                                 |

| 3.5  | $z \leq p$                                                                                                         |

| 3.6  | z > p                                                                                                              |

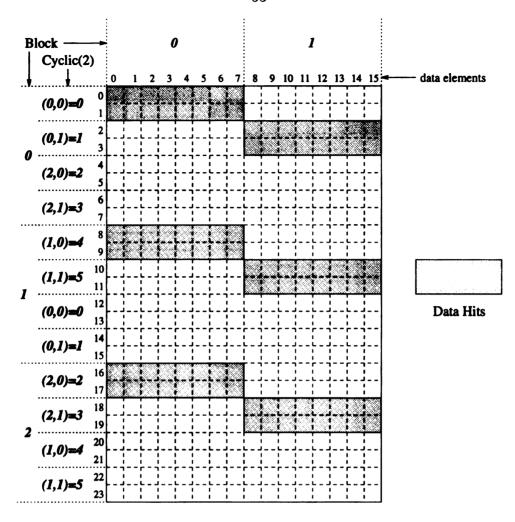

| 3.7  | (BLOCK <sub>3</sub> , BLOCK <sub>4</sub> ) to (CYCLIC <sub>3</sub> (3), CYCLIC <sub>4</sub> (2)) redistribution 49 |

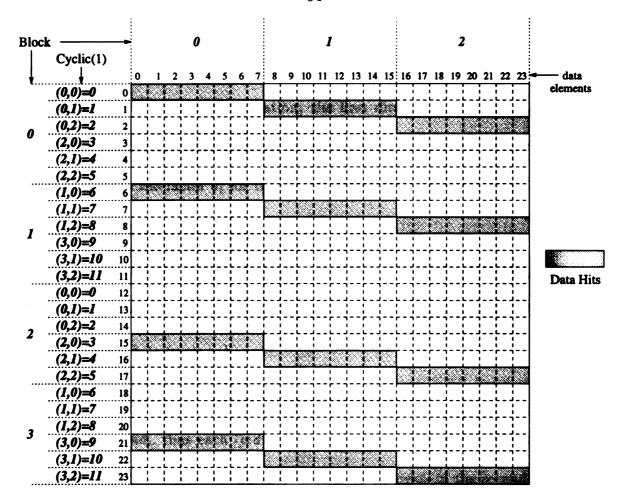

| 3.8  | (BLOCK <sub>3</sub> , BLOCK <sub>2</sub> ) to (CYCLIC <sub>6</sub> (2),*) redistribution                           |

| 3.9  | (BLOCK <sub>4</sub> , BLOCK <sub>3</sub> ) to (CYCLIC <sub>12</sub> (1),*) redistribution                          |

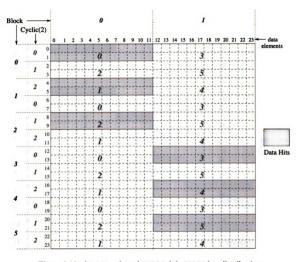

| 3.10 | (BLOCK <sub>6</sub> ,*) to (CYCLIC <sub>3</sub> (2),BLOCK <sub>2</sub> ) redistribution                            |

| 3.11 | (BLOCK <sub>12</sub> ,*) to (CYCLIC <sub>4</sub> ,BLOCK <sub>3</sub> ) redistribution                              |

| 4.1  | Distinct scatter-gather sets                                                                                       |

| 4.2  | C-based interface for DaReL                                                                                        |

| 4.3  | Parameters for the invocation of DaReL 6                                                                           |

| 4.4  | Different shaped process configurations                                                                            |

| 4.5  | CDES example for process $(1,1)$                                                                                   |

| 4.6  | Partitioning CDES                                                                                                  |

| 4.7  | ED using MPI point-to-point communication                                                                          |

| 4.8  | ED using MPI collective communication                                                                              |

| 4.9  | Limitation of derived types and collective communication                                                           |

| 5.1  | Comparison of three AM pairs                                                                                       |

| 5.2  | Scaled work vs. execution time of two AM pairs 8'                                                                  |

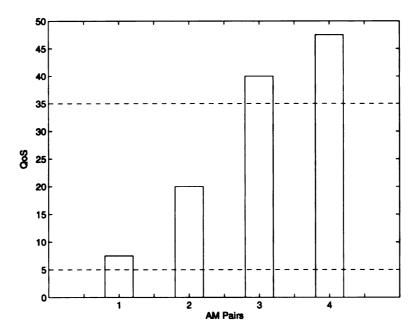

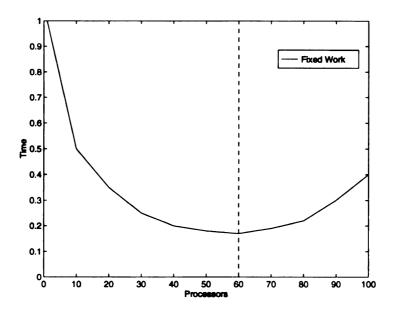

| 5.3  | Quality of Solution for $\sin(x)$                                                                                  |

| 5.4  | Execution time vs. number of processors tradeoff                                                                   |

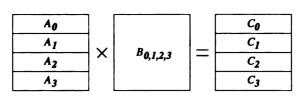

| 5.5  | Data distribution of $a_1 \ldots 100$                                                                              |

| 5.6  | Algorithm $a_1 \ldots \ldots \ldots \ldots \ldots \ldots$                   | 106 |

|------|-----------------------------------------------------------------------------|-----|

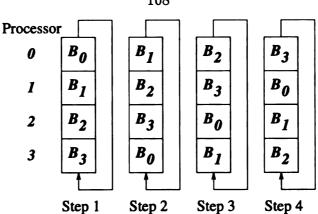

| 5.7  | Data distribution and operation of $a_2 \ldots \ldots \ldots \ldots \ldots$ | 107 |

| 5.8  | Communication pattern of $a_2 \ldots \ldots \ldots \ldots \ldots \ldots$    | 108 |

| 5.9  | Algorithm $a_2$                                                             | 109 |

| 5.10 | Data distribution and operation of $a_3 \ldots \ldots \ldots \ldots \ldots$ | 109 |

| 5.11 | Algorithm $a_3$                                                             | 110 |

| 5.12 | Tree-based MPI Reduction used in $a_3M$                                     | 112 |

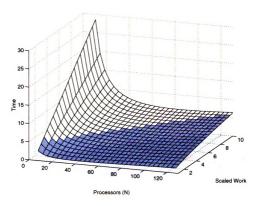

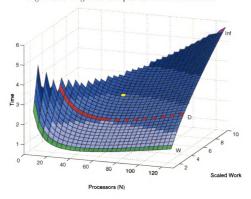

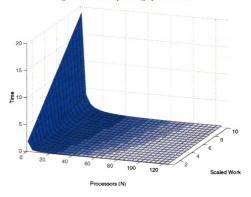

| 5.13 | A generic AM pair 3D surface illustration                                   | 116 |

| 5.14 | Scalability metrics illustrated on AM surface                               | 116 |

| 5.15 | $S(\lambda_D)$ comparison of $a_2M$ and $a_3M$ where $\lambda_D=20$         | 117 |

| 5.16 | $S(\lambda_D)$ comparison of $a_1M$ and $a_2M$ where $\lambda_D=5$          | 118 |

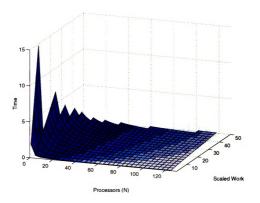

| 5.17 | Incorporating speed metric                                                  | 119 |

| 5.18 | Incorporating efficiency metric                                             | 119 |

| 6.1  | Mappings when physical node mapping is static                               | 123 |

| 6.2  | Mappings when physical node mapping is dynamic                              | 124 |

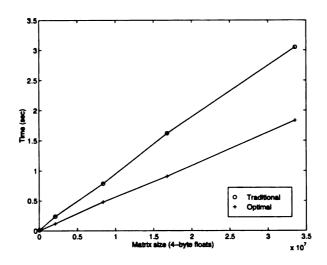

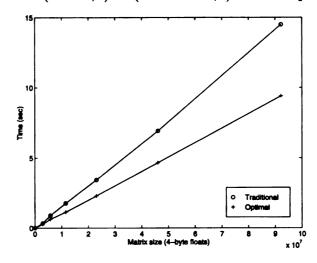

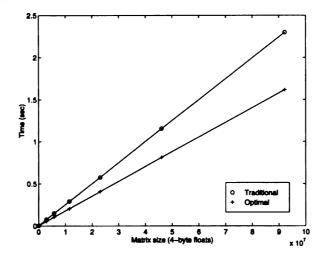

| 6.3  | (BLOCK,*) to (CYCLIC( $c$ ),*) on $8 \times 1$ processors                   | 128 |

| 6.4  | (BLOCK, BLOCK) to (CYCLIC(c), CYCLIC(c)) on $4 \times 3$ processors         | 128 |

| 6.5  | (BLOCK, BLOCK) to (CYCLIC(c), CYCLIC(c)) on $6 \times 4$ processors         | 128 |

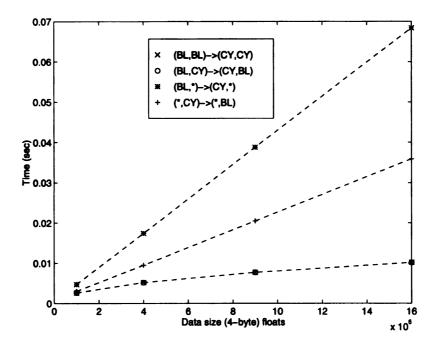

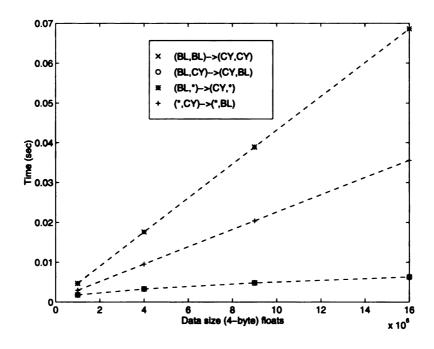

| 6.6  | CDES performance on 20 processor configurations                             | 130 |

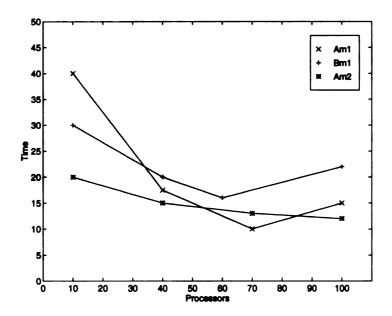

| 6.7  | ED performance on 20 processor configurations                               | 131 |

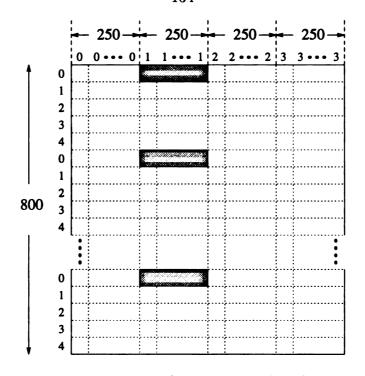

| 6.8  | Local data set for (BLOCK, BLOCK) to (CYCLIC, CYCLIC)                       | 133 |

| 6.9  | Local data set for (BLOCK, CYCLIC) to (CYCLIC, BLOCK)                       | 134 |

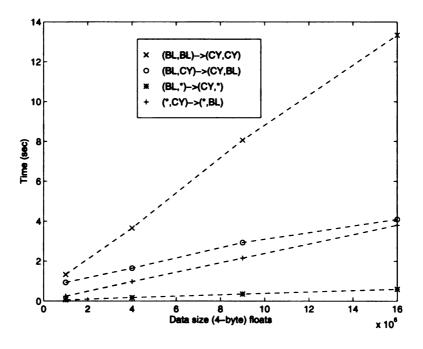

| 6.10 | CDES performance on 100 processor configurations                            | 135 |

| 6.11 | ED performance on 100 processor configurations                              | 135 |

| 6.12 | (BLOCK, BLOCK) to (CYCLIC, CYCLIC) redistributions                          | 137 |

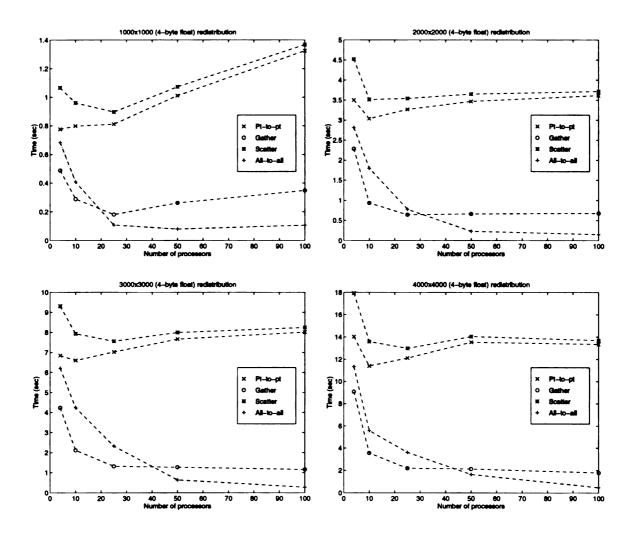

| 6.13 | Communication paradigm using Scatter (top) and Gather (bottom)              | 141 |

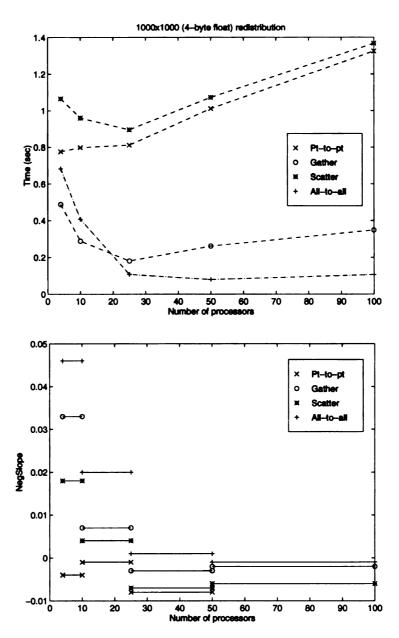

| 6.14 | 1000 × 1000 redistribution with                                             | 144 |

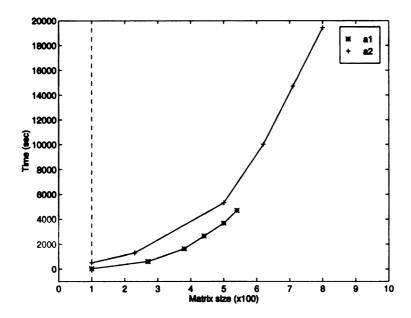

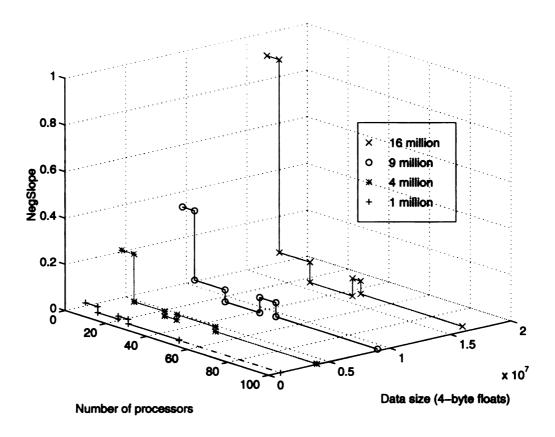

| 6.15 | DaReL scalability measured by $NegSlope(N, N')$                             | 146 |

# Chapter 1

## Introduction

Only in the past several years, Scalable Parallel Computers (SPCs) have come to be viewed not only as indispensable for large-scale engineering and scientific applications, but also as viable platforms for commercial and financial applications. Many SPCs, such as the IBM Scalable POWERparallel (SP-1 and SP-2), Intel Paragon, Cray T3D, nCUBE-2/3, and Networks of Workstations (NoW), have demonstrated scalable performance in these domains. Distributed-memory machines comprise an ensemble of nodes where each node consists of a processor, local memory, and other supporting devices. The nodes of the machine are interconnected by a point-to-point (direct) or switch-based (indirect) network. These distributed-memory systems offer proportional performance increases as the processor configuration size, network and I/O bandwidth, and memory capacity and bandwidth are increased without changing the basic machine architecture.

In order to fully utilize SPCs, the application software must also be scalable to exploit increased computing capacity as it becomes available with larger machine

configurations. Programming SPCs has been a major challenge impeding the greater success of such systems. Unfortunately, the traditional message-passing programming paradigm for these machines based on separate name spaces is tedious, time consuming, and error-prone for programmers. In contrast, the data-parallel or SPMD programming model provides an easier and more familiar programming style for users. The SPMD model is based on a single name space and loosely synchronous parallel computation with a distinct data set for each processor. In order to provide highlevel language support for data-parallel programming, several data-parallel Fortran languages have been proposed, such as Fortran D [1] and Vienna Fortran [2]. The High Performance Fortran Forum, composed of over forty academic, industrial, and governmental agencies, has developed HPF (High Performance Fortran) [3] in an effort to standardize data-parallel Fortran programming for distributed-memory machines. Many of the concepts originally proposed in Fortran D, Vienna Fortran, and other data-parallel Fortran languages have been incorporated in HPF. Dataparallel C [4], and pC++ [5] represent language design efforts focusing on C-based data-parallel extensions.

An essential part of HPF is the specification of the decomposition of data arrays through compiler directives. Due to the non-uniform memory access times characteristic of distributed-memory machines, determining an appropriate data decomposition is critical to the performance of data-parallel programs on these machines. The data decomposition problem involves data distribution, which deals with how data arrays

<sup>&</sup>lt;sup>1</sup>The research contained in this dissertation is presented in the context of HPF due to its emerging acceptance as a standard. With minor syntactic changes, the concepts proposed herein could be applied to other data-parallel Fortran languages as well.

should be distributed among processor memories, and data alignment, which specifies the collocation of data arrays. The goal of data decomposition is to maximize system performance by balancing the computational load among the processors and by minimizing remote memory accesses (or communication messages). To facilitate data distribution onto an application-dependent, rather than a machine-dependent, topology, an HPF programmer declares a multi-dimensional mesh of logical (or virtual) processors. The mapping of the logical processors to the physical machine is determined by the compiler or run-time system.

HPF provides flexible primitives for specifying data decompositions; however, it does not provide the programmer any guidance in selecting a suitable data decomposition. Given the large number of distribution and alignment possibilities, it is inherently difficult for programmers to select an appropriate decomposition which maximizes program performance. Mace [6] proved that determining an optimal data distribution, even for one- and two-dimensional arrays is NP-complete. Li and Chen [7] proved that finding a set of alignments for the indices of multiple program arrays that minimizes data movement among the processors is also NP-complete. A number of heuristics for determining suitable distributions and alignments have been proposed in the literature.

Assuming a viable technique for selecting an appropriate data decomposition, the best possible performance may not be achieved with only a single data distribution or alignment for the entire program. Depending upon the algorithm and its data-parallel implementation, a particular data decomposition that is well-suited for one phase of an algorithm may not be good, in terms of performance, for a subsequent

phase. Therefore, many data-parallel languages define mechanisms for explicit runtime data redistribution and realignment.

#### 1.1 HPF Example

We illustrate the above data decomposition constructs in a small HPF code example for solving a linear system of equations. Figure 1.1 illustrates an HPF program for solving the system Ax = b using Gaussian elimination and subsequent backward substitution [8]. The basic idea of the algorithm is to reduce the matrix A to upper triangular form in the first phase and then to use backward substitution to diagonalize the matrix. In the program, A is declared as an  $n \times (n+1)$  array, where the (n+1)st column of A stores the constant vector b. Following the array declarations are a set of compiler directives, including alignment and distribution primitives described earlier. Statements s7-s8 demonstrate the alignment of two different data vectors to the rows of A, while statement s9 shows the alignment of another array to the (n+1)st column of A. Statement s10 declares a vector of n logical processors. The matrix, along with its aligned data, is distributed by contiguous rows in statement s11 onto the logical processor array. Statement s27 specifies a run-time redistribution of data between the Gaussian elimination phase (s13-s26) and the backward substitution phase (s28-s33). Note that this code segment merely illustrates HPF constructs and is by no means the most efficient algorithm.

```

PROGRAM LINSYS(A,x,n)

s1:

s2:

REAL INTENT (IN) :: A(:,:)

REAL INTENT (OUT) :: x(:)

s3:

INTEGER INTENT (IN) :: n

s4:

INTEGER xindx(n)

s5:

REAL intrm(n), temp(n)

s6:

!HPF$ ALIGN x(:) WITH A(*,:)

s7:

!HPF$ ALIGN xindx(:) WITH A(*,:)

s8:

!HPF$ ALIGN intrm(:) WITH A(:,n+1)

s9:

s10: !HPF$ PROCESSORS P(n)

s11: !HPF$ DYNAMIC, DISTRIBUTE A(BLOCK,*) ONTO P

s12: FORALL (i = 1:n) xindx(i) = i

s13: DO i = 1, n

s14:

maxloc = MAXLOC(A(i,i:n))

s15:

maxval = A(i, maxloc)

temp = A(:,maxloc)

s16:

s17:

A(:,maxloc) = A(:,i)

s18:

A(:,i) = temp

s19:

tempx = xindx(maxloc)

s20:

xindx(maxloc) = xindx(i)

s21:

xindx(i) = tempx

s22:

A(i,i:n+1) = A(i,i:n+1) / maxval

s23: !HPF$ INDEPENDENT (j,k)

s24:

FORALL (j = i+1:n, k = i+1:n+1)

s25:

A(j,k) = A(j,k) - A(j,i) * A(i,k)

s26: END DO

s27: !HPF$ REDISTRIBUTE A(CYCLIC, *)

s28: intrm(n) = 0

s29: DO i=n, 1, -1

x(xindx(i)) = (A(i,n+1) - intrm(i)) / A(i,i)

s30:

s31:

FORALL (j = i-1:1:-1)

intrm(j) = intrm(j) + (A(j,i) * x(xindx(i)))

s32:

s33: END DO

```

Figure 1.1: HPF Linear System Solver

#### 1.2 Motivation

Two-dimensional and three-dimensional FFT (Fast Fourier Transform) [9] and ADI (Alternating Direction Implicit method) [10] are frequently cited examples for which efficient data redistribution between algorithm phases results in increased performance. Use of redistribution mechanisms, however, involves communicating program data arrays among the nodes of the machine resulting in interprocessor communication overhead. Data redistribution may require a temporary interruption of application-useful computation while processors await their new data. Consequently, there is a performance tradeoff between the higher efficiency of a new data decomposition for a subsequent algorithm phase and the time required to establish it.

Many researchers have espoused the necessity of incorporating a redistribution capability into Fortran- and C-based data-parallel languages. The Kali language [11] was one of the first to incorporate run-time data redistribution mechanisms. DINO [12] addresses the implicit redistribution of data at procedure boundaries. The Hypertasking compiler [13] for data-parallel C programs incorporated a run-time redistribution facility. Both Vienna Fortran [14] and Fortran D [15] specify data redistribution primitives as well.

While data-parallel languages provide run-time primitives that facilitate an explicit change in data decomposition, implicit data redistribution is possible as well. Array assignment statements, subprogram boundaries, and array realignment are implicit sources of redistribution in data-parallel programs. For instance, consider two arrays: A and B whose distributions are different. The assignment statement A=B

causes an implicit redistribution of array B to match the distribution of array A. At subprogram boundaries, data redistribution occurs when the distribution of actual parameters to a subprogram do not match the distribution of the dummy arguments in the subprogram interface. Finally, realignment of data can require the redistribution of data to satisfy the chosen new alignment.

Many data-parallel languages define dozens of language intrinsics that could be implemented as software libraries, significantly simplifying the role of the language compiler. Data redistribution is one type of operation whose implementation can be provided as a software library. Providing a rich set of libraries to data-parallel programmers is becoming increasingly popular because libraries offer some unique advantages [8]. For instance,

- A uniform interface provided by the library enhances the portability of programs among various distributed-memory architectures.

- Although a library provides a uniform interface to programs, the design and implementation of the library can explicitly exploit machine specific features to provide better performance.

- The program development cycle for the consumer of the library can be shortened as the correctness of libraries can be independently verified.

- The existence of libraries can simplify the tasks that the data-parallel compilers would otherwise have to perform.

As there are multiple sources of redistribution in a data-parallel program, even when it is not explicitly invoked by the programmer, we contend that research in the area of data redistribution in distributed-memory machines has particular merit. Changing array data decompositions within a program may yield substantial performance gains, but only if the overhead of such operations is mitigated. Therefore, the

efficient and scalable implementation of data redistribution mechanisms is important to the overall performance of data-parallel programs on SPC architectures.

The term scalability has been used extensively in the parallel processing community to characterize the ability of parallel architectures and algorithms to exhibit greater performance as more processors are employed to solve a problem. However, the term "performance" is equivocal as it may be used to identify widely varying algorithmic or architectural properties: speedup, execution time, processor speed or efficiency, or the quality (accuracy) of a solution. Many of these properties have been used either separately or in conjunction to describe the scalability of parallel algorithms and architectures. The ambiguity regarding scalability leads us to ask several questions: How are the relative scalabilities of parallel algorithms and machines related? Can a universal definition of scalability be applicable to all scenarios? How can scalability be quantified? If scalability can be quantified, which property best describes it, or is scalability a combination of factors? Answers to these questions are relevant to providing scalable redistribution methods.

Efficient and scalable data redistribution necessitates consideration of many issues. First, redistribution is a communication-dominant task, thus, the efficiency of the communication mechanisms used is of great importance. For instance, the relative merits of point-to-point or collective communication for redistribution must be considered along with the tradeoffs of using blocking or non-blocking message-passing. Second, the amount of data communicated between processors during redistribution is a significant factor in the total execution time of the operation. Consequently, methods for reducing the amount of data that must be exchanged via message-passing

may benefit redistribution performance. Third, to be viable to potential data-parallel programmers and compilers alike, efficient redistribution must consider the obtained performance as data and processor configuration sizes as scaled. Quantification of redistribution scalability using relevant performance metrics facilitates comparison of different techniques. Fourth, to the extent possible, efficient redistribution mechanisms should be portable among distributed-memory machines to enhance their utility in today's heterogeneous high-performance computing environments.

#### Problem Statement

The efficient operation of implicit and explicit data redistribution on distributed-memory architectures can greatly impact the overall performance of data-parallel programs. This dissertation investigates language, data mapping, message-passing, and scalability issues, all of which affect the performance of data redistribution. This dissertation is distinguished as the earliest known research to propose a portable and scalable redistribution library, processor-data mapping techniques for optimizing data exchange, and a framework for quantifying the scalability of data redistribution on SPC platforms.

#### 1.3 Organization of Dissertation

Chapter 2 discusses static (distribute and align) and dynamic (redistribute and realign) data decomposition. Salient data redistribution issues are discussed and related work is summarized. Chapter 3 presents a technique for partitioning (or mapping)

data onto processor memories that facilitates the minimal amount of data exchange among processor memories during redistribution between a large class of regular HPF distribution patterns. The technique is independent of the underlying machine architecture, and thus it is portable among distributed-memory platforms. We prove the optimality of the technique with respect to minimizing the amount of data exchanged. Chapter 4 proposes a data redistribution library, DaReL, for distributed-memory machines that utilizes the emerging message-passing standard, MPI [16]. The library supports multi-dimensional data redistribution among arbitrary regular HPF distribution patterns. A uniform interface to DaReL is defined, facilitating its potential incorporation into a data-parallel compiler. Chapter 5 proposes a framework for quantifying scalability that incorporates end-user requirements to enable quantification of the scalability of parallel algorithm-machine combinations, or pairs. We illustrate the framework with a matrix multiplication case study to assess the relative performance of several different algorithm-machine pairs. Chapter 6 presents performance and scalability results. We demonstrate redistribution performance improvements of up to 40% using the processor mapping technique (Chapter 3) on a distributedmemory machine, an IBM SP-x.<sup>2</sup> We address the impacts of the mapping technique on the data-parallel programmer and compiler, respectively. We extend the scalability framework (Chapter 5) to quantify DaReL's performance as data and processor configuration sizes are scaled. Chapter 7 concludes the dissertation with a summary of the major contributions and suggests potential future research directions.

<sup>&</sup>lt;sup>2</sup>SP-x denotes an IBM SP multicomputer consisting of SP-1 processors and an SP-2 network switch.

# Chapter 2

# **Data Decomposition**

Due to their non-uniform memory access times, determining an appropriate data decomposition among different memories is critical to the performance of data-parallel programs on distributed-memory machines. The goal of data decomposition is to maximize system performance by balancing the computational load among the processors and by minimizing remote memory accesses. Data-parallel languages, e.g., HPF, support compiler directives that statically specify the decomposition of data to processor memories prior to program execution. Additionally, these languages support modification of data decompositions during run-time in favor of a different one that, presumably, is better suited to the ensuing computation. Existing data-parallel Fortran languages, however, provide no inherent capability for determining static data placement nor run-time modification of data decomposition. This chapter surveys research in the area of data decomposition with particular emphasis on data redistribution issues.

#### 2.1 Static: Align and Distribute

In HPF, data arrays are aligned relative to one another and then, as a group, they are distributed onto an abstract, or logical, processor configuration. This process of static data decomposition is accomplished with the !HPF\$ ALIGN, !HPF\$ DISTRIBUTE, and !HPF\$ PROCESSORS compiler directives. These directives do not affect the result of the program, rather they suggest an implementation strategy to the compiler. Therefore, these directives may only appear in the declaration part of an HPF program.

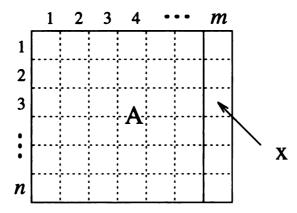

The !HPF\$ ALIGN directive specifies the collocation of data array elements from distinct arrays. Figure 2.1 illustrates a possible alignment of an array,  $\mathbf{x}$  to the m-th column of an  $n \times m$  matrix  $\mathbf{A}$ . For aligning multiple arrays to one another, it is sometimes convenient to define an HPF template. The !HPF\$ PROCESSORS directive defines a processor configuration as a multi-dimensional mesh of processors. Data arrays, or templates, are mapped onto a processor configuration with the !HPF\$ DISTRIBUTE directive. The programmer applies an HPF distribution pattern to each dimension of a data array specifying the mapping of the data dimension onto a dimension of the processor configuration. The number of data dimensions must equal the number of processor dimensions. BLOCK, CYCLIC, BLOCK(b), and CYCLIC(c) comprise the set of regular data distribution patterns in HPF; \* denotes the absence of a distribution pattern for a dimension, i.e., the entire dimension is allocated to the processor. [17] discusses possible HPF language extensions to permit user-defined array distribu-

<sup>&</sup>lt;sup>1</sup>The mapping of logical processors onto the physical nodes of the machine is not within the scope of HPF. Henceforth, we assume *logical* processor when we write processor, unless otherwise stated.

tion patterns.<sup>2</sup> With these mechanisms, the program data is aligned and distributed among the processors. By HPF's owner-computes rule, the processor that stores the data element on the left-hand side of a program statement is responsible for computing its update. Thus, the distribution of computation is determined by the decomposition of data.

Figure 2.1: Example of HPF alignment

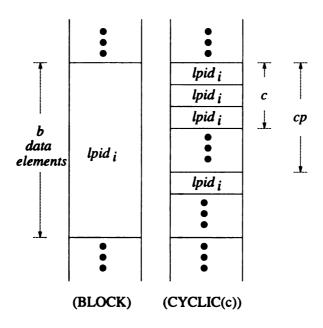

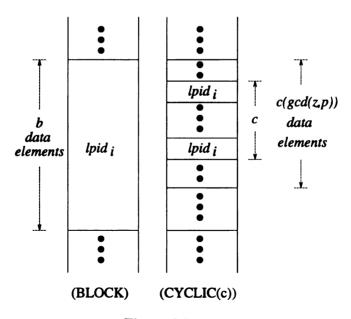

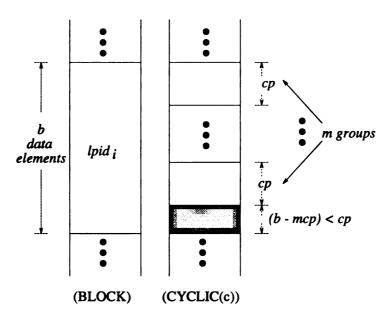

With the BLOCK specification, contiguous blocks of an array are distributed to each processor. If n is the data size along a given dimension and p denotes the number of processors, the block size is  $\lceil \frac{n}{p} \rceil$  for the first p-1 processors, the last processor receiving the residual if it does not receive a full block. With the CYCLIC distribution, elements of a dimension of an array are assigned to each processor in a round-robin fashion. An extension of BLOCK and CYCLIC are the BLOCK(b) and CYCLIC(c) distribution patterns. With BLOCK(b), each processor is assigned a data segment of size b, with the restriction that  $n \leq p \times b$ , while CYCLIC(c) distributes round-robin contiguous blocks of size c to each processor. By definition, CYCLIC is equivalent to CYCLIC(1). BLOCK(b) and CYCLIC(c) imply the same distribution when

<sup>&</sup>lt;sup>2</sup>This dissertation focuses on regular distribution patterns as defined in the original language specification.

b=c and  $n \leq p \times b$ ; however, BLOCK(b) additionally asserts that there is no wrap-around. The potential round-robin effect, when  $n > p \times c$ , of CYCLIC(c) may be difficult to discern at compile-time if c is an expression.

Figure 2.2 illustrates various data distribution examples: (a) and (b) show an eight-element vector distributed BLOCK and CYCLIC, respectively, on four processors; (c) illustrates CYCLIC(c) where c = 2 on two processors; (d), (e), and (f) show various possible distributions for an  $8 \times 8$  data matrix. The distributions for (d)-(f) are shown as an ordered pair: the first pattern applies to the row dimension while the second pattern applies to the column dimension. The processor IDs, indicating data ownership, are shown in italics: in (a)-(c) they are superimposed over the data, while in (d)-(f) they are shown as Cartesian coordinates. Processor IDs are numbered beginning with  $\theta$ . Recall that, the \* denotes the absence of a distribution pattern for a dimension. The row dimension is not distributed in (f).

Figure 2.2: One- and two-dimensional HPF data distributions.

Figure 2.2 shows only a few of the many possible distributions for the one- and two-dimensional data. Recall that depending upon the application algorithm, the choice of data distribution will affect the computational load balance and the size and number of remote memory accesses when implemented on a distributed-memory machine. Selecting the optimal distribution is NP-complete as stated in Chapter 1. The situation is further complicated when one considers the possible data array alignments. Automatically determining array alignments is an active area of research [18]. Several heuristics have been proposed to automatically determine an appropriate data decomposition based on the application code. A survey of some of these heuristics and their limitations and drawbacks can be found in [19]. Anderson and Lam [20] present a mathematical framework for systematically determining data decompositions. A first-order model for reducing the search space of possible distributions to a select few based on architecture-specific communication and computation parameters can be found in [21]. Xu and Ni [22] propose low-complexity algorithms for determining array alignments in an effort to maximize processor load balance while minimizing interprocessor communication. Ponnusamy, et al. [23] focus on automatic selection of data distributions for irregular problems, i.e., programs for which the data access patterns are input-dependent. Lee and Tsai [24] propose a dynamic programming technique for determining data distributions.

The HPF programmer specifies an initial distribution of data onto a set of logical processors as discussed previously. The data mapping, from the programmer's perspective, is independent of the underlying machine topology and physical processor IDs. The mapping of the logical processor IDs to the physical nodes of the machine

is relegated to the compiler. To facilitate efficient program execution, the logical to physical processor mapping must consider the machine topology, communication subsystem, memory capacity, and number of nodes [25]. Chittor and Enbody [26, 27] investigate logical to physical processor mapping for wormhole-routed architectures.

#### 2.2 Dynamic: Realign and Redistribute

Run-time data redistribution has been shown to improve the performance of FFT and ADI. HPF defines run-time primitives for changing data alignment (!HPF\$ REALIGN) and distribution (!HPF\$ REDISTRIBUTE). These constructs may be inserted anywhere in the executable portion of a program to change the alignment or distribution of the global data arrays or templates. Henceforth, we shall refer to the aggregate program data as the global data and the data owned by each processor, from the perspective of the processor, as its local data.

To determine the appropriateness of utilizing these run-time primitives, an HPF programmer must consider the tradeoff between the anticipated increased performance of a new distribution or alignment and the cost of changing the data decomposition which typically involves interprocessor communication. Given the difficulty of estimating the execution time of a phase of an algorithm with a particular decomposition, the effective use of realignment and redistribution is an important research issue. Chatterjee, et al. [28] propose a model for assessing realignment cost, and they formulate the alignment problem as an optimization of realignment cost. Algorithms for automatically determining good mobile alignments, i.e., alignments which are a

function of the loop induction variable, are presented. Kunchithapadam and Miller [29] present a graph-coloring technique for recording data movement among nodes during program execution. They propose a simple algorithm to optimize the graph coloring to describe new distributions which would result in reduced communication. Thus, the technique identifies places within a program's execution where redistribution can effect greater program performance.

In contrast to HPF's approach to user-specified static and dynamic data decompositions, techniques for automatic data decomposition are proposed in [20]. The compiler, rather than the programmer, determines the decomposition of data for each program loop. Redistribution is viewed as an implicit activity to be undertaken when the decomposition of an array in a loop differs from the decomposition of the same array in another (subsequent) loop. They propose a graph model, where nodes represent loops and edges represent redistribution communication costs between loops. A greedy algorithm for eliminating edges with large weights, thereby eliminating costly redistributions, is presented. The elimination of the redistributions deemed to be too costly, however, is achieved at the cost of reduced parallelism in the resulting code. Chase and Reeves [30] propose a similar approach for automatically performing array redistribution. Arrays are grouped into compatibility classes, i.e., aligned together and distributed. The compiler inserts assertions about the classes into the code, and these assertions are checked during run-time to discern whether a redistribution is necessary. Should a compatibility relationship change, redistribution is performed. Unfortunately, the cost/benefit tradeoff of redistribution is not addressed.

Many researchers have espoused the necessity of incorporating a redistribution

capability into data-parallel languages. The Kali language [11] was one of the first to incorporate run-time data redistribution mechanisms. DINO [12] addresses the implicit redistribution of data at procedure boundaries. Hall et al. [15] discuss global optimizations that can be employed to a set of redistribution calls in a Fortran D program. The Hypertasking compiler [13] for data-parallel C programs incorporated a run-time redistribution facility. To avoid packing and unpacking of data and ownership calculation in some instances, the Hypertasking compiler performs data redistribution by moving an entire data set around to all processors, each processor removing its portion. Chapman et al. [14] introduce Vienna Fortran's dynamic data distribution capability and discuss the high-level implementation of it in the Vienna Fortran Engine (VFE).

#### 2.3 Example of Redistribution in HPF

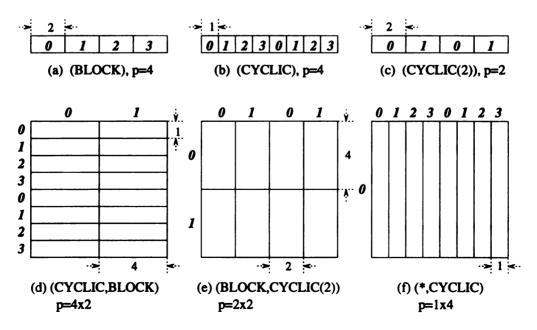

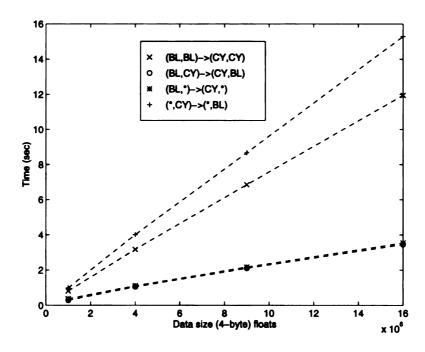

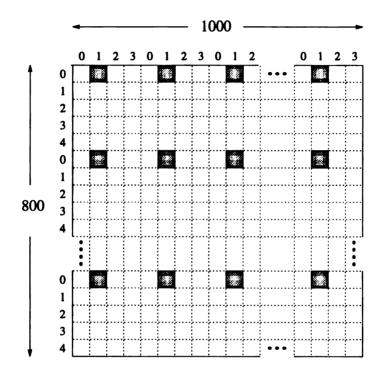

Figure 2.3 presents a segment of HPF code illustrating the use of data redistribution in HPF. A  $20 \times 12 \times 10$  array of real numbers,  $\mathbf{A}$ , is initially distributed onto a three-dimensional processor configuration,  $\mathbf{P}$ , with distribution patterns \*, BLOCK, and CYCLIC applied to the three dimensions, respectively. P contains forty processors and each processor owns  $\frac{20\times12\times10}{40}=60$  data elements. Following some amount of computation,  $\mathbf{A}$  is redistributed with a new set of patterns, CYCLIC, CYCLIC, BLOCK, onto a different shape logical processor configuration,  $\mathbf{Q}$ . Figure 2.4 illustrates the initial distribution of  $\mathbf{A}$  (left) and its subsequent redistribution (right). The shaded portions of the figure depict the data elements of  $\mathbf{A}$  owned by processor (0,0,0).

Whereas (0,0,0) owns data in globally contiguous locations initially, it owns data in globally *non*-contiguous locations following redistribution. Note that processor configuration Q also consists of forty processors; however, P and Q vary in shape.

The example illustrates one redistribution possibility; many more distinct combinations of source and destination distribution patterns are possible. The HPF programmer has great flexibility in declaring data and processor configurations of arbitrary dimension. Recall, however, that HPF restricts the programmer to have the same dimensionality for the data, processor, and distribution pattern declarations, e.g., in Fig. 2.3, the data, processor, and pattern declarations are all threedimensional. HPF does not require that the source and target processor configurations have equal size.

# 2.4 Rudimentary Operation of Data Redistribution

Henceforth, we denote the initial (source) distribution pattern(s) of a program as  $D_s$  and the destination (target) distribution pattern(s) as  $D_t$ . Similarly, we shall refer to the source and target processor configurations as  $P_s$  and  $P_t$ , respectively. Note that  $D_t$  and  $P_t$  are embedded in the !HPF\$ REDISTRIBUTE primitive in Fig. 2.3.

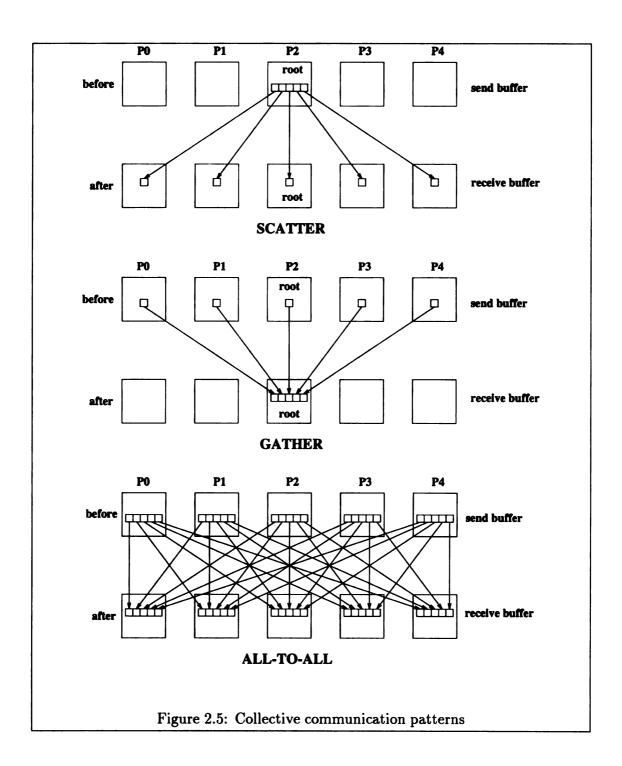

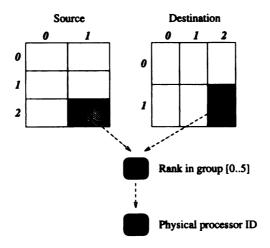

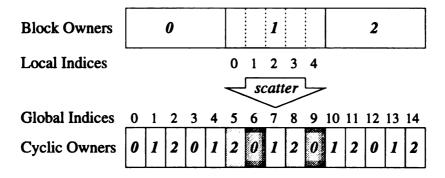

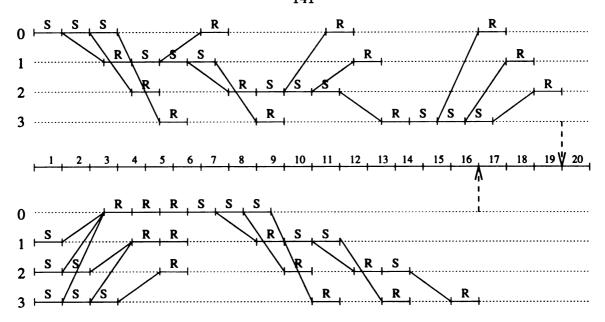

The previous example illustrates that data redistribution results in changing the mapping of data to processors, thus necessitating data exchange among the processors. From the perspective of a sending processor, the data exchange is viewed as a scattering of data elements to the processors in  $P_t$ , i.e., the sending of distinct data elements to each processor in the target processor configuration. This paradigm is illustrated in the top portion of Fig. 2.5. From the perspective of a receiving processor, the data exchange is viewed as a gathering of data elements from the processors in  $P_s$ , i.e., the receiving of distinct data elements from each processor in the source processor configuration. This paradigm is illustrated in the middle portion of Fig. 2.5. When  $P_s = P_t$ , data exchange is viewed as an all-to-all personalized communication as illustrated in the bottom portion of Fig. 2.5.

In order to perform data redistribution between  $D_s$  and  $D_t$ , a processor must determine the identity of the processors from which it is to receive data as well as the identity of processors to which it must send data. Once these sets are computed, processors exchange their data. Recall that we have defined redistribution between logical processors; therefore, the logical to physical processor mapping determines the actual data movement among the memories of the machine. For example, logical processors mapped to the same physical node would obviously not require message-passing to exchange data.

#### 2.4.1 Determination of Processor Send and Receive Sets

Several research efforts have focused on efficient methods for determining the send and receive processor sets for redistribution. Gupta et al. [31] derive closed form expressions for these communication sets based on Fortran D's (BLOCK), (CYCLIC), and (BLOCK-CYCLIC) distribution patterns. In this approach, global array (or template) indices combined with knowledge of  $D_{\bullet}$  and  $D_{t}$  are used to compute the send and receive sets. An alternative approach [32] is for each node to scan its local data array once, determine the destination processor for each element and place the element in a message packet bound for that processor. In [32], one-dimensional data redistribution is performed by distinct algorithms for different combinations of distribution patterns for  $D_{\bullet}$  and  $D_{t}$ . Distinct algorithms are proposed in order to introduce optimizations that apply only to the given case. Multi-dimensional redistributions are implemented as a series of (sequential) one-dimensional redistributions. This approach to multidi-

mensional redistributions is unnecessarily costly and does not scale well. Stichnoth et al. [33] propose methods for computing ownership sets for array assignment statements. Due to the similarity of determining send and receive sets, they advocate computing these together on the sending processor and communicating the information together with the data to a receiver. While this approach is chiefly intended for communicating right-hand side operands, it can be incorporated into data redistribution. Ramaswamy and Banerjee [34] propose a mathematical representation for regular distributions called PITFALLS, which facilitates determining the processor sets for data redistribution. PITFALLS robustly handles arbitrary source and target processor configurations and arbitrary number of data array dimensions in a scalable manner. PITFALLS is being developed for inclusion in the PARADIGM [35] compiler project at the University of Illinois. The research presented in [31, 32, 33, 34] focus on the efficiency of computing send/receive processor sets, excluding the actual data exchange portion of redistribution which can be several orders of magnitude more costly, in terms of execution time, than send and receive set determination; see Chapter 6.

#### 2.4.2 Data Exchange with Message-Passing

Data exchange on a distributed-memory machine is performed with either pointto-point or collective communication message-passing primitives. In an effort to standardize message-passing primitives on distributed-memory platforms, the MPIF (Message Passing Interface Forum) [16] was founded. MPI defines a host of pointto-point and collective primitives. Collective communication primitives such as MPI\_Scatter, MPI\_Gather, or MPI\_Alltoall may achieve lower communication latencies and less network contention than straightforward point-to-point routines if implemented to effect parallelization in communication. Techniques for efficient multiple scatter and gather operations are presented in [36]. To achieve a higher performance, the scatter and gather operations may be optimized for the specific architecture. Portability of a redistribution implementation that utilizes MPI primitives would be ensured among platforms which conform to the MPI standard. A data redistribution library utilizing MPI is described in Chapter 4. McKinley et al. [37] survey issues related to efficient collective communication in wormhole-routed machines. Of particular relevance to data redistribution, they review techniques for all-to-all personalized communication.

The efficiency of the simultaneous redistribution of data among physical processors is affected by the topology, routing, and switching mechanisms of the underlying machine. The routing mechanism, such as dimension-order routing [38, 39] for hypercube and mesh-connected machines, affects communication latency. A technique for communication-efficient data redistribution which addresses message contention for certain topologies is presented in [40]. The authors propose a data redistribution communication cost model which parameterizes the number of messages and their sizes. Network contention is modeled by expressing the communication as a sequence of permutations which may be executed in a fixed number of (contention-free) steps. *Multi-phase* redistribution is defined as redistributing data to intermediate distribution patterns, eventually arriving at the destination distribution. The model is

used in conjunction with multi-phase redistribution to show that lower overall cost can be achieved as compared to single-phase redistribution. Redistributing perfect power-of-two sized arrays on hypercubes is discussed in [41].

As static distribution of a data array or template causes the distribution of all aligned data; redistribution of those arrays or templates causes the redistribution of aligned data as well. Depending upon the data alignment(s), there may be more data distributed to some processors than others. Thus, during redistribution, the amount of data to be exchanged among processor memories could vary significantly, resulting in an unbalanced communication load. This situation could increase the time of the redistribution operation for some physical nodes.

## 2.5 Implicit Redistribution

While the example in Figs. 2.3 and 2.4 illustrates explicit run-time redistribution of data arrays, other program statements or HPF constructs can cause the *implicit* redistribution of data. For instance, array assignment statements, !HPF\$ REALIGN, and subprogram interfaces may cause implicit data redistribution in data-parallel programs.

Consider two arrays A and B that are distributed BLOCK and CYCLIC, respectively.

The assignment statement A=B causes an implicit redistribution of array B to the distribution of array A. While such an assignment is not the same as a redistribution of B, the former operation must perform the same functions as the latter, e.g., computing processor sets and exchange of data. This type of redistribution may occur frequently

in data-parallel programs with many arrays that have dissimilar distributions.

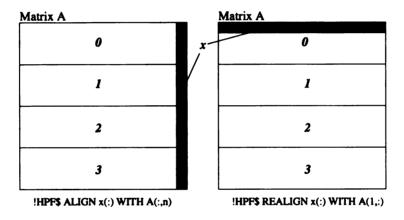

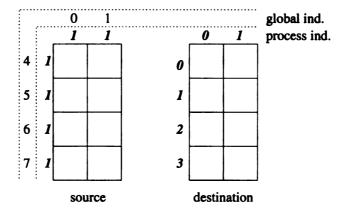

Figure 2.6 illustrates how realignment can cause implicit data redistribution. Initially, x is aligned to the last column of A; then it is shown realigned to the first row of A. With the (BLOCK,\*) distribution, this would cause the implicit redistribution of a portion of x from processors 1, 2, and 3 to processor 0. Processor 0 must remap its own local data set to conform to the new alignment. Realignment, like static alignment, may cause an unbalanced communication load since processors may not own equal amounts of data.

Figure 2.6: Realignment of x causes redistribution.

Implicit redistribution can occur at subprogram (subroutine) boundaries. If a distribute or align directive is applied to a dummy argument specified in a subprogram interface, then HPF requires that the corresponding actual parameter to the subprogram conform with the dummy argument's decomposition. If the dummy argument specifies a decomposition that differs from the actual parameter, implicit data redistribution and/or realignment is necessary. Additionally, upon return to the main program, the original decomposition of the parameter data arrays must be re-established. Thus, there are two redistributions and/or realignments necessary

REAL A(20,20)

!HPF\$ DISTRIBUTE A(\*,BLOCK)

• • •

CALL SUB(A)

SUBROUTINE SUB(Z)

REAL Z(20,20)

!HPF\$ TEMPLATE T(20,20)

!HPF\$ DISTRIBUTE T(BLOCK, BLOCK)

!HPF\$ ALIGN WITH T::Z

Figure 2.7: Redistribution at subprogram interface

for each parameter. Figure 2.7 demonstrates this type of implicit redistribution. In this case, the actual parameter, A, originally distributed (\*,BLOCK) is redistributed (BLOCK, BLOCK) to conform with the distribution of the dummy parameter, Z.

Programmers will attempt to optimize the subprogram with a particular data decomposition [20], so long as the change in decomposition does not result in higher overhead than the performance benefit of a new decomposition. Remapping of the actual parameter to the dummy argument can be overridden with HPF's INHERIT attribute. This attribute specifies that the dummy argument takes on the data decomposition of the actual parameter, whatever it may be. Providing for any legal distribution in a library, however, may be complicated and may not be cost effective [8].

Johnsson discusses redistribution at subroutine calls in the context of designing subroutine libraries [42]. He cites the ability to communicate data decomposition information to the subroutine, and subsequent determination of whether to use redistribution or realignment, as salient issues. These issues are explored in the design of

FFT and matrix-vector multiplication subroutines. Hall et al. [15] propose insertion of redistribution primitives in the caller, rather than the callee. This approach is shown to lead to compiler optimizations, for instance, the elimination of unnecessary redistributions.

## 2.6 Redistribution Optimizations

Due to the overhead cost that data redistribution represents, it can be beneficial to explore optimizations that can reduce the execution time of data redistribution. For instance, data that is to be redistributed at a certain point in program execution may not be referenced in subsequent computation. Certainly, for correct program execution, such data need not be redistributed. For example, suppose the redistribution of a template T with aligned arrays A and B is called for, but only B is used in subsequent computation; redistribution of A would be unnecessary for correct program semantics. If the compiler is able to recognize such a situation, then the data could be left in place, reducing the redistribution cost. If such data represented a significant portion of the whole and could be recognized by the compiler as unused in later computation, then this optimization may prove useful. Less straightforward situations, however, may prove more difficult to optimize. For instance, say that A is a large matrix which is to be redistributed, but only a fraction of its elements will be accessed subsequently. A desirable optimization would be to only redistribute data elements which will be referenced later.

Pipelined redistribution of data is another possible optimization considered by

several researchers. Strip Mining Redistribution [43] is a technique whereby the data to be communicated in a redistribution is temporally overlapped with the subsequent computation phase. Rather than redistribute all the data prior to resuming algorithmic computation, data is redistributed in a pipelined manner. A key issue in this technique is the ability to identify the computation pattern under the destination distribution pattern and to arrange the communication schedule to enable significant overlapping with computation. The technique is shown to have speedups of up to 1.7 over "massive redistribution", i.e., non-pipelined, when the data sizes are relatively large compared to message start-up latencies. Strip Mining Redistribution is limited to two-to-one and one-to-two dimension redistributions so that the size of the individual messages fed into the pipe are large enough to amortize message startup cost. Explicit Data Placement (XDP) [44, 45] is similar to Strip Mining Redistribution in that it facilitates pipelined data redistribution. A novel feature of this approach is the unified treatment of data and ownership transfer<sup>3</sup> to allow for compiler-recognizable optimizations. Using a 3D FFT application as an example, XDP is shown to facilitate overlapped data redistribution with algorithm computation. Unfortunately, no performance data illustrating the performance of the proposed method are given.

Various message-level optimization techniques, such as message coalescing, message aggregation, and message pipelining [25] may prove useful in data redistribution.

Message coalescing involves the combining of separate references to the same array.

Message aggregation combines messages from distinct arrays to the same processor.

Message pipelining attempts to hide communication latency through the separation

<sup>&</sup>lt;sup>3</sup>In contrast to HPF's owner-computes rule.

of send and receive primitives. Message aggregation, for example, could be utilized to combine aligned data in a common message buffer for redistribution to another processor. Techniques for applying these optimizations to the data movement problem, when the owner-computes rule is relaxed, are presented in [46].

Prior to data redistribution, whether using !HPF\$ REDISTRIBUTE or at a subprogram interface, the logical to physical processor mapping is already determined for the initial data distribution, *i.e.*,  $D_s$ ; however, it is possible to manipulate the data element/logical processor mapping in the target, *i.e.*, the mapping of  $P_t$  onto  $D_t$ , so long as the semantics of the target distribution pattern are not violated. For instance, in Fig. 2.2 (b), the mapping of processors to data elements is in increasing processor number order, *i.e.*, 0,1,2,3. This mapping, however, need not be in increasing order. For instance, the mapping order could be permuted to be 0,2,1,3. The alternative mapping does not violate HPF semantics and can lead to possible run-time optimizations. In Chapter 3, we present a theory for permuting the processor-to-data mapping for HPF patterns.

Wakatani and Wolfe [47] propose a technique for mapping logical to physical processors in a data redistribution library that can reduce communication overhead. This technique assumes an underlying torus topology and maps the data in such a way that communicating processors are partitioned into non-overlapping sets, *i.e.*, there is no channel contention between sets. Thus, by keeping communication local to a group, message contention on the physical network, presumably, is reduced. The drawback of this approach is that the logical to physical data mapping is based on "local" information. In other words, the technique imparts a mapping based solely

on what is best to optimize redistribution. However, since the logical to physical data mapping must remain consistent throughout the execution of a data-parallel program, the chosen mapping may increase communication cost elsewhere. We assert that the compiler, privy to global information, *i.e.*, the entire data-parallel program, ought to determine the logical to physical processor mapping.

# Chapter 3

# **Data Mapping Optimization**

Since interprocessor communication is the predominant source of redistribution execution time, minimizing the total amount of data movement among processor memories may increase redistribution performance. This chapter presents a technique, based on logical processor to data element mapping, that minimizes the total amount of data movement among processor memories for BLOCK to CYCLIC(c), and vice-versa, redistributions. We present mapping functions for one-to-one, m-to-m, one-to-two, and two-to-one dimension data redistributions, and we prove their optimality. The proposed methodology is architecture-independent facilitating its potential integration into distinct redistribution implementations for different distributed-memory architectures.

In Chapter 6, we discuss the possible impacts on the programmer and compiler of using the optimal mapping technique. We show that the technique offers the programmer extra flexibility in determining data placement in some instances. Additionally, the technique could be used in a straightforward manner by a compiler. We demon-

strate redistribution performance improvements over the traditional data-processor mapping of up to 40% using the optimal technique on an IBM SP-x.

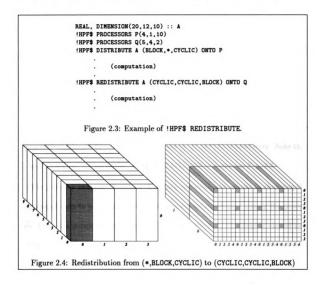

## 3.1 One-dimensional Logical Processor Mapping

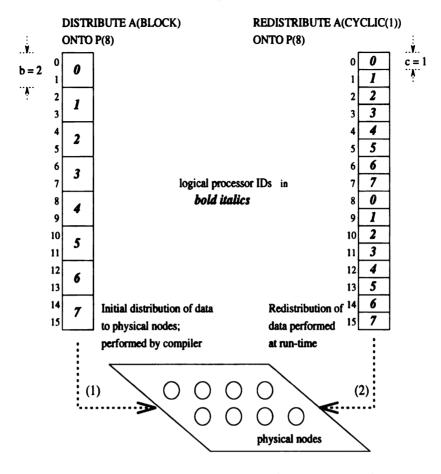

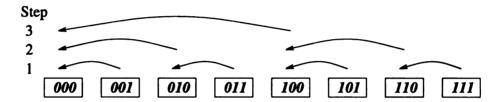

We begin by illustrating the utility of the mapping technique for one-dimensional data. Figure 3.1 illustrates an initial BLOCK distribution of a sixteen element data array, A, onto eight processors and a subsequent redistribution of the array using the CYCLIC pattern. The mapping of the initial distribution of data onto the physical nodes of the machine is established at program initialization; see arrow labeled (1). Subsequent redistribution among processors must retain a consistent logical to physical processor mapping; see arrow labeled (2). Logical processor IDs (lpids) are in bold italics and are superimposed over the data. Each processor owns two contiguous elements under BLOCK, but two non-contiguous elements, with a stride of p, the number of processors, under CYCLIC. The *lpids* are mapped in increasing numerical order as specified in [3]. We claim that this is an unnecessary restriction as any permutation of the lpids,  $\theta...7$ , can conform to the semantics of the CYCLIC pattern since data distribution to logical processors in HPF has no concept of the "ordering" of processors. CYCLIC requires only that the global data elements owned by a processor have global indices that are separated by a stride of p. For clearer presentation, we view the data as being static, and we manipulate the processor mapping to the data.

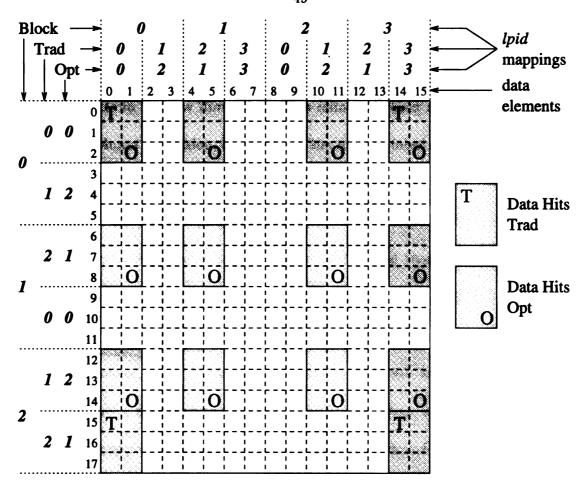

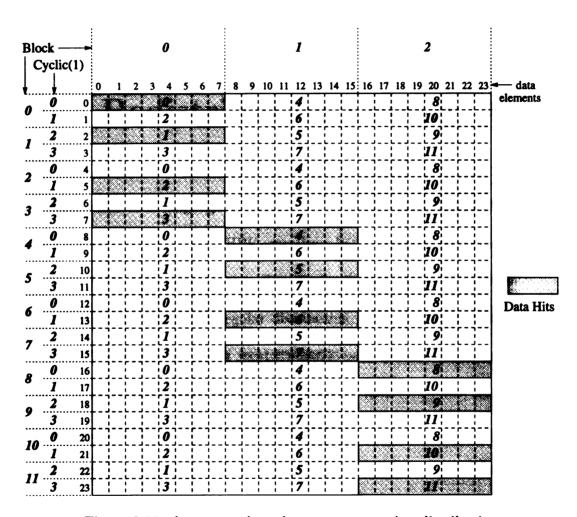

Figure 3.2 illustrates the benefit of permuting the *lpids* when mapping them to data elements. Using the same sixteen element array of Fig. 3.1, we show two alter-

Figure 3.1: Data Distribution and Redistribution onto physical nodes.

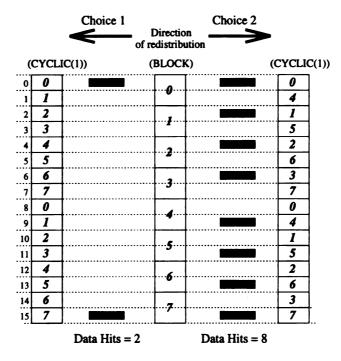

natives for redistributing the array cyclically. Choice 1 shows the conventional cyclic mapping of *lpids* to data. This results in only two of sixteen data elements (marked with filled rectangles) remaining on the same processor following redistribution. We call this the number of *data hits* among all processors. Choice 2 shows an alternative cyclic mapping with the *lpids* permuted, 0,4,1,5,2,6,3,7, which results in a total of eight data elements, one per processor, remaining on their original memories. This eliminates the exchange of six data elements among processors. Another advantage is that processors 1,...,6 must send data to two processors when using Choice 1, but only one processor each when using Choice 2, thus reducing the number of destinations. Each of these factors reduces interprocessor communication overhead. The reduction

in redistribution cost for the example in Fig. 3.2 is small given the size of the example. If we extend A to be sixteen million data elements with the same permutation of *lpids*, we eliminate the exchange of six million data elements across processors.<sup>1</sup>

Figure 3.2: Logical processor to data mapping alternatives.

### 3.1.1 Processor Mapping Technique

To consistently minimize the size of data transfer for arbitrary data block and processor set sizes, we develop a systematic method for determining a permutation of *lpids* to map to the data. The technique ensures that each processor retains the maximum amount of data possible while conforming to the semantics of the source and target distribution patterns,  $D_s$  and  $D_t$ .

We establish the upper bound on the ratio of the amount of data that can be

<sup>&</sup>lt;sup>1</sup>Assuming the number of processors is kept the same, the block size in BLOCK is two million, and the block size in CYCLIC(c) is one million.

retained on p processors to the total number of data elements, n. We present a function for determining an lpid to data mapping for redistribution from BLOCK to  $CYCLIC(c)^2$  that achieves the upper bound. We make the following assumptions:

- 1. Let p be the number of processors numbered 0..p-1, and n be the total number of data elements, numbered 0..n-1, distributed over p. We assume each processor owns b elements, thus b=n/p.

- 2. We consider redistribution between BLOCK and CYCLIC(c) patterns; the BLOCK(b) pattern, where b is a variable, is not considered; b = n/p by assumption 1. For CYCLIC(c), we assume that c divides b, i.e., b = cz for an integer z.

- 3. If the data is initially distributed among p processors, then we assume that the data is redistributed among p processors.

Extensions of the above assumptions to the general case will be discussed in Chapter 7.

**Definition 1** Define r as the number of data elements of the global array that remain (data hits) on their original processors following redistribution between BLOCK and CYCLIC(c). Define HitRatio as r:n and MaxHitRatio as the upper bound on HitRatio.

<sup>&</sup>lt;sup>2</sup>Redistribution is symmetric in terms the amount of data movement among processors, *i.e.*, redistribution from BLOCK to CYCLIC(c) or redistribution from CYCLIC(c) to BLOCK results in an equal amount of data movement.

**Lemma 1** Let b and c be the block sizes in the BLOCK and CYCLIC(c) patterns, respectively. If n = bp and z = b/c, where z is an integer, then MaxHitRatio =  $\lceil \frac{b}{cp} \rceil cp : n$  and HitRatio  $\leq$  MaxHitRatio.

**Proof:** Case 1: z = ip, for all  $i \ge 0$ , i is an integer. For every cycle of cp data elements, each  $lpid_j$ ,  $0 \le j \le p-1$ , maps to c contiguous data elements with CYCLIC(c). Since b = icp, there are i complete cycles of lpids that map to one complete data block owned by  $lpid_j$  under the BLOCK pattern. Processor  $lpid_j$  will map to exactly ic of the elements, i.e., there are ic data hits. For p processors, the number of data hits is  $icp = \left\lceil \frac{ip}{p} \right\rceil cp = \left\lceil \frac{b}{cp} \right\rceil cp$ . HitRatio is  $\left\lceil \frac{b}{cp} \right\rceil cp : n$ .

Case 2: (i-1)p < z < ip, for all i > 0, i is an integer. Since b < icp, there cannot be i complete cycles of lpids mapped to  $lpid'_js$  original block of data under BLOCK. Thus, the number of hits can be no greater than i for each lpid; consequently, the number of hits across all processors can be no greater than icp. The remainder of the proof follows as in Case 1.

MaxHitRatio is achieved with any permutation of lpids when z is an integer multiple of the number of processors, i.e., when z = ip. However, our goal is to achieve the upper bound for all values z where (i-1)p < z < ip. In order to satisfy this aim, we must consider different permutations of the lpids to maximize the number of data hits. Figure 3.2 demonstrates that not all permutations of lpids yield MaxHitRatio. Next, using the semantics of  $D_t$ , we define a function for determining a permutation of lpids to map to the data array.

#### 3.1.2 Mapping Function

Define a p-tuple,  $(q_0, q_1, q_2, ..., q_{p-1})$ , as p place holders. Let  $f: i \to j$  be a function that maps  $lpid_i$  to place holder  $q_j$  for  $0 \le i, j \le p-1$ . An assignment of each lpid to a place holder specifies a permutation of the lpids and represents a mapping of lpids to data elements for the CYCLIC(c) distribution pattern. There are p! possible permutations for p processors and it may be the case that many of the permutations yield a ratio of MaxHitRatio. However, exhaustively testing each permutation to determine whether it produces the ratio would be impractical since this would require an exponential amount of computation for general p. Therefore, we present a function for determining a permutation that achieves MaxHitRatio for b, p and c. Each  $lpid_i$ ,  $0 \le i \le p-1$ , maps to a unique  $q_{f(i)}$ . Equation (3.1) specifies the function that maps  $lpid_i$  to  $q_{f(i)}$ .

$$f(i) = (iz) \mod p, \ 0 \le i \le p - 1, \ z = b/c.$$

(3.1)

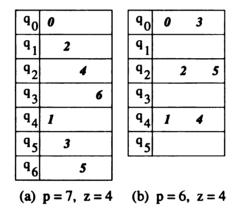

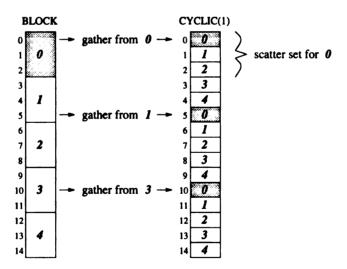

The intuition behind the mapping function is to first view the place holders,  $q_j$ , as a circular list. The function maps  $lpid_0$  to place holder  $q_0$ , maps  $lpid_1$  z places from  $lpid_0$ , maps  $lpid_2$  z places from  $lpid_1$ , and so on. In general, we map  $lpid_{i+1}$ , ( $z \mod p$ ) places from  $lpid_i$ . Figure 3.3 illustrates the behavior of f applied to different values of f and f and f and f are the case for f and f are the case for f and f are the case for f and f and f are the case for f and f and f are the case for f and f are the case for f and f are the case for f and f and f are the case for f are the case for f

is one-to-one in part (a), but f is not one-to-one in part (b); that is, in part (b), more than one lpid maps to some locations, while no lpids map to other place holders. More formally, depending on the values of z and p, it is possible that f(i) = f(j),  $i \neq j$ . While f yields one permutation for part (a), it produces six possible permutations for part (b): since  $lpid_0$  and  $lpid_3$  map to  $q_0$ , it turns out that we can arbitrarily map the two lpids to place holders  $q_0$  and  $q_1$ . The same holds true for  $lpid_2$  and  $lpid_5$  to place holders  $q_2$  and  $q_3$  and for  $lpid_1$  and  $lpid_4$  to place holders  $q_4$  and  $q_5$ . We shall prove this result in a later lemma.

Figure 3.3: Mapping *lpids* to place holders.

### 3.1.3 Optimality of Mapping Function

Given arbitrary z and p, the gcd(z,p) determines whether f is one-to-one or not. Lemmata 2 and 3 establish this. Lemmata 4 and 5 establish that f achieves MaxHitRatio whether or not it is one-to-one.

**Lemma 2** Let p and z be natural numbers and z = b/c. Let gcd(z, p) be the greatest common divisor of z and p. If gcd(z, p) = 1, then  $f: i \to j$  establishes a one-to-one

<sup>&</sup>lt;sup>3</sup>all optimal in terms of MaxHitRatio

mapping between  $lpid_i$ ,  $0 \le i \le p-1$ , and place holder  $q_j$ ,  $0 \le j \le p-1$ . In other words, if gcd(z,p) = 1, then  $f(j) \ne f(k)$  for all j,k and  $0 \le j,k \le p-1$ ,  $j \ne k$ .

**Proof:** Proof by contradiction. Assume gcd(z,p) = 1, f(j) = f(k) = n for arbitrary j,k and choose k > j. Recall that the mapping function, f, maps each  $lpid_{i+1}$ ,  $(z \mod p)$  places from  $lpid_i$ . Let r = k - j, then  $lpid_k$  is mapped a distance of  $r(z \mod p)$  place holders from  $lpid_j$ . Since f(j) = f(k) = n, then  $lpid_j$  and  $lpid_k$  map to the same place holder, so their distance, mod p, is zero, i.e.,  $r(z \mod p) = 0$ . Since r > 0, it must be that  $z \mod p = 0$ . This implies that the gcd(z,p) > 1, a contradiction. Thus, our assumption that f(j) = f(k) = n when gcd(z,p) = 1 is false.

**Lemma 3** Let p and z be natural numbers and z = b/c. If gcd(z, p) = k, then f maps  $lpid_{i+j(p/k)}$  to  $q_{f(i)}$  for  $0 \le i \le p/k - 1$  and  $0 \le j \le k - 1$ .

**Proof:** Show that f(i) = f(i + j(p/k)) for  $0 \le i \le p/k - 1$ ,  $0 \le j \le k - 1$ .

$$f(i) = f(i+j\frac{p}{k})$$

$$(iz) \bmod p = (i + j\frac{p}{k})z \bmod p$$

$$(iz) \bmod p = (iz + jz\frac{p}{k}) \bmod p$$

$$(iz) \bmod p = (iz) \bmod p + (jz\frac{p}{k}) \bmod p$$

Since k divides z,  $jz^{\frac{p}{k}} = mp$  for some integer m.  $mp \mod p = 0$  for arbitrary m. Thus, the second term of the sum,  $(jz^{\frac{p}{k}}) \mod p = 0$ , so we are left with