PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due.

| il -         | DATE DUE | DATE DUE |

|--------------|----------|----------|

| OCT 2 1 1999 |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

MSU is An Affirmative Action/Equal Opportunity Institution ctcircldstadus.pm3-p.1

# MANAGING THE OVERALL BALANCE OF OPERATING SYSTEM THREADS ON A MULTIPROCESSOR USING AUTOMATIC SELF-ALLOCATING THREADS (ASAT)

By

Charles R. Severance

# **A DISSERTATION**

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

**DOCTOR OF PHILOSOPHY**

Department of Computer Science

1996

# **ABSTRACT**

MANAGING THE OVERALL BALANCE OF OPERATING SYSTEM THREADS ON A MULTIPROCESSOR USING AUTOMATIC SELF-ALLOCATING THREADS (ASAT)

By

# Charles R. Severance

While commodity processor based parallel processing systems have an advantage over traditional supercomputers in price/performance, traditional supercomputers retain a significant advantage over parallel processing systems in overall system dynamic load balancing. Traditional supercomputers can easily handle a mix of interactive, batch, scalar, vector, parallel, and large memory jobs simultaneously while maintaining high utilization. This work focuses on an effort to make a large commodity based sharedmemory parallel processing system perform as well as a traditional parallel/vector supercomputer under dynamic load conditions with many users. A solution called Automatic Self-Allocating Threads (ASAT) is proposed as a way to balance the number of active threads across a multi-processing system. Dynamically matching the number of active threads to the available system resources improves performance by eliminating contention for resources. The approach used by ASAT is significant in that it is designed for a system running multiple jobs, and it considers the load of all running jobs in its thread allocation. In addition, the overhead of ASAT is sufficiently small so that it can be used as part of the startup processing for every parallel loop. Furthermore, the approach uses self-scheduling so it can be implemented in a run-time environment rather than in an operating system and not all jobs need to be using ASAT scheduling.

Copyright by CHARLES RUSSELL SEVERANCE 1996

| Dedicated to my wife Teresa, daughter Amanda, son Brent, and parents Russell and |

|----------------------------------------------------------------------------------|

| Marcia for all of their support.                                                 |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

|                                                                                  |

# **ACKNOWLEDGMENTS**

In an educational career which spans over 21 years at the same institution, there are many people who deserve my appreciation. I will note some of them here. First, I am deeply indebted to my advisor Dr. Richard Enbody. His tireless effort and boundless patience is very much responsible for this work. I would also like to thank my committee members, Dr. Lionel M. Ni, Dr. Abdul-Hossein Esfahanian, and Dr. David Tomanek. They have made this a truly remarkable learning experience. I would like to thank Dr. Sakti Pramanik who as my masters thesis advisor originally taught me the basics of research and publishing. I would like to thank my masters academic advisor the late Dr. Carl Page. And even if it has been so long ago that perhaps he has forgot he was my undergraduate advisor at Michigan State University, I thank Dr. Richard Reid. I would like to thank several other members of the Department of Computer Science at Michigan State University. I would like to thank Dr. Tony Wojcik for his support, guidance, and for giving me a chance to teach at Michigan State University in 1990. I would like to thank Dr. Charles R. Maccluer of the Department of Mathemetics for his advice and counsel over the years. I thank the teachers who over the years have had an impact on my education. I would like to thank Dr. Harold Grossman of Lyman Briggs for teaching the class during which I fell in love with computers (despite occasionally falling asleep in class). I thank Dr. Hans Lee for his CPS300 class in which I learned the important lesson

to use an algorithm if one is provided on the program handout. I would like to thank Dr. Martin Keeney for teaching me to hand in assignments on time and that college was something to take very seriously. I would like to thank Dr. Abdul-Hossein Esfahanian, Dr. Richard Enbody, Dr. Eric Torng, Dr. Phillip McKinley, and Mark McCullen for the classes which they have taught so well that I learned the material and how to teach. From my sophomore year on, I was employed full-time at Michigan State University while also taking classes – hence the 21 years. During that time, many of my supervisors, employees and colleagues have been very understanding of my seeming obsession with getting a doctorate. I would like to thank Richard Moore, Dr. Lewis Greenberg, Dr. Paul Hunt, and Dr. Ted Bickart for their support and understanding. I would like to thank Dr. David Kuck, Dr. Paul Petersen, and the others of Kuck and Associates for their guidance on ASAT and for implementing ASAT in their compiler. There were many people who have supported, encouraged, and assisted me over the years in many ways including: Tom Davis, Richard Wiggins, Paul Wolberg, Ted Shotwell, Paul Barczak, Chuck Henrich, and Jerold McAllister. Last but not least, I would like to thank my fellow graduate students without whose support I would never have got this far including: Steve Wagner, Barb Birchler, Mark Brehob, Natawut Nupairoj, Hugh Smith, Jerry Gannod, and Travis Doom. I wish them all the best in their own academic pursuits.

# **TABLE OF CONTENTS**

| INTRODUCTION                                                         | 1          |

|----------------------------------------------------------------------|------------|

| 1.1 MOTIVATION                                                       |            |

| 1.2 Execution Model                                                  |            |

| 1.3 ASAT IMPLEMENTATION                                              |            |

| 1.4 ASAT IN OPERATION                                                |            |

| 1.5 ASAT IN A COMPILER RUN-TIME ENVIRONMENT                          |            |

| 1.6 Previous Work                                                    |            |

| 1.6.1 Dynamic Thread Adjustment Techniques                           |            |

| 1.6.2 Dynamic Load Balancing                                         |            |

| 1.7 ASAT CONTRIBUTIONS                                               | 17         |

| THE STATE-OF-THE-ART IN SHARED-MEMORY PARALLEL PROCESS               | OR         |

| RUN-TIME ENVIRONMENTS                                                | 19         |

| 2.1 Processor Self Scheduling                                        | 19         |

| 2.1.1 Compiler Options on the SGI                                    | 20         |

| 2.1.2 Processor Self Scheduling Research                             | 26         |

| 2.2 DYNAMIC LOAD BALANCING ON CONVEX VECTOR/PARALLEL SUPERCOMPUTERS. | 30         |

| 2.2.1 Performance of the Convex on Parallel Jobs                     | <i>3</i> 6 |

| 2.3 FORTRAN RUN-TIME THREAD MANAGEMENT                               | 38         |

| 2.3.1 Run-Time Thread Management Details                             | <b>4</b> 0 |

| 2.4 Problems with Dynamic Load                                       |            |

| 2.4.1 Loop Performance Under Load                                    |            |

| 2.4.2 Parallel Applications and Load on the SGI                      | <i>51</i>  |

| 2.5 SUMMARY                                                          | 54         |

| AUTOMATIC SELF-ALLOCATING THREADS                                    | 55         |

| 3.1 ASAT DESIGN                                                      |            |

| 3.2 ASAT Version 1 Implementation                                    | 57         |

| 3.3 TIMED BARRIER PERFORMANCE STUDY                                  |            |

| 3.4 ASAT Version 2 Implementation                                    |            |

| 3.5 ASAT Version 2 Tunables                                          | 65         |

| 3.6 Summary                                                          | 66         |

| PERFORMANCE RESULTS                                                  | 67         |

| 4.1 MEASURING ASAT OVERHEAD AND BENEFITS                             | 67         |

| 4.2 SINGLE JOB PERFORMANCE WITH ASAT                                 | 71         |

| RIRLIOGRAPHY                                         | 110 |

|------------------------------------------------------|-----|

| APPENDIX A - SOURCE CODE FOR LOOP LATENCY TEST       | 108 |

| 5.2 FUTURE WORK                                      | 106 |

| 5.1 CONCLUSION                                       |     |

| CONCLUSION AND FUTURE WORK                           | 105 |

| 4.8 SUMMARY                                          |     |

| 4.7.4 Multiple Grain Size=1M and 4M Jobs             |     |

| 4.7.3 Multiple Grain Size=100K Jobs                  |     |

| 4.7.2 Multiple Grain Size=10K Jobs                   |     |

| 4.7.1 Multiple Grain Size=2K Jobs                    |     |

| 4.7 RUNNING MULTIPLE PARALLEL JOBS                   |     |

| 4.6 RUNNING COMBINATIONS OF SERIAL AND PARALLEL JOBS | 86  |

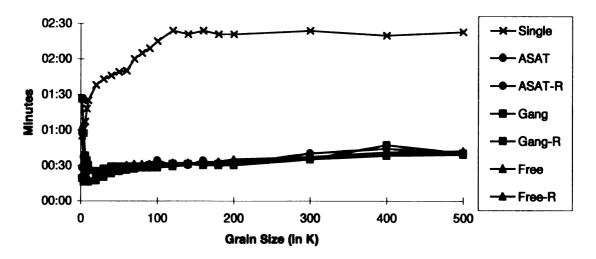

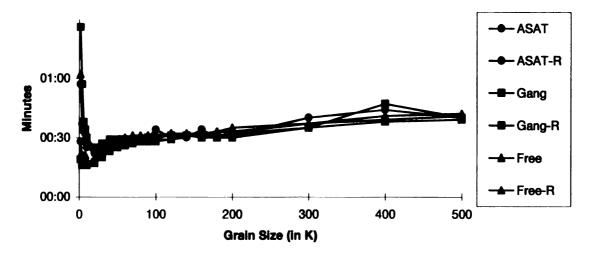

| 4.5 RUNNING JOBS ON AN EMPTY SYSTEM                  | 82  |

| 4.4.3 Execution Environment                          |     |

| 4.4.2 Code Structure                                 |     |

| 4.4.1 Run Time Scheduling Options                    |     |

| 4.4 FOCUSED ASAT PERFORMANCE TESTS                   |     |

| 4.3 ASAT RESPONSE TO DYNAMIC LOAD                    |     |

| 4.2.2 ASAT On the Convex Exemplar                    |     |

| 4.2.1 ASAT Version 1 on the SGI                      |     |

# LIST OF TABLES

| Table 1 - Types of Run-Time Choices         | <b>79</b> |

|---------------------------------------------|-----------|

| Table 2 - Parameters Relative to Grain size |           |

| Table 3 - ASAT Run-Time Settings            | 82        |

# LIST OF FIGURES

| Figure 1 - Execution Model                                                      | 5  |

|---------------------------------------------------------------------------------|----|

| Figure 2 - Operation of ASAT Over Time                                          | 8  |

| Figure 3 - Iteration Assignment for Simple Scheduling                           | 21 |

| Figure 4 - Iteration Assignment in Dynamic Scheduling                           | 23 |

| Figure 5 - Impact of SGI Iteration Scheduling Options                           | 25 |

| Figure 6 - Iteration Assignment for Guided Self Scheduling                      | 28 |

| Figure 7 - Convex C-Series Architecture                                         |    |

| Figure 8 - The Operation of ASAP Under Load                                     | 35 |

| Figure 9 - Performance of the Convex Under Load                                 |    |

| Figure 10 - Free (Non-Gang) Thread Scheduling                                   | 40 |

| Figure 11 - Gang Thread Scheduling                                              | 41 |

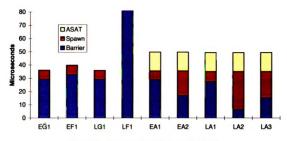

| Figure 12 - Thread Timing Results                                               | 43 |

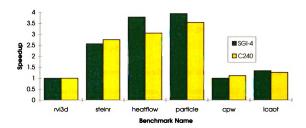

| Figure 13 - Comparing Speedup on SGI Challenge and Convex C240                  | 46 |

| Figure 14 - Loop Timing Under Load                                              |    |

| Figure 15 - Loop Timing Under Load (Log Scale)                                  | 50 |

| Figure 16 - Individual Iteration Timing - Thread 2/Free (Log Scale)             | 51 |

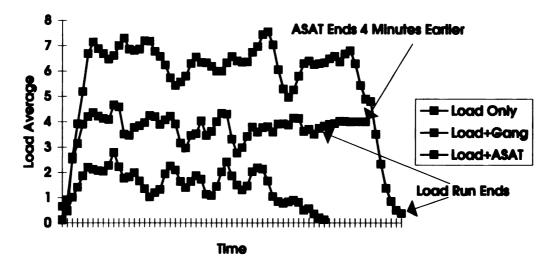

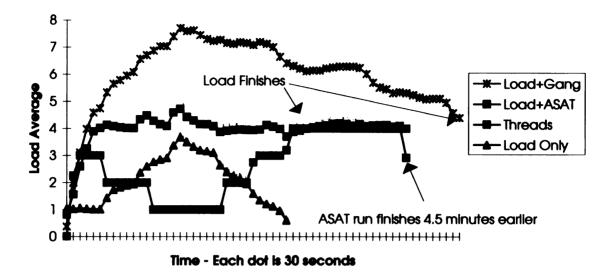

| Figure 17 - SGI Performance with Load                                           | 53 |

| Figure 18 - Impact of Thread Imbalance                                          | 54 |

| Figure 19 - Iteration Differential In Loaded and Unloaded Conditions            | 59 |

| Figure 20 - Barrier Passage Time (scaling)                                      | 61 |

| Figure 21 - Timed Barrier Passage With and Without Load                         | 62 |

| Figure 22 - Loop Iteration Timing with ASAT                                     | 68 |

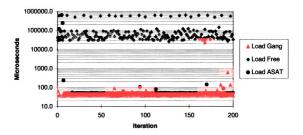

| Figure 23 - ASAT Performance Over Time                                          | 70 |

| Figure 24 - ASAT Performance on the SGI                                         | 72 |

| Figure 25 - ASAT on the Convex Exemplar                                         | 74 |

| Figure 26 - ASAT Response to Rapidly Changing Load                              | 77 |

| Figure 27 - ASAT Responses to Slow Changes in Load                              | 78 |

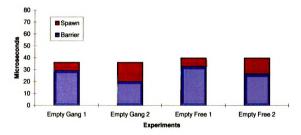

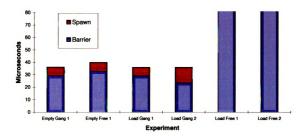

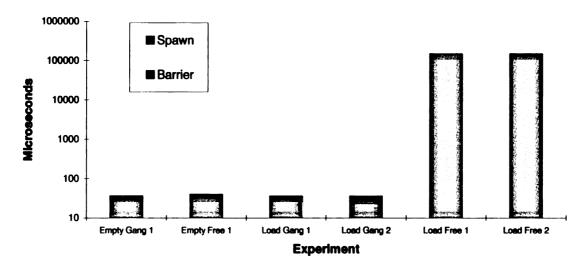

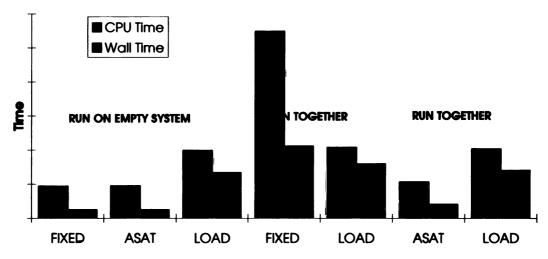

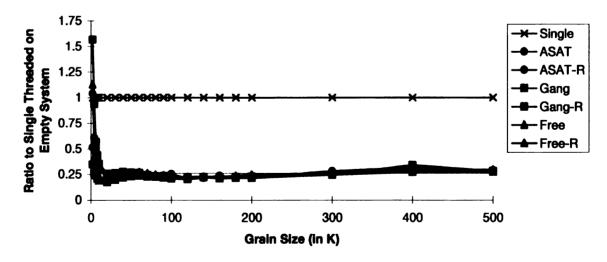

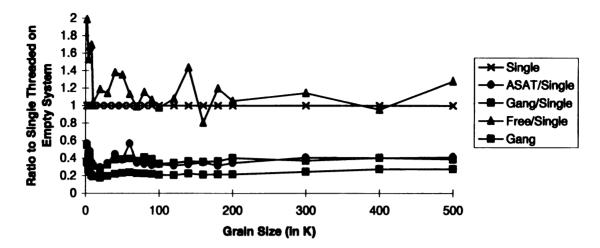

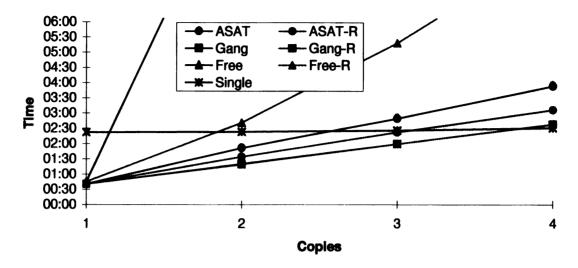

| Figure 28 - Runs on Empty System                                                | 83 |

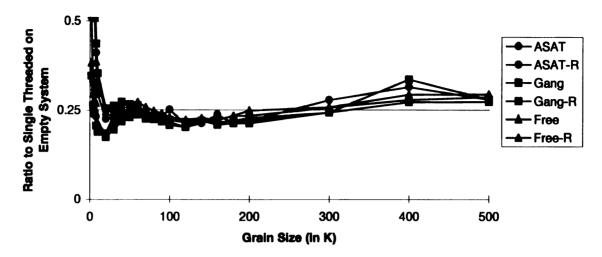

| Figure 29 - Runs on Empty System (Expanded Vertical Axis)                       | 83 |

| Figure 30 - Speedup for Parallel Jobs on Empty System                           |    |

| Figure 31 - Speedup for Parallel Jobs on Empty System (Expanded Vertical Axis)  |    |

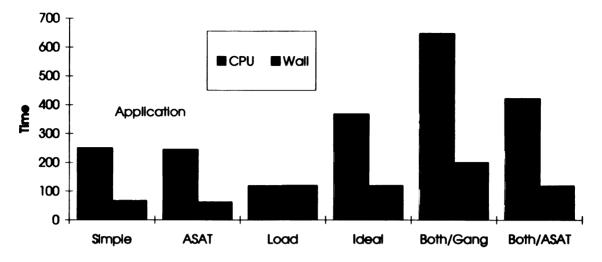

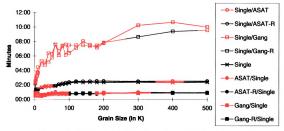

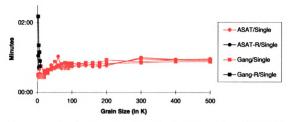

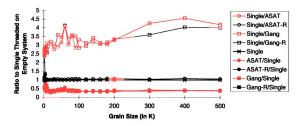

| Figure 32 - Performance of ASAT and Gang Combination Runs                       | 87 |

| Figure 33 - Performance of ASAT and Gang Combination Runs (Expanded Vertical    |    |

| Axis)                                                                           | 88 |

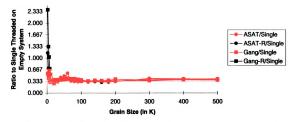

| Figure 34 - Relative Performance of ASAT and Gang Compared to Single Threaded J | ob |

| on an Empty System.                                                             | 89 |

| Figure 35 - Relative Performance (ASAT and Gang) compared to a Single threaded John  | b    |

|--------------------------------------------------------------------------------------|------|

| on an Empty System (Scale)                                                           | . 89 |

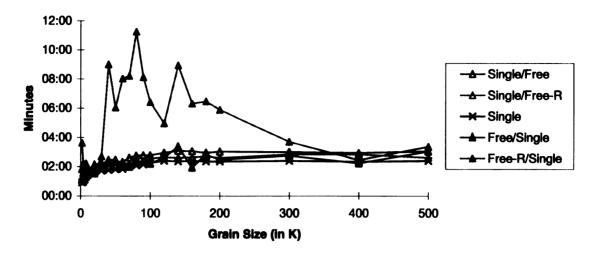

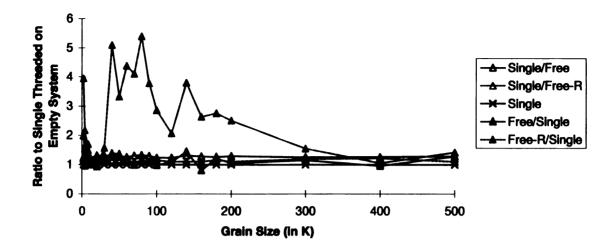

| Figure 36 - Performance of Free Scheduled Jobs With Fixed Threads                    | . 91 |

| Figure 37 - Performance of the Single Threaded Job With Other Jobs Executing         | . 92 |

| Figure 38 - Performance of Various Parallel Jobs with a Single Threaded Job Running. | . 93 |

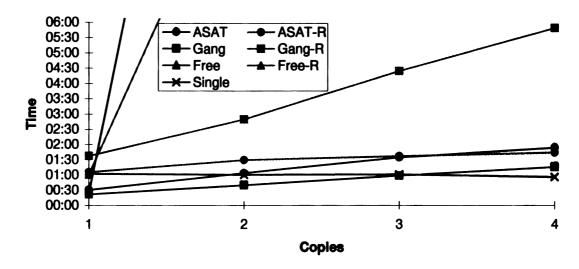

| Figure 39 - Multiple Jobs with Grain Size 2K                                         | . 95 |

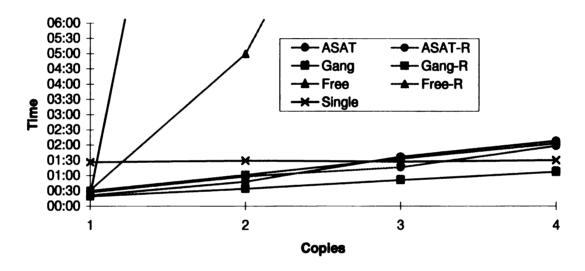

| Figure 40 - Multiple Jobs with Grain Size 10K                                        | . 97 |

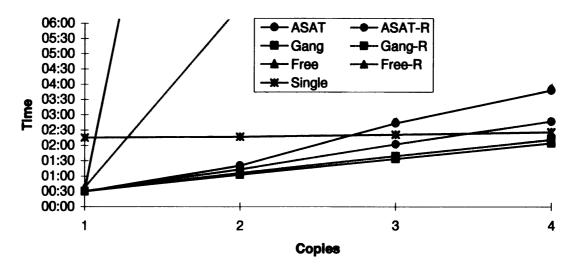

| Figure 41 - Multiple Copies with Grain Size 100K                                     | . 99 |

| Figure 42 - Multiple Jobs with Grain Size 1M                                         | 100  |

| Figure 43 - Multiple Jobs with Grain Size 4M                                         | 101  |

# **CHAPTER**

# 1.

# **INTRODUCTION**

This thesis describes a tool called Automatic Self-Allocating Threads (ASAT) which addresses the problem of dynamic load balancing to make efficient use of low cost parallel processing systems under widely varying loads. ASAT has been implemented as part of the FORTRAN run-time environment for parallel applications. ASAT adjusts the number of active threads executing in an application as the overall system load changes to maintain thread balance across the entire system.

Most dynamic load balancing research focuses on the effective division of computations, data, or tasks among the threads of a running process or across several computer systems. This work focuses on how a single parallel processing system processing multiple unrelated processes each with multiple threads can most effectively make joint use of the overall system resources.

# 1.1 Motivation

The high performance computing and scientific computing market segments are making a dramatic transformation from the heavy use of vector supercomputers to medium scale symmetric parallel processing systems based on commodity processors. The peak performance of a high-end commodity Central Processing Unit (CPU) is within a factor

of three of all but the fastest supercomputer CPU. This price/performance has caused a migration away from shared central computer resources toward dedicated desktop compute resources for many applications. However, regardless of how fast individual desk top systems become, many users still have applications which need more cycles, memory, or disk than are available on their desk top. In order to satisfy those users' quest for more cycles, parallelism is the only remaining way to provide 2-3 orders of magnitude performance increase over the typical desktop system. In this computing environment, parallel processing systems such as the SGI Challenge and Power Challenge have enjoyed excellent market penetration against the traditional Cray or Convex vector supercomputers. Computing centers have been purchasing these systems with 16 to 32 processors and large memories to replace central vector supercomputers.

However, unlike a workstation, such a large single resource must often be shared among a pool of compute users in order to amortize its cost. As we will show later, these parallel processors have excellent performance for a multi-processing load and excellent performance for a single multi-threaded compute application. Unfortunately, these processors still have trouble dealing with the combination of running a multi-processing load and a multi-threaded compute application simultaneously. Furthermore, these processors have difficulty in handling more than one multi-threaded compute application simultaneously without using Gang Scheduling. The problem occurs when there are more active threads than available processors. This limitation in flexibility remains a primary disadvantage with respect to older supercomputer systems.

This lack of flexibility on these commodity-processor based parallel processors has not significantly slowed the migration away from vector supercomputers. The price/performance of these systems is so superior that even if 50% of the cycles are wasted, these Symmetric Multi-Processing (SMP) systems are still the better purchase in many situations. When vendors of these systems are asked about the limitations of their systems in being used as a shared *computing* resource, they have one of several reactions:

- They suggest that because "CPUs are so cheap" you can buy some extra CPUs to make up for the inability to use the existing CPUs at 100%.

- They suggest that you "partition" (also known as space sharing) your 16-way parallel processing system into four 4-way parallel processing systems. In this way at least four people can operate without impacting each other.

- They suggest that you buy two or more of their systems. One system can be used

for interactive use and the second system can be used as a "batch back end".

Again this is a form of space sharing and limits the ability to achieve 100%

overall utilization. It is also expensive to replicate features such as a very large

memory across two systems to make the interactive environment precisely mirror

the production environment.

The interesting running theme in each of these vendor approaches to solving the problem is that they entail purchasing more hardware. Also, in each of the vendor solutions above, the user community must take some of the responsibility for these systems inability to handle dynamic computational load. Few procurements actually take into

account the ability to perform dynamic load balancing between a multi-processing and multi-threaded load when designing benchmarks for these low cost systems. Most benchmarks (user developed or industry-wide) are run on "stand-alone" systems with no other activity so effective utilization is not an issue. As we demonstrate later, the negative performance impact of a dynamic load is surprisingly large.

The purpose of ASAT is to allow the users of these new style parallel processing systems to "have their cake and eat it too". That is, they will have all of the price/performance advantages of the low-cost SMP systems with the flexibility of the vector supercomputers. Most importantly, when a user purchases a system with sixteen CPUs which supports ASAT, they will actually be able to expect to use 100% of those sixteen CPUs regardless of the dynamic load patterns on the system.

# 1.2 Execution Model

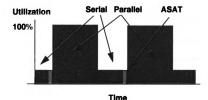

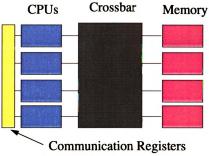

The goal of ASAT is to dynamically adjust the number of threads of a process so that the number of threads matches the number of available processors. The basic concepts of ASAT can be used in a wide variety of multi-threaded applications ranging from explicit, user-controlled threads to run-time environments for parallel implementations of functional languages. This work focuses on FORTRAN applications using automatic, compiler-generated parallelism. ASAT depends on an execution model in which a serial portion of the code is periodically executed between the parallel sections of the code. In Figure 1, the time profile of this type of application is shown.

Figure 1 - Execution Model

The duration of the serial and parallel portions of the time profile varies widely, but many applications which are well suited to parallel processors have relatively short periods of serial execution followed by relatively long periods of parallel execution. ASAT depends on the existence of the serial code because it performs the thread adjustment as part of the startup of the parallel portion of the code as shown in red in Figure 1.

A FORTRAN program similar to the following will generate this common serial-parallel pattern when compiled with compiler-detected parallelism:

```

DO ITIME=1,INFINITY

DO PARALLEL IPROB=1,PROBSIZE

ENDDO

...

ENDDO

```

ASAT determines the proper number of threads to execute a parallel loop each time the parallel loop starts. The proper number of threads depends on the system's multi-processing load and other multi-threaded compute jobs.

# 1.3 ASAT Implementation

The key implementation detail in ASAT is determining the appropriate number of threads before each parallel loop without adding significant overhead to the loop startup. Each ASAT job evaluates the overall system load independently, eliminating any need for a central server process, shared data structure, or operating system modification. Because of its completely distributed load evaluation, ASAT jobs can efficiently operate with any combination of multitasking *and* multi-threaded jobs which are not using ASAT.

The actual goal of the of ASAT is not to precisely determine the number of threads which is appropriate, but rather to determine if the current number of threads is too large or too small. The situation in which there are an inappropriate number of threads is called "thread imbalance". When there more active threads than processors it is called "excess threads", and the situation where there are fewer threads than processors is called "wasted resources". When an ASAT process detects that there are more active threads than processors operating across the entire system it drops a thread. When an ASAT process detects that there are more processors than active threads across the entire system, it adds a thread. In this way, ASAT jobs always move toward overall system equilibrium by implicitly reacting to any combination of innumerable changes in system load.

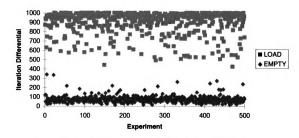

A number of different approaches to determine the relative thread balance were tried [26, 27, 29, 30]. The approach which was the most successful was to periodically run a barrier synchronization and time the barrier passage. It will be shown later that that there is up to three orders of magnitude difference in barrier passage times when comparing thread-balanced to thread-imbalanced conditions. The system real-time clock and a user-

settable parameter are used to insure that the ASAT evaluation is not run too frequently. This timed barrier must be run during the serial portion of the code, and any changes in the number of active threads takes effect when the next parallel loop is encountered.

For example, to use the public domain version of ASAT on the SGI Challenge[35], the calls to the ASAT run-time library must be added immediately before each parallel loop:

```

DO ITIME=1,INFINITY

CALL ASAT_ADJUST()

DO PARALLEL IPROB=1,PROBSIZE

Work..

ENDDO

ENDDO

ENDDO

END

```

The ASAT\_ADJUST routine handles all the timer operations, performs the thread balance test if necessary, and adjusts the number of threads for the next parallel loop, if thread imbalance is detected. This routine also periodically determines if there are idle cycles and increases threads, if it is appropriate. The details of ASAT implementation are covered in Chapter 3.

# 1.4 ASAT In Operation

Using ASAT, an application can react to changes in system load regardless of the source of the changes. ASAT can react to other long running parallel jobs, medium length jobs such as compiler runs, bursts of interactive usage such as editing, load due to incoming network activity, load due to system server processes, excessive operating system overhead, and implicitly compensates for input-output activity on the system. Figure 2 shows how an application with ASAT generally operates when working on a four-processor system with variable load. In this figure, a single application using ASAT is executing while other users are using the system in different ways. As the load average

increases due to other users, the ASAT application releases threads to maintain balance.

Under high load conditions, the ASAT application only has one thread. As the other load decreases, the ASAT application adds threads, increasing its throughput by using the idle cycles.

Figure 2 - Operation of ASAT Over Time

In the rest of this thesis, the dynamic load balancing ability of ASAT is shown to be excellent under a wide variety of different loads, and is studied on several computer architectures.

# 1.5 ASAT in a Compiler Run-Time Environment

The initial versions of ASAT required that library calls be manually added before the parallel loops as shown above. The ultimate goal is for ASAT to be supported directly by the compiler. In this latter case, there are two possible options for its implementation. In the first option, ASAT is transparently called before every parallel loop as part of the runtime library. In this way, all parallel users using that compiler will use ASAT processing

(i.e. ASAT is not optional – like ASAP on the Convex). Another approach is to control its use through a compiler directive such as:

```

DO ITIME=1,INFINITY

...

C$DOACROSS LOCAL(IPROB),THREADS(ASAT)

DO IPROB=1,PROBSIZE

...

ENDDO

...

ENDDO

```

In this way, the user can decide when ASAT is used on a particular loop. The actual approach may vary from compiler to compiler and possibly even from system to system under the control of the system administrator.

There is one possible programming style which will be in conflict with a compiler runtime which provides ASAT without the awareness of the programmer. Some highly tuned parallel applications contain code which depends on a particular number of threads or that the same number of threads execute in every loop. A contrived example of this programming style is as follows:

```

REAL*8 A(1000,4)

IF ( NUM_THREADS() .GT. 4 ) STOP

C$ DO_PARALLEL

DO I=1,NUM_THREADS()

DO J=1,1000

A(J,I) = 0.0

ENDDO

ENDDO

C$ DO_PARALLEL

DO I=1,NUM_THREADS()

DO J=1,1000

A(J,I) = A(J,I) + 3.14159

ENDDO

ENDDO

ENDDO

ENDDO

```

The above code will work properly without ASAT as long as the number of threads never exceeds four. However, if ASAT implicitly adjusts (increases or decreases) the number of threads between the loops, the results will most likely be incorrect.

This style of programming can also be used to allow the programmer to manually perform load balancing, iteration scheduling, or control the patterns of access to memory when the compiler does not provide a robust enough solution for their particular application.

Like iteration scheduling, these techniques often assume a fixed number of threads and may not work efficiently when the number of threads changes from one loop execution to another.

# 1.6 Previous Work

The first part of this section covers the previous work which relates directly to the dynamic management of the number of run-time threads for compute-intensive applications. The second part of this section covers the broader area of dynamic load balancing and places ASAT relative to other dynamic load balancing work. Chapter 2 covers some additional previous work combined with experimental results which develop a broader framework for the environment in which ASAT is intended to be deployed.

# 1.6.1 Dynamic Thread Adjustment Techniques

The dynamic thread management work most closely related to ASAT falls into three categories:

# • Hardware approaches

- Software approaches which depend on operating system modifications

- Software approaches which depend on all the processes cooperating through a central data structure

The Convex C-Series [7] vector/parallel supercomputers implemented low-overhead dynamic thread count adjustment using significant hardware features collectively called Automatic Self-Allocating Processors (ASAP). In many ways the design of ASAT is inspired by ASAP. In [29] and in later chapters, the performance of ASAT will be directly compared to the performance of ASAP.

Cray Research's Autotasking [9] dynamically manages threads, but does not actually alter the number of threads during run-time. Through a combination of hardware, run-time software, iteration scheduling, and operating system support, Autotasking can operate efficiently across a wide range of load conditions. Autotasking allows the number of threads *executing* in a particular parallel loop to change during the execution of the loop as a result of load change through a cooperative agreement between the run-time library and operating system.

Both [1] and [37] proposed a solution which can dynamically adjust the number of runtime threads to accomplish overall load balancing. This approach depends on modifications to the operating system to maintain information regarding the load state of the system. In [1] the operating system actually removes an executing thread from the application when it detects excess threads. The application and run-time library had to cope with the loss of the thread and still insure correct program execution. In [Tuck93]

this load information was periodically consulted by the SPLASH run-time environment which would then adjust the thread usage appropriately for each parallel section. In [1] the technique is called "scheduler activation's" and in [37] it is called "process control".

The significant negative performance impact of thread imbalance on these commodity processor based parallel processing systems was identified in [1,37,21]. In [37] the negative performance impact was broken down into its component causes and carefully measured using the SPLASH [SPLASH] benchmark applications. These issues are explored further in Chapter 2.

Recent work in [41,42,43] is most closely related to the current ASAT. This work seems to have evolved at about the same time as ASAT although ASAT was published earlier. The technique is called "Loop-Level Process Control" (LLPC). Like ASAT, LLPC does not require any operating system or hardware modifications. The primary difference between LLPC and ASAT is that LLPC communicates the overall system load information among the LLPC-enabled processes using a shared memory location. The primary limitation of the LLPC approach is that it is difficult for this approach to adapt to a changing multi-processing load or a multi-threaded load which does not use LLPC. This limitation could be mitigated by creating a "shepherd" process to periodically update the central data structure with operating system provided load information.

Unfortunately, this would require the addition of a locking protocol which was eliminated from LLPC because of its negative performance impacts.

While the implementation of the LLPC run-time load test is inferior to that used in ASAT, they performed an excellent study [43] of the positive value of dynamically

adjusting the number of run-time threads. This study showed that a wide range of applications (Perfect Club) [Perfect] demonstrate the parallel-serial pattern of execution necessary for all of these software-based approaches (ASAT, LLPC, Scheduler Activation's, and Process Control) to work effectively.

This thesis summarizes and extends a long history of ASAT publications. The initial work on ASAT for the SGI Challenge was described in [26]. A second version of ASAT was developed and ported to the Convex Exemplar [CONEXMP] and those results were reported in [27]. The results of ASAT on the SGI and Convex Exemplar were presented as a poster session in [28]. The ASAT performance on the Convex Exemplar was compared to the Convex ASAP hardware solution in [29]. In [30] the second version of ASAT was evaluated on the SGI Challenge. ASAT is currently integrated into a Beta version of a production compiler [11] run-time environment from Kuck and Associates. The performance of the Guide compiler implementation of ASAT when multiple processes are executed is presented in [31].

In summary, the previous and concurrent work makes a very strong case that some form of software-based thread adjustment is necessary for these systems to handle a diverse dynamic load efficiently. However, none of the earlier or current approaches were sufficiently well developed to be deployed in a production environment.

# 1.6.2 Dynamic Load Balancing

ASAT operates within the general framework of Dynamic Load Balancing. Dynamic Load Balancing is one of the classic topics in the parallel processing area of Computer Science [23]. Hundreds or thousands of parallel processors are not too useful if all but

one of the processors is at a barrier waiting for a single processor to complete a computation.

There are three general computing entities which are the object of dynamic load balancing approaches: (1) computations, (2) data, and (3) tasks. The use of these dynamic load balancing approaches often follows computer architectures. Computations are balanced on shared memory systems. The data distribution approach is often used on clusters of workstations and multicomputers. Data distribution load balancing is the preferred technique for SIMD computers. Tasks are balanced on workstation clusters and message passing multicomputers.

# 1.6.2.1 Balancing Computations

When computations are being balanced, the location of the data which is being used in the computations is not considered in the load balancing algorithms. Data is either present in all of the memories or there is a single shared memory with uniform access characteristics. The general topic of scheduling for parallel loops on shared memory computers is one that is well studied. Many of these techniques are actually implemented in today's production parallel compilers [33]. The basic approach of these techniques is to partition the iterations of a parallel loop among a number of executing threads in a parallel process. The goal is to have balanced execution times on the processors while minimizing the overhead for partitioning the iterations and maximizing the potential for cache reuse. A number of scheduling techniques have been proposed and implemented.

An excellent survey of these techniques is presented in [17]. These iteration scheduling techniques include Pure Self Scheduling (PSS), Chunk Self Scheduling (CSS), Guided

Self Scheduling (GSS) [24], Trapezoidal Self Scheduling (TSS) [39,40], and Safe Self Scheduling (SSS) [16,18]. These techniques, their impact on performance and their relationship to ASAT will be discussed in greater detail in Chapter 2.

# 1.6.2.2 Balancing Data

When data is being balanced, the challenge is to move data among the processors so that each processor operates on its local data and has a balanced workload. Often processors are working in a SIMD or SPMD mode where all of the processors are performing portions of a single computation. The simplest approach to balancing data is direct decomposition. In direct decomposition, the data structures are divided geometrically and the subsets are mapped onto processors maintaining the geometric relationship between the subsets. Each processor is assigned a uniformly sized section of the data structure. It is hoped that by balancing the distribution of the data structure, the computations associated with that data structure will naturally be balanced. The primary contribution of the High Performance FORTRAN (HPF) [12] language is to add directives to FORTRAN-90 which support direct decomposition.

Direct decomposition has a number of advantages including: 1) it is relatively simple to implement, 2) it scales very nicely—with more processors, more grids can be created, and 3) it takes advantage of geometric relationships present in many parallel processors (e.g. 2D Mesh, 3D Mesh, or Hypercube).

The primary disadvantage of direct decomposition is that the overall processor utilization can be very low when patterns of computation times are different for different areas of the data structures. With the right problem direct mapping can perform very well on SIMD or

SPMD system as shown in [3]. Interestingly, the limitation of direct decomposition is one of the problems which HPF-2 [13] is attempting to fix by adding non-uniform data distribution constructs to the language.

There are a number of approaches to non-uniform partitioning data in order to balance computations which are not suitable for direct decomposition including scattered decomposition [22], Orthogonal Recursive Bisection [2], and Eigenvalue Recursive Bisection [Will91], Parallel Simulated Annealing, Parallel Neural Network, Parallel Genetic Algorithms [20], and Real-Valued Indexed Arrays [32]. Unlike direct decomposition, these approaches are not supported by high level FORTRAN constructs but must be accessed using explicit calls to subroutine libraries or are only supported in object oriented languages such as C++ [4].

# 1.6.2.3 Balancing Tasks

Tasks are units of work which consist of both the data and computations. In the load balancing activity, the self-contained tasks migrate around the system seeking computational resources. Sometimes the tasks which are balanced are completely independent (e.g. an operating system) and other times, the tasks are all part of a single large problem which can be independently computed (such as Monte Carlo trials). Some approaches in this area of load balancing include the V- System[36], Sprite [10], Condor [15], Stealth[14], and Utopia [ZhoZhe93]. A formal model for this type of load balancing was proposed in [5] and [6].

# 1.6.2.4 Dynamic Load Balancing Summary

Of the load balancing approaches described in this section, the techniques which have the broadest use include:

- Iteration scheduling is in broad use on supercomputers and parallel processors including: Cray, Convex, SGI, SUN, DEC, and others

- Direct decomposition is typically done using HPF, in a subroutine library, or explicitly coded by the programmer. It is used on systems such as the IBM SP-2, MasPar, or networks of workstations (NOW).

- Balancing of unrelated tasks is often used in a distributed operating system or a

batch queuing environment such as the Load Sharing Facility [19]. This approach

is most prevalent on networks of workstations (NOW).

Within the broad framework of dynamic load balancing, ASAT expands the area of dynamic load balancing using processor self scheduling on shared-memory parallel processors.

#### 1.7 ASAT Contributions

This work contains a number of significant unique contributions. No other solution to the problem of matching the overall number of threads to the number of processors has all of these features:

- Requires no special hardware to support its dynamic load balancing

- Requires no operating system modifications to support its dynamic load balancing

- Does not require that all of the processes running on a system use ASAT

- Does not require any centrally managed information for its operation

- Can be used without any compiler modifications

- Sufficiently well developed to be cleanly integrated into existing production compilers

The most significant contribution is the fact that when ASAT becomes generally available in production parallel compilers, shared memory parallel computers around the world processing a combination of multi-threaded and multi-processing load will immediately experience up to a 100% improvement in throughput.

In summary, ASAT is a straightforward, portable technique which can be implemented on a wide variety of parallel processing architectures and thread environments. ASAT takes a large step in moving the dynamic load balancing capability of the commodity-based parallel processors to be nearly equivalent to the capabilities long enjoyed on the traditional vector/parallel supercomputers.

# **CHAPTER**

2.

# THE STATE-OF-THE-ART IN SHARED-MEMORY PARALLEL PROCESSOR RUN-TIME ENVIRONMENTS

In this chapter, we examine the current techniques in use in production compilers on existing shared-memory parallel processing systems. We identify the strengths and weaknesses in the actual environments currently in use around the world for High Performance Computing. First, we examine the general field of choosing a distribution of iterations to threads based on the expected distribution of individual iteration times.

Second, we examine how the Convex C-Series vector/parallel supercomputers uses hardware features to enable excellent dynamic load balancing. Finally, we examine the shortcomings of commodity-based parallel processing systems when trying to implement loop-based load balancing on systems experiencing dynamic load.

# 2.1 Processor Self Scheduling

The most common dynamic load balancing approach for shared-memory parallel processors is called processor self-scheduling. In processor self-scheduling, each processor determines which iterations of a particular loop it will process independently. Processor self-scheduling can be contrasted with a master-slave approach where tasks or messages are placed on a queue by a master process and independently removed by slave processes running in parallel. Consider the following pair of example code segments:

```

C VECTOR ADD

DO PARALLEL IPROB=1,10000

A(IPROB) = B(IPROB) + C(IPROB)

ENDDO

C PARTICLE TRACKING

DO PARALLEL IPROB=1,10000

RANVAL = RAND(IPROB)

CALL ITERATE_ENERGY(RANVAL)

```

In both loops, all the computations are independent so if there were 10,000 processors, each processor could execute a single iteration. In [25] such a loop with no crossiteration dependencies is called a DOALL loop. In the vector-add example, each iteration would be relatively short and the execution time would be relatively constant from iteration to iteration. In the particle tracking example, each iteration will choose a random number for an initial particle position and iterate to find the minimum energy. Each iteration will take a relatively long time to complete, and there will be a wide variation of completion times from iteration to iteration.

These two examples are effectively the ends of a continuous spectrum of the iteration scheduling challenges facing the FORTRAN parallel run-time environment.

# 2.1.1 Compiler Options on the SGI

The SGI compiler has options for programmer-controlled iteration scheduling provided as part of its parallel FORTRAN compiler [33] and [34]. Similar options are typically available on most parallel FORTRAN compilers. The iteration scheduling options for a parallel loop on the SGI include:

- Simple At the beginning of a parallel loop each thread takes a fixed continuous portion of iterations of the loop based on the number of threads executing the loop.

- Dynamic With dynamic scheduling, each thread processes a "chunk" of data and

when it has completed processing, a new "chunk" is processed. The "chunk size"

can be varied by the programmer, but is fixed for the duration of the loop.

- Guided Self Scheduled (GSS) This is essentially a modification of "dynamic" scheduling except that large "chunks" are taken during the first few iterations, and the "chunk size" is reduced as the loop nears completion.

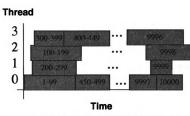

The two example loops above can be used to show how these iteration scheduling approaches might operate on a four-processor system. In the vector-add loop, simple scheduling would distribute iterations 1-2500 to processor 0, 2501-5000 to processor 1, 5001-7500 to processor 2 and 7501-10000 to processor 3. In Figure 3, the mapping of iterations to threads is shown for the simple scheduling option.

Figure 3 - Iteration Assignment for Simple Scheduling

Since the loop body (a single statement) is short with a consistent execution time, Simple scheduling should result in roughly the same amount of overall work (and time if you assume a dedicated CPU for each thread) assigned to each thread per loop execution.

Even though the "work" might be exactly the same across the threads, there may still be a load imbalance at the end of the loop because of cache effect, interrupts, or timesharing.

Also, there is sometimes a lag in getting the threads other than thread zero started processing the loop which can lead to some imbalance at the start of a parallel loop [10].

Later, we will precisely measure this thread startup skew on the SGI Challenge.

A further advantage of simple scheduling may occur if the entire loop is executed repeatedly. If the same iterations execute repeatedly on the same processors, the cache for each processor might actually contain the values for A, B, and C from the previous loop execution. The run-time pseudo-code for simple scheduling in the first loop might look as follows:

```

C VECTOR ADD - Simple Scheduled

ISTART = (PROCESSOR_NUMBER * 2500 ) + 1

IEND = ISTART + 2499

DO ILOCAL = ISTART, IEND

A(ILOCAL) = B(ILOCAL) + C(ILOCAL)

ENDDO

```

Using the simple approach of giving a fixed number of iterations to each thread, is not always a good strategy. If it were used in the second loop example, it would result in poor load balancing given that the iteration times are long and varying. A better approach is to have each processor simply get the next value for IPROB each time at the top of the loop. That approach is called dynamic scheduling and it can adapt to widely varying iteration times. In Figure 4, the mapping of iterations to processors using dynamic

scheduling is shown. As soon as a processor finishes one iteration, it processes the next available iteration in order.

Figure 4 - Iteration Assignment in Dynamic Scheduling

If a loop is executed repeatedly, the assignment of iterations to threads may vary due to very subtle timing issues which randomly affect threads. Any remaining load imbalance is caused by thread start skew and the lengths of the last iterations executed by each thread. The pseudo code for the dynamic scheduled loop at run-time is as follows:

```

C PARTICLE TRACKING - Dynamic Scheduled

IPROB - 0

WHILE (IPROB <= 10000)

BEGIN CRITICAL SECTION

IPROB = IPROB + 1

ILOCAL = IPROB

END_CRITICAL_SECTION

RANVAL = RAND(ILOCAL)

CALL ITERATE_ENERGY(RANVAL)

ENDHILL

```

While each of these loop iteration scheduling approaches works well for one loop, there is a significant negative performance impact if the programmer were to use the wrong approach for the loop. For example if the dynamic approach were used for the vector-add loop, the time to process the critical section to determine which iteration to process may

be larger than the time to actually process the iteration. Furthermore, any cache affinity of the data would be effectively lost because of the virtually random assignment of iterations to processors.

Because the choice of loop iteration approach is so important, the compiler relies on directives from the programmer to specify which approach to use. On the SGI the following directives would be added to insure the right approach was taken in each of our example loops:

```

C VECTOR ADD

C$DOACROSS LOCAL(IPROB), SHARE(A, B, C), MP_SCHEDTYPE=SIMPLE

DO PARALLEL IPROB=1,10000

A(IPROB) = B(IPROB) + C(IPROB)

ENDDO

C PARTICLE TRACKING

C$DOACROSS LOCAL(IPROB, RANVAL), MP_SCHEDTYPE=DYNAMIC

DO PARALLEL IPROB=1,10000

RANVAL = RAND(IPROB)

CALL ITERATE_ENERGY(RANVAL)

ENDDO

```

Figure 5 shows parallel performance of a simple application, much like the vector-add loop example, on an unloaded 4-CPU SGI with various iteration scheduling options. As expected, the Dynamic and GSS options add overhead to the loops and are the worst performers for this particular loop. Further, the "random" assignment of threads (Dynamic, GSS) to processors results in the loss of cache affinity which occurs when iterations are distributed deterministically among processors (Simple).

Figure 5 - Impact of SGI Iteration Scheduling Options

Even on an empty system, the critical section overhead and loss of cache affinity caused by using the dynamic iteration scheduling options on the SGI is apparent.

Iteration scheduling does not solve the problem of thread imbalance. Iteration scheduling choices should only be made based on the nature of the iterations. If an application is well suited to dynamic iteration scheduling, it has a chance of acceptable performance when there are excess threads. On the other hand, if an application is well suited to simple scheduling, converting it to have dynamic scheduling will have a significant negative performance impact as shown above. ASAT solves the problem of having more active threads than processors independently of iteration scheduling approach. ASAT enhances all the iteration scheduling approaches because when ASAT is enabled they can depend on threads which have nearly 100% access to a CPU.

While these example FORTRAN loops are two ends of a spectrum, there are a number of different types of processor self-scheduling approaches. Part of the challenge is to balance the cost (or existence) of the critical section against the amount of work done per

invocation of the critical section. In the ideal world, the critical section would be free and all of the scheduling would be done dynamically. Convex's ASAP can nearly achieve the ideal using dynamic approaches with relatively small chunk size and expensive hardware. The following section summarizes some of the research into the choice of iteration scheduling technique.

# 2.1.2 Processor Self Scheduling Research

The primary focus of the dynamic load balancing of loop iterations has been in the study of the assignment of iterations to threads for different loop bodies. The challenge is to balance the overhead of distributing the iterations dynamically and the cost of waiting for an out-of-balance computation to complete.

The following is the breakdown of iteration scheduling techniques:

- Pure Self Scheduling (PSS)

- Chunk Self Scheduling (CSS)

- Guided Self Scheduling (GSS)

- Trapezoid Self Scheduling (TSS)

- Safe Self Scheduling (SSS)

Pure Self Scheduling (PSS) is the same as dynamic scheduling in the SGI compiler as described in the previous section. PSS allocates iterations to a processor dynamically for each iteration. As each processor reaches the top of a parallel loop, it enters a critical section to determine the next iteration to be performed. PSS has the potential for having

ideal load balancing because its granularity is a single iteration, but the overhead of the critical section may be prohibitive.

Chunk Self Scheduling (CSS) is an improvement to PSS for situations where iterations are short but still have some variation. In CSS a "CHUNK" of iterations are "grabbed" during each critical section. CSS reduces the scheduling overhead, but can have problems in producing a balanced execution time for each processor [24]. The run-time would be modified as follows to perform the particle tracking loop example using a chunk size of 100:

```

IPROB = 1

CHUNKSIZE = 100

WHILE (IPROB <= 10000 )

BEGIN_CRITICAL_SECTION

ISTART = IPROB

IPROB = IPROB + CHUNKSIZE

END_CRITICAL_SECTION

DO ILOCAL = ISTART, ISTART+CHUNKSIZE-1

RANVAL = RAND(ILOCAL)

CALL ITERATE_ENERGY(RANVAL)

ENDDO

ENDWHILE</pre>

```

The choice of chunk size is a compromise between overhead and termination imbalance.

Again, typically the programmer must get involved through directives in order to control chunk size.

Guided Self Scheduling (GSS) and Trapezoidal Self Scheduling(TSS) are more complicated approaches which dynamically alter the chunk size as the loop progresses to attempt to blend the benefits of PSS and CSS while minimizing their negative impacts.

In GSS [24], the chunk size is varied throughout the execution of the loop. Early in the execution of the loop, large chunks are processed, and as the loop nears termination, the

chunk size is reduced. This technique has the advantage that for the early iterations, overhead is minimized because many iterations of the loop execute for each critical section execution. As the loop nears termination, GSS approaches pure self scheduling. In GSS the chunk size is reduced in a geometric fashion as the loop proceeds. One example would be to have the chunk size divided by two each time though the critical section. In Figure 6, one possible iteration assignment for GSS is shown.

Figure 6 - Iteration Assignment for Guided Self Scheduling

Note that the first time each thread takes iterations, it takes 100 iterations and the second time through it takes 50. A slight modification to GSS called GSS(k) bounds the minimum chunk size to a fixed value (k) so GSS approaches CSS toward the end of the loop. GSS(k) is used in loops with short iteration times to keep GSS from performing one and two iterations per critical section execution during the final phase of the loop. GSS is supported in the SGI Power FORTRAN [33] compiler.

Trapezoid Self Scheduling (TSS) [39,40] improves on GSS. One problem with GSS is that the number of critical section executions required at the end of the loop becomes quite large as the chunk size approaches one. The other problem occurs when there is a

widely varying execution time for the work of each iteration. A processor which grabs a large number of iterations at the beginning of the loop may get an inordinate number of iterations which take a long time causing significant imbalance. Another case in which GSS performs poorly is when the time of execution for each iteration is decreasing uniformly. The first large chunk grabbed at the beginning of the loop will have the longest execution time per iteration. TSS reduces the number of iterations in a linear fashion as the loop progresses. TSS achieves a balanced workload under a broader range of execution conditions than any of the other scheduling techniques.

In TSS, the size of the first and last chunk is specified as well as the change in chunk size.

The chunk size starts out high and during each critical section, the chunk size is

decremented. By reducing the chunk size in a linear fashion, TSS has less overhead than

PSS and is more capable of coping with varied work loads than CSS or GSS.

An important aspect of TSS is the choice of the starting, ending, and incremental chunk size. To determine the optimum for these values, some advance knowledge of the iteration times is needed. However, there are some conservative values which can be chosen without pre-knowledge of loop execution time for the starting, ending, and incremental chunk size which yield good results for a wide range of loops. TSS has been implemented in a Beta version of a production compiler [11].

The goal of Safe Self Scheduling (SSS) [16] is to assign each processor the largest possible number of iterations as its initial chunk size and then perform the rest of the loop in a simple self scheduled mode. If the initial assignment of iterations to the processors accurately reflects the actual execution time, SSS can perform excellent load balancing.

# 2.2 Dynamic Load Balancing on Convex Vector/Parallel Supercomputers

Each of these iteration scheduling approaches has its strengths and weaknesses based on the cost of the critical section and loss of cache affinity. Both problems can be minimized with sufficient hardware investment. The Convex C-Series (C240, C3240, C3480, C3880, C4xx) vector/parallel supercomputers have solved both of these problems with extra hardware.

Convex computer systems are used as departmental and central site computers for many numerically-intensive computing applications. These systems have a maximum of 4 or 8 CPUs and extensive parallel processing support in hardware called Automatic Self-allocating Processors (ASAP) [7]. No cache is used and the memory subsystems have a large number of banks. With these hardware features, the Convex can use dynamic scheduling for every parallel loop. Because the Convex systems have vector registers with 128 elements, it is quite natural to schedule most parallel loops with a chunk size of 128 for maximum performance and nearly ideal load balancing.

Figure 7 - Convex C-Series Architecture

The ASAP processing in the Convex C-Series systems is made possible because of an architectural feature called "Communication Registers" (Figure 7) which are shared by all of the CPUs. These communication registers allow a multi-threaded process to create, delete, or context-switch threads with minimal performance impact. Using this hardware, the compiler can parallelize loops without regard for the number of threads which will actually execute in the parallel loop. An idle CPU can dynamically create a thread and enter a parallel computation with low overhead.

This hardware support allows users to compile their applications assuming a generalized parallel environment regardless of whether or not there will be enough resources at runtime to execute with multiple CPUs. One significant benefit of ASAP is that a long running job that is compiled to run in parallel can "soak-up" idle cycles as load changes.

This flexibility allows a parallel/vector computer to be nearly 100 percent utilized over long time periods.

ASAP capabilities are accessed using special machine language extensions. In the following example, a small FORTRAN loop with its associated machine language is shown.

```

DO I = 1,256

A(I) = B(I) * 3.14

ENDDO

snd.l s0,0x8001 ; Communication Register ****

spawn L3,sp

; Post Request for Help ****

L3: 1dw #0,a5

; Nice constant

L5: inc.w 0x8001,a5

: Increment Comm Register ****

bra.f L5

; Make sure we get it

le.w 1020,a5

; Loop Termination

jbra.t L6

; Get Out

ld.w

B(a5),s0

; Load value

mul.s 3.14,s0

; Multiply

st.w s0,A(a5)

; Store

jbr L3

; Jump Back up

L6: join

; Drop back to 1 CPU ****

```

In the above example<sup>1</sup>, the instructions marked with asterisks (\*\*\*\*) are the instructions which access the communication registers. The "snd.l" instruction stores a value into a communication register and the "inc.w" instruction increments the communication register. The "spawn" instruction indicates the beginning of a parallel loop and requests that any free processors create a thread and enter the loop. At run-time if there is only one CPU available, the ASAP "spawn" will be executed, but the ASAP hardware will not

<sup>&</sup>lt;sup>1</sup> This example was taken from Convex training materials, dated 1988.

create any additional threads. If additional CPUs become available while the loop is being executed, new threads will be created and enter the computation at the "spawn" point.

The run-time environment uses the global communications registers for iteration variables in parallel loops regardless of whether the loop is being executed on one CPU or several. Accesses to these communication registers are implicitly synchronized across processors so there is no need for a separate critical section for access to these shared values.

The "join" instruction indicates the end of the parallel loop. As each thread finishes its last iteration, it executes the "join". For all threads except the last thread, the join destroys the thread. When the last thread executes the join, the join is a no-op and the thread continues on the serial portion of the code.

Because the ASAP instructions and the communication registers are so fast, the single CPU performance of an ASAP application is not much slower than the performance of the application compiled for a single CPU. Using ASAP, the number of processors and threads assigned to the application depends on the system load. As the load changes dynamically, the number of processors and threads assigned to the parallel code in an application changes as the loop is executed.

When ASAP is used on these systems, it is very easy to keep the system 100% utilized under dynamic load conditions. Parallel applications can get the best possible time to solution (under current load) while other programs continue to use the system effectively.

When an ASAP job runs concurrently with a randomly changing load on a four processor Convex C-240, ASAP automatically adjusts the number of threads in use on the system so that there are never more than four threads overall. If there are more than four jobs running, the ASAP job only uses a single thread. ASAP works to maximize overall system load by allowing the parallel jobs to use all the available cycles which remain after yielding to the single processor jobs (assuming equal priority).

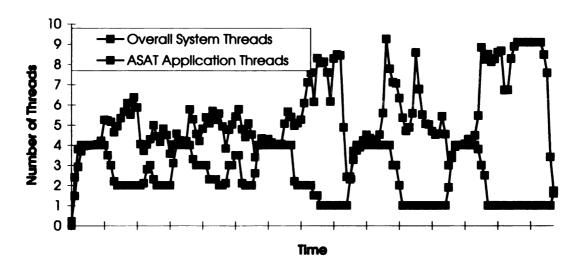

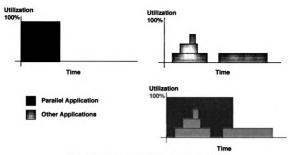

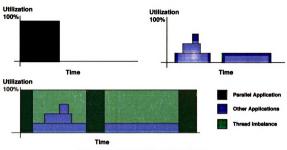

Figure 8 shows graphically how this resource sharing occurs. In this figure, the horizontal axis is time and the vertical axis is the percentage of the four CPUs in use. In the first graph, a parallel application uses all four CPUs because there is no other load on the system. The second graph of the figure shows several unrelated serial jobs executing on an otherwise empty system. Each job has a different start time and duration. While this job is running, at times there are no CPUs in use and at other times, there are 3 CPUs in use. Because of the variations in load, the system is not 100% utilized over the indicated time period. This collection of jobs is the "load" that is put on the system. In the third graph, the parallel ASAP application is run at the same time as the other serial code. The ASAP hardware automatically adjusts the usage of the parallel ASAP job to match the load on the rest of the system. The ASAP job "soaks-up" the available cycles resulting in high overall utilization under the dynamic load. In addition, the parallel job does not slow down the serial jobs.

Figure 8 - The Operation of ASAP Under Load

The time to solution for the parallel application when run with the other applications is affected by the load on the system, but the total CPU use by the parallel application is approximately the same as on an unloaded system. Under light load, the parallel application grabs as many free processors as it is capable of using. It should be noted that the number of processors an application is capable of using can vary from loop to loop (see operating point later in this chapter). When there is a heavy load on the system, the scheduler does not assign more than one CPU to the ASAP application (assuming the ASAP application does not have a fixed higher priority than the other applications). In some sense, the parallel ASAP application politely allows the other applications to use the processors they need.

Hardware approaches have one advantage over ASAT and other software-based, threadadjustment solutions because they have the ability to adjust threads while a parallel loop is executing. The details of this process are rather complex and won't be covered here. However, because of this, hardware based approaches do *not* depend on the existence of the serial portion of the execution profile to accomplish dynamic load balancing.

There is a disadvantage to the hardware approaches when compared to the software solutions such as ASAT, LLPC, or Process Control. The hardware approaches are forced to use some form of dynamic iteration scheduling with a relatively small chunk size to cope with dynamic load. With small chunk sizes the overhead of the critical section can become significant. Simple scheduling, on the other hand, has no overhead during the processing of the loop because it completely divides the iterations among the threads before the loop starts. Simple iteration scheduling is ruled out for hardware approaches because the number of threads which will actually execute the loop is unknown before the loop starts, and the number may dynamically change throughout the execution of the loop. Because there is a very large number of parallel loops for which simple iteration scheduling is the proper approach, this disadvantage is not a trivial one.

## 2.2.1 Performance of the Convex on Parallel Jobs

To test the performance of ASAP on the Convex C-240, a simple, parallel computation will be used as the benchmark application. The kernel for these tests is as follows:

```

C$ DO_PARALLEL

DO J=1,100000

A(I) = B(I) + C(I) * D(I)

ENDDO

```

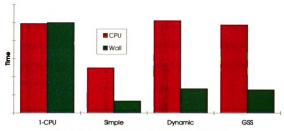

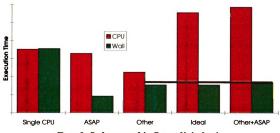

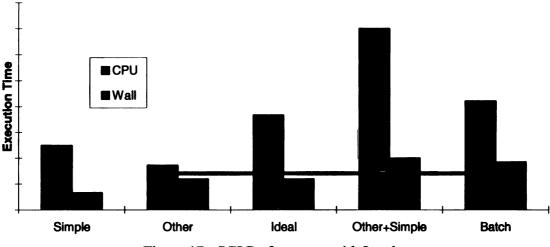

Figure 9 shows the performance of the code with several compiler options and load scenarios. The first bars show the CPU and wall time for the application on a single CPU.

The second set of bars shows the performance of the same application on four empty

CPUs. Since the application makes good use of the parallel resources, its CPU time is roughly the same and its wall time is reduced by 75%. The third bars, labeled "Other", indicate the overall time for a set of single-threaded applications spaced out over time. These applications do not generate enough load to completely utilize the four processor system. These applications arrive randomly and execute for a random amount of time. The wall time and CPU time shown in the chart is the aggregate duration for all of the jobs.

The fourth bar shows the "Ideal" CPU and wall time for the combination of the parallel job and the set of single-threaded jobs running simultaneously assuming perfect load balancing on four CPUs. Note that while CPU time increases additively, the wall time does not increase from the "Other" bars to the "Ideal" bars. This lack of an increase is because on the four CPU system, there are enough "spare" cycles while the "Other" job is running for the parallel job to execute to completion. The ideal performance would only occur if the ASAP job could "soak up" the free cycles while the "Other" jobs were running without adding a great deal of overhead. The last bar shows the actual performance achieved on the Convex C-240 when the jobs are run together.

Figure 9 - Performance of the Convex Under Load

In the actual run using ASAP and the "Other" jobs, both the CPU time and the wall time are about 1.05 times longer than the ideal time. This small difference shows that ASAP is very effective in maintaining good utilization when faced with a combination of a compute job with other unrelated load. Long term experience has shown that this excellent load balancing capability with low overhead (~5%) is maintained across a wide range of load scenarios consisting of various mixes of computer and interactive processes.

### 2.3 FORTRAN Run-Time Thread Management

Because bus-based commodity parallel processors have no hardware support for the dynamic creation of threads, a parallel application must depend on the operating system to manage its threads. Before a loop can begin execution with a number of threads, the threads must be activated to join the parallel loop. In this section we examine how this is thread activation is accomplished at run-time. Thread management is only mildly related to iteration scheduling (Section 2.1). Iteration scheduling assumes that some externally controlled number of threads are participating in the loop and distributes the iterations

among those threads. Thread management deals with the issues related to activating threads which are to participate in a parallel loop. Of particular interest is the number of threads which are made available to the iteration scheduler for each parallel loop execution.

One simple approach would be to invoke the operating system to create the necessary threads at the beginning of each parallel loop, and destroy the threads at the end of the loop much like the Convex ASAP processing. Unfortunately, calling the operating system at the beginning of each loop would incur excessive overhead. In addition to the operating system overhead, the arrival of these newly created threads to enter the parallel computation is often skewed significantly [10]. To avoid this overhead and late thread arrival, the run-time library typically creates its threads once at the beginning of execution and then manages those threads in user space.

This approach which creates a fixed number of threads at the beginning of execution and uses them throughout the duration of the application is referred to as Fixed Thread Scheduling (FTS) throughout this document. The choice of the name "Fixed" emphasizes the fact that the number of threads does not change once the application begins execution.

In this section, we will examine how these threads are managed by the run-time library and the performance of this approach in the face of a dynamic load.

#### 2.3.1 Run-Time Thread Management Details

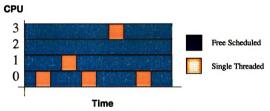

When a compiled parallel application is executed, the run-time environment starts up a number of threads. The number of threads is often the same as the number of installed processors. These threads are scheduled by the operating system much like UNIX processes. On some systems, these threads are scheduled by the operating system using gang scheduling. When a set of threads is gang scheduled, either all of the threads are executing or all of the threads are suspended<sup>2</sup>. In Figure 10 (Free Scheduling) and Figure 11 (Gang Scheduling) these approaches are graphically compared.

Figure 10 - Free (Non-Gang) Thread Scheduling

If gang scheduling is done in its strictest sense, a significant amount of time could be wasted when a multi-threaded application is timesharing with a single-threaded application as in Figure 11.

<sup>2</sup> This is a simplified definition. In actuality the operating system tries to do its best to get all threads started within a specified time period.

-

Figure 11 - Gang Thread Scheduling

Regardless of the way the operating system schedules the threads, when the program starts, one thread begins executing the user application while the other threads "spin", waiting for a parallel loop to be encountered. The code which these waiting threads execute is as follows:

```

while ( wakeup == 0 ) ; // "Infinite loop"

goto beginning_of_loop;

```

The variable wakeup is initially set to zero. With a bus-based system, this approach might appear to cause a great deal of unnecessary memory traffic. Actually, each waiting processor ends up with a shared cached copy of the wakeup variable with the value zero. Once the caches have been filled, there is no additional memory traffic as these waiting processors execute this tight loop. Some systems [35] have added special hardware instructions to make this wakeup from a spin loop perform even more efficiently.

When a parallel loop is encountered, the variable beginning\_of\_loop is set to indicate which parallel loop is about to be executed and the variable wakeup is set to one to

activate the waiting threads. Setting wakeup to one causes all of the cached copies to be invalidated and the next iteration of the spin loop exits as the caches reload with the new value of wakeup. The waiting threads immediately notice the change, exit the spin loop and join the computation. Once the threads arrive at the loop, they each determine the appropriate iterations to process using the iteration scheduling technique chosen for this particular loop and begin processing those iterations.

When the loop completes, each executing thread enters a barrier and when all of the threads have entered the barrier one thread continues executing in serial. The remaining threads again execute the spin loop waiting for the next parallel loop. This approach results in extremely quick thread activation times.

To demonstrate the timing of these operations, the following FORTRAN loop was executed on the SGI:

The entire source code for this program is included in Appendix A. Because the scheduling type is SIMPLE, the consistent mapping of a CPU to an iteration of the J loop is forced. By checking the elapsed time between the IN and MIDDLE times, one can determine the time for a thread to arrive in the parallel section of a loop (spawn time). By checking the elapsed time between the MIDDLE and OUT, the time spent processing the loop-end barrier can be determined for each thread. Once the overhead for the WALLTIME calls is removed, this loop does no work and we should be able to measure

the performance of the parallel loop startup and completion. This loop will be used to measure how fast a thread can be brought into the loop from a spinning state. Later we will measure how these timings change when a loop is executed when there are more threads than processors.

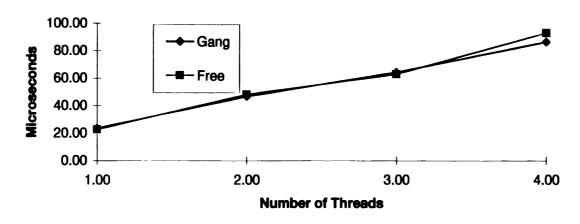

In the Figure 12, the performance of this loop is measured on an empty system. The loop was executed a number of times and the average values are reported in this figure.

Figure 12 - Thread Timing Results

This figure shows the performance of the first and second threads (out of four threads) using free scheduling and gang scheduling. Using Gang Scheduling, the entire loop takes 36 microseconds and using free scheduling it takes 40 microseconds. Thread one is the thread which wakes the other threads up so it is the first to arrive in the body of the loop. Thread one takes 7 microseconds to go from the serial code to the body of the loop in both cases. Thread two takes 16 microseconds to arrive in the body of the loop. This difference shows how quickly the "helper" threads can arrive from their spin loops. The

barrier at the end of the loop takes somewhat longer in general than the spawn process.

Also, since thread one arrives quicker, it completes its work quicker and as such spends more time at the barrier waiting until thread two arrives to terminate the loop. The performance for threads three and four look identical to thread two.

While the spin-wakeup approach results in fast loop startup times, a problem is that it assumes that all the available threads are actually executing the spin loop at all times when they are not participating in a parallel loop. There are two reasons that a thread might not be executing the spin loop when a parallel loop is encountered. The first reason is that the thread may have decided to voluntarily put itself to sleep because it has waited too long in the spin loop code at a barrier or waiting for work. The second reason is that the operating system may have suspended a thread involuntarily because of other unrelated load.

A spinning thread waiting for work will voluntarily suspend itself to minimize the wasted CPU time in case an application is about to spend a significant time running serial code.

The pseudocode for this is roughly as follows:

```

while ( wakeup == 0 ) {

counter = 10000;

while (counter > 0 ) {

if ( wakeup == 0 ) break;

counter --;

}

if ( counter == 0 ) release_cpu();

}

goto beginning_of_loop;

```

The *counter* value is typically controllable by the application programmer. The programmer may also be able to suppress the *release cpu* behavior altogether.