THESIB

This is to certify that the

thesis entitled

Hardware-software Partitioning in Co-design of Embedded Systems

presented by

Habeel Ahmad

has been accepted towards fulfillment of the requirements for

Master's degree in Electrical Eng

Dearry J Koron

Major professor

Date 8/20/48

**O**-7639

MSU is an Affirmative Action/Equal Opportunity Institution

# LIBRARY Michigan State University

# PLACE IN RETURN BOX

to remove this checkout from your record. TO AVOID FINES return on or before date due.

| DATE DUE | DATE DUE | DATE DUE                  |

|----------|----------|---------------------------|

|          |          |                           |

|          |          |                           |

|          |          |                           |

|          |          |                           |

|          |          |                           |

|          |          |                           |

|          |          |                           |

|          |          |                           |

|          |          | 1/98 c/CiRC/DateDue.p85-p |

# HARDWARE-SOFTWARE PARTITIONING IN CO-DESIGN OF EMBEDDED SYSTEMS

By

Habeel Ahmad

# A THESIS

Submitted to Michigan State University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

Department of Electrical Engineering

#### ABSTRACT

# HARDWARE-SOFTWARE PARTITIONING IN CO-DESIGN OF EMBEDDED SYSTEMS

By

## Habeel Ahmad

The rapid advancements in science and technology and especially in the field of computers have made an impact on every aspect of our daily life. Among the latest trends is to make devices known as embedded systems that consist of one or more programmable components. Hardware-software co-design is a methodology that provides rules and techniques for embedded system design.

This work has focused on one of the aspects of co-design called hardware-software partitioning. A variety of co-design frameworks were studied with a view to explore the partitioning algorithms. POLIS, which currently supports manual partitioning, was chosen as a candidate for implementation of automatic partitioning. Two partitioning algorithms, namely, Group Migration and Simulated Annealing were implemented in  $C^{++}$  for this purpose. The existing design flow in POLIS was altered to generate the performance estimates for both software and hardware implementations of system modules. The algorithms used these estimates to find the best partition that satisfied the constraints.

The results produced by the partitioning algorithms are in agreement with the results published in the POLIS documentation. The work can be extended to integrate the partitioning algorithm with POLIS design flow and to include a rapid prototyping environment for verification. I dedicate this thesis to my parents,

Aziz Ahmad and Amna Aziz

#### ACKNOWLEDGEMENTS

I start in the name of Allah Almighty, the most beneficent and the most merciful, whose everlasting blessings made the completion of this thesis possible.

Next, I wish to express my sincere gratitude to my advisor Dr Diane T. Rover for her commitment, encouragement and guidance that helped me conclude this study. Appreciation is also extended to Dr. Micheal Shanblatt and Dr. Bruce E. Kim for their valuable suggestions and also for serving as members of my guidance committee. My thanks are also due to the secretarial staff of EE Department for their support at all times.

I am grateful to Mr. Bassam Tabbara at UC Berkeley for his prompt response and guidance during my struggle with POLIS and PTOLEMY.

I would like to express my gratitude to all of my valuable friends, especially Mr. Abdul Naeem Khan, Dr. Pervaiz Akhtar, Mr. Fida M. Khan and Dr. Dale Joachim for their understanding, encouragement and social support during my stay at East Lansing. My special thanks to Mr Aman-ullah Ateequi and his family for their caring.

Finally, I wish to acknowledge the support and sacrifice of my mother, wife and sister back home during my stay at MSU that enabled me to fully concentrate on my studies. I am especially grateful to my loving wife, Najm us Saher, who always remained a source of inspiration and encouragement during the course of studies. I also acknowledge her patience and courage for single handedly running all the affairs in looking after our children, Rafiah, Sa'ad, Saleha and Sa'adiah during my long absence from home.

# **TABLE OF CONTENTS**

| LIST OF TABLES                                        | viii |

|-------------------------------------------------------|------|

| LIST OF FIGURES                                       | ix   |

|                                                       |      |

| CHAPTER 1                                             |      |

| INTRODUCTION                                          |      |

| 1.1 Embedded Systems                                  | . 2  |

| 1.2 Hardware-Software Co-design                       | 4    |

| 1.3 Co-design Methodology                             | 5    |

| 1.4 Conventional Approach                             | 6    |

| 1.4.1 Specification                                   | 6    |

| 1.4.2 Partitioning                                    | 9    |

| 1.4.3 Synthesis                                       | 9    |

| 1.4.3.1 Hardware Synthesis                            | 9    |

| 1.4.3.2 Software Synthesis                            | 10   |

| 1.4.3.3 Interface Synthesis                           |      |

| 1.4.4 Hardware-Software Integration and Co-simulation |      |

| 1.5 Model-Based Approach                              |      |

| 1.5.1 Validation                                      | 11   |

| 1.5.2 Partitioning and Implementation                 |      |

| 1.6 Partitioning Problem                              |      |

| 1.7 Scope of This Work                                |      |

| •                                                     |      |

| CHAPTER 2                                             |      |

| RELATED WORK                                          | 15   |

| 2.1 Vulcan                                            | 16   |

| 2.2 COSYMA                                            | 16   |

| 2.3 LYCOS: The Lyngby Co-Synthesis System             | 17   |

| 2.4 COMET                                             |      |

| 2.5 Ptolemy                                           |      |

| 2.6 SpecSyn                                           |      |

| 2.7 TOSCA                                             |      |

| 2.8 Other Frameworks                                  |      |

|                                                       |      |

| CHAPTER 3                                             |      |

| POLIS                                                 | . 24 |

| 3.1 Introduction                                      |      |

| 3.1.1 Model of Computation (CFSM)                     |      |

| 3.2 Design Flow                                       |      |

| 3.2.1 Overview                                        |      |

| 3.2.2 High Level Language Translation                 |      |

| 3.2.3 Formal Verification                             |      |

| 3.2.3 System Co-simulation                            |      |

| 3.2.4 Partitioning and Architecture Selection         |      |

|                                                       | 55   |

|     | <ul> <li>3.2.5 Hardware Synthesis</li> <li>3.2.6 Software Synthesis</li> <li>3.2.7 Interfacing Implementation Domains</li> <li>3.2.8 Rapid Prototyping</li> <li>Design Example</li> <li>3.3.1 Specification</li> <li>3.3.2 Estimation</li> <li>3.3.3 Co-simulation</li> </ul> | 34<br>35<br>35<br>35<br>36<br>38 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|     | 3.3.4 Hardware Synthesis                                                                                                                                                                                                                                                      |                                  |

|     | 3.3.5 Software Synthesis                                                                                                                                                                                                                                                      |                                  |

|     | 3.3.6 Implementation                                                                                                                                                                                                                                                          |                                  |

|     |                                                                                                                                                                                                                                                                               | ••                               |

| CH  | APTER 4                                                                                                                                                                                                                                                                       |                                  |

| SYS | STEM PARTITIONING                                                                                                                                                                                                                                                             | 42                               |

| 4.1 | Partitioning Approaches                                                                                                                                                                                                                                                       | 43                               |

|     | 4.1.1 Structural Partitioning                                                                                                                                                                                                                                                 | 43                               |

|     | 4.1.2 Functional Partitioning                                                                                                                                                                                                                                                 | 44                               |

| 4.2 | Partitioning Issues                                                                                                                                                                                                                                                           | 45                               |

|     | 4.2.1 Specification and Levels of Abstraction                                                                                                                                                                                                                                 |                                  |

|     | 4.2.2 Granularity                                                                                                                                                                                                                                                             | 47                               |

|     | 4.2.3 System-Component Allocation                                                                                                                                                                                                                                             | 47                               |

|     | 4.2.4 Metrics and Estimation                                                                                                                                                                                                                                                  | 48                               |

|     | 4.2.5 Cost Function                                                                                                                                                                                                                                                           |                                  |

|     | 4.2.6 Partitioning Algorithm                                                                                                                                                                                                                                                  | 50                               |

|     | 4.2.6.1 Constructive/Iterative Algorithms                                                                                                                                                                                                                                     |                                  |

|     | 4.2.6.2 Greedy/Hill-climbing Algorithms                                                                                                                                                                                                                                       |                                  |

|     | 4.2.7 Output                                                                                                                                                                                                                                                                  |                                  |

| 4.3 | Basic Partitioning Algorithms                                                                                                                                                                                                                                                 |                                  |

|     | 4.3.1 Vulcan Algorithms                                                                                                                                                                                                                                                       |                                  |

|     | 4.3.2 Ratio Cut                                                                                                                                                                                                                                                               |                                  |

|     | 4.3.3 Group Migration (Kernighan-Lin)                                                                                                                                                                                                                                         |                                  |

|     | 4.3.4 Simulated Annealing                                                                                                                                                                                                                                                     |                                  |

|     | 4.3.5 Genetic Evolution                                                                                                                                                                                                                                                       |                                  |

|     | 4.3.6 Binary Constraint-Search                                                                                                                                                                                                                                                |                                  |

|     | 4.3.7 Integer Linear Programming                                                                                                                                                                                                                                              |                                  |

|     | APTER 5                                                                                                                                                                                                                                                                       |                                  |

|     | PLICATION OF PARTITIONING ALGORTIHMS IN POLIS                                                                                                                                                                                                                                 |                                  |

| 5.1 | Background                                                                                                                                                                                                                                                                    | 60                               |

|     | Partitioning in POLIS                                                                                                                                                                                                                                                         |                                  |

|     | Generation of Estimates                                                                                                                                                                                                                                                       |                                  |

| 5.4 | Selection of Algorithms for Automatic Partitioning in POLIS                                                                                                                                                                                                                   |                                  |

|     | 5.4.1 Assumptions                                                                                                                                                                                                                                                             |                                  |

| 5.5 | Features of C <sup>++</sup> Code                                                                                                                                                                                                                                              |                                  |

|     | 5.5.1 Group Migration (GM) Algorithm                                                                                                                                                                                                                                          | 67                               |

|     | 5.5.2 Simulated Annealing (SA) Algorithm                                                                                                                                                                                                                                      |                                  |

| 5.6 Case Studies                                                              | 71 |

|-------------------------------------------------------------------------------|----|

| 5.6.1 Hypothetical Cases                                                      | 71 |

| 5.6.1.1 Small Size Example                                                    |    |

| 5.6.1.2 Large Size Example                                                    | 72 |

| 5.6.2 Real World Example (Dashboard Controller)                               | 73 |

| 5.6.2.1 Design Constraints                                                    |    |

| 5.6.3 Results Obtained                                                        | 75 |

| 5.7 Analysis of Results                                                       |    |

| 5.8 Limitations of POLIS                                                      | 82 |

|                                                                               |    |

| CHAPTER 6                                                                     |    |

| CONCLUSION AND FUTURE DIRECTIONS                                              |    |

| 6.1 Summary                                                                   |    |

| 6.2 Validity of Results                                                       | 86 |

| 6.3 Recommendations and Future Directions                                     |    |

| 6.3.1 Integrating the Partitioning Algorithm in Polis Design Flow             |    |

| 6.3.2 Rapid Prototyping Platform                                              | 87 |

| ADENDICES                                                                     | 00 |

| APPENDICES                                                                    |    |

| APPENDIX A Group Migration Algorithm implementation in C <sup>++</sup>        |    |

| APPENDIX B Simulated Annealing Algorithm implementation in C <sup>++</sup> 10 |    |

| APPENDIX C Group Migration Algorithm Results                                  |    |

| APPENDIX D Simulated Annealing Algorithm Results                              |    |

| APPENDIX E Dashboard Example Results                                          |    |

| BIBLIOGRAPHY 14                                                               | 41 |

# LIST OF TABLES

| Table 2.1 | List of co-design frameworks examined in this thesis              |

|-----------|-------------------------------------------------------------------|

| Table 5.1 | Estimates for the modules of dashboard example                    |

| Table 5.2 | Partition found using GM and SA algorithms (1 MHz Clock)77        |

| Table 5.3 | Partition found using GM and SA algorithms (4 MHz Clock)79        |

| Table C.1 | Input data for the small example114                               |

| Table C.2 | Partitioned system of the small example116                        |

| Table C.3 | Input data for the large example117                               |

| Table C.4 | Partitioned system of the large example with equal weights 118    |

| Table C.5 | Partitioned system when Hw_Area is more important                 |

| Table D.1 | Input data for the small example 122                              |

| Table D.2 | Partitioned system of the small example                           |

| Table D.3 | Input data for the large example                                  |

| Table D.4 | Partitioned system of the large example 127                       |

| Table E.1 | Input and partition data for belt_control module135               |

| Table E.2 | Input and partition data for engine_speed module                  |

| Table E.3 | Input and partition data for wheel_speed module                   |

| Table E.4 | Input and partition data for net dac_demo (1 MHz Clock) 138       |

| Table E.5 | Partition data for net dac_demo (4 MHz Clock) 139                 |

| Table E.6 | Partition data for net dac_demo (Hw_Area constraint = 4000000)140 |

# **LIST OF FIGURES**

| Figure 1.1 | Architecture of a typical embedded system                               |

|------------|-------------------------------------------------------------------------|

| Figure 1.2 | Conventional co-design methodology 7                                    |

| Figure 1.3 | Model-based co-design methodology 8                                     |

| Figure 3.1 | Overview of the design flow in POLIS                                    |

| Figure 3.2 | The POLIS design flow                                                   |

| Figure 3.3 | Transition diagram of seat belt controller                              |

| Figure 4.1 | Essential partitioning issues                                           |

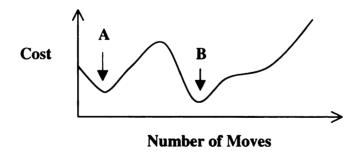

| Figure 4.2 | Escaping local minimum in iterative partitioning 51                     |

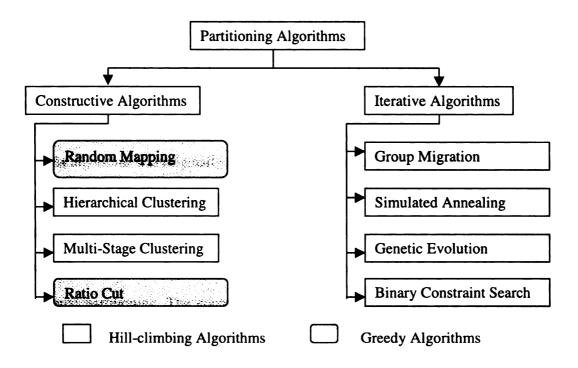

| Figure 4.3 | Classification of automatic partitioning algorithms53                   |

| Figure 4.4 | Group migration algorithm with two-way partitioning                     |

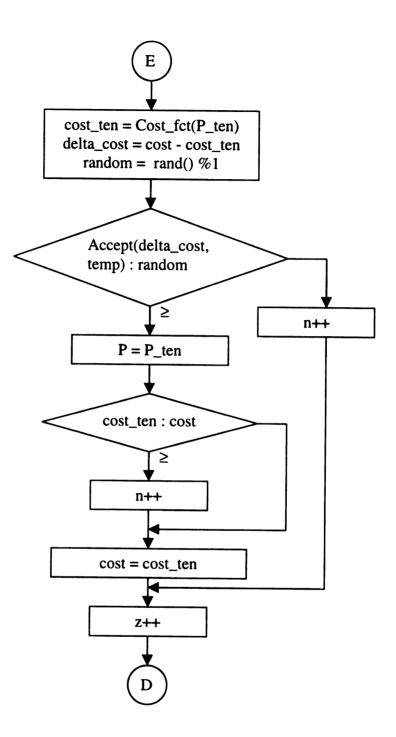

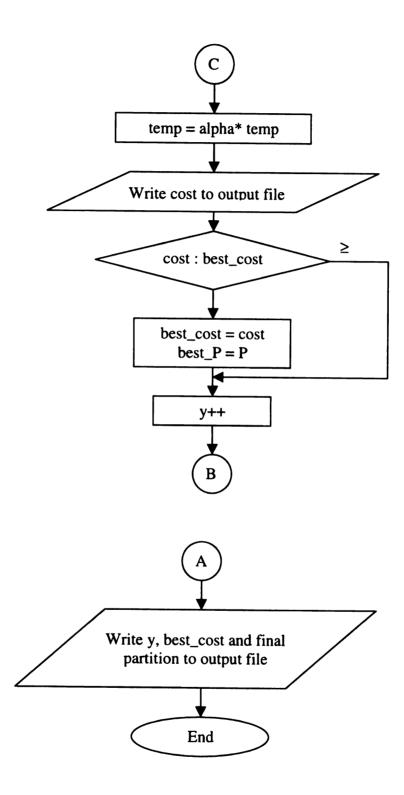

| Figure 4.5 | Simulated annealing algorithm 57                                        |

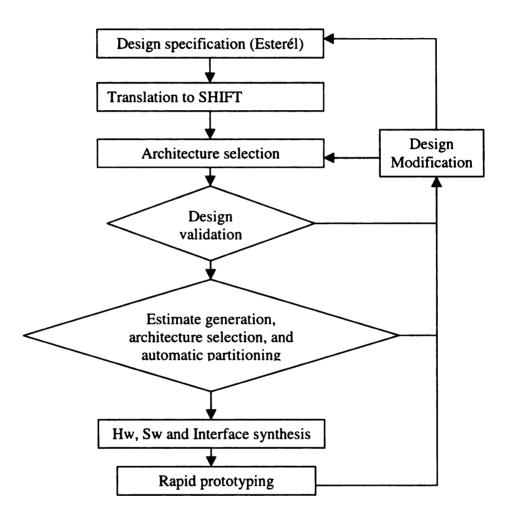

| Figure 5.1 | Modified design flow in POLIS                                           |

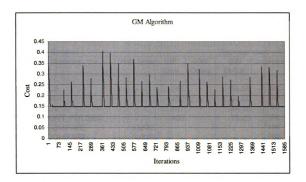

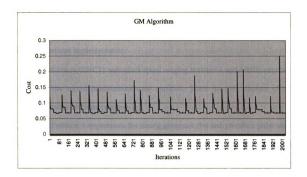

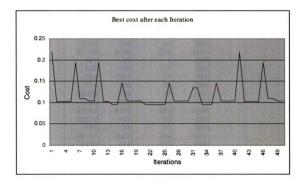

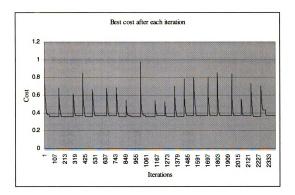

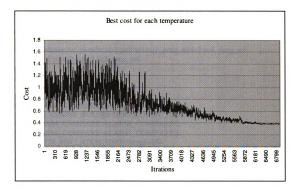

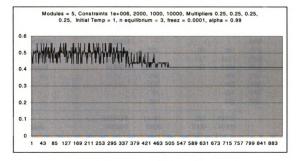

| Figure 5.2 | Plot of cost vs. iterations for GM algorithm (1 MHz Clock)78            |

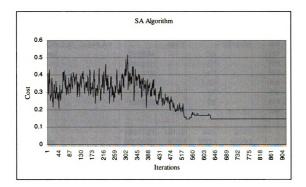

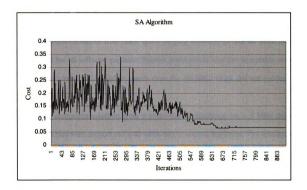

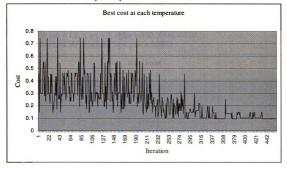

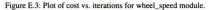

| Figure 5.2 | Plot of cost vs. iterations for SA algorithm (1 MHz Clock)              |

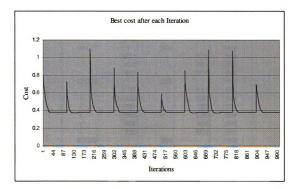

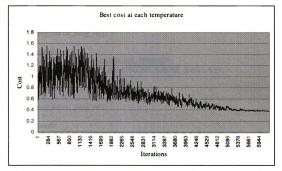

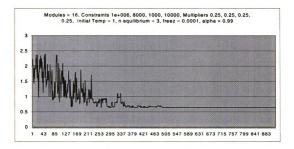

| Figure 5.3 | Plot of cost vs. iterations for GM algorithm (4 MHz Clock)80            |

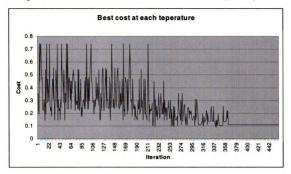

| Figure 5.4 | Plot of cost vs. iterations for SA algorithm (4 MHz Clock)              |

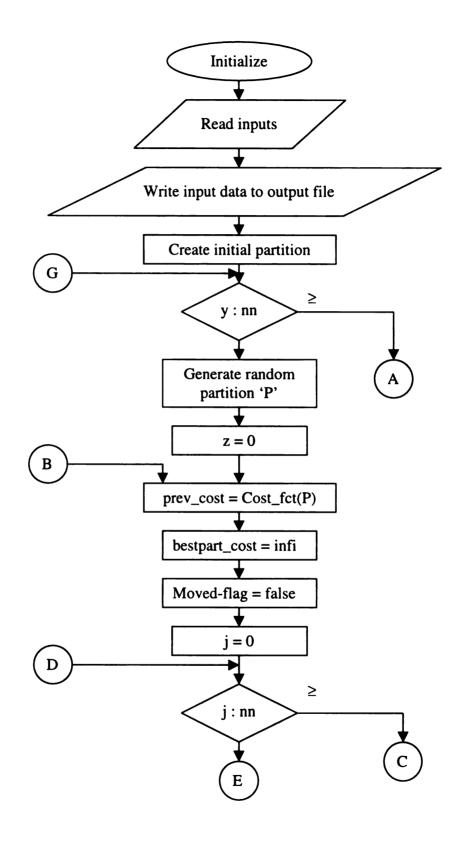

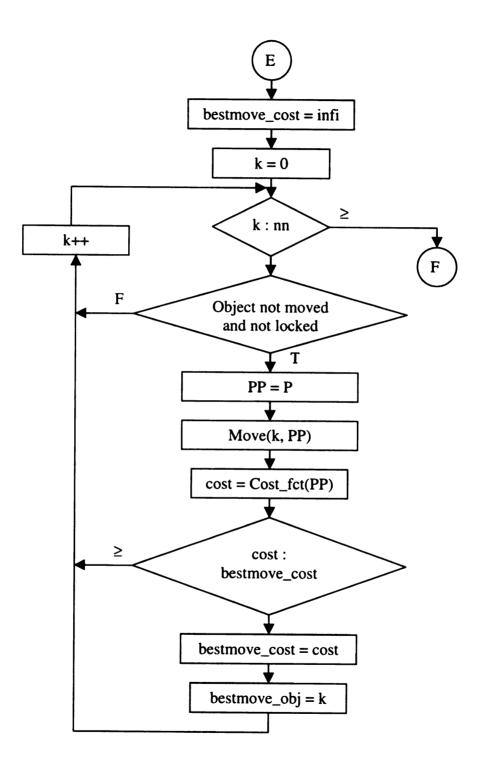

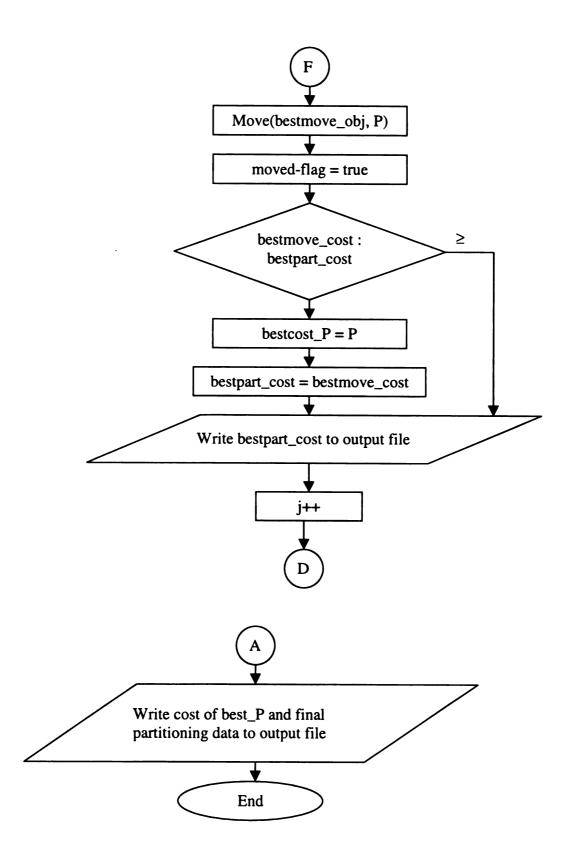

| Figure A.1 | Flow chart of GM algorithm program                                      |

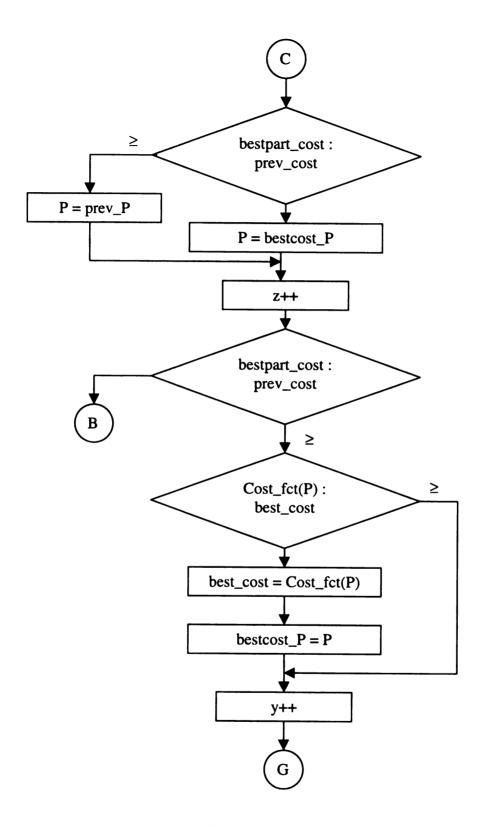

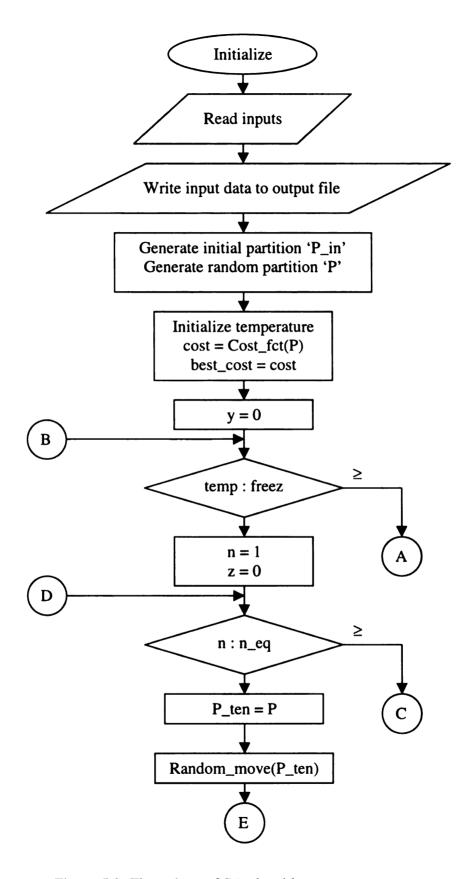

| Figure A.2 | Flow chart of SA algorithm program                                      |

| Figure C.1 | Plot of cost vs. iterations corresponding to partition in Table C.2 116 |

| Figure C.2 | Plot of cost vs. iterations corresponding to partition in Table C.4     |

| Figure C.4 Plot of cost vs. iterations corresponding to partition in Table C.5 |

|--------------------------------------------------------------------------------|

| Figure D.1 Plot of cost vs. iterations for the small example (Case 1)          |

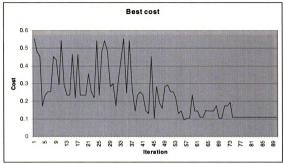

| Figure D.2 Plot of cost vs. iterations for the small example (Case 2) 124      |

| Figure D.3 Plot of cost vs. iterations for the small example (Case 3)          |

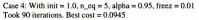

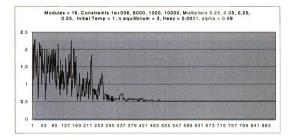

| Figure D.4 Plot of cost vs. iterations for each temperature value (Case 4) 125 |

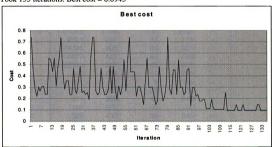

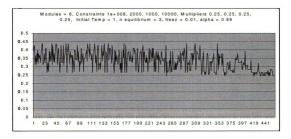

| Figure D.5 Plot of cost vs. iterations for the small example (Case 5) 125      |

| Figure D.6 Plot of cost vs. iterations for the small example (Case 6) 126      |

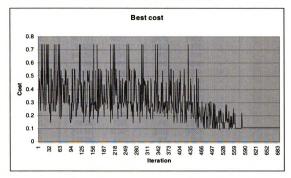

| Figure D.7 Plot of cost vs. iterations for the large example (Case 1)          |

| Figure D.8 Plot of cost vs. iterations for the large example (Case 2)          |

| Figure E.1 Plot of cost vs. iterations for belt_control module                 |

| Figure E.2 Plot of cost vs. iterations for engine_speed module                 |

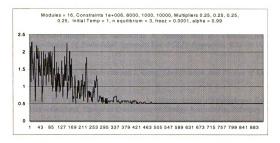

| Figure E.3 Plot of cost vs. iterations for wheel_speed module                  |

| Figure E.4 Plot of cost vs. iterations for net dac_demo (1 MHz Clock)          |

| Figure E.5 Plot of cost vs. iterations for net dac_demo (4 MHz Clock)          |

# CHAPTER 1

# **INTRODUCTION**

Electronics has made inroads in all fields of science and technology. Digital electronics is one of the most prolific fields in the present day world. It provides the building blocks for the wonder of the 20<sup>th</sup> century, the computer. Digital electronics is the enabling technology for the design of high-performance systems in which reliability and dependability are key issues, in such applications as space exploration and medical instrumentation. The continued miniaturization of digital circuits has made it possible to design and manufacture programmable components such as microprocessors and microcontrollers.

With the increasing role of computers in our daily life, one may envision a world where everything would assume an electronic dimension; *i.e.*, either it would be controlled by a computer or may contain one or more programmable components. This demands reconsideration of the role of computers in our daily life. For now, a user buys a computer as a platform to run a variety of programs that make it perform widely different tasks. With the advances in technology and increased market competition, the prices of computer hardware have gone so low that the highest cost a user has to pay today is that of software. In this scenario, it is logical to think of building special-purpose devices with optimized functionality for a dedicated application. The manufacturers of electronics systems have already adopted this approach. Out of the millions of microprocessors manufactured each year, only 20% are being used in the general-purpose

computers, whereas the rest of them are used in digital systems for dedicated applications known as embedded systems.

#### **1.1 Embedded Systems**

Embedded systems are digital systems, which perform specific functions. They are normally categorized as hardware-software systems. Embedded systems are defined as a collection of programmable parts and dedicated hardware components that are continuously interacting with the environment. By virtue of the requirement of continuous interaction with the environment they are also termed as reactive systems [1]. The software runs on microcontrollers or Digital Signal Processors (DSPs) and dedicated hardware is implemented in Application Specific Integrated Circuits (ASICs) or Field Programmable Gate Arrays (FPGAs). Generally, software is used for features and flexibility, while hardware is used for performance. Design of embedded systems can be subject to many different types of constraints, including timing, size, weight, powerconsumption, reliability and cost. Rapid advancement in the field of computer aided design (CAD) during the recent past has opened numerous vistas of research and development in the area of embedded system design. The research efforts are now being directed towards the development of such techniques, which not only result in meeting the requisite performance criteria but also reduce time-to-market and cost [2]. Following are some examples of embedded systems:

• Consumer Electronics: medical instruments, cameras, compact disc players, VCRs, microwave ovens and washing machines.

- Telecommunications: networking and communication systems such as satellites and cellular phones.

- · Automotive: engine controllers, anti-lock brakes and dashboard controllers.

- Defense and Aviation Electronics: airborne radio and radar, fire control, navigation and guidance, and cryptographic systems.

- · Plant and Process Control: Remote controlled toys, robots and plant monitors.

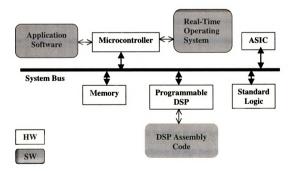

Figure 1.1 shows an example of the architecture of a typical embedded system. It consists of programmable components such as microcontroller and DSP and dedicated hardware such as ASIC and standard logic components. The microcontroller runs the application program under the control of real-time operating system (RTOS). The interface among the various components is implemented with the system bus.

Figure 1.1: Architecture of a typical embedded system.

Current practices of embedded system design tend to follow different paths for the design of hardware and software. A specification, often incomplete and written in non-formal language, is developed and sent to the hardware and software engineers. It involves multiple, subsequent hardware/software development steps in which a prototype is designed through refinement of specifications. Hardware-software partition is decided in advance and is adhered to as much as possible, because any changes in this partition may necessitate extensive redesign. Designers often strive to make everything fit in software, and off-load only some parts of the design to hardware to meet timing constraints. The problems with this design strategy are:

- Lack of a unified hardware-software representation, which leads to difficulties in verifying the whole system and, therefore, to incompatibilities across the hardware-software boundary.

- Definition of hardware-software partitions in the early design stages, which leads to sub-optimal designs.

- Lack of a well-defined design flow, which makes specification revision difficult, and directly impacts time-to-market.

#### 1.2 Hardware-Software Co-design

Hardware-Software co-design is considered to be a design methodology that can avoid the above-mentioned disadvantages. It is trying to meet system-level objectives by exploiting the synergism of hardware and software through their concurrent design. It can be viewed as a management discipline, which offers the possibility to develop large complex system products. Hardware-Software codesign is a complex process that

involves transforming a high-level system specification to an implemented hardwaresoftware system that meets the specification constraints.

Hardware-software co-design is predominant in the development of such systems where hardware and software modules closely interact to solve a certain task [3]. As discussed earlier, hardware-software systems are not new and they have continued to be designed using conventional approaches, however, methodologies that concurrently apply to both domains are now emerging. The growing interest in hardware-software co-design can be attributed to following developments or compulsions:

- Advances in enabling technologies such as system level specification and simulation environments, prototyping techniques, formal methods for design and verification, high-level synthesis and the emergence of CAD frameworks have opened new venues for hardware-software co-design.

- The increasing diversity and complexity of embedded systems demands advanced design methods for the development of both hardware and software.

- The market competition has made it imperative to decrease the cost of design and test of hardware-software systems. More than ever, optimization of cost and performance and a significant reduction in time-to-market are vital issues in the development of embedded systems.

# 1.3 Co-design Methodology

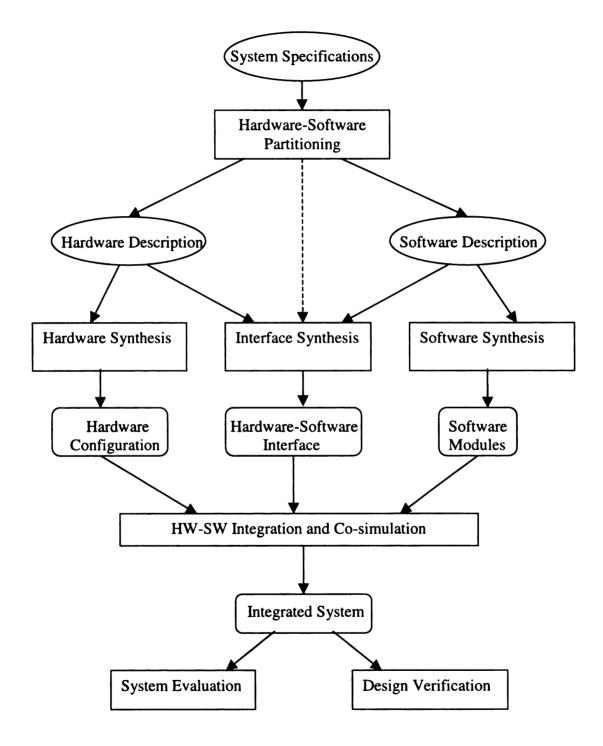

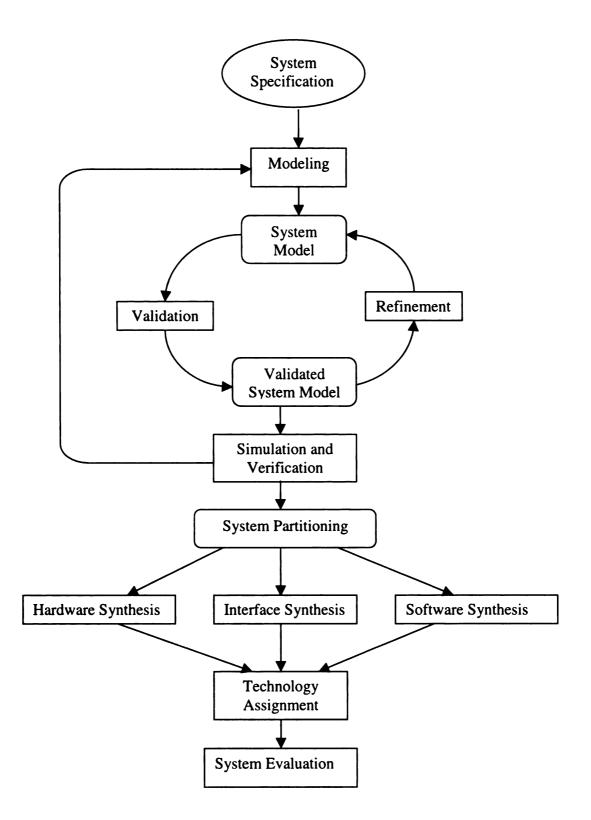

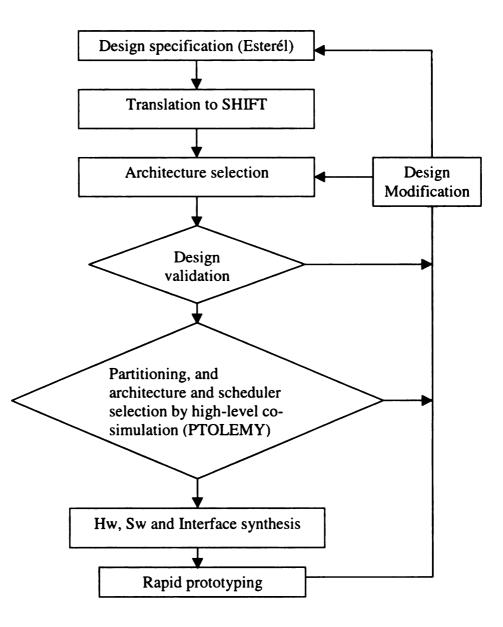

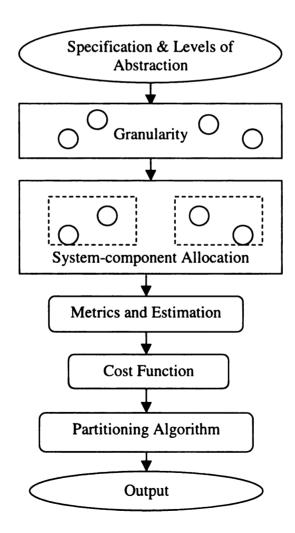

Co-design as practiced today relies heavily on techniques and methods that have been successfully applied in the past. New contributions are being made in the areas of design automation tools, tool interface, hardware-software partitioning techniques, and enhanced framework technologies. Currently, two approaches are followed by hardware-software system designers [3]. The conventional approach is the traditional approach where generic framework techniques are employed to facilitate tool encapsulation and integration, and management support is provided for coordinated and cooperative design. Figure 1.2 depicts a typical series of steps in this co-design methodology. This approach has been the focus of research in the past. The model-based approach is the focus of more recent research and favors late partitioning during the design process. Figure 1.3 illustrates the model-based approach. A brief description of both approaches follows.

# **1.4 Conventional Approach**

#### **1.4.1 Specification**

The first step in the conventional approach is description of specification. The objectives, requirements and constraints supplied by the user are often incomplete and lack clarity. This step helps in removal of inconsistencies and location of missing information, which results in formulation of system specifications. The traditional approach of system specification as an informal natural-language description has proved to be inadequate over the past [2][3]. It is not possible to automate the co-design process by using natural language descriptions. The designers have therefore evolved an executable-specification approach to overcome this limitation. In this approach the system's functionality is first captured with an executable language and then the functional objects are derived and partitioned. Since the specifications are machine readable, it is possible to develop tools to automate co-design. The specifications could

be verified using simulation, thereby eliminating errors early in the design and preventing costly changes in the subsequent stages of the design.

Figure 1.2: Conventional co-design methodology.

Figure 1.3: Model-based co-design methodology.

## 1.4.2 Partitioning

The next step is partitioning, where the designer decides to realize various components of the design in hardware and software. Partitioning is usually done manually. Partitioning may be done at various levels of abstraction or at different stages of the design. Early partitioning is preferred by the industry because of requirements of preplanning the development cycle. This however restricts late changes in the specifications. Late partitioning may result in better performance optimization and allows user change requests at later stages of the design.

## 1.4.3 Synthesis

Synthesis is final realization of a system in hardware and software. It also provides some feedback to the partitioning process based on the technology requirements or the specific application of the system. Tools for software synthesis have already been available in the past because of efforts put in by the software designers in development of compilers. Hardware synthesis tools are also appearing which have made rapid prototyping of hardware possible.

## 1.4.3.1 Hardware Synthesis

The hardware platform on which the software is to execute and the dedicated hardware that shares the functionality are synthesized during this phase, using the results of partitioning. Hardware synthesis involves technology binding by translation (mapping) of hardware descriptions such as VHDL, HardwareC, BLIF, *etc.* into gate level netlists.

#### **1.4.3.2 Software Synthesis**

Software synthesis involves translation of functionality into a program for a particular processor. The software description is generated in terms of a high level language such as  $C/C^{++}$ . A compiler is then used to translate this description into an executable code for the selected processor. The software synthesis may also include synthesis of the operating system, some times called real-time operating system (RTOS) due to the real-time reactive nature of embedded systems [1].

# **1.4.3.3 Interface Synthesis**

In order to provide the signal/data exchange capability an interface between the hardware and software is often required. Interface synthesis provides a means of hardware and software synchronization. Typically signal exchange (hardware), semaphore (software) or interrupt driven schemes are employed in this phase [1]. Implementations range from custom logic to dynamically configurable logic devices. A central scheduler in software may also be incorporated to control the hardware processes.

# **1.4.4 Hardware-Software Integration and Co-simulation**

The integration step involves co-simulation of hardware and software on a heterogeneous simulator. The results of simulation provide an assessment of the performance of design in terms of meeting the specifications and satisfaction of constraints. The verification step ensures that the designed system performs according to specifications.

# 1.5 Model-based Approach

Modeling is the process of conceptualizing and refining the given specifications. There exist a wide variety of potential formalizations of a design, but often a relation between a set of inputs and outputs characterizes the behavior of a system. This relation could be informal, may even be expressed in natural language, but the result of such an informal specification can easily be an expensive and unnecessary redesign. Formal modeling of a design consists of the following components:

- A functional specification, given as a set of explicit or implicit relations, which consists of inputs, outputs and internal state information.

- A set of performance indices that evaluate the quality of the design (cost, reliability, size, speed, power consumption, etc.) given as a set of equations, which include at least inputs and outputs.

- A set of constraints on these performance indices, specified as a set of inequalities.

- A set of properties that must be satisfied, given as a set of relations over inputs, outputs and states that can be checked against the functional specification.

# 1.5.1 Validation

After transforming a specification into a formal model, the whole model has to be checked on its functional correctness. This step is known as validation. It includes functional validation of subtasks and of the whole system, including formal verification and functional simulation. Functional validation and simulation concerning functionality and constraints such as hardware size, costs, timing and reusability are also performed.

#### **1.5.2 Partitioning and Implementation**

After validation, the designer can start to be more concrete by partitioning the model. The decision of what to do in hardware and what in software is important. If the best partitioning is found and validated successfully, a prototype of the hardware and the necessary machine code is generated for testing the system in actual environment.

## **1.6 Partitioning Problem**

One phase of the co-design process, the partitioning of specification into components and binding them to hardware/software resources, is the focus of current research. It is the central problem where a system designer decides which components of the system will be implemented in hardware and which will be realized in software. Partitioning requires an effective means of exploring the design space through evaluation of candidate solutions, considering the interaction of multiple constraints [2]. The decision to put a particular component in hardware or software has to be based on an evaluation of the metrics of interest for the entire system. This evaluation can either be done in the physical domain by actual implementation, *e.g.*, by synthesizing the hardware to a gate netlist on which accurate metrics for area and performance can be obtained; or it can be done in the model domain, which is less accurate but much faster. Co-design is an iterative process that requires repeated partitioning and evaluation for design space exploration, and thus the speed of this process is a critical issue. In practice, it means that the model domain is the right choice for efficient estimation and evaluation. The hardware-software partitioning problem involves two key metrics: performance and hardware size. Performance is normally improved by moving objects to hardware, while the hardware size is obviously improved by moving objects out of hardware. This tradeoff has led to the development of specialized algorithms for hardware-software partitioning. Depending on the underlying theoretical model, the level of abstraction, and the integration strategy, several performance and size estimation methods are available [5]. Among the possible partitioning schemes derived mostly from related areas, such as VLSI design, the deterministic, statistical, benchmarking and profiling techniques are most popular. Deterministic estimation requires a fully specified model, with all data dependencies removed and all costs of components known. This method leads to very good partitions but fails whenever data items are unavailable. Statistical estimation based on the analysis of similar systems and certain design parameters is then required.

## **1.7** Scope of This Work

This thesis examines the hardware-software co-design framework called POLIS to explore the possibility of performing automatic partitioning. POLIS is a software system which takes as input the system specifications in terms of an executable code written in a high-level language called Esterél [6] and provides the output in terms of C<sup>++</sup> code for software and VHDL code or technology-mapped gate-level netlists for hardware. The partitioning process in POLIS is manual. In this thesis we investigated automatic partitioning algorithms that may be integrated within the POLIS framework and report the results of several case studies.

In the next chapter the related work in the area of co-design, with an emphasis on the partitioning issues are discussed. Various techniques and algorithms have been explored and their strengths and weaknesses are highlighted. Chapter 3 presents an in-depth analysis of the design flow in POLIS and the partitioning methodology based on simulations using the Ptolemy simulation platform. In Chapter 4, partitioning issues and algorithms for automatic partitioning are discussed. Application of automatic partitioning algorithms in POLIS and their implementation in  $C^{++}$  are presented in Chapter 5. The results obtained after the application of selected algorithms to automate the partitioning process in POLIS and their validity are also discussed in this chapter. The last chapter draws some conclusions and sets forth the goals for future work in this direction.

# **CHAPTER 2**

# **RELATED WORK**

Hardware-software co-design with its promise of bringing order to the chaotic world of embedded system design, has attracted a lot of attention in recent years. Several research groups have addressed the problem of co-design and in particular that of hardware-software partitioning. Two research projects can be called the pioneers in the field of hardware-software partitioning: Vulcan [7][8][9] and COSYMA [10][11]. Others have also joined in the effort, and numerous co-design frameworks employing automatic or manual partitioning techniques are now being developed at various universities and research institutions. A brief description of some of these frameworks and environments is presented in this chapter. Where applicable, the partitioning strategies employed in each environment are also identified. Chapter 4 describes the partitioning in detail. Table 2.1 lists the co-design environments examined in this thesis along with their important attributes.

|    | System  | Input       | Partitioning | Algorithm                     |

|----|---------|-------------|--------------|-------------------------------|

| 1. | Vulcan  | HardwareC   | Automatic    | Iterative                     |

| 2. | COSYMA  | $C, C^{x}$  | Automatic    | Simulated Annealing           |

| 3. | LYCOS   | C, VHDL     | Automatic    | PACE(Fine grain partitioning) |

| 4. | COMET   | VHDL        | Automatic    | Scoreboard (Ratio-cut)        |

| 5. | PTOLEMY | C, ptl-code | Manual       | Iterative                     |

| 6. | SpecSyn | SpecChart   | Automatic    | Clustering                    |

| 7. | TOSCA   | C, VHDL     | Automatic    | Clustering                    |

| 8. | POLIS   | Esterél     | Manual       | None                          |

| 9. | Chinook | Verilog     | Manual       | None                          |

Table 2.1: List of co-design frameworks examined in this thesis.

# 2.1 Vulcan

The Vulcan system was developed at Stanford University [7][8]. The target architecture consists of single CPU and one or more ASICs, connected to the CPU via a communication bus. It starts with an all-hardware solution specified in HardwareC. The input to Vulcan consists of two components: system's functionality and design constraints. The specification is translated into an internal graph-based representation on which the partitioning is performed. The partitioning algorithm uses an iterative approach to move operations from hardware to software under a timing constraint. It tries to keep the communication cost minimum by keeping the neighboring vertices together in either software or hardware. The Vulcan system attempts to reduce the size of hardware by moving the functionality to software using a CPU. The system can handle multiple processes as hardware and software can run in parallel.

# 2.2 COSYMA

COSYMA is an acronym for COSYnthesis of eMbedded Architectures. It is a hardware-software codesign system designed at Technical University of Braunsheweig, Sweden [10][11]. COSYMA has a graphical user interface which runs under X-windows environment. The target architecture for COSYMA consists of one CPU and one ASIC, where ASIC is used as a co-processor to speed up the execution.

The input to COSYMA comprises a high level description of the algorithm in  $C^x$  and a constraint file.  $C^x$  is a C dialect with some restrictions and modifications to ANSI C. The objective of COSYMA is to partition the algorithmic description into hardwaresoftware parts such that the user supplied constraints are met while keeping the hardware cost minimum. The system provides the user with information to fine-tune or remove the emerging bottlenecks from the algorithmic description.

Input to COSYMA can be of three types. The input file can be in ANSI C, pure  $C^x$  or a  $C^x$  program with parallel extensions to encode concurrent interacting processes. The user can specify rate constraints, inter/intra-process constraints and communication between processes. The input description is translated to a syntax graph. The run-time analysis of the program is then performed. For the parallel extensions, a scheduler orders the processes for a single processor environment with respect to their timing and communication constraints. COSYMA uses simulated annealing algorithm for automatic partitioning. The algorithm starts with an all-software solution and moves the chunks of software code to hardware until the timing constraints are met. The software part is compiled by a C compiler and the hardware part is handed over to the high level synthesis. Finally a co-simulation is performed using the compiled software part and the timing information of the hardware part supplied by the high level synthesis.

# 2.3 LYCOS: The Lyngby Co-Synthesis System

LYCOS is an experimental co-synthesis environment being developed at Technical University of Denmark [12]. LYCOS targets an architecture consisting of a single CPU and a single dedicated hardware component (ASIC, FPGA etc.) communicating through memory mapped I/O. The areas of application include DSP, embedded systems, software execution acceleration and hardware emulation and prototyping.

LYCOS is built as a suite of tools centered around an implementation independent model of computation based on communicating Control Data Flow Graphs (CDFGs). The

design process starts with an input specification described in either C or VHDL translated to the computational model, Quenya. The CDFGs are divided into chunks of computation called Basic Scheduling Blocks (BSBs) [13], that may be moved between hardware and software. An automatic partitioning algorithm called PACE [14] is used to partition the CDFG by moving BSBs from software to hardware to achieve the best speed-up while keeping the total hardware area less than or equal to the area available on a particular ASIC or FPGA. PACE is based on a fine-grain partitioning [15] approach where adjacent blocks sharing the same variables are moved to hardware so as to reduce communication between hardware and software as well as increase hardware utilization.

# **2.4 COMET**

The main goal of the COMET project [16] at University of Cincinnati is to transform a high-level system specification into application-specific electronic signal processing modules using a hardware-software co-synthesis process and to produce working hardware within a two-week time period. The input to and output from the COMET system are in VHDL. The design framework maintains a database of modules with a variety of functionality.

The system specification is divided into modules, matched to component specifications, and then allocated to either hardware or software synthesis processes. The Co-synthesis process is iterative during which alternate bindings are used to satisfy constraints such as performance and area requirements. The Co-synthesis tool issues requests to the design database using qualifications on design properties, and the query processor determines the set of design objects that match the request. In other words, a

query is a module description, and any modules in the database that have at least the desired functionality (possibly additional functionality) are returned. The co-synthesis tool analyzes candidate solutions and determines the best assignment of resources to hardware and software using an iterative binding approach, called Scoreboard algorithm. The hardware and software specifications are processed by hardware and software synthesis tools, then integrated to form a system that satisfies the initial specifications. The end result of these transformations is an application-specific hardware design that can be fabricated along with the embedded software that will be executed on the manufactured hardware.

# 2.5 **PTOLEMY**

The PTOLEMY [17] [19] software is a system-level design framework developed at University of California, Berkeley. The objectives of the PTOLEMY project include most aspects of designing signal processing and communications systems, ranging from designing and simulating algorithms to synthesizing hardware and software, parallelizing algorithms, and prototyping real-time systems. PTOLEMY allows the interaction of diverse models of computation by using the object-oriented principles of polymorphism and information hiding. For example, using PTOLEMY, a high-level data-flow model of a signal processing system can be connected to a hardware simulator that in turn may be connected to a discrete-event model of a communication network.

PTOLEMY is still in a state of evolution. Recent enhancements of the software have been in the field of data-flow modeling of algorithms, synthesis of embedded software from such data-flow models, animation and visualization, multidimensional signal

processing, managing complexity by means of higher-order functions, hardware-software partitioning, and VHDL code generation.

PTOLEMY has been used for a broad range of applications including signal processing, telecommunications, parallel processing, wireless communications, network design, radio astronomy, real time systems, and hardware-software co-design. The main emphasis in PTOLEMY is on co-simulation of system modules targeted for different implementations. A hardware-software partitioning algorithm [18] has also been implemented in the framework of PTOLEMY. The input to this algorithm is a system level description. The partitioning goal is to minimize hardware area given a global execution time constraint.

# 2.6 SpecSyn

SpecSyn [3] is another Co-design system, which incorporates automatic hardwaresoftware partitioning. It extends the scope of system design from the previously discussed systems in three key ways:

- It includes two additional component types such as memories and buses,

- It allows inclusion of functionality in terms of variables and communication channels that together with behaviors comprise an executable specification, and

- The numbers and types of physical system components can be changed as an integral part of system design.

In SpecSyn the input specification is produced in the visual language SpecChart which is based on Statecharts [21]. This is translated into an intermediate system representation called SLIF [22], on which the system analysis and partitioning is

performed. SpecSyn supports several partitioning algorithms [3] & [23]. [23] Presents a combined approach where clustering is used to reduce the number of code blocks to be considered and a greedy algorithm is used to obtain the partition. The interesting aspect of this approach is that it is able to reach regions in the design space, which lie between the regions obtained by fast greedy algorithms and those obtained by the more costly simulated annealing algorithms.

# 2.7 TOSCA

In TOSCA [20] the internal representation is based on concurrent hierarchical finite state machines (FSM) which are generated from either standard languages such as C or VHDL or from higher-level languages such as SpecChart [2]. Hardware-software partitioning is done automatically by a clustering algorithm, which tries to cluster FSMs based on some closeness criteria. The target architecture for TOSCA is a single standard processor and one or more coprocessors embedded on a single chip.

## 2.8 Other Frameworks

A number of researchers have focused on algorithmic aspects rather than complete systems. Janstch et al. [24], [25] present a dynamic programming algorithm to solve the partitioning problem of optimizing an existing C program for speed, given a hardware area constraint. The algorithm is derived from the Knapsack Stuffing algorithm [26] and solves (with exponential memory requirements) the partitioning problem for a partitioning model in which blocks can include other blocks and blocks in general therefore cannot be moved to/from hardware independently of each other. A full loop

block for example includes the loop body and loop test blocks but all three are considered simultaneously in their model. Another approach using a high level language as input is presented by Barros et al. [4]. The partitioning algorithm is a two-stage clustering algorithm which selects groups of code based on similarity measures obtained from classification of assignments in the input specification, which is described in UNITY [27].

Co-design systems in which hardware-software partitioning is obtained with user interaction were also investigated. Among these are POLIS [1], PARTIF [28] and CASTLE [29]. POLIS is the focus of our research and its features are discussed in detail in Chapter 3. PARTIF is an interactive partitioning tool, which allows the designer to explore different partitions by applying a small set of transformation and decomposition rules. These rules are applied to a system representation consisting of hierarchical concurrent FSMs. The CASTLE system is another co-design framework where the input specs are given in a standard language, which can be Verilog, VHDL or C/C++. This input specification is translated into a common representation based on control data flow graphs called SIR, which provides the backbone for all tools. As for POLIS and PARTIF, the partitioning is done manually, but in CASTLE it is based on mappings from a hardware library which is used to specify complex components including microprocessors.

In the Chinook [30] system the emphasis is on module interface and synchronization. The system is used for real-time reactive controllers initially specified in Verilog. Chinook does not provide automatic hardware-software partitioning, but leaves it to the designer, nor does it provide code generation tools for the target processors, but uses

standard C compilers. However, Chinook does synthesize the hardware and software needed for inter- process communication which is a difficult task as different components may not initially fit very well together.

This chapter has shown that there are two main directions for hardware-software partitioning methods:

- Automatic partitioning, which almost always means a restricted target architecture i.e. one processor and one or more ASICs/FPGAs. The emphasis in automatic partitioning is on transferring the functionality from one domain to the other so as to achieve the best performance at a minimum cost.

- Manual partitioning, which typically allows for more advanced architectures involves detailed analysis of design tradeoffs. The complexity of the system and design constraints demand exploration of a variety of architectural choices to meet the system specifications. Also, with advanced target architectures, synchronization and communication between different components becomes much more difficult and very important.

With this review, we may now proceed to explore the design methodology adopted by POLIS.

# **CHAPTER 3**

# POLIS

# 3.1 Introduction

POLIS is a software system developed at the University of California Berkeley for hardware-software co-design of control-dominated embedded systems [1]. The main aspect of POLIS that distinguishes it from other co-design methods is the use of a formal model of computation. This model, called Co-design Finite State Machine (CFSM) [1], is based on the Extended Finite State Machine (EFSM) [1] model operating on a set of finite-valued (enumerated or integer sub-range) variables by using arithmetic, relational and Boolean operators as well as user-defined functions. EFSM model is similar to the FSM model, but the transition relation may also depend on a set of internal variables. POLIS offers a flexible environment for design analysis and verification.

The design can be analyzed at the behavioral level either with formal tools such as model checking or by co-simulation in a heterogeneous simulation environment offered by PTOLEMY, another tool for co-design. The user can select an architecture for evaluation of design tradeoffs with respect to constraints during the simulation phase. Hardware-software partitioning is based on the results of simulation. Software synthesis is fully automated including generation of a custom scheduler and hardware synthesis also involves limited user interaction. POLIS has a path towards an emulation board including Xilinx FPGAs [1], the microprocessor of choice, and A/D and D/A interfaces.

## **3.1.1 Model of Computation (CFSM)**

A Co-design Finite State Machine (CFSM), as does a classical finite state machine, transforms a set of inputs into a set of outputs with only a finite number of internal states. The difference between the two models is that the synchronous communication model of classical concurrent FSMs is replaced in the CFSM model by a finite, non-zero, unbounded reaction time. This model of computation can also be described as Globally Asynchronous, Locally Synchronous. Each element of a network of CFSMs describes a component of the system to be modeled.

The CFSM specification is a priori unbiased towards a hardware or software implementation. While both perform the same computation for each CFSM transition, hardware and software exhibit different delay characteristics. A synchronous hardware implementation of CFSM can execute a transition in one clock cycle, while a software implementation will require more than one clock cycle. CFSM is also a synthesizable and verifiable model, because many existing theories and tools for the FSM model can be easily adapted for CFSM. Each transition of a CFSM is an atomic operation. All the analysis and synthesis steps ensure that:

- A consistent snapshot of the system-state is taken just before the transition is executed.

- The transition is executed, thus updating the internal state and output of the CFSM.

- The result of the transition is propagated to the other CFSMs and to the environment.

The interaction between CFSMs is asynchronous, in order to support neutral specification of hardware and software components by means of a single CFSM network. This means that:

- The execution time for a CFSM transition is unknown but assumed to be non-zero in order to avoid the problem of zero-delay feedback loops. The synthesis procedure refines this initial specification, by adding more precise timing information, as more design choices are made (*e.g.* partitioning, processor selection, compilation, *etc.*). The designer, during the analysis steps, may on the other hand add constraints on this timing information that synthesis process should satisfy. The overall design philosophy of POLIS is to provide the designer with such tools that help in meeting these constraints, rather than provide a quickfix solution.

- Communication between CFSMs is not by means of shared variables (as in the classical composition of finite state machines), but by means of events. An event is a semi-synchronizing communication primitive that is both powerful enough to represent practical design specifications and efficiently implementable in hardware, software, and between the two domains.

CFSM's behavior and the CFSM network topology are represented using an intermediate language called SHIFT, for Software Hardware Interchange FormaT. SHIFT is however, not meant to be used as a specification language. The FSM semantics of each CFSM ensures that any of the following graphical or textual languages can be used to specify individual behaviors:

• Reactive synchronous languages, such as StateCharts, Esterél, Lustre and Signal;

- The so-called synthesizable subset of hardware description languages such as VHDL and Verilog; and

- System specification languages with FSM semantics such as SDL [2].

The interconnection between the CFSMs, on the other hand, can be specified (due to the distinctive asynchronous interconnection semantics) within the POLIS environment, using either a textual netlist auxiliary language or a graphical editor VEM [17] that is part of the PTOLEMY co-simulation environment.

Events are emitted by CFSMs and/or by the environment over a set of carriers called signals. One or more CFSMs can detect the emission of each event (the actual delay depends on several implementation-related factors, such as partitioning, scheduling policy and so on). Each detecting CFSM has its own copy of the event, and each emission can be detected at most once by each receiving CFSM.

Signals can carry control information, data information, or both. Events occurring on pure control signals, such as reset input, can be used only to trigger a transition of a CFSM. Once the receiver CFSM has detected an event, it can no longer be detected again until its sender CFSM re-emits it. Values carried by data signals, such as keyboard input or a data sample, can be used as inputs to and output from the CFSM data path. Signals carrying only control information are often called pure signals, while signals carrying only data information are often called pure values. Each CFSM transition has a precondition of a set of:

- Input event presence or absence conditions (only for signals with a control part)

- Boolean functions of some relational operations over the values of its input signals.

The post-condition is the conjunction of a set of:

- Output event presence or absence conditions (presence implies emission, absence implies no action), and

- Values assigned to output data signals.

Note that no buffering is provided by the POLIS communication mechanism, apart from the event and value information. This means that events can be overwritten, if the sending end is faster than the receiving end. This overwriting, also called "losing" may or may not be a problem depending both on the application and the type of the event. The designer can make sure that "critical" events are never lost either by:

- Providing an explicit handshaking mechanism, built by using a set of signals, between the CFSMs, or

- Using synthesis directives, such as partitioning choices or scheduling techniques, that ensure that no such loss can ever occur. For example, this can be achieved by:

- a) implementing the receiving CFSM in hardware

- b) implementing both CFSMs in software and using a round-robin scheduler that executes both at the same rate.

# 3.2 Design Flow

#### 3.2.1 Overview

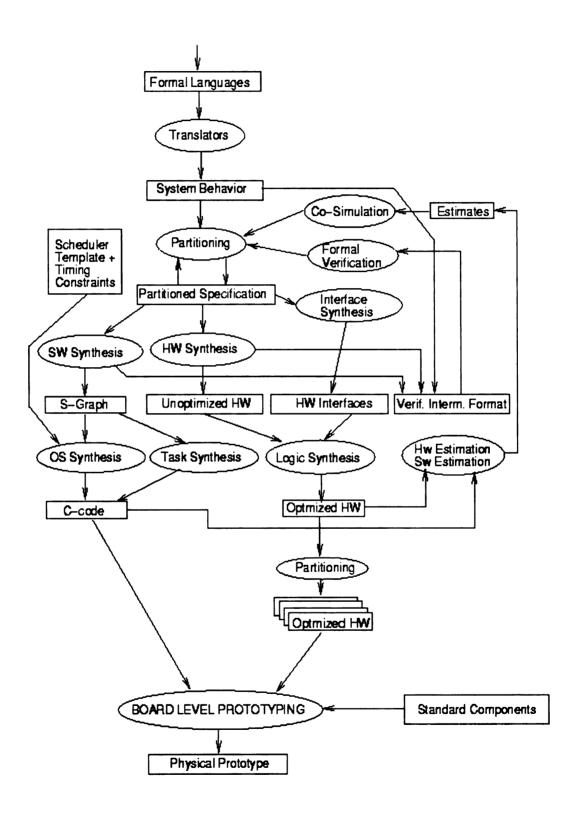

An overview of the design flow in the POLIS system is depicted in Figure 3.1. The detailed composition of POLIS is shown in Figure 3.2. The input specifications are described in Esterél language. The Esterél code is first translated to SHIFT code. This format is used by POLIS to generate S-Graphs similar to Control Data Flow Graph

(CDFG) for software synthesis and BLIF (Berkeley Logic Interchange Format) code for hardware synthesis. In the architecture selection step, a processor is chosen. POLIS supports Motorola 68HC11 and 68832, and MIPS R3000 processors. POLIS has powerful software and hardware cost estimation capabilities, which can guide the user in selection of the best architecture.

Figure 3.1: Overview of the design flow in POLIS [courtesy POLIS group].

Figure 3.2: The POLIS design flow [courtesy POLIS group].

The S-Graph is further translated to C code and PTOLEMY code for use by PTOLEMY for simulation. The cost estimates are also passed to PTOLEMY for use in simulation. The user can interactively define the system architecture within PTOLEMY as well by changing the implementation of each CFSM to software or hardware. The software and hardware models are executed in the same simulation environment, and the simulation code is the same that will run on the target processor. The simulation can be done at two levels of abstraction: functional and timing. In functional simulation, timing is ignored and only the functional correctness is checked. In timing-based simulation, the timing is approximated using cycle count estimations for software and using a cyclebased simulation for hardware.

After starting the simulation, input events are generated and then the overflow file is checked for any missed deadlines. The processor clock speed can be adjusted to simulate different versions of a processor. If the highest speed processor is also unable to meet the deadlines, then the critical CFSM is transferred to hardware by changing its implementation. Depending upon the results of co-simulation, the final partitioning is decided. A complete SHIFT netlist describing the CFSM-network topology and implementation choice for each CFSM is then created. This SHIFT file is passed back to POLIS for synthesis of hardware (BLIF) and software (C code). The final software also contains a RTOS for the target processor, and the hardware contains the interface circuitry required for communication between hardware and software. There is a path available in POLIS for rapid prototyping of final design for functional validation or insystem testing. Results of this step may then be fed back for the improvement in design.

#### 3.2.2 High Level Language Translation

In POLIS, designers write their specifications in a high level language (e.g., Esterél, graphical FSMs, subsets of Verilog or VHDL) that can be directly translated into CFSMs. Any high level language with precise semantics based on extended FSMs can be used to model individual CFSMs. Currently, however, Esterél is supported directly. The Esterél programs are translated to SHIFT format using the command *strl2shift*. The Esterél compiler first compiles Esterél code and then another tool *oct2shift* translates the output to SHIFT.

## **3.2.3 Formal Verification**

The formal specification and synthesis methodology embedded within POLIS makes it possible to interface directly with existing formal verification algorithms that are based on FSMs. POLIS includes a translator from the CFSM to the FSM formalism which can be fed directly to verification systems (*e.g.* VIS [31]). In addition to uncovering bugs in a design, it also uses formal verification to guide the synthesis process. Since the abstract CFSM model covers the behavior of all possible hardware-software implementations at once, it is possible to refine the specification based on the results of formal verification. Formal verification tools of today still have problems with complexity. A methodology has been developed that incorporates a set of rules specific to POLIS and CFSMs so that it is now possible to verify larger designs.

## 3.2.3 System Co-simulation

System level hardware-software co-simulation provides feedback on the design choices. These design choices include hardware-software partitioning, CPU selection, and scheduler selection. Fast co-simulation, in the order of millions of clock cycles per second (on a workstation) is possible due to the software synthesis and performance estimation techniques available. The purpose of high-level co-simulation in POLIS is to provide the designer with a flexible environment where architectural tradeoffs can be explored. POLIS currently utilizes PTOLEMY as a simulation engine, but it is not limited to PTOLEMY. VHDL code including all the co-simulation information such as code size and delays *etc.* can also be generated by POLIS.

## 3.2.4 Partitioning and Architecture Selection

Making system-level design decisions such as hardware-software partitioning, target architecture selection and scheduler selection is not a trivial task. These decisions are based heavily on design experience and are very difficult to automate. In POLIS the designer is provided with an environment to quickly evaluate any such decisions through various feedback mechanisms from either formal verification or system co-simulation. This feedback is however limited to the results of simulation in terms of signal arrival times and missed deadlines. The key advantage of CFSM specification is that it is implementation-independent. The designer can interactively explore the implementation options using the same user interface as co-simulation.

#### 3.2.5 Hardware Synthesis

A CFSM sub-network chosen for hardware implementation is implemented and optimized using logic synthesis techniques from SIS [32]. Each CFSM, interpreted as a Register-Transfer Level (RTL) specification, can be mapped into BLIF, XNF (XILINX Netlist Format), VHDL or Verilog.

#### 3.2.6 Software Synthesis

A CFSM sub-network chosen for software implementation is mapped into a software structure that includes a procedure for each CFSM, together with a simple real-time operating system (RTOS).

The reactive behavior of CFSM is synthesized in a two-step process:

- Implement and optimize the desired behavior in a high-level, processorindependent representation similar to a CDFG,

- Translate the CDFG into portable C code and use any available compiler to implement and optimize it in a specific microcontroller dependent instruction set.

A timing estimator quickly analyzes the program and reports code size and speed characteristics. The algorithm uses a formula, with parameters obtained from benchmark programs, to compute the delay of each node in the CDFG for various microcontroller architectures (characterization data for MIPS R3000 and Motorola 68HC11 and 68332 are already available). The precision of the estimator, with respect to true cycle counting, is currently on the order of  $\pm$  20 %. An application-specific operating system, consisting

of a scheduler (*e.g.* Rate-Monotonic and Deadline-Monotonic) and I/O drivers, is generated for each partitioned design.

## **3.2.7 Interfacing Implementation Domains**

Interfaces between different implementation domains (hardware-software) are automatically synthesized within POLIS. These interfaces come in the form of cooperating circuits and software procedures (I/O drivers) embedded in the synthesized implementation. Communication can be through I/O ports available on the microcontroller, or general memory-mapped I/O.

# 3.2.8 Rapid Prototyping

A rapid prototyping environment is also available in POLIS based on APTIX architecture [1] [33] system.

### **3.3 Design Example**

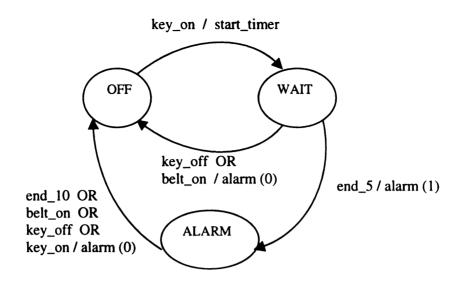

In order to elaborate the various design steps in POLIS, it is convenient to work through an example. A seat-belt alarm example given in POLIS user's manual [33] is highlighted in this work to explain the design methodology. Figure 3.3 shows the transition diagram for the system. The specification of the system is stated as follows:

When the ignition key is turned on, wait for five seconds for the belt to be fastened. If the belt is not fastened within five seconds, turn the alarm on for five seconds. If the belt is fastened or the ignition is turned off, then don't turn the alarm on.

Figure 3.3: Transition diagram of seat belt controller [courtesy POLIS group].

# 3.3.1 Specification

The initial specification of the system is written in Esterél language. The system is divided into two modules; belt\_control and timer, and functionality of each module is then described in terms of an Esterél program. The belt\_control program is shown below:

```

module belt_control:

input reset, key_on, key_off, belt_on, end_5, end_10;

output alarm: boolean, start_timer;

100p

abort

emit alarm(false);

every key_on do

abort

emit start_timer;

await end_5;

emit alarm(true);

await end_10;

when [key_off or belt_on];

emit alarm(false);

end

when reset

end

```

The first line of each Esterél program gives a name to the module being described. The next two lines declare the input and output signals of the module. All input signals here are control signals meaning they do not have any values associated. One of the output signals *alarm* has a value of type Boolean. The **loop** statement starts an infinite loop. The **abort** statement instantaneously kills its body whenever *reset* signal is received. The **emit** *alarm* (false ) signal has an associated Boolean value to turn the alarm off. The **every**  $key_on$  **do** statement executes its body every time  $key_on$  is present. The **abort** statement instantaneously kills its body whenever  $key_off$  or *belt\_on* signals are present. The **abort** statement instantaneously kills is an output to be sent to timer module. The **await** *end\_5* halts the execution until *end\_5* signal is received. The **emit** *alarm* (true) signal is an output signal with a value (true) to turn the alarm on. The **await** *end\_10* again halts the execution until *end\_10* signal is received, which means that five seconds have elapsed since the alarm was turned on. The **emit** *alarm* (false) signal then turns the alarm off and the system goes back to its initial or OFF state.

Following is a listing of timer module:

```

module timer:

constant count_5, count_10 : integer;

input msec, start_timer;

output end_5, end_10;

every start_timer do

await count_5 msec;

emit end_5;

await count_10 msec;

emit end_10;

end

```

The second line declares a **constant**, whose actual value will be defined later in the design. The timer starts counting whenever it receives the *start\_timer* signal. The **await**