2 (1999)

LIBRARY

Michigan State

University

This is to certify that the

dissertation entitled

## DESIGN OF HIGH PERFORMANCE AND LOW POWER CMOS SWITCHED-CURRENT DATA CONVERTERS

presented by

Jin-Sheng Wang

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Electrical Eng

Date Oct 19, 98

MSU is an Affirmative Action/Equal Opportunity Institution

0-12771

PLACE IN RETURN BOX to remove this checkout from your record.

TO AVOID FINES return on or before date due.

MAY BE RECALLED with earlier due date if requested.

| DATE DUE | DATE DUE | DATE DUE |

|----------|----------|----------|

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

1/98 c:/CIRC/DateDue.p65-p.14

# DESIGN OF HIGH PERFORMANCE AND LOW POWER CMOS SWITCHED-CURRENT DATA CONVERTERS

By

Jin-Sheng Wang

#### **A DISSERTATION**

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

**DOCTOR OF PHILOSOPHY**

Department of Electrical Engineering

1998

#### **ABSTRACT**

## DESIGN OF HIGH PERFORMANCE AND LOW POWER CMOS SWITCHED-CURRENT DATA CONVERTERS

#### By

#### Jin-Sheng Wang

The advent of portable communication and computing service has stirred a great deal of interests in both commercial and research areas. The circuit technology used in portable equipment has been changed from the conventional analog circuit technology to mixed-signal circuit technology. Low power and high performance are strongly needed for both analog and digital circuits to increase operation time of the portable equipment. The design of low power and high performance mixed-signal CMOS IC's is hindered by processing techniques that are optimized for digital applications. Moreover, scaling/reliability consideration are driving CMOS process towards submicrometer feature size and lower power supply voltages.

Switched-current (SI) technique has received considerable attention as an alternative for analog data acquisition and conversion circuit design. However, existing SI circuits cannot make the theoretically expected performance due in part to the use of non-optimal current copiers, its basic building blocks. Based on our development of design methodologies and synthesis process for optimally generating low power and high performance CMOS current copiers, SI technique becomes feasible.

This thesis develops high performance and low power CMOS SI data converters,

ADCs (analog-to-digital converters) and DACs (digital-to-analog) converters. A 12-bit

CMOS cyclic ADC circuit which consumes 1.9mW in power and takes 2.13 mm<sup>2</sup> in chip area, has designed and fabricated. A 11-bit CMOS DAC circuit which consumes 4.4mW in power and achieves 100 MSamples per second in conversion rate, has been designed and simulated, where 3.3 V power supply voltage and MOSIS SCN20 2 µm CMOS process with 2-level transistor parameters are employed. This thesis also presents the design methodologies and performance analysis process. The developed design methodologies guide the designers to properly select the transistor sizes and capacitances based on a given set of design specifications including input dynamic range, full-scale current, SNR, power consumption, etc., and the performance analysis process estimates the calibration time, holding time, and accuracy of the data converter circuits.

This study also develops a built-in tester to enhance the testability of SI circuits,

The tester possesses the features of autozeroing and self-testability. The autozeroing property increases the accuracy, while the self-testability ensures the correctness of the tester before it is used to test SI circuits.

With the successful development in this thesis study, we believe that SI technique will soon become an alternative industrial standard for designing analog components in mixed-signal circuits for low-voltage/low-power signal processing applications.

To my parents, wife, daughter and brothers

#### **ACKNOWLEDGEMENTS**

I sincerely thank Professor Chin-Long Wey, my thesis advisor, for his support and valuable suggestions throughout this research. It has been a pleasure to work under his supervision and I have certainly learn a lot from him. I would also like to express my gratitude to the members of my guidance committee, Dr. James A. Resh, Dr, Gregory M. Wierzba and Dr. Chester Tsai, for taking time to serve in the committe. This research is sponsored in part by National Science Foundation under grant number MIP-9321255.

I have to thank my fellow graduate students, Dr. Chen-Ping Wang and Wei-hsing Huang. I got much inspiration from the discussion with them.

A special thanks goes to my parents, Fu-tseng Wang and A-chin Lin, my wife, Huie-fang Tsao, and my brothers, Jin-hsiang and Jin-tao, for their long-term support and encouragement they have given me during the critical stage of my life.

I also need to thanks Brain Dazsi, Mohammad Athar Khalil, Malinda Funk and Jim Ganong for reading and editing this work.

A final note of appreciation must be sent to all the nice people who have ever enriched my campus life while I stayed in Michigan State University.

### **TABLE OF CONTENTS**

| LIST OF TABLES                                | хi |

|-----------------------------------------------|----|

| LIST OF FIGURES                               | x  |

| 1. INTRODUCTION                               | 1  |

| 1.1 Switched-Current (SI) Circuits            | 2  |

| 1.2 Objectives and Research Tasks             | 3  |

| 1.3 Thesis Organization                       | 5  |

| 2. CMOS SI CIRCUITS                           | 7  |

| 2.1 Current Copiers                           | 7  |

| 2.2 Multiplier and Divider Circuits           | 9  |

| 2.3 Data Converter Circuits                   | 12 |

| 2.3.1 Conversion Algorithms                   | 14 |

| 2.3.2 Design Specification of Data Converters | 16 |

| 2.3.3 CMOS SI ADC Circuits                    | 17 |

| 2.3.3.14-cycle Conversion                     | 21 |

| 2.3.3.22-cycle Conversion                     | 22 |

| 2.3.4 CMOS SI DAC Circuits                    | 23 |

| 2.4 Test Generation                           | 26 |

| 2.4.1 Fault Models                            | 26 |

|    | 2.4.2 Test Generation of Current Copie               | 28 |

|----|------------------------------------------------------|----|

|    | 2.4.3 Test Generation of ADC Circuits                | 30 |

|    | 2.5 Discussion                                       | 32 |

| 3. | CMOS SI ADC CIRCUIT DESIGN                           | 36 |

|    | 3.1 Design and Consideration                         | 36 |

|    | 3.1.1 2-Cycle Residual Amplifier                     | 37 |

|    | 3.1.2 2-Cycle Conversion with Modified RSD Algorithm | 37 |

|    | 3.2 Design Consideration                             | 44 |

|    | 3.3 Simulation Results and Measurements              | 46 |

|    | 3.4 Conclusion                                       | 53 |

| 4. | CMOS SI DAC CIRCUIT DESIGN                           | 56 |

|    | 4.1 Current-Mode DAC Circuits                        | 56 |

|    | 4.1.1 CRG_DC Circuits                                | 57 |

|    | 4.1.1.1 Divide-by-Two (DB2) Circuit                  | 59 |

|    | 4.1.1.2 m-bit CRG_DC Circuit                         | 63 |

|    | 4.1.2 CRG_MC Circuits                                | 64 |

|    | 4.1.3 Design Methodology                             | 66 |

|    | 4.1.4 Performance Analysis                           | 69 |

|    | 4.2 Design Examples                                  | 72 |

|    | 4.2.1 A 6-bit CRG_DC Circuits               | 72  |

|----|---------------------------------------------|-----|

|    | 4.2.2 A 7-bit CRG_MC Circuits               | 78  |

|    | 4.2.3 Simulation Results                    | 78  |

|    | 4.3 DAC Circuit Design                      | 78  |

|    | 4.3.1 Low Power SI DAC Circuit              | 82  |

|    | 4.3.2 Design Examples an 11-bit DAC Circuit | 82  |

|    | 4.3.3 Alternative Designs                   | 83  |

|    | 4.4 Conclusion                              | 87  |

| 5. | BUILT-IN TESTERS FOR SI CIRCUITS            | 89  |

|    | 5.1 Built-in Testers                        | 89  |

|    | 5.2 CMOS Current Comparator                 | 97  |

|    | 5.2.1 Autozeroing                           | 97  |

|    | 5.2.2 Self-Testability                      | 99  |

|    | 5.3 Conclusion                              | 105 |

| 6. | CONCLUSION                                  | 107 |

|    | 6.1 Summary and Contribution                | 108 |

|    | 6.2 France World                            | 110 |

## LIST OF TABLES

| 2.1 | Relationship among k, r, and accuracy                | 13 |

|-----|------------------------------------------------------|----|

| 2.2 | Summary of defects and circuit fault                 | 27 |

| 2.3 | Fault types                                          | 30 |

| 3.1 | The summarized performance od ADC                    | 55 |

| 4.1 | Parameter values for CRG_DC in Figure 4.5(a)         | 75 |

| 4.2 | Performance analysis for various bit sizes of CRG_DC | 75 |

| 4.3 | Parameter values for CRG_DC in Figure 4.5(b)         | 77 |

| 4.4 | Performance analysis for various bit sizes of CRG_DC | 77 |

| 4.5 | Parameter values for CRG_MC in Figure 4.3(c)         | 79 |

## **LIST OF FIGURES**

| 1.1 | Schematic diagram of a typical DSP-based mixed-signal IC           | 2  |

|-----|--------------------------------------------------------------------|----|

| 2.1 | Various current copier structures                                  | 8  |

| 2.2 | SI circuits                                                        | 11 |

| 2.3 | Cyclic conversion algorithms                                       | 19 |

| 2.4 | Cyclic ADC circuits                                                | 20 |

| 2.5 | Current-Mode DAC circuits                                          | 24 |

| 2.6 | Fault behavior and switching sequence                              | 31 |

| 2.7 | Simplified schematic diagram of SI algorithmic ADC with additional |    |

|     | comparator                                                         | 31 |

| 2.8 | Test sequence A                                                    | 33 |

| 2.9 | Test sequence B                                                    | 34 |

| 3.1 | Proposed 2-cycle residual amplifier                                | 38 |

| 3.2 | Proposed switched-current CMOS cyclic ADC                          | 39 |

| 3.3 | Bit conversion                                                     | 41 |

| 3.4 | Modified RSD conversion algorithm                                  | 42 |

| 3.5 | Simulation results                                                 | 48 |

| 3.6 | Implementation                                                     | 49 |

| 3.7 | Schematic circuit of voltage-to-current converter         | 51  |

|-----|-----------------------------------------------------------|-----|

| 3.8 | Analysis of nonlinearity                                  | 52  |

| 3.9 | FFT analysis of designed ADC                              | 54  |

| 4.1 | CRG_DC circuit                                            | 58  |

| 4.2 | DB2 circuits analysis                                     | 61  |

| 4.3 | CRG_MC                                                    | 65  |

| 4.4 | Small signal analysis of negative feedback current copier | 70  |

| 4.5 | 6-bit CRG_DC circuit                                      | 73  |

| 4.6 | Simulation results                                        | 80  |

| 4.7 | Proposed DAC circuit structure                            | 81  |

| 4.8 | Nonlinearity analysis of M7D4 DAC                         | 84  |

| 4.9 | Nonlinearity analysis of M5D6 DAC                         | 86  |

| 5.1 | Tester                                                    | 90  |

| 5.2 | SI Tester                                                 | 92  |

| 5.3 | Schematic and configuration of built-in tester            | 93  |

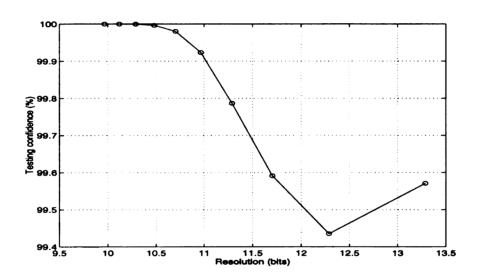

| 5.4 | Test confidence vs. resolution                            | 96  |

| 5.5 | Autozero current comparator                               | 98  |

| 5.6 | Analysis of current comparator                            | 100 |

| 5.7 | The configuration of circuit under testing                | 101 |

| 5.8 | Operation phase of built-in tester | 102 |

|-----|------------------------------------|-----|

| 5.9 | Fault simulation results           | 104 |

### Chapter 1

#### INTRODUCTION

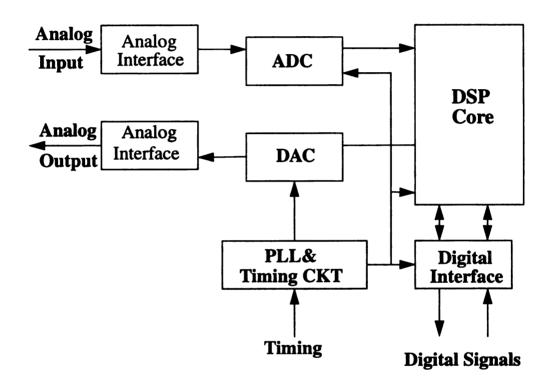

High speed and low power data converters, analog-to-digital converters (ADCs) and digital-to-analog converters (DACs), have been highly demanded in portable systems, such as personal communication systems, astronomy research equipments, and multimedia. The analog circuit technology conventionally employed for such applications has been gradually switched to analog/digital mixed-signal circuits technology [1]. Integrating both digital and analog on a single chip has improved performance and reduced board size and cost. Figure 1.1 shows the schematic diagram of a typical DSP (digital signal processing)-based mixed-signal IC. The current trend shows that data converters' interfaces are incorporated as a cell in a complex mixed-signal IC containing mostly digital blocks for DSP and control. Even though very complicated DSP circuits have been widely used, analog circuits will remain for processing or interfacing analog signals to/from I/O devices.

The silicon area in a typical mixed-signal integrated circuit (IC) contains 10% analog circuits and 90% digital circuits. The overall system cost can be reduced significantly if both analog and digital portions can use the same supply-voltage and the analog portions can be fabricated using the low cost digital CMOS process. If both analog and digital portions use the same supply-voltage, then the system does not need dc-dc converters to generate multiple supply voltages.

Figure 1.1 Schematic diagram of a typical DSP-based mixed-signal IC.

Since most of analog components in a mixed-signal ICs are used for processing and interfacing analog signals, their accessibility becomes drastically reduced [2,3]. Recently, manufacturers have found the costs associated with high-volume production of mixed-signal ICs are strongly affected by the cost of testing. Testing effort is just the opposite of the silicon areas in mixed analog and digital circuits; i.e., 90% for analog testing and 10% for digital testing. Therefore, enhancing testability can reduce test cost and thus further decrease system cost.

#### 1.1 Switched-Current Circuits

Traditionally, the analog interface portion of a mixed-signal circuit employs the switched-capacitor (SC) technique which requires high quality linear capacitors [4]. The high quality linear capacitors are usually implemented using two layers of polysilicon. However, the second layer of polysilicon used by SCs is not needed by purely digital circuits and may become unavailable as process dimensions shrink to the deep submicron range. On the other hand, to be compatible with low-voltage systems, analog circuits must be operated at a supply voltage of 2 V or below. However, with lower supply voltages the realization of high-speed, high-gain operation amplifiers in the SC technique becomes more difficult [5,6].

Recently, a class of analog circuits wherein current, rather than voltage, is the primary signal medium has received considerable attention. The use of current-mode creates a potential for speed improvement because stray-inductance effects in such low-impedance switched-current (SI) circuits are much less severe than those in high-impedance SC circuits [5-18]. High accuracy can be obtained by using dynamic calibration to alleviate

the error due to element mismatch. The SI technique couples itself well with the down-scaled CMOS technology, where the transistors with a high cut-off frequency are available, leading to a higher calibration. In addition, highly linear capacitance is not needed for high accuracy analog signal processing. Alternatively, accuracy has been traded with speed in  $\Sigma$ - $\Delta$  modulations using oversampling techniques to achieve performance several orders of magnitude higher than traditionally associated with analog limitations [9]. The challenge and the gains are clear for the designer who can manage the extra demands on analog performance with diminishing resource of digitally-motivated VLSI process development [18].

Even though the SI technique possesses the salient features mentioned above, one frequently asked question is: why hasn't the SI technique become an industrial standard yet? A simple answer is that the accuracy, linearity, and noise problems are still not resolved completely and satisfactorily [18]. It is necessary to develop sound design methodology and synthesis processes for generating high performance analog circuits [18]. Since current copier is the basic building block of SI circuits, the performance of a SI circuit is determined by the performance of the current copiers it employs. Therefore, developing a sound design methodology and synthesis process for generating high performance current copiers becomes a very important task.

#### 1.2 Objectives and Research Tasks

Based on the recently developed current copiers [5-7,14], our research goal is to develop high performance CMOS SI circuits for low-power/low-voltage signal applica-

tions and the objective of this thesis study is to develop high performance and low power CMOS SI data converters.

In the past years, a number of high-speed ADC and DAC circuits have been designed for portable systems [19-46]. For such applications, a sample rate above 5 MS/s (Mega Samples per second) and 8-12 bit resolutions is required. Most of such converter designs use the switched-capacitor (SC) technique. The power consumption is typically ranged from 100 mW to 500 mW. Apparently, for battery-powered portable applications, this level of power consumption is not suitable. Therefore, power reduction is essential for power-optimized ADC and DAC circuits.

To accomplish our research objective, the research tasks include the development of design methodologies and performance analysis processes for the optimized data converters. The design methodologies provide the designers to select appropriate structures and parameter values to meet the design specifications such as accuracy, speed, power consumption, signal-to-noise ratio (SNR), supply voltage, and etc., while the performance analysis processes allow the designers to evaluate the performance of the designed circuits. In this study, the developed data converter circuits will be designed and fabricated using the low-cost digital CMOS process and the same low supply voltage for both digital and analog parts. In addition, the developed data converters must be easily testable.

#### 1.3 Thesis Organization

The thesis is organized as follows: Chapter 2 reviews the background which relates to this research. The basic current copier is introduced first. Several different structures and circuit cells are also presented to endorse the feasibility of SI technique. Two current-

mode ADC circuits in [8,16] and a current-mode DAC in [47] are discussed. Finally, the test generation and fault coverage of SI CMOS ADC developed in [48-52] are briefly described.

Chapter 3 describes the design and operation of the developed high performance and low power cyclic ADC circuit using modified redundant-signed-digit (RSD) algorithm. A 12-bit CMOS SI circuit has been designed, simulated, and fabricated. Both simulation results and measurements will be discussed.

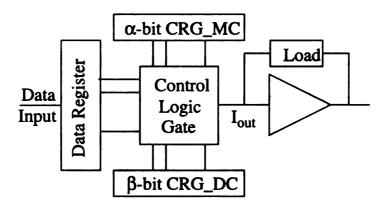

Chapter 4 presents the design and operation of the developed DAC circuits. The weighted current references are generated using current reference generator (CRG) circuits. Two types of CRG circuits are introduced with their simulation results. The design methodology and performance analysis of DAC circuits for low power applications are also presented.

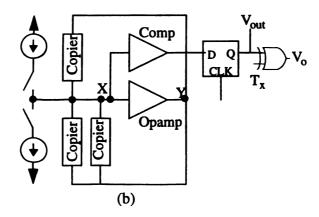

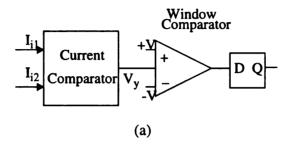

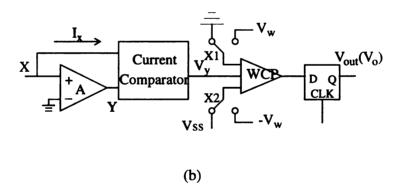

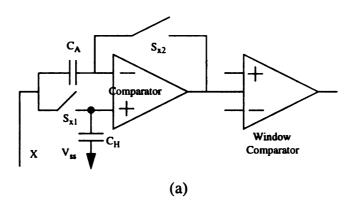

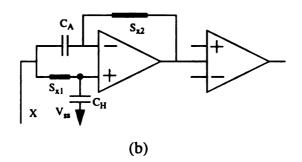

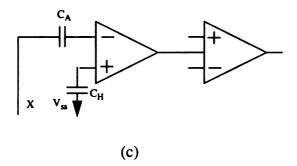

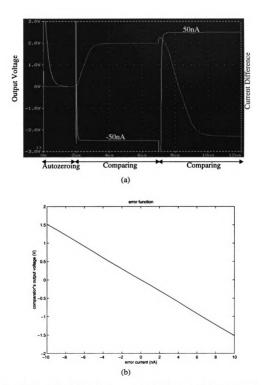

Chapter 5 introduces a built-in tester to enhance the testability of SI circuits. The tester is comprised of a current comparator, a voltage window comparator, and a digital latch. The current comparator is required to have high-accuracy, low-power consumption, simple structure with small chip area, and moderate speed. A comparator adopting an autozeroing technique is developed to achieve high accuracy, and it possesses the self-testing capability for detecting both catastrophic and parametric faults of all its components.

Finally, Chapter 6 summarizes the thesis study and gives concluding remarks and future research directions.

#### Chapter 2

#### **BACKGROUND**

This chapter reviews the background knowledges related to the thesis research. Current copier is the basic building block of SI circuits. Section 2.1 reviews the existing current copiers. Section 2.2 introduces the current-mode multiplier and divider circuits. Section 2.3 presents the design and operation of data converter circuits. Finally, test generation of both current copiers and ADCs are discussed in Section 2.4.

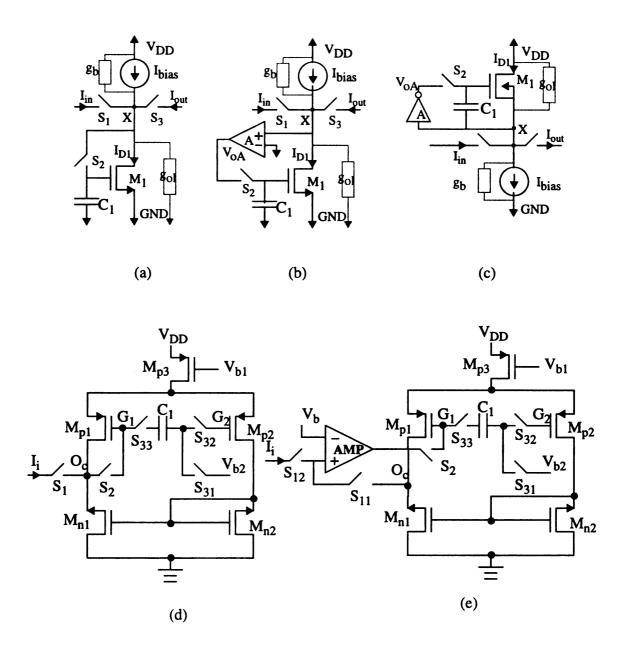

#### 2.1 CMOS Current Copiers

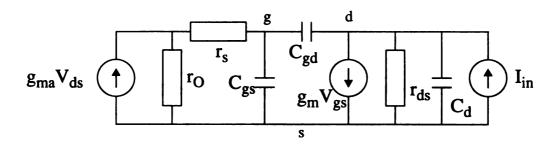

A simple current copier, as shown in Figure 2.1(a) [7], is comprised of two switches  $S_1$  and  $S_2$ , a current-storage transistor  $M_1$ , and a holding capacitor  $C_1$ . To copy the current  $I_{in}$ ,  $S_1$  and  $S_2$  are turned on, therefore feeding  $I_{in}$  to  $M_1$  and  $C_1$ . The capacitor charges up to whatever gate voltage is needed by  $M_1$  to support a current equal to  $I_{in}$ . When  $S_1$  and  $S_2$  are off, the copier cell is disconnected from the current source. Thereafter, the copier cell is capable of sinking a current  $I_{in}$  when connected to a load. No well-matched components are needed in the current copier. However, the copier is suffered from two major error effects due to (1) the nonzero conductance of  $M_1$  and (2) charge-feedthrough of  $S_2$  [7]. The non-zero output conductance results from the channel length-modulation effect and the drain-gate capacitive coupling of  $M_1$ . The charge-feedthrough

Figure 2.1 Various current copier structures: (a) simple copier; (b) negative feedback (inverter) structure; (c) negative feedback (follower) structure; (d) differential-pair; and (e) differential-pair with feedback amplifier.

error is caused as follows: when the gate voltage of  $S_2$  goes down during the turn-off transient, the charge held in the transistor realized by  $S_2$  will be forced to leave. Since one end of  $S_2$  is connected to the gate node of  $M_1$ , some charges of  $S_2$  will be dumped to the gate of  $M_1$ , which changes the voltage across  $C_1$ . As a result, the current held in  $M_1$  will deviate from  $I_{in}$ , and the charge-feedthrough error results.

The effect of error due to nonzero conductance of  $M_1$  can be alleviated by using cascode structures [6,9] and negative feedback structures [7,14,18]. The current-storage transistor  $M_1$  together with the input current source constitutes a voltage inverter in Figure 2.1(b) [7], but forms a source follower in Figure 2.1(c) [14,18]. In order to keep the feedback negative, the former implements an amplifier with a positive gain, while the latter employs a negative-gain amplifier. On the other hand, the charge-feedthrough error effect can be reduced by either increasing the capacitance  $C_1$ , or using appropriate switches. Recently, a fully differential-pair current copier, as shown in Figure 2.1(d) [17], was developed in which the distortion is reduced by cancelling even-order harmonics and crosstalk from neighboring digital circuits. The current copier in Figure 2.1(e) [17] can reduce both error effects mentioned above.

#### 2.2 Multiplier and Divider Circuits

Current multipliers and dividers are usually implemented by using resistor networks or weighted transistors. However, the accuracy of such solutions is limited by resistor or transistor mismatch. To obtain accurate signal multiplication/division without the need for well-matched components, switched-current multiply-by-two (MX2) circuits [8] and divide-by-two (DB2) circuits [53,54] are introduced.

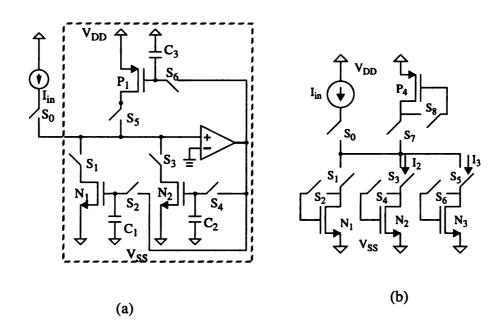

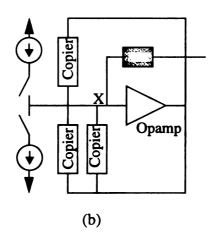

Figure 2.2(a) illustrates a 3-cycle MX2 circuit [8] which generates an output current equal to  $2I_{in}$  without the need of well-matched devices. Initially, Switches  $S_0$ ,  $S_1$ , and  $S_2$ are turned on. After the op-amp is settled, I<sub>1</sub> will equal I<sub>in</sub>. When S<sub>2</sub> is turned off, the gate capacitance will cause transistor  $N_1$  to "memorize" the input current level. This procedure is then repeated for transistor N<sub>2</sub> by turning on S<sub>0</sub>, S<sub>3</sub>, and S<sub>4</sub>. Once N<sub>2</sub> has been set, an output current of 2I<sub>in</sub> is produced by turning on S<sub>1</sub>, S<sub>3</sub>, S<sub>5</sub> and S<sub>6</sub>, which will cause I<sub>out</sub> to be equal to  $I_1+I_2$  (or  $2I_{in}$ ).

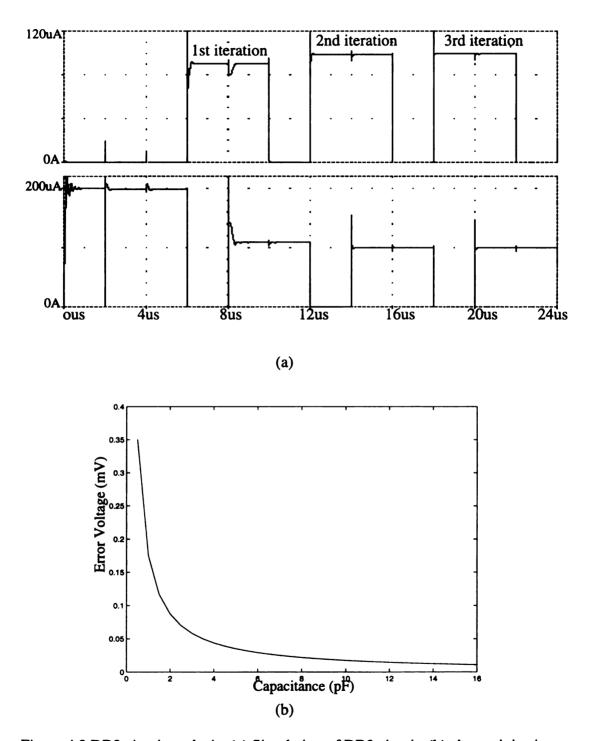

Figure 2.2(b) shows an accurate current divider [53] which divides an input current by two. The number of iterations necessary to obtain half the current with certain accuracy depends on the mismatch of transistors  $N_2$  and  $N_3$ . Each iteration takes three clock cycles. The current copying sequences for the first iteration and the remaining iterations are listed in (a1)-(c1), and in (A1)-(C1), respectively [53].

$$(a1) I_{in} \rightarrow N_2 \& N_3$$

(a1)

$$I_{in} \rightarrow N_2 \& N_3$$

(A1)  $I_{in} \& N_1 \rightarrow N_2 \& N_3$

(b1)

$$N_2 \rightarrow P_4$$

(b1)

$$N_2 \rightarrow P_4$$

(B1)  $N_2 \rightarrow P_4$

(c1)

$$P_4 \& N_3 \rightarrow N_1$$

(C1)  $P_4 \& N_3 \rightarrow N_1$

$$(C1) \quad P_4 \& N_3 \rightarrow N_1$$

where " $I_{in} \rightarrow N_2 \& N_3$ " in (a1) means that the input current  $I_{in}$  is stored to both copiers with  $N_2$  and  $N_3$ . By (b1) and (c1),  $I_1=I_2-I_3$  which is stored to the copier with  $N_1$ . Since the NMOS copier stores only a positive current, hence the divider functions properly only when  $I_2 > I_3$ .

Let  $\alpha_2$  and  $\alpha_3$  be the mismatch factors of the transistors  $N_2$  and  $N_3$ , respectively, where  $I_2=\alpha_2I_{in}$ ,  $I_3=\alpha_3I_{in}$ , and

$$\alpha_2 = [k_2(V_{gs}-V_{T2})^2] / [k_2(V_{gs}-V_{T2})^2 + k_3(V_{gs}-V_{T3})^2]$$

(2.1)

$$\alpha_3 = [k_3(V_{gs}-V_{T3})^2] / [k_2(V_{gs}-V_{T2})^2 + k_3(V_{gs}-V_{T3})^2]$$

(2.2)

Figure 2.2 SI circuits: (a) MX2 [8]; and (b) DB2 [53].

where  $V_{T2}$  and  $V_{T3}$  are the threshold voltages of transistors  $N_2$  and  $N_3$ , respectively, and the device transconductance  $k_i=k_i'(W/L)_i$ , i=1 or 2, is the aspect ratio of transistor  $N_i$ . Thus,  $\alpha_2 > \alpha_3$  if  $I_2 > I_3$ . Because the transistor mismatch is generally unknown in advance, the current divider functions properly only when the mismatch factor  $\alpha_2 > \alpha_3$ . Thus, an alternative current divider is presented in [53], in which the division works for any mismatch factors. The relationship among the number of iterations required for the division process, the mismatch factor, and the desired accuracy, was derived as follows. Let  $\gamma$  denote the mismatch ratio, i.e.,  $\gamma=(\alpha_3/\alpha_2)-1$ . According to the current copying sequence, the current held in  $N_3$  at the end of the first cycle of the k-th iteration, denoted as  $I_{3k}$ , is expressed as [54]

$$I_{3k} = (I_{in}/2)\{1 + (-1)^{k-1}[\gamma/(2+\gamma)]^k\}$$

(2.3)

Table 2.1 lists the relationship among the number of iterations k, the mismatch factor  $\gamma$ , and the accuracy, i.e.,  $II_{3k}-I_{in}/2l/(I_{in}/2)$ , or  $I[\gamma/(2+\gamma)]^k I$ . Apparently, the error term  $[\gamma/(2+\gamma)]^k$  diminishes rapidly as k increases, i.e.,  $I_{3k}\approx I_{in}/2$ . Thus, the error term is used to determine the number of iterations necessary to obtain  $I_{in}/2$  with certain accuracy. Results show that the divider can achieve an accuracy of  $6.21\times10^{-6}$  by taking five iterations for 20%. On the other hand, for a practical 1% transistor mismatching, the circuit takes only two iterations to achieve an accuracy of  $2.47\times10^{-5}$ .

#### 2.3 Data Converter Circuits

This section reviews the basic data converter algorithms and data converter circuits.

|  |  | ا ند |

|--|--|------|

Table 2.1 Relationship among k. y. and accuracy.

(k: number of iterations,  $\gamma$ : mismatch factor)

| k                     | γ=20%                                                    | γ=10%                                                    | γ=5%                                                     | γ=2%                                                     | γ=1%                                                     |

|-----------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5 | 9.09e-02<br>8.26e-03<br>7.51e-04<br>6.83e-05<br>6.21e-06 | 4.76e-02<br>2.26e-03<br>1.07e-04<br>5.14e-06<br>2.45e-07 | 2.44e-02<br>5.95e-04<br>1.45e-05<br>3.53e-07<br>8.63e-09 | 9.90e-03<br>9.80e-05<br>9.70e-07<br>9.60e-09<br>9.51e-11 | 4.97e-03<br>2.47e-05<br>1.23e-07<br>6.12e-10<br>3.04e-12 |

| k                     | γ=-20%                                                   | γ=-10%                                                   | γ=-5%                                                    | γ=-2%                                                    | γ=-1%                                                    |

| 1<br>2<br>3<br>4<br>5 | 1.11e-01<br>1.23e-02<br>1.37e-03<br>1.52e-04<br>1.69e-05 | 5.26e-02<br>2.77e-03<br>1.45e-04<br>7.67e-06<br>4.03e-07 | 2.56e-02<br>6.57e-04<br>1.68e-05<br>4.32e-07<br>1.11e-08 | 1.01e-02<br>1.02e-04<br>1.03e-06<br>1.04e-08<br>1.05e-10 | 5.02e-03<br>2.52e-05<br>1.26e-07<br>6.37e-10<br>3.20e-12 |

#### 2.3.1 Conversion Algorithms

A DAC converts binary numbers, represented by patterns of 1's and 0's, into discrete analog data represented by, either voltage or current. To simplify the discussion in the later chapters, current data conversion is referred to. Depending on how the DAC is configured, the transfer function of a DAC can be unipolar (outputs having only positive or negative values, but not both) or bipolar (outputs can be either positive or negative). There is a simple linear correspondence between the input codes and the output current levels. For an N-bit DAC, the output current is represented by

$$I_{\text{out}} = I_{\text{FS}} (b_1/2 + b_2/4 + ... + b_{N-1}/2^{N-1} + b_N/2^N)$$

(2.4)

where the coefficients,  $b_1$ ,  $b_2$ , ...,  $b_N$ , represent the logic levels of the input bits, which can be 1 or 0,  $b_1$  is the *most significant bit* (MSB) while  $b_N$  is the *least significant bit* (LSB), and  $I_{FS}$  is the full-scale (FS) current. Eqn (2.4) can be achieved from the following recursive algorithm,

$$I_k = I_{k-1} / 2;$$

(2.5)

$$B_k = B_{k-1} + b_{N-k+1} \times I_{k-1};$$

$k=1,2,...,N$  (2.6)

where  $I_k$  is the reference current for the k-th bit conversion and  $B_k$  is the current that is accumulated at the end of the k-th bit conversion. The initial conditions for (2.5) and (2.6) are  $B_0=0$ , and  $I_0=I_{FS}$ . For simplicity, this approach is referred to as the *dividing conversion* (DC) approach.

On the other hand,  $I_{FS}=2^N$   $I_{LSB}$ , or  $I_{LSB}=I_{FS}/2^N$ , where  $I_{LSB}$  is the current for converting the LSB. Eqn (2.4) can be rewritten as

$$I_{\text{out}} = (b_1 2^{N-1} + b_2 2^{N-2} + .. + b_{N-1} 2 + b_N) I_{\text{LSB}}$$

(2.7)

and can be achieved by the following recursive algorithm,

$$J_k = 2 \times J_{k-1}; \tag{2.9}$$

where  $J_k$  is the reference current for the (N-k)-th bit conversion and  $B_k$  is the current that is accumulated at the end of the (N-k)-th bit conversion. The initial conditions for (2.8) and (2.9) are  $B_0$ =0, and  $J_0$ = $I_{LSB}$ . This approach is referred to as *multiplying conversion* (MC) approach.

The objective of an ADC is to determine the output digital word corresponding to an analog input signal. The ADC usually requires a sample-and-hold (S/H) circuit at the input because it is not possible to convert a changing input signal. The characterization of the ADC is almost identical to that of the DAC if the input and output definitions are interchanged. Cyclic (or algorithmic) and successive-approximation (SA) ADCs convert an input signal (either current or voltage) into an N-bit digital data word using the MC or the DC approach, respectively.

More specifically, a cyclic ADC first samples and holds an input current/voltage, and converts the MSB of the input current/voltage by comparing twice the input current/voltage to the reference current/voltage. If the signal exceeds the reference, the MSB will be a "1" and a residual current/voltage is the difference of twice the input signal and the reference. Otherwise, the MSB will be a "0" and the residual current/voltage is just the twice the input signal. The residual current/voltage is then converted to find the next bit. This sequence is repeated until the desired resolution has been achieved. Thus, a cyclic ADC requires a multiply-by-two (MX2) circuit to generate the double residual current/voltage value.

On the other hand, the SA ADC requires a divide-by-two (DB2) circuit to generate

the weighted references, as in Eqn. (2.4). The SA ADC converts the MSB of the input current/voltage by comparing it to the generated weight which is half of the reference at this step. If the input signal exceeds the weight, the MSB will be a "1" and the residual current/voltage is the difference of the input signal and the weight. Otherwise, the MSB will be a "0" and the residual is just the input signal. The residual is then converted to calculate the next bit. This sequence is repeated until the desired resolution is achieved.

#### 2.3.2 Design Specifications of Data Converters

One of th basic problems in specifying the transfer function of an A/D convert is that the characteristics of the transfer function are dependent on the application and test circuit, the type of input signal, and the sampling rate of the converter [55]. This section reviews the important parameters and terminology used in the data converters developed in this thesis.

Dynamic range is the ratio of the largest input that can be converted to the smallest step size of the converter. For example, a 10-bit current-mode ADC with an input range from  $100\mu$ A to  $600\mu$ A has a quantization step size of  $(600\mu-100\mu)/2^{10}\approx0.5\mu$ A. Therefore, the dynamic ratio is 1024 and can be also expressed in decibnels as  $20 \log 1024 = 60 \text{ dB}$ .

Resolution refers to the number of quantization levels an input signal can be determined to. This number is usually given in bits. For example, if which of 1024 levels an input signal lies within can be identified, then the converter is said to have an 10-bit resolution.

Effective number of bits (ENOB) is a measure of overall A/D performance under dynamic conditions. Cumulative effects of many error sources such as quantization noise,

dyn noi:

late

fun

ı2<sup>5</sup>

the

ide

cor

tio: ma

an.

da m

2.3

the ap

the

the

dynamic differntial nonlinearity error, missing codes, integral nonlinearity, jitter, and noise, all contribute to a lower effective number of bits. In general, ENOB can be calculated from the SNR obtained from dynamic FFT testing, i.e., ENOB=(SNR-1.76)/6.02.

Differential nonlinearity (DNL) error is a measure of how uniform the transfer function step sizes are. Each step size is compared to the ideal step size, i.e., ( $I_{max}$ - $I_{min}$ )/ (2<sup>b</sup>-1). An difference in magnitude is DNL error. If the DNL error is less than one LSB, the converter will not have any missing codes. If the DNL error is less than 0.5 LSB, the converter will be monotonic.

Integral Nonlinearity (INL) error is the deviation of code midpoints from their ideal locations. A differential error is the error in a particular step size at any specific location in the converter transfer function. Integral error is equivalent to the integration (summation) of these errors along the converter's transfer function.

Signal-to-Noise ratio (SNR) is characterized by sampling a pure sinusoidal input and performing an FFT on the collected data. SNR is the ratio of the magnitude of the fundamental frequency to the root mean square (rms) of all other frequencies including harmonics.

#### 2.3.3 CMOS SI ADC Circuits

The ADC circuits can be generally classified into three categories according to their conversion speed: Flash/Folding techniques [29,32], Algorithmic/Successive approaches [34,56], and Oversampling techniques [35,36]. Flash/folding techniques have the fastest conversion speed but the lowest resolution, while the oversampling ones have the slowest speed but the highest resolution. *Cyclic* or *algorithmic conversion* is well

kn tio **c**01 Di **SO**2 śic as of ag th Si L tł tł eı a known for its ability to achieve medium resolution within small silicon area [58].

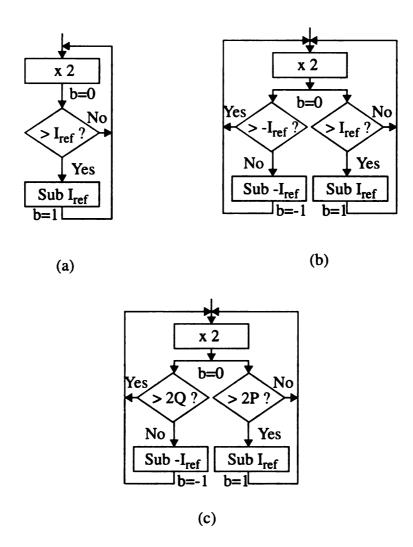

Figure 2.3 illustrates the cyclic conversion algorithms: (1) based on the conventional restoring numerical division principle [59], as shown in Figure 2.3(a), referred to as conventional cyclic conversion algorithm; (2) based on the RSD (Redundant Signed-Digit) cyclic conversion with the SRT division principle developed by Sweeney, Robertson, and Tocher [59], as shown in Figure 2.3(b); and (3) based on the RSD cyclic conversion with the modified SRT division principle [24], as shown in Figure 2.3(c), referred to as modified RSD cyclic conversion algorithm.

The conventional cyclic conversion algorithm, consists of the multiplication of two of the signal to be converted followed by a comparison of the result with a reference voltage (current): If the signal is larger than the reference, the MSB (most significant bit) of the output code is set to 1, and the reference is subtracted from the signal; else, the MSB is set to 0, and no arithmetical operation is carried out. The remaining part of the signal, the so-called "residue voltage (current)" corresponding to the partial remainder of the division, undergoes the same operation for the next bit decision, and the loop is run until the LSB (least significant bit) is obtained. The ADC in [8], as shown in Figure 2.4(a), adopts this conversion algorithm. For the modified RSD cyclic conversion algorithm, two conversion levels P and Q are used, where P is positive and Q is negative. If the input signal, twice of the residue voltage (current) is larger than 2P, the output code bits is set to a 1 and the reference is subtracted; if it is smaller than 2Q, the output code is set to -1 and the reference is added; else, then the bit is set to 0 and no arithmetical operation is carried out. The ADCs with switched-capacitor [58] and switched-current [10] techniques adopt this algorithm. The modified RSD conversion algorithm provides a large tolerance for the

Figure 2.3 Cyclic conversion algorithms: (a) conventional restoring numerical division; (b) RSD approach on the SRT division; and (c) RSD approach on the modified SRT division (referred to as modified RSD approach)

Figure 2.4: Cyclic ADC Circuits: (a) in [8]; and (b) in [16,18].

(b)

comparator's inaccuracy, thus high levels of noise, error effect, and even hysteresis are allowed [58]. The detail design and operation of the ADCs with the above both conversion approaches will be discussed in the next section.

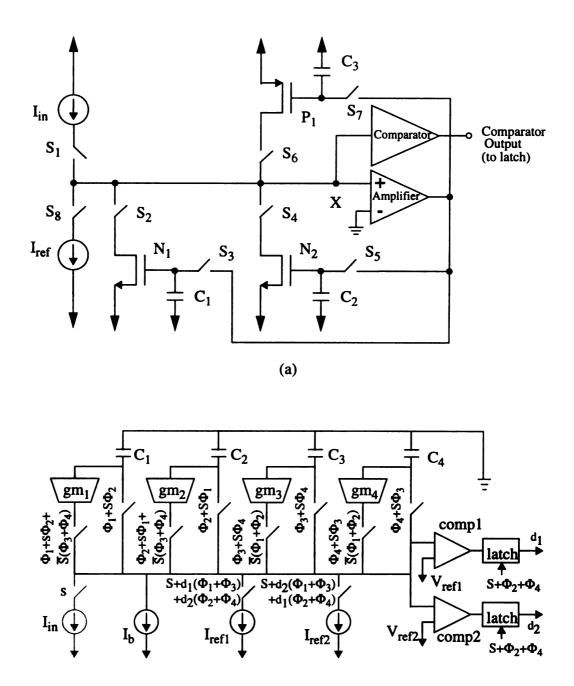

The ADC in [8] employs a residual amplifier which takes three cycles to double a current, and it requires 4 cycles to complete one bit conversion. The residual amplifier in [10,58] also requires 3 cycles to double a current, but the ADC's needs only 3 cycles to complete one bit conversion. A dynamic calibration technique was employed to alleviate the error due to component mismatch. However, the accuracy of the residual amplifier is limited by two major error effects, *charge-feedthrough* and *non-zero output conductance* of a copier. The errors are introduced and accumulated at each cycle. To reduce such errors, a two-cycle residual amplifier for a SI cyclic ADC, as shown in Figure 2.4(b), which takes only 2 cycles to complete one bit conversion was presented in [16,18].

# 2.3.3.1 4-cycle Conversion

Figure 2.4(a) illustrates the schematic diagram of the ADC circuit [8], where a 3-cycle residual amplifier, as shown in Figure 2.2(a), is employed. The converter is comprised of two NMOS current copiers, one PMOS copier, an op-amp, and a current comparator. The converter starts converting for the most significant bit (MSB) of an input current  $I_{in}$  by generating twice the input signal and holding into  $P_1$ . After doubling the current, the current held in  $P_1$  compares with the reference current  $I_{ref}$  in the 4th cycle. If the signal exceeds the reference, the MSB will be a "1", otherwise it will be a "0". This completes the conversion for the MSB.

The remaining (N-1) bits are then converted in the same manner. The signal held in

$P_1$  is loaded into  $N_1$ . If the preceding bit was a "1", the reference is substracted from the signal in  $P_1$ . On the other hand, if it was a "0", the signal remains unchanged. Once  $N_1$  is set,  $N_2$  is followed by the same procedure of  $N_1$ . The signal is then doubled and stored on the gate of  $P_1$ . Finally, it is compared with the reference. This sequence is repeated until the desired resolution has been achieved. An end of conversion pulse is then generated to signal the end of conversion. The converter achieves a 10-bit resolution and a sample rate of 250 kbits/s.

This ADC adopts the conventional restoring numerical division principle. Taking the comparator error into consideration, the residual current may fall off the convergence region and provides incorrect decision [10]. Therefore, such an ADC design needs a comparator with high accuracy and an operation amplifier with low offsets.

## 2.3.3.2 2-cycle Conversion

The number of cycles in conversion can be reduced to two by using four current copiers and comparing the residual current in the amplification phase [16,18]. Figure 2.4(b) shows the structure of the 2-cycle A/D converter. During the conversion state, where the start signal S is low, the four copiers are grouped as two copier pairs,  $gm_{1-2}$  and  $gm_{3-4}$ . At each bit conversion, the residue current, the sum of the currents stored in a copier pair, is copied during  $\Phi_1$  and  $\Phi_2$  (or  $\Phi_3$  and  $\Phi_4$ ) to two current copiers to  $gm_1$  during  $\Phi_1$ , while this sum is copied to  $gm_2$  during  $\Phi_2$ . The sum of the current stored in the latter pair ( $gm_1$  and  $gm_2$ ) becomes the new residue current and is copied back to the former pair ( $gm_3$  and  $gm_4$ ), respectively. Since it takes one cycle to copy the residue current in the

former pair to a current copier in the latter pair, the residue amplifier takes only two cycles to double a current. Two comparators are used to monitor the transconductance current indirectly. The relationship between the input voltage and the current in the transconductance is  $I_i=gm_iV_{ci}$ , where  $I_i$  is the current of transconductance  $gm_i$  and  $V_{ci}$  is the voltage on the capacitance Ci. Therefore, the voltages  $V_{ci}$  can be compared with the reference voltages  $V_{ref1}$  and  $V_{ref2}$  in the circuit. Since large comparator errors are permitted by a RSD algorithm, neither exact transconductance nor accurate comparators are needed. The comparison results are latched at the ends of  $\Phi_2$  and  $\Phi_4$ , where the conversion for one bit is completed. The single-bit binary outputs  $d_1$  and  $d_2$  of the latches control the two reference currents  $I_{ref1}$  and  $I_{ref2}$  to implement a RSD algorithm. There exists a large tolerance of  $I_{ref}/4$  for the comparison levels. Results show that the 2-cycle ADC can achieve 12-bit resolution, 50ns/b conversion rate, and 5mW power consumption.

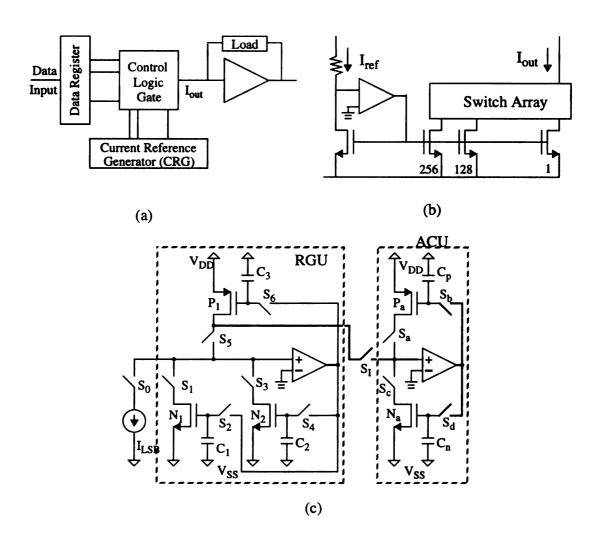

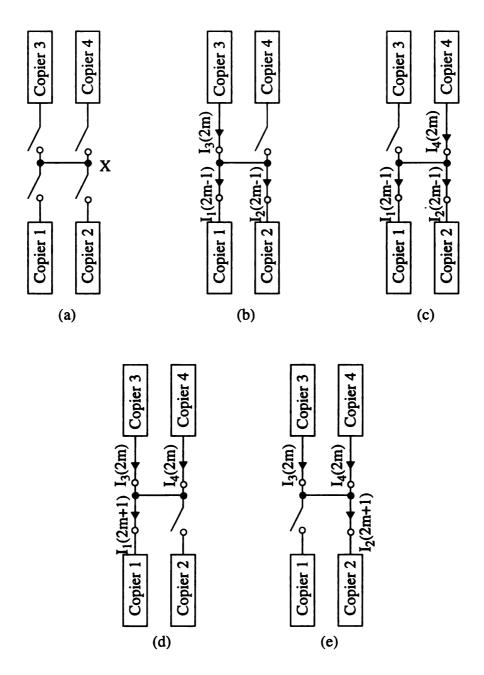

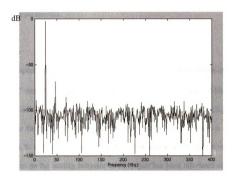

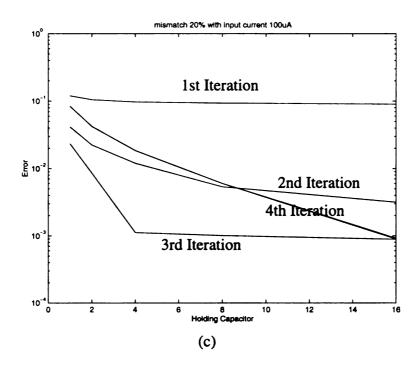

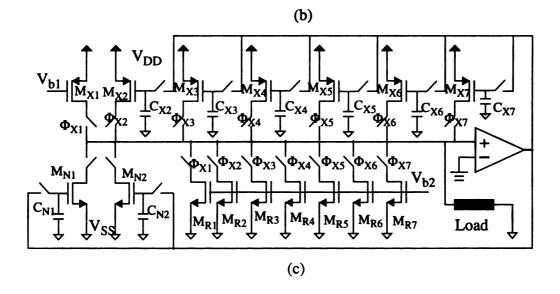

#### 2.3.4 CMOS SI DAC Circuits

Figure 2.5(a) illustrates a design of current-mode DAC, where the current reference generator (CRG) generates the current references, or binary weights, for the converter. Figure 2.5(b) shows a typical CRG circuit, where the current references are realized by ratioed currents. To obtain accurate signal multiplication/division without the need for well-matched components, a switched-current CMOS CRG circuit using MC approach, referred to as CRG\_MC circuit, was developed in [60] which generates the current references in (2.8) and (2.9). Recently, a switched-current CRG circuit using DC approach, referred to as CRG\_DC circuit, was presented in [47] which generates the cur-

Figure 2.5 Current-Mode DAC circuits: (a) a typical design; (b) a typical current reference generator (CRG); and (c) a SI DAC with CRG\_MC [47].

rent reference in (2.5) and (2.6). Thus, both CRG\_DC and CRG\_MC can be used as the current reference generator of the DAC in Figure 2.5(a).

Figure 2.5(c) shows the algorithmic current-mode DAC in [47]. The converter consists of a current Reference-Generating Unit (RGU), a switch S<sub>I</sub>, and a current ACcumulation Unit (ACU). The RGU is used to generate the double current reference [60] which is exactly the same as the CRG\_MC circuit; The switch S<sub>I</sub> is controlled by the digital input code, where the switch is turned on when b<sub>i</sub>=1 and off when b<sub>i</sub>=0, for i=N, N-1,.., 1; The ACU is employed to conduct the current accumulation in (2.8). The RGU, realized by the multiply-by-two circuit (MX2), is shown in Figure 2.2(a). The double current reference  $I_k$ generated by the RGU is stored in P<sub>1</sub>. The ACU is comprised of an NMOS copier and a PMOS copier with an op-amp. Whether or not a current reference generated by the RGU is accumulated is determined by each input bit  $b_k$ . If  $b_k=1$ , i.e.,  $S_I$  is on, then the current reference is accumulated and finally stored in Pa; otherwise, the current held in Pa is unchanged. The RGU needs four cycles to generate a current reference for each bit conversion, while the ACU requires two cycles for the current accumulation. Therefore, for repetitive conversions of continuously changing inputs, the converter requires (4N-2) clock cycles for simultaneously converting three N-bit digital data signal. For a single conversion, the converter may need (4N-1) cycles. Conversion rate can be improved by using a parallel DAC presented in [47] in which the converter can simultaneously convert seven digital data signals in a demultiplexing fashion. The PMOS copier in the ACU is used to store the accumulated current while the NMOS copier acts as a temporary storage element. Conversely, the reference current is stored in the NMOS copiers of the RGU. Thus,

the 1154 2. ŝŪ ar m fa T T C u c

2

8

T

the NMOS copier in the ACU holds the accumulated current while the PMOS copier is used only as a temporary storage element.

#### **2.4** Test Generation of SI Circuits

Although mismatched components are allowed in SI circuits, the SI circuits are still susceptible to faulty switching elements. Any faulty switching elements may result in an incorrect converted data. Based on single stuck-at fault model on the switching elements, the fault behaviors of the ADC in Figure 2.4(a) have been reported [51], in which a faulty switch can be either permanently stuck-at ON state (S/ON) or OFF state (S/OFF). The failure of other components can be modeled as the fault of the associated switch. Thus, the converter can be fully testable. Due to the simplicity of the test generation process, a built-in self-test (BIST) design of the ADC is developed in [62]. However, the simulation results reported in [48] show that stuck-at faults, or catastrophic faults, are approximately 70% of the total faults. This implies that 30% of the total faults are still undetectable. These faults are referred to as parametric faults. Therefore, an efficient and effective fault macromodeling process was developed to enhance the testability of SI circuits [48].

## 2.4.1 Fault Models

Based on circuit layout, technology data, and defect statistics, a set of fault types was developed [50]. According to the functionality of switches in a SI circuit, two types of switches can be identified: voltage switch and current switch. Based on the circuit layout, Table 2.2 shows five examples of process defects which are significant and cause the cir-

Table 2.2. Summary of defects and circuit faults.

| Defect                       | Circuit fault                                                                                                                                  | defect type             |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Break of metal               | a floating drain/source                                                                                                                        | Type f1                 |

|                              | disconnects the switch's input/output                                                                                                          | Type f2                 |

| Break of gate<br>polysilicon | a floating gate may trap some<br>amount of charges on the gate<br>isolates the gate of PMOS transistor<br>isolates the gate of NMOS transistor | Type f3<br>f3-P<br>f3-N |

|                              | shortens the channel width.                                                                                                                    | Type f4                 |

| Defects in active region     | in region increases the channel impedance                                                                                                      |                         |

cuit to malfunction, and summarizes the faults due to these defects. Based on the defects, four fault types of the voltage switch and three fault types of the current switch are concluded and summarized in Table 2.3 [48-51]. Based on the fault types, test generation processes for current copiers [50] and SI ADC [49] were reported and they are discussed below.

#### **2.4.2 Test Generation of Current Copiers**

Consider the basic current copier cell in Figure 2.1(a). The switch faults are summarized in Table 2.2, and the faults on current-storage transistors and holding capacitors can be modeled as the equivalent faults of the associated switch(es) [48,61]. In addition, the following defects may occur in a current-storage transistor. Breaks on gate polysilicon, a Type f3 defect, is equivalent to an S/OFF fault on the associated voltage switch, a Type VS1 fault. Shorten channel width, a Type f4 defect, is equivalent to a Type CS1 fault. Break on metal, either drain or source, a Type f1 defect, is equivalent to an S/OFF fault on the associated current switch, a Type CS1 fault. A short between drain and gate implies an S/ON fault on the associated voltage switch, a Type VS2 fault; A short between source and gate, or between drain and source, is equivalent to a S/OFF fault on the associated voltage switch, a Type VS1 fault. Any defects in active region, a Type f5 defect, is equivalent to a Type CS1 fault. Any process deviation causing an increase of on-resistance implies the presence of a Type CS1 fault. The following defects may occur in the holding capacitors. Any defects causing a decrease of capacitance, or an open circuit in the capacitor, is equivalent to a Type VS4 fault on the associated voltage switch. Any defects caus-

Table 2.3. Fault types.

# (a) Voltage Switch

| Fault<br>Types | Time<br>Constant                                  | Leakage<br>Current |  |

|----------------|---------------------------------------------------|--------------------|--|

| VS1            | Intolerable                                       | Tolerable          |  |

| VS2            | Tolerable                                         | Intolerable        |  |

| VS3            | Intolerable                                       | Intolerable        |  |

| VS4            | Excess charge flows out switch when switch is off |                    |  |

# (b) Current Switch

| Fault<br>Types | Error Current (switch is on) | Leakage Current (switch is off) |

|----------------|------------------------------|---------------------------------|

| CS1            | Intolerable                  | Tolerable                       |

| CS2            | Tolerable                    | Intolerable                     |

| CS3            | Intolerable                  | Intolerable                     |

ing an increase of capacitance, or a short circuit in the capacitor is equivalent to a Type VS1 fault

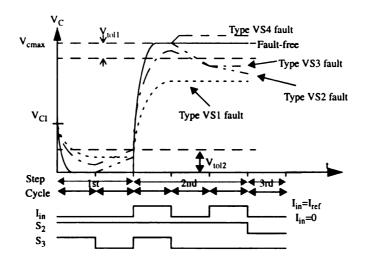

The above equivalent faults include both catastrophic and parametric faults for both current-storage transistors and the holding capacitors in a copier. Based on the fault types in Table 2.3, the fault behaviors, as illustrated in Figure 2.6 [50], can be distinguished from the fault-free behavior by the test sequence. Thus, all fault types in Table 2.3 can be tested.

#### 2.4.3 Test Generation of ADC Circuits

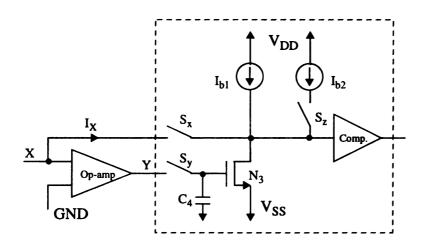

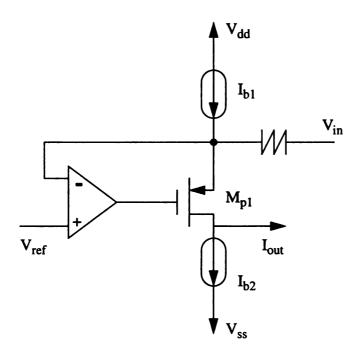

Consider the ADC from Figure 2.4(a) with a comparator, as shown in Figure 2.7. In the comparator, a current copier consisting of  $N_3$ ,  $C_4$  and switches  $S_x$  and  $S_y$ , is used as a load to copy the difference current  $I_x$ . Since the difference current may be positive or negative, a bias current source  $I_{b1}$  is used to keep a positive current to be copied to  $N_3$ . A current which is slightly higher than  $I_{ref}$  is chosen for  $I_{b1}$ . The copier memorizes the current  $I_x$  and produces a voltage deviation to compare to a zero-voltage in the comparator. Since the resolution of an ADC is 0.5 LSB, or 0.5  $I_{ref}$ , here a simple comparator instead of window comparator, can be used. It should be noted that an additional bias current  $I_{b2}=I_{ref}$  and the switch  $S_z$  are used only for testing purpose. During the normal operation,  $S_z$  is off and the bias current is isolated from the converter circuit. Thus, the extra circuitry does not affect the performance of the converter.

In Figures 2.4(a) and 2.8,  $S_1$ ,  $S_2$ ,  $S_4$ ,  $S_6$ ,  $S_8$ ,  $S_x$ , and  $S_z$  are current switches, while  $S_3$ ,  $S_5$ ,  $S_7$ , and  $S_y$  are voltage switches. The ADC consists of four copiers. One may apply

Figure 2.6 Fault behavior and switching sequence

Figure 2.7 Simplified schematic diagram of SI algorithmic ADC with additional comparator

the test sequence developed in the previous section for all copiers in the ADC. However, in the ADC, we can only observe the result from the output of the comparator, i.e., the converted digital data. Thus, the test sequence should be generated to maximize the accumulated errors so that the error effect can be reflected to the converted digital data [49].

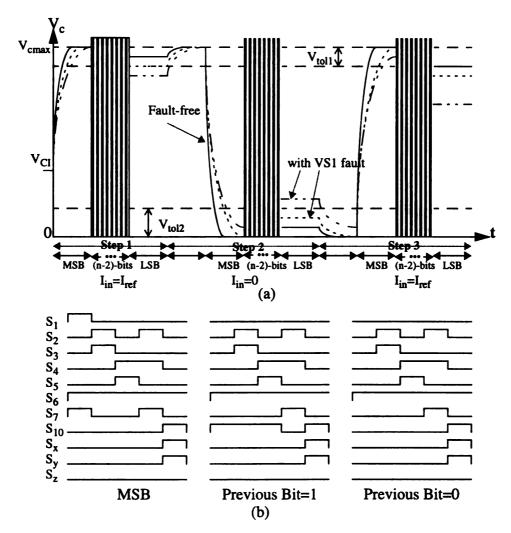

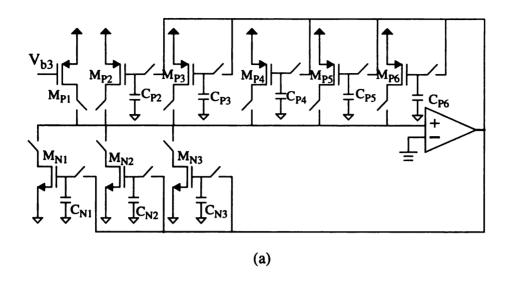

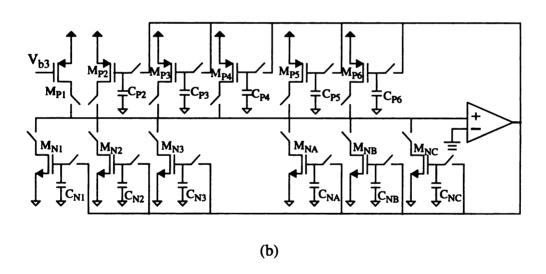

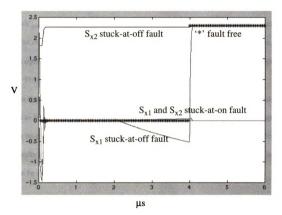

Figure 2.8 illustrates the fault behaviors and switching sequences of a test sequence, referred to as Test Sequence A, which detects  $Types\ VS1$ , VS3, and VS4 faults for  $S_3$ ,  $S_5$ , and  $S_7$ ,  $Types\ CS1$ -CS4 faults for  $S_1$ ,  $S_2$ ,  $S_4$ ,  $S_6$ , and  $S_{10}$ , and  $Types\ CS2$  and CS3 faults for  $S_x$ . Figure 2.9 shows the fault behaviors and switching sequence of another test sequence, referred to as Test Sequence B, which detects  $Types\ VS2$  and VS3 faults for  $S_3$ ,  $S_6$ ,  $S_7$ ,  $Types\ CS1$  and CS3 faults for  $S_x$ ,  $Types\ CS1$ -CS3 faults for  $S_y$ , and  $Types\ VS1$ -VS4 faults for  $S_y$ . This implies that both test sequence will detect all switching faults.

## 2.5 Discussion

Current copier is the basic building block of a SI circuit. The performance of a SI circuit is determined by the performance of the current copiers it employs. Thus, synthesizing optimum current copiers for SI circuits becomes very important task in the SI circuit design [63].

The objective of this study is to develop high performance and low power data converters. For the design of CMOS SI DAC circuits, as discussed in Section 2.3.4, the CRG circuit can be either realized by using the CRG\_DC circuit or CRG\_MC circuit. However, for an N-bit CRG\_DC circuit, its LSB current,  $I_{LSB}=I_{FS}/2^N$ , cannot be lower than its SNR. This implies that its bit size is limited by the given full-scale current  $I_{FS}$ . It also implies that, for a given SNR of an N-bit CRG\_DC circuit, the only way to increase

Figure 2.8 Test sequence A: (a) Fault behaviors; (b) Switching sequence.

Figure 2.9 Test Sequence B: (a) Fault Behavior; and (b) Type VS2 fault.

the bit size is the use of larger I<sub>FS</sub>, but it will be penalized by the increase of power consumption. This concludes that the bit size of both CRG\_DC and CRG\_MC circuits cannot be arbitrarily large for low-power applications. Therefore, to increase the resolution of a SI CMOS DAC circuit for low-power application, Chapter 4 will present alternative structures of DAC circuit combining CRG\_DC and CRG\_MC circuits.

As discussed in Section 2.4, test signals for testing current copiers and ADC circuits with the catastrophic faults can be easily generated and applied. However, test generation for those circuits with the parametric faults will become much complex [48]. This is partially due to the lack of accessibility. As suggested in [48], a built-in tester can be used to simplify the test generation and application. In practice, however, the built-in tester must be able to test itself to increase the reliability of the tester and also autozero the comparator to increase the accuracy of the tester. Chapter 6 presents a built-in tester which includes a current comparator with autozero and self-test capabilities.

# Chapter 3

#### CMOS SI ADC CIRCUIT DESIGN

This chapter presents a high-speed, high-resolution, and low-power CMOS SI ADC circuit [64]. High performance is attributed to the use of the following components: (1) a high-performance residual amplifier which takes two clock cycles to double a current; and (2) an efficient cyclic RSD algorithm which provides 1.5b resolution without using two matched reference currents. Section 3.1 describes the design and operation of the developed ADC using a 2-cycle residual amplifire and 2-cycle conversion algorithm. Section 3.2. discusses the design consideration for achieving high performance and lower power. Section 3.3 presents the design, simulation, layout, and measurement of the fabricated chip. Finally, a concluding remark is given in Section 3.4.

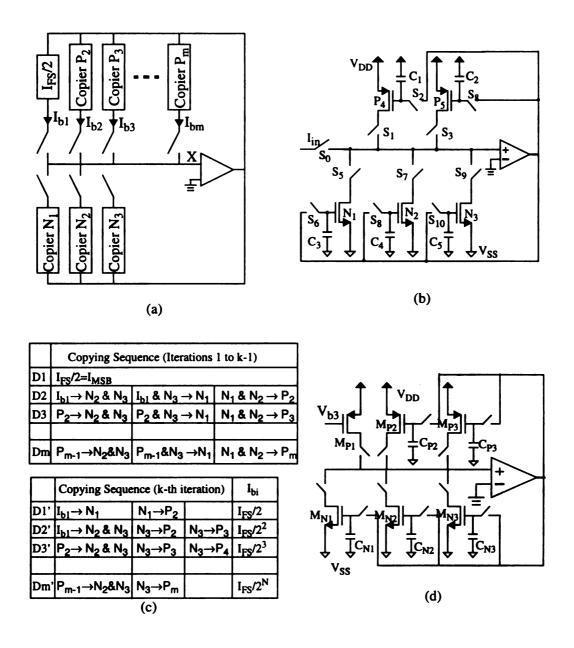

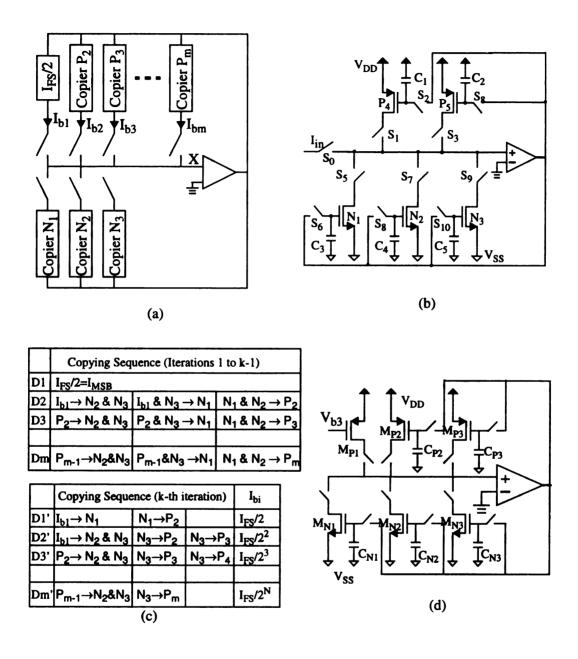

## 3.1 Design and Operation

This section presents the developed 2-cycle residual amplifier and 2-cycle conversion algorithm. The special features in the residual amplifier are: (1) the amplifier has a negative gain; and (2) the use of two reference currents which do not need to be well-matched. Based on the special features, the modified RSD algorithm is used for the developed CMOS SI ADC.

# 3.1.1 2-cycle Residual Amplifier

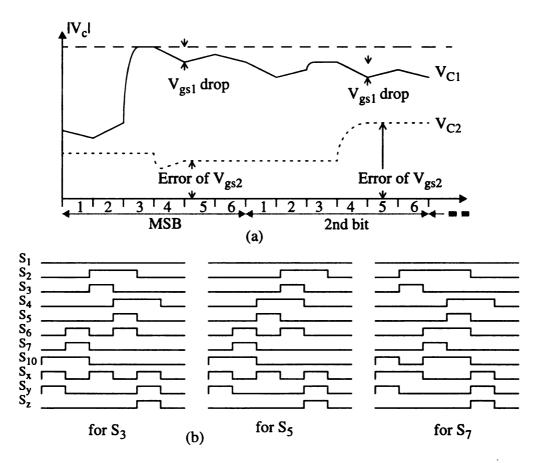

To reduce the number of cycles, a 2-cycle residual amplifier is developed as shown in Figure 3.1(a), where four copiers are used. First, the input current is copied to copiers 1 and 2 in two consecutive cycles, where  $I_1(1)=I_2(1)=I_{in}$ . Then, the sum current,  $I_1(1)+I_2(1)=2I_{in}$  are stored to copier 3 and then to copier 4. Both copiers 3 and 4 hold the same doubled current, i.e.,  $I_3(2)=I_4(2)=I_x=2I_{in}$ . Similarly, the sum currents,  $I_3(2)+I_4(2)=2I_x$ , are then stored to copier 1 and then to copier 2. Thus both copiers 3 and 4 have the same doubled current, i.e.,  $I_1(1)=I_2(1)=2I_x$ .

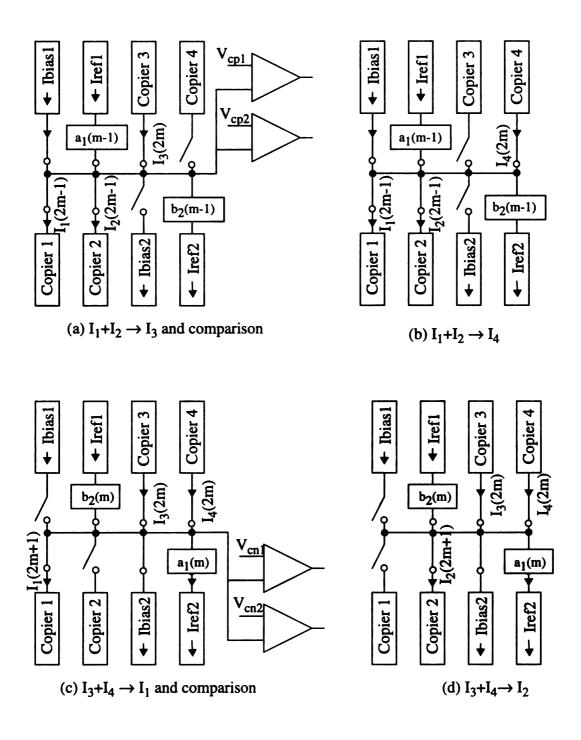

Let  $I_1(2m-1)$  and  $I_2(2m-1)$  be the currents held in copiers 1 and 2, respectively, and determine the (m-1)-th bit  $D_{m-1}$ . The sum current  $I_1(2m-1)+I_2(2m-1)$  is stored to copier 3 and then copier 4, as shown in Figures 3.1(b) and 3.1(c), where  $I_3(2m)=I_4(2m)=I_1(2m-1)+I_2(2m-1)$ . The sum current determines the m-th bit. Similarly, as shown in Figures 3.1(d) and 3.1(e), the sum current  $I_3(2m)+I_4(2m)$  is copied to copier 1 and then to copier 2 to determine the (m+1)-th bit. The process is repeated and it takes 2 cycles to double a current.

When the sum current  $I_1(2m-1)+I_2(2m-1)$  is stored to copier 3, once the copier is settled, the voltage at node X, as denoted in Figure 3.1(a), is compared to determine the m-th bit. Similarly, the (m+1)-th bit is determined when the sum current is copied to copier 1, as shown in Figure 3.1(d). Thus, the ADC design using the developed residual amplifier takes only 2 cycles for one bit conversion.

## 3.1.2 2-cycle Conversion with Modified RSD Algorithm

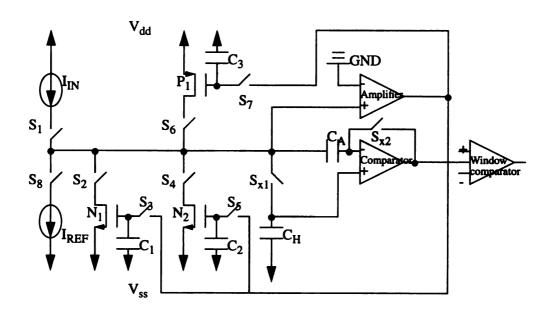

Figure 3.2 shows the schematic circuit diagram and block diagram of the developed SI cyclic ADC design, where copiers 1 and 2 are implemented with NMOS copiers, and

Figure 3.1 Proposed 2-cycle residual amplifier: (a) block diagram with 4 copiers; (b)&(c) operations for m-bit; and (d)&(e) operations for (m+1)-bit.

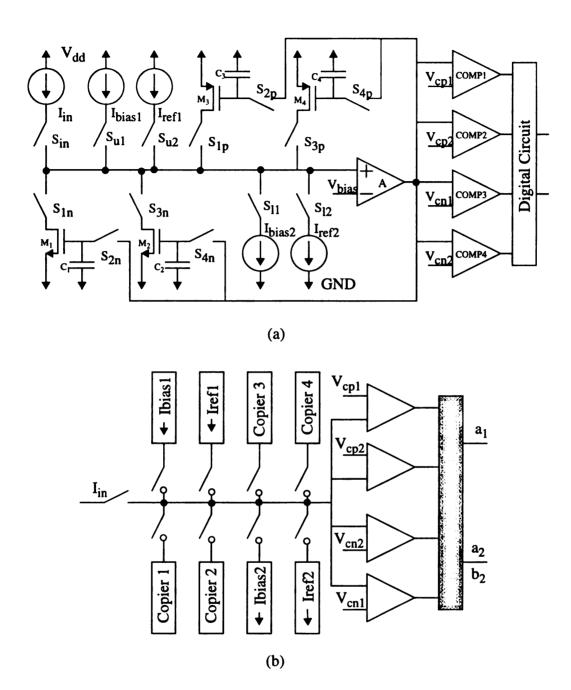

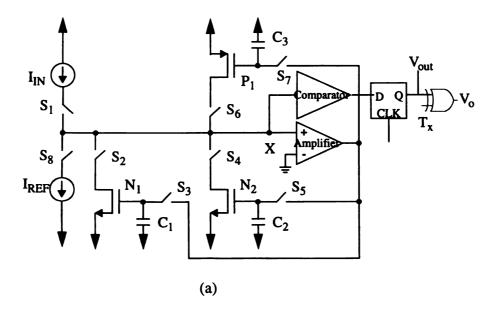

Figure 3.2 Proposed switched-current CMOS cyclic ADC: (a) schematic diagram; and (b) block diagram.

copiers 3 and 4 are implemented with PMOS copiers. In addition, two bias current sources,  $I_{bias1}$  and  $I_{bias2}$ , and two reference current sources,  $I_{ref1}$  and  $I_{ref2}$ , are employed. Two pairs of comparators are used: the upper pair compares the voltage at node X when the residue current is copied to copier 3, as illustrated in Figure 3.3(a), while the lower pair compares the voltage when the residue current is copied to copier 1, as shown in Figure 3.3(c). The ADC design adopts a modified RSD conversion algorithm described below.

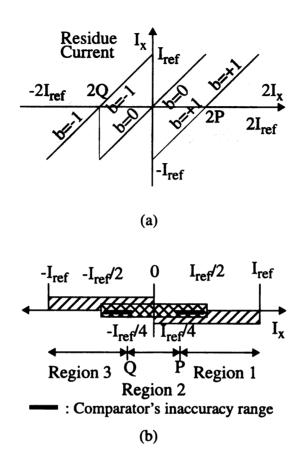

Consider the modified RSD conversion algorithm, as illustrated in Figure 2.3(c). At each bit decision, two comparison levels P and Q are used, with P positive and Q negative. If the input signal I<sub>x</sub> is larger than P, the output code bit is set to 1 and the reference is subtracted; if I<sub>x</sub> is smaller than Q, the output code bit is set to -1 and the reference is added; else, then the bit is set to 0 and no arithmetic operation is carried out. If the comparison takes place before the multiplication by 2, the only requirement on the comparison levels is  $2P \in [0,I_{ref}]$  and  $2Q \in [-I_{ref},0]$ , as shown in Figure 3.4(a), i.e.,  $P \in [0,I_{ref}/2]$  and  $Q \in [-I_{ref}/2]$ 2,0]. Setting P and Q, respectively, at about +I<sub>ref</sub>/4 and -I<sub>ref</sub>/4, as shown in Figure 3.4(b), provides a large tolerance of  $\pm I_{ref}/4$  for the comparator's inaccuracy, thus high levels of noise effect, and even hysteresis are allowed. However, the probability of having b=0 becomes only 25%, where both b=1 and b=-1 take 75%. Note that the converter circuit takes no operation when b=0. Therefore, this implementation chose P=+I<sub>ref</sub>/3 and Q=-I<sub>ref</sub>/3 to increase the probability of b=0 as 33%. Note that the tolerance of the comparator's inaccuracy is  $\pm I_{ref}$ 6 which is sufficiently large for us to comfortably design the comparator, where  $I_{ref}$ =250 $\mu$ A is used in this implementation.

Let I<sub>res</sub>(m-1) be the residue current that determines the m-th digit, where

$$I_{res}(m-1)=I_1(2m-1)+I_2(2m-1)$$

Figure 3.3 Bit conversion: (a)&(b) Operations for m-bit; and (c)&(d) operations for (m+1)-bit.

Figure 3.4 Modified RSD conversion algorithm: (a) Robertson diagram; and (b) Conversion ranges and comparison levels.

By Figures 3.3(a) and 3.3(b), the currents stored in copiers 3 and 4 are

$$I_{3}(2m)=I_{4}(2m)=\begin{cases} I_{res}(m-1)-I_{bias1}-I_{ref1} & : Region 1 \\ I_{res}(m-1)-I_{bias1} & : Region 2 \\ I_{res}(m-1)-I_{bias1}+I_{ref2} & : Region 3 \end{cases}$$

(3.1)

where the convergency regions are defined as

$$D_{m-1} = \begin{cases} 1 & \text{if } I_{res}(m-1) > I_{bias1} + I_{ref1}/3 & : \text{Region 1} \\ 0 & \text{if } I_{bias1} - I_{ref1}/3 \le I_{res}(m-1) \le I_{bias1} + I_{ref1}/3 & : \text{Region 2} \\ -1 & \text{if } I_{bias1} - I_{ref1}/3 > I_{res}(m-1) & : \text{Region 3} \end{cases}$$

(3.2)

Similarly, for the (m+1)-th bit, by Figures 3.3(c) and 3.3(d) the residue current is  $I_{res}(m)=I_3(2m)+I_4(2m)$ , and the currents held in Copiers 1 and 2 are

$$I_{1}(2m+1)=I_{2}(2m+1)=\begin{cases} I_{res}(m)-I_{bias2}-I_{ref2} & : Region 1 \\ I_{res}(m)-I_{bias2} & : Region 2 \\ I_{res}(m)-I_{bias2}+I_{ref2} & : Region 3 \end{cases}$$

(3.3)

where the convergency regions are defined as

$$D_{m-1} = \begin{cases} 1 & \text{if } I_{res}(m) > I_{bias2} + I_{ref2}/3 & : \text{Region 1} \\ 0 & \text{if } I_{bias2} - I_{ref2}/3 \le I_{res}(m) \le I_{bias2} + I_{ref2}/3 & : \text{Region 2} \\ -1 & \text{if } I_{bias2} - I_{ref2}/3 > I_{res}(m) & : \text{Region 3} \end{cases}$$

(3.4)

The m-th converted digit  $D_m$  is encoded as <1,1>, <0,1>, <0,0> for  $D_m=1$  (region 1), 0 (region 2), -1 (region 3), respectively. Let  $b_2(m)$  be the bit complement of  $a_2(m)$ , i.e.,

$$b_2(m) = \begin{cases} 1 & \text{if } a_2(m) = 0\\ 0 & \text{if } a_2(m) = 1 \end{cases}$$

(3.5)

Therefore, (3.1) and (3.3) can be respectively written as the following general form

$$I_3(2m)=I_4(2m)=I_{res}(m-1)-I_{bias1}-a_1(m-1)I_{ref1}+b_2(m-1)I_{ref2}$$

(3.6)

$$I_1(2m+1)=I_2(2m+1)=I_{res}(m)-I_{bias2}-a_1(m)I_{ref2}+b_2(m)I_{ref1}$$

(3.7)

where the residue currents are

$$I_{res}(m-1) = I_1(2m-1) + I_2(2m-1) = 2I_{res}(m-2) - 2I_{bias2} - 2a_1(m-2)I_{ref2} + 2b_2(m-2)I_{ref1}(3.8)$$

$$I_{res}(m)=I_3(2m)+I_4(2m)=2I_{res}(m-1)-2I_{bias1}-2a_1(m-1)I_{ref1}+2b_2(m-1)I_{ref2}$$

(3.9)

It should be noted that, by (3.1) and (3.3), the stored current is with  $I_{ref1}$ ,  $I_{ref2}$ , or neither. Thus, both reference currents  $I_{ref1}$  and  $I_{ref2}$  are not necessary to be well matched. However, the use of well-matched reference current sources guarantees the quality of the stored currents, i.e.,  $I_1=I_2$  and  $I_3=I_4$ , and also reduces the possible current variation in those copies. Let  $I_{ref1}=I_{ref2}=I_{ref}$ . Also, let  $I_{bias1}=I_{bias2}=I_b$ . Therefore, (3.1)-(3.4) can be summarized as follows.

| Region | $D_{m}$ | a <sub>1</sub> | a <sub>2</sub> | b <sub>2</sub> | I <sub>res</sub> (m+1)                                       | Convergent Range                                                                                  |

|--------|---------|----------------|----------------|----------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 1      | 1       | 1              | 1              | 0              | 2I <sub>res</sub> (m) - I <sub>bias</sub> - I <sub>ref</sub> | $I_{res}(m) > I_{bias} + I_{ref}/3$                                                               |

| 2      | 0       | 0              | 1              | 0              | 2I <sub>res</sub> (m) - I <sub>bias</sub>                    | $I_{\text{bias}} - I_{\text{ref}}/3 \le I_{\text{res}}(m) \le I_{\text{bias}} + I_{\text{ref}}/3$ |

| 3      | -1      | 0              | 0              | 1              | $2I_{res}(m) - I_{bias} + I_{ref}$                           | $I_{\text{bias}} - I_{\text{ref}}/3 > I_{\text{res}}(m)$                                          |

## 3.2 Design Consideration

The goal of the developed ADC is to achieve low-power with low supply voltage and moderate conversion speed. There exist design tradeoffs among speed, power consumption, SNR (signal-to-noise ratio), and etc. The speed can be improved, i.e., the decrease of the settling time, by increasing the bias current at the cost of increasing power consumption. The SNR can be reduced by also increasing the bias current while keeping the same input dynamic range. On the other hand, the SNR can be increased by using a large storage capacitance.

Current copier is the basic building block of a SI circuit. The performance of the SI circuit is generally determined by the performance of the copiers it employs. The calibration speed of the copier is determined by the time constant  $\tau = C/g_M$ , where C is the capacitance of the storage capacitor and  $g_M$  is the transconductance of the storage transistor M. Apparently, increasing the gate capacitance results in a slow calibration speed. The questions are: Can a copier with a large gate capacitance still be operated at a high calibration speed? how does  $g_{M1}$  affect the accuracy? and what are the design constraints on selecting C for keeping the time constant  $\tau$  small? The issues on selecting appropriate capacitance has been addressed and can be found in [13-16].

For low-power application, the storage capacitance should be limited by its SNR requirement and determined as follows [65-68],

$$SNR = 10 \log[V_{cn}^{2}(rms) / (kT/C)]$$

(3.10)

where  $V_{cn}(rms)$  is the tolerable noise variation across the capacitor, T is the operation absolute temperature, the Boltzmann constant k=1.23\*10<sup>-23</sup> JK<sup>-1</sup>, and C is the storage capacitance. Thus, for 12-bit resolution, i.e., SNR=74 dB, if  $V_{cn}(rms)$ =1 V, by (3.10), we obtain the storage capacitance C=0.093 pF, where T=300° K. Note that this implementation,  $V_{cn}(rms)$ =0.85 V. With a 74 dB SNR for the 12-bit ADC, the storage capacitance is approximately 0.11 pF. As mentioned, the larger capacitance can decrease noises and errors, and thus decreasing the DNL and INL.

The transistor sizes are determined by the input dynamic range and the bias current. The transistor size should be sufficiently large to operate in the saturation region so that the current can be held correctly. Note that  $V_{gs}$ - $V_T$  <  $V_{ds}$  when the transistor is operated in the saturation region. Taking the process variation into account, for purpose of safety, this im-

plementation sets the maximum voltage of  $(V_{gs}-V_T)$  to be 85% of  $V_{ds}$ , i.e.,  $V_{gs(max)}-V_T=0.85V_{ds}$ . For a power supply of 3.3V,  $V_{ds}\approx1.65V$ . This implies that the maximum voltage  $V_{gs(max)}-V_T=0.85V_{ds}\approx1.4V$ . In general, to keep the transistor inside the strong inversion region, we need  $V_{gs(min)}-V_T=0.2V$ . If the input currents are ranged from  $I_{bias}-(I_{max}/2)$  to  $I_{bias}+(I_{max}/2)$ , then

$$[I_{\text{bias}} + (I_{\text{max}}/2)] / [I_{\text{bias}} - (I_{\text{max}}/2)] = [0.85 \text{V}_{\text{ds}}/0.2]^2$$

Therefore, the transistor sizes are selected based on the selected  $I_{\text{bias}}$  and  $I_{\text{max}}$ .

#### 3.3 Simulation Results and Measurements

The developed ADC circuit, as shown in Figure 3.2(a), employs four copiers with the current-storage transistors  $M_1$ - $M_4$ . Both  $I_{ref1}$  and  $I_{bais1}$  are implemented with two PMOS transistors,  $M_{ref1}$  and  $M_{bais1}$ , and  $I_{ref2}$  and  $I_{bais2}$  are with two NMOS transistors,  $M_{ref2}$  and  $M_{bais2}$ . Switches  $S_{2n}$ ,  $S_{2p}$ ,  $S_{4n}$ , and  $S_{4p}$  are realized by CMOS switches with dummy switches to alleviate the charge-feedthrough errors, while the remaining switches are implemented with simple CMOS switches. The copiers with negative feedback structure are used to reduce the error due to channel-modulation. The digital logic circuits, realized by CMOS transistors, are used to produce the digital codes and the control signals.

The circuit has been designed and simulated by *pspice*, where the *SCAN20* 2 $\mu$ m CMOS process with level-2 transistor parameters and a supply voltage of 3.3 V are employed. The transistor sizes for both M<sub>1</sub> and M<sub>2</sub> are 36  $\mu$ m/2  $\mu$ m, and for both M<sub>3</sub> and M<sub>4</sub> are 80  $\mu$ m/2  $\mu$ m, where the transconductances of both NMOS and PMOS transistors are 780  $\mu$ A/V and 730  $\mu$ A/V, respectively. All capacitances are 0.2 pF. The reference and biased current are chosen as  $I_{ref} = I_{ref1} = I_{ref2} = 250 \mu$ A and  $I_{bias} = I_{bias1} = I_{bias2} = 350 \mu$ A. The

bias voltage for the feedback amplifier is  $V_{bias}=1.65$  V. In the comparators,  $V_{cp1}=1.813$  V,  $V_{cp2}=1.6$  V,  $V_{cn1}=1.46$ V, and  $V_{cn2}=1.689$  V were chosen. The chip layout has been generated by L-edit and simulated by *pspice*. Simulation results show that the current storage transistor can be converged within 30 ns. However, a clock rate of 50 ns is chosen for this ADC simulation.

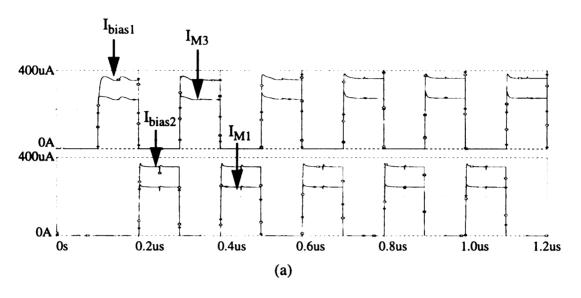

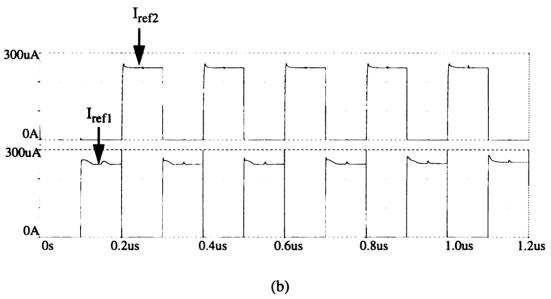

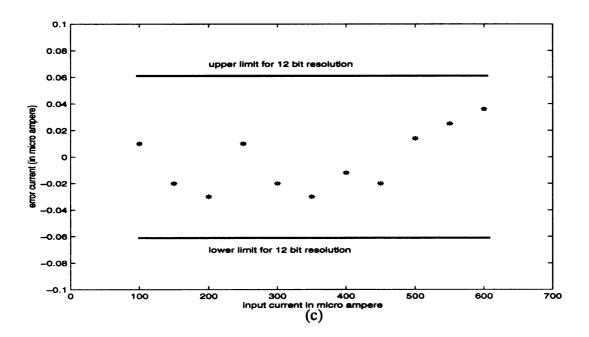

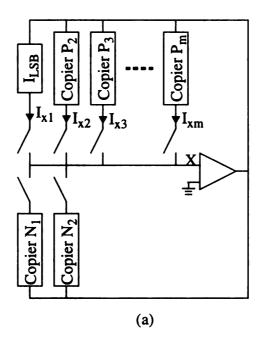

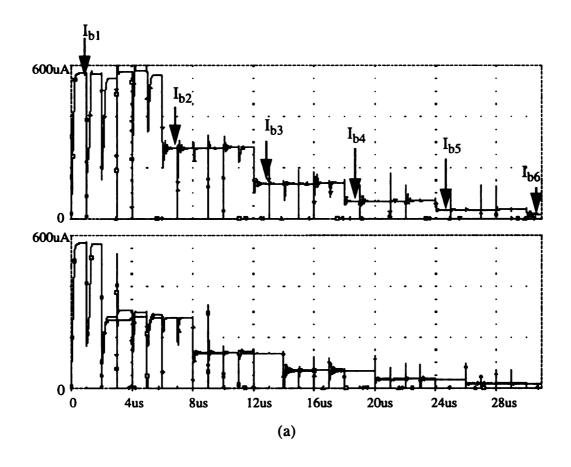

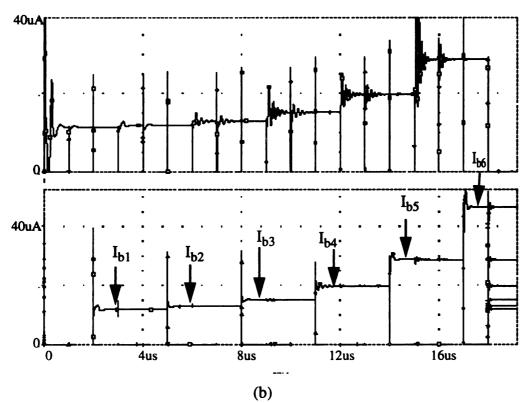

Figure 3.5(a) shows a typical current waveform in a current-storage transistor, where Figure 3.5(b) plots the partial output of  $I_{ref1}$  to demonstrate the three states in the RSD approach. Since the clock rate for calibration is 50 ns, one state is obtained in every 100 ns. Figure 3.5(c) summarizes the accuracy of the proposed ADC which achieves a 12-bit resolution for the input currents ranged between 100  $\mu$ A and 600  $\mu$ A. The power dissipation is approximately 1.9 mW.

It should be mentioned that the effects on mismatched reference currents, i.e.,  $I_{ref1} \neq I_{ref2}$ , and loop offsets errors, have been studied. The proposed ADC will keep the same accuracy and the lower limit of the dynamic range. However, the upper limit of dynamic range decreases as the error effects. More specifically, if both currents  $I_{ref1}$  and  $I_{ref2}$  are off r% from  $I_{ref}$ , or the loop offset error increases r%, the upper limit of the dynamic range will be reduced approximately (r/2)%.

Figures 3.6(a) and 3.6(b) show the layout of the designed chip and the die photo of the fabricated chip, respectively. The ADC is fabricated by MOSIS with the SCNA20 2μm N-well CMOS process, where the threshold voltages for the NMOS and PMOS are 0.83V and 0.99V, respectively. The test chip does not use the double-poly linear capacitor, i.e., it is fabricated by a digital CMOS process. The 40-pin test chip is comprised of three major parts: analog portion, digital portion, and clock/pulse generator portion. The analog por-

Figure 3.5 Simulation results: (a) typical current in a current-storage transistor; (b) partial outputs of Iref1; and (c) 12-bit resolution.

Figure 3.5 (cont'd)

# Clock Control Part ADC Part 1311um (a)

Figure 3.6 Implementation: (a) The layout of the designed ADC; (b) the die photo of the fabricated ADC

(b)

tion is approximately (0.967\*0.42)=0.41 mm<sup>2</sup>, the digital portion is about (0.967\*0.52)=0.50 mm<sup>2</sup>, and the clock/pulse generator is nearly (0.6\*0.31)=0.186 mm<sup>2</sup>. The total active area of the fabricated chip is (1.628\*1.311)=2.13 mm<sup>2</sup>.

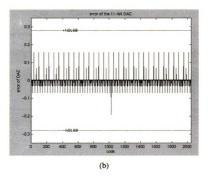

To measure the test chip, a voltage-to-current (V-I) converter, as shown in Figure 3.7 [30], and voltage sources are used to generate the input current signals, where the voltage source for the V-I converter is 5 V. A 24.4 kHz sine wave is applied to the test chip at a 0.8 Msamples per second conversion rate with a 3.3 V supply voltage to measure the linearity of the test chip. The total of 102,400 test data are collected to process the DNL and INL measurements. Figures 3.8(a) and 3.8(b) show the resultant DNL and INL, respectively, where the maximum DNL and INL are 0.6 LSB and 0.5 LSB, respectively. The linearity plots for 12-bit resolution show that the converter may potentially achieve 12-bit or more resolution.

More specifically, as discussed in Section 3.2, for 12-bit converter, the required SNR is set to 74 dB. For V<sub>cn</sub>(rms)=0.85 V, the theoretical value of the storage capacitance is 0.11 pF to keep both DNL and INL within 0.5 LSB. In this implementation, the capacitances are all 0.2 pF for conservative design which will have about 77 dB theoretically. Note that the use of larger storage capacitance can decrease both DNL and INL. In addition, since the converter adopts the RSD correction scheme, the use of smaller capacitance can still achieve the desired DNL and INL. Therefore, with the RSD scheme and the use of larger storage capacitor, the converter achieves very small DNL and INL. If the design limits both DNL and INL to be within 1 LSB, the converter can have the potential to achieve a 13-bit resolution. However, since the clock generator in the test chip was designed for 12-bit resolution, the converter resolution is set to 12 bits.

Figure 3.7 Schematic circuit of voltage-to-current converter

Figure 3.8 Analysis of nolinearity: (a) The INL of designed ADC; and (b) The DNL of designed ADC

Figure 3.9 FFT analysis of designed ADC

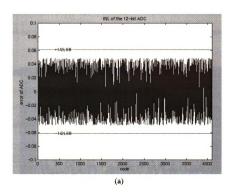

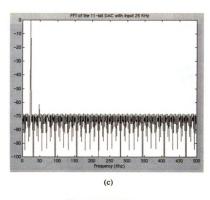

Figure 3.9 shows the measured fast Fourier transform (FFT) spectrum of the test chip. The input signal 24.4 kHz was applied and 24,576 test data were collected to analyze. The total harmonic distortion (THD) is -66.7 dB and the signal-to-noise/distortion ratio (SNDR) is 65 dB which is about 9 dB less than the ideal value. Table 4.1 summarizes the performance parameters.

#### 3.4 Conclusion