THS

## LIBRARY Michigan State University

This is to certify that the

thesis entitled

Implementation and Evaluation of AC/OS for the Handy Board

presented by

Anthony E. Pappas

has been accepted towards fulfillment of the requirements for

Master's degree in Electrical Eng

Major professor

Date \_\_\_\_\_8/10/98

MSU is an Affirmative Action/Equal Opportunity Institution

# PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due. MAY BE RECALLED with earlier due date if requested.

| DATE DUE | DATE DUE | DATE DUE |

|----------|----------|----------|

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

1/98 c:/CIRC/DateDue.p65-p.14

## IMPLEMENTATION AND EVALUATION OF $\mu\text{C/OS}$ FOR THE HANDY BOARD

By

Anthony E. Pappas

### A THESIS

Submitted to

Michigan State University

In partial fulfillment of the requirements

For the degree of

**MASTER OF SCIENCE**

Department of Electrical Engineering

1998

#### **ABSTRACT**

## IMPLEMENTATION AND EVALUATION OF μC/OS FOR THE HANDY BOARD

By

#### Anthony E. Pappas

RTOS (Real-Time Operating System) technology is a viable design option for many embedded systems and applications. It has proven itself as a reliable and useful tool in developing systems that have hard and soft real-time requirements. Many engineers have written their own RTOS because nothing else has been available. However, this often takes away from the application development time. Their RTOS would often be inefficient, requiring maintenance and would not be scalable or portable.

Commercial RTOSs are now available. More engineers chose them over writing their own because commercial RTOSs are proven technology. They are written efficiently, scale well to meet the real-time requirements and port easily to new processors. These RTOSs allow the application to remain abstract and they take the responsibility of handling the system details away from the application. We investigate  $\mu$ C/OS, an RTOS for the MC68HC11, with the following key objectives. First,  $\mu$ C/OS must be ported to the MC68HC11 and there must be a basic understanding of how to use and expand its features for real-time embedded applications. Second, applications must be developed to illustrate these features. Also, a prototype environment must be created to test them. Finally, recommendations for curricular use of the RTOS must be made and a description of how an RTOS fits into co-design must be given.

## **DEDICATION**

This paper is dedicated to my loving wife, Rachelle Pappas, who has given me full support and encouragement on this thesis and to my parents, Greg and Gloria Pappas to whom I owe so much.

#### **ACKNOWLEDGEMENTS**

I would like to thank my family and friends for understanding the importance of what this thesis means to me and for giving me their full support. I would also like to thank my advisor, Dr. Diane Rover, for her support and leadership throughout my project. She has been very flexible and understanding of my work situation and I greatly appreciate it.

I would also like to thank Seth Mosier and Andy Huang for the work on the train simulator that is used in conjunction with my bridge control application.

#### **TABLE OF CONTENTS**

|      |                        | TABLESFIGURES                      |    |

|------|------------------------|------------------------------------|----|

| СНАР | TER 1                  | 1 INTRODUCTION                     | 1  |

| 1.1  | PRO                    | BLEM STATEMENT                     | 2  |

| 1.2  | APP                    | ROACH                              | 3  |

| 1.3  | CON                    | TRIBUTIONS                         | 4  |

| 1.4  | ORG                    | ANIZATION OF THESIS                | 4  |

| СНАР | TER 2                  | 2 BACKGROUND                       | 5  |

| 2.1  | RTO                    | OS INTRODUCTION                    | 5  |

| 2.2  | RTO                    | OS SPECTRUM                        | 8  |

| 2    | 2.2.1                  | 8-bit Processors                   |    |

| 2    | .2.2                   | 16-bit Processors                  | 16 |

| 2    | 2.2.3                  | 32-bit Processors                  |    |

| 2.3  | SUM                    | MARY                               | 23 |

| СНАР | TER :                  | 3 DESIGN & IMPLEMENTATION OF μC/OS | 24 |

| 3. I | INTR                   | ODUCTION                           | 24 |

| 3.2  | TARG                   | GET ARCHITECTURE                   |    |

| 3    | .2.1                   | MC68HC11                           |    |

| 3    | .2.2                   | Handy Board                        |    |

| 3.3  | EVEI                   | OPMENT ENVIRONMENT                 | 31 |

| 3    | 3. <i>1</i>            | Whitesmiths Tools                  | 31 |

| 3    | 3. <i>3</i> . <i>2</i> | Support Tools                      |    |

| 3.4  | ТНЕ                    | RTOS, µC/OS                        |    |

| 3    | 3.4.1                  | Resources                          |    |

| 4    | 1.4.2                  | Tasks                              | 35 |

| 3.4.3         | Communication                                      | 40 |

|---------------|----------------------------------------------------|----|

| 3.4.4         | Interrupts                                         | 43 |

| 3.5 D         | EVELOPMENT CHALLENGES AND SOLUTIONS                | 45 |

| 3.5. <i>1</i> | Task Argument Passing                              | 45 |

| 3.5.2         | Print Services                                     | 49 |

| 3.5.3         | The Debugger Interface                             | 49 |

| 3.5.4         | Simulating Interrupts                              | 50 |

| 3.6 St        | JMMARY                                             | 54 |

| СНАРТЕІ       | R 4 TEST APPLICATION FOR μC/OS                     | 56 |

| 4.1 IN        | TRODUCTION                                         | 56 |

| 4.2 G         | ENERAL SPECIFICATIONS                              | 56 |

| 4.3 E         | NVIRONMENT AND DESIGN                              | 58 |

| 4.3.1         | PC Components                                      | 59 |

| 4.3.2         | Bridge Algorithm                                   | 59 |

| 4.3.3         | Tasks                                              | 60 |

| 4.4 St        | JMMARY                                             | 61 |

| СНАРТЕІ       | R 5 RESULTS                                        | 62 |

| 5.1 IN        | TRODUCTION                                         | 62 |

| 5.2 PI        | ERFORMANCE METRICS                                 | 62 |

| 5.3 C         | 4SE STUDIES                                        | 64 |

| 5.3.1         | Task Communication And Timing Function Application | 64 |

| 5.3.2         | Priority Inheritance Application                   | 66 |

| СНАРТЕІ       | R 6 SUMMARY AND CONCLUSION                         | 69 |

|               |                                                    |    |

| CHARTE        | 2 FUTURE WAR                                       | 70 |

## **LIST OF TABLES**

| Table 1. Real-time interrupt rate for MC68HC11                      | 26 |

|---------------------------------------------------------------------|----|

| Table 2. Handy Board memory map <sup>17</sup>                       | 28 |

| Table 3. Latch control for data bus.                                | 29 |

| Table 4. Stack snapshot, SP begin at 0x8900                         | 46 |

| Table 5. Interrupt bit allocation for CXBD - MC68HC11 <sup>19</sup> | 51 |

| Table 6. Task level context switching example.                      | 54 |

| Table 7. Interrupt context switching example                        | 54 |

## **LIST OF FIGURES**

| Figure 1. Task states.                 | 6  |

|----------------------------------------|----|

| Figure 2. RTEK System Generation Tool  | 19 |

| Figure 3. Handy Board pin out          | 30 |

| Figure 4. Task context.                | 36 |

| Figure 5. Task states for μC/OS        | 38 |

| Figure 6. μC/OS mailbox                | 42 |

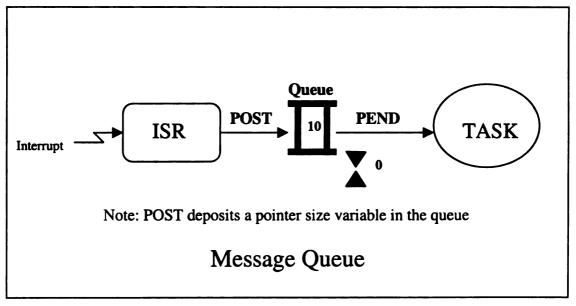

| Figure 7. μC/OS message queue          | 42 |

| Figure 8. μC/OS interrupt handling     | 44 |

| Figure 9. Train track representation.  | 57 |

| Figure 10. PC to Handy Board interface | 58 |

## **Chapter 1 Introduction**

Real-time operating systems (RTOS) live at the core of any system that requires applications to be logically correct and meet real-time constraints. These operating systems support real-time applications and systems via kernel services, task and resource management, and interrupt handling. There are two types of real-time systems, hard and soft.

Hard real-time tasks operate correctly and in a timely fashion<sup>1</sup>. Hard real-time requirements put strict time constraints on the system where the success of its operation hinges on the timeliness of tasks.

Soft real-time requirements have some time constraints but a "best effort" by the tasks to meet their deadlines is sufficient. The real time operating system must support one of these two types of real-time systems.

To support either hard or soft real-time systems, the RTOS must possess a number of capabilities. It must be written efficiently, supporting and optimizing the use of the available hardware. It must have real-time kernel services that aid the application in meeting the real-time requirements. In essence, the RTOS must allow the application to be more abstract, meet real-time requirements and avoid hardware or system details. To accomplish this, the RTOS interfaces the application to resources, interrupts and timing processes. The RTOS provides this interface through kernel services. These services allow the application to concentrate on the specifications of the problem and the design rather than deal with underlying system details.

The application can remain abstract by being broken up into tasks. These tasks can have priorities, communicate among each other and have access to resources. They also have access to the timing services that help meet the application's needs.

Application portability can be maintained by choosing the proper RTOS. Keeping the application abstract leaves the RTOS to handle the system details and provide a standard system interface for the application. Re-writing an application for an RTOS may not be simple but once this has been done, running it on a new system could be trivial. Only the RTOS needs to support the new system and most are written to be portable. This abstraction allows the application to take on new features more easily. It could be as simple as writing a new task or using a resource in a unique way. Also, future designs and upgrades need not be concerned with portability or system interfaces because of a new processor. This is made possible by the fact that RTOS kernel services remain the same while the underlying system may change. Most of the time, a new system or processor means re-working the applications (not written for an RTOS). This often introduces new problems or extends application development time. Thus, an RTOS may also reduce the time to market in an industry where timing, in every sense of the word, is crucial.

#### 1.1 Problem Statement

8-bit and 16-bit microprocessors support increasingly more complex embedded applications and require RTOS support to manage them. This thesis presents the implementation of an RTOS written for the Handy Board, which incorporates Motorola's popular 8-bit embedded microprocessor, the MC68HC11. The MC68HC11 thrives in many of the industries' real-time applications and has many features that fit well with an

RTOS. Many educators have also embraced this processor because of its industrial popularity and wide spread use in educational books and publications.

Also in this thesis, we discuss the tools that aid in the implementation and development process of porting and writing applications for an RTOS.  $\mu$ C/OS by Jean Labrosse is a well-documented and portable RTOS chosen for this thesis<sup>1</sup>. A framework application for a classroom environment at Michigan State University has been developed using  $\mu$ C/OS. This thesis intends to support future labs or assignments on RTOS application development in embedded systems. A course that may have such labs or assignments would be an operating systems class or a computer engineering capstone course on embedded systems. This thesis may also serve as a tool for co-design research involving such tools as POLIS from UC Berkeley<sup>2</sup>.

#### 1.2 Approach

In this thesis, we present how to implement and use an RTOS in an 8-bit embedded environment. Implementing an RTOS such as  $\mu$ C/OS requires the proper tools and RTOS knowledge as well as good programming skills. Research in the RTOS market gives insight to what standard features are used in the development process. For this thesis to be useful in an instructional environment, the expectations of the student and teacher were explored and understood. We present a real-time train application developed for  $\mu$ C/OS and other case studies to demonstration the usefulness  $\mu$ C/OS.

#### 1.3 Contributions

The following lists the contributions of this thesis.

- An implementation of  $\mu$ C/OS for the Handy Board.

- The development of real-time applications with  $\mu$ C/OS.

- An analysis of the features and performance of  $\mu$ C/OS.

- An environment that makes RTOS development part of MSU's real-time systems education and research.

#### 1.4 Organization of Thesis

Chapter 2 gives background information on RTOS technology and the hardware design choices that relate to them. This gives enough information to understand how  $\mu$ C/OS works and what it provides to real-time applications. Chapter 3 discusses all the components of implementing and using  $\mu$ C/OS. Chapter 4 explains the train application written for  $\mu$ C/OS. The results of using  $\mu$ C/OS and a performance analysis of it are given in Chapter 5.

### Chapter 2 Background

#### 2.1 RTOS Introduction

"When used properly, an RTOS changes your design from one of main functions calling lots of subroutines to an event-driven, interrupt-responsive system organized by tasks and time." A transition of an application to tasks that make use of a real-time operating system may not be easy but it will have great benefits.

If an application can be broken into tasks then the RTOS optimizes them for the system and runs them in a multitask environment. Each task may not need continuous use of the CPU allowing other tasks to execute. This may not have been possible in a non-RTOS system because the application lacked any abstraction that would allow for context switching.

Task communication can allow for synchronization of the tasks or provide a data path among them via kernel services such as semaphores, message boxes and queues.

Tasks can also use timing services provided by the kernel to ensure that they meet their real-time specifications or requirements. A task may delay its self for a specified amount of time or obtain the current time. This gives a task some sense of time and allows it to take time intensive action i.e. sounding an alarm at 6:30 A.M. or waiting 30 seconds before attempting to gain access to a printer.

To avoid resource corruption by tasks, the RTOS handles the resources of the system. Two or more tasks may attempt to modify a resource and the RTOS will maintain the integrity of the resource during this process. The RTOS must provide this service in a simple and standard way, allowing the tasks to focus on their true function. Thus, a resource can be shared among tasks without concern for misuse. The main functions of the kernel provide context switching and management of tasks, handling the communication among them.

To accomplish task management, the RTOS must have a scheduler that handles various states of the task. The task states usually consist of the following: Current, Ready, Delaying, Suspended, Timed or Blocked. Figure 1 is an example of how these tasks move among the states.

Figure 1. Task states.

A task begins in the Ready state and the scheduler will allow it to run when the processor becomes available and another task is not deemed worthier based on the scheduling algorithm. Once it begins to run, it may continue until the scheduler decides that it must be moved to one of the other states such as Timed or Suspended. This could occur as part of the scheduling algorithm. The scheduler would move the task to the Timed state because all tasks are time-sliced to run on the processor. A task could be moved to the Suspended state while the RTOS performs some kernel services or handles an interrupt. The scheduler may have nothing to do with changing the state of the task, the task may move itself to a Delayed or Blocked state. The task may need to wait for a given amount of time; thus, changing its state to Delayed. It may also attempt to obtain a resource that another task holds; thus, changing its state to Blocked. The processing of the states must be fast and efficient to keep overhead to a minimum. Scheduling decisions are made based on the priority and state of the task.

An RTOS must implement one of several available scheduling algorithms and chooses one based on the expectations of the kernel. Some of the more advanced algorithms can be event-driven, priority-based, preemptive scheduling or can incorporate a rate monotonic scheme. This is based on the thought that what is required of the real-time software will vary over the lifetime of the system. This scheduling causes lower priority tasks to be preempted when a higher, time-critical task needs to execute and ensures the application performance goals are achieved. Others implement a round robin approach or may still be priority based but not preemptive. Task priorities can either be static or dynamic. Static priorities only have one priority that can not change throughout its life. A dynamic priority based task can be changed during its lifetime.

Priority inheritance can be a crucial feature for resource and task management.

This scheme has the task holding a resource temporarily inherit the priority of any higher

priority task attempting to gain access to the same resource. Without this scheme, schedule problems arise because a task holding a resource may not be scheduled in time for other higher priority tasks to gain access to this resource; thus, preventing the tasks from meeting their real-time requirement. In essence, a lower priority task blocks a higher priority one, entirely contradicting the priority-based scheme. This is often referred to as priority inversion.

It is often important to know whether the kernel supports preemptive scheduling. Preemptive scheduling allow tasks to be interrupted to re-evaluate which task ultimately deserves control of the system. Implementing a preemptive RTOS often results in system overhead but its response time will often offset the overhead. A preemptive RTOS may be the only real choice for many systems and applications with hard real-time requirements. These applications and embedded microprocessors have found their way into electronics devices, appliances, automobiles, industrial control systems and computer network equipment using 8-bit processors and DSP chips.<sup>5</sup>

#### 2.2 RTOS Spectrum

The requirements of the target architecture determine what CPU-board hardware to implement, what software OS vendor to use, and what the architecture of the real-time OS should be for the design.<sup>6</sup> An RTOS interfaces the hardware system to the application to provide a real-time environment. An RTOS can only optimize the use of the hardware components and interface it to the application but its maximum performance limitations lie with the hardware. Many times, the hardware constraints should be considered before looking at the RTOS features because certain processor features such as context switching and interrupt handling are first limited by the hardware

chosen. If the hardware suffices then an analysis of the RTOS kernel becomes the next logical step.

Features supported by most microkernels include fast multitasking, built-in interrupt handling support, and preemptive, non-preemptive or round robin scheduling. It should also provide the application with timing services to aid in meeting the real-time requirements. Memory management is often a good feature to have in an RTOS. Often a quality feature of an RTOS is its ability to dynamically allocate and de-allocate memory.

The microkernel design should minimize system overhead and enable fast responses to external events. It should also provide efficient task communication mechanisms, permitting tasks to coordinate within the real-time system and to external systems. This can be accomplished via mailboxes, message queues and network interfaces. Control of critical system resources is handled via various types of semaphores.

Other RTOS features are related to its implementation. Scalability often becomes important for a range of embedded systems. The scalability of an RTOS allows an application to incorporate only the functionality it requires. Where memory and system resources are limited, some of the RTOS elements may have to be scaled back or eliminated. Other larger and more powerful systems may have the resources to make use of all the available features. Certain applications and systems may require particular kernel services such as a network interface or priority inheritance.

Good development environments help the RTOS to be a success, reducing the time to market. The necessary RTOS development tools include compilers, debuggers, simulators, emulators and other development tools. Compilers and the language used for

the RTOS applications must be accepted by the industry and be in wide spread use by developers. Most developers are familiar with developing with a known processor that can easily be tested and controlled. In embedded systems, this type of environment should be preserved where possible to aid in the development process. These tools should also be processor independent or be able to conform to other processors. The embedded systems industry utilized numerous processors that are required to meet stringent specifications; thus, not only should the tools be processor independent but so should the RTOS. Part of the RTOS must be written for a particular processor but it should be kept to a minimum.

Testing and debugging a real-time system requires special simulators or emulators because the actual system may not be available or does not lend itself to development.

The test environment should match the system closely and allow the developer to take control. The same type of environment should allow the developer access to source code and aid in debugging the application or system.

To continue the development cycle of design, test, debug, and optimize, a tool should be available to optimize the performance of the RTOS and its applications. It should be customizable and intuitive for the developer, who may have a system that requires certain optimizations or run in a non-standard fashion. One such RTOS, DR DOS has an open kernel that allows developers to fine-tune the application as needed. This can be accomplished by keeping to standards such as POSIX 1003.1b real-time extensions (ANSI/IEEE) and by maintaining an open environment for the developer. By conforming to a standard such as POSIX, the developer is free to migrate to various hardware architectures as needed, allowing him/her the option of using off-the-shelf

solutions.<sup>8</sup> Without these environments and tools, the system will be more of a "black box" with limited information of how the system is working. This is unacceptable in a market that demands the "faster-cheaper-better" systems with seemingly impossible deadlines.

These systems may take on different forms, having various specification and expectations. Some systems may have strict speed and heavy resource requirements.

Many of the simpler designs have very minimal requirements, needing only the basic services an RTOS has to offer. The type of processor chosen for a real-time system usually reflects what kinds of features are required from the RTOS. 32-bit processors usually reflect a system that need all the rich features an RTOS has to offer while a 16-bit processor may require only a few and a 8-bit processor the bare minimum.

Architectural differences between 8-bit, 16-bit and 32-bit processors are quite pronounced. The instruction set varies the most among these processors. As the bit width is extended, more instructions can be added that may take advantage of hardware. Also, greater address ranges can be accomplished with greater register width. Computer engineers incorporate all the latest architectural advances in the newer 32-bit processors, leaving 16-bit processors with some of the recent advancements and 8-bit usually with older technology. These advancements affect a processor's performance drastically and new advancements open the door to new embedded applications that may not have been possible a few years ago. For example, many new advanced devices may take advantage of new technology such as speech recognition or image processing that makes use of these 32-bit RTOSs. The following sections discuss other distinctions that may be more relevant to implementing an RTOS.

#### 2.2.1 8-bit Processors

8-bit processors can often help an RTOS be configurable, efficient and stay within a tight budget. On the other hand, these processors can also be limited on several fronts. For these processors, CPU speed remains relatively low. This limits the speed requirements of the application, making features such as multithreading unavailable. For a task to meet its requirements, a task's scheduled uninterrupted time slot must not be too short i.e. tasks may be time sliced in milliseconds. On higher speed processors, the time slot can be shorter because the task can achieve more work in a shorter interval i.e. tasks may be time sliced in microseconds. However, for certain processors and applications, 8-bit processors schedule the tasks adequately and other hardware choices need to be considered.

Often, processor speed does not dictate the choice of a hardware system. For example, 8-bit processors often do not have the same number of internal registers. This makes it difficult for tasks to accomplish much of their work in their scheduled time slot. A task would be forced to use memory more often that is considerable slower than working out of internal registers. Others have improved upon the 8-bit processor, making large internal registers available. As an example the Intel 80386SX and the Motorola (West Austin, TX) 68008 both have an 8-bit external data bus that feeds 32-bit wide internal registers. <sup>10</sup>

Often 8-bit processors do not have the same interrupt handling ability as other more advanced processors. These processors may not have the same number of interrupts that restricts the number of external devices in the system. Also, CPU

response time to interrupts may be a limiting factor for many real-time applications.

Many times an 8-bit CPU's interrupt system suffices and only the RTOS interrupt services need to be evaluated.

Most 8-bit processors have ample timing functions, a feature that the RTOS demands from the hardware. The limitation lies in the resolution of the timers i.e. they may be measured only in microseconds. For some embedded systems, the timer resolution may be adequate and system I/O must be considered.

The nature of embedded systems is often one of heavy I/O. The speed of the I/O device(s) often becomes a driving force in determining the hardware requirements. This device will also determine the width of the data path between it and the processor. Many times, 8-bits processors may not meet this requirement or they may have to rely on other external devices to interface to these devices. Present 8-bit processors may have a need to be maintained because a system has a small board area and low power requirements.

Otherwise, other higher performance processors may be more effective.

Memory requirements often dominate the choice of hardware systems. One of the major limitations of the 8-bit processors is their addressing ability. However, special hardware can expand the addressing range of these processors, as with the MCS51 that expands the addressing limit to 16 Megabyte. Some other processors may be limited to as little as 256 bytes of internal memory. Often the memory consists of not only RAM but also ROM where the RTOS resides. If adding the expanded memory can eliminate this limiting factor, then the RTOS can provide more of its microkernel services. Toshiba, that did implement an expanded memory solution in their 807 family allows for its

processor to reap the benefits of an RTOS's ability to context-switching among tasks or handle ISRs(Interrupt Service Routine) within an RTOS.<sup>11</sup>

8-bit processors have other compelling advantages, at least presently, that make them useful. First of all, they are cheap. This alone is a very compelling reason to use an 8-bit processor. Mass production of embedded systems such as small appliances demand that component costs remain low. In particular, portable devices not only require the parts to be low cost but power efficient. Intelligent, low-powered devices are becoming common place as seen in many handheld computers, mobile phones, pagers, etc. These devices are what driver processors and the hardware they mange to shrink in size and consume less power while maintaining their intelligence.

Finally, most 8-bit processors have proven themselves in the industry. This also implies that many current processors may be upgraded with an RTOS and optimized or improved upon. This already eliminates the need to chose or design hardware, allowing the focus to be on matching the current processor with the appropriate RTOS.

Some engineers desire a low cost 8-bit processor but need better performance.

One vendor has a solution that is a combined 8/16 bit microcontroller, developed by

SGS-Thomson Microelectronics (STM) from their ST9+ core, that provides both the low

cost of the 8-bit MCU's and improved performance with certain functions from their 16bit technology. 12

#### 2.2.1.1 Example RTOS

$\mu$ C/OS is the focus of this thesis and it is a kernel that can be used with 8-bit processors because it is implemented in a small, efficient way without sacrificing many of the critical real-time services. The following is a list of its features.

- Supports the following processors but can be ported to almost any processor:

- AMD's 29K; Hitachi's H8/300H; Intel: ix86 SMALL model, ix86 LARGE model, 80486 Protected Mode with context switching of floating-point regs; MCS-251; Motorola: MC68HC11,68HC16,680x0 and CPU32; Philips: XA MEDIUM model, XA LARGE model; VLSI Technology: ARM; Zilog: Z-80/Z-180

- Event driven operation

- Multitasking preemptive scheduling

- Static and dynamic kernel objects

- Tasks

- Semaphores

- Queues

- Mailboxes

- Timers

- Interrupt Handlers

- Fixed or dynamic task priorities

- Inter-task communication and synchronization

- Semaphores

- Mailboxes

- Oueues

- Timeout options for many services

- Efficient interrupt servicing

- Small RAM and ROM requirements

- Standard programmer interface in C on all processors

#### 2.2.2 16-bit Processors

16-bit processors have limits in some of the same areas as the 8-bit processors but not to the same degree. Most 16-bit processors form a much more powerful system than their 8-bit predecessors. Usually they contain higher speed processors that may accommodate more powerful applications but may be inadequate for certain high performance embedded systems. When a task is scheduled, it can complete a reasonable amount of work within its allocated time slot. Higher speed processors may be able to accomplish a heavier workload in this time but 16-bit processors may be sufficient for many applications.

As with 8-bit processors, speed is not the only consideration in choosing a hardware system. 16-bit processors often have more internal hardware available that can aid in running the RTOS and its applications. More internal general registers are available as well as more timers with higher resolutions. This can accommodate applications that having strict timing requirements. Often other issues are more of a factor. 16-bit processors usually handle interrupts in a sufficient manner. They usually have a sufficient number of interrupts or its response time meets the specifications. As with some 8-bit processors, this is not an issue but it must be known how the RTOS handles the interrupts with respect to microkernel services.

16-bit processors can usually accommodate faster devices with wider data paths.

This eliminates any need for external interfaces for these devices. Limited file systems or other forms of storage may be an option. Still, many of the newer devices have data paths and speed requirements that surpass those available with a 16-bit processor.

16-bit processors have several other advantages. Advancement in chip technology has brought the price of these processors down drastically, making them a viable option to an 8-bit processor. Small, embedded system designs can incorporate 16-bit processors at a marginal cost. They also get more out of the RTOS kernel services and see greater improvement in system performance. The power specifications of 16-bit processors may also meet the requirements of many portable applications. In the past few years, 16-bit processors have been the choice for many applications and can be considered a proven technology. Because many of these processors exist, the only real cost of implementing an RTOS or real-time system environment is software and time intensive. As with its 8-bit predecessor, 16-bit processors may lack the performance of 32-bit processors but may still meet the needs of many real-time applications. Motorola has recognized this and has built the M.Core that reduces power consumption and improves the performance by using the 32-bit architecture and a 16-bit instruction set. 13

#### 2.2.2.1 Example RTOS

Motorola's RTEK Kernel, used in developing real-time applications, is classified as a deterministic, multitasking real-time kernel. <sup>14</sup> Its API (Application Program Interface) supports C and assembly language; thus, kernel services are accessed in a familiar way. The following is a list of its features.

- Supports AMCU microcontrollers products

- Event driven operation

- Multitasking with selectable scheduling methods

- Preemptive

- Round Robin

- Time-Sliced

- Static and dynamic kernel objects

- Tasks

- Semaphores

- Queues

- Mailboxes and Messages

- Memory Partitions

- Exclusive Access Semaphores (Mutexes)

- Timers

- Interrupt Handlers

- Fixed or dynamic task priorities

- Inter-task communication and synchronization

- Semaphores

- Mailboxes and Messages

- Queues

- Timer management

- Timeout options for many services

- Partitioned memory management

- Efficient interrupt servicing

- Fast context switch

- Small RAM and ROM requirements

- Standard programmer interface in C on all processors

- Highly flexible configuration to custom fit the application

RTEKgen is the development tools that handle the host development and downloading of code to the target system. It has many default values for the RTOS such as number of

tasks or creation of semaphores and communication structures. It provides a comfortable GUI to interface the RTOS to the user. Figure 2 gives a snap shot of the RTEK interface.

Figure 2. RTEK System Generation Tool.

#### 2.2.3 32-bit Processors

Most of the advanced embedded real-time systems make use of 32-bit processing technology. Often, these same systems run most of today's desktop computers. They out perform any of the other available 8-bit or 16 bit processors for embedded processing and for hosting an RTOS. 32-bit processors incorporate such features as multithreading and advanced memory management. They can satisfy the most demanding applications.

When a task is scheduled, it completes more work than was previously possible with 8-bit or 16-bit processors. Because of this, more advanced and feature rich tasks can be designed.

Processing speed may not be the only factor, as previously discussed. 32-bit processors have the most internal hardware. They have the highest resolution timers available that can aid in running the RTOS and its applications. For those systems or application that are extremely time sensitive, a 32-bit processor provides the best solution.

These processors usually handle interrupts in the most optimal manner, responding to them quickly and providing excellent interrupt handling. This leaves the RTOS to handle the remaining overhead, such as task management and nested interrupt handling.

A 32-bit processor can handle almost any device with a wide address and data bus. This opens the door to newer devices and new applications. Full file systems may be implemented if the application requires this feature. Other I/O such as networking interfaces may also be part of the design.

The memory constraints of the other systems are not a concern for this 32-bit processor. Almost any kernel service can be implemented with a 32-bit processor, the only impediment may be either financial costs or lack of available development time.

Financial cost is often the major obstacle to using a 32-bit processor, but even this changes with time and many systems with 32-bit processing can be used at a reasonable cost. Some other obstacles include large power requirements and size restrictions. Larger embedded system designs are now incorporating 32-bit processing and maximize the use of RTOS kernel services. 32-bit processors are becoming the *de facto* processor for many embedded applications and most RTOSs support the majority of available 32-bit processors. These 32-bit processors do exist in some embedded systems without an RTOS and integrating one would prove to be beneficial.

#### 2.2.3.1 Example RTOS

VxWorks<sup>TM</sup> of WindRiver Systems leads the RTOS market. One of its more notable applications is NASA's data and control application for its Mars Pathfinder. The following gives a list of the powerful features of VxWorks<sup>TM</sup>.

- Efficient task management

- multitasking, unlimited number of tasks

- preemptive and round-robin scheduling

- fast, deterministic context switching

- 256 priority levels

- Fast, flexible inter-task communications

- binary, counting and mutual exclusion semaphores with priority inheritance

- message queues

- POSIX pipes, counting semaphores, message queues, signals and scheduling control sockets

- shared memory

- Fast, efficient interrupt and exception handling

- Optimized floating-point support

- Dynamic memory management

- System clock and timing facilities

#### **Network Support**

- Complete TCP/IP networking, including Zbuf (No-Copy TCP)

- Communications across various media (Ethernet, serial, backplane, custom)

- Sockets

- Remote login (rlogin, telnet)

- Remote Procedure Calls (RPC)

- Network File System (NFS) client & server

- File Transfer Protocol (ftp/tftp client & server)

- Remote command execution (rsh)

- BOOTP booting protocol

- SNMP (MIB-II support)

- STREAMS

#### Fast, Flexible I/O and Local File System

- Complete portable I/O system

- POSIX asynchronous I/O and directory handling

- SCSI support

- Extended MS-DOS and RT-11 file systems

- Raw disk file system

#### **Target Development Features**

- Full ANSI C compliance and C++ support

- Extensive POSIX 1003.1, .1b compatibility

- Interactive, C-interpreter target shell

- Symbolic debugging and disassembly

- Powerful performance monitoring

- Extensive kernel, task, and system information utilities

- Dynamic linking loader

- Libraries of over 1100 utility routines

- Flexible booting from ROM, local disk or over the network

- Highly scalable design allows for wide range of applications

Another advantage of VxWorks<sup>TM</sup> is its modularity and scalability. This allows the RTOS to be tailored for a system with unique specifications or constraints. It does so by keeping the design of the kernel layered, adding the support modules as needed.

It also has a rich set of development tools designed around a host/target environment, using the Object Oriented C++ language for development. Host-based tools included with VxWorks<sup>TM</sup> are a cross-compiler along with a powerful remote source-level debugger VxGDB<sup>TM</sup>. Target tools include an interactive C-interpretive shell and linking loader for prototyping, as well as libraries of over 1100 utility routines. Optional VxWorks<sup>TM</sup> accessory products include VxVM?<sup>TM</sup> for virtual memory interface, VxMP<sup>TM</sup> for multi-processing and VX-Windows for graphics support. Optional WindPower<sup>TM</sup> host-based tools include the WindView<sup>TM</sup> real-time dynamic system visualizer, the StethoScope real-time data monitor, WindC++ TM (including the popular iostreams class library), WindC++ Gateway for ObjectCenter, and the VxSim<sup>TM</sup> simulator.

#### 2.3 Summary

A powerful RTOS is the key to a successful real-time system. It makes use of proven hardware with a well-designed and re-useable real-time kernel. This eliminates the need for development time and money toward building a custom operating system. Often these commercial operating systems meet very high standards due to the immense competition and stringent requirement of real-time systems. They far surpass the quality of many desktop operating systems.

Yet many engineers that don't develop an operating system for the desktop feel they must develop their own RTOS. In the past there has been no alternative and applications were not as sophisticated. However, widely available and high quality RTOSs can now be incorporated into these complex embedded designs. The trend is shifting to designers using an RTOS to develop more complex applications. <sup>15</sup> The task

may be a daunting one for those that have to port over an entire system and it may not be practical to use an RTOS. For those that build a new system or re-design is possible, an RTOS is a great way to improve and optimize their real-time system. Most vendors attempt to aid in this process by developing user-friendly development tools and provide turnkey design solutions for these complex embedded applications. <sup>16</sup>

A RTOS aids in designing and building new systems that have real-time requirements or optimizing and enhancing existing real-time systems. Implementing these systems only requires that application specifications fit well with the hardware and appropriate RTOS kernel services.

## Chapter 3 Design & Implementation of $\mu$ C/OS

#### 3.1 Introduction

We present the implementation details of  $\mu$ C/OS and how it was ported to the Handy Board. We explain some of the reasoning behind both our hardware and software choices related to the implementation. A more in depth explanation of what the Handy Board consists of and what the MC68HC11 processor has to offer is also discussed. The development environment is presented as well. It was a key in porting  $\mu$ C/OS and developing its applications.

#### 3.2 Target Architecture

The MC68HC11 serves as the target architecture for this thesis and the Handy Board's system incorporates this processor into a more useful system. This processor is widely used in MSU engineering labs and in products throughout the embedded industry; thus, implementing  $\mu$ C/OS for this processor has merit and usefulness. Implementing  $\mu$ C/OS for the Handy Board, which incorporates the MC68HC11, will help to bring a real-time development environment to the MSU engineering labs.

#### 3.2.1 MC68HC11

The MC68HC11's 8-bit embedded architecture has proven to be a solid design in the embedded industry; thus, using  $\mu$ C/OS for the MC68HC11 is industry motivated. Many robotic and control applications could make use of the real-time kernel services. Some of the features that make the MC68HC11 a well-suited embedded controller are its timer functions, prioritized interrupts, digital ports and on-board A/Ds.

The MC68HC11's real-time interrupt capabilities provide  $\mu$ C/OS with a periodic interrupt that  $\mu$ C/OS uses to schedule tasks. The RTI (Real-Time Interrupt) is based off the MC68HC11's crystal of 8.0 MHz (E = 2.0 MHz) and can be configured for various interrupt periods (see Table 1 for listing of rates). It ranges from 4.10 to 32.77 millisecond interrupt rates and is selected by two bits in a control register for the RTI.

A fast rate may cause too much system overhead and not allow a task to complete a reasonable amount of work. On the other hand, not interrupting often enough may affect the timeliness of the application. A reasonable rate of 8.19 milliseconds allows the task to execute approximately 1700 lines of C code( assumed average of 3 assembly instructions per line of C code and each instruction takes 3 cycles), a good amount of work for most tasks.

Table 1. Real-time interrupt rate for MC68HC11

| RTI Con | ntrol Bits<br>RTR0 | Rate is E<br>divided by | Interrupt Period (in milliseconds for 8.0 MHz crystal) |

|---------|--------------------|-------------------------|--------------------------------------------------------|

| 0       | 0                  | 213                     | 4.10                                                   |

| 0       | 1                  | 2 <sup>14</sup>         | 8.19                                                   |

| 1       | 0                  | 2 <sup>15</sup>         | 16.38                                                  |

| 1       | 1                  | 216                     | 32.77                                                  |

The MC68HC11 saves the context of the processor during an interrupt by storing the register to where the SP (Stack Pointer) points. Upon return from the interrupt the registers are restored from the SP location. The  $\mu$ C/OS scheduler is aware of this process and uses it to save and restore the tasks' context.

The MC68HC11 provides a built-in serial interface. To begin using, it only needs to be enabled and set to the proper baud rate via a serial configuration register. The serial interface can be used to debug and developing code through *printf()* statements. It may also be used to communicate with other devices that are part of the real-time design.

All register and ports within the MC68HC11 are memory mapped. External devices may also be memory mapped if they have access to the processor's data bus, as with the Handy Board. This allows for easy access to external devices and configuration of the MC68HC11.

## 3.2.2 Handy Board

The MC68HC11 by itself is a useful and prominent component in the embedded systems industry but it not a complete system. The Handy Board incorporates the processor into its design giving the MC68HC11 added value. The following is a list of Handy Board features.

- socketed 52-pin 6811

- 32K battery-backed static RAM that is rechargeable

- digital input latch

- digital output latch driving two L293 chips

- 14-pin LCD interface

- two user pushbuttons

- powered/polarized individual sensor connectors

- 40 kHz IR output drive

- one servo motor output

- External Serial Card for easy access to serial communications. It communicates with the Handy boards on board serial interface through a standard telephone wire.

- LCD Display

Table 2 gives the memory map that allows the Handy Board to communicate to the outside world. First, the data bus is made available via memory mapped address ranging from \$4000-6fff. Second, other interfaces exist to facilitate expanded memory and motor control. Also, the MC68HC11's registers are memory mapped. Finally, the MC68HC11 interrupt vector bank is located at \$bfc0 to \$bfff for the Handy Board rather than the normal range of \$ffc0 to \$ffff.

Table 2. Handy Board memory map<sup>17</sup>

| Device                 | Location                                         | Notes                                                                                                                                                                                                              |

|------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6811 internal RAM      | \$0000-\$00ff (A1chip)<br>\$0000-\$01ff (E1chip) | Built-in                                                                                                                                                                                                           |

| 6811 control registers | \$1000-\$103f                                    | Built-in                                                                                                                                                                                                           |

| Expansion I/O Bank 0   | \$4000-\$4fff                                    | Memory reads in this range enable the Y1 latch selector, present on the HB Expansion Bus. Memory writes in this range enables the Y0 selector on the Expansion Bus. No devices are present on a stock Handy Board. |

| Expansion I/O Bank 1   | \$5000-\$5fff                                    | Reads enable Y3; writes enable Y2. See explanation above.                                                                                                                                                          |

| Expansion I/O Bank 2   | \$6000-\$6fff                                    | Reads enable Y5; writes enable Y4. See explanation above.                                                                                                                                                          |

| Digital inputs         | \$7000-\$7fff                                    | The digital inputs consist of the two switches and sensor ports 10 through 15. A memory read from anywhere in this range returns the value of the digital input byte from the data bus.                            |

| Motor outputs          | \$7000-\$7 <del>fff</del>                        | A memory write to anywhere in this range controls the motor outputs. The low four bits are motor direction, and the high four bits are motor enable (1=on).                                                        |

| External RAM           | \$8000-\$ffff                                    | The 32K of battery-backed memory is mapped to the upper 32K block of the 6811 address space.                                                                                                                       |

The Handy Board pin out is represented in Figure 3 and lays out the MC68HC11 interface. The Y0-Y1 pins control external latching of the data bus, D0-D7. The latch is controlled as depicted in Table 3. For example a read from address \$4000 will bring

The Y0-Y1 pins control external latching of the data bus, D0-D7. The latch is controlled as depicted in Table 3. For example a read from address \$4000 will bring R/W' low and will set Y0. Setting Y0 could trigger an external latch to latch in data from an external device.

Table 3. Latch control for data bus.

| R/W' | Address Range | I/O | Latch selector |

|------|---------------|-----|----------------|

| 0    | \$4000-\$4FFF | O   | Υ0             |

| 1    | \$4000-\$4FFF | I   | Y1             |

| 0    | \$5000-\$5FFF | O   | Y2             |

| 1    | \$5000-\$5FFF | I   | Y3             |

| 0    | \$6000-\$6FFF | 0   | Y4             |

| 1    | \$6000-\$6FFF | I   | Y5             |

| 0    | \$7000-\$7FFF | O   | Y6             |

| 1    | \$7000-\$7FFF | I   | Y7             |

## 3.3 Development Environment

The design environment consists of the Whitesmiths tools, CodeWright and Telix.

These tools provide reading, modifying and processing of application source code. They provide an interface to debug the application and for communication via a serial port.

### 3.3.1 Whitesmiths Tools

The DOS-based Whitesmiths tools cross compile, link and load into the processor the  $\mu$ C/OS kernel and its applications. These tools handle the entire process of taking the source code in standard ANSI C to the necessary Motorola S-record format (the ASCII format downloaded to the processor). These tools also provide a debugger to aid in the development process.

### 3.3.1.1 Compiler and Linker

The compiler is the key in converting the RTOS source code into object form for conversion into machine language. In this case, it represents a key aspect in how the RTOS functions. The compiler places pointers to ISR functions into the vector table. This is often done via *extern* definitions of the functions that the programmer defines in another source file, in this case the  $\mu$ C/OS source code.

The compiler defines how functions are called and how arguments are passed down to them. This is important when porting the RTOS because when context switching or scheduling a task, the RTOS must emulate how the compiler would normally operate.

The RTOS must be concerned about stack usage because many compilers use a stack to store local variable and pass arguments. The stack represents the context of the processor or task and the stack must be preserved during scheduling and context switching. The compiler also provides an assembly language interface for the RTOS to controller the processor where high level code is inefficient or inadequate.

### 3.3.1.2 Debugger

The Whitesmiths' debugger provides much insight in porting  $\mu$ C/OS and developing its application. When the compiler produces code, it may also produce extra information for debugging. CXDB, the Whitesmiths' debugger, uses this information to create a simulated environment that allows the developer to dissect and analyze the RTOS and application code. It allows the programmer to step through routines, check that the status of tasks (by reading the Task Control Block structure variable in  $\mu$ C/OS), and simulate I/O or interrupts via memory reads and writes. This can be done at the high level, C source code, or the low level, assemble code. This gives the developer insight into the application and allows him/her full control of it.

## 3.3.2 Support Tools

A simple COM port program, Telix, provided an interface to the Handy Boards serial interface. Telix captures all data from the serial port and engineers can make use of *printf()* functions to develop and debug an application.

CodeWright provides a customizable editor to modify the source code for the applications and  $\mu$ C/OS. This may not seem important, but a good editor can save time and make a programmer feel more comfortable reading and modifying source code.

## 3.4 The RTOS, µC/OS

This kernel had originally been designed specifically for the 8-bit processor but is capable of running on other higher performance processors. Certain portions of the  $\mu$ C/OS are done in Motorola assembly but it is kept to a minimum to maintain the RTOS's portability.  $\mu$ C/OS only requires that the processor have a stack and its registers be available. It also provides many of the essential kernel services that help maintain a real-time environment. It implements the core features of many RTOSs. We present  $\mu$ C/OS in this section beginning with its handling of system resources. We then discuss how  $\mu$ C/OS manages its tasks and the communication among them. Interrupt handling is discussed and we finish with the performance of the kernel services.

#### 3.4.1 Resources

Real-time systems contain many resources that various applications require in order to complete their work. This can range from I/O devices to abstract concepts such as shared arrays. Shared resources are available to all tasks or a subset of tasks and must be managed to avoid corruption or other problems that may include dead lock. Deadlock will occur when two tasks hold a resource the other needs in order to continue and each will wait indefinitely for the needed resource. <sup>18</sup>

Semaphores provide a method by which tasks can synchronize or gain access to a resource. Once the semaphore is obtained, the task can continue executing. Two types of semaphores can be used. Binary semaphores follow the key/lock concept. This allows a task to gain access to resources. Once a semaphore for a given resource is obtained by a task its state transfers to the locked state. Any other task attempting to obtain the semaphore for that resource will see that it is locked and wait for it to be unlocked. Thus, the semaphore has a binary value or state of lock or unlocked.

Counting semaphores goes beyond the idea of binary semaphores and provides multiple valued semaphores. Its size is determined by its bit width i.e. an 8-bit semaphore would have 256 possible values. Tasks that attempt to use the semaphore when its value is zero are put on a priority waiting list under  $\mu$ C/OS. On the other hand, if the semaphore is positive then the resource is made available. When the semaphore becomes available,  $\mu$ C/OS schedules the highest priority task and decrements the semaphore. When the task releases the semaphore the scheduler increments the semaphore's value.

### 3.4.2 Tasks

$\mu$ C/OS defines a task to be similar to a thread but the task is an independent process. A thread often resides within a process, sharing control of allocated memory and resources. A task, like a thread, must be concerned about resources that may be shared among tasks. It can also synchronize with other tasks, much like threads. Tasks are different in that they do not automatically inherit any resource as threads do. Threads are often time sliced where tasks, in  $\mu$ C/OS, are priority-based. It is up to the designer to assign these priorities based on the needs of the application.

## 3.4.2.1 Task Priority

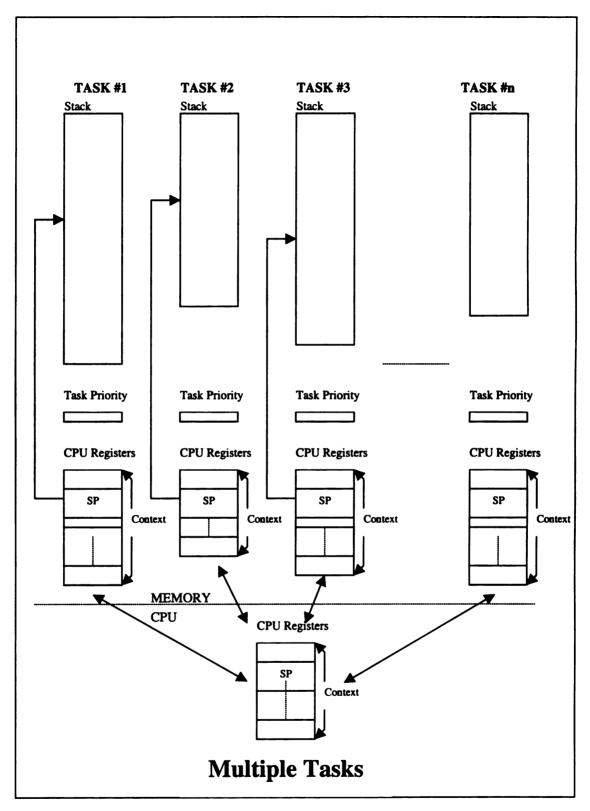

The priorities within  $\mu$ C/OS are unique, no two tasks can have the same priority. The highest priority matches the numerically lowest priority number; thus, the highest possible priority is "0" and the lowest "63". This gives the application 63 possible tasks to accomplish its goals, the last priority is usually reserved for the "idle" task. The "idle" task runs when all other tasks are inactive for whatever reason and  $\mu$ C/OS needs a task to fill the time slice until another task is ready to run. The context of each task entails the current CPU registers, its own stack and a priority. A task can be static or dynamic in nature. It can be statically assigned a priority on creation and can not change.  $\mu$ C/OS allows the priority to change during execution making it a dynamic priority. Figure 4 illustrates the task context within  $\mu$ C/OS.

Figure 3. Task context.

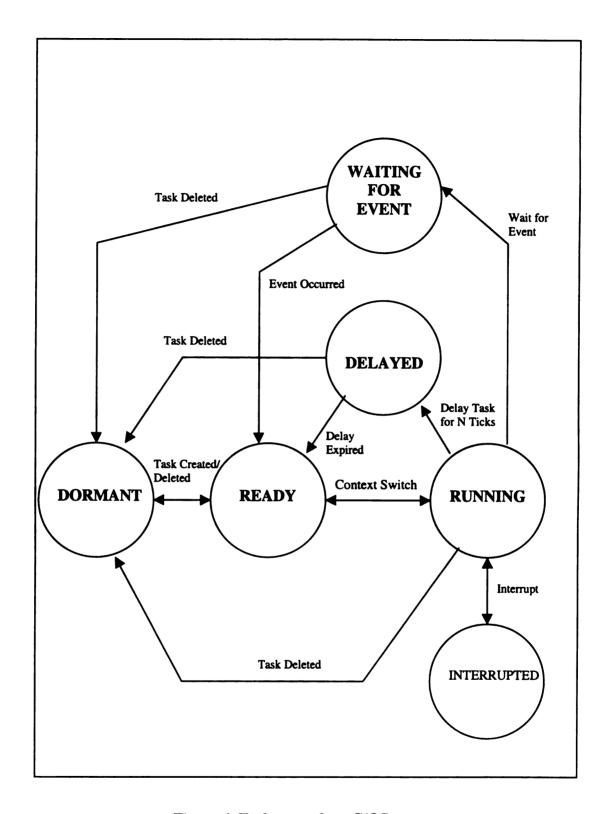

### 3.4.2.2 States

To implement these tasks in a multitasking environment requires that each task be assigned a particular state. The possible states of a task are Dormant, Ready, Running, Delayed, Waiting For An Event or Interrupted. If a task's state is Dormant, it is not ready to take control of the CPU and the kernel has not made the task available to run. A task in the Ready state wants to take control of the CPU. The kernel will allow it as soon as the current tasks with higher priorities are not scheduled to execute. The Delayed state translates to a task that has suspended itself for a period of time. If a task is in the Waiting For An Event state it will not execute or attempt to execute until a particular event has occurred such as a semaphore becoming available or a message resides in a mailbox, etc. Lastly, the Interrupted state occurs when a task looses control because of an interrupt that must be serviced. Figure 5 shows the flow among task states.

Figure 4. Task states for  $\mu$ C/OS

Figure courtesy of Jean J. Labrosse,  $\odot$  R & D Publications, 1992. All rights reserved

### 3.4.2.3 Task Control Blocks

Because  $\mu$ C/OS incorporates a preemptive scheduling algorithm it must keep track of the task control information. This is accomplished via a structure called the Task Control Block (TCB). This contains all the necessary information to suspend or interrupt a task and to bring it back into execution. The TCB is a table with entries that keep track of the state of the task, priority and stack information and TCB control management fields such as previous and next entries. This aids in the scheduling process of the tasks. The "idle" task created by  $\mu$ C/OS is also placed in the table. The kernel keeps track of available entries for new tasks and manages the deletion of tasks from the table.

## 3.4.2.4 Task Scheduling

A preemptive, priority-based scheduling algorithm is implemented by  $\mu$ C/OS. The kernel determines the highest ready-to-run task and executes it. All other tasks are scheduled based on their given priorities. This type of scheduling better matches real-time applications because system response is higher. The current task will be preempted to allow a higher priority task immediate access to the processor. Thus, the higher priority tasks have a better chance of meeting deadlines specified for the real-time application. This creates a more deterministic system.

Extra care must be taken with this design because shared functions, data and resources can be corrupted when a task is preempted and returns to execution. For example, a task could be operating on a global variable when it is preempted. It will assume the value has not changed when it begins execution. However, while it is preempted, another higher priority task may manipulate the very same global variable causing data corruption. One can maintain the integrity of shared resources via semaphores.

## 3.4.3 Communication

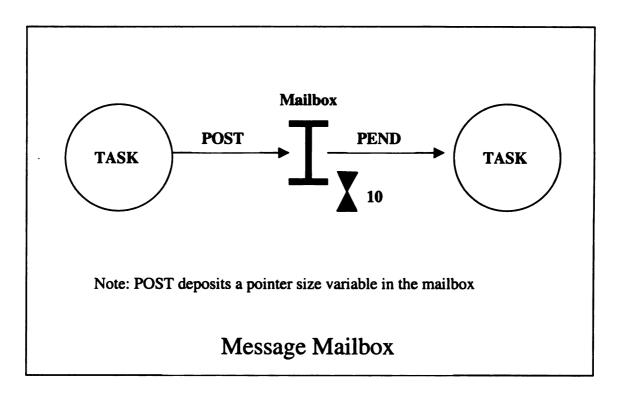

Frequently, tasks need to communicate among themselves. The kernel services should provide the vehicle to communicate.  $\mu$ C/OS provide this service via mailboxes and queues. Both are consider events that a task triggers via a POST or waits for the event via a PEND. When a task PENDs,  $\mu$ C/OS puts the task on a priority waiting list similar to the semaphore list. When the event occurs, the highest priority task in the list takes control of the processor and retrieves the message from a mailbox or queue.

### 3.4.3.1 Event Control Block

$\mu$ C/OS uses a structure similar to the TCB called the Event Control Block to control mailboxes, queues and semaphores. It is used in scheduling tasks for the various events such as scheduling the next task for an available semaphore.

#### 3.4.3.2 Mailboxes and Queues

Mailboxes contain messages POSTed by other tasks. The application defines what type of message resides in the mailbox and other tasks that use the message must be aware of the type. For example, if a character based message is stored by one task all others must be aware that the message is character based when they retrieve it. μC/OS provides the kernel services to create a mailbox, PEND to the mailbox and POST to it. ISRs must never make calls to these services because an ISR does not have the required task information i.e. they cannot be put on a priority waiting list. A timeout can be specified when waiting for the event, but an application can specify that it will wait indefinitely. The mailbox can only contain one message at any given time and an error will occur if this is violated.

$\mu$ C/OS implements queues to extend the mailbox concept. A queue can contain multiple messages and operates as a standard queue with a FIFO (First-In First-Out). Tasks manipulate queues in a similar fashion as mailboxes with a creation function and POST/PEND functions.  $\mu$ C/OS manages the tasks as it did for mailboxes but allows multiple POSTs to the queue. Figures 6 and 7 illustrate the flow of mailboxes and queues.

Figure 5.  $\mu\text{C/OS}$  mailbox Figure courtesy of Jean J. Labrosse,  $\circledcirc$  R & D Publications, 1992. All rights reserved

Figure 6.  $\mu$ C/OS message queue

Figure courtesy of Jean J. Labrosse, © R & D Publications, 1992. All rights reserved

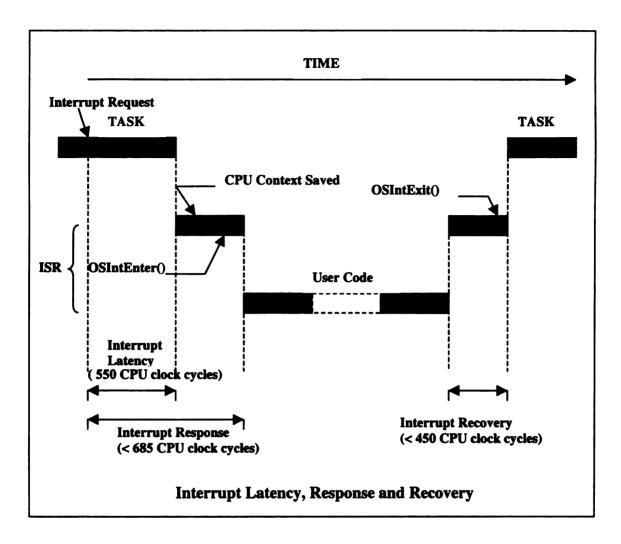

## 3.4.4 Interrupts

Interrupt handling often requires an assembly language interface and is handled by an ISR. Applications often require fast interrupt response and handling, but this depends on the specific architecture of the processor. Writing the ISR that interface to the RTOS in the assembly language of the target processor can greatly increase interrupt response time. When an interrupt occurs, the current task context must be saved and other interrupt handling overhead will be incurred such as re-scheduling.

The scheduler makes use of one of the processor's periodic interrupts for a system clock. This allows for periodic re-scheduling of the tasks i.e. multitasking. The system designer can optimize the frequency of this periodic interrupt so that the tasks complete their work while meeting their deadlines.

An 8-millisecond interrupt was implemented to act as  $\mu$ C/OS's periodic interrupt for scheduling the tasks.  $\mu$ C/OS does not handle this interrupt as it does other interrupts. It performs a software context switch as opposed to a typical interrupt context switch.  $\mu$ C/OS expects this interrupt and knows the state of the system when this interrupt occurs. Other interrupts can occurs at more random or unexpected times and the interrupt handling mechanism must reflect it.  $\mu$ C/OS uses this periodic interrupt to provide timing services such as its delay and clock functions. Figure 8 reflects how  $\mu$ C/OS handles interrupts.

Figure 7.  $\mu$ C/OS interrupt handling

Figure courtesy of Jean J. Labrosse, © R & D Publications, 1992. All rights reserved

## 3.5 Development Challenges and Solutions

The following sections discuss some of the challenges that arose from porting  $\mu$ C/OS to the MC68HC11. The following sections have been included to facilitate better use of  $\mu$ C/OS and to avoid possible pitfalls or problems when re-porting  $\mu$ C/OS to another processor.

## 3.5.1 Task Argument Passing

Tasks are initialized in  $\mu$ C/OS upon creation by parameters that are passed to it as arguments. The argument to the task function had been invalidated due to  $\mu$ C/OS's assumptions about how the compiler passed arguments for the MC68HC11. This problem was observed by attempting to print the parameter passed into the task. The argument is passed a void pointer parameter in order to accommodate all data types; thus, by default it is passed by reference. This adheres to the ANSI C language standard but is handled by a processor dependent process. This process determines how the pointer is stored in memory and passed to functions.

The main() function calls a TaskCreate() function for each task. This sets up the individual tasks stack, priorities and all other TCB information including the task's initial parameters. Argument passing is processor dependent in the sense that the compiler uses different architectural features to pass parameters, handle variables and other language details; thus, setting up  $\mu$ C/OS and its tasks involves understanding how the compiler operates.

For the MC68HC11, the Whitesmiths tools compiler passed arguments by reference in the 'D' register. This register consists of the 'A' and 'B' accumulators. The 'A' accumulator is in the high order byte and 'B' in the low order. Each task has an associated stack that holds the argument and context of the task. Part of the context of the task is the value of the accumulators and PC (Program Counter) that includes the 'A' and 'B' accumulators. These two accumulators are 8-bits wide and together they form a word, while the other accumulators and the PC are 16 bits wide; thus, when the stack is being set up with its data (arguments), it is done so in word fashion as shown in Table 4. The following code segment assigns the stack pointer to the argument.

\*stk = pdata; where stk currently points to the beginning address of 'A' and pdata is the argument.

Table 4. Stack snapshot, SP begin at 0x8900.

| Stack locat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ion. Memory | Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|