19 G

# LIBRARY Michigan State University

This is to certify that the

dissertation entitled

## EFFICIENT TESTABILITY DESIGN METHODOLOGIES FOR ANALOG/MIXED-SIGNAL INTEGRATED CIRCUITS

presented by

Cheng-Ping Wang

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Electrical Eng

Cheques

Major professor

Date Soptember 25, 97

MSU is an Affirmative Action/Equal Opportunity Institution

0-12771

# PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due. MAY BE RECALLED with earlier due date if requested.

| DATE DUE | DATE DUE | DATE DUE |

|----------|----------|----------|

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

1/98 c/CIRC/DateDue.p65-p.14

# EFFICIENT TESTABILITY DESIGN METHODOLOGIES FOR ANALOG/MIXED-SIGNAL INTEGRATED CIRCUITS

Ву

Cheng-Ping Wang

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of requirements

for the degree of

**DOCTOR OF PHILOSOPHY**

Department of Electrical Engineering

1997

#### **ABSTRACT**

### EFFICIENT TESTABILITY DESIGN METHODOLOGIES FOR ANALOG/MIXED-SIGNAL INTEGRATED CIRCUITS

By

#### Cheng-Ping Wang

More and more mixed-signal devices are being designed recently for the applications of multimedia, wireless communication, and portable data systems. The analog circuit technology conventionally employed for such applications has been gradually switched to analog/digital mixed-signal circuit technology. Even though much more complicated digital circuits have been widely used in the DSP-based mixed-signal IC, analog circuits will remain for processing or interfacing analog signals. Integrating both digital and analog on a single chip has improved performance and reduced board size and cost. However, the increasing complexity of mixed-signal circuits drastically reduces the controllability and observability of the circuit on the chip. As a result, testing of such complex circuit becomes very difficult and expensive. Therefore, the goal of the thesis study is to develop an efficient testability design system for analog/mixed-signal circuits so that all designed circuits are easily testable.

The thesis study has developed efficient testability design methodologies and testability enhancement methodologies. The developed design methodology defines a set of fault types from circuit layout, technology data, and process defect distribution, and it generates a set of test vectors based on the parameter deviation bounds which are derived from the design specification, discrete input set, and defined fault types. The test vectors and parameter deviation bounds allow us to evaluate the fault coverage of a designed analog circuit. This methodology was developed using the inductive fault analysis (IFA) technique. However, the IFA technique requires a tremendous amount of computational time and thus it has been limited for small circuits. For reasonable large analog circuits, a hierarchical testability design methodology is developed to reduce the computational complexity. Basically, a designed circuit is decomposed into many components. The components can be further decomposed until they can be handled comfortably by the IFA technique. In other words, a circuit is decomposed as primitive cells and/or macros.

Based on the hierarchical fault macromodeling process, a hierarchical testability design system, namely, PETOMIC (Packages for Enhancing Testability Of Mixed-signal Integrated Circuit) is also developed. The system generates cell library, macro library, test set, and evaluates the fault coverage. The system has been developed and implemented in C language, Spice, and Matlab. The detail system development is discussed with examples of generating a cell library of an Opamp and a macro library of a current copier.

Some testability enhancement methodologies have also been developed in this study. Based on the given design specifications, a set of discrete inputs used for design verification, and the fault types, a set of testability design rules is developed to ensure the existence of the circuit parameter deviation bounds for these discrete inputs and for all fault types. These parameter deviation bounds are used to generate test vectors. Thus, the designed circuit can be easily testable. In addition, a high-accuracy current comparator is developed as a built-in tester (BITER). The use of BITER not only enhances the testability, but also simplifies the test generation process and reduces the test sequence length.

To my parents, brother and his wife.

#### **ACKNOWLEDGEMENTS**

I sincerely thank Professor Chin-Long Wey, my thesis advisor, for his support and valuable suggestions throughout this research. It has been a pleasure to work under his supervision and I have certainly learn a lot from him. I would also like to express my gratitude to the members of my guidance committee, Dr. James Resh, Dr. Gregory Wierzba and Dr. Chien-Peng Yuan, for taking time to serve in the committee.

I have to thank my fellow graduate students, Wei-Hsing Huang and Jin-Sheng Wang. I got much inspiration from the discussion with them.

A special thanks goes to my parents, my brother and his wife for the support and encouragement they have given me during the critical stage of my life.

A final note of appreciation must be sent to all the nice people who have ever enriched my campus life while I stayed in Michigan State University.

#### **TABLE OF CONTENTS**

| LIST OF T | ABLE | s                                                   | viii |

|-----------|------|-----------------------------------------------------|------|

| LIST OF F | IGUR | ES                                                  | ix   |

| Chapter 1 | INT  | RODUCTION                                           | 1    |

| -         | 1.1  | Objectives and Research Tasks                       | 6    |

|           | 1.2  | Thesis Organization                                 | 9    |

| Chapter 2 | BAC  | CKGROUND                                            | 11   |

| -         | 2.1  | Fault Definition                                    | 11   |

|           | 2.2  | Test Generation of Switched-Current Circuits        | 14   |

|           |      | 2.2.1 Switched-Current Circuits                     | 14   |

|           |      | 2.2.2 Structures and Operations                     | 15   |

|           |      | 2.2.3 Fault Behaviors and Test Generation of an ADC | 20   |

|           | 2.3  | Analog/Mixed-Signal Testing Schemes                 | 23   |

|           |      | 2.3.1 Design-for-Testability Techniques             | 23   |

|           |      | 2.3.2 BIST Designs                                  | 27   |

| Chapter 3 | FAU  | LT MACROMODELING                                    | 30   |

|           | 3.1  | Fault Types in Switches                             | 31   |

|           | 3.2  | Heuristic Fault Macromodeling Process               | 35   |

|           |      | 3.2.1 Example Circuit - Current Copier              | 36   |

|           |      | 3.2.2 Example Circuit - ADC                         | 42   |

|           |      | 3.2.3 Discussion                                    | 49   |

|           | 3.3  | IFA-Based Fault Macromodeling Process               | 50   |

|           |      | 3.3.1 Fault Classification                          | 50   |

|           |      | 3.3.2 Testability Design Rules                      | 56   |

|           |      | 3.3.3 Test Generation and Fault Coverage            | 60   |

|           |      | 3.3.4 Example                                       | 61   |

|           | 3.4  | Discussion                                          | 72   |

| Chapter 4 | TES  | TABILITY ENHANCEMENT                                | 74   |

| =         | 4.1  | Hierarchical IFA-Based Fault Macromodeling          | 74   |

|           |      | 4.1.1 Macro Library                                 | 76   |

|           |      | 4.1.2 Fault Coverage Estimation                     | 82   |

|           | 4.2  | Testability Design Rule                             | 87   |

|           |     | 4.2.1 Development                       | 88  |

|-----------|-----|-----------------------------------------|-----|

|           |     | 4.2.2 Discussion                        | 91  |

|           | 4.3 | High-Accuracy Built-In Tester           | 91  |

|           |     | 4.3.1 Design and Operation              | 94  |

|           |     | 4.3.2 Simulation Results                | 98  |

|           |     | 4.3.3 Performance Analysis              | 104 |

|           |     | 4.3.4 Built-In Tester and Test Sequence | 108 |

| Chapter 5 | HIE | RARCHICAL TESTABILITY DESIGN SYSTEM     | 111 |

| •         | 5.1 | CLG_Routine                             | 111 |

|           | 5.2 | MLG_Routine                             | 128 |

| Chapter 6 | CON | NCLUSION                                | 137 |

| •         | 6.1 | Summary                                 | 137 |

|           | 6.2 | Future Work                             | 139 |

| APPENDIC  | ES  |                                         | 141 |

| REFERENC  | CES |                                         | 166 |

#### LIST OF TABLES

| Table 2.1 | Fault types and expected outputs.                                       | 2  |

|-----------|-------------------------------------------------------------------------|----|

| Table 3.1 | Defect and fault count distributions.                                   | 69 |

| Table 3.2 | Defect and fault count distributions. (With inaccurate test instrument) | 70 |

#### LIST OF FIGURES

| Figure 1.1 | Schematic diagram of a typical DSP-based mixed-signal IC                                                                                 | 2  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2 | Single stuck-at-fault-model-based testing in digital circuit                                                                             | 4  |

| Figure 1.3 | Broad view of this thesis study.                                                                                                         | 7  |

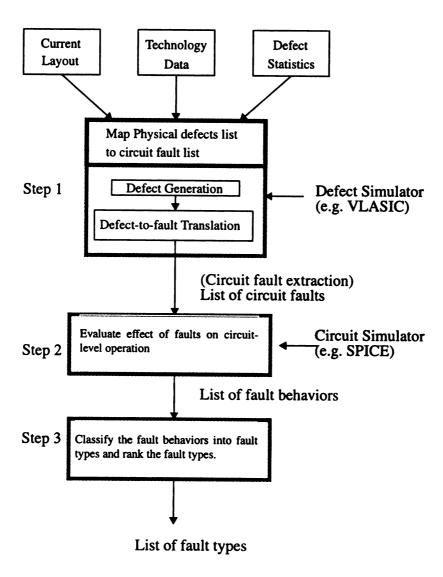

| Figure 2.1 | Inductive fault analysis.                                                                                                                | 13 |

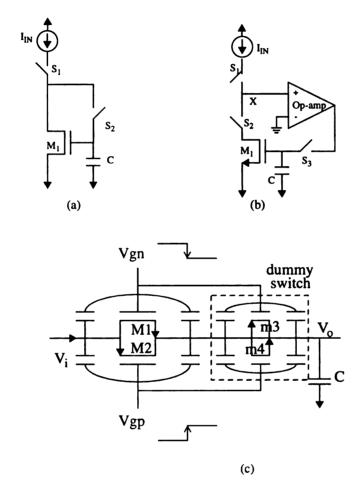

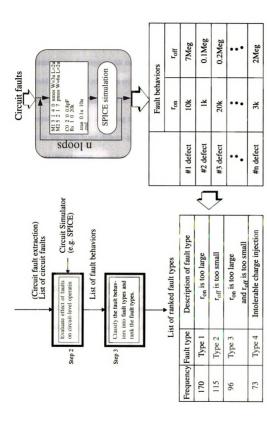

| Figure 2.2 | Current copier: (a) basic copier; (b) with feedback amplifier; and (c) CMOS switch with a dummy switch.                                  | 16 |

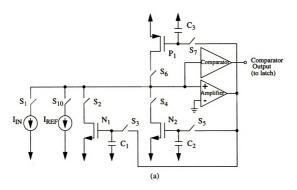

| Figure 2.3 | An SI algorithmic ADC: (a) schematic diagram; and (b) simulation results.                                                                | 18 |

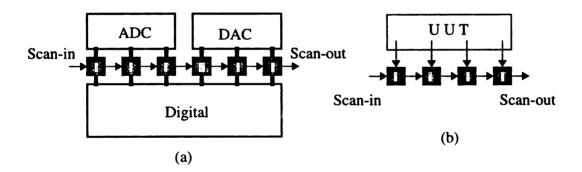

| Figure 2.4 | DSP-based IC with scan structures.                                                                                                       | 24 |

| Figure 2.5 | Test bus.                                                                                                                                | 26 |

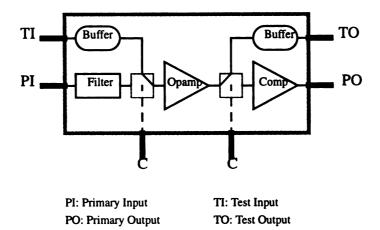

| Figure 2.6 | BIST design of an ADC.                                                                                                                   | 26 |

| Figure 3.1 | Defects: (a) switch layout; (b) defected layout; and (c) summary of defects and circuit fault.                                           | 32 |

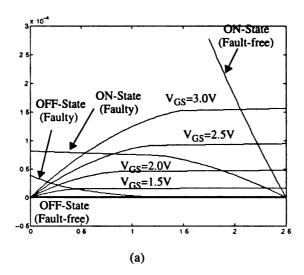

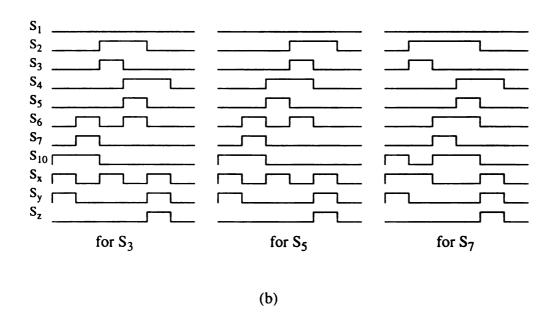

| Figure 3.2 | (a) Simulation results of I-V plot of M <sub>1</sub> with load lines for S <sub>2</sub> ; and (b) fault behavior and switching sequence. | 37 |

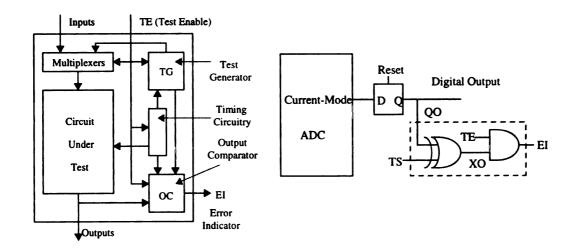

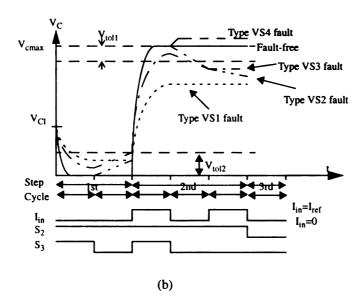

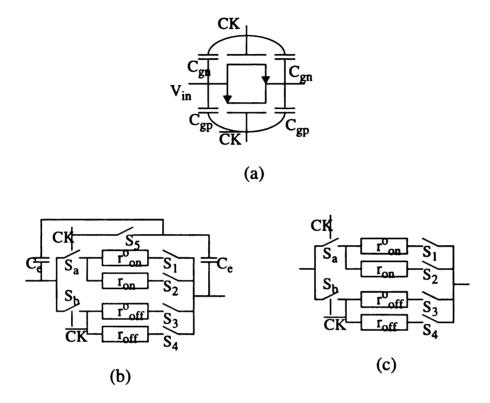

| Figure 3.3 | Built-in tester: (a) schematic; (b) switching sequence; and (c) fault simulation results.                                                | 40 |

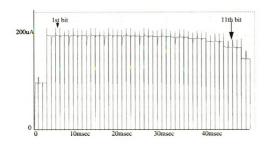

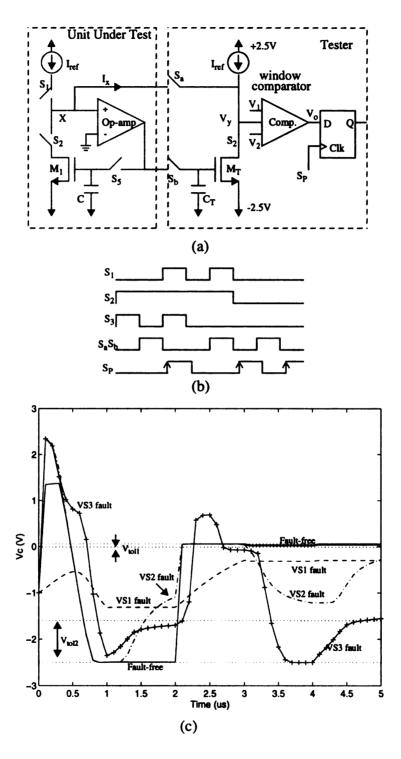

| Figure 3.4 | Test structure for SI algorithmic ADC: (a) schematic diagram; and (b) comparator.                                                        | 43 |

| Figure 3.5 | Test sequence A: (a) fault behaviors; and (b) switching sequence.                                                                        | 45 |

| Figure 3.6 | Test sequence B: (a) fault behavior; and (b) type VS2 fault                                                                              | 47 |

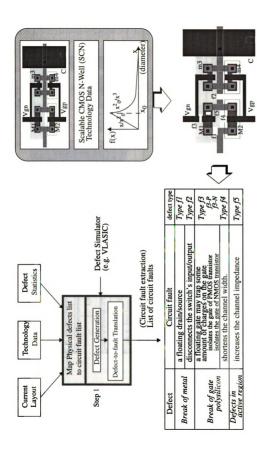

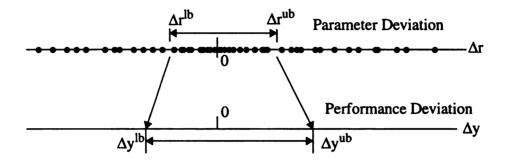

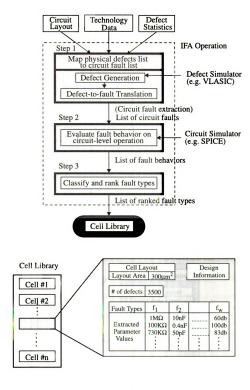

| Figure 3.7  | Step 1 of IFA-based fault macromodeling.                                                                                                                                       | 51 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.8  | Step 2 & 3 of IFA-based fault macromodeling.                                                                                                                                   | 52 |

| Figure 3.9  | Switches: (a) schematic; (b) fault model for voltage switch; and (c) fault model for current switch.                                                                           | 54 |

| Figure 3.10 | Relationship between parameter deviation and performance deviation.                                                                                                            | 57 |

| Figure 3.11 | Example for the definition of parameter deviation bounds                                                                                                                       | 57 |

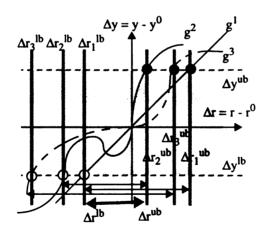

| Figure 3.12 | Equivalent circuit of the portion including transistor and current switch of the current copier, and its I-V characteristic.                                                   | 62 |

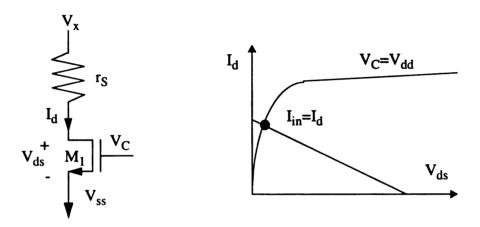

| Figure 3.13 | Simulation results: (a) for f <sub>1</sub> ; and (b) for f <sub>2</sub> .                                                                                                      | 67 |

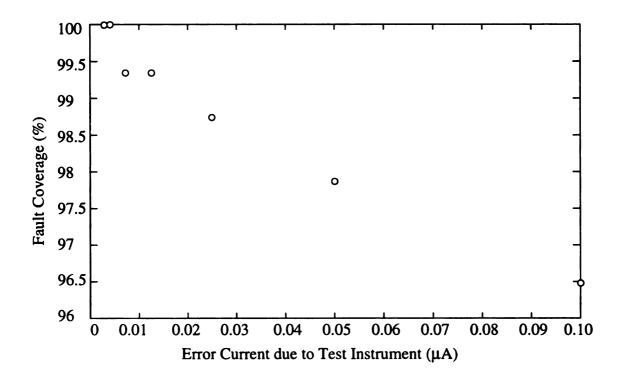

| Figure 3.14 | Fault coverages with respect to accuracy of test instrument                                                                                                                    | 71 |

| Figure 4.1  | Computational complexities of IFA process.                                                                                                                                     | 75 |

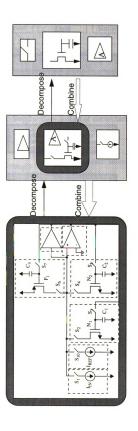

| Figure 4.2  | Concept of hierarchical fault modeling.                                                                                                                                        | 77 |

| Figure 4.3  | Cell library of hierarchical IFA-based fault macromodeling                                                                                                                     | 78 |

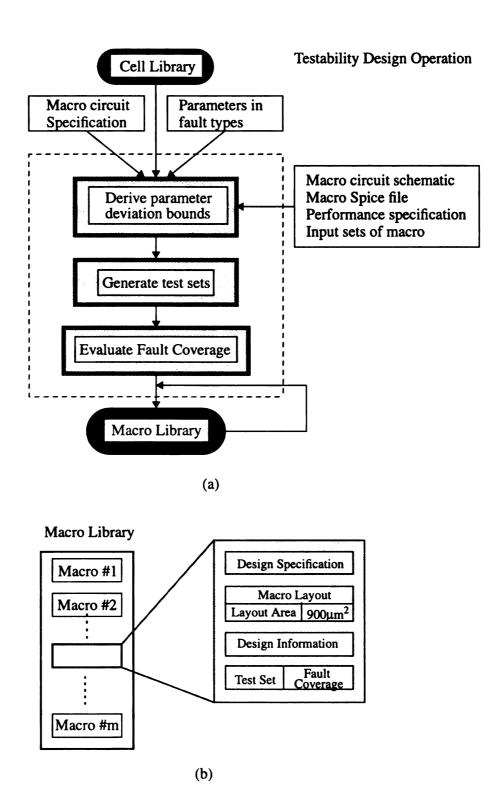

| Figure 4.4  | Macro library of hierarchical IFA-based fault macromodeling                                                                                                                    | 79 |

| Figure 4.5  | Fault equivalence.                                                                                                                                                             | 81 |

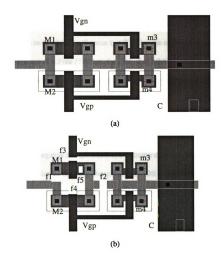

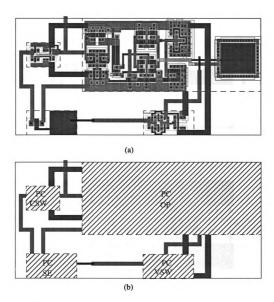

| Figure 4.6  | Macro "current copier": (a) layout; and (b) routing area                                                                                                                       | 83 |

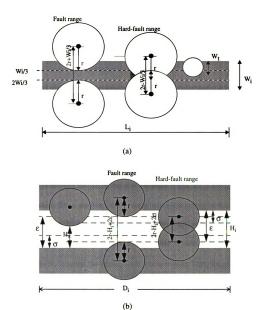

| Figure 4.7  | Fault coverage for routing area: (a) due to etching defect; and (b) due to extra defect.                                                                                       | 84 |

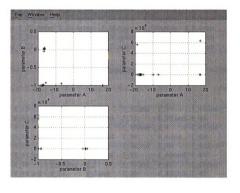

| Figure 4.8  | Examples for the definition of parameter deviation bounds: (a) in 1-dimension; and (b) & (c) in 2-dimension.                                                                   | 89 |

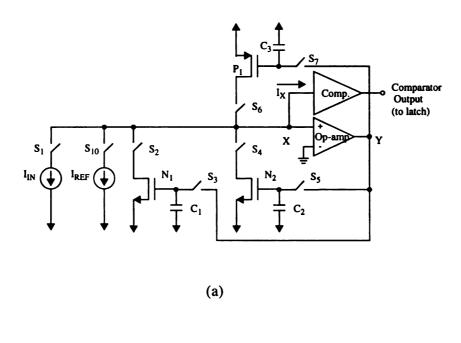

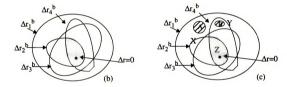

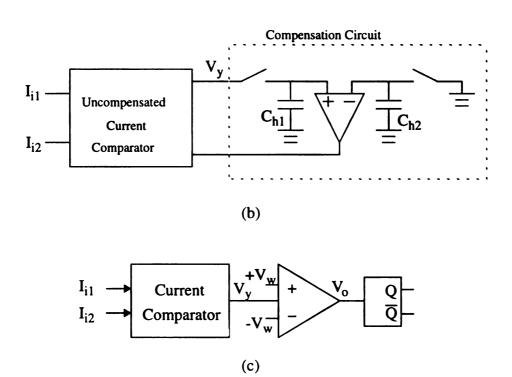

| Figure 4.9  | Current comparators: (a) in [52]; (b) in [60]; and (c) proposed design.                                                                                                        | 92 |

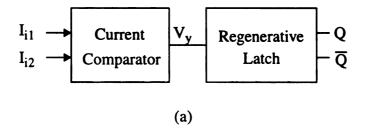

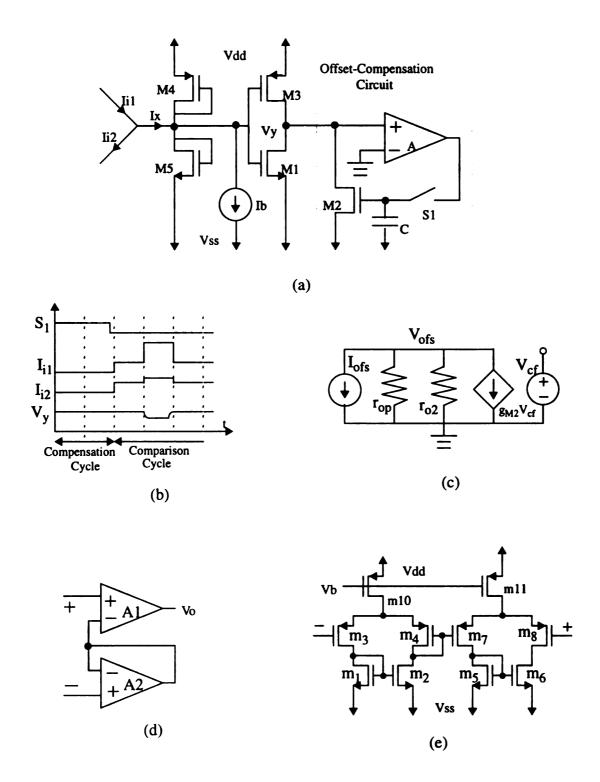

| Figure 4.10 | Current comparator: (a) schematic diagram; (b) switching sequence; (c) small signal equivalent circuit when S <sub>1</sub> is off; and (d) & (e) offset-compensated amplifier. | 95 |

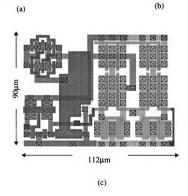

| Figure 4.11 | Proposed current comparator: (a) parameter values of Figure 4.10(a); (b) parameter values for Figure 4.10(e); and (c) physical                                                 |    |

|             | layout.                                                                                                                                                            | 99  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

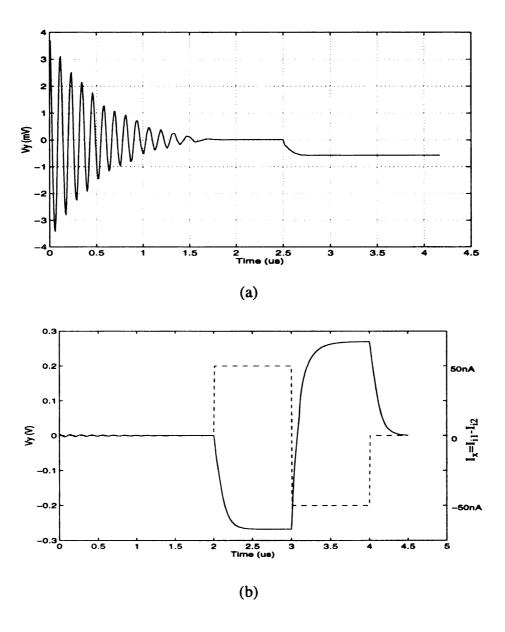

| Figure 4.12 | Transient responses: (a) during the compensation process; and (b) during the comparison process.                                                                   | 100 |

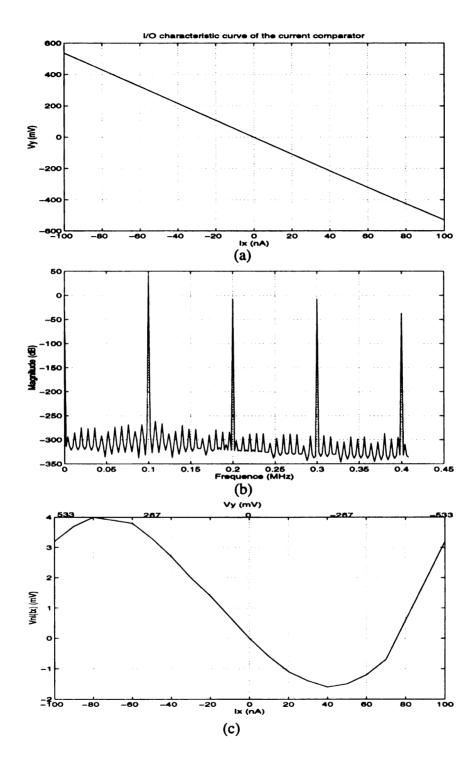

| Figure 4.13 | Simulation results: (a) $I_x$ - $V_y$ characteristic curve; (b) harmonic distortion; and (c) nonlinearity element $V_{nl}(I_x)$ vs $I_x$ & $V_y$                   | 101 |

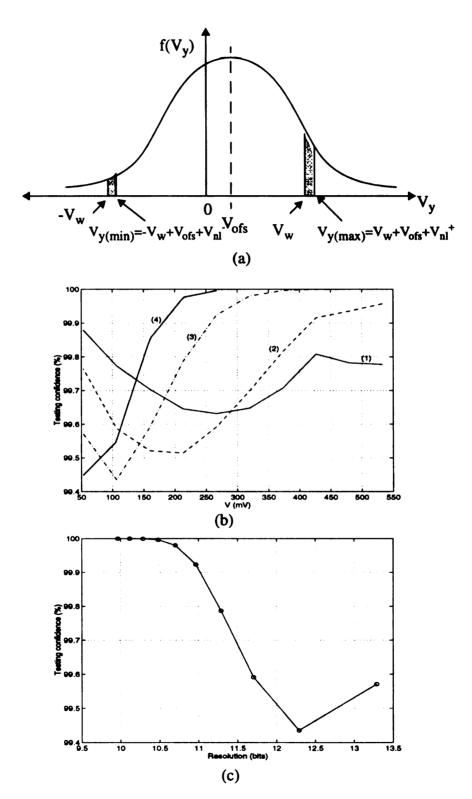

| Figure 4.14 | Performance analysis: (a) Gaussian distribution of $V_y$ ; (b) statistical confidence vs. window threshold voltage; and (c) statistical confidence vs. resolution. | 106 |

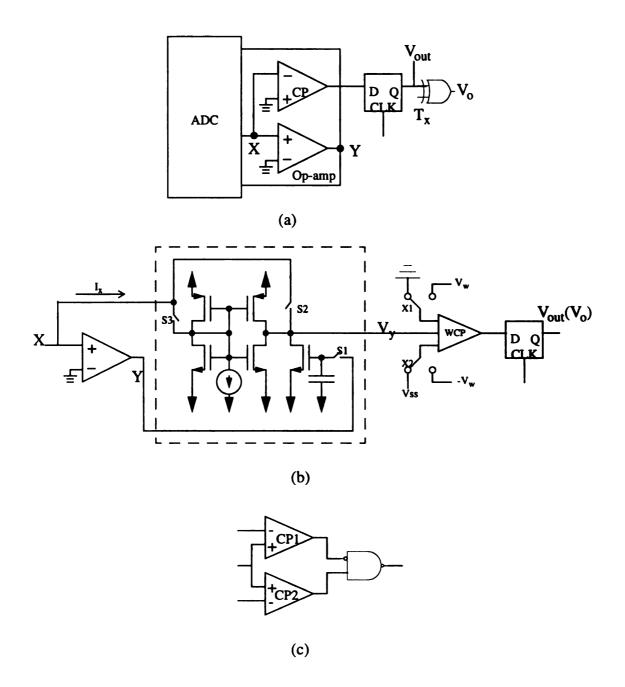

| Figure 4.15 | ADC with built-in tester: (a) ADC; (b) with built-in tester; and (c) window comparator.                                                                            | 109 |

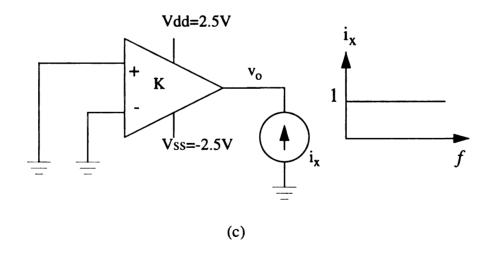

| Figure 5.1  | Structure of PETOMIC.                                                                                                                                              | 112 |

| Figure 5.2  | The use of defect generator in cell library establishing.                                                                                                          | 113 |

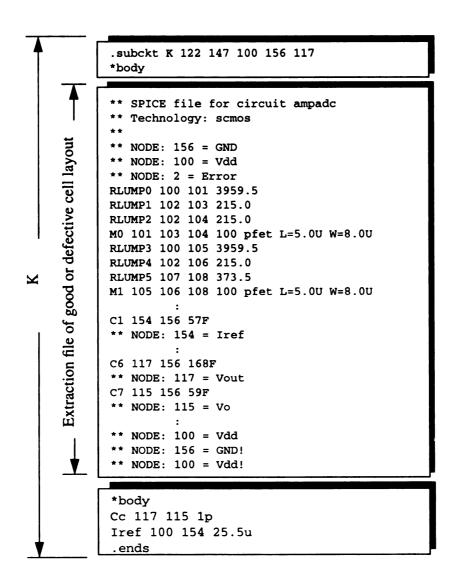

| Figure 5.3  | Example of extraction file and K.                                                                                                                                  | 115 |

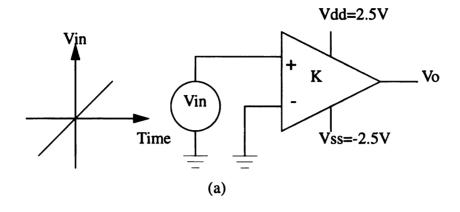

| Figure 5.4  | Experiments for extract parameters from cell K, Opamp in this example.                                                                                             | 116 |

| Figure 5.5  | Example of prem.cir.                                                                                                                                               | 117 |

| Figure 5.6  | The use of fault behavior evaluator and fault type classification environment in cell library establishing.                                                        | 120 |

| Figure 5.7  | Example of cell library.                                                                                                                                           | 121 |

| Figure 5.8  | Fault behavior display window.                                                                                                                                     | 126 |

| Figure 5.9  | Summary of files used or generated in CLG_routine.                                                                                                                 | 127 |

| Figure 5.10 | Example of macro.cir.                                                                                                                                              | 129 |

| Figure 5.11 | Example of macro library.                                                                                                                                          | 131 |

#### Chapter 1

#### INTRODUCTION

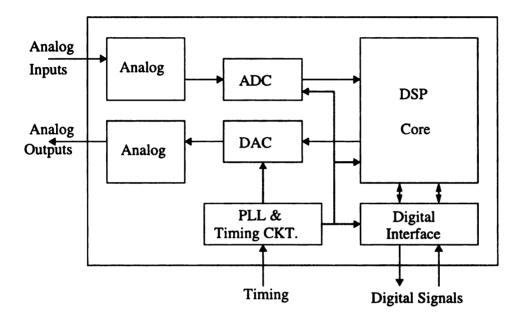

More and more mixed-signal devices are being designed recently for the applications of multimedia, wireless communication, and portable data systems. The analog circuit technology conventionally employed for such applications has been gradually switched to analog/digital mixed-signal circuit technology. Figure 1.1 shows a typical digital signal processing (DSP)-based mixed-signal integrated circuit (IC). The digital area typically takes more than 60% of the total IC area [1]. The main analog and mixed-signal components tend to be analog-to-digital converter (ADC), digital-to-analog converter (DAC), phase-locked-loop (PLL), operational amplifier (OP-amp), and filters. Even though much more complicated digital circuits have been widely used in the DSP-based mixed-signal IC, analog circuits will remain for processing or interfacing analog signals [2]. Integrating both digital and analog on a single chip has improved performance and reduced board size and cost. However, the increasing complexity of mixed-signal circuits drastically reduces the controllability and observability of the circuit on the chip. As a result, testing of such complex circuit becomes very difficult and expensive.

In mixed-signal circuits, the digital and analog components are tested separately. Procedure and equipment for testing stand-alone digital or analog chips have been well-established and implemented. However, manufacturers have found the costs associated

Figure 1.1 Schematic diagram of a typical DSP-based mixed-signal IC.

with high-volume production of mixed-signal ICs are strongly affected by the cost of testing, where the analog circuit testing dominates. Considerable effort has been devoted to identify the causes of the analog test complexity [3]. Unlike digital circuits, analog circuits do not have the binary distinction of pass and fail. The time and voltage continuous nature of their operation make them further susceptible to defects [4-6]. Analog systems are often nonlinear, thus their performance depends heavily on circuit parameters. Process variations within allowable limits can also cause unacceptable performance degradation.

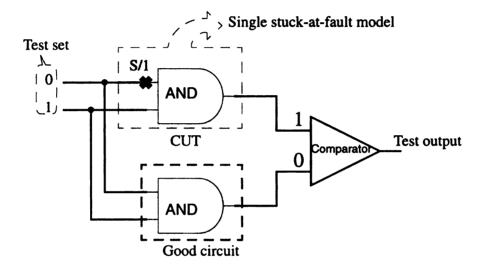

In digital circuits, there exists a wide range of fault models [7]. These models or abstractions form the basis of representing the faulty circuit behavior as well as the test generation. Given a set of test vectors, if the simulated output (signature) of a fault differs from that of the good circuit, then this set of test vectors can detect the fault. This testing process is called *fault-model-based testing* in which the *fault definition* and *test generation* are the major tasks. Thus, simulation before manufacture can be used to determine a set of test vectors for post-manufacture testing. Similar analysis can be done to determine the testability of a design. Figure 1.2 shows an example of the fault-model-based testing process for an AND gate. For a stuck-at one fault (S/1) on input of the AND gate, we can use test input {0,1} to distinguish the faulty circuit under test (CUT) from good one by comparing their outputs.

Analog testing is usually a specification-driven process. It tests a circuit for all specifications both during wafer-probe and final tests. However, given a set of specifications for a circuit, a basic question is [8]: Are these specifications necessary and sufficient? In fact, insufficient specifications may result that some faults cannot be detected properly, while unnecessary specifications cause the increase of the complexity of test

Figure 1.2 Single stuck-at-fault-model-based testing in digital circuit.

generation process. Therefore, analog testing may be simplified if the specification-driven process can be mapped to a fault-model-based process [9]. However, the effectiveness of applying digital fault models on analog circuit is questionable.

The similar stuck-at fault model has been applied for testing analog circuits. In order to enhance the reliability of ADCs for real-time applications, a CMOS switchedcurrent algorithmic ADC which possesses the concurrent error detection (CED) capability was developed in [10-15] to detect transient faults and permanent faults. Based on single stuck-at fault model on the switching elements, the fault behaviors of the A/D converter (ADC) were reported. It was assumed that faulty switched are either permanently stuck-at-ON state (S/ON) or stuck-at-OFF state (S/OFF). The failure of other components can be modeled as the fault of the associated switch. Thus, the converter can be fully testable. Due to the simplicity of the generated test patterns for the ADC [10-15], a built-in self-test (BIST) design of the ADC is reported in [16] which demonstrates the self-testability with a simple BIST structure. The above studies have shown that the failure of non-switch components can be modeled as the fault of the associated switch. Thus, the converter can be fully testable, but only for stuck-at faults. As it will be discussed later in this thesis study, our simulation results will show that the stuck-at faults in a CMOS switch are about 70% of the total circuit faults. This implies that a 30% of the total faults are not detectable in those studies, and they are referred to as parametric faults. Therefore, to enhance the testability, the first major task is to develop an efficient and effective fault model for analog circuits.

The second major task is to develop test generation and fault coverage evaluation.

Most analog circuits are presently designed without considering the testability. More spe-

cifically, a set of nominal parameter values and the associated tolerances are selected to meet a given set of design specifications. Therefore, a designed circuit meets the specifications, if all parameters are selected to be within the tolerances. In many circuit designs, however, a circuit may still meet the specification even if a parameter deviation is far beyond the tolerance. Testability design methodologies have been developed successfully for digital circuits, and its success is attributed to the well-defined fault models and testability design rules. Therefore, based on the fault models defined in the first task, it is necessary to develop certain testability design rules for the designed analog circuits in order to make it easily testable, i.e., the test vectors can be easily generated.

In summary, the goal of this thesis study is to develop an efficient testability design system for analog/mixed-signal circuits so that all designed circuits are easily testable.

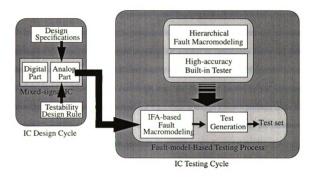

#### 1.1 Objectives and Research Tasks

The approaches for developing an efficient testability design system for analog/mixed-signal circuits include: (1) the development of efficient testability design methodologies; and (2) the development of testability enhancement methodologies. Figure 1.3 illustrates a broad view of the thesis study. The testability design system develops an analog circuit in two different cycles. In the design cycle, based on design specification, a set of testability rules is adopted to make the designed circuit easily testable. In the testing cycle, based on the process data and design circuit layout, the fault models of the design circuits are defined using an inductive fault analysis (IFA) technique [17]. Based on the defined fault models, test generation process is invoked to generate a test set and evaluate the fault coverage of the design circuit using the generated test set.

Figure 1.3 Broad view of this thesis study.

The IFA technique has been used to efficiently generate the layout defects and fault types. However, its computational complexity is always a major problem, and it is only applicable to small circuits. For reasonably large analog circuits, a hierarchical fault macromodeling process should be developed so that a large circuit can be hierarchically decomposed into smaller macros or primitive cells which can be handled comfortably by the IFA technique.

As mentioned, analog circuits are designed with a set of testability design rules. The rules ensure that a test set can be generated to test the designed circuit. However, the rules do not guarantee that the test set be generated at low cost. Thus, testability enhancement methodologies should be developed to reduce the number of hard-to-test faults and thus decrease the test generation cost. ICs are usually tested with expensive ATE (automatic test equipment). In addition to the instrument cost, the distortion caused by the interface between internal circuitry and external test equipment is always a severe problem in the IC testing. Therefore, the use of a built-in tester (BITER) not only prevents the distortion problem, but also simplify the test generation process.

In summary, the objectives of the thesis study are to develop efficient testability design methodologies and testability enhancement methodologies for analog/mixed-signal circuits. The major research tasks include the development of: (a) an IFA-based fault macromodeling process; (b) a hierarchical fault macromodeling process; (c) test generation and fault coverage evaluation processes; and (d) built-in testers. The final goal is to develop an efficient and effective testability design system which produces easily testable analog circuits.

#### 1.2 Thesis Organization

The dissertation is organized as follows: Chapter 2 reviews the background required for the thesis study. The IFA technique [17] used for modeling digital circuits is first discussed. Then, the test generation and fault coverage of the switched-current CMOS ADCs [10-15] are briefly described. It will include the salient features of switched-current circuits [18-22,23], the designs and operations of current copiers and CMOS ADCs, the fault behaviors, test generation, and fault coverage evaluation. Finally, some design-fortestability schemes developed for analog/mixed-signal circuits are reviewed.

Chapter 3 presents the developed fault macromodeling process. The process includes two major tasks: Fault-Type definition and Test Generation. Two macro fault macromodeling processes have been developed: heuristic process and IFA-based process. The former process defines the fault types from the circuit layout, technology data, and possible defects, and generates test set based on the fault types. To systematically generate practical fault types, the latter process defines the fault types from the circuit layout, technology data, and the defect distribution from real manufacture process. The fault types are ranked in terms of their occurrences and the higher ranked fault types are used to generate test set. To demonstrate the effectiveness of the developed fault macromodeling process, both current copiers and switched-current ADCs are used as example circuits.

Chapter 4 presents some testability enhancement methodologies. To reduce the computational complexity of the fault macromodeling process with the IFA technique, a hierarchical fault modeling process is developed. A circuit is partitioned as primitive cells and/or macros. The procedures for generating cell library and macro library will be presented. Based on both cell library and macro library, the test set for the target circuit is

generated and the fault coverage of the generated test set is evaluated. To simplify the testability design process, the refinement of the set of testability design rules presented in Chapter 3 will be presented. Finally, a high-accuracy CMOS current comparator is introduced as a built-in tester. The detail design and operation of the tester will be discussed with the simulation results and performance analysis. In addition, this study also addresses the design trade-off between the accuracy of the tester and test sequence length.

Based on the hierarchical fault macromodeling process presented in Chapter 4, Chapter 5 presents a hierarchical testability design system, namely, PETOMIC (Packages for Enhancing Testability Of Mixed-signal Integrated Circuit). The system generates cell library, macro library, test set, and evaluates the fault coverage. The detail system development is discussed with examples of generating a cell library of an Opamp and a macro library of a current copier. The system demonstrates the feasibility of the hierarchical fault macromodeling process.

Finally, Chapter 6 summarizes the thesis study and gives a concluding remark and some future research directions.

#### Chapter 2

#### **BACKGROUND**

Analog circuit testing process can be simple and effective if the specification-driven test process can be mapped to a fault-model-based testing process. Fault definition and test generation are two major tasks in a fault-model-based testing process. Section 2.1 reviews the fault definition and IFA technique. Section 2.2 discusses a test generation process developed in [12,14,15] for switched-current (SI) ADCs. This section briefly describes the importance of SI circuits, the structures and operations of current copiers and an ADC, and the fault behaviors and test generation of an ADC. Finally, some analog/mixed-signal testing schemes are presented in Section 2.3.

#### 2.1 Fault Definition

A number of factors contribute to the failure of a fabricated circuit. Process disturbance, which is essentially random in nature, result in either global or local defects [24-27]. Typically, local defects cause structural deformation at the physical level. The deformations that alter the circuit topology (hard shorts, opens) create *catastrophic faults*, while that do not alter the circuit topology (component deviation) or the DC circuit connection (capacitance bridges) appear as *non-catastrophic faults*. Catastrophic faults result in complete circuit malfunction. Circuit failures are marginal in the presence of non-catastrophic

ŀ

faults. On the other hand, global defects result in either obvious failures (spotted by virtual inspection) or, subtle parametric faults. The deviation of process parameters beyond tolerable limits results in *parametric faults* which cause marginal failures of some design specifications [24].

Inductive fault analysis (IFA) [17] is a common technique for deriving a graded list of the most likely faults from a description of circuit layout, process parameters, and defect statistics of the fabrication process. The IFA procedure is comprised of three steps, as illustrated in Figure 2.1. The first step includes the defect generation and the defect-tofault translation. Based on the defect distribution obtained from an actual manufacture process, a defect generator generates a collection of defects, and it injects these defects into the circuit layout. Note that the manufacture process statistics contains the defect density per area and the distribution of defect size. Once the defective layouts are generated, and their associated circuit parameters are extracted by a circuit extractor. This step translates the defects in the layout level to faults in the circuit-level. VLASIC [28] is a software tool commonly used for both defect generation and fault translation for catastrophic faults. The second step defines the macro-level fault behaviors of the faulty circuit parameters. The circuit parameters extracted from the defective layout are simulated by a circuit simulator, SPICE, to generate macro-level fault behaviors such as output impedance, DC bias voltage on macro output or frequency response, etc.

Step 3 groups the fault behaviors into a collection of fault types, where the fault types may be ranked according to the number of their occurrences. This generates a list of fault types.

Figure 2.1 Inductive fault analysis.

#### 2.2 Test Generation of Switched-Current Circuits

There exists many kinds of fault models in digital circuits. These fault models form the foundation of representing the faulty circuit behavior as well as the test generation. For given test vectors, if the simulated output (signature) of a faulty circuit is different from that of the good one, these test vectors can detect the fault. Thus, simulation before manufacture can be used to determine a set of test vectors for post-manufacture testing. In this section, a switched-current ADC is used as an example to demonstrate the test generation process.

#### 2.2.1 Switched-Current Circuits

Low-voltage/low-power circuit design is strongly needed for both analog and digital circuit in portable data systems to increase operation time and to decrease the number of batteries and the weight, volume, and operating temperature of the equipment. With the trend that analog-digital interfaces are incorporated as a cell in complex mixed-signal integrated circuits, the use of the same supply-voltage for both analog and digital circuits can give advantages in reducing the overall system cost by eliminating the need of generating multiple supply voltages with dc-dc converters. Therefore, to be compatible with low-voltage systems, analog signal processing components must be able to operate at supply voltage 2-3 V. Reducing power dissipation associated with high-speed sampling and quantization is another important key factor.

Traditionally, the switched-capacitor (SC) technique has been employed extensively in the analog interface portion of mixed-signal designs. However, SC circuits are not fully compatible with digital CMOS processing technology and, as the technology

advances further, the drawbacks of SC technique are becoming more significant. SC techniques traditionally require high quality linear capacitors, which are usually implemented using two layers of polysilicon. The second layer of polysilicon used by SCs is not needed by purely digital circuits and may become unavailable as process dimensions shrink to the deep submicron range. The trend towards submicron processes is also leading to a reduction in supply voltages, directly reducing the maximum voltage swing available to SCs and consequently reducing their maximum achievable dynamic range. With lower supply voltages, the realization of high-speed high-gain operation amplifier becomes more difficult.

Recently, a class of analog circuits wherein current rather than voltage is the primary signal medium has been received considerable attention. The use of current-mode creates a potential for speed improvement because stray-inductance effects in such low-impedance switched-current (SI) circuits are much less severe than those in high-impedance SC circuits. The SI technique couples itself well with the down-scaled CMOS technology, where transistors with a high cut-off frequency are available, meaning a high calibration speed. In addition, highly-linear capacitance is not needed for high accuracy analog signal processing circuits using SI technique. Thus, the same low-cost digital CMOS process for the digital portion of mixed-signal circuits can also be used for the analog portion with SI technique [18-20].

#### 2.2.2 Structures and Operations

Current copier is the basic building block of switched-current circuits. The performance of SI circuits is determined by the current copiers they employ. A copier, as shown

Figure 2.2 Current copier: (a) basic copier; (b) with feedback amplifier; and (c) CMOS switch with a dummy switch.

in Figure 2.2(a) [21], is comprised of  $S_1$  and  $S_2$ , the current-storage transistor  $M_1$ , and the holding capacitor C. To copy the current  $I_{in}$ ,  $S_1$  and  $S_2$  are turned on for feeding  $I_{in}$  to  $M_1$  and C. The capacitor is charged up to whatever gate voltage is needed by  $M_1$  to support a current equal to  $I_{in}$ . When  $S_1$  and  $S_2$  are turned off, the copier cell is disconnected from the current source; thereafter the copier cell is capable of sinking a current  $I_{in}$  when connected to a load.

Copier suffers from two major error effects: (1) the nonzero conductance of  $M_1$  and (2) charge-injection of  $S_2$  [22]. The non-zero output conductance results from the channel length-modulation effect and the drain-gate capacitive coupling of  $M_1$ . The charge-injection error effect is caused as follows: When the gate voltage of  $S_2$  goes down during the turn-off transient, the charge held in the transistor realizing  $S_2$  will be forced to leave. Since one end of  $S_2$  is connected to the gate node of  $M_1$ , some charge of  $S_2$  will be dumped to the gate of  $M_1$  and change the voltage across C. As a result, the current held in  $M_1$  will deviate from  $I_{in}$ , and charge-injection error results. The error effect due to the nonzero conductance of  $M_1$  can be alleviated by using a negative feedback structure, as shown in Figure 2.2(b), where an amplifier is inserted between the drain and the gate of  $M_1$ . On the other hand, the charge-injection error effect can be reduced by either increasing the capacitance C, or the use of CMOS switch with a dummy switch, as shown in Figure 2.2(c) [29-30].

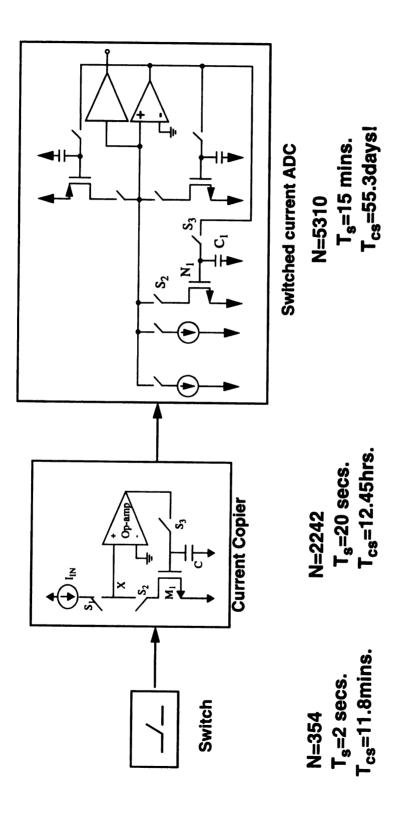

Figure 2.3 illustrates an SI algorithmic ADC that combines current mode and dynamic techniques [23]. This converter does not rely on high gain amplifiers or well-matched components to achieve high resolution and it's inherently insensitive to the amplifier's offset voltage. This converter is comprised of two NMOS current copiers, one

Figure 2.3 An SI algorithmic ADC: (a) schematic diagram; and (b) simulation results.

(b)

PMOS copier, an op-amp, and a current comparator. The conversion starts sampling the input current and holding it in  $P_1$  by turning on  $S_1$ ,  $S_6$ , and  $S_7$ , and converting for the most significant bit (MSB) of an input current  $I_{IN}$  by first switching on  $S_6$ ,  $S_2$ , and  $S_3$  to cause the current in  $N_1$  to be set to  $I_{IN}$ . Once the current in  $N_1$  is held,  $S_2$  and  $S_3$  are switched off while  $S_4$  and  $S_5$  are on to copy  $I_{IN}$  to  $N_2$ . The currents stored in  $N_1$  and  $N_2$ , twice the input signal, are then loaded into  $P_1$  by turning off  $S_1$  and  $S_5$  while switching on  $S_2$ ,  $S_6$ , and  $S_7$ . After  $P_1$  is set,  $S_2$ ,  $S_4$ , and  $S_7$  are turned off, and  $S_{10}$  is turned on, it allows the comparator to sense the current imbalance, and determines if the signal,  $2I_{IN}$ , is greater than  $I_{ref}$ . If the signal exceeds the reference, the MSB will be a "1" otherwise it will be a "0". This completes the conversion for the MSB.

The remaining (N-1) bits are then converted in the same manner. The signal held in  $P_1$  is loaded to  $N_1$  by turning on  $S_6$ ,  $S_2$ , and  $S_3$ . If the preceding bit was a "1",  $S_{10}$  is also turned on to subtract the reference from the signal in  $P_1$ . On the other hand, if it was a "0",  $S_{10}$  is off so that the signal remains unchanged. Once  $N_1$  is set,  $N_2$  is set by the same procedure. The signal is then doubled and stored in  $P_1$ . Finally, it is compared with the reference. The sequence is repeated until the desired resolution is achieved: and the end of conversion pulse is then generated to signal the end of conversion. The converter needs 4N clock cycles for and N-bit conversion [29,31].

The circuit has been implemented and simulated using MOSIS  $2\mu m$  CMOS process parameters, where supply voltages  $\pm 2.5 V$  are used [29]. Figure 2.3(b) shows the pspice simulation results for the currents held in the PMOS copier at each conversion cycle, where an input currents  $I_{IN}=100\mu A$  is applied. The results show that the converter

achieves a 11-bit resolution. The results also show that the sampling rate and resolution can be improved. However, the performance improvement is not of primary concern in this study. The circuit is implemented to demonstrate and endorse the correctness of our fault simulations.

#### 2.2.3 Fault Behaviors and Test Generation of an ADC

Although mismatched components are allowed in the ADC of Figure 2.3(a), the converter is still susceptible to faulty switching elements. Any faulty switching element may result in an incorrect converted data. Based on the single stuck-at fault model commonly employed for digital test generation, the implementation [12,14,15] assumes that only one faulty switch occurs at a time and the faulty switch is permanently stuck-at ON state (S/ON) or OFF state (S/OFF). That study generates test signals to completely test the ADC.

The analysis of the faulty switches in the ADC revealed that, due to the fault equivalence, the fault behaviors can be classified into three types: *Type 1 fault* behavior occurs when the faulty switch results in the same conversion output regardless of the values of the input current. Switches  $S_1$ ,  $S_2$ ,  $S_4$ ,  $S_7$ , and  $S_{10}$  being *S/ON* and  $S_1$ ,  $S_2$ ,  $S_4$ ,  $S_6$ , and  $S_{10}$  being *S/OFF* illustrate this fault behavior: *Type 2 fault* occurs when the faulty switch renders the conversion output dependent on the initial condition of the active capacitors. Switches  $S_3$ ,  $S_5$ , and  $S_7$  lead to this condition when *S/OFF*: and *Type 3 faults* makes the result of the conversion process dependent on the CMOS structure  $P_1/N_1$  (or  $P_1/N_2$ ) when  $S_3$  (or  $S_5$ ) is being *S/ON*. Throughout the next analysis,  $I_{P1}$  ( $I_{N1}$ , or  $I_{N2}$ ) will denote the current held in  $P_1$  ( $N_1$ , or  $N_2$ ).

Table 2.1 Fault types and expected outputs.

| Fault Types | Input Current To Be Converted | Expected Output Bit Pattern |

|-------------|-------------------------------|-----------------------------|

| Type 1A     | xxxx                          | 0000                        |

| Type 1B     | xxxx                          | 1111                        |

| Type 2      | 0000                          | 001xx                       |

|             | 1111                          | 110xx                       |

| Type 3      | xxxx                          | 1xxx<br>xx1xx<br>xx1        |

More specifically, consider the case when  $S_1$  or  $S_6$  is S/OFF, the input current will not be copied into  $P_1$ ; this is effectively equivalent to an input current of zero.  $S_{10}$  being S/OFF leads to the current in  $P_1$  being compared to zero instead of  $I_{ref}$ . Hence conversion results in a string of ones. For simplicity of this discussion, Type 1 faulty elements are distinguished as  $Type\ 1A$  if they result in a string of zeros, and as  $Type\ 1B$  if they produce a string of ones. The detailed fault behaviors for various fault types can be found in [12,14,15].

Table 2.1 summarizes the expected output bit string for each type of faults. A string of zeros is expected in the presence of a Type 1A fault for applying any input current to the converter. Similarly, a string of ones is expected for Type 1B fault. Thus, two test currents, I<sub>T1</sub>=0 and I<sub>T2</sub>=I<sub>ref</sub>, can detect both types of faults. More specifically, a bit string of zeros is expected when the test current I<sub>T1</sub>=0 is applied to a fault-free converter. Thus, the test current I<sub>T1</sub>=0 detects Type 1B faults. Similarly, the expected bit string of ones for I<sub>T2</sub>=I<sub>ref</sub> detects Type 1A faults. For Type2 faults, the application of I<sub>IN</sub>=0 results in a bit-string pattern of 0..01x..x. This implies that the expected bit string of zeros for the test pattern I<sub>T1</sub>=0 detects the faults. On the other hand, a bit pattern of 1..10x..x is produced when  $I_{IN}=I_{ref}$  is applied. Thus, the expected bit string of ones for the test current I<sub>T2</sub>=I<sub>ref</sub>, detects such faults. Finally, in the presence of a Type 3 fault, a bit string containing at least a 1 is generated and the fault can be detected by the test current  $I_{T1}=0$ . This concludes that both test currents, I<sub>T1</sub>=0 and I<sub>T2</sub>=I<sub>ref</sub>, detect all single stuck-at faults at the switching elements of the ADC. If fault coverage is defined as the ratio of the number of faults can be detected over the total number of faults in that circuit, then the converter is

;

te

ci

Ç0

and

2.3.

sign digit

incre regis

2.4(a

test d

two a

free. T

data, as

realize

cucuit ii

fully testable with respect to single switching element faults using these two test currents.

# 2.3 Analog/Mixed-Signal Testing Schemes

Design for testability (DFT) techniques and methodologies as well as built-in selftest (BIST) structures have been successfully developed and implemented for digital circuits [32,7], they are recently extended to mixed-signal circuits to increase both controllability and observability. This section reviews the development of DFT techniques and BIST structure.

## 2.3.1 Design-for-Testability Techniques

Conceptually, testability can be considered as the ability to control and observe signals at the circuit (internal) nodes. Given the complex chip in Figure 1.1, analog and digital blocks are generally tested separately. Each block is isolated with a scan path to increase both controllability and observability [33,34]. A scan chain using digital shift registers is added to the interface between the ADC/DAC and DSP core, as shown in Figure 2.4(a), where each register is connected to a node to be accessed. The scan chain allows the test data to be simultaneously loaded to the register and sequentially shifted out, where only two additional pins required for scan-in and scan-out to ensure the scan chain to be fault-free. The same scan design concept can be extended for analog block. Analog shift registers (ASRs), realized by sample/hold (S/H) circuits, can be used to load and shift out the test data, as shown in Figure 2.4(b) [35]. A switched-capacitor (SC) S/H circuit was used to real ize the shift register for voltage test data measurement, while current copier, as S/H circuit in switched-current (SI) technique, implements for current test data measurement

Figure 2.4 DSP-based IC with scan structures.

[36,37]. For voltage test data measurement, each unit (corresponding to a test point) of the scan structure requires a test-point buffer and an ASR. The test-point buffer is used to isolate the test circuit from the UUT (Unit Under Test) so that it will not affect the voltage level at the test point during the sampling period. The buffer is implemented by a voltage follower that has a very high input impedance and a very low output impedance. The scan structure allows parallel of loading the test data and serially shifting them to the output buffer for circuit testing and fault diagnosis. The scan chain also ensures the testability of the analog shift register, i.e., the scan structure is self-testable. Results show that highaccuracy, high-linearity, and high-speed performance can be achieved by the analog shift registers. Connecting all shift registers as scan chain works perfectly in digital circuits, however, the offset voltage in each analog SC S/H circuit may be accumulated to a huge error. This has motived the development of an alternative structure using analog multiplexers [36] which alleviate the error effects. The design concept of combining analog multiplexing and demultiplexing to analog inputs and outputs has been extended to develop analog test bus, as shown in Figure 2.5 [38]. It has also further extended as the IEEE 1149.4 standard for boundary scan design. Scan structures are well-suited for those designs which have insufficient probing pads, and have been applied to board- and system-level design to offset the hardware overhead. However, it may be applied in circuit-level design if the hardware overhead can be reduced.

In addition to controllability and observability, fault coverage is also a very important testability measure in digital testing. Fault coverage is a measure of completeness in testing. Instead of number of faults detected, the term fault coverage in analog testing should be:

how many parameters should be tested to ensure adequate performance in the intended

Figure 2.5 Test bus.

Figure 2.6 BIST design of an ADC.

application. The concern is which parameters to test. Analog circuits have many parameters to be tested, but only some parameters, referred to as critical parameters, may significantly affect the circuit behavior. The error effect due to the variations of such parameters may cause a system failure. Thus, it is desirable to investigate the relationship between parameter variation and system failure, and to further identify the critical parameters. The set of critical parameters should be minimal in order to simplify the testing/diagnosis process.

## 2.3.2 BIST Designs

Since most analog components in mixed-signal circuits are used for processing and interfacing analog signals, pin overhead becomes an important issue. A number of analog BIST structures have been presented [39-49,31] to enhance the testability and fault diagnosability of analog circuits. The major design issues include the hardware and pin overhead, self-testable capability of the added hardware, and performance degradation. A BIST structure of a digital circuit, as shown in Figure 2.6 [31], is comprised of five major parts: *Test Generator* (TG), *Input multiplexers* (INMUX), *UUT*, *Output Comparator*, and *Timing Circuitry*. The INMUX selects the input signals either from the normal input signals during the operation mode, or from the test signal generated from TG during the test mode. The timing circuitry is used to synchronize the entire operation. Two extra pins, *test enable* (TE) and *error indicator* (EI), are needed.

In [31], the single stuck-at fault model was assumed. A fault which occurs at any components in the BIST structure causes an error and will be indicated by EI. By faults, we mean the stuck-at ON/OFF faults at all switching elements in the converter circuit and the

stuck-at 0/1 faults at the D-input and Q-output (denotes as QO) of the flip-flop, TS, XO, TE, and EI. The self-testing process starts with checking the latter faults, and then testing the former faults in the converter circuit.

Checking the latter faults is conducted by turning on the power and resetting the flip-flop to a 0. The test enable signal TE is changed from a 0 to a 1, and it is expected that, for a fault-free AND gate, the signal EI is also changed from a 0 to a 1, where the signal TS is set to a 1. Consequently, an unchanged signal EI=1 implies that a stuck-at-1 (s-a-1) fault occurs at EI or TE. On the other hand, an unchanged signal EI=0 indicates the occurrence of either a s-a-0 fault at TE, EI, TS, or XO, or a s-a-1 at QO. Note that the s-a-1 fault at QO also implies that the flip-flop fails to perform the reset function. After passing the above test, the signal TS is set to a 0 and the signal TE remains as a 1, hence, the signal EI is expected to be a 0. Therefore, an unexpected EI=1 implies that a s-a-1 fault occurs at TS, QO, EI, or XO. Therefore, with these two tests, the only undetected stuck-at 0/1 faults include the s-a-0 fault at QO and the s-a-0/1 fault at the D-input of the flip-flop which will be tested later.

By Table 2.1, a converted bit string of zeros is the result of *Type 1A faults* and a string of ones for *Type 1B faults*; a bit string of 0...01x...x for Type 2 faults with the application of  $I_{IN}$ =0 and a string of 1...10x...x for *Type 2 faults* with the application of  $I_{IN}$ = $I_{ref}$ ; and a bit string having at least one 1 for *Type 3 faults*. Therefore, to test the converter circuit, we first apply the zero test current, where TS is set to a 0, the flip-flop is reset, and TE remains as a 1 for the test mode. In this test, the signals EI=0 and XO=1 are expected for a fault-free circuit. An unexpected EI=1 implies the occurrence of a *Type 1B*, *Type 2, or Type 3 fault*, or a s-a-1 fault at the D-input of the flip-flop. After passing the test,

the test current  $I_{ref}$  is applied, where TS is set to a 1, the flip-flop is reset, and TE=1. This test is also expected to produce EI=0. An unexpected EI=1 implies the occurrence of either a *Type 1A fault*, or a s-a-0 fault at QO or D-input of the flip-flop.

This concludes that the BIST structure is fully testable for all single stuck-at non-redundant faults [31].

# Chapter 3

# **FAULT MACROMODELING**

This chapter presents two fault macromodeling processes that map the specification-driven analog testing process to a simple fault-model-based process: Heuristic [29,30,50] and IFA-based [51]. The former process defines the fault types from the circuit layout, technology data, and possible defects, and generates test set based on the fault types. To systematically generate practical fault types, the latter process defines the fault types from the circuit layout, technology data, and the defect distribution from real manufacture process. The fault types are ranked in terms of their occurrences and the higher ranked fault types are used to generate test set.

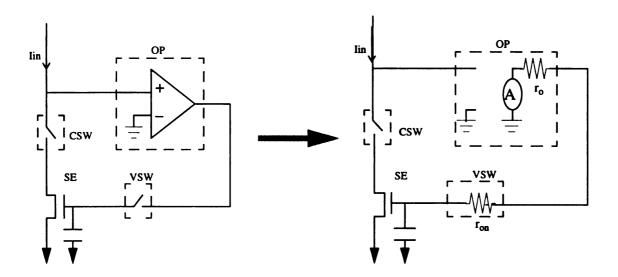

Switches are commonly used in both SI and SC circuits. According to the functionality, two types of switches, *voltage switch* and *current switch*, can be identified. Section 3.1 describes some defects and circuit faults of both switches and illustrates their fault behaviors and fault models. Based on the circuit faults, Section 3.2 presents the heuristic fault macromodeling process. Two example circuits, current copier and ADC, are used to demonstrate the process. Section 3.3 introduces the developed IFA-based fault macromodeling process. Finally, summary and concluding remark for the fault macromodeling is discussed in Section 3.4.

# 3.1 Fault Types in Switches

Current switches have been commonly used in SI circuits, while Voltage switches are used in both SC and SI circuits. As their names imply, the current switch passes current signal, while the voltage switch passes voltage signal. For example, as shown in Figure 2.2(b),  $S_2$  is used to pass the currents held in copiers,  $S_1$  used to pass  $I_{IN}$ . Thus, they are all implemented by current switches. On the other hand,  $S_3$ , used in copier for calibration, is implemented with voltage switches.

Figure 3.1(a) shows the physical layout of the switch in Figure 2.2(c), where the MOSIS 2μm CMOS technology, a two-metal, single polysilicon, and n-well, was assumed. Figure 3.1(b) gives five examples of process defects which are significant and cause the circuit to be malfunction. The faults due to these defects are summarized in Figure 3.1(c). In addition, other process defects may also cause faults, such as variations of channel size, errors in doping concentration, errors in the thickness of the gate oxide, etc.

Consider a voltage switch. Let  $T_{clk}$  be the clock pulse width applied to the switch. When a fault-free switch is on, the time constant  $\tau_{on}=R_{on}C$  should be smaller than  $T_{clk}$  for sampling the input voltage signal. On the other hand, when the switch is off, the maximum leakage current  $I_{leak}$  should be tolerable, i.e.,  $I_{leak} < I_{tol}$ . The on-resistances of both PMOS and NMOS transistors in the switch should be connected in parallel when the switch is on. As shown in Figure 3.1(c), the presence of the  $Type\ fl$  defect causes a floating drain/source in PMOS/NMOS transistors. This results in an increase of on-resistance, while the off-resistance remains the same. Therefore, the increase of on-resistance due to this defect will cause  $\tau_{on}>T_{clk}$ . This implies that the capacitor C samples and holds a unsettled, incorrect input voltage when the switch is on. Note that the fault does not affect the switch when it

| Defect                       | Circuit fault                                                                                                                                  | defect type             |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Break of metal               | a floating drain/source                                                                                                                        | Type f1                 |

|                              | disconnects the switch's input/output                                                                                                          | Type f2                 |

| Break of gate<br>polysilicon | a floating gate may trap some<br>amount of charges on the gate<br>isolates the gate of PMOS transistor<br>isolates the gate of NMOS transistor | Type f3<br>f3-P<br>f3-N |

|                              | shortens the channel width.                                                                                                                    | Type f4                 |

| Defects in active region     | increases the channel impedance                                                                                                                | Type f5                 |

(c)

Figure 3.1 Defects: (a) switch layout; (b) defected layout; and (c) summary of defects and circuit fault.

is off. A Type f2 defect is equivalent to a S/OFF fault in the switch, in which both the onand off-resistances are sufficiently large. In other words, when the switch is on, the increase of on-resistance due to this defect will cause  $\tau_{on} > T_{clk}$ , but the off-resistance is not affected.

In the presence of a *Type f3* defect, the gate of an NMOS transistor is isolated and traps some charges, either positive or negative charges. Three cases can be identified for trapping a positive charge: (1) for larger positive charges, it causes a decrease of off-resistance, but the on-resistance remains the same; (2) for large negative charges, it causes an increase of on-resistance, but the off-resistance remains the same; and (3) for a small amount of positive or negative charge, it causes a decrease of off-resistance and an increase of on-resistance. Similarly, isolating the gate of PMOS transistor has the same fault behaviors but exactly opposite to those of NMOS transistors. The first case causes  $I_{leak} > I_{tol}$ , while the second case results in  $\tau_{on} > T_{clk}$ . Case 3 includes both defect effects and causes a larger time constant  $\tau_{on}$  and an intolerable leakage current. *Types f4* and *f5* defects cause an increase of on-resistance. Based on the fault behaviors of the defects, the following three fault types are concluded,

Type VS1 fault: causes an intolerable time constant  $\tau_{on}$  and

a tolerable leakage current;

Type VS2 fault: causes a tolerable time constant  $\tau_{on}$  and

an intolerable leakage current; and

Type VS3 fault: causes an intolerable time constant  $\tau_{on}$  and

an intolerable leakage current;

Note that the charge-injection error occurs at the moment when switch is turned off. Since

the charge held by the capacitor changes when switch state is changed, an additional fault

type should be included.

Type VS4 fault:

cause excess charge flows out of switch

at the moment when switch is turned off.

Consider the fault models of a current switch. Let V<sub>max</sub> be the maximum voltage

across the switch. In general,  $V_{max}=V_{DD}$  (power supply voltage). For a fault-free current

switch, its on-resistance R<sub>on</sub> must be sufficiently small so that the maximum switch current

$(=V_{max}/R_{on})$  is larger than the maximum input current,  $I_{IN(max)}$ , and its off-resistance  $R_{off}$

has to be sufficiently large so that the maximum leakage current  $I_{leak}$  (= $V_{max}/R_{off}$ ) is

smaller than a tolerance,  $I_{tol}$ . Therefore, an increase of on-resistance, i.e.,  $V_{max}/R_{on}$  <

$I_{IN(max)}$ , results in an error current,  $\Delta I = I_{IN} - V_{max} / R_{on}$  when  $I_{IN} > (V_{max} / R_{on})$  is applied. On

the other hand, a decrease of the off-resistance causes the maximum leakage current  $V_{max}$

R<sub>off</sub> to be greater than the predetermined current tolerance I<sub>tol</sub>. Let V<sub>tol</sub> be the equivalent

voltage across the switch, where  $V_{tol} = I_{tol}R_{off}$ . Therefore, it produces an intolerable leakage

current,  $V/R_{off}$ , where  $V_{tol} < V < V_{max}$ . Three fault types can be concluded in a current

switch as follows,

Type CS1 fault:

causes an error current when switch is on, and

a tolerable leakage current when switch is off;

Type CS2 fault:

causes an intolerable leakage current when switch is off

and no error current when switch is on; and

Type CS3 fault: causes an error current when switch is on and

an intolerable leakage current when switch is off.

The deviation of an output current in a current switch is caused only by the channel

resistance, but not influenced by the charge-injection errors. Thus, the charge-injection

should not be considered in the fault model for the current switch.

This study shows that a fault-free switch macro may be used as either a current

switch or a voltage switch. However, the number of fault types in a current switch is less

than those in a voltage switch. In other words, the fault model of current switch is simpler

than that of voltage switch. This concludes that a fault-free macro may be used for different

applications, but the fault models of the same macro may be different depending upon the

applications. Those fault types causing only minor or no effects should be excluded in order

to simplify fault simulation and test generation.

3.2 Heuristic Fault Macromodeling Process

The heuristic fault macromodeling process defines the fault types based on circuit

layout, technology data, and some possible defects on the circuit layout. Based on the

defined fault types, a test set is generated. For simplicity of discussion, two example

circuits, current copiers and ADC, are used to demonstrate the process.

### 3.2.1 Example Circuit - Current Copier

A current copier, as shown in 2.2(c), is comprised of switches and other components. The faults on current-storage transistors and holding capacitors can be modeled as the equivalent faults of the associated switch(es) [12,14,15]. It is also valid in this study based on the defects shown in Figure 3.1(c). More specifically, the following defects may occur in a current-storage transistor: Breaks on gate polysilicon, i.e., Type f3 defect, is equivalent to a S/OFF fault on the associated voltage switch, i.e., Type VS1 fault; Shorten channel width, i.e., Type f4 defect, is equivalent to a Type CS1 fault; Break on metal, either drain or source, i.e., Type fl defect, is equivalent to a S/OFF fault on the associated current switch, i.e., Type CSI fault; Short between drain and gate implies that a S/ON fault on the associated voltage switch, i.e., Type VS2 fault; Short between source and gate, or between drain and source, is equivalent to a S/OFF fault on the associated voltage switch, i.e., Type VS1 fault. Any defects in active region, i.e., Type f5 defect, is equivalent to a Type CS1 fault. Any process deviation causing an increase of on-resistance implies the presence of a Type CS1 fault. The following defects may occur in the holding capacitors: Any defects causing a decrease of capacitance, or an open circuit in the capacitor, is equivalent to a Type VS4 fault on the associated voltage switch. Any defects causing an increase of capacitance, or a short circuit in the capacitor is equivalent to a Type VSI fault.

The above equivalent faults include both catastrophic and parametric faults for both current-storage transistors and the holding capacitors in a copier. Based on the fault types for both current switches and voltage switches, the test generation process for the current copier is described as follows.

Figure 3.2(a) plots the I-V characteristics of  $M_1$  and the load  $S_2$  with and without

Figure 3.2 (a) Simulation results of I-V plot of  $M_1$  with load lines for  $S_2$ ; and (b) fault behavior and switching sequence.

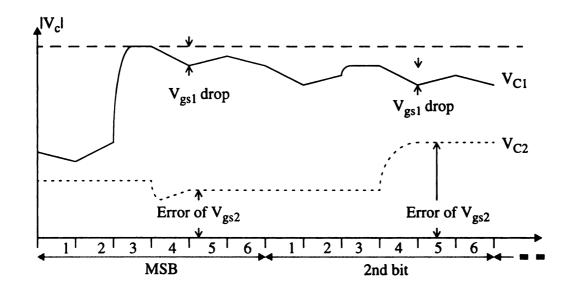

faults, where the aspect ratio of  $M_1$  is (W/L)=6 $\mu$ m/4 $\mu$ m. The copier including  $S_2$  and  $M_1$  can be treated as an amplifier with a switch which acts as a voltage control active load. For a fault-free current copier,  $M_1$  can store a current of 100 $\mu$ A when the switch is on and  $V_{GS}$ =2.5V. Figure 3.2(b) illustrates the behaviors of faulty and fault-free copiers with the application of the test sequence. The test sequence is comprised of three steps, or six clock cycles, and can detect all types of switch faults, i.e., *Types CS1-CS3* and *VS1-VS4 faults*. It also shows the test currents with the switching sequences for both switches  $S_2$  and  $S_3$  at each clock cycle.

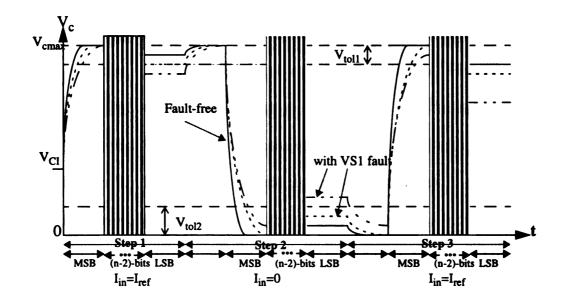

Let  $V_{CI}$  be the initial voltage held in the holding capacitor C, and  $V_{cmax}$  be the maximum voltage across the capacitor. Taking the process variation into account, let  $V_{tol1}$  and  $V_{tol2}$  be the allowable voltage deviations for both  $V_{cmax}$  and 0, respectively. The corresponding current tolerances are  $I_{tol1}=\beta(V_{cmax}-V_{th})^*V_{tol1}$  and  $I_{tol2}=0.5\beta(V_{tol}-V_{th})^2$ , where  $V_{th}$  is the threshold voltage of  $M_1$ . In the first cycle of Step 1, the input current  $I_{in}=0$  is copied and stored in  $M_1$ , where both  $S_2$  and  $S_3$  are on, to discharge the capacitor. Thus, after turning off  $S_3$  in the second cycle of Step 1, the current held in  $M_1$  is compared with an expected zero-current. Step 2 consists of three clock cycles. An input current  $I_{in}=I_{ref}$  is applied and copied to  $M_1$  so that the capacitor is charged up to  $V_{cmax}$  within the clock cycle  $T_{clk}$ . Once the current is copied, both  $S_2$  and  $S_3$  are turned off and the current  $I_{ref}$  is held in  $M_1$  even though the test current is changed in these three clock cycles, as shown in Figure 3.2(b). Thus, at the end of Step 2, the current held in  $M_1$  is compared with an expected current  $I_{ref}$ . Finally, in the Step 3, when  $I_{in}=0$  and both  $S_2$  and  $S_3$  are off, a zero-current is expected for fault -free circuit.

M<sub>1</sub> is expected to hold a zero-current at the end of the 2nd cycle of Step 1,

unsuccessful test implies the existence of a *Type VS1*, *VS2*, or *VS3* fault. More specifically, the presence of a *Type VS1* or *VS3* fault causes an intolerable time constant  $\tau_{on}$  which may be too short to discharge the capacitor so that the voltage across the capacitor exceeds  $V_{tol2}$ . On the other hand, a *Type VS2* or *VS3* fault produces an intolerable leakage current and results in a current held in  $M_1$  to exceed  $I_{tol2}$ .

If the copier passes the test in Step 1, the test pattern and clock sequence in Step 2 are applied. At the end of the 3rd cycle in Step 2, for fault-free circuit, the current held in  $M_1$  is expected to be  $I_{ref}$ , i.e., the voltage across the capacitor is expected to be between (V<sub>cmax</sub>-V<sub>tol1</sub>) and V<sub>cmax</sub>. Unsuccessful test implies the existence of a Type VS1-VS4, CS1 or CS3 fault. More specifically, an intolerable time constant  $\tau_{on}$  caused by a Type VS1 or VS3 fault may be too short to charge up the capacitor and result that the voltage across the capacitor is below (V<sub>cmax</sub>-V<sub>tol1</sub>). On the other hand, during the second cycle of Step 2, for fault-free circuit, switches  $S_2$  is on and  $S_3$  is off, the test current is changed from  $I_{ref}$  to 0, where the current held in  $M_1$  is still  $I_{ref}$ , i.e., the voltage across the capacitor is  $V_{cmax}$ . Since the output of the amplifier is zero, the voltage across  $S_3$  is also  $V_{cmax}$ . However, when  $S_3$ is off, an intolerable leakage current caused by a Type VS2 or VS3 fault will discharge the capacitor so that the voltage across it is below (V<sub>cmax</sub>-V<sub>tol1</sub>). Even though the test current is changed back to  $I_{ref}$ , the leakage current may continuously discharge the capacitor, as shown in Figure 3.2(b). Since a Type VS4 fault causes excess charge flows at the moment when  $S_3$  is off, the fault is identified if the voltage across the capacitor exceeds  $V_{cmax}$ .

Finally, as illustrated in Figure 3.2(a), a *Type CS1* or *CS3* fault causes the maximum current which can be stored in  $M_1$  being reduced. Hence, when  $I_{in}=I_{ref}$  is applied, the fault is identified if the current held in  $M_1$  is less than  $(I_{ref}-I_{toll})$ . Finally, unsuccessful test for

Figure 3.3 Built-in tester: (a) schematic; (b) switching sequence; and (c) fault simulation results.

Step 3 identifies a Type CS2 or CS3 fault. Since the fault causes an intolerable leakage current when  $S_2$  is off, the fault is identified if a non-zero leakage current is detected. This concludes that the test sequence in Figure 3.2(b) detects Type VS1-VS4 and CS1-CS3 faults.

In the above test process, a tester is needed to compare the current held in  $M_1$  to 0 in Step 1 and  $I_{ref}$  in Step 2. The tester, as shown in Figure 3.3(a), is comprised of a current copier, a window comparator, and a D-flip-flop, and its switching sequence is illustrated in Figure 3.3(b). Let  $I_{M1}$  denote the current held in  $M_1$ . Turning on  $S_1$  and  $S_2$  causes a difference current  $I_x = I_{in} - I_{M1}$ . Turning on  $S_a$  and  $S_b$  will copy a current ( $I_{ref} + I_x$ ) to  $M_T$  and virtual ground  $V_y$ . A zero current or  $I_{ref}$  is applied from the input source through  $S_1$  when  $I_{M1}$  is compared to a 0 or a  $I_{ref}$ . Applying a zero current is equivalent to turning off  $S_1$ . Closing  $S_a$  and  $S_b$ , then, will lead to a shift of  $V_y$  from 0. The voltage  $V_y$  is compared with the threshold voltages  $V_1$  and  $V_2$  of the window comparator. The output is defined as:  $V_0$ =0 if  $V_2 < V_y < V_1$ , and  $V_0$ =1 otherwise. Let  $I_{tol}$  be the tolerance of  $I_{I_x}I$ , then the values  $V_y$  and  $V_{tol2}$  can be expressed in terms of  $I_{tol}$  as follows,

$$v = V_1 = -V_2 = I_{tol} / [I_{ref} * (\lambda_n + \lambda_p)]$$

$$V_y = -I_x / [I_{ref} * (\lambda_n + \lambda_p)]$$

$$V_{tol1} = I_{tol} / \sqrt{2I_{ref}\beta_n}$$

$$V_{tol2} = V_{th} + \sqrt{2I_{tol}/\beta_n}$$

If  $I_x=0$ , the voltage  $V_y$  is equal to 0. On the other hand, if a current equal to or greater than  $I_{tol}$ , by the above equations,  $|V_y| \ge v$ , and thus  $V_o=1$ . Thus, the digital data Q=0 means the comparison is asserted, and Q=1, otherwise.

Figure 3.3(c) shows the simulation results of the circuit in Figure 3.3(a), where the transistor size is W/L=6 $\mu$ m/4 $\mu$ m for both M<sub>1</sub> and M<sub>T</sub>,  $I_{ref}$ =100 $\mu$ A, and V<sub>1</sub>=-V<sub>2</sub>=v=0.1V. The process parameters are  $\lambda_n$ =1.991479e-2,  $\lambda_p$ =4.921086e-2, V<sub>th</sub>=0.822163, k<sub>p</sub>=4.89376e-5, and  $\beta_n$ =k<sub>p</sub>\*(6/4)=7.3406e-5. Thus, we obtain  $I_{tol}$ =0.69126 $\mu$ A, V<sub>tol1</sub>=5.7mV, and V<sub>tol2</sub>=0.9594V. Results show that Step 1 takes 1 cycle to initialize the circuit, 2 cycles to force a zero current to be held in N<sub>1</sub>, and 1 cycle to compare the result, Step 2 takes 2 cycles to keep  $I_{ref}$  and 1 cycle to compare the result, and Step3 takes 2 cycles. Results conclude that Type VS1-VS3 faults can be detected in Steps 1 and 2, Step 2 also detects Type VS4, CS1 and CS3 faults, and Step 3 detects Type CS2 and CS3 faults.

# 3.2.2 Example Circuit - ADC

In the test generation process for current copier, the emphasis was placed on generating a test sequence that maximizes the error effects caused by failure switch(es). However, for ADC, the emphasis should be on maximizing the accumulated error generated at each conversion step. Based on the accumulated errors, a test sequence is generated to excite the fault and the fault effects are observed from the converted digital data.

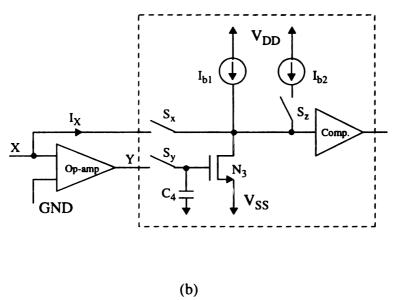

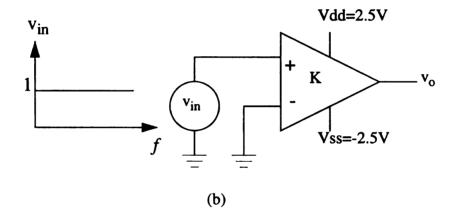

Consider the ADC in Figure 3.4(a) [23] with a comparator in Figure 3.4(b). In the comparator, a current copier consisting of  $N_3$ ,  $C_4$  and switches  $S_x$  and  $S_y$ , is used as a load to copy the difference current  $I_x$ . Since the difference current may be positive or negative, a bias current source  $I_{b1}$  is used to keep a positive current to be copied to  $N_3$ . A current which is slightly higher than  $I_{ref}$  is chosen for  $I_{b1}$ . The copier memorizes the current  $I_x$  and produces a voltage deviation to compare to a zero-voltage in the comparator. Since the

Figure 3.4 Test structure for SI algorithmic ADC: (a) schematic diagram; and (b) comparator.

resolution of an ADC is 0.5LSB, or  $0.5I_{ref}$ , here a simple comparator instead of window comparator, can be used. It should be noted that an additional bias current  $I_{b2}=I_{ref}$  and the switch  $S_z$  are used only for testing purpose. During the normal operation,  $S_z$  is off and the bias current is isolated from the converter circuit. Thus, the extra circuitry does not affect the performance of the converter. The function of this extra circuitry will be explained shortly. Just like current copier, the current switch and voltage switch are also used in ADC.

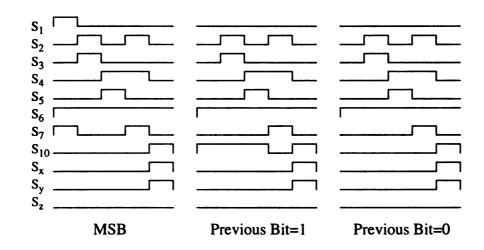

In Figure 3.4,  $S_1$ ,  $S_2$ ,  $S_4$ ,  $S_6$ ,  $S_{10}$ ,  $S_x$ , and  $S_z$  are current switched, while  $S_3$ ,  $S_5$ ,  $S_7$ , and  $S_y$  are voltage switches. The ADC consists of four copiers. One may apply the test sequence developed in the previous section for all copiers in the ADC. However, in the ADC, we can only observe the result from the output of the comparator, i.e., the converted digital data. Thus, the test sequence should be generated to maximize the accumulated errors so that the error effect can be reflected to the converted digital data.

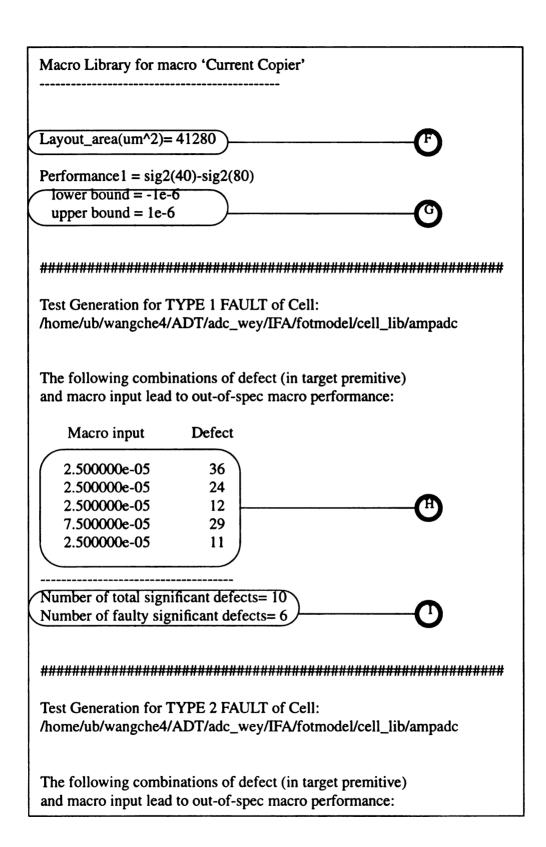

As discussed in Section 3.2.1, the current switch faults,  $Type\ CS1\text{-}CS3$  faults, can be detected by applying a test current  $I_{ref}$ . when  $I_{in}=I_{ref}$  is applied, a  $Type\ CS1$  or CS3 fault at  $S_2$  is identified if the current held in  $N_1$  is less than  $(I_{ref}-I_{tol1})$ . This error will be accumulated so that the converted digital data with the pattern 1...0xx...x, "x" means "don't care", i.e., either 0 or 1, is obtained. On the other hand, with the application of a zero input current, an intolerable leakage current occurs in the presence of a  $Type\ CS2$  or CS3 fault at  $S_2$  when the switch is turned off. The accumulated error will cause the converted digital data pattern to be 0...1xx..x. Thus, both  $I_{ref}$  and 0 detects the current switch faults.