THESIS

This is to certify that the

#### dissertation entitled

## MULTICASTING IN MULTISTAGE INTERCONNECTION NETWORKS

presented by

Chi-Ming Chiang

has been accepted towards fulfillment of the requirements for

PhD degree in Computer Science

...ujo. protes.

Date May 26, 1995

# LIBRARY Michigan State University

PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due.

| DATE DUE  | DATE DUE | DATE DUE |

|-----------|----------|----------|

| 1820 to 1 |          |          |

|           |          |          |

|           |          |          |

|           |          |          |

|           |          |          |

|           |          |          |

|           |          |          |

MSU is An Affirmative Action/Equal Opportunity Institution

## MULTICASTING IN MULTISTAGE INTERCONNECTION NETWORKS

By

Chi-Ming Chiang

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Computer Science

#### ABSTRACT

## MULTICASTING IN MULTISTAGE INTERCONNECTION NETWORKS

By

#### Chi-Ming Chiang

Multicast communication, also known as multi-point communication, refers to the delivery of a message from a single source node to a number of destination nodes. It is a frequently used communication pattern in distributed-memory parallel computers and computer networks. *Multistage interconnection networks* (MINs) have resurged as another popular class of interconnection architecture for constructing scalable parallel computers and high speed network switches. While efficient implementation of multicast communication is critical to the performance of message-based scalable parallel computers and switch-based high speed networks, little research has been devoted to supporting multicast in MINs.

Unlike unicast communication, the size of a header in a multicast message depends on the number of destinations, the distribution of destinations, and the multi-address encoding/decoding schemes. This research suggests and compares six different multi-address encoding/decoding schemes to shorten the header which is an overhead to

the system. Each of them has its own advantages and disadvantages. An appropriate choice of the multi-address encoding scheme depends on the destination pattern and is detailed in this research.

Several efficient multicast algorithms, both hardware and software implementations, for unidirectional wormhole-switched MINs are proposed in this research. The hardware implementation offers better performance than the software approach. Tree-based hardware approaches for wormhole-switched MINs, namely multi-head worms, require special mechanisms to avoid potential deadlocks when there are multiple multicasts. As shown in this research, the hardware approaches to support multicast should be considered in the design of high performance networks. In systems which do not support hardware multicast, multicast must be implemented atop existing unicast communications. This research proposes an efficient unicast-based multicast (or software multicast) algorithm for such systems.

While Banyan MINs are limited to a unique routing path between any source and destination pair, an extra stage MIN can provide extra routing paths. Extra routing paths can reduce the message transmission blocking probability and allow additional flexibility in selecting a routing path. An algorithm to find a traffic-optimal multicast tree in such networks within polynomial time is proposed.

Many new ideas and new algorithms are proposed to support efficient multicast communication in wormhole-switched MINs. Performance evaluation and comparison of different approaches are conducted through extensive simulation experiments. Research results obtained from this work will be extremely useful to parallel computer and network switch designers who wish to support multicast in their designs.

© Copyright 1995 by Chi-Ming Chiang All Rights Reserved To my parents

#### ACKNOWLEDGMENTS

I would like to take this opportunity to express my appreciation to several persons, without whom this dissertation could not have been completed. My achievements, great or little, were possible through their participation. I will always be indebted to my advisor, Lionel M. Ni. He has been my mentor, my colleague, and my friend. His very positive influence on my personal and technical development will carry forward into my future endeavors.

I am very grateful to the other members of my dissertation committee: Herman D. Hughes, Abdol Esfahanian, and Raoul D. LePage, for their valuable comments, help, encouragement, and friendship. I would also like to thank all my colleagues and friends who made my stay at Michigan State University enjoyable.

A person cannot accomplish anything without the help and understanding of family members. I thank my parents, brother, and sisters for their contiguous encouragement, support, patience, and love. I appreciate my host family, Ows, for their help, love, and friendship throughout the course of my master and doctorate work. I proudly share this accomplishment with them all.

Last, but not least, my very special thanks go to my wife Ya-Ping and her family for sustaining me with their everlasting love and understanding.

## TABLE OF CONTENTS

| LI | ST ( | OF TA    | BLES                                       | X   |

|----|------|----------|--------------------------------------------|-----|

| LI | ST ( | OF FIG   | GURES                                      | хi  |

| 1  | Intr | oducti   | on                                         | 1   |

|    | 1.1  | Worml    | hole Switching                             | 4   |

|    | 1.2  |          | tage Interconnection Networks              | 5   |

|    | 1.3  |          | ation and Problem Definition               | 5   |

|    | 1.4  |          | mance Metrics                              | 13  |

|    | 1.5  |          | tives and Thesis Outline                   | 14  |

| 2  | Mu   | lti-Add  | lress Encoding                             | 18  |

|    | 2.1  | Heade    | r Encoding Design Considerations           | 19  |

|    | 2.2  | Multi-   | Address Encoding Schemes                   | 21  |

|    |      | 2.2.1    | All-Destination Encoding                   | 21  |

|    |      | 2.2.2    | Bit String Encoding                        | 22  |

|    |      | 2.2.3    | Multiple Region Broadcast                  | 23  |

|    |      | 2.2.4    | Multiple Region Stride                     | 25  |

|    |      | 2.2.5    | Multiple Region Mask                       | 27  |

|    |      | 2.2.6    | Multiple Region Bit String                 | 28  |

|    | 2.3  | Multi-   | Address Decoding                           | 29  |

|    |      | 2.3.1    | All Destination Decoding                   | 31  |

|    |      | 2.3.2    | Bit String Decoding                        | 33  |

|    |      | 2.3.3    | Multiple Region Broadcast Decoding         | 34  |

|    |      | 2.3.4    | Multiple Region Stride Decoding            | 35  |

|    |      | 2.3.5    | Multiple Region Mask Decoding              | 37  |

|    |      | 2.3.6    | Multiple Region Bit String Decoding        | 37  |

|    | 2.4  | Summ     | ary                                        | 39  |

| 3  | Mu   | ltistage | e Interconnection Networks                 | 40  |

|    | 3.1  | Switch   | es                                         | 41  |

|    | 3.2  | Netwo    | rk Topology                                | 42  |

|    | 3.3  |          | Architecture                               | 45  |

|    | 3.4  | Decodi   | ing in Multistage Interconnection Networks | 4.5 |

|    |      | 3.4.1    |                                            | 49  |

|   |     | 3.4.2 Bit String Decoding                                        | 51         |

|---|-----|------------------------------------------------------------------|------------|

|   |     | 3.4.3 Multiple Region Broadcast Decoding                         | 53         |

|   |     | 3.4.4 Multiple Region Stride Decoding                            | <b>5</b> 4 |

|   |     | 3.4.5 Multiple Region Mask Decoding                              | 56         |

|   |     | 3.4.6 Multiple Region Bit String Decoding                        | 57         |

|   | 3.5 | Performance of Multi-Address Encoding and Decoding on Multistage |            |

|   |     | Interconnection Networks                                         | 59         |

|   | 3.6 | Summary                                                          | 64         |

| 4 | Har | ware Multicast Wormhole-Switched                                 | 66         |

|   | 4.1 | Implementation of Multi-head Worms                               | 67         |

|   | 4.2 | The Synchronous Multi-head Worm                                  | 73         |

|   | 4.3 | Multi-address Encoding                                           | 78         |

|   | 4.4 | Performance and Comparison                                       | 82         |

|   | 4.5 | Summary                                                          | 88         |

| 5 | Not | ork Partitionability and Traffic Localization                    | 89         |

| J | 5.1 | Influence of Traffic Localization                                | 90         |

|   | 5.2 | Definition of Different Cubes                                    | 94         |

|   | 5.3 | Contention Free and Channel Balanced Partition                   | 96         |

|   | 5.4 |                                                                  | 102        |

|   | 5.5 |                                                                  | 105        |

|   | 0.0 |                                                                  | 106        |

|   |     |                                                                  | 108        |

|   | 5.6 | •                                                                | 111        |

|   | 5.7 |                                                                  | 115        |

| 6 | Evt | a Stage Multistage Interconnection Networks                      | 117        |

| U | 6.1 | MINs with Extra Stages                                           |            |

|   | 0.1 |                                                                  | 119        |

|   | 6.2 |                                                                  | 121        |

|   | 0.2 |                                                                  | 121        |

|   |     |                                                                  | 124        |

|   | 6.3 |                                                                  | 126        |

|   | 0.0 |                                                                  | 127        |

|   |     |                                                                  | 128        |

|   |     | S i                                                              | 130        |

|   |     | • •                                                              | 131        |

|   |     |                                                                  | 132        |

|   | 6.4 |                                                                  | 134        |

|   | 0.1 | _                                                                | 135        |

|   |     | <u>g</u>                                                         | 137        |

|   |     |                                                                  | 138        |

|   | 6.5 | -                                                                | 142        |

|   | 5.5 | 6.5.1 Simulation Description                                     | 14.        |

|    |      | 6.5.2 Dimension Patterns and Output Parameters                   | 143   |

|----|------|------------------------------------------------------------------|-------|

|    |      | 6.5.3 Plots and Observations                                     | 144   |

|    | 6.6  | Summary                                                          | 147   |

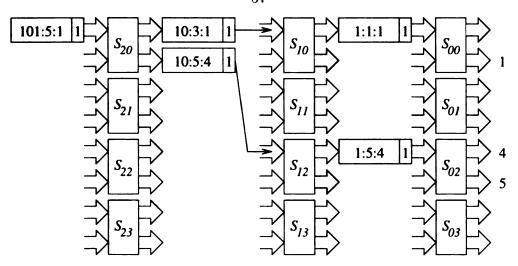

| 7  | Soft | tware-based Multicast                                            | 149   |

|    | 7.1  | Issues in Multicast Communication                                | 149   |

|    | 7.2  | Multicast Algorithm                                              | 153   |

|    | 7.3  | Non-Optimal Multicast in Baseline and Butterfly Networks         | 157   |

|    | 7.4  | The C-min Algorithm                                              | 159   |

|    | 7.5  | Performance Evaluation                                           | 163   |

|    | 7.6  | Summary                                                          | 167   |

| 8  | Rel  | ated Work                                                        | 169   |

|    | 8.1  | MIN-based ATM Switches                                           | 171   |

|    | 8.2  | Hardware Multicast                                               | 177   |

|    |      | 8.2.1 Path-based Multicast                                       | 177   |

|    |      | 8.2.2 Trip-Based Multicast                                       | 179   |

|    |      | 8.2.3 A Multidestination Worm Conforming to Base Routing Schemes | s 180 |

|    |      | 8.2.4 Synchronous Receiver Initiated Multicast                   | 181   |

|    | 8.3  | Software Multicast                                               | 182   |

|    | 8.4  | Summary                                                          | 185   |

| 9  | Cor  | nclusions and Future Work                                        | 187   |

|    | 9.1  | Research Contributions                                           | 187   |

|    | 9.2  | Directions for Future Research                                   | 190   |

| Bl | IBLI | OGRAPHY                                                          | 192   |

## LIST OF TABLES

| 3.1 | Number of flits in a   | header based on    | various multi-address | encoding |     |

|-----|------------------------|--------------------|-----------------------|----------|-----|

|     | schemes. A header      | consists of a cour | iter and addresses    |          | 61  |

| 6.1 | Patterns of this study |                    |                       | 1        | 143 |

## LIST OF FIGURES

| 1.1  | Broadcast 100 integers from process 0 to every process in the group 2                  |

|------|----------------------------------------------------------------------------------------|

| 1.2  | The framework                                                                          |

| 1.3  | Path-based hardware multicast                                                          |

| 1.4  | Tree-based hardware multicast                                                          |

| 1.5  | An asynchronous multicast tree                                                         |

| 1.6  | A synchronous multicast tree                                                           |

| 2.1  | The message header format of six address encoding schemes                              |

| 2.2  | Single region broadcast and single region stride, where the source node is             |

|      | 0 and the destination sets are $\{4, 5, 6\}$ and $\{1, 3, 5\}$ , respectively 24       |

| 2.3  | Multicast to the same row and column in (a) 2D mesh and (b) linear array architectures |

| 2.4  | (a) A generic switch/router with four input/output ports, and the message              |

|      | is forwarded via both output ports 1 and 3. (b) The receiving of                       |

|      | a duplicated message when the header is not handled properly and                       |

|      | alternate routing paths are allowed                                                    |

| 2.5  | All destination decoding algorithm                                                     |

| 2.6  | An example of all-destination decoding                                                 |

| 2.7  | Buffered bit string decoding algorithm                                                 |

| 2.8  | An example of buffered bit string decoding                                             |

| 2.9  | An example of hierarchical bit string decoding                                         |

| 2.10 | Multiple region broadcast decoding algorithm                                           |

| 2.11 | An example of multiple region broadcast decoding                                       |

| 2.12 | An example of multiple region stride decoding                                          |

|      | An example of multiple region mask decoding                                            |

| 2.14 | Multiple region bit string decoding algorithm                                          |

|      | An example of multiple region bit string decoding                                      |

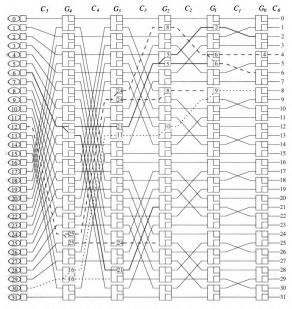

| 3.1  | A generic MIN structure with $N = k^n$ input/output ports and $n$ stages.              |

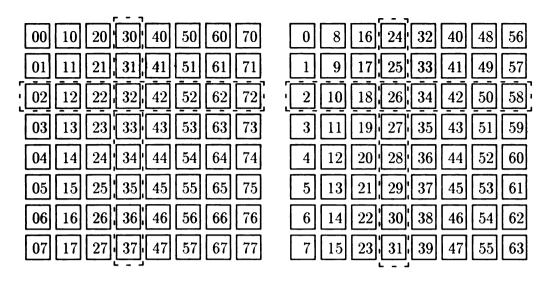

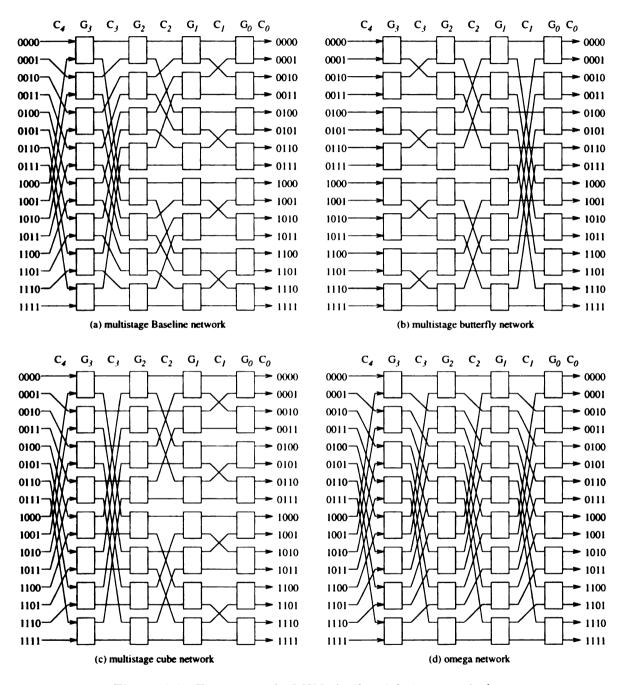

| 3.2  | Four 16-node MINs built with $2 \times 2$ switches                                     |

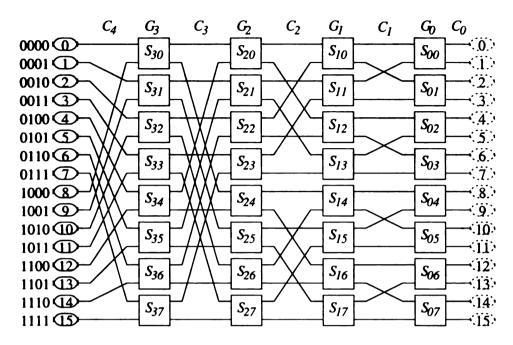

| 3.3  | A $16 \times 16$ cube network built with $2 \times 2$ switches                         |

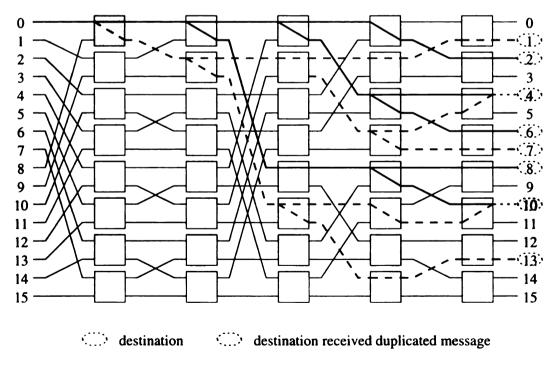

| 3.4  | A duplicated receiving when there are alternative paths, in an extra stage             |

|      | MIN, between source and destination nodes                                              |

| 3.5  | All address decoding algorithm                                                         |

| 3.6  | An example of all-destination decoding                                                 |

| 3.7  | The algorithm of bit string decoding schemes for MIN                                   |

| 3.8  | An example of buffered bit string decoding                                             |

| 3.9  | An example of hierarchical bit string decoding                                                                                                                                       | 53  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.10 | Multiple region broadcast decoding algorithm                                                                                                                                         | 54  |

| 3.11 | An example of multiple region broadcast decoding                                                                                                                                     | 55  |

| 3.12 | An example of multiple region stride decoding                                                                                                                                        | 55  |

| 3.13 | Define a subcube in a MIN                                                                                                                                                            | 56  |

| 3.14 | An example of multiple region mask decoding                                                                                                                                          | 57  |

| 3.15 | Multiple region bit string decoding algorithm for MIN                                                                                                                                | 58  |

| 3.16 | An example of multiple region bit string decoding                                                                                                                                    | 58  |

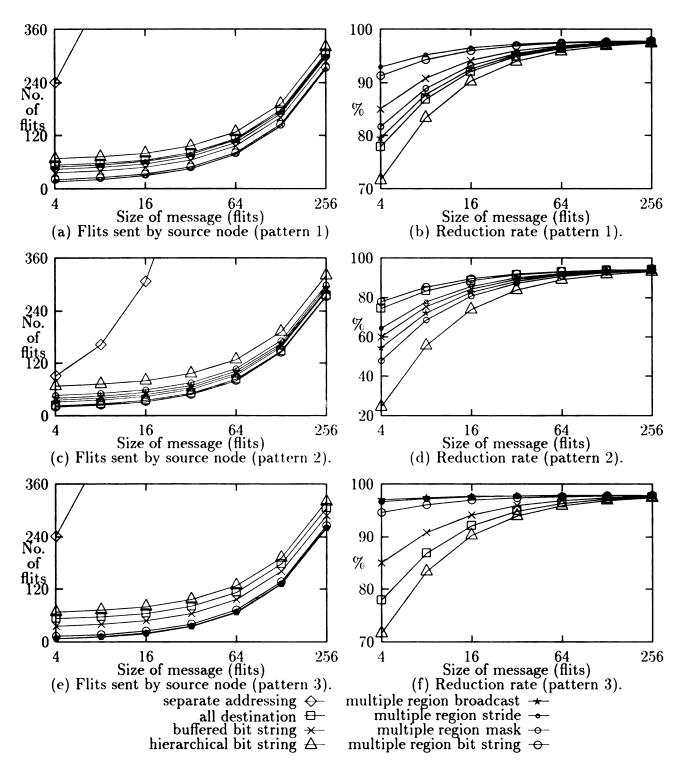

| 3.17 | The length of header and reduction rate on different destination patterns vs different multi-address encoding/decoding schemes                                                       | 62  |

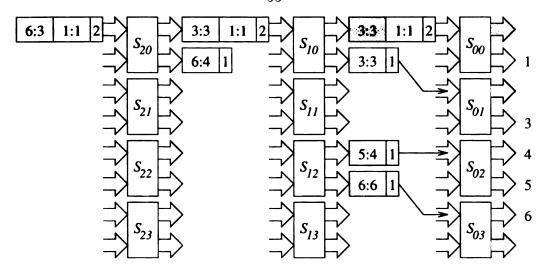

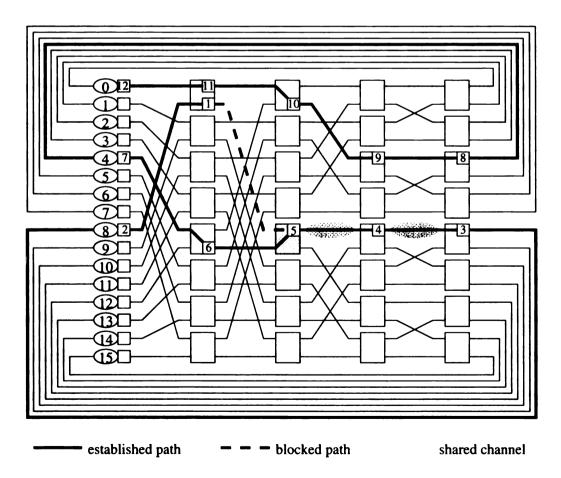

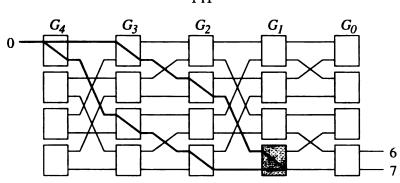

| 4.1  | An example of deadlock for a path-based multicast on a 16-node multistage cube network                                                                                               | 68  |

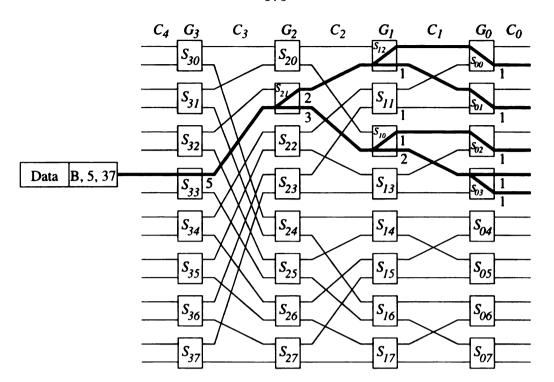

| 4.2  | An example to establish a wormhole-switched multicast tree, where the shadow box represents the header flit and white box stands for data flits.                                     | 70  |

| 4.3  | Establishment of an asynchronous multi-head worm with network contention                                                                                                             | 71  |

| 4.4  | An example of a deadlock situation with two multi-head worms, where the bold line represents the multi-head worm $T_0$ and the dotted line stands for $T_6$                          | 72  |

| 4.5  | Establishment of a synchronous multi-head worm with network contention.                                                                                                              | 74  |

| 4.6  | Two multi-head worms requesting common channels to achieve destination sets may cause deadlock or starvation.                                                                        | 74  |

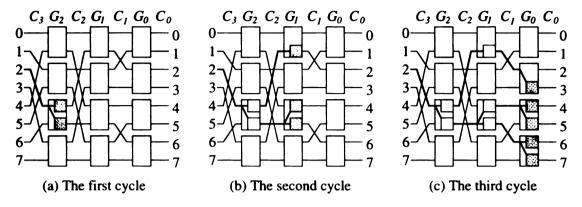

| 4.7  | A deadlock example with all-destination encoding/decoding scheme with 3 synchronous multi-head worms, where the destination information carried by a flit is numbered within the box | 81  |

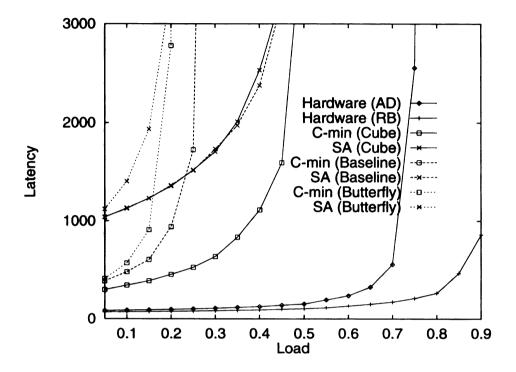

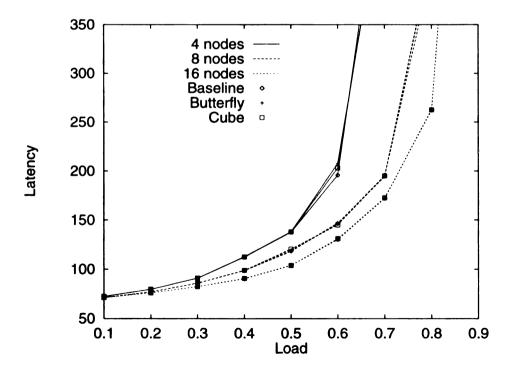

| 4.8  | Comparison among hardware and software implementations                                                                                                                               | 84  |

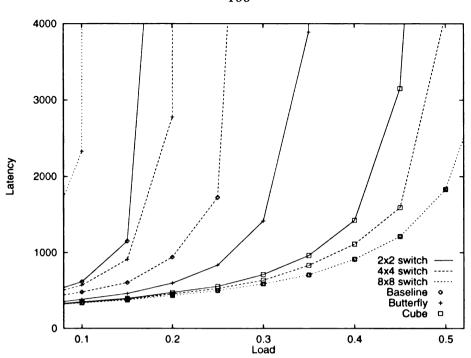

| 4.9  | Latency comparison of different switch sizes and different number of destinations on a cube network                                                                                  | 85  |

| 4.10 | Comparison on a butterfly network with different sized switches and a different number of destinations                                                                               | 86  |

| 4.11 | Latency comparison of the different number of nodes in each cluster                                                                                                                  | 86  |

| 4.12 | Comparison between the region broadcast and pseudo all-destination encoding schemes                                                                                                  | 87  |

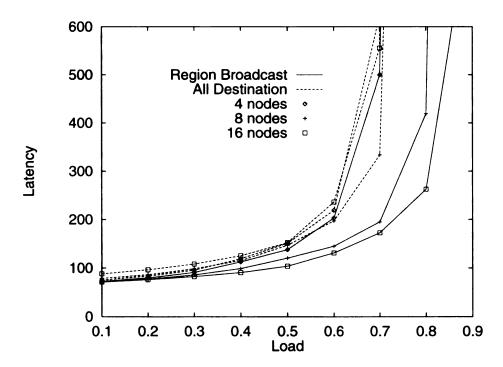

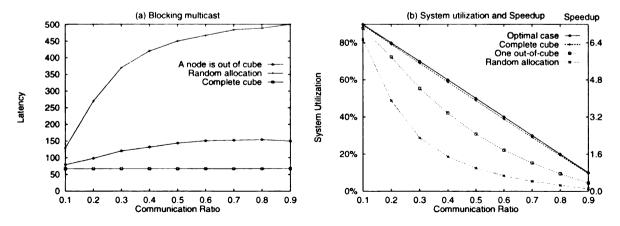

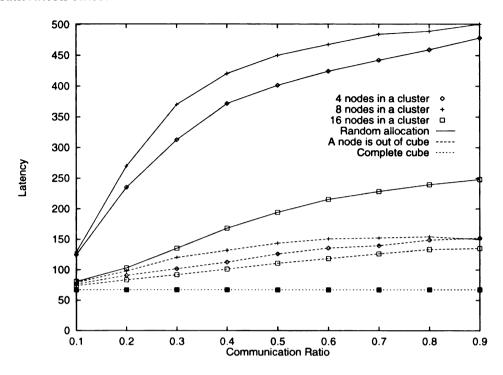

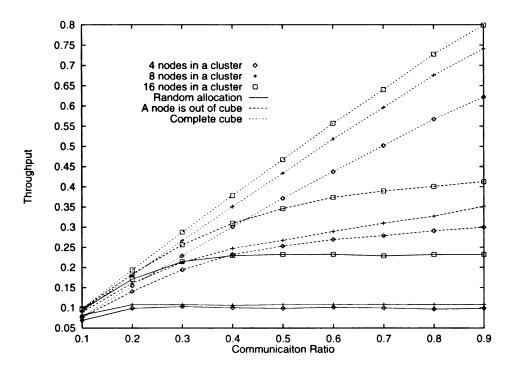

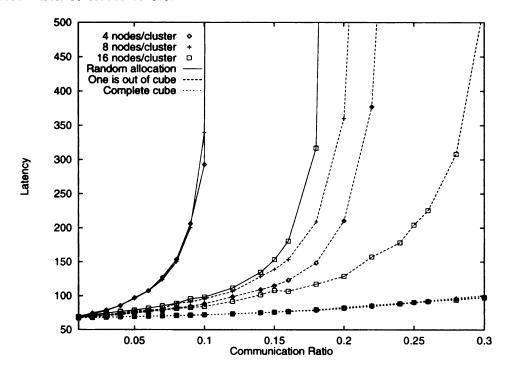

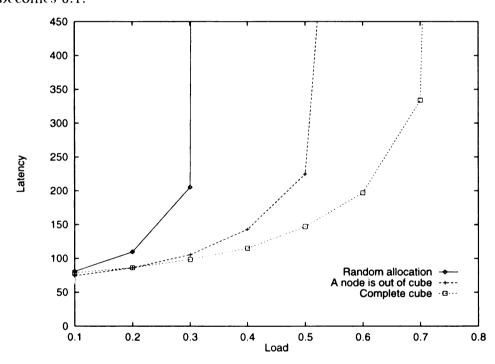

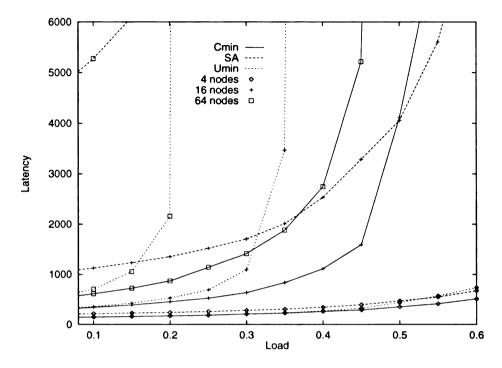

| 5.1  | Average latency and associated system utilization of a blocking multicast message on a 64-node cube network                                                                          | 92  |

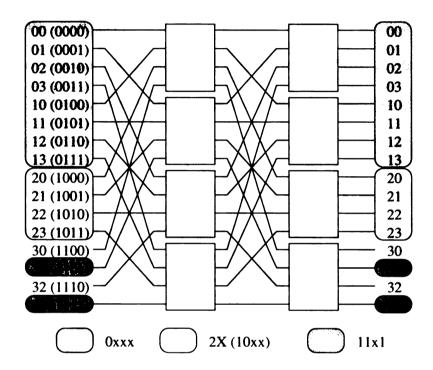

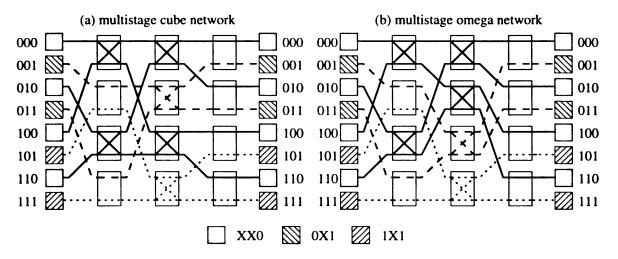

| 5.2  | Three different processor clusters, $0xxx$ , $10xx$ or $2X$ , and $11x1$                                                                                                             | 96  |

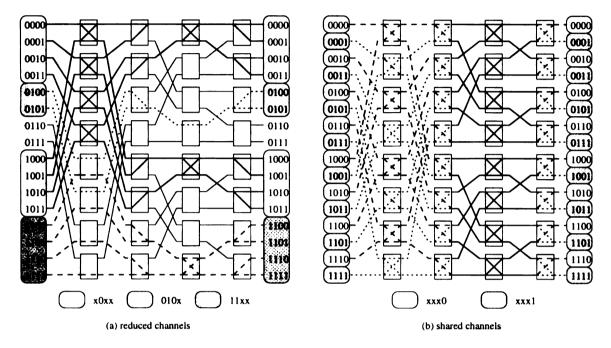

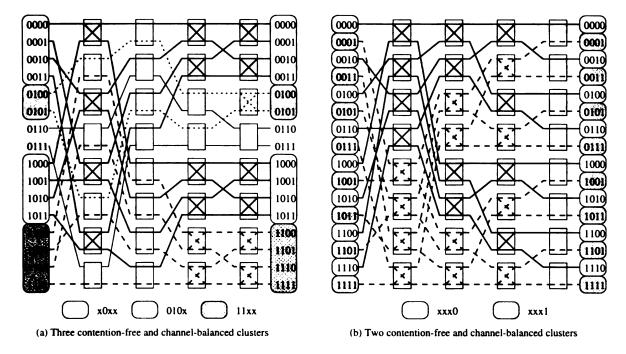

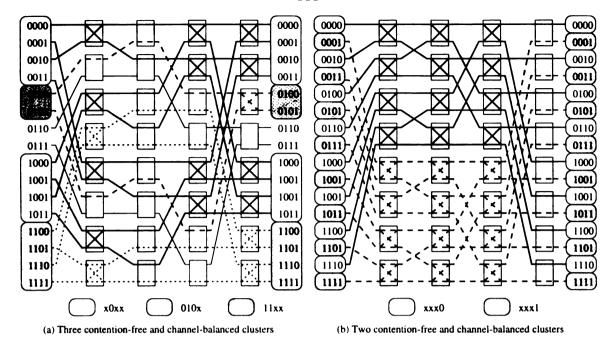

| 5.3  | A 16-node cube network based on $4 \times 4$ switches is partitioned into four contention-free and channel-balanced binary cube clusters, $x0xx$ , $01xx$ ,                          | 100 |

| 5.4  | An 8-node cube network and an 8-node omega network are partitioned                                                                                                                   | 101 |

| 5.5  | •                                                                                                                                                                                    | 101 |

| 5.6  |                                                                                                                                                                                      | 104 |

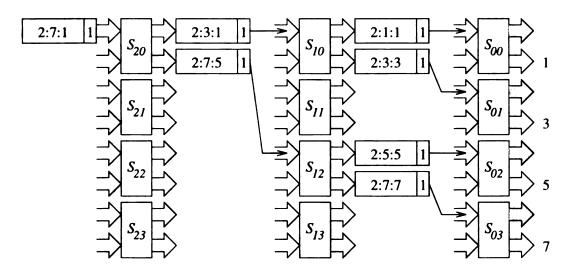

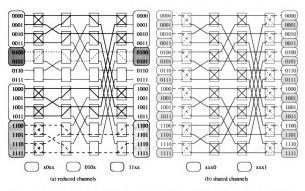

| 5.7  | An example to partition a 16-node modified baseline network into contention-free and channel-balanced disjoint k-ary cubes | 108 |

|------|----------------------------------------------------------------------------------------------------------------------------|-----|

| 5.8  | An example to partition modified butterfly network into contention-free                                                    |     |

|      | and channel-balanced disjoint k-ary cubes                                                                                  | 111 |

| 5.9  | Average latency of a blocking multicast message with various intertask                                                     |     |

|      | contention                                                                                                                 | 112 |

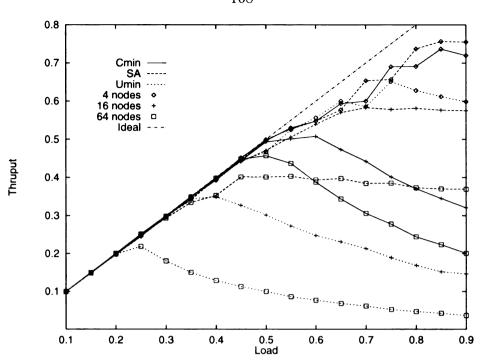

|      | Average throughput in cube network with average 64-flit messages.                                                          | 113 |

| 5.11 | Average latency in cube network of non-blocking message with average 64-flit length                                        | 114 |

| 5.12 | Average latency in cube network of non-blocking message with multiple                                                      | 111 |

|      | sources                                                                                                                    | 115 |

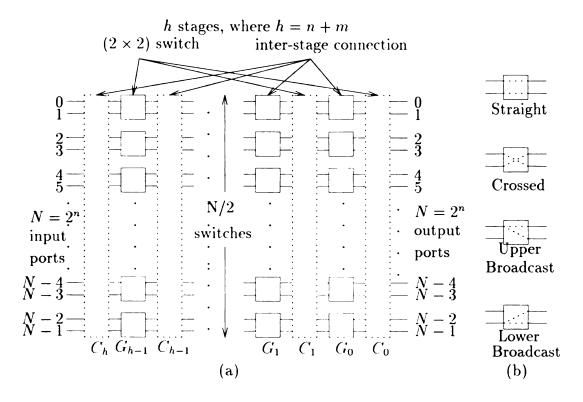

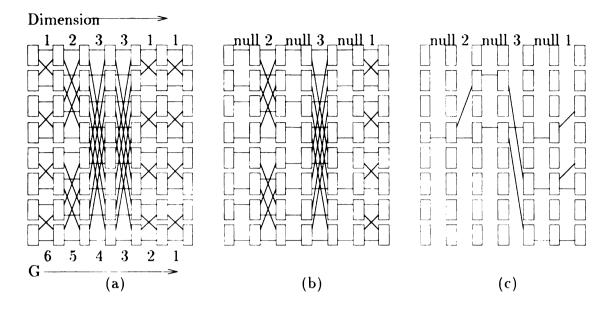

| 6.1  | A generic MIN structure with $N=2^n$ input/output ports and $h$ stages,                                                    |     |

|      | where each $2 \times 2$ switch has four connectivity choices                                                               | 118 |

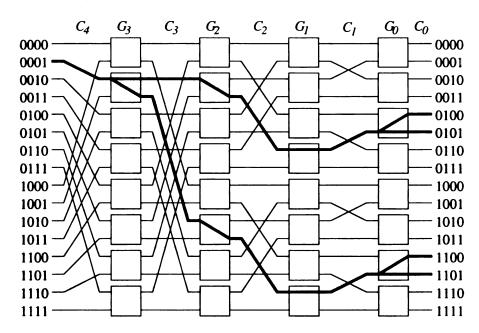

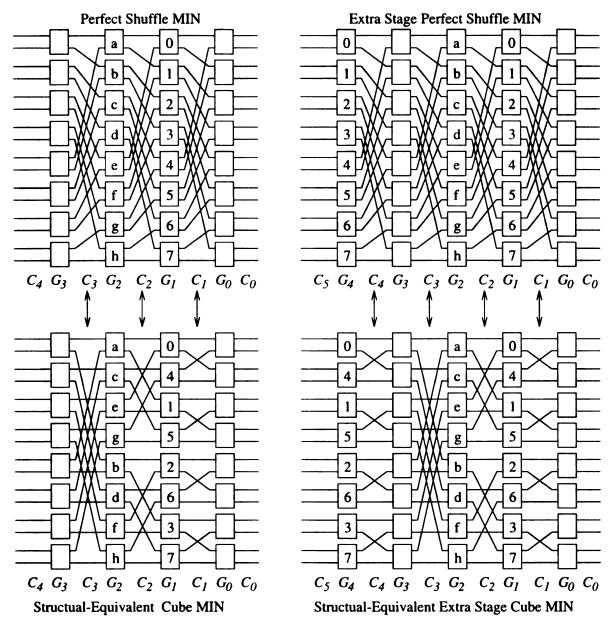

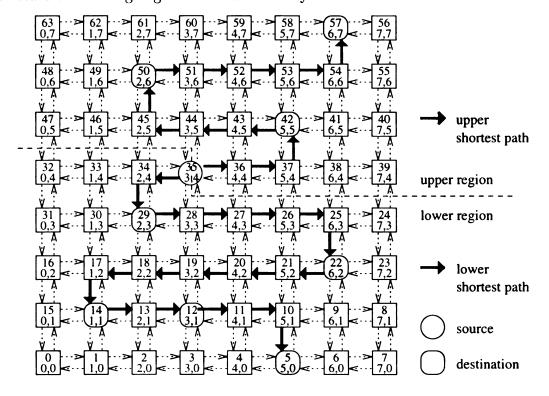

| 6.2  | Structural equivalence between (a) PS-MIN(16) and CU-MIN(16) and (b) PS-ESMIN(16:5) and CU-ESMIN(16:1,3,2,1,0)             | 122 |

| 6.3  | An example of the inadequacy of the traditional routing approach (source                                                   |     |

|      | ⊕ destination): A source node 1 to destination node 2 route does not                                                       |     |

|      | lead to the right destination                                                                                              | 128 |

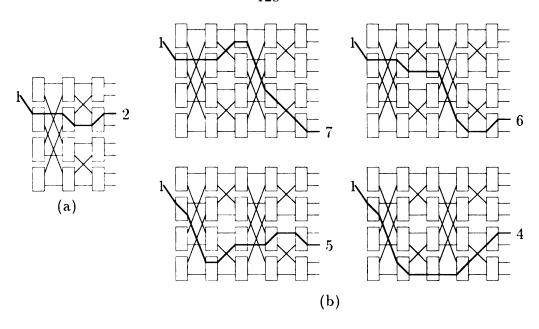

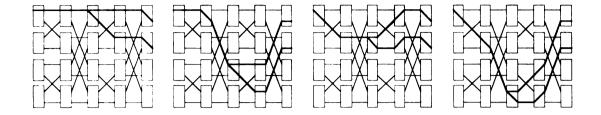

| 6.4  | The four optimal multicast trees in an ESMIN(8:1,2,1,2,0)                                                                  | 134 |

| 6.5  | The eight optimal multicast trees in an ESMIN(8:1,1,2,2,0)                                                                 | 134 |

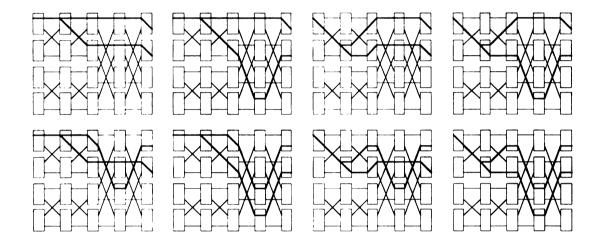

| 6.6  | Latest-Branch multicast algorithm illustration: a) CU-                                                                     |     |

|      | $ESMIN(16:1,2,3,3,1,1,0)$ , b) Construction of the CU- $ESMIN^1$ by                                                        |     |

|      | seeking the rightmost occurrence of each dimension and marking                                                             |     |

|      | the remaining stages as 'horizontal.' Horizontal stages merely                                                             | 100 |

| c 7  | carry-forward the data. c) Example multicast in the CU-ESMIN <sup>1</sup>                                                  | 136 |

| 6.7  | An example of blocking in multicast tree construction by the RB algorithm.                                                 |     |

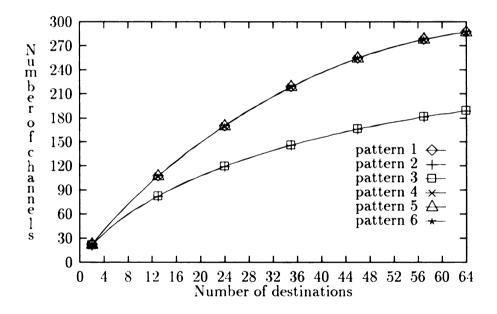

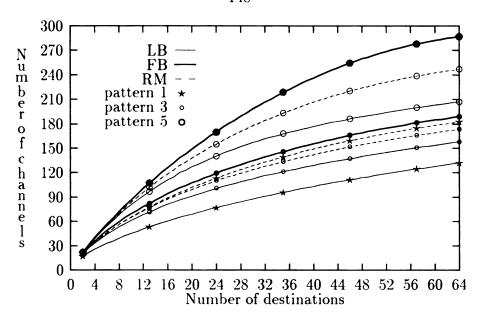

| 6.8  | The number of channels used in the first branch algorithm                                                                  | 144 |

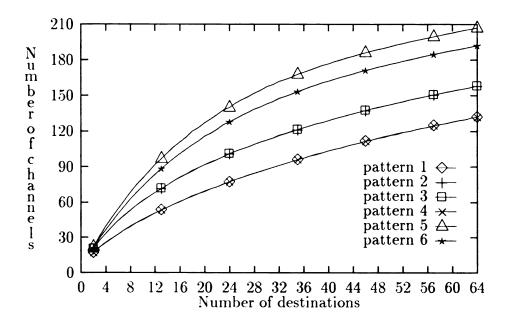

| 6.9  | The number of channels used in the latest branch algorithm                                                                 | 145 |

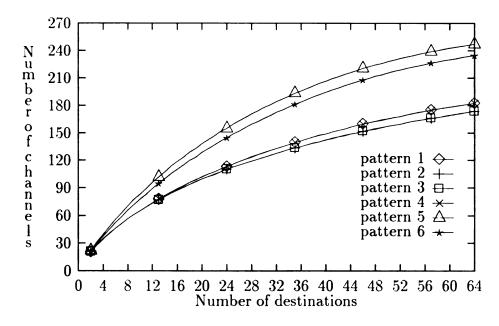

| 6.10 | The number of channels used in the random mapping algorithm                                                                | 145 |

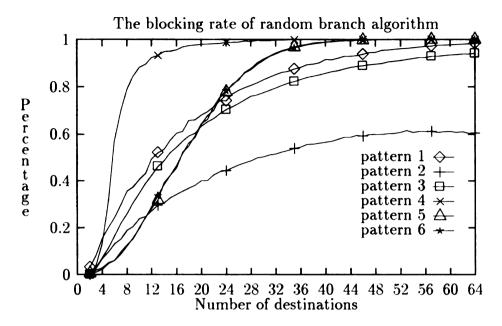

|      | The probability of blocking in random branch algorithm                                                                     | 147 |

| 6.12 | The number of channels used in three non-blocking algorithms                                                               | 148 |

| 7.1  | An example of deadlock in single region broadcast                                                                          | 150 |

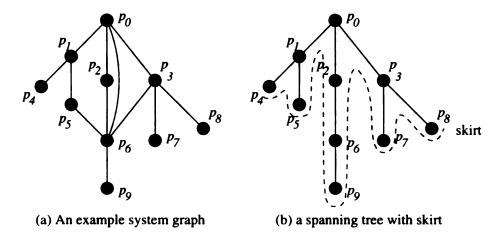

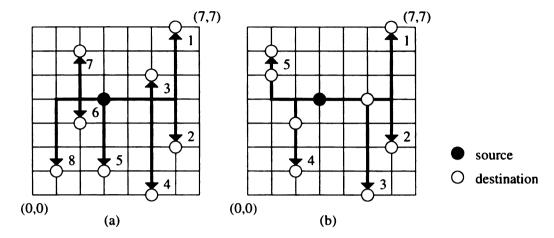

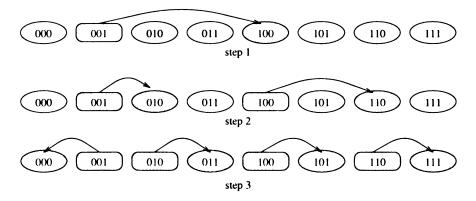

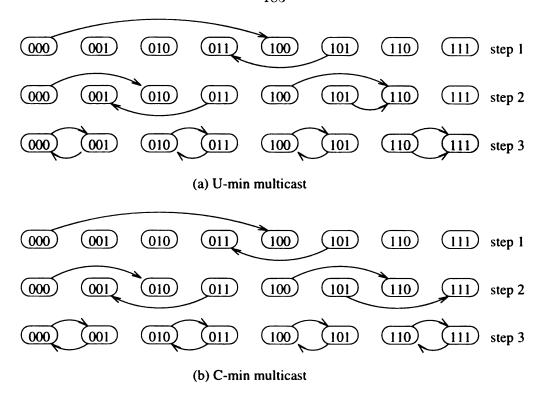

| 7.2  | Unicast-based software multicast trees                                                                                     | 152 |

| 7.3  | The C-min algorithm                                                                                                        | 160 |

| 7.4  | An example of software multicast tree implemented by C-min algorithm.                                                      | 161 |

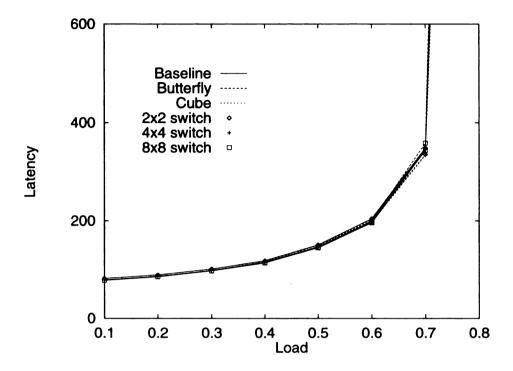

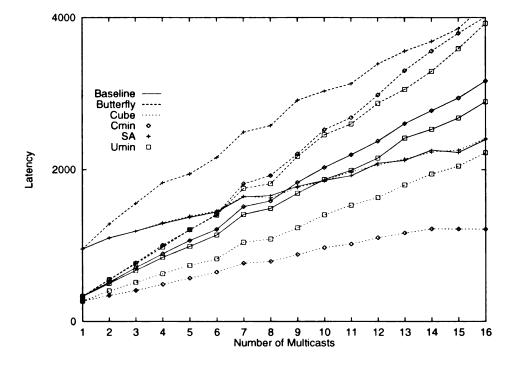

| 7.5  | The latency in blocking multicasts                                                                                         | 164 |

| 7.6  | The latency of C-min algorithm on various networks and various sized switches                                              | 166 |

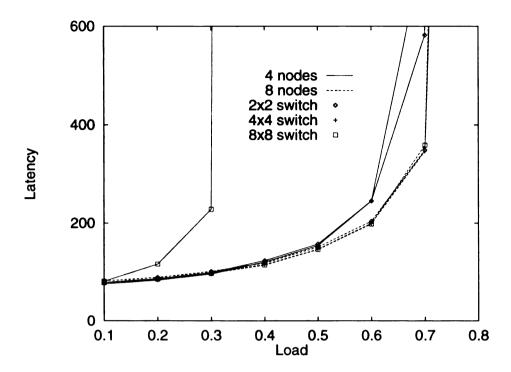

| 7.7  | The latency of various algorithms on a cube network constructed by 4 × 4 switches.                                         | 167 |

| 7.8  | The throughput of various algorithms on cube networks with $4 \times 4$ switches                                           |     |

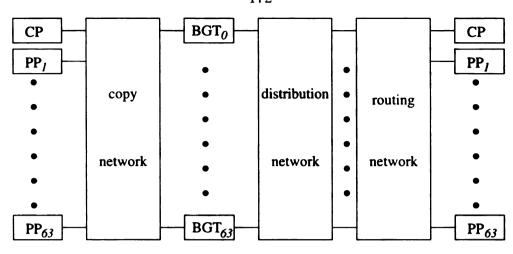

| 8.1  | Switch fabric.                                                                                                             | 172 |

## xiv

| 8.2 | A $16 \times 16$ copy network                                           | 173 |

|-----|-------------------------------------------------------------------------|-----|

| 8.3 | An example of synchronous region broadcast                              | 176 |

| 8.4 | An example of a path-based multicast in a 2-D mesh. The lower pair of   |     |

|     | numbers is the absolute address of a node and the upper number is the   |     |

|     | relative address of the same node based on a Hamiltonian path           | 178 |

| 8.5 | An example of a trip-based multicast                                    | 180 |

| 8.6 | Examples of a multidestination worm conforming to base routing schemes. | 181 |

| 8.7 | An example of a U-min multicast                                         | 183 |

| 8.8 | An example of two multicasts based on U-min and C-min algorithms        | 185 |

|     |                                                                         |     |

## CHAPTER 1

## Introduction

Efficient data communication among processor nodes is critical to the performance of message-based scalable parallel computers (SPCs). Generally data communication can be classified into point-to-point communication and collective communication [1]. While point-to-point communication deals with the basic send and receive operations between two nodes, collective communication deals with communication that involves a group of processes which form a process group. Multiple applications may spaceshare an SPC in a way that processor nodes in the system can be partitioned into several disjoint subsets, namely processor clusters or clusters, each of which is dedicated to a distinct application. Multiple processes may time-share a processor node and multiple process groups may exist in a cluster. Each process group includes a subset of all processes in the cluster. As a result, a system-level multicast service, in which the same message is delivered from a source node to an arbitrary number of destination nodes, is fundamental in supporting collective communication primitives including the application-level broadcast, reduction, and barrier synchronization [2].

Multicast communication is also demanded in high speed networks, such as ATM switches, for various network applications [3, 4] including multimedia applications (e.g., [5]).

For example, the format of the group broadcast in MPI is specified as follows:

MPI\_Bcast(buffer, count, datatype, root, comm)

The parameters buffer, count, datatype, root, and comm represent the data buffer, number of data, data type, source process, and communicator, respectively. The communicator is used to distinguish different process groups since a process can join more than one process group. The message is delivered to every process which owns the specified communicator. Figure 1.1 gives an example that source process 0 forwards an array of 100 integers to all processes in the process group specified by comm. Note that this example only shows partial codes. Some of the variables, such as comm, must have been assigned appropriate values before these codes.

```

MPI_Comm comm;

int array[100];

int root = 0;

...

MPI_Bcast (array, 100, MPI_INT, root, comm);

```

Figure 1.1: Broadcast 100 integers from process 0 to every process in the group.

As indicated in [6], lots of applications require multicast communication. As the scale of application increases, communication becomes a bottleneck and degrades the overall performance [7].

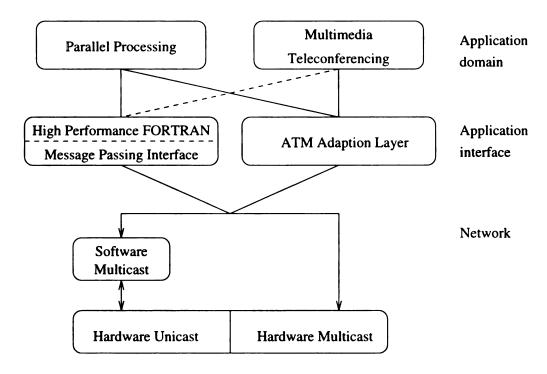

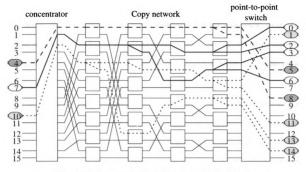

The relationship between different applications, high level parallel languages, communication packages, ATM adaptor layer and networks is shown in Figure 1.2. The message passing interface (MPI) explicitly supports application-level broadcast as well as multicast [1] while High Performance Fortran (HPF) supports these functions implicitly [8]. Both of them rely on the system to provide efficient multicast communication. The interconnection network for these applications can be either a special purpose network or an asynchronous transfer mode (ATM) network.

Teleconferencing, multimedia, and interactive television are some newly emerging and natural applications for multicast communication. As long as there are more than two parties communicating in a teleconference, multicast communication is required. Although the source may send multiple copies of the message individually (one for each party), the scalability of such an approach is limited by the bandwidth, and the latency among different parties may become intolerable. Efficient multicast support becomes a critical issue for the success of these applications.

Figure 1.2: The framework

As shown in Figure 1.2, teleconferencing, multimedia and interactive TV are basically based on the ATM network. The current knowledge of multicast support of ATM switches is still limited. For example, both the Fore Systems ATM switch and the SynOptics ATMX switch support multicast via high speed buses [9, 10].

The objective for this work is to support efficient multicast communication for all applications on top of a MIN. It is certainly network topology dependent. In this thesis, we will concentrate our effort in wormhole-switched unidirectional MINs.

## 1.1 Wormhole Switching

Switching methods greatly affect network latency. Wormhole switching [11], which has been adopted in almost all existing direct networks, is also being used in multistage networks. In wormhole switching, a message consists of a sequence of flow control digits, or flits. The header flit(s) of the message governs the route, and the remaining flits follow in a pipeline fashion. If the header flit(s) encounters a busy channel, other flits will hold and wait. This property makes wormhole switching susceptible to deadlock. As a result, deadlock avoidance is a critical issue in wormhole-switched networks. Because of its low network latency and the small amount of dedicated buffer space required at each node, wormhole switching has become the most promising switching technology and will be the only switching method considered in this thesis.

A message is divided into small packets, called *cell*, in the ATM network. The propagation of a cell within a switch is similar to wormhole switching [12]. Thus, the

proposed model could be applied to ATM switching with minor modifications.

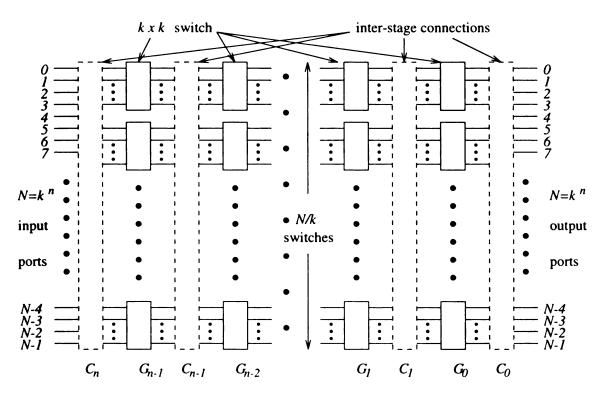

### 1.2 Multistage Interconnection Networks

Multistage interconnection networks (MINs) are a popular class of interconnection architecture for constructing SPCs, such as the BBN GP-1000 [13] and TC-2000 [14], IBM SP-1[15] and SP-2, TMC CM-5 [16], Meiko CS-2 [17], and NEC Cenju-3 [18], as well as high speed networks, such as the SynOptics ATMX [19] and DEC GIGAswitch [20]. In such systems, processor nodes are interconnected though a MIN, a class of indirect networks. Each processor node has its own processor(s), local memory, and other supporting devices. As the number of nodes in the system increases, the total communication bandwidth, memory bandwidth, and processing capability of the system scales up as well. MINs can be further classified as unidirectional MINs and bidirectional MINs [21]. As indicated in [21], bidirectional MINs are essentially a fat tree, such as the TMC CM-5, IBM SP-1, and Meiko CS-2. This thesis concentrates on those unidirectional MINs, such as the NEC Cenju-3 [18] and the BBN TC-2000 [14].

#### 1.3 Motivation and Problem Definition

Since the multicast communication service is the primitive basis for increasing performance of parallel processing applications and newly emerged applications, several research efforts and works have been done on direct networks, such as 2-D mesh and hypercube, but very little in unidirectional wormhole-switched MINs. Basically, there are two different approaches for providing multicast services: the hardware implementation and the software implementation. No matter what topology a network employs, a multicast message header must carry all destination addresses so that routers can make appropriate routing decisions. The header information is an overhead to the system and should be minimized in order to reduce communication latency and to increase effective network bandwidth.

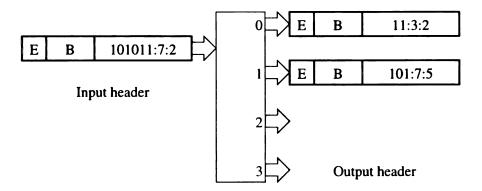

#### Multi-Address Encoding and Decoding

The multiple address (multi-address) encoding and decoding is overlooked or ignored by most researchers. The all-destination encoding scheme, which puts all destination addresses in the header, is the most intuitive approach and the one used by most researchers when they mention this issue [22]. Basically, such a scheme is fine when the number of destinations is small; however, when the number of destinations increases, the overhead of the header increases. Few other works have used the single region broadcast or single region mask which forces their multicast communication to be limited in a single contiguous region, e.g., the NEC Cenju-3, or in a single subcube, e.g., the nCUBE-2, respectively. To reduce the overhead of multi-address and eliminate such restrictions becomes the first challenge to us. A good multi-address encoding scheme should consider how to minimize the message header length overhead, how to reduce the header processing time (or routing decision making time), and how to support cut-through switching.

#### Hardware Approach

There are two different hardware approaches to support multicast: the path-based and the tree-based. As shown in Figure 1.3 and 1.4, a path-based multicast is basically a copy-and-forward technology, while the tree-based multicast is a replicate-and-forward technology. In a path-based approach, the router will replicate an incoming

Figure 1.3: Path-based hardware multicast.

flit and forward one copy to the processor if the process is one of the destination while sending the other copy to the outgoing channel as shown in Figure 1.3. As shown in this figure, a path is established from the source node to all destinations in a certain order. Every destination is visited once and only once. The path-based approach is more suitable for a direct network since the router is connected to the processor directly. In a unidirectional MIN, the distance between any source and destination pair is constant. The most serious problem is that deadlocks become possible due to a self-blocking property.

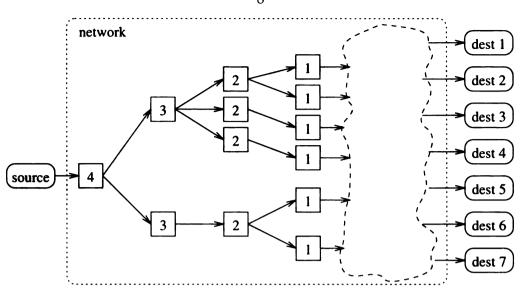

Figure 1.4: Tree-based hardware multicast.

The router in a tree-based network may replicate the incoming flits and then forwards them to multiple outgoing ports as shown in Figure 1.4. Intuitively, such an approach may cause deadlock if there are multiple multicast trees. Some restrictions must be applied to avoid deadlock when multiple multicast trees are allowed simultaneously. Such restrictions depend on the underlying network topology.

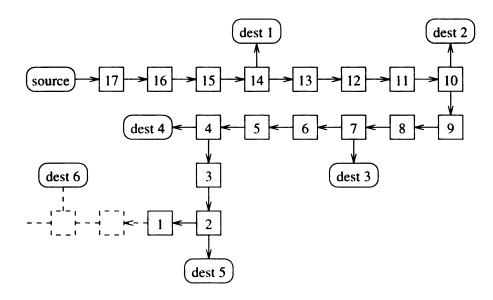

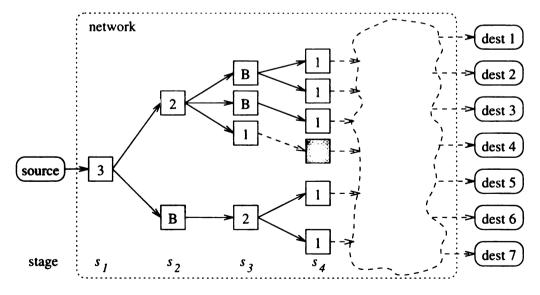

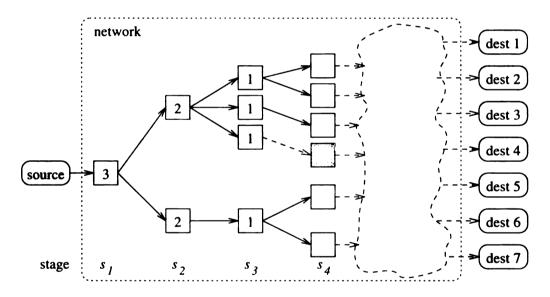

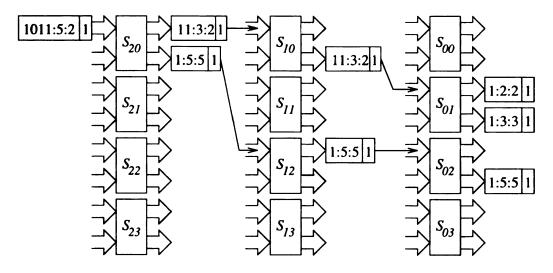

Figure 1.5: An asynchronous multicast tree.

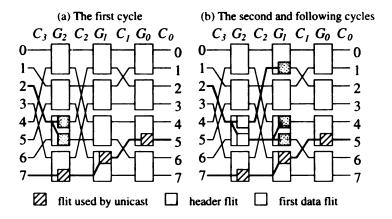

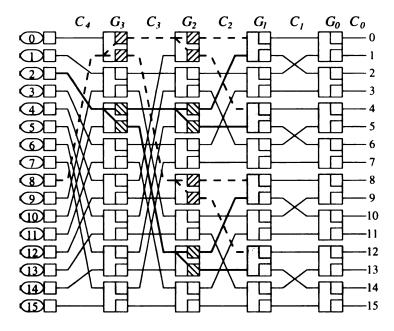

Because multiple branches exist in a tree-based multicast, two different approaches

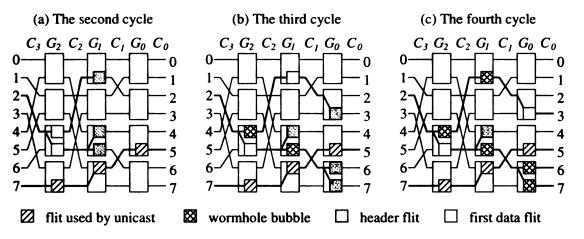

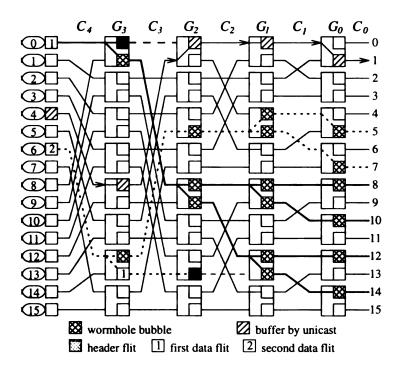

may be used when some branches are blocked. A switch in the asynchronous method forwards its flits independently as shown in Figure 1.5. As long as all associated switches in the next stage are ready to receive the next flit, the switch forwards the flit residing in its buffer. For example, flit 1 on the top switch at stage  $s_3$  is forwarded to stage  $s_4$  since those two associated switches in stage  $s_4$  are ready. Flit 2 in the top switch at stage  $s_2$  is blocked since not all three associated switches are ready. A buffer is left empty in a switch if the next flit is blocked and the previous flit is forwarded. Such an empty buffer is named a wormhole bubble and marked by B in Figure 1.5.

Figure 1.6: A synchronous multicast tree.

On the contrary, the synchronous multicast requires headers of all branches to be forwarded simultaneously. While any branch is blocked, all branches stay in current status as shown in Figure 1.6. In this figure, the fourth switch at stage  $s_4$  is used by some other communication. The third switch at stage  $s_3$  is unable to forward flit 1. Thus, it sends the condition back to the source node and the source node

forces every branch to stop forwarding. A wire-AND or wire-OR connection may be used to implement the control circuit to avoid long latency caused by the condition checking. Obviously, such a switch would be more complicated than the switch used in an asynchronous multi-head worm. It offers a potential solution for deadlock-free multicasts and is adapted by the nCUBE-2 [23].

Both a synchronous multi-head worm and an asynchronous multi-head worm have their own problems. To avoid deadlock in an asynchronous multi-head worm is very difficult, if not impossible. To restrict one multicast at a time is a possible solution but a high speed bus may offer the same performance. To enlarge the buffer within each switch is another solution if the buffer is large enough. Such a solution makes the network become a virtual cut-through network instead of a wormhole-switched network. Avoiding deadlock for multiple synchronous multi-head worms seems to be easier than for the asynchronous one, but it is not as easy as we think. For example, the nCUBE-2 has a synchronous multi-head worm but is forced to disable the hardware multicast due to potential deadlock. The NEC Cenju-3 is another system which supports the hardware multicast. Nonetheless, deadlock is still possible when multiple multicasts are allowed due to its asynchronous multi-head worm. Consequently, to provide hardware multicast capability without potential deadlock and/or starvation is one of the objectives of this work.

#### Software Approach

In systems which do not support hardware multicast, we have to resort to software approaches to support efficient multicast, referred to as software multicast or unicastbased multicast. Traditional approaches use separate addressing in which the source node sends the message to one destination at a time. As the number of destinations increases, separate addressing may require excessive time because many systems allow a local processor to send only one or a few messages at a time. An alternative approach is a multicast  $tree^1$  in which the source sends the message to a subset of the destinations. Each recipient of the message forwards it to some subset of the destination that has not yet received it. Which type of multicast trees to use depends on the switching strategy and the unicast routing algorithm. An efficient multicast tree involves no local processors other than the source and destination processors, exploits the distance-insensitivity of wormhole switching, and is of minimum height, specifically, height  $\lceil log_2(m+1) \rceil$  for m destination nodes. Another key requirement is that there be no channel contention among the constituent messages of the multicast. That is, the unicast messages involved should not simultaneously require the same channel.

<sup>&</sup>lt;sup>1</sup>The software multicast tree is different from hardware multicast trees which are based on cutthrough switching. In a software multicast tree, each intermediate node has to receive the complete message before forwarding to other nodes.

#### **Multicast Communication in MINs**

Multicast communication has been extensively studied for distributed-memory multicomputers based in direct network architectures, but little research has been done in indirect networks, especially MIN-class topologies. There are several characteristics which distinguish a MIN from other network architecture such as unique length between any (source, destination) pair, and  $O(N \log N)$  hardware complexity, etc. Since those multicast approaches proposed for direct networks are not suitable for MINs, this thesis concentrates on multicast communication in MIN-based networks.

A regular MIN with N inputs and  $log_kN$  stages, where k is the number of input/output of a switch, is a unique-path network. With such property, deadlock becomes possible if multicast trees share more than two channels. The multicast capability in current systems is provided by either the unicast-based (software-based) approach or the hardware approach with excessive hardware and some limitations in order to avoid deadlock. Both approaches suffer long latency, inefficiency, or cost. Even worse, some of them are not deadlock-free. A general multicast algorithm to avoid these drawbacks and guarantee deadlock-free system is the major focus of this thesis.

A regular MIN is a unique-path network; hence, the multicast tree is also unique unless some variants of the MIN topology are considered. One such design extension, among a few others, is to consider a MIN with extra stages. The idea is to attach a few extra stages to the regular n-stage MIN. The extra stages bring forth the flexibilities in multicast paths and the difficulties. To find all traffic-optimal multicast trees in

an ESMIN becomes an NP problem.

#### 1.4 Performance Metrics

An important metric used to evaluate a network is its communication latency, which is the sum of three component values: start-up latency, network latency, and blocking time [24]. The start-up latency refers to the time required for message framing/unframing, memory/buffer copying, validation, and so on, at both source and destination nodes. The startup latency is mainly dependent on the design of system software within the nodes and the interface between nodes and routers. Start-up latency can be further classified into sending latency, the software latency at source node, and receiving latency, the software latency at destination node. The network latency equals the elapsed time after the head of a message has entered the network at the source until the tail of the packet emerges from the network at the destination. Given a source and destination node, the startup and network latencies are static values, frequently used to characterize contention-free networks. The blocking time includes all possible delays encountered during the lifetime of a message. These delays are mainly due to conflicts over the use of shared resources, such as busy channels and filled buffers. Blocking time reflects the dynamic behavior of the network due to the passing of multiple messages and may be high if the network traffic is heavy or unevenly distributed. In this dissertation, multicast latency is used to measure multicast performance. The multicast latency refers to the time interval from when the source processor begins to send the first copy of the message until the last destination

processor has received the message.

## 1.5 Objectives and Thesis Outline

The main objective of this research is to establish efficient multicast communications in unidirectional wormhole-switched MINs. To support efficient multicast communication, the header overhead of the multicast message should be minimized and external network contention among different applications should be eliminated. These objectives and the thesis outline are discussed in the following.

In Chapter 2, we discuss the issue to shorten the header overhead by investigating different multi-address encoding and decoding schemes. Unlike a unicast message, the header of a multicast message must carry multiple destination information. Because of that, the length of a header varies with the number of destinations, the distribution of destinations, and the multi-address encoding/decoding schemes. The consideration of such a header as well as six multi-address encoding and decoding schemes are addressed in this chapter for general network topology. As the scale of networks increases and the demand of multicast communication increases, the overhead of message header becomes critical, which implies that multi-address encoding becomes critical. Although the proposed multi-address encoding and decoding schemes can be applied to networks with different switching techniques, such as circuit switching, store-and-forward switching, and cell relay, the emphasis of this thesis will be in the wormhole-switched technique. Depending on characteristics of a network topology, these multi-address encoding and decoding schemes may be further optimized.

In Chapter 3, we brief review the different interconnection patterns as well as associated network topologies of MINs. Furthermore, the optimization of the multi-address encoding schemes and the associated decoding algorithm in a switch for each encoding scheme in MINs are also addressed in this chapter. Performance evaluation of different multi-address encoding and decoding schemes is given based on simulations.

In Chapter 4, two different tree-based hardware multi-head worm implementations are studied — the asynchronous and synchronous. The asynchronous multi-head worm allows that each branch forwards independently while the synchronous multi-head worm insists that all branches forward synchronously. Unfortunately, both implementations are not deadlock-free unless certain rules are applied. Hence, current hardware implementations exhibit either undesirable properties or are restricted in their use. A deadlock-free and starvation-free hardware implementation of multiple synchronous multi-head worms is presented. The difficulty to the implementation of deadlock-free multiple asynchronous multi-head worms is also shown in this chapter.

Unlike the unicast message whose header has a fixed size, the size of a multicast message header depends on the number of destinations, the distribution of destinations and the encoding scheme. Since a single flit may not be able to carry all destination information, a multi-head worm may have different distances of branches toward different destinations. Such latency may cause deadlock of synchronous multi-head worms. We address this issue and propose a pseudo multi-address encoding scheme to eliminate the potential deadlock.

In Chapter 5, the network partitionability of different delta class networks is ex-

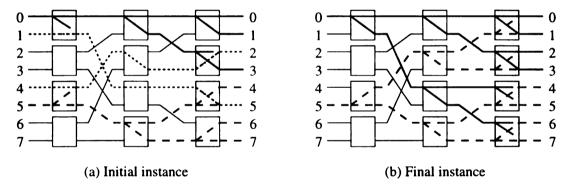

amined and performance results of various allocation schemes is given. By exploiting the locality of processor allocation, we show that the known topologically equivalent delta-class MINs have different capabilities in supporting hardware and software multicasts. Since the internal contention is unavoidable unless doing one multicast at a time, we concentrate on eliminating the external contention. A binary cube network partitioning scheme is studied and shown to be external contention-free in both cube and omega MINs. On the contrary, we also show that the baseline and butterfly MINs may not be partitioned into contention-free and channel-balanced subcubes. Two connection patterns are studied to modify baseline and butterfly MINs. Both modified baseline and butterfly MINs have the same partitionability as cube and omega MINs.

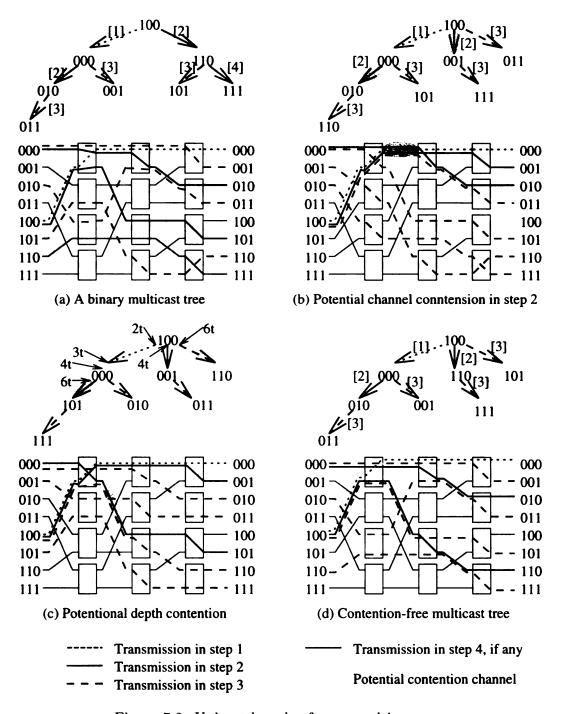

In Chapter 6, we consider the multicast problem for various MIN classes of topologies. Since the multicast problem for a regular MIN has a unique solution and does not offer any flexibility, we consider a design extension, namely extra-stage MIN (ESMIN), as our focus. The ESMIN multicast problem is formulated and an optimality criterion is defined. A lower bound on the number of multicast trees is estimated, and we show that the total number of traffic-optimal multicast trees may itself be exponential. However, a traffic-optimal multicast tree can be generated in polynomial time. We propose an algorithm towards this. The performance of this algorithm, with respect to three other proposed heuristics, is shown using simulation.

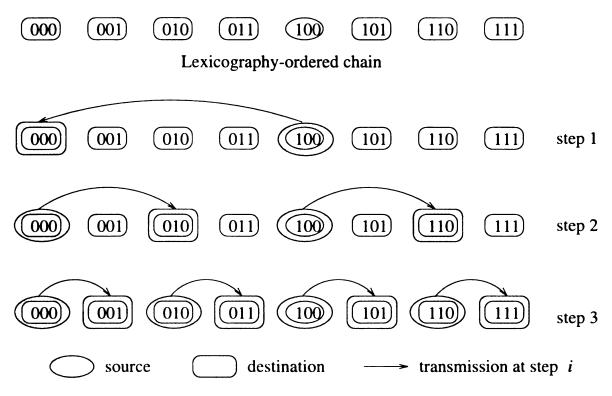

In Chapter 7, an efficient software-based multicast algorithm is presented and analyzed for those existing message-based SPCs which do not have hardware multicast support. One way to implement multicast in such systems is *separate addressing*. An alternative approach is *multicast tree*. The focus here is on such multicast tree implementation, also known as *unicast-based* multicast implementation. By exploiting the locality of processor allocation, a minimum-time unicast-based multicast algorithm is proposed for some classes of MINs which support one-port communication.

In Chapter 8, we give an overview of related work. Since lots of research has devoted to multicast on different network topologies and different switching techniques, we concentrate on the work related to the multicast in MIN-based ATM switches as well as the hardware multicast and the software multicast in wormhole-switched networks. The concluding remarks as well as some possible future research directions are discussed in Chapter 9.

## CHAPTER 2

## **Multi-Address Encoding**

No matter what kind of topology a network is, a message header for multicast communication must carry the destination set information needed for routers/switches to make appropriate routing decisions. In some networks, such a header is needed in a sender-initiated control message in order to establish a multicast circuit; while in some other networks, such a header is used in all data messages. Nevertheless, the header information is an overhead to the system and should be minimized in order to reduce communication latency and to increase effective network bandwidth.

Basically, a multicast message header carries multiple destination addresses (multi-address) information. A destination address can be either a physical address or a relative address. A relative address is usually used to represent the relative location to the source address. Each address may be further represented by a number of dimensions. For example, in a 2D mesh network, each address may have two dimensions — one for each dimension. In this work, we don't further distinguish different types of addresses. Unless otherwise specified, an address refers to all details of the

address in our work.

#### 2.1 Header Encoding Design Considerations

Each multicast message header must have a number of flits to carry the necessary routing information, where each flit is a flow control unit. It could be an address or a region (to be discussed later) depending on the encoding scheme. The total number of flits or header length is usually not only dependent on the number of destinations but also on the selected multi-address encoding scheme. The function of switches is taking a message from an input channel, making a routing decision, and forwarding (with possibly replicating) the message to one or more output channels. A good multi-address encoding scheme should not only shorten the message header length, but minimize communication latency and ease routing decisions. The following header design issues are considered.

The length of a message header can be either fixed or variable in terms of the number of destinations. The length of a variable length header is dynamically adjusted by switches as the message header is processed. For the fixed one, the length may be a function of the location of switches in the network.

In cut through switching, should each switch buffer the whole message header before making the routing decision? For a large message header, it implies a large buffer to hold the whole message header and a longer communication latency. In wormhole routing, a message is divided into a number of flits, and the minimum capacity of each buffer is one flit. Since a message header may be composed of many

flits, it is desirable that the routing decision in each router can be made as soon as possible to minimize the buffer requirement. Ideally, a message header can be processed on the fly on the flit basis.

For a variable length header, the number of destination addresses (or regions to be discussed later) is another design parameter. It may be impractical and inefficient to use a counter to indicate the number of destinations (or regions) because the counter flit is usually placed at the beginning of a message header. Since the value of counters may be changed by switches if the destination address set is split into different subsets, it will prohibit the processing of message headers on the fly by switches. An alternative approach is to have an end-of-header (EOH) flit to indicate the end of an address header. Some known hardware and software techniques, such as code violation and address stuffing, may be used to implement the EOH flit.

Both tree-based multicast, in which a router is able to replicate an input message through multiple output channels, and path-based multicast, in which a message traverses along a certain path picked by the destination nodes along the path, may be considered to implement multicast communication [25]. Usually, path-based multicast is used in direct networks, such as multi-dimensional meshes, and tree-based multicast is used in indirect (switch-based) networks, such as MINs. In both approaches, the message header may have to be modified by those intermediate routers/switches.

# 2.2 Multi-Address Encoding Schemes

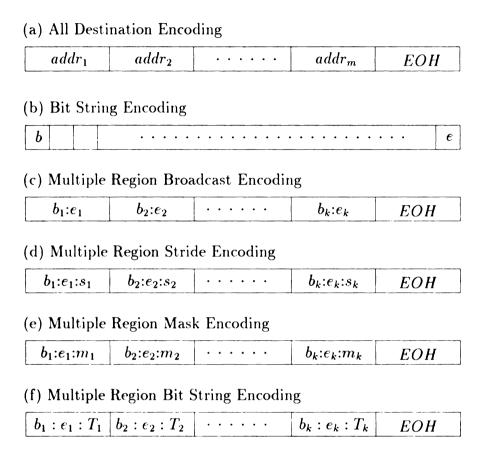

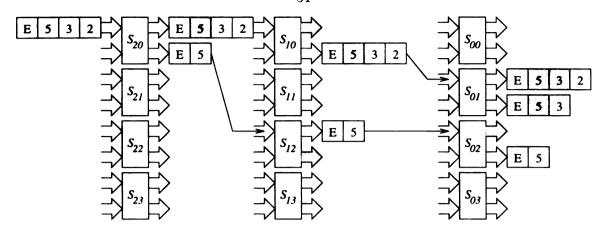

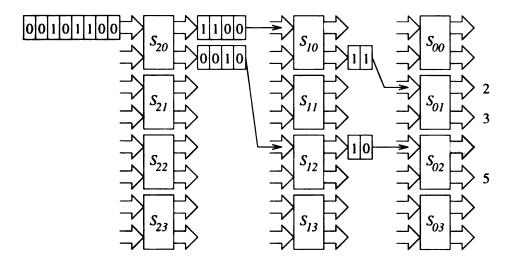

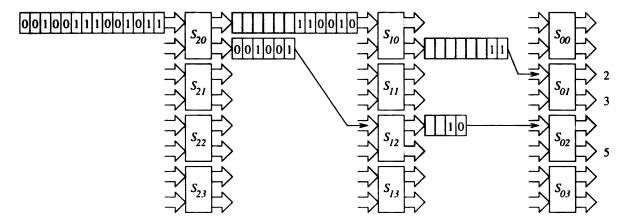

Six multi-address encoding schemes are described in this section. The message header format of these schemes is shown in Figure 2.1.

Figure 2.1: The message header format of six address encoding schemes.

#### 2.2.1 All-Destination Encoding

This is an intuitive method used in [26], in which all destination addresses are carried by the header as shown in Figure 2.1(a). Assuming that all addresses are sorted in ascending order, the EOH flit can be all 0's. If the only destination address is all 0's, the second all 0's indicates the EOH. If the routing requires that the addresses

be arranged in a certain order, such as path-based multicast [25], the EOH flit may be represented by replicating the last address. However, for tree-based multicast, it is easier to generate the same EOH flit for all replicated outgoing messages. In this case, the EOH flit could be an unused address or use other methods. Note that if an EOH flit takes many addresses, the flit buffer must be large enough to hold the EOH flit. Clearly, all-destination encoding is good for a small number of irregular addresses as its header length is proportional to the number of addresses.

#### 2.2.2 Bit String Encoding

The major drawback of the all-destination encoding scheme is its significant header overhead when the number of destinations is large. One way to limit the size of a header is to have a bit string to indicate destinations, where each bit corresponds to a destination ranged between node b and node e as shown in Figure 2.1(b). Since the number of nodes in a system is predefined, there is no need of an EOH field. In some network topologies, such as MINs, the bit string length can be a function of the number of reachable nodes from a given switch, which is still independent of the number of destinations. Apparently, the bit string encoding scheme is inefficient when the system is large and the number of destinations is small. However, it is flexible in handling a large number of irregular destination addresses.

Usually, it is extremely difficult for a switch to make the routing decision on the fly based on the incoming bit string information and to produce the bit string information for each output port. Thus, a switch usually has to buffer the entire bit string in order to make the routing decision and to generate output bit strings. This is named buffered bit string. Although the buffered bit string encoding scheme allows distributed routing, each switch requires a large flit buffer and the communication latency is also increased.

To eliminate a large flit buffer, a hierarchical bit string may be used. This is a source routing method in which the source node has to determine the complete multicast tree information. In this scheme, the input message header has 1 + k flits for a switch with k output ports. The first flit has k bits corresponding to k output ports. A "1" in a bit position indicates that the corresponding output port should forward a copy of the message. The remaining k even sized flits carry bit string information for each output port. The bit string information is recursively defined because each bit string becomes an input to the next switch. Note that if these bit string flits are not even sized or have less than k flits, it will be very difficult to determine the delimiter between two adjacent flits. Obviously, the hierarchical bit string encoding scheme can perform routing on the fly and requires a small flit buffer in each switch. However, the header length is much longer than the buffered bit string method.

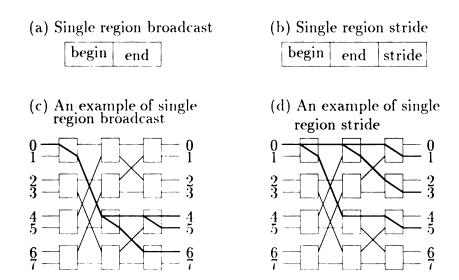

## 2.2.3 Multiple Region Broadcast

In order to enforce communication locality and minimize communication interference among processors from different process groups, processors belonging to the same process group are usually allocated in a contiguous region, if possible. Thus the multicast addresses can be confined within a region, and each region is specified by two fields: (b:e), the beginning and ending addresses of the region, respectively. This is referred to as region broadcast and is used in some ATM switches and the NEC Cenju-3 [18].

Figure 2.2: Single region broadcast and single region stride, where the source node is 0 and the destination sets are  $\{4, 5, 6\}$  and  $\{1, 3, 5\}$ , respectively.

Figure 2.2(a) shows the specification of a single region broadcast, where the beginning address must be no greater than the ending address. An example is given in Figure 2.2(b). When a message enters a switch, it buffers the complete region flit and then directs the message to corresponding output port(s). The header is revised at every switch where the message is replicated. For example, the incoming header at the shadow switch is (4:6), and the outgoing headers for upper and lower ports are (4:5) and (6:6), respectively.

However, depending on the processor allocation scheme and application program characteristics, not all process groups can have all their nodes in a contiguous region.

The single region broadcast thus cannot achieve the multicast in a single multicast communication. Two approaches may be used. One method is to send multiple single region broadcast messages in sequence to different disjoint regions. Another method is to add extra hardware (e.g., the copy network used in [27, 28]) and to introduce the concept of dummy addresses. Here, we generalize this scheme to multiple regions by allowing multiple region specification in the header.

The multiple region broadcast, see Figure 2.1(c) for its header format, forwards the message to every node covered by each region. The EOH flit can be specified as a region containing an address with all 1's followed by an address with all 0's (i.e., address violation). In fact, any pair of addresses can be an EOH as long as the second address is smaller than the first address.

Figure 2.3(a) illustrates an example of multiple region broadcast. Consider 64 nodes organized as a 2D array. For some 2D matrix applications, it may require the source node (3,2) to send a message to all nodes in the same column and in the same row. If the source node can also be a destination, the header for node (3,2) is (3:3,0:7; 0:7,2:2). Otherwise, the header will be (3:3,0:1; 3:3,3:7; 0:2,2:2; 4:7,2:2).

#### 2.2.4 Multiple Region Stride

In some applications, a source node may wish to send a message to all odd-numbered destinations or to all even-numbered destinations. In other words, the destination addresses have a constant distance between two adjacent addresses. Thus, the addresses (or flit) can be specified by three parameters: (b:e:s), the beginning address,

Figure 2.3: Multicast to the same row and column in (a) 2D mesh and (b) linear array architectures.

the ending address, and the stride value. Note that for a multi-dimensional address, each dimension may have its own stride value. This encoding scheme is referred to as region stride multicast.

Figure 2.2(c) shows the specification of a single stride-region. Consider a stride-region, (b:e:s), where  $(b \le e)$  and s is the stride value. The message is forwarded to node  $\{d|d=b+i\times s, i=0,1,\ldots,\lfloor (e-b)/s\rfloor\}$ . Figure 2.2(d) shows an example in which destinations are  $\{1,3,5\}$  and the source node is 0. The header can be either (1:5:2) or (1:6:2). The header is also revised when the message is replicated. For example, the incoming header is revised to (1:3:2) and (5:5:2) for the outgoing messages to upper and lower ports of the shadow switch, respectively.

Similarly, this encoding scheme can be generalized to multiple region stride. The header format is shown in Figure 2.1(d). To be consistent with the stride-region flit specification, the EOH flit may contain three fields. Like multiple region broadcast, an address with all 1's followed by an address with all 0's may be used to indicate

the EOH, where the third stride field is irrelevant.

Consider the same multicast example illustrated in Figure 2.3(b). If the processors are organized in a linear order, such as the NEC Cenju-3 and the IBM SP-1, all nodes in the same row are not in a contiguous region. The multiple region stride encodes these destinations as (2:58:8; 24:31:1) if the source node is also a destination; otherwise, the header is (2:18:8; 34:58:8; 24:25:1; 27:31:1).

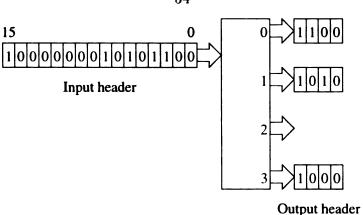

#### 2.2.5 Multiple Region Mask

Another regular pattern of destination addresses that typically occurs in k-ary n-cube networks is subcube. Let  $d_{n-1} \dots d_1 d_0$  represent a node in a k-ary n-cube, where  $0 \le d_i \le k-1$  (note that this definition can be easily extended to a more general cube network in which the radix of each dimension may be different). Any subcube can be described by a binary mask, m, with an address, b. The binary mask m defines the size and dimensions of the subcube, i.e., the number of ones in m and the location of each dimension with  $m_i = 1$ . The address b defines which subcube among those subcubes, i.e.,  $b_i$ 's where  $m_i = 0$ . This approach is used in the nCUBE-2 [23]. In a more general case, we define a subset of a subcube with three fields: (b:e:m), where  $b_i = e_i$  when  $m_i = 0$  and for those i's with  $m_i = 1$ ,  $b_i$  and  $e_i$  specify the lower and upper bounds of the subcube, respectively. The multiple region mask shown in Fig. 2.1(e) extends this approach to allow that a message be destined for multiple subsets of subcubes.

Consider a binary 4-cube with eight destinations {0100, 0101, 0110, 0111, 1100,

1101, 1110, 1111}. The multiple region mask encodes the header to (0100: 1111:1011), which is a complete 3-cube. When the destinations are {0110, 0111, 1100, 1101, 1110}, a subset of the 3-cube is specified as (0110:1110:1011).

#### 2.2.6 Multiple Region Bit String

Both multiple region broadcast and multiple region stride are suitable for destinations that can be divided into a number of clusters and with a regular address pattern within each cluster. If the destinations are not in any regular shape, the header encoded by previous encoding schemes may be too large (e.g., many disjoint regions). The multiple region bit string encoding scheme shown in Figure 2.1(f) is proposed to reduce the header overhead under such a situation. In general, a region bit-string flit is specified as  $(b, \epsilon, T)$ , where b and  $\epsilon$  ( $b \le \epsilon$ ) indicate the beginning and ending addresses, and T is a binary bit string. Each bit in T corresponds to a node within b and  $\epsilon$ . A node is a destination if the corresponding bit is 1. Both b and  $\epsilon$  are destinations and T has  $(\epsilon - b + 1)$  bits<sup>1</sup>.

Consider a system with 16 nodes and the destinations are  $\{0,1,3,4,6,12,13,15\}$ . With multiple region broadcast, it requires five regions. With multiple region bit string, one possible specification is (0:6:1101101:12:15:1101). Apparently, in multiple region bit string, the length of each region is not fixed and is determined by the values of b and e. Depending on the flit buffer capacity, the system has to limit the maximum value of e - b. The EOH flit can contain two fields — a field with all 1's

<sup>&</sup>lt;sup>1</sup>Since the first and last bits are always 1 in T, these two bits may be removed from T.

followed by one with all 0's. Although the multiple region bit string is more flexible and can handle addresses with irregular patterns, it may be difficult to determine the most efficient number of regions, and the switch design may be more complicated.

# 2.3 Multi-Address Decoding

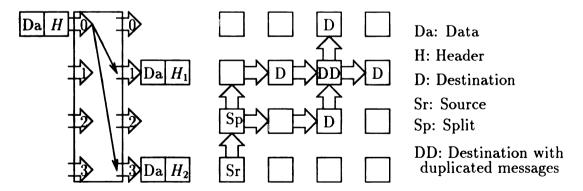

Consider a generic network switch/router with k input ports and k output ports as shown in Figure 2.4(a) with k=4. The interconnection of routers defines the network topology. Each router may or may not have a local processor depending on the system architecture. When a multicast message arrives at a router via an input port, the router examines the header and may enable a number of output ports depending on the routing strategy. The message is replicated and forwarded to all enabled output ports. A critical issue is how to define new header information for each enabled output port. If not handled properly, the same message may be received repeatedly by the same processor as shown in Fig. 2.4(b).

Figure 2.4: (a) A generic switch/router with four input/output ports, and the message is forwarded via both output ports 1 and 3. (b) The receiving of a duplicated message when the header is not handled properly and alternate routing paths are allowed.

In distributed routing, if a router is able to process the input message header

on the fly, it will buffer one header flit, make the routing decision, and deposit new message header flit information to a selected output port. When an address or a region is forwarded to its associated output port, the other enabled ports will be idle since there is no address or region to be forwarded to these output ports. Such an idle on timing is referred to as wormhole bubble. Note that a wormhole bubble does not necessarily imply an empty or a null flit. With self-timed design, a wormhole bubble implies a timing delay to the next flit. However, for ease of explanation, the wormhole bubble is represented as an individual flit in the following figures as B.

When a router replicates a message, the message header will be revised and an output message header is generated for each enabled output port (or each replicated message). Figure 2.4(a) shows an example replicating a message into two messages in which the headers H1 and H2 are different. Usually, the destination address set is divided into a number of disjoint address subsets, one for each replicated message. This approach can avoid multiple receptions of the same message, which is especially important if there are many alternate paths to a destination. The drawback of having disjoint subsets is its decreased flexibility in forming the header format. However, if the routing path is unique, those destination subsets may overlap. Since a router usually makes its routing decision based on the first field of a region flit, it may ignore any destination which is not reachable from its output port. This approach is more flexible in forming the header format.

For a single region which contains a number of addresses, the region may be split into several regions by a router. Each region is directed to an enabled output port. It is possible that two or more disjoint regions are directed to the same output port. Thus, the number of regions in the new header may be larger than the incoming one.

Therefore, placing the number of regions in the header may not be feasible.

For each of the six multi-address encoding schemes, this section will describe some generic address decoding algorithms that may be performed by a router. Given a header flit, say F, the routing function Route(F) will determine the output port number to be selected to forward the message. Furthermore, we assume that if the processor, if any, associated with a router is one of the destinations, a copy of the message will be sent to the processor. An output port is enabled if a copy of the message is to be forwarded through the port. At the end of message transmission, all output ports will be disabled. These behaviors will not be further described in the following algorithms.

# 2.3.1 All Destination Decoding

For each incoming flit, d, Figure 2.5 shows the corresponding decoding algorithm. When sending information through an enabled port, it implies that the corresponding output channel is available; otherwise, the message transmission will be pending until the port is available. Avoiding deadlock is another critical design issue. The solution is dependent on the network topology and routing strategy, which is beyond the scope of this chapter.

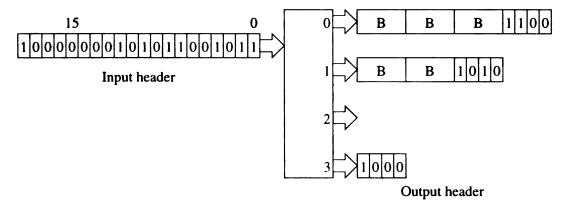

For example, the addresses of a message into a router are  $\{2, 3, 5, 7, 15, B, B\}$  as shown in Figure 2.6, where B indicates wormhole bubble and E represents EOH. Let the reachable nodes from port i be node  $i \times 4$  to node  $i \times 4 + 3$ , where  $0 \le i \le 3$ .

```

Algorithm: all-destination decoding

Input: An address d.

Output: append d to the header of the selected output port.

Procedure:

begin

if d = EOH then send EOH to all enabled ports; exit;

j:=Route(d);

send d to port j;

end

```

Figure 2.5: All destination decoding algorithm.

We further assume that there are 16 nodes in the system. The router enables port 0 and forwards address 2 when address 2 is decoded. Address 3 is forwarded to port 0. While address 5 is decoded, port 1 is enabled and address 5 is forwarded to port 1. There is a wormhole bubble on port 0. The process is repeated until the header is split completely as shown in the figure. Port 2 is not enabled since there is no destination via this port.

Figure 2.6: An example of all-destination decoding.

#### 2.3.2 Bit String Decoding

#### Buffered Bit String.

A router stores the entire bit string and then detects each bit which has a 1 to enable the corresponding output port. If there is more than one output port that can reach the destination, the router selects exactly one port. The length of each bit string is dependent on the corresponding port and the number of nodes reachable from that port. The router also knows the reachable node for a given bit position. The buffered bit string decoding algorithm is given in Figure 2.7 while an example based on the previous example is shown in Figure 2.8.

```

Algorithm: buffered bit string decoding

Input: Binary bit string, T.

Output: Bit string, D_j, for each enabled output port j.

Procedure:

begin

for every bit, t_i, in bit string T do

(j,k) := Rout \epsilon(i);

(* route through port j, bit position k *)

d_{j,k} := t_i;

endfor

enable port j with D_j \neq 0 for all j;

end

```

Figure 2.7: Buffered bit string decoding algorithm.

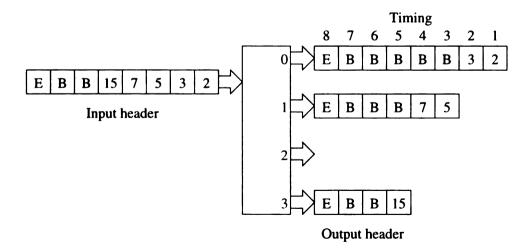

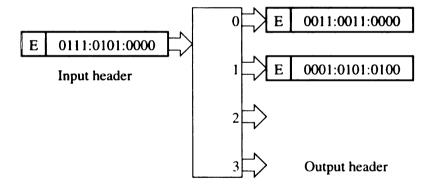

#### Hierarchical Bit String Decoding.

In hierarchical bit string, the first field (k bits) of an incoming bit string indicates the enabling or disabling of the k output ports of a k-port router. The following bits are divided into k fields, one for each output port. The  $i^{th}$  field is forwarded to the

Figure 2.8: An example of buffered bit string decoding.

associated router in the next stage if port i is enabled, for  $0 \le i \le k$ . Otherwise, it is eliminated at the router. The decoding algorithm is too simple to be described here, and the corresponding example is shown in Figure 2.9.

Figure 2.9: An example of hierarchical bit string decoding.

## 2.3.3 Multiple Region Broadcast Decoding

As shown in Figure 2.1(c), the header in multiple region broadcast contains several regions. All nodes covered by all regions should receive a copy of the message. Thus, the router may have to divide a region into several sub-regions, and each sub-region is directed through an appropriate output port. The algorithm for decoding each region

is given in Figure 2.10.

```

Algorithm: multiple region broadcast Input: A region (b,e).

Output: Send each sub-region to an output port. Procedure: begin

if (b,e)=EOH, send EOH to all enabled ports; exit; while (b \le e) do

(j,e'):=Route(b,e); send region (b,e') to port j; b = e' + 1; end while; end;

```

Figure 2.10: Multiple region broadcast decoding algorithm.

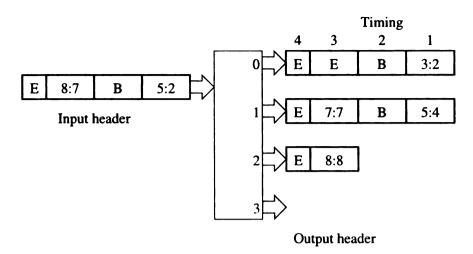

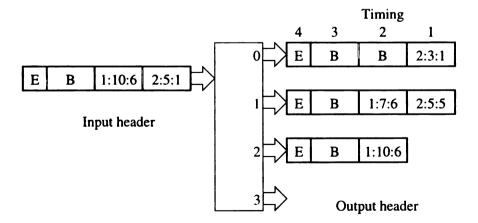

In this decoding algorithm, the router checks the beginning address of a region and searches for the first address,  $\epsilon'$ , which cannot be reached by the same output port. A sub-region is then identified for that output port. The process repeats until all sub-regions have been identified. For example, consider an incoming header of (2:5; 7:8) shown in Figure 2.11. The router splits the first region to (2:3) and (4:5) for ports 0 and 1, and the second region to (7:7) and (8:8) for ports 1 and 2, respectively.

#### 2.3.4 Multiple Region Stride Decoding