# LIBRARY Michigan State University

This is to certify that the

dissertation entitled

#### DESIGN AND ENGINEERING OF COMPLEX REAL-TIME SYSTEMS

presented by

Aleksandar M. Bakic

has been accepted towards fulfillment of the requirements for

Doctoral degree in Computer Science & Engineering

Maly W. Mult Major professor

Date May 3, 2000

## PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due. MAY BE RECALLED with earlier due date if requested.

| DATE DUE | DATE DUE |

|----------|----------|

|          |          |

|          |          |

|          |          |

|          |          |

|          |          |

|          |          |

|          |          |

|          |          |

|          |          |

|          |          |

|          |          |

|          | DATE DUE |

11/00 c:/CIRC/DateDue.p65-p.14

## DESIGN AND ENGINEERING OF COMPLEX REAL-TIME SYSTEMS

$\mathbf{B}\mathbf{y}$

Aleksandar M. Bakić

## A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Computer Science and Engineering

2000

#### ABSTRACT

## DESIGN AND ENGINEERING OF COMPLEX REAL-TIME SYSTEMS

By

#### Aleksandar M. Bakić

Complex real-time systems are emerging parallel or distributed, heterogeneous computer systems with many disparate constraints and requirements. Their subsystems and components are designed using appropriate, multiple models from real-time scheduling theory, resource allocation and quality-of-service managements schemes. Issues in the design, engineering and deployment of complex real-time systems addressed by this research include problem-solving approaches for finding satisfactory values of system parameters according to the real-time models and their integration; dynamic reconfiguration; instrumentation; and on-line performance analysis and visualization.

Four main objectives of this research resulted in proof-of-concept contributions. A compiler-based approach to design and engineering of complex real-time systems was designed, implemented and evaluated that represents a systems engineering framework particularly suitable for this systems domain. A distributed instrumentation system kernel was developed and evaluated in order to investigate performance and

portability issues of the instrumentation of parallel and distributed, heterogeneous systems. A comprehensive on-line performance analysis and visualization technology, for the same domain and with an emphasis on complex real-time systems, was developed that incorporates common properties of extant tools and provides a basis for advanced on-line performance analysis and visualization tools. A mainly automated technology that combines the preceding results was developed in an attempt to integrate systems engineering and on-line performance analysis and visualization in a way that facilitates on-line reconfiguration of complex real-time systems.

© Copyright 2000 by Aleksandar M. Bakić All Rights Reserved To my parents

#### ACKNOWLEDGMENTS

I would like to thank my advisor, Dr. Matt W. Mutka, for his continued guidance and support during my research. I have been fortunate to have an experienced researcher and talented pedagog to supervise me. He made the pursuit of my Ph.D. an enjoyable and invaluable professional experience.

I am thankful to Dr. Diane T. Rover for providing me with my first research opportunity and continuing to support me as a Ph.D. student. Her ideas and constructive critiques in our collaboration made a difference so many times.

I thank the other members of my guidance committee, Dr. Anthony S. Wojcik and Dr. James Stapleton, for their helpful comments and suggestions.

I wish to thank Dr. George C. Stockman again for extending me an offer to come to the MSU in the first place. I am indebted to Dr. Lionel M. Ni for valuable lectures in practical, and Dr. Eric K. Torng in theoretical aspects of Computer Science; as well as to other MSU professors who taught me advanced and exciting.

Many of my fellow students helped me and collaborated with me over the course of study. I would like to thank them all, especially Peter C. Wong, Paul A. Reed, Hugh M. Smith, Wenting Tang, Kuk-jin Lee and Abdul Waheed. I would also like to

thank the CSE and ECE departments for the excellent facilities, and technical and administrative support.

I am grateful to my family for their love, support and patience. Special thanks to my wife Vera for her love and understanding, and to our little daughter Jovana for bringing joy to our lives.

## TABLE OF CONTENTS

| LIST OF TABLES                                                   | x         |

|------------------------------------------------------------------|-----------|

| LIST OF FIGURES                                                  | хi        |

| 1 Introduction and Motivation                                    | 1         |

| 1.1 Focus of the Dissertation                                    | 2         |

| 1.2 Motivation                                                   | 6         |

| 1.2.1 Design and Engineering of Complex Real-Time Systems        | 7         |

| 1.2.2 Distributed Instrumentation Systems                        | 9         |

| 1.2.3 On-Line Performance Analysis and Visualization             | 11        |

|                                                                  | 13        |

| · · · · · · · · · · · · · · · · · · ·                            | 17        |

| 2 Background and Related Work                                    | 20        |

| 2.1 Distributed Real-Time System Design                          | 21        |

| · · · · · · · · · · · · · · · · · · ·                            | 26        |

| · · ·                                                            | 27        |

|                                                                  | 30        |

| ••                                                               | 32        |

|                                                                  | 34        |

| •                                                                | 38        |

| · ·                                                              | 42        |

| 3 A Compiler-Based Approach to Design and Engineering of Complex |           |

|                                                                  | <b>47</b> |

| 3.1 Real-Time System Specification in RTSML                      | 48        |

|                                                                  | 55        |

| <u>-</u>                                                         | 57        |

|                                                                  | 58        |

|                                                                  | 61        |

| •                                                                | 64        |

| = <u>=</u>                                                       | 65        |

|                                                                  | 69        |

| · · · · · · · · · · · · · · · · · · ·                            | 70        |

| • •                                                              | 71        |

|                                                                  | 75        |

| •                                                                | 77        |

|                                                                  | 78        |

| 4 A Portable and Flexible Distributed Instrumentation System          | 80  |

|-----------------------------------------------------------------------|-----|

| 4.1 Objectives and Approaches                                         | 81  |

| 4.2 Description of BRISK                                              | 85  |

| 4.2.1 Architecture                                                    | 85  |

| 4.2.2 Implementation                                                  | 87  |

| 4.3 Evaluation of BRISK                                               | 96  |

| 4.3.1 Local Performance                                               | 97  |

| 4.3.2 Distributed Performance                                         | 101 |

| 4.4 Summary                                                           | 108 |

| 5 An On-Line Performance Visualization Technology                     | 109 |

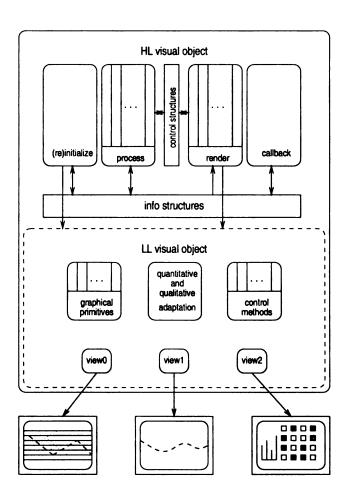

| 5.1 Visual Object Architecture                                        | 110 |

| 5.1.1 Low-level visual object                                         | 112 |

| 5.1.2 High-level visual object                                        | 114 |

| 5.1.3 Application of visual objects to a heterogeneous system         | 117 |

| 5.2 Visual Object Markup Language (VOML)                              | 118 |

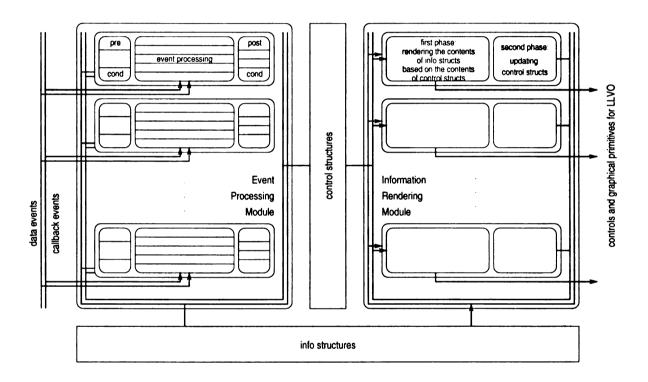

| 5.2.1 Event Processing and Information Rendering Architecture (EPIRA) | 119 |

| 5.2.2 The VOML language                                               | 121 |

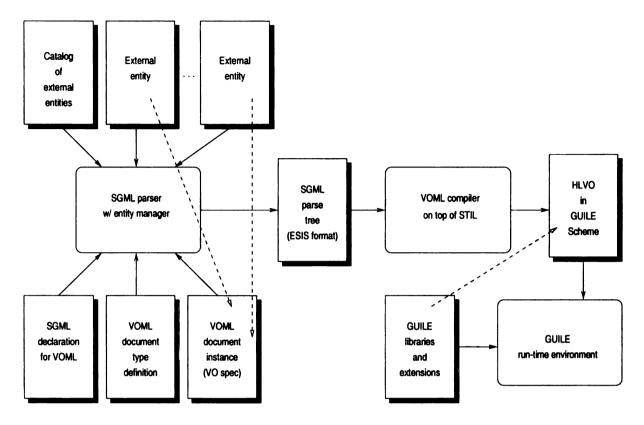

| 5.2.3 The VOML compiler                                               | 125 |

| 5.3 The VOML Specification of a Simple Visual Object                  | 128 |

| 5.4 Summary                                                           | 134 |

| 6 An Integrated Approach to Real-Time System Design and On-Lin        | e   |

| Performance Visualization with Steering                               | 136 |

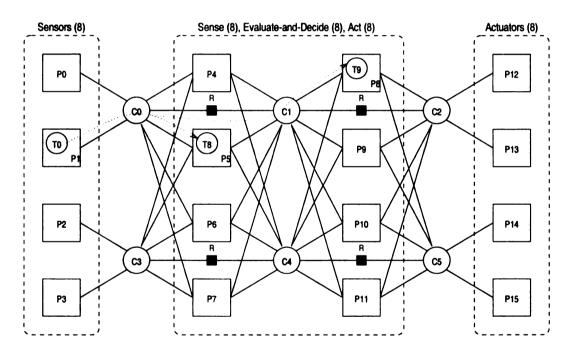

| 6.1 Target Real-Time System                                           | 137 |

| 6.2 RTSML Specification                                               | 141 |

| 6.3 RTSML Compiler Extension                                          | 150 |

| 6.4 Example Run-Time Session                                          | 156 |

| 6.5 Summary                                                           | 161 |

| 7 Conclusions and Future Work                                         | 162 |

| 7.1 Research Contributions                                            | 162 |

| 7.2 Future Work                                                       | 164 |

| APPENDICES                                                            | 166 |

| A RTSML Document Type Definition (excerpt)                            | 167 |

| B VOML Document Type Definition (excerpt)                             | 170 |

| BIBLIOGRAPHY                                                          |     |

## LIST OF TABLES

| 2.1 | Performance visualization tools and systems |

|-----|---------------------------------------------|

| 3.1 | Ranges of system parameters                 |

| 3.2 | Some constraint predicates used             |

| 3.3 | Scenario of parameter changes               |

| 3.4 | Conventional CLP approach timings           |

|     | Repair-based CLP approach timings           |

| 3.6 | Successive solutions' distances             |

| 4.1 | Summary of BRISK evaluation                 |

| 4.2 | CPU time per 6-integer NOTICE macro         |

| 4.3 | Count of increases in time frame $T$        |

|     | Peak time frame $T$ in milliseconds         |

## LIST OF FIGURES

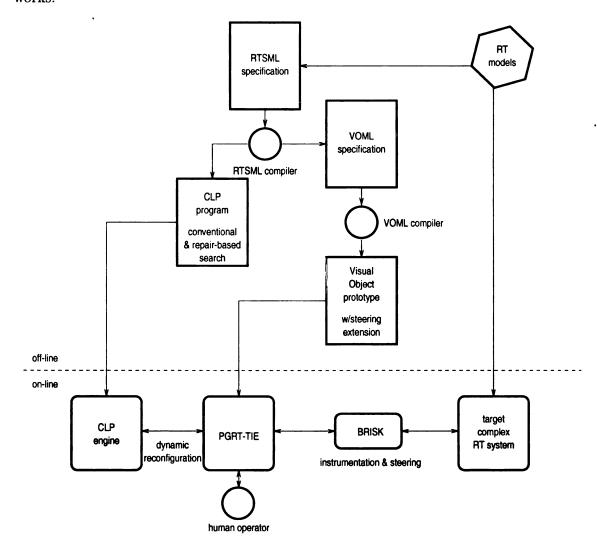

| 1.1  | Overview of the integrated approach                                                                              | 19  |

|------|------------------------------------------------------------------------------------------------------------------|-----|

| 3.1  | An example complex RT system                                                                                     | 48  |

| 3.2  | RTSML specification excerpts                                                                                     | 49  |

| 3.3  | A generic repair-based CLP program                                                                               | 66  |

| 4.1  | BRISK as an instrumentation system kernel                                                                        | 81  |

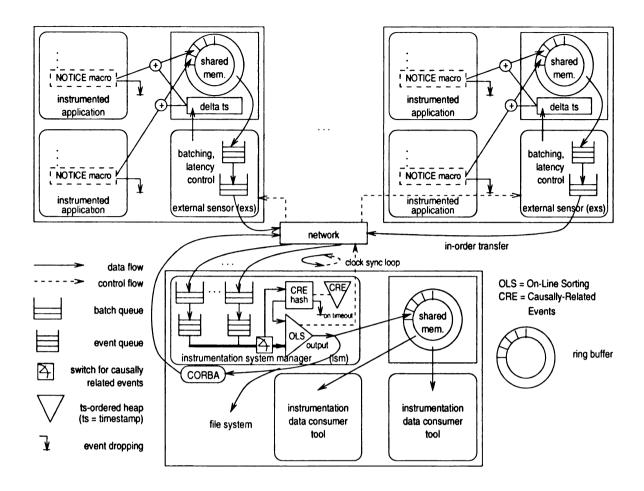

| 4.2  | Architecture of the BRISK instrumentation system                                                                 | 86  |

| 4.3  | Diagram of the BRISK basic implementation                                                                        | 88  |

| 4.4  | An example three-field NOTICE macro call (internal sensor)                                                       | 91  |

| 4.5  | In-memory structure of the event record generated by the call in Figure 4.4                                      | 91  |

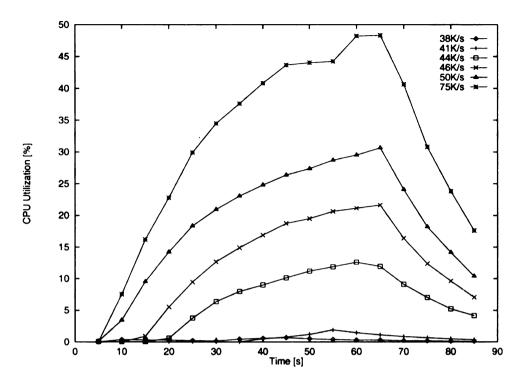

| 4.6  | EXS CPU utilization for various event rates                                                                      | 99  |

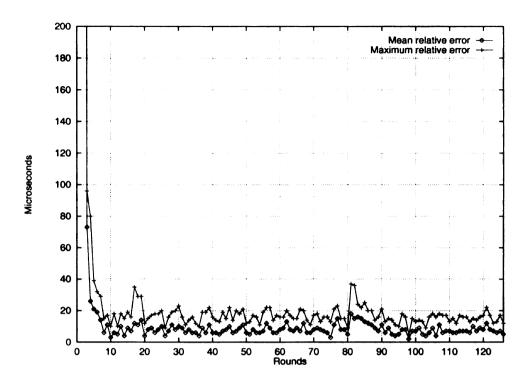

| 4.7  | Measurements of the clock synchronization algorithm (8 EXS nodes, 5-second polling period, 10-minute experiment) | 103 |

| 5.1  | The design of a visual object                                                                                    | 111 |

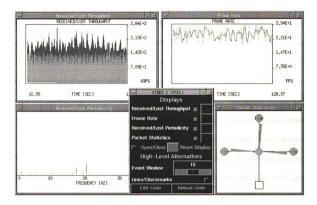

| 5.2  | On-line performance visualization of the real-time multimedia application                                        | 117 |

| 5.3  | Event Processing and Information Rendering Architecture (EPIRA)                                                  | 119 |

| 5.4  | A brief description of VOML                                                                                      | 122 |

| 5.5  | Code of the IR component used as lineplotrender in Figure 5.4b                                                   | 123 |

| 5.6  | VOML compilation and execution process diagram                                                                   | 126 |

| 5.7  | Sketch of a VOML specification that uses remote component definitions .                                          | 128 |

| 5.8  | Event declarations                                                                                               | 129 |

| 5.9  | Info and control structures                                                                                      | 130 |

| 5.10 | View initialization                                                                                              | 130 |

| 5.11 | Event processing components                                                                                      | 131 |

| 5.12 | Template IR component                                                                                            | 132 |

| 5.13 | Active IR component                                                                                              | 133 |

| 5.14 | A snapshot of the view                                                                                           | 135 |

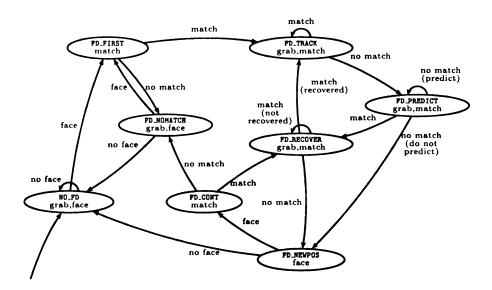

| 6.1  | Original face-tracking system's state diagram                                                                    | 137 |

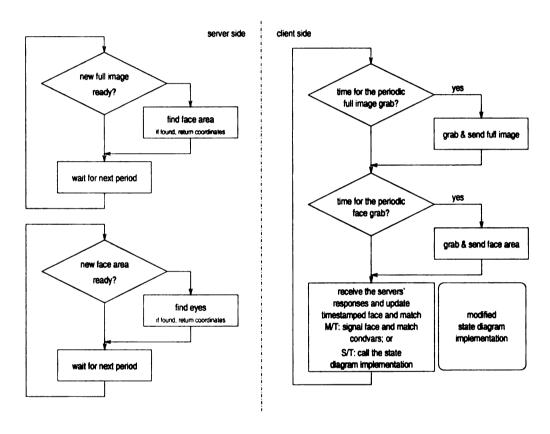

| 6.2  | Distributed face-tracking system                                                                                 | 139 |

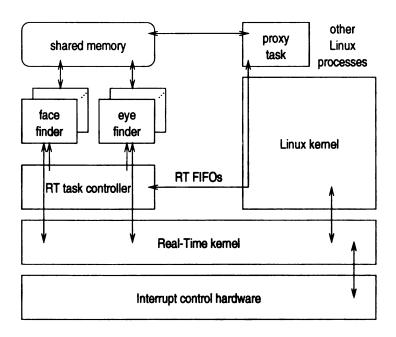

| 6.3  | RTL-specific details of the target system                                                                        | 141 |

| 6.4  | RTSML specification excerpts                                                                                     | 148 |

| 6.5  | Integrated visualization, repair and steering                                                                    | 151 |

| 6.6  | A snapshot from the RTSML-based visual object                                                                    | 160 |

## Chapter 1

## Introduction and Motivation

A broad variety of different software systems—ranging from small, embedded controllers with microsecond response times to large, heavyweight systems with response times of seconds or even minutes—have been designated "real-time." For both a power plant control system and a global air-ticket reservation system, as well as an abundance of other diverse systems, certain common characteristics can be summarized in the following definition by Selic [100]:

**Definition.** A real-time system is a software system that maintains a timely and ongoing interaction with its environment.

Unlike other system resources in conventional software systems, such as memory and processing power, the (real) time cannot be controlled; only its progress can be measured. The timeliness property of a software system is a function of the timeliness of individual activities (or tasks) that the system supports. A real-time system achieves its timeliness by managing its resources accordingly. Jensen further defines "real-time-liness" of a task [62]:

**Definition.** A task is real-time to the degree that its completion timeliness predictability is part of its logic.

The ongoing interaction property of a software system relates to a quality that is often referred to as reactivity [77]. Translated from a logic-theoretic framework to English:

**Definition.** A reactive system persists across some interval of time (possibly indefinitely) during which it responds to inputs as they occur.

In this setting, the dominant feature of a real-time system is its structure, rather than its function. To reason about the above two properties of a real-time system, its structure must be fixed, while the function may be modified. Consequently, the focus of software system design shifts from the traditional, algorithmic to structural approaches. The structural approaches range over different domains. On one end, real-time scheduling theory is mainly concerned about low-level issues, such as physical resource allocation. On the other, formal software-engineering methods address more abstract real-time requirements, such as timing relations among different application states.

## 1.1 Focus of the Dissertation

Complex real-time systems are emerging parallel or distributed, heterogeneous computer systems with many disparate constraints and requirements. For example, an embedded complex real-time system may possess limited system resources (for computation, communication and I/O) that need to be shared by many of its components.

It must perform certain tasks in a timely fashion under possibly large variances in the amount of data and events that it processes. If the system or some of its components are critical for the operation of its embedding system and/or environment, they must be made fault-tolerant. The dynamics of the environment may span from static models to stochastic ones, to unpredictable ones.

Consequently, components and subsystems of a complex real-time system are designed using appropriate, multiple models from real-time scheduling theory, resource allocation and quality-of-service management schemes. Issues that arise in the design, engineering and deployment of complex real-time systems include the following.

- Detailed models are complex and require exhaustive search through the design space to find values of model parameters for which the system satisfies imposed requirements. Engineers of complex real-time systems often cannot afford this, and use fast heuristics or simple, ad hoc schemes instead.

- 2. As the above mentioned models and schemes may vary greatly in their assumptions and goals, it is hard to analyze how they interact when the components and subsystems are to be integrated. The integration further increases the complexity of the system.

- 3. One design solution most likely cannot satisfy the requirements when the system parameters vary significantly and dynamically. In a dynamic system reconfiguration, the quality of a new design solution is almost always traded for the speed of the reconfiguration.

- 4. System performance data needed to decide whether and what kind of dynamic reconfiguration should be performed, has to be collected and analyzed on-line. In integrated complex real-time systems with end-to-end requirements, justified decisions can only be made using global information.

- 5. To collect the performance data from a distributed, heterogeneous real-time system, a portable distributed instrumentation system (IS) is needed. It has to be designed with low real-time intrusion and flexible performance in mind.

- 6. Although the performance data can be analyzed completely automatically, it is often required that a human operator has insight into the system performance and makes reconfiguration decisions. To present system performance information at a high level, a performance visualization technology is crucial.

Problem Statement. The central focus of research presented in this dissertation has been a unifying, extensible, compiler-based framework for the design and engineering of complex real-time systems. Its novelty is manifest in a comprehensive application of a constraint programming technology in model-based design and integration of complex real-time systems. In addition, the framework lends itself to further extensions, such as a novel integration of on-line performance visualization and dynamic system reconfiguration. In this broader context, the dissertation research foci are in the areas of distributed system instrumentation and on-line performance visualization, aiming at improved testing and deployment support for complex real-time systems.

The unifying property of the framework is related to the goal of supporting disparate real-time models of system components and their integration. The compiler-based property is aimed at allowing users of the framework to specify complex real-time systems at a high level, and have a knowledge-based compiler that would handle the complexity behind high-level specifications. The extensibility property applies to both the front and back ends, and is achieved through an extensible syntax and add-on modules that cooperate in constructing a model of the whole complex real-time system. The framework supports solving for the system parameters using multiple, controllable problem-solving approaches. It also integrates an on-line performance visualization technology and facilitates creating real-time model- and system-specific performance visualizations. This integration is especially suitable for visualization-driven on-line system reconfiguration.

The general problem and solution of this dissertation should be regarded from a systems engineering point of view. As defined in [55], systems engineering is a discipline that develops and exploits structured, efficient approaches to analysis and design to solve complex engineering problems. Its focus is on methods to solve problems, not the solution of the problems per se.

In the following section, the motivation is discussed for the research in the areas of the design and engineering of complex real-time systems, distributed system instrumentation, and on-line performance visualization, respectively.

## 1.2 Motivation

In [104], Stankovic concludes that, despite extensive results in the area of real-time scheduling in recent years, the state of the art still provides piecemeal solutions. There are many realistic issues that have not yet been addressed in an integrated and comprehensive manner. New scheduling approaches should be analyzable and comprehensive enough to simultaneously handle multiple characteristics of real-time systems, such as: task preemptiveness, periodicity, importance, and grouping; precedence, placement, and end-to-end timing constraints; communication, resource, and fault tolerance requirements; tight and loose deadlines, and normal and overload conditions. The solution should be integrated enough to handle interfaces between

- CPU scheduling and resource allocation,

- I/O scheduling and CPU scheduling,

- CPU scheduling and real-time communication scheduling,

- local and distributed scheduling, and

- static scheduling of critical tasks and dynamic scheduling of essential and nonessential tasks.

These issues are too complex to be addressed all at once, and it will probably take years of researchers' work before first comprehensive and tightly integrated real-time models are devised. However, there are two constituents of a solution to the general problem: one is the real-time theory (including scheduling and formal methods), and the other is systems engineering. Tools are needed that will bridge the gap between theory and practice in an efficient manner.

## 1.2.1 Design and Engineering of Complex Real-Time Systems

An idea behind this dissertation that has led to the choice of the main parts of the compiler-based framework—the target language and compiler back-end—is that a complex real-time system could be regarded as a complex, highly non-linear network (or circuit), seemingly analogous to those from, e.g., control theory. (Although the similarity comes from non-linear relations between interconnected components—in particular, the way changes in operation of an element affect the operation of other elements—it is difficult to see whether analogues of the control theory approaches can help with solving real-time computer system problems. Almost the opposite, real-time control systems, are common nowadays [14]. There has been theoretical research [110] in applying the control theory to proving the stability of self-stabilizing distributed algorithms. However, no real-time properties of algorithms or systems have been analyzed.) In such a network, real-time activities are performed according to real-time models, across interconnected bounded hardware resources. Relations among the activities and the resources, within subsystems and among the subsystems, are relatively simple and best termed as time and resource constraints expressed via equations and inequalities of the real-time models. This common underlying property of real-time models has been a major motivation for adopting a constraintprogramming approach to solving complex real-time system problems. To solve such a network means to solve for unknown real-time model parameters and perform the resource allocation. This inevitably requires combinatorial search in general.

A new class of programming languages combining the declarativity of Logic Programming with the efficiency of constraint solving is Constraint Logic Programming (CLP). New application areas, including combinatorial search problems such as scheduling, planning or resource allocation can now be tackled, which were intractable for logic programming [36]. The declarativity of a Prolog-like CLP language provides an elegant way of expressing the disparate requirements of complex real-time systems in an integrated manner.

Among the research foci proposed by a group of leading experts for real-time systems [103] is the development of requirements and internal documentation which can state real-time requirements precisely and can be used for maintenance and inspection of safety critical systems. Specifying a complex real-time system means specifying its structure and relations among individual components and subsystems, accompanied with real-time semantics. This task can be broken into two orthogonal ones. First, the structure (such as the breakdown of computation and communication onto tasks and messages) and basic relations (such as resource allocation) are independent of the heterogeneity present in complex real-time systems that primarily comes from disparate real-time models. Their specification can be supported by a fixed syntax. Second, each real-time model defines certain semantics, and some semantics are attached to the rules of integration of two different real-time models. These rules can be viewed as a variable, model-specific syntax.

The Standard Generalized Markup Language (SGML) [42] is a meta-language and information infrastructure for structured documents and specifications that has been used, among many other applications, for maintaining technical documentation. It

allows for explicitly specifying the structure of a document and the relations among its elements, while the checking of the document semantics is performed by tools called SGML applications. The motivation to use SGML for the compiler front-end comes from an idea that a complex real-time specification can also be viewed as a multi-purpose specification document. In other words, the compiler front-end is an SGML application.

### 1.2.2 Distributed Instrumentation Systems

Besides specification and problem-solving tools addressed in the previous subsection, tools are also needed that can provide feedback from tested and deployed complex real-time systems. The feedback in the form of collected system performance data can be analyzed on-line or most-mortem, and is necessary for validating the design assumptions. Furthermore, the performance data collected and analyzed on-line can be further fed to a problem-solving tool, in order to find new values of system parameters that might better handle a current situation imposed onto a deployed system by the environment. It should also be possible to enforce the new parameters onto the running target system. Altogether, a distributed instrumentation system, which can be used for collecting performance data in real time and without significant intrusion on the target complex real-time system, is necessary. Since it would have an infrastructure to link the real-time system performance data and the problem-solving tool in one way, reusing the infrastructure for steering the target system (i.e., enforcing the new parameters) is possible. Finally, the heterogeneous and still evolving

nature of complex real-time systems prevents making most of detailed design and implementation decisions of such a distributed IS at once and in advance. Hence, the needed IS should rater be designed and seen as a kernel than a final and complete implementation.

Designers and users of parallel and distributed systems have applied a variety of monitoring methods and instrumentation techniques to gather information for testing, debugging, and analyzing performance and optimizing systems [112]. These methods and techniques require development of systems for instrumentation data collection, management and analysis, which are themselves distributed systems. A distributed instrumentation system is typically specialized to an application domain and/or computing environment. Moreover, the distributed nature often makes it harder to use and adapt. A significant investment in time and effort may be needed to understand the IS implementation sufficiently to port and/or configure it for another application and/or environment.

An off-the-shelf distributed IS that is robust, portable and flexible would benefit both designers and users of a wide range of parallel and distributed systems. It would allow them to instrument and begin monitoring their system rapidly, and as needed subsequently, to optimize or extend the IS for their environment. High performance and openness of the IS implementation are equally important for its success as general-purpose systems software.

Obviously, the requirements of a distributed IS for instrumenting and steering complex real-time systems are broad, and even exceed those for instrumenting conventional parallel and distributed systems. A viable approach to the design and

implementation of such an IS could be one of a portable and flexible distributed IS kernel, augmented with features that are needed in the complex real-time system domain. One such IS feature, for example, is being able, to a certain degree and with cooperation with the operating system, to schedule its computation and communication activities in a way that reduces its intrusion, in the real-time sense, on the target system.

#### 1.2.3 On-Line Performance Analysis and Visualization

With the advent of computer technology, systems are becoming more and more complex and, at the same time, there is more and more computing power available and needed for supporting the systems themselves, in various forms of on-line analyses. One large class of the on-line analysis deals with the system performance, trying to summarize and/or explain various performance metrics, such as the efficiency of resource usage or quality of service provided for higher-level activities. Advanced analyses attempt to diagnose performance problems and suggest actions that may lead to the performance improvements. In the domain of complex real-time systems, the on-line analysis places emphasis on different measures of the real-time-liness, both hard and soft, individual and collective ones.

Performance analysis and visualization (PAV) tools are crucial components of an effective development cycle, as well as deployment, of parallel and distributed applications. On-line PAV is even becoming necessary for the latter. Since the amount of performance data to be analyzed and visualized increases with the size of a target par-

allel/distributed application, on-line PAV itself should be distributed. Heterogeneous systems, in addition, need PAV tools that provide flexible integration and configuration support for heterogeneous performance data. Extant generic and library-specific PAV tools for parallel/distributed systems can cover only low-level performance aspects, provided that the target systems fit into their generic schemes and/or use specific libraries, such as PVM [32] and MPI [31]. A wider range of performance aspects, at multiple levels, global and local, are needed to capture and visually explain the behavior of a heterogeneous system.

As the performance data are gathered from different subsystems and components of a complex real-time system by a distributed IS, they need to be analyzed according to general, but also model-specific real-time-liness criteria. One example of modelspecific criterion is that in all sequences of n invocations of a periodic activity, at least  $m \ (m < n)$  must meet their deadline [15]. This requires a PAV tool that can be extended to support new analyses. There are also real-time quality-of-service metrics of interest that have a more complex semantics than, for example, the just mentioned m-out-of-n criterion. Such metrics are often used for applications running atop of systems that provide generic real-time support. In these cases of vertical realtime integration, automated analyses that are comprehensive and helpful are hard to devise, and it may be necessary to provide visualizations of simpler performance metrics for a human operator to analyze ad hoc instead. Finally, complex real-time systems are supposed to guarantee a degree of aggregate real-time-liness through the integration of its subsystems and components. However, if certain temporary conditions, such as overloads, violate the design assumptions, the guarantee is voided. If the assumed real-time-liness is found to have deteriorated, it may be safer to treat the situation as unpredicted than to analyze it automatically. Again, the human operator needs a potentially large amount of performance information presented in the form of visualizations in order to make a dynamic reconfiguration/recovery decision.

Altogether, on-line PAV tools can greatly benefit the testing and deployment of complex real-time systems. If well integrated with a suitable model-based problem solving framework, it would extend the latter from a static to a dynamic one, and make it achieve even higher level of abstraction (from textual specifications to visualizations) provided for the system designers and users.

## 1.3 Research Objectives, Activities and Contributions

This section states the objectives of the research presented in the dissertation. The statements are followed by the description of activities undertaken towards meeting the objectives, and a summary of contributions that have resulted from the activities.

There are four research objectives:

To devise a systems engineering framework particularly suitable for the design and engineering of complex real-time systems. This includes a systems specification language and multiple problem-solving approaches, as well as an automated mapping between them.

- 2. To investigate performance and portability issues of the instrumentation of parallel and distributed, heterogeneous systems. The performance issues include real-time properties relevant to the instrumentation of complex real-time systems.

- 3. To discover common properties of extant on-line PAV tools for parallel and distributed, heterogeneous systems, as well as gather desired properties of the on-line PAV viewed as a real-time middleware. Using the findings, to devise a comprehensive PAV framework as a basis for advanced extensions.

- 4. Finally, to integrate the systems engineering and on-line PAV frameworks in a way that facilitates on-line system steering/reconfiguration of complex real-time systems. The integrated approach should be semi-automated, and allow algorithmic and visual analyses of instrumentation data received from the target system to utilize problem-solving tools.

The activities in pursuit of the above objectives were carried in the following order, with certain overlappings:

- 1. The first version of an object-oriented, on-line PAV software was designed and implemented.

- 2. The CLP technology was chosen as appropriate and promising for solving design and engineering problems of complex real-time systems.

- 3. A simple distributed instrumentation system was designed and developed.

- 4. Several real-time models and small test systems were used for determining the power of a publicly available CLP tool. The CLP code was either written manually or generated by utility tools.

- 5. The distributed IS was made more portable, augmented with performance tuning options and reconceived as an extensible IS kernel.

- 6. The first version of a complex real-time system specification language and its translator to CLP were designed and implemented.

- 7. The on-line PAV software was vertically extended into a component-based technology, and supported by a high-level language and compiler.

- 8. A new version of the systems specification language was introduced together with an extensible compiler. The first complex real-time system was modeled.

- 9. The distributed IS kernel was evaluated, and then extended to provide instrumentation control and steering.

- 10. The on-line PAV technology was ported, in addition to the Unix/X11 domain, to the Java/WWW domain.

- 11. A real-time test-bed and client-server system were prepared for evaluating the three constituents (the systems engineering framework, the on-line PAV technology, and the distributed IS kernel) of the integrated approach together.

- 12. The compiler for the complex real-time system specification language was rewritten and extended to generate system-specific code that is input to the on-line PAV technology.

This research has made four notable contributions to the state of the art in the design and engineering of complex real-time systems, and instrumentation and on-line performance analysis & visualization of a wider range of parallel and distributed, heterogeneous systems:

1. A compiler-based approach to design and engineering of complex realtime systems. Based on a comprehensive usage of the CLP technology, this contribution addresses the first objective and problem statement by (1) enabling high-level specifications of complex real-time systems that place emphasis on the system structure and real-time models involved; (2) automated handling of model-specific details, including the integration of different real-time models; and (3) providing multiple problem-solving approaches, such as finding optimal solutions and repairing partially correct solutions.

This contribution addresses the second objective and part of the problem statement by providing (1) a flexible and robust tool for instrumenting complex

2. A portable and flexible distributed instrumentation system kernel.

real-time systems; (2) base for developing elaborate, domain-specific distributed

ISes; and (3) test-bed for experimenting with IS managing polices and IS-specific

distributed algorithms.

- 3. An on-line performance visualization technology. Centered around an object-oriented, portable and distributable, adaptive, system- and application-specific on-line performance analysis and visualization framework that supports rapid prototyping, this contribution addresses the third objective and important part of the problem statement related to the dynamic reconfiguration/steering of complex real-time systems. The technology extends the core framework with (1) a PAV-specific architecture and very high-level language designed atop of it; and (2) component-based approach to development of PAV tools; which together form (3) a base for automated and advanced PAV systems, such as the last contribution in this list.

- 4. An integrated approach to real-time system design and on-line PAV with steering. This contribution extends the compiler from the first contribution with support for generating code that is treated as input to the PAV technology of the third contribution; it also utilizes the distributed IS kernel

from the second contribution to instrument and steer complex real-time systems. The fourth objective and problem statement are addressed by a novel, integrated technology that tightly links a target complex real-time system, its specification, an appropriate PAV, and PAV-driven and model-based dynamic reconfiguration; and does so in a mainly automated manner.

Overall, all the contributions were supported with a proof of concept. Whenever the time and technical conditions permitted, performance evaluations were carried out additionally to support the contributions.

## 1.4 Organization

Chapter 2 discusses background and related work. Several approaches to the design of distributed real-time systems are described first. Constraint Logic Programming is introduced and several works that use it as support for the specification and verification of real-time systems are described next. They are followed by related work on checking of explicit timing constraints. Issues in distributed instrumentation are discussed, and an overview of several distributed ISes is presented. The chapter ends with a discussion on on-line performance analysis and visualization (PAV).

Chapter 3 presents the compiler-based approach to design and engineering of complex real-time systems, the central focus of the dissertation. First, the Real-Time System Markup Language (RTSML) is described. An example complex real-time system is presented next, followed by the process of compiling its RTSML specification to CLP. Salient characteristics of the compiler back-end and the descriptions of

two real-time model-specific modules are presented. Results of experiments with the example complex real-time system are analyzed.

Chapter 4 presents a portable and flexible distributed instrumentation system kernel called BRISK. Along with the description, approaches that provided IS performance gains are discussed. The objectives of BRISK, approaches taken in its design and implementation, the architecture and implementation details, and results of evaluating its performance and scalability are presented.

Chapter 5 presents a software technology for on-line performance analysis and visualization of parallel and distributed, heterogeneous systems. A visual object framework is described, followed by an example of its successful use for PAV of a distributed multimedia real-time application. A PAV architecture for the visual objects, a markup language based on it called VOML, and the development environment are presented next. The chapter concludes with an example of a VOML specification and corresponding performance visualizations.

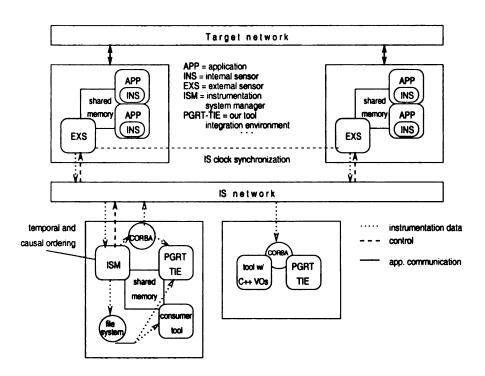

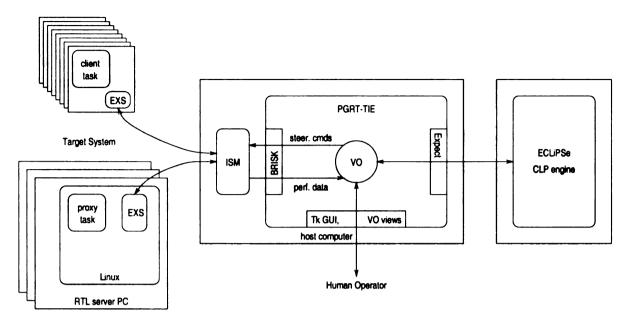

Chapter 6 presents an integrated approach to the design and engineering of complex real-time systems, their instrumentation, on-line PAV, and dynamic system reconfiguration. Figure 1.1 illustrates this approach; it also serves as a reference by showing the relations between different parts of the work presented in this dissertation. A real-world target distributed real-time system is described, followed by a description of its design and engineering performed using the approach described in Chapter 3. Technical details of the integration are explained next, and the operation of the new, integrated technology is shown on an example execution scenario.

Chapter 7 concludes the dissertation with a summary of the major contributions and future directions in areas that include complex real-time system problem-solving related optimizations, extensions of the distributed IS kernel, advanced on-line PAV tools, and different integrations of the systems engineering and on-line PAV frameworks.

Figure 1.1: Overview of the integrated approach

## Chapter 2

## **Background and Related Work**

This chapter discusses background and previous work related to the dissertation research presented in the following chapters. The first section covers several approaches to the design of distributed real-time systems. The second section provides background in Constraint Logic Programming (CLP) and presents several works that use it as a tool in the area of real-time systems. The third section overviews other works in the area of real-time systems that deal with explicit timing constraints (as opposed to implicit ones, such as those contained in the constraint formulae from real-time scheduling theory models). The fourth section describes several distributed instrumentation systems and their relation with BRISK. Finally, the fifth section describes related work in the area of system performance visualization, including a few more comprehensive, integrated approaches.

## 2.1 Distributed Real-Time System Design

As was stated in Section 1.2, the state of the art in the area of real-time scheduling still does not provide integrated and comprehensive solutions for realistic scenarios. Among many fragmented design and engineering approaches for parallel and distributed real-time systems, some concentrate on integration and decomposition. More comprehensive approaches usually propose a search algorithm for solving system parameters, such as branch-and-bound, simulated annealing, or even greedy. For specific classes of distributed real-time systems, an approach may include run-time support as well. The descriptions of some related approaches are presented below and ordered approximately from simpler to more complex ones.

In [102], Spuri and Stankovic address the problem of integration of task precedence constraints with resource sharing in real-time scheduling. Their motivation is to give more freedom to the scheduler so that more dynamic real-time systems can be supported. They derive analytical task schedulability formulae that can be applied in more real-time system situations than previously developed.

An engineering technique for decomposing end-to-end delays in distributed realtime systems is proposed by Saksena and Hong [97]. In effect, a global distributed scheduling problem is transformed into a set of single-processor scheduling problems with local deadlines. The problem solving approach consists of an approximate technique to quickly generate an initial solution, and an iterative method to fine-tune the initial solution. In an end-to-end approach to the design of real-time systems by Gerber et al. [39], real-time applications are structured as a set of process components, connected by asynchronous channels in which the end-points are the system's external inputs and outputs. End-to-end propagation delay, temporal input-sampling correlation, and allowable separation times between updated output values, are postulated as end-to-end constraints. The problem solving approach is a multi-stage procedure that involves an augmentation of the problem, an optimization algorithm that generates a set of intermediate rate constraints, and a domain-specific constraint solver.

An approach to scheduling and allocation in multiprocessor real-time systems is described in [23]. Cheng develops a hybrid timings model that combines absolute and relative timing constraints on tasks. Based on this model, the simulated annealing technique is applied as the overall search algorithm to find feasible schedules over multiple processors. A task replication technique (for the purpose of improving the scheduling) is developed and embedded into the simulated annealing algorithm.

A framework that provides a systematic approach to designing distributed, heterogeneous real-time systems that utilize resources in an efficient, pipelined and predictable manner, is proposed by Chatterjee and Strosnider in [22]. It defines abstractions for representing real-time applications and capturing the fundamental properties of distributed pipelining; a flow control mechanism; a decomposition of the multi-resource scheduling problem into a set of single resource scheduling problems with well-defined interactions; an analysis methodology to support heterogeneous scheduling policies among system resources; and a delineation of how manipulating

system configuration parameters affect various application timing metrics. It does not specify any particular mapping or optimization technique.

In [84], Mutka and Li describe a tool that finds feasible processor allocations for sets of rate-monotonically scheduled (RMS) tasks over a set of heterogeneous processors. It uses three different RMS tests, considers possible task blocking due to priority inversion, allows task co-allocation, and can perform task transformations if needed. Communication among the tasks is not considered. The problem solving approach is based on a branch-and-bound algorithm.

An optimal solution to the problem of allocating communicating periodic tasks to heterogeneous processing nodes in a distributed real-time system by Peng et al. is presented in [87]. The maximum normalized task response time is minimized subject to the precedence constraints resulting from intercommunication among the tasks to be allocated. The task system is modeled with a task graph in which computation and communication modules, communication delays, and intertask precedence constraints are described. These tasks are assigned to processing nodes by using a branch-and-bound search algorithm.

In [66], Kang et al. describe a distributed real-time system model with statistical, end-to-end constraints. It exploits both discrete-time Markovian analysis and real-time scheduling theory, and uses several approximations to avoid modeling the entire system. A system is modeled as a set of chains, where each chain is a distributed pipeline of tasks, and a task can represent any activity requiring non-zero load from a processor or network resource. Every chain has two end-to-end constraints: delay and minimum allowable success rate for outputs that meet their delay constraints. The

search algorithm uses two heuristics, which help in significantly reducing the number of potential feasible solutions but, at the same time, can miss some and report a failure.

PERTS [101] is a commercial prototyping environment based on the rate monotonic analysis (RMA), initially developed at the University of Illinois at Urbana-Champaign. It integrates multiple analysis tools allow a real-time system designer to test and evaluate the system against various design scenarios. Several real-time scheduling algorithms and protocols are supported, and end-to-end analysis for single-and multiple-node architectures is provided. It interfaces to Real-Time CORBA [27], ObjecTime [74] and a few more real-time software technologies.

An approach due to Welch et al. for engineering time-constrained systems which must operate in dynamic environments (with potentially unknown worst-case scenarios and large, unpredictable variances in system parameters) is presented in [120]. A specification language was developed that enables the description of environment-dependent features. An abstract model constructed from the specifications is augmented dynamically with the state of environment-dependent features. It is also used to define techniques for quality-of-service monitoring and diagnosis, and allocation analysis. A prototype resource-management middleware was developed to experimentally evaluate the approach.

In the light of an overall approach that would be able to handle all the issues brought out by Stankovic and listed in Section 1.2, the approach presented in this dissertation attempts to address the need for a comprehensive computer-aided design and engineering framework for complex real-time systems. However, it fundamentally

differs from one that implicitly follows from the above-mentioned motivation in [102] by the same author. The latter is based on the need for a single real-time scheduling approach that would address as many realistic scenarios at once as possible. The approach presented in this dissertation aims to integrate and compose extant realtime scheduling approaches, which address only specific scenarios, into a complex, more realistic one. Intuitively, a single complex scheduling approach might not scale well in complex real-time systems, which are parallel/distributed systems that should scale with respect to the system real-time-liness. (It is easy to see that for a single resource, such as CPU, the addition of support for more realistic scenarios in real-time systems, such as fixed priorities to activities and/or resource sharing among activities, strengthens schedulability conditions, resulting in a lower resource utilization.) Such an approach might overly underutilize the resources, leaning toward extensive resource sharing and tight integration. In other words, an inherent property of loosely-coupled systems, such as distributed computer systems, is that the operating time scale is larger than that of tightly-coupled ones, such as symmetric multiprocessors. This is rather relevant to realistic real-time systems, in which the operating time scale affects the real-time-liness. (As a side note, anticipating as many realistic scenarios at once as possible is similar to analyzing worst cases in the hard real-time scheduling theory. For a reference, Jensen in [63] argues that hard real-time scheduling does not scale.) Another important difference between the two approaches is that Stankovic' one is more scheduling theoretic, while the one presented in this dissertation is a systems engineering approach. The former attempts to devise real-time scheduling models that would support more realistic scenarios without strengthening feasibility

conditions. The latter attempts to build realistic real-time systems by placing an emphasis on the use and integration of appropriate extant real-time models.

# 2.2 Constraint Logic Programming and Real-Time Systems

Constraint Logic Programming tools have matured over the last decade and solvers exist for a wide range of problem domains. For example, solvers for combinatorial problems over finite domains and sets, systems of equations and inequalities involving rational and real numbers, and solvers for systems of non-linear equations over real numbers can be integrated within a CLP tool by the means of a Logic Programming language, usually extended Prolog. CLP has been used in a variety of applications, such as scheduling, resource allocation, timetabling, financial planning, frequency assignment for cellular phones, etc. [116] Research in various areas of engineering have used CLP for solving practical industrial problems. Constraint Logic Programming has been used in some areas of computer-aided engineering (e.g., in mechanical engineering [69, 107]; for VLSI design of electrical circuits [13]; in manufacturing [124]; in computer system performance analysis [75]) in the recent past. In the context of Artificial Intelligence, a more general framework of Constraint Programming has been used in reactive systems [35] and electro-mechanical machines [114].

Before more related work, which uses CLP in the area of real-time systems, is presented in Section 2.2.2, CLP background is given in Section 2.2.1. Section 2.2.3 describes  $ECL^iPS^e$ , the CLP tool used in the work presented in this dissertation.

### 2.2.1 Constraint Logic Programming Background

The insight which led to the design of the CLP framework is the observation that the algorithm of unification used in Logic Programming (LP) is a constraint solving algorithm and as such it could be combined with, or replaced by, various other constraint solving algorithms. In other words, LP offers the means to create a single and powerful framework for various cooperating constraint solving algorithms [116].

More formally, CLP is a many-sorted generalization of LP, in which different sorts are associated with different interpretation domains, and corresponding formulae are manipulated using predefined constraint solvers. Special classes of formulae, called constraints, are not handled using traditional resolution, but are interpreted under a predefined specific interpretation and handled by external constraint solvers. Basic definitions of the formal CLP framework presented in [71, 56] are given below.

A CLP language is built upon a set  $\Sigma$  of function and constraint predicate symbols, called *signature*. Primitive constraint predicates (including the equality symbol =) belong to  $\Sigma$  and are interpreted with respect to a predefined interpretation structure, called  $\Sigma$ -structure, while user-defined constraint predicates are subject to the user definitions.

A term is an object created using function symbols from  $\Sigma$  and a collection of variables. It can be either a simple variable or an application  $f(t_1, \ldots, t_n)$  of an n-ary function symbol  $f \in \Sigma$  to n terms  $t_1, \ldots, t_n$  ( $n \geq 0$ ). An atom is an application  $p(t_1, \ldots, t_n)$  of a constraint predicate symbol p to n terms  $t_1, \ldots, t_n$ . If p is a primitive constraint predicate, then the atom is called a *primitive constraint*. Every *constraint* is built from primitive constraints. A program is composed of a collection of clauses, where each clause has the form:

$$head: -c \mid b_1, \ldots, b_k$$

where head and  $b_i (i = 1, ..., k)$  are user-defined atoms, while c is an arbitrary conjunction of constraints. The symbol | is used in the body of the clause to separate the constraint part from the goals and can be read as "and," in the same way as a comma in the body of the clause.

A  $\Sigma$ -structure D consists of a set D and an interpretation function  $I_D$ . A constraint c is solvable if  $D \models \exists (c)$ , where the notation  $\exists (\phi)$  denotes the existential closure of the formula  $\phi$  (i.e., each variable in  $\phi$  is within the scope of an existential quantifier). A  $\Sigma$ -theory is a collection of closed  $\Sigma$ -formulae (i.e., formulae built over  $\Sigma$ ). A solution  $\theta$  for c is a mapping from the variables in c to D, such that  $D \models c\theta$ .

The execution of a constraint program requires the use of constraint solvers capable of deciding the solvability of each possible constraint formula. Resolution is extended in order to embed calls to constraint solvers. If  $?-c_1 \mid g_1, \ldots, g_n$  is a

goal, and  $p:-c_2 \mid b_1,\ldots,b_k$  is a clause in the program, then the resolvent of the goal wrt. the given clause is

$$? - (c_1, c_2, g_1 = p) \mid b_1, \dots, b_k, g_2, \dots, g_n$$

as long as  $D \models (c_1 \land c_2 \land (g_1 = p))$ . The symbol = is an abbreviation for the conjunction of equations between corresponding arguments of  $g_1$  and p, if  $g_1$  and p have the same predicate symbol. The constraint solver is used to test the validity of the condition on the constraints.

The idea behind the introduction of the CLP framework is that a logic-based programming language, its declarative and operational semantics and the relationships between these semantics can be parameterized by a choice of the domain of computation and constraints. The resulting scheme defines the class of languages  $CLP(\mathcal{X})$  obtained by instantiating the parameter  $\mathcal{X}$  [116].

The parameter  $\mathcal{X}$  stands for a 4-tuple  $(\Sigma, D, \mathcal{L}, \mathcal{T})$ , where  $\Sigma$  is a signature, D is a  $\Sigma$ -structure,  $\mathcal{L}$  is a collection of  $\Sigma$ -formulae and  $\mathcal{T}$  is a first-order  $\Sigma$ -theory. The  $\Sigma$  determines the predefined predicate and function symbols with their arities, D is the structure over which computation is to be performed,  $\mathcal{L}$  is the class of constraints which can be expressed, and  $\mathcal{T}$  is an axiomatization of some properties of D. The pair  $(D, \mathcal{L})$  is called a *constraint domain*. One such domain, FD, will be described in Section 2.2.3.

#### 2.2.2 Use of CLP as Support for Real-Time Systems

CLP and its more general version, Constraint Programming, have successfully been used as a tool for solving specific problems in the area of real-time systems as well as other areas with certain real-time aspects, ranging from temporal reasoning and scheduling to formal methods, to resource allocation. This fact supports the motivation for using CLP as an elegant way of expressing the disparate requirements of real-time systems, in Section 1.2.1.

A family of logics and associated programming languages for representing and reasoning about time is introduced in [37]. The family is conceptually simple while allowing for different models of time. Formulae can be labeled with temporal information using annotations. Unlike temporal logic [88], both qualitative and quantitative (metric) temporal reasoning about definite and indefinite information with time points and time intervals in different models of time are supported. The introduced temporal annotated logic can be made an instance of annotated constraint logic, and there is a systematic was to make a clausal fragment executable as a CLP program.

A new class of application domains for Constraint Programming is introduced in [98], due to the emergence of special real-time systems, enjoying increasing popularity in the areas of automotive electronics and aerospace industry. Real-time systems of this kind are time-triggered in the sense that their overall behavior is globally controlled by a recurring clock tick. An off-line scheduling approach maps infinite, periodic processing onto a single time window of a fixed length. The authors also

describe which techniques from traditional scheduling and real-time computing led to success and which failed, when confronted with a large-scale application of this type.

In [33], the author first explains how the bottom-up evaluation method of Revesz for computing least-fixed points of CLP programs can be adapted from the domain of integers to the domain of reals. The procedure is applied on a state reachability problem in timed automata [2], also including certain extensions of timed automata. It has been successfully experimented for proving automatically the correctness of a sophisticated reactive program that controls dataflow rates on ATM networks.

A CLP-based framework is developed in [46] for specification and verification of real-time systems that is based on the notion of timed automata. A user models the ordering of real-time events as the grammar of a language accepted by a timed automaton, and real-time constraints on these events are then captured as denotations of the grammar productions specified by the user (i.e., the valuation function of the associated denotational semantic maps into the time domain). The resulting specification is a CLP program that is executable. Many interesting properties of the real-time system can be verified by posing appropriate queries to this CLP program. The approach is also constructive in the sense that conditions can be computed under which a property will hold for a given real-time system.

In [45], the author applies CLP on a problem of global optimization of DSP application mapping onto parallel architectures. The problem is characterized by numerous resources (number of processors, bandwidth, memory size), real-time constraints (latency, sampling) and many non-linear constraints. The author also notices the capacity of CLP to compose several concurrent system models. Certain aspects

of the problem are presented in [3]. It is shown how it is possible to handle and solve three system models at once, under architectural and real-time constraints: a data-partitioning model equivalent to that supported by HP Fortran; a fine-grained (at macro-instruction level) scheduling; and a capacitive, distributed shared memory model.

#### 2.2.3 Overview of $ECL^iPS^e$

The ECL<sup>i</sup>PS<sup>e</sup> platform integrates a number of constraint solvers, including ones for solving sets of constraints over finite domains CLP(FD), real and rational numbers (CLP(R,Q) [52]), and intervals over real numbers (RIA) [53]. A special library called REPAIR [96] allows the user to start with a tentative solution, which can be modified, or repaired, if it turns out inconsistent with the constraint set.

The finite domain support consists of three libraries: for symbolic finite domains; for handling integer variables and numerical constraints on these variables; and with built-in complex constraints. The second library is the major one, propagating equations and inequalities between linear expressions. A linear numeric expression is one that can be written in the form  $Term_1 + Term_2 + \ldots + Term_n$ , where each term can, in turn, be written as Number or  $Number \cdot Variable$ . According to the definitions in Section 2.2.1, the set D in this case is the set Z of integers, and finite domain constraints are existential positive formulae built up from the linear expressions and the five predicates =, >, >, < and  $\le$ , interpreted in Z, and infinitely many membership predicates  $\in [a, b]$ , one for each finite interval [a, b] of Z. The

primitive constraint  $x \in [a, b]$  is interpreted by the empty set when b < a; similarly, x = a and  $x \in [a, a]$  are identified. Solving finite domain constraints is both NP-complete and very important for practice, which has favored the use of a practically efficient technique called *constraint propagation*. It consists of a set of transformation rules such that each primitive ordering or equality constraint c between the variables  $x_1, \ldots, x_n$  in c, whose domains are defined by membership constraints  $x_i \in [a_i, b_i]$ , induces new restrictions on these domains, resulting in new membership constraints. A reduced domain  $RD(x_j, c)$  of the variable  $x_j$  for c is the smallest interval  $[a'_j, b'_j]$  containing all  $m \in Z$  such that the constraint obtained by substituting  $x_j$  by m in  $c \wedge \left( \bigwedge_{i=1}^{i=n} x_i \in [a_i, b_i] \right)$  is satisfiable in FD.

In practice, a typical CLP(FD) program consists of three sections. First the domains of program variables are declared (the notation is slightly different than above; comma is used to separate intervals, and intervals are specified using ..). For example, the variable declaration Task\_0.TimeAt1MIPS :: [0, 1000 .. 2000] could be interpreted as task 0 being either inactive (does not use any CPU time) or active such that it may require between 1,000 and 2,000 milliseconds of CPU time on a unit-capacity CPU. (Some program variables, a.k.a. meta-terms, may be assigned attributes other than finite domains, and multiple different, cooperating constraint solvers may be involved.) Second, constraints are stated that are used to build a constraint network at run time. As opposed to the generate-then-test approach to searching of logic programming, CLP uses a much more efficient constrain-thengenerate approach. The last program section defines the order the program variables will be assigned values, which are consistent with the constraints, and the order

those values will be tried; this is called *labeling*. Sometimes, stating the constraints is enough to reduce the domains of program variables to single values and obtain solutions, if any. In other situations, the CLP system cannot decide the problem with this information only, i.e., it may return domains of the program variables' values for which there might be solutions. As the program variables are assigned values in an user-specified order, their domains are further reduced by the constraint propagation. If the CLP system detects that the constraints cannot be satisfied with current value assignments, backtracking is performed and most recent assignments are undone. Other CLP solvers may handle their constraints more or less differently than CLP(FD).

## 2.3 Explicit Timing Constraint Checking

In the area of specification and verification of real-time systems, explicit timing constraints have been a research focus during the last years. They have been studied in two main contexts. The first one is formal methods, where theories based on the timing constraints have been developed, independently of the real-time scheduling theory, for expressing and statically checking temporal properties of real-time systems. The other context is real-time languages and systems, where the timing constraints are checked dynamically at run-time.

Major work in the context of formal methods has been done by A. Mok and F. Jahanian et al. Their work started with Real-Time Logic (RTL) [59], a formal language for the specification of real-time systems. RTL formulae are constructed

using addition and subtraction of event occurrence functions (which map to the time domain) with integers, (in)equality predicates, universal and existential quantifiers, and logic connectives. The semantics of RTL is based on the occurrence of events (using the absolute timing, not only ordering) that are based on the execution of a real-time system, such as an event coming from the environment, the start and end of code blocks or the assignment of values to a state variable. Checking whether a set of timing constraints in RTL is satisfied is generally undecidable, although certain classes of RTL formulae are easier to check [57, 106]. Algorithms were developed for checking safety properties [60] and partial event-traces [57].

The research was later directed toward the other context. A distributed on-line monitoring and checking tool was described in [24] and [58] that allows for specifying timing properties in a subset of RTL and checking for their violation. The work describes how to store events coming from the system, how to define timing constraints based on these events, and how to evaluate the constraints in a distributed environment. A graph-based algorithm was developed that evaluates these RTL formulae whenever a new event arrives or when a timeout expires (at earliest possible time).

In the context of dynamic timing constraint checking, a real-time system is equipped with means for detecting and/or preventing timing constraint violations. When a timing constraint violation is detected, the system tries to adapt by, for example, activating stand-by resources, rescheduling of the remaining resources, or executing alternative algorithms for solving the problem under different conditions.

A methodology for specifying and checking timing constraints in a distributed object-oriented environment is presented in [40]. The focus there is on how object

orientation can be utilized to simplify the specification and the checking of timing constraints and how this can be integrated in an existing programming language like C++. The methodology integrates a precompiler that generates instrumentation code and a constraint checker based on RTL-like timing constraints specified for each class, and a distributed instrumentation system. The functional and timing specifications are semantically separated. Notifications by constraint checkers in the form of events are used as the feedback from the target system.

Another approach to dynamic timing constraint checking in distributed objectoriented systems is presented in [93]. Like the previous approach, it separates realtime requirements from individual commands in a program. The real-time requirements are timing constraints described by declarative synchronization code between

the interfaces of objects, expressing common, message-based temporal coordination

patterns. Objects in the system are based on the Actor model [1], and a high-level

programming language construct called RTsynchronizer is defined that specifies a

collection of temporal constraints between actors. The run-time system is able to

dynamically enforce timing constraints, based on the principles of safe progress and

unsafe wait, by e.g. delaying messages. A group of actors may be constrained by

overlapping RTsynchronizers, which may be dynamically added or removed.

In [85], the work has been extended and the actors and synchronizers have been assigned formal operational semantics. The actor semantic interprets actor primitives as two-phase transitions between configurations, which are modeled by ordered pairs  $(\alpha, \mu)$ , where  $\alpha$  represents actor states and  $\mu$  is the set of pending messages. As for the synchronizers, a constraint configuration is similarly defined as an ordered pair

$(\chi, \xi)$ , where  $\chi$  is a multi-set of demands for message invocations corresponding to the constraint  $\xi$ ; transitions are determined by constraint firings, whenever a message invocation matches a pattern in a constraint. A collection of synchronizers is termed an interaction constraint system configuration. Finally, the two operational semantics are composed into one. The overall model is yet to be implemented, and the authors have identified three main tasks: a (so-called constraint-directed) scheduling strategy that fits the synchronizer approach; constraint propagation by the compiler and runtime system; and the distribution of synchronizer entities.

A number of other formal methods for real-time systems treat explicit timing constraints using various time models. For static checking, the CLP approach described in this dissertation could support some of the formal methods on the grounds of common underlying frameworks such as logic and Presburger (linear) arithmetic. An interesting issue is one of the integration of these models with models from real-time scheduling theory within the compiler-based framework.

While the behavior of a real-time system based on static analysis becomes undefined as soon as some of its design assumptions are violated, it is difficult to provide any guarantees for a real-time system equipped only with dynamic timing constraint checking. The approach to dynamic system reconfiguration described in this dissertation attempts to combine static analysis and constraint checking with on-line system performance analysis. Similarly to, for example, common analysis of missed task deadlines, the on-line performance analysis may include dynamic timing constraint checking as described above. Namely, parts of real-time models that allow for static analysis are evaluated in advance by the CLP tool to derive unknown system param-

eters. Run-time system performance degradations and constraint violations are then fed back to the CLP tool, which tries to solve for new, better values of the system parameters by taking into consideration all the static requirements that result in certain guarantees. While a run-time system for dynamic timing constraint checking can prevent some constraint violations and quickly detect unpreventable ones, it itself lacks complete information to steer the target system toward a provably better configuration.

## 2.4 Distributed Instrumentation Systems

Many distributed ISes have been developed over the past decade (e.g., [30, 80, 47]), usually as components of larger software toolkits for analysis of parallel/distributed systems. Only a few have been ported to multiple platforms and made available to broader usage. Several such systems are briefly discussed here. The usage of BRISK in the context of the objectives and features of these distributed ISes is based on certain inferences only, and their developers may have different recommendations.

The Automated Instrumentation and Monitoring System (AIMS) [123] contains xinstrument, a source-code instrumentor for Fortran77 and C, and monitor, a library of time-stamping and trace-collection routines that generates trace files. Tools for off-line processing of trace files include a utility for removing monitoring overhead and maintaining consistency of causally-related events, and a trace file animation and analysis toolkit. If xinstrument were modified to support BRISK, BRISK could replace the rest of the IS.

The Pablo [91] software instrumentation system contains an instrumenting parser with a GUI, and a performance data capture library for generating trace files in Self-Describing Data Format (SDDF) [4]. The instrumentation software supports tracing, interval timing, and counting. The instrumentation library monitors the instrumentation overhead and volume of data, and can automatically adjust the intrusion on the target application by changing the monitoring method. The basic implementation of BRISK could be extended to support SDDF and automatic intrusion adjustment.

Paradyn [79] takes an approach called dynamic instrumentation for dynamically controlling the performance data to be collected. The design of the tool is based on two data abstractions: metric-focus and time-histogram. The dynamic instrumentation environment includes a compiler and code generation, structural analysis of the binary, and an instrumentation manager that allows code to be inserted and removed from the running program. It also incorporates a strategy for describing performance information to users of high-level parallel languages. This is an example of a comprehensive, specialized distributed IS, although ported to multiple platforms, which probably would not benefit fundamentally from BRISK as its kernel.