200<sup>1</sup> 56992220

HE

## This is to certify that the dissertation entitled

## AN EVOLUTIONARY COMPUTATIONAL APPROACH TO CONFIGURING PORTABLE EMBEDDED SYSTEM ARCHITECTURES

presented by

JAMES NORTHERN, III

has been accepted towards fulfillment of the requirements for the

Doctoral

degree in

Electrical and Computer Engineering

Major Professor's Signature

Nov. 25, 2003

**Date**

MSU is an Affirmative Action/Equal Opportunity Institution

# LIBRARY Michigan State University

PLACE IN RETURN BOX to remove this checkout from your record.

TO AVOID FINES return on or before date due.

MAY BE RECALLED with earlier due date if requested.

| DATE DUE                   | DATE DUE | DATE DUE |

|----------------------------|----------|----------|

| 072 () 0 5<br>SEP 0 7 2005 |          |          |

|                            |          |          |

|                            |          |          |

|                            |          |          |

|                            |          |          |

|                            |          |          |

|                            |          |          |

|                            |          |          |

|                            |          |          |

|                            |          |          |

6/01 c:/CIRC/DateDue.p65-p.15

## AN EVOLUTIONARY COMPUTATIONAL APPROACH TO CONFIGURING PORTABLE EMBEDDED SYSTEM ARCHITECTURES

By

James Northern, III

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

**DOCTOR OF PHILOSOPHY**

Department of Electrical and Computer Engineering

2003

#### **ABSTRACT**

### AN EVOLUTIONARY COMPUTATIONAL APPROACH TO CONFIGURING PORTABLE EMBEDDED SYSTEM ARCHITECTURES

By

#### James Northern, III

Portable embedded systems (e.g., medical equipment, cellular phones, pagers, and video game consoles) are being driven by consumer demands to be thermally efficient (produce less heat), perform faster, and have longer battery life. To design such a system, various hardware units (e.g., level one (L1) and level two (L2) caches, functional units, registers) are selected based on a set of specifications for a particular application. Currently, chip architects are using software tools to manually explore different configurations, so that tradeoffs for consumption, performance, and chip size may be understood.

However, when evaluating multiple design parameters simultaneously, the exploration space expands, design time increases, and human errors become a concern. Genetic algorithms, which are effective in rapid global search of large and poorly understood spaces, have been modified for multiple objectives and applied to guide this process to an improved solution.

This dissertation presents a framework for an evolutionary approach to configuring an "ideal" embedded processor based on power consumption and performance. In addition, a database of simulation results that gives a

more comprehensive evaluation of tradeoffs between power and performance, and of the inter-dependence between parameter configurations is presented. Appropriate search techniques to reduce exploration space and decrease time-to-market are also discussed.

Copyright by

James Northern, III

2003

#### **Dedication page**

To God, my loving wife, Teasa, and my first born child, Jonah, who have been with me since the beginning and the inspiration for completing this project. To my Mom, brothers, Brian and Winston, and sister, Chiniqua who constantly reminded me of the family motto "Do your best and let God do the rest...".

#### **ACKNOWLEDGEMENTS**

I wish to express sincere appreciation to Drs. Barbara O'Kelly and Renate Snider for their assistance in the preparation of this manuscript. In addition, special thanks are due to my committee chair, Dr. Michael Shanblatt, whose critical eye, and enlightened mentoring were instrumental and inspiring. I wish to acknowledge my gratitude to Dr. Erik Goodman, whose familiarity with the subject matter was helpful during the early programming phase of this undertaking. I also thank the members of my committee, Drs. Percy Pierre, Bruce Sagan, and Andrew Mason.

#### **TABLE OF CONTENTS**

| LIST OF TA                                    | ABLES                                      | X   |

|-----------------------------------------------|--------------------------------------------|-----|

| LIST OF FI                                    | GURES                                      | xii |

| INTRODUC<br>CHAPTER                           |                                            | 1   |

| Embedded                                      | System Architectures                       | 2   |

| 1.1                                           | Configurable Semiconductor IP Systems      | 4   |

|                                               | 1.1.1 Design Methodology                   | 5   |

|                                               | 1.1.2 Target Architecture                  | 6   |

| 1.2                                           | Problem Statement                          | 8   |

| 1.3                                           | Main Contributions                         | 10  |

| 1.4                                           | Structure of Dissertation                  | 11  |

| CHAPTER<br>Overview o                         | 2<br>f Simulation Tools                    | 13  |

| 2.1 Taxonomy of Architecture Simulation Tools |                                            | 14  |

| 2.2 SimpleScalar Toolset Overview             |                                            | 16  |

|                                               | 2.2.1 Out-of-order Processor Simulator     | 18  |

|                                               | 2.2.2 Simulator Command Options            | 21  |

|                                               | 2.2.3 Processor Performance Estimation     | 25  |

|                                               | 2.2.4 Validation of Out-of-order Simulator | 27  |

| 2.3                                           | Power Analysis Simulator Overview          | 28  |

|                                               | 2.3.1 Power Modeling Methodology           | 31  |

|                                               | 2.3.2 Array Structures                     | 33  |

|                                               | 2.3.3 CAM Structures                       | 34  |

|                                               | 2.3.4 Complex Logic Blocks                 | 35  |

|                                               | 2.3.5 Clocking Network                     | 35  |

|                                               | 2.3.6 Validation of Wattch Simulator       | 36  |

| CHAPTER :             | 3<br>f Search Algorithms                          | 40       |

|-----------------------|---------------------------------------------------|----------|

| 3.1                   | Global Search Methods                             | 41       |

| 3.1                   |                                                   |          |

|                       | 3.1.1 Branch and Bound Method                     | 42<br>43 |

| 3.2                   | Global-Local Search Methods                       |          |

|                       | 3.2.1 Kernighan-Lin and Fiduccia-Matheyses Method | 44       |

|                       | 3.2.2 Ratio Cut Method                            | 46       |

| 3.3                   | Adaptive Search Methods                           | 46       |

|                       | 3.3.1 Simulated Annealing                         | 47       |

|                       | 3.3.2 Evolutionary Computing                      | 51       |

| 3.4                   | Comparison of Search Methods                      | 54       |

| CHAPTER 4 Overview of | 4<br>f Genetic Algorithms                         | 56       |

| 4.1                   | Defining Genetic Algorithm Criteria               | 57       |

|                       | 4.1.1 Solution Representation                     | 57       |

|                       | 4.1.2 Fitness Function                            | 58       |

|                       | 4.1.3 Reproduction Operators                      | 58       |

|                       | 4.1.4 Selection Criteria                          | 61       |

|                       | 4.1.5 Stopping Criteria                           | 64       |

| 4.2                   | Non-standard Genetic Algorithms                   | 64       |

|                       | 4.2.1 Representation of Non-binary Chromosomes    | 65       |

|                       | 4.2.2 Scaling of Fitness Function                 | 66       |

|                       | 4.2.3 Stochastic Universal Sampling               | 67       |

| CHAPTER               |                                                   | 60       |

|                       | Processor Configuration Methodology               | 68       |

| 5.1                   | Defining Genetic Algorithm Criteria               | 71       |

|           | 5.1.1 Single-objective Fitness Function        | 76        |

|-----------|------------------------------------------------|-----------|

|           | 5.1.2 Encoding and Decoding Algorithm          | 76        |

|           | 5.1.3 Reproduction Operators                   | 77        |

|           | 5.1.4 Selection Criteria                       | 79        |

| 5.2       | Evolutionary Search Criteria                   | 79        |

|           | 5.2.1 Population Size                          | 80        |

|           | 5.2.2 Random Initial Populations               | 84        |

|           | 5.2.3 Termination Criteria                     | 87        |

| CHAPTER 6 | S<br>ve Optimization Search                    | 91        |

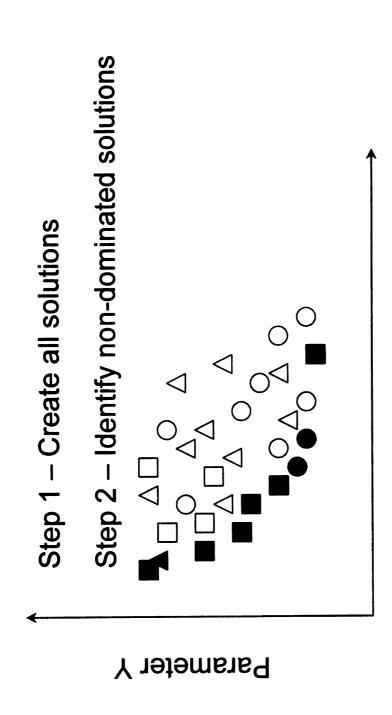

| 6.1       | Pareto-Optimal Front                           | 93        |

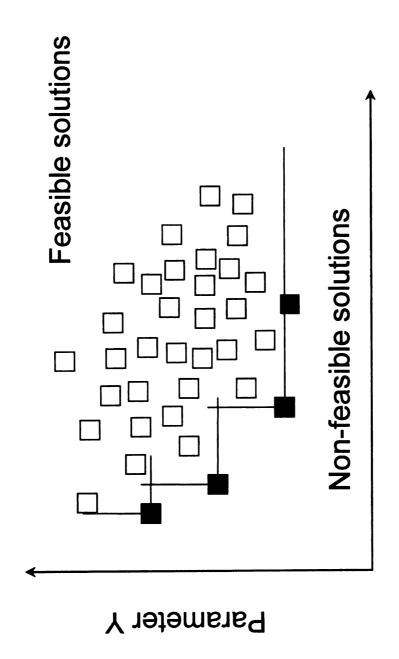

| 6.2       | Pareto-Optimal Front Generation in GALOPPS     | 96        |

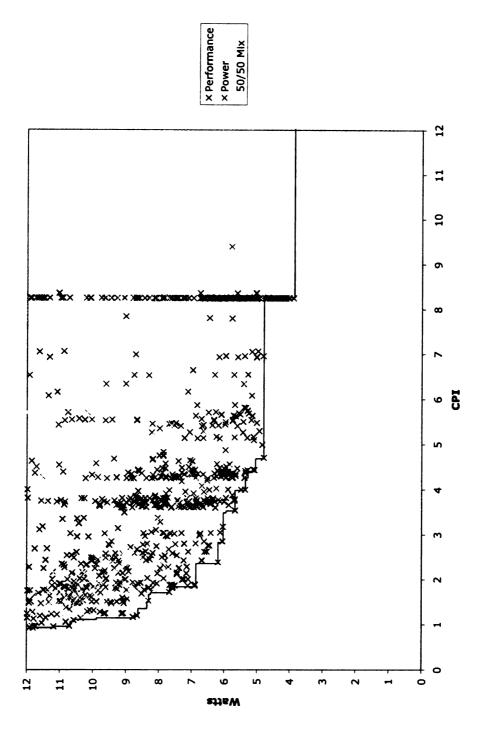

| 6.3       | Power and Performance Trade-offs for Benchmark | Designs98 |

| 6.4       | Test Configurations and Benchmarks             | 101       |

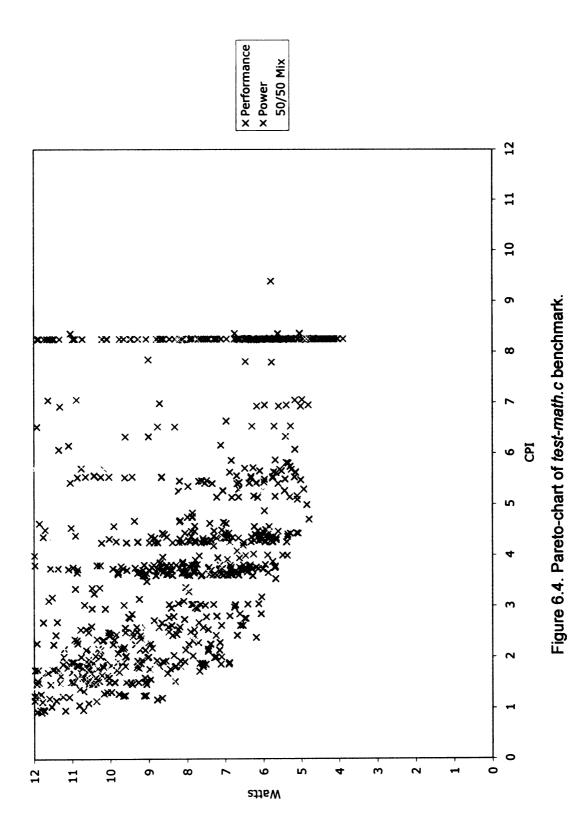

|           | 6.4.1 Math Benchmark                           | 105       |

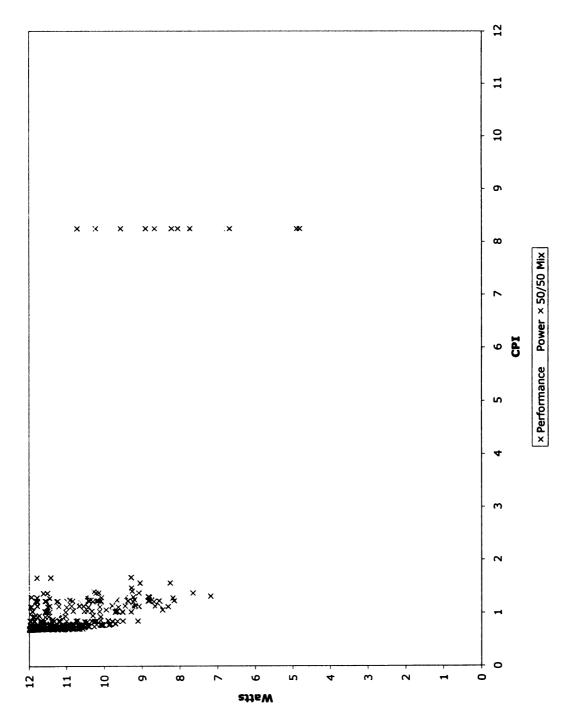

|           | 6.4.2 GNU C Benchmark                          | 109       |

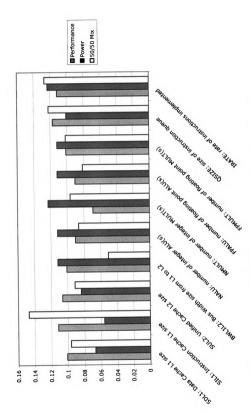

| 6.5       | Sensitivity Analysis of Parameters             | 113       |

| CHAPTER 7 | 7<br>s and Scope for Future Work               | 118       |

| 7.1       | Contributions                                  | 118       |

| 7.2       | System Implementation                          | 119       |

| 7.3       | Discussion                                     | 119       |

| 7.4       | Conclusions                                    | 121       |

|           | Future Work                                    | 122       |

|           |                                                |           |

#### LIST OF TABLES

| 1.1. Fundamental approaches to designing embedded system architectures                  | 3    |

|-----------------------------------------------------------------------------------------|------|

| 1.2. Performance and power specifications for embedded processors                       | 3    |

| 1.3. Basic components of an embedded processor and its key feature                      | es 7 |

| 2.1. Command-line options for the processor core                                        | 21   |

| 2.2. Command-line options for memory hierarchy                                          | 22   |

| 2.3. Cache configuration fields                                                         | 23   |

| 2.4. Default cache configuration                                                        | 23   |

| 2.5. Specifying the branch predictor                                                    | 24   |

| 2.6. Predictor-specific options                                                         | 24   |

| 2.7. Validation of performance measures via benchmark testing [23]                      | 27   |

| 2.8. Capacitance formulas used in power analysis methodology [32]                       | 32   |

| 2.9. Common processor hardware structures and the model used by Wattch                  | 36   |

| 2.10. Configuration for base and industry models                                        | 37   |

| 2.11. Comparison between modeled and reported power breakdowns for the Pentium Pro [30] | 38   |

| 2.12. Comparison between modeled and reported power breakdowns for the Alpha 21264 [30] | 38   |

| 5.1. Characteristic values for each parameter                                           | 74   |

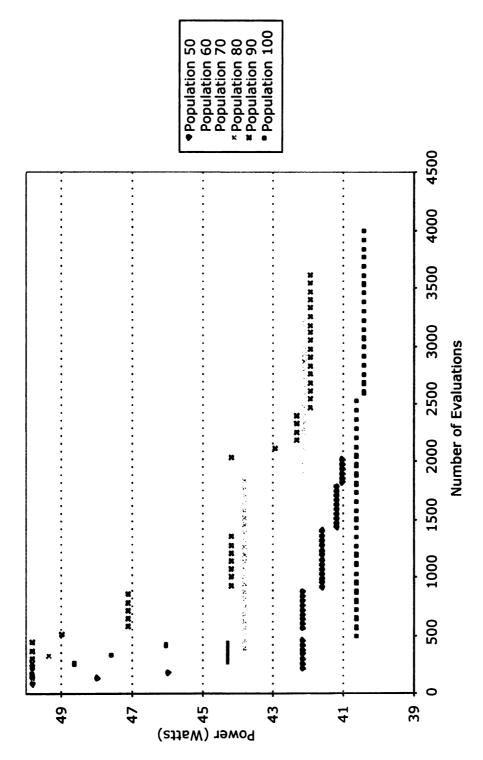

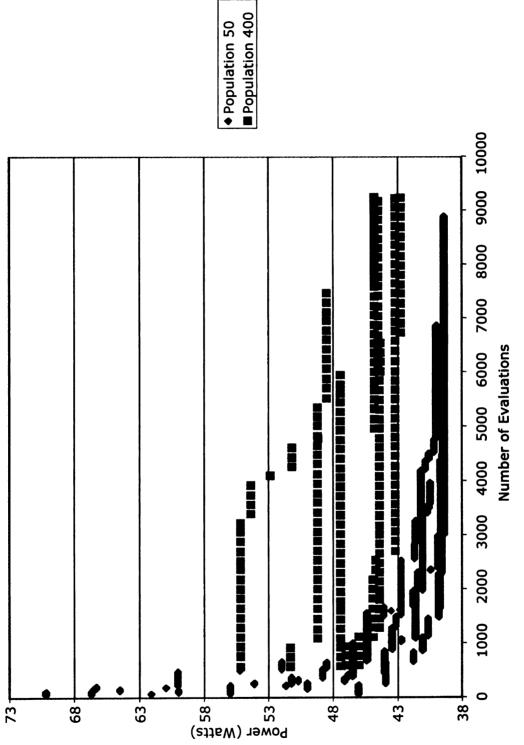

| 5.2. Analysis of population experiment                                                  | 82   |

| 5.3. "Best" configuration of GA run for each population size                            | 83   |

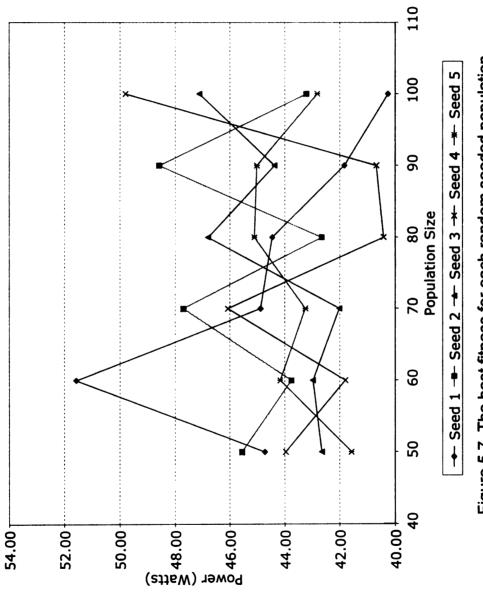

| 5.4. Fitness of each random seeded population                                           | 86   |

| 5.5. Population size of 50 for 400 generations                                          | 89   |

| 5.6. Population size of 400 for 50 generations                                          | 90   |

| 6.1. Test configurations for power-performance tradeoffs | 102 |

|----------------------------------------------------------|-----|

| 6.2. Comparison results from Math Benchmark              | 104 |

| 6.3. Comparison results from GNU C Compiler Benchmark    | 104 |

| 6.4. GA results for CPI performance optimization         | 106 |

| 6.5. GA results for power consumption optimization       | 107 |

| 6.6. GA results for CPI performance optimization         | 110 |

| 6.7. GA results for power consumption optimization       | 111 |

#### **LIST OF FIGURES**

| 1.1. | System design flow for an embedded system implementation                                         | 6  |

|------|--------------------------------------------------------------------------------------------------|----|

| 1.2. | Target architecture model for programmable superscalar RISC/VLIW processor with memory hierarchy | 7  |

| 2.1. | High-level view of architectural simulator                                                       | 13 |

| 2.2. | Taxonomy of architecture simulators                                                              | 15 |

| 2.3. | Graphical view of SimpleScalar                                                                   | 17 |

| 2.4. | Sim-outorder five-stage pipeline                                                                 | 19 |

| 2.5. | Three scenarios for using architecture-level power analysis [30]                                 | 30 |

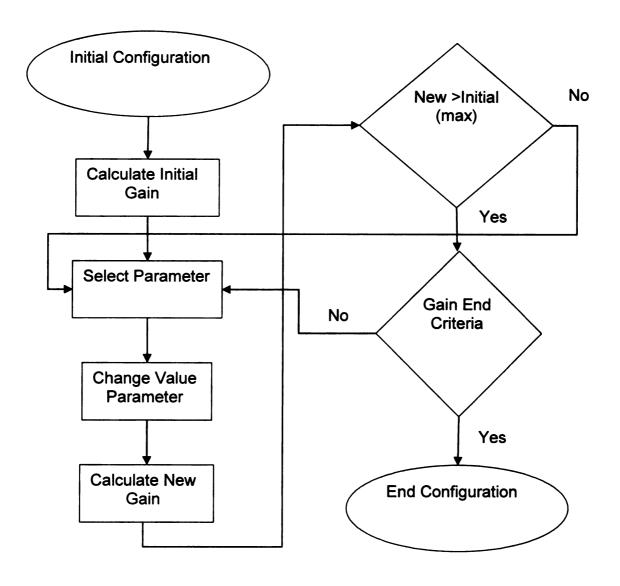

| 3.1. | Flowchart for KL-FM partitioning algorithm                                                       | 45 |

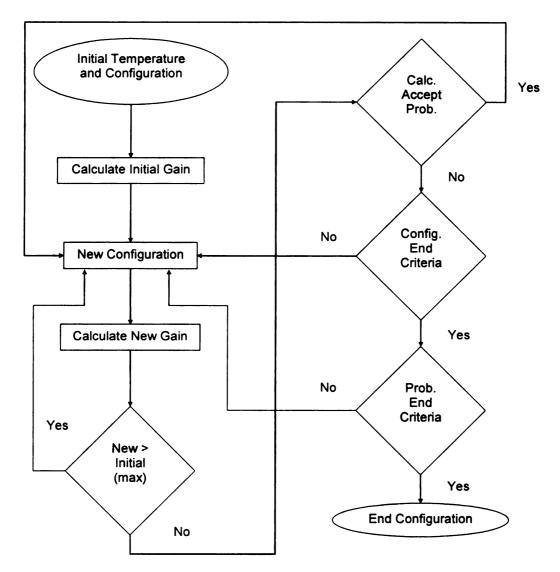

| 3.2. | Flowchart of the simulated annealing algorithm                                                   | 49 |

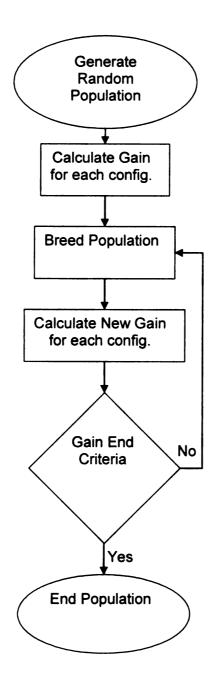

| 3.3. | Flowchart of a simple genetic algorithm                                                          | 52 |

| 4.1. | Example of a mutation operation                                                                  | 59 |

| 4.2. | Example of a crossover operation                                                                 | 60 |

| 4.3. | Example of two-point crossover                                                                   | 60 |

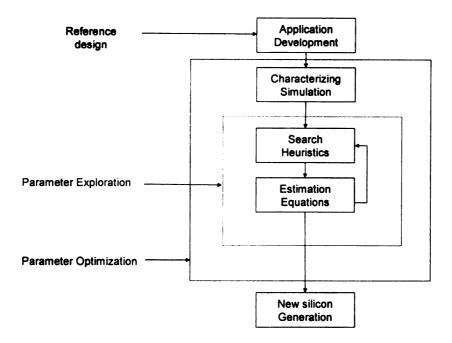

| 5.1. | Flowchart of parameterized system design                                                         | 70 |

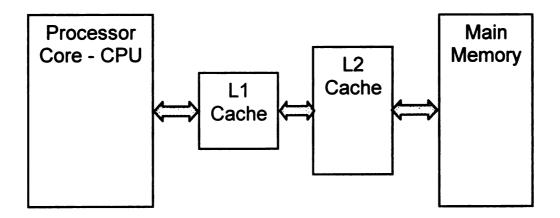

| 5.2. | Target architecture for embedded system design                                                   | 72 |

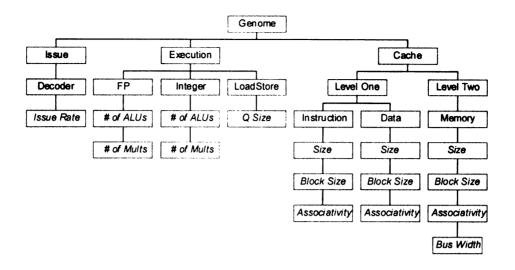

| 5.3. | Genome structure for GA                                                                          | 73 |

| 5.4. | Non-specified parameter values during GA search                                                  | 75 |

| 5.5. | Translation of chromosome to integer array                                                       | 77 |

| 5.6. | Experimentation results from varied population sizes                                             | 81 |

| 5.7. | Best fitness for each random seeded population                                                   | 85 |

| 5.8. | Fitness evaluations for extended run of generations                                              | 88 |

| 6.1. | Pareto-optimal front for a two-dimensional problem                                               | 94 |

| 6.2. | Identification of Pareto-points in GALOPPS                                                       | 97 |

| 6.3. Power-Performance tradeoff using Pareto-chart                        | 100 |

|---------------------------------------------------------------------------|-----|

| 6.4. Pareto-chart of <i>test-math.c</i> benchmark                         | 108 |

| 6.5. Pareto-chart for GNU C Compiler benchmark                            | 112 |

| 6.6. Parameter sensitivity of GA for performance, power, and weighted mix | 116 |

#### INTRODUCTION

Embedded systems are application-specific (single task) computer systems built into larger devices. In today's world, embedded systems are everywhere – homes, offices, cars, factories, hospitals, airplanes, and consumer electronics. An embedded system differs from a general-purpose computer in that it has one fixed application and cannot be changed by the outside environment. However, an embedded system is reactive to internal changes. These types of systems often run in real-time and are designed to meet requirements of low cost and low power consumption, and are usually small in size. In addition, consumer demands have driven embedded systems to be thermally efficient, perform faster, and have longer battery life. Challenging design issues arise, such as multi-objective design goals, configurability (customization), and time-to-market.

This dissertation presents a framework for an evolutionary computational approach to configuring an "ideal" embedded processor based on power consumption and performance. In addition, a database of simulation results that gives a more comprehensive evaluation of tradeoffs between power and performance, and of inter-dependence between parameter configurations (*i.e.*, L1 to L2 cache size, memory bandwidth, instruction window size, datapath width) is presented.

#### **CHAPTER 1**

#### **Embedded System Architectures**

New portable embedded systems require a high level of performance to meet their hard and/or soft real-time deadlines, where hard real-time is an absolute deterministic response to an event. Examples of embedded systems in the consumer market are digital cameras, video cameras, video game consoles, and medical equipment (e.g., glucose monitor, heart rate monitor). As the complexity and importance of these applications increase, the type of architectures that support them will lead to higher power consumption than traditional portable devices. Thus, limited power-supply capability of current battery technology is forcing designers to explore a combination of high-performance and low-power architectures.

The solution for attaining these new goals is to customize the processor for a particular application. Designers are evaluating three fundamental approaches: RISC ICs, hard cores, and configurable semiconductor intellectual property (IP) cores. Table 1.1 summarizes the three fundamental approaches.

Table 1.1. Fundamental approaches to designing embedded system architectures.

| Approach                       | Description                                                                                                    |

|--------------------------------|----------------------------------------------------------------------------------------------------------------|

| RISC ICs                       | Off-the-shelf, stand alone parts that are selected from component data books.                                  |

| Hard cores                     | Pre-defined macro layout blocks that can be integrated into application specific ICs.                          |

| Configurable semiconductor IPs | Fully programmable processors that can be customized and build by multiple contract semiconductor fabricators. |

The advantages of using RISC ICs are their ease of purchase (commodity) and tailored appeal to a specific kind of market. Examples of RISC ICs include Intel's Pentium XScale, IBM's PowerPC, MIPS VR5000, Philips TriMedia TM-1300. Disadvantages of these processors are low integration, poor system performance, and high power requirement. An example of performance and power for selected RISC ICs is shown in Table 1.2.

Table 1.2. Performance and power specifications for RISC ICs.

| RISC ICs            | Performance | Power |

|---------------------|-------------|-------|

| Intel's XScale      | 1 GHz       | 1.5 W |

| IBM's PowerPC 750CX | 400 MHz     | 4.0 W |

| MIPS VR5000         | 250 MHz     | 5.0 W |

| TriMedia's TM1300   | 166 MHz     | 2.7 W |

Hard cores are more flexible than RISC ICs because they are predefined macro layout blocks that can be integrated into embedded processors. They can be provided and serviced by any application-specific design house. Disadvantages of hard cores include that they are process-specific, that their non-configurable captive IP demands premium price in the market, and that they require additional hardware when integrated into systems-on-a-chip (SoC).

Configurable semiconductor IP cores are more flexible than hard cores because they are not process dependent. They provide foundry-independence for multiple manufacturing sources. The disadvantages of configurable semiconductor IPs are their availability of processor options, configurability of hardware and instruction set architecture (ISA), optimization of software compiler, and integration in an SoC as lack of architectural models of all execution units and peripherals makes it difficult to model paths through the system. In the present work, the configurability of hardware, optimization for power and performance, and ease-of-design (i.e., low design complexity for reduced design time and fast time-to-market) for a configurable semiconductor IP are explored.

#### 1.1 Configurable Semiconductor IP Systems

Configurable semiconductor IP systems are fully programmable processors that can be customized and constructed by multiple contract semiconductor fabricators. These embedded processors are becoming an attractive alternative to RISC ICs and hard cores for the following main reasons: design time and time-to-market are much shorter than that for hardwired custom implementations; time can be reduced if the processor is simulated and explored in software; and the ability to change part of the

functionality of any system is crucial in determining the design time. The cost of design and implementation of a programmable processor is lower compared to hardwired implementation. The cost of silicon processing increases in foundries with every new generation of technology [1]. Enabling technologies for programmable processors are becoming mature and competitive. Compilers and design tools are improving at an increasingly rapid rate [2,3] and more attention is being given to improving these tools [4,5]. Programmable processors are now able to provide power versus performance tradeoffs [6,7,8,9,10].

#### 1.1.1 Design Methodology

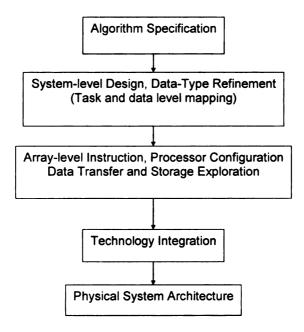

Many design flows and methods have been proposed in the past, where different steps in design methodology and their consequences on design decisions have been studied. Figure 1.1 shows the different steps involved in the design of a configurable embedded IP system [11]. The five main stages (abstraction levels) in this design methodology are algorithm specification, system-level design, array-level instruction, technology integration, and physical system architecture design [12]. The algorithm specification level is where the type of ISA is chosen. The system-level design stage maps the actual task (C program) to the ISA through a GNU *gcc* compiler at the array-level instruction stage, the processor configuration is explored at the technology integration stage, and the circuit design takes place. The physical architecture system level determines the final layout of the embedded system. The present work addresses the array-level instruction stage where the processor

configuration is explored and optimized. In the methodology to be described a genetic algorithm is successfully applied to accomplish this goal.

Figure 1.1. System design flow for an embedded system implementation.

#### 1.1.2 Target Architecture

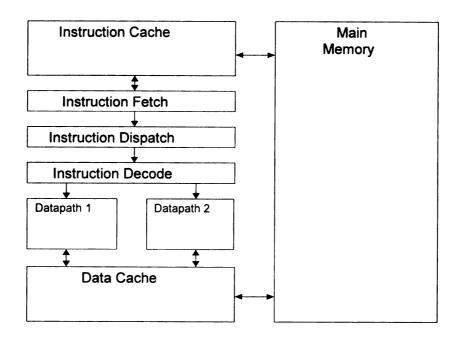

The target architecture consists of basic components in configurable semiconductor IPs. Figure 1.2 shows as an example a general abstraction of the current state-of-the-art multi-media embedded processor [13,14]. The key components typically observed in these architectures are described in Table 1.3.

Figure 1.2. Target architecture model for programmable super-scalar RISC/VLIW processor with memory hierarchy.

Table 1.3. Basic components of an embedded processor and its key features.

| Component               | Description                                                                                                                                                       |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functional units (FU)   | Multiple units for integer and floating-point operations using arithmetic logic unit and multiplier.                                                              |

| Instruction fetch queue | Size and issue width constitute a superscalar [15] or a very long instruction word (VLIW) [13,14] processor or a multi-threaded multiprocessor type of core [16]. |

| Instruction window      | Register update unit for the integer and floating-point instructions. Uses a reorder buffer to automatically rename registers.                                    |

| Cache                   | One or more levels of cache memories are present, at least one of which resides on chip.                                                                          |

| Centralized bus         | A centralized bus is selected with one or two data buses, depending on data-dominated multimedia applications [12].                                               |

The architecture of embedded programmable processors has features that are parameterizable. Examples include the functional unit, which can vary in datapath size and bitwidths, cache size and organization; the memory unit, which may vary in the number and size of register files; and the interconnections within the processor data paths [17]. The framework for a configurable processor is a compiler coupled to a machine simulator, with parameterizable features tunable by the designer. Interdependence between two parameters has been investigated [18], however, exploration and optimization of all of these parameters have not been addressed.

#### 1.2 Problem Statement

Many embedded processor studies focus on issues related to cache size and organization, and their relationship to energy and power consumption. Although points of diminishing returns exist, decreasing the size generally decreases power consumption. However, the focus of research has shifted to the inter-relationships of other major parameters and their tradeoffs when optimizing for multiple objectives, namely power and performance.

A common difficulty when optimizing for multiple objectives is the conflict between objectives when maximizing or minimizing over a given set of solutions. For example, decreasing cache size reduces power consumption, but also decreases performance. If the cache is too small, cache misses may mask the effects of other processor parameters, such as branch mispredictions, because of parameter interdependency.

Conversely, increasing the number of functional units may increase performance, but also will increase power consumption. While searching the design space for an "ideal" embedded processor configuration, optimizing for two or more criteria can lead to "non-ideal" solutions. Hence, for portable, high-performance embedded implementations, much more advanced techniques, which are efficient in ease-of-design and multi-objective decision-making, need to be explored.

In the context of embedded architecture and organization, the following goals are outlined:

- Finely tuned performance to meet application requirements:

Some embedded designs require high performance for multimedia and communication algorithm processing.

- 2. Small size: Highly integrated circuits need to be optimized for small size and low system cost.

- 3. Energy and power efficiency: The embedded processor must operate at a very low MIPS per watt rating to meet requirements for portable applications. For example, a processor's power budget may be a maximum of 1W, but it must still be able to drive the processing for an intense algorithm like speech recognition or data compression.

- 4. Ease-of-design: Low design complexity will result in reduced design time and fast time-to-market. Design complexity must be kept to a minimum to speed the time-to-market for a system level product. However, when evaluating multiple design parameters simultaneously, the exploration space expands (e.g., four options per parameter with 16 parameters to a set

solution, give 4,294,967,296 possible solutions), thus increasing design time.

#### 1.3 Main Contributions

The main contributions of this work are the following:

- 1. A methodology for exploring embedded system architectures [Chapter 5]: Issues related to processor architectures and organization, are addressed using an evolutionary approach for configurable processors. An application of a simple genetic algorithm in the exploration of a configurable processor design is used in the process. With this methodology we are able to improve power and performance (*i.e.*, find solution better than original) of embedded processors for practical applications given a large set of parameters [19].

- 2. A sensitivity analysis for embedded system optimization [Chapter 5]: Based on experimentation with practical applications, we have determined a heuristic for training the genetic algorithm to better represent the configuration problem. The less sensitive parameter value (size, number, etc.) is replaced with their best value from a previous GA run, and used as a constant in future evaluations [19]. Therefore, this step reduces the configured design space and refines the exploration criteria.

3. Multi-objective analysis for configuring embedded system architectures [Chapter 6]: An efficient multi-objective genetic algorithm [20] that generates a set of alternative solutions and indicates the best power/performance tradeoff is developed. These alternative solutions are expressed as non-dominated points (*i.e.*, a solution is dominant over another only if it has superior performance in all criteria).

#### 1.4 Structure of Dissertation

The remainder of this dissertation is organized as follows. First, Chapter 2 provides the necessary background material related to this work. An overview of superscalar out-of-order processor simulators is presented. Emphasis is placed on the estimation of power consumption and performance rather than on out-of-order procedures. Also, a methodology for exploring embedded system architectures is presented.

Chapter 3 presents the taxonomy of different search and optimization algorithms. Examples of each method are given and trade-offs between the techniques are reviewed. Based on our research, genetic algorithms (GAs) offer greater flexibility for a larger search space. An explanation of how GAs are used in the configuration methodology is also presented.

Chapter 4 presents the concepts of the GA search and optimization technique. Standard GA concepts such as solution (chromosome) representation, fitness function, reproduction operators, selection criteria, and stopping criteria are discussed. Other techniques for expanding the

use of GAs to non-standard problems are also presented.

Chapter 5 presents a methodology for improving power consumption of a computer simulated configurable processor. The functional parameters and the estimation of power consumption are incorporated into a genetic framework. This chapter addresses the use of genetic algorithms and the criteria needed to establish a good search (*i.e.*, population size, random populations, and stopping criteria).

Chapter 6 describes the techniques developed in this work, such as incorporating the parameters into a genetic framework, the sensitivity analysis, and multi-objective decision-making. The encoding and decoding of the parameters are very important in performing an efficient search. The sensitivity analysis involves a technique for training the genetic algorithm to better represent the design search space. A sensitivity analysis of each parameter is performed and the less sensitive values for parameters are substituted for a constant value to reduce exploration time for validation runs. The problems faced with multi-objective decision-making, and the corresponding solutions for power and performance are also discussed. A method is presented for providing a Pareto-optimal front for optimal solutions of two objectives. Experimental results as well as issues related to automation of this technique are presented.

Finally, Chapter 7 presents the main contributions of this thesis and provides directions for future work.

#### **CHAPTER 2**

#### **Overview of Simulation Tools**

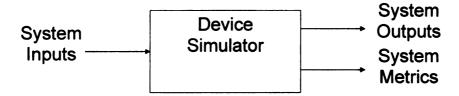

Computer-aided design simulators are used to help in the design of new electronic circuits and devices such as systems-on-a-chip, embedded systems, intellectual property cores. These types of circuits are designed from specifications given at very high levels of abstraction in order to shorten the time-to-market of new products. However, modern processors have become incredibly complex and increasingly hard to evaluate. Architectural simulators have become the solution for evaluating these processors early in the design cycle. An architectural simulator is a tool that reproduces the behavior of a computing device, as illustrated in Figure 2.1.

Figure 2.1. High-level view of architectural simulator.

In addition to simulating processors, architectural simulators have advanced to evaluation of multiple designs. The evaluation focuses on the discovery of performance tradeoffs and "ideal" solutions (*i.e.*, better operating configurations within the limited time frame). These tools have been enhanced by the use of search techniques (*e.g.*, simulated

annealing, integer linear programming, and genetic algorithms) to aid designers in finding optimal solutions. The work discussed in this chapter provides the background for the simulation and search of optimal designs of portable embedded processors.

#### 2.1 Taxonomy of Simulation Tools

Simulation tools have become an attractive solution to chip architects because more development can be done with software, which allows for greater flexibility and faster leverage in the design cycle. The following benefits are derived from software-based development:

- 1. Permits more design space exploration.

- 2. Facilitates validation before commitment to hardware.

- 3. Level of abstraction (e.g., RTL, compiler, assembly language, VHDL, etc.) can be suited for a specific design task.

- 4. System instrumentation can be increased and/or improved.

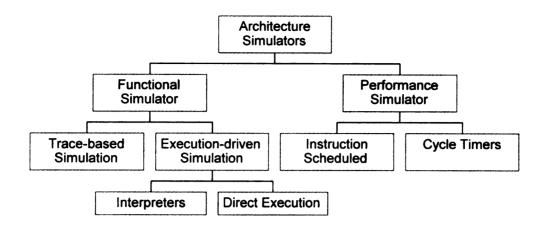

To better understand simulation tools and how they work, an example of the taxonomy is shown in Figure 2.2.

Figure 2.2. Taxonomy of architecture simulators.

The functional simulator implements the instruction set architecture and is concerned with the correctness of the simulation, which is what programmers actually see. It simulates the direct execution of the task. The performance (timing) simulator implements the micro-architecture and models the system internals. This simulator is more concerned with access time and the functions that are not apparent to the programmer such as cache hits and misses.

A functional simulator may be implemented in either an execution- or trace-based manner. Trace-driven simulation reads a "trace" of instructions saved from the previous execution whereas execution-based simulation "runs" the program and generates a stream dynamically. Execution-driven simulation has many advantages, but is more difficult to implement. Instead of implementing direct execution, where an instrumented program runs on a host, an interpreter can be built to accurately simulate execution down to the level of mis-speculated paths.

Performance simulators are based on instruction schedulers or cycle timers. Constraint-based instruction schedulers schedule instructions based on resource availability. Instructions are processed one at a time, in order. They are usually simpler to implement and/or modify, and are generally less detailed. During each cycle, cycle-timer simulators track the micro-architecture state and many instructions in various stages at any time. The simulator state is the same as the micro-architecture state. This type of simulator is good for detailed micro-architecture simulation.

In this thesis, the emphasis will be placed on the SimpleScalar [21] toolset because it is currently a widely accepted tool among researchers. The SimpleScalar toolset uses a combined functional and performance simulator, where instructions are execution-driven and the simulator is synchronized with the micro-architecture state.

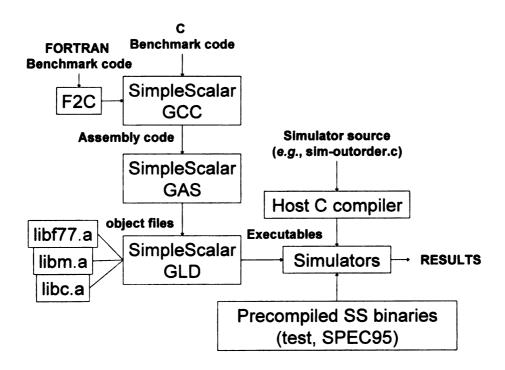

#### 2.2 SimpleScalar Toolset Overview

SimpleScalar [21] provides a toolbox of simulation components (a branch predictor module, a cache module, and a statistics-gathering module) as well as several simulators built from these components. Each simulator interprets executables compiled by *gcc* version 2.6.3 for a virtual instruction set (PISA) that most closely resembles MIPS IV [22]. A graphical overview of the toolset is shown in Figure 2.3. Benchmarks written in FORTRAN are converted to C using Bell Lab's *f2c* converter. Both benchmarks written in C and those converted from FORTRAN are compiled using the SimpleScalar version of *gcc*, which generates SimpleScalar assembly code. The SimpleScalar assembler and loader,

along with the necessary libraries, produce SimpleScalar executables that can then be fed directly into one of the provided simulators. SimpleScalar optimizes performance and flexibility by reducing design time and maximizing design exploration. In addition, it provides portability for big or little endian machines and varied detailed for different levels of simulations.

Figure 2.3. Graphical view of SimpleScalar.

#### 2.2.1 Out-of-order Processor Simulator

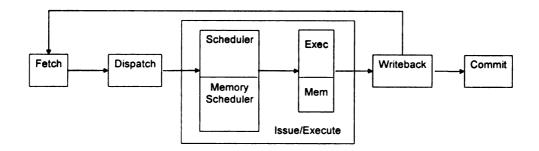

The most complicated and detailed simulator in the SimpleScalar toolset is *sim-outorder* which supports out-of-order issue and execution instructions. The pipeline for *sim-outorder* is handled in five stages: fetch, dispatch, issue, wirteback, and commit.

Sim-outorder simulates a unified active list, issue queue, and rename register file (register update unit). The register update unit (RUU) handles register synchronization and communication. Entries are allocated at dispatch and deallocated at commit. Using an RUU eliminates artifacts arising from interactions between active list size and issue queue size, and reduces the number of architecture variables to be examined.

The processor's memory system employs a load store queue (LSQ). The LSQ handles memory synchronization and communication. Stored values are placed in the queue if the store is speculative. Loads are dispatched to the memory system only when addresses are known not to conflict. Loads may be satisfied either by the memory system or by an earlier stored value residing in the queue, if their addresses match. Speculative loads may generate cache misses, but a speculative translation look-aside buffer (TLB) misses may stall the pipeline until the branch condition is known.

The five-stage pipeline is illustrated in Figure 2.4. The pipeline is actually traversed backwards, so that inter-stage latch synchronization can be handled correctly with only one pass through each stage.

Figure 2.4. Sim-outorder five-stage pipeline.

The fetch stage models the machine fetch bandwidth and takes the following inputs: program counter, predictor state, and misprediction from branch execution units. During each clock cycle, this stage fetches the instructions from one instruction cache line and block until I-cache or I-TLB are resolved. After fetching the instructions, it places them in the dispatch queue (IFQ), and probes the line predictor to obtain the correct cache line to access in the next cycle.

The dispatch stage models the processor decode, rename, RUU/LSQ allocation bandwith and architected machine state for execution. During each clock cycle, instructions are decoded and executed, where early detection of branch mispredictions is permitted. If a branch misprediction occurs, stat copy-on-write of architected state to speculative buffers is done. Finally, instructions are entered into the RUU and LSQ, rename table, and machine state.

The issue stage is split into two sub-stages: scheduler and execute sub-stage. The scheduler unit models instruction wake-up, selection, and issue. It separates schedule, track register and memory dependencies. The scheduler uses inputs from the RUU and LSQ. During each cycle, the

scheduler locates instructions with all register inputs ready and loads with all memory inputs ready. The issue function then updates the RUU and LSQ and the functional unit state. The execute sub-stage models the functional units and data cache. It accepts as inputs the instructions ready to execute, as issued by the scheduler, and the states of the functional unit and data cache. Each cycle, the execute stage takes the ready instructions, which are supported by issue bandwidth, finds a free functional unit and access port, and reserves the unit for entire issue latency. Finally, the writeback events are scheduled using the operation latency of the functional unit. The execute sub-stage updates the functional unit, data cache state, and writeback events.

The writeback stage models writeback bandwidth and the wake-up ready instructions, detects mispredictions, and initiates misprediction recovery. The function uses completed instructions as indicated by the event queue and RUU/LSQ state for wake-up walks. The event queue is updated during each cycle. When it finds a completed instruction, it walks the dependence chain of the instruction outputs to mark instructions that are dependent on the completed instruction. If a dependent instruction is waiting for that completion, the routine marks the instruction as ready. The writeback stage also detects branch mispredictions. When a misprediction occurs, it rolls the state back to the checkpoint, discarding the erroneously issued instructions.

The commit stage handles the instructions from the writeback stage that are ready to commit. This function does in-order committing of instructions, updating of the data caches (or memory) with stored values, and TLB miss handling. The routine retires instructions at the head of the RUU that are ready to commit until the head instruction is the one that is

not ready. When an instruction is committed, its result is placed in a register file and the RUU/LSQ resources devoted to that instruction are reclaimed.

# 2.2.2 Simulator Command Options

Sim-outorder is a detailed superscalar simulator that runs slower than most of the other simulators in SimpleScalar. Sim-outorder provides the user with a host of command-line options for the processor core (Table 2.1), memory hierarchy (Table 2.2), and branch predictor (Table 2.5). Subsequent tables for the memory and branch configuration are shown in Tables 2.3 and 2.6.

Table 2.1. Command-line options for the processor core.

| Line Option                    | Description                                                                                                                                                             |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -fetch:ifqsize <size></size>   | Sets the fetch width to be <size>. Must be a power of 2, and the default is 4.</size>                                                                                   |

| -fetch:speed <ratio></ratio>   | Sets the ratio of the front-end speed relative to<br>the execution core (allowing <ratio> times as<br/>many instructions to be fetch as decoded per<br/>cycle).</ratio> |

| -fetch:mplat <cycles></cycles> | Sets the branch misprediction latency. The default is 3.                                                                                                                |

| -decode:width <insts></insts>  | Sets the decode width to be <insts>, which must be a power of two. The default is 4.</insts>                                                                            |

| -issue:width <insts></insts>   | Sets the maximum issue width in a given cycle. Must be a power of two. The default is 4.                                                                                |

| -issue:inorder                 | Forces the simulator to use in-order issue. The default is False.                                                                                                       |

| -issue:wrongpath               | Allows instructions to issue after a misspeculation. The default is True.                                                                                               |

| -ruu:size <insts></insts>      | Sets the capacity of the RUU (in instructions). The default is 16.                                                                                                      |

Table 2.1. Command-line option for the processor core (cont.).

| -lsq:size <insts></insts> | Sets the capacity of the load/store queue (in instructions). The default is 8. |

|---------------------------|--------------------------------------------------------------------------------|

| -res:ialu <num></num>     | Specifies number of integer ALUs. The default is 4.                            |

| -res:imult <num></num>    | Specifies number of integer multipliers/dividers. The default is 1.            |

| -res:memports <num></num> | Specifies number of L1 cache ports. The default is 2.                          |

| -res:fpalu <num></num>    | Specifies number of floating point ALUs. The default is 4.                     |

| -res:fpmult <num></num>   | Specifies number of floating point multipliers/dividers. The default is 1.     |

Table 2.2. Command-line option for memory hierarchy.

| Line Option                  | Description                                        |

|------------------------------|----------------------------------------------------|

| -cache:dl1 <config></config> | Configures a level-one data cache.                 |

| -cache:dl2 <config></config> | Configures a level-two data cache.                 |

| -cache:il1 <config></config> | Configures a level-one instruction cache.          |

| -cache:il2 <config></config> | Configures a level-two instruction cache.          |

| -tlb:dtllb <config></config> | Configures the data TLB.                           |

| -tlb:itlb <config></config>  | Configures the instruction TLB.                    |

| -flush <boolean></boolean>   | Flush all caches on a system call;                 |

|                              | ( <boolean>=0 1 true TRUE false FALSE).</boolean>  |

| -icompress                   | Remap SimpleScalar's 64-bit instructions to a      |

|                              | 32-bit equivalent in the simulation (i.e., model a |

|                              | machine with 4-word instructions).                 |

| -pcstat <stat></stat>        | Generate a text-based profile.                     |

| -cache:dl1lat                | Specify the hit latency of the L1 data cache. The  |

| <cycles></cycles>            | default is 1 cycle.                                |

| -cache:dl2lat                | Specify the hit latency of the L2 data cache. The  |

| <cycles></cycles>            | default is 6 cycles.                               |

| -cache:il1lat                | Specify the hit latency of the L1 instruction      |

| <cycles></cycles>            | cache. The default is 1 cycle.                     |

| -cache:il2lat                | Specify the hit latency of the L2 instruction      |

| <cycles></cycles>            | cache. The default is 6 cycles.                    |

| -mem:lat <1 <sup>st</sup> >  | Specify the main memory access latency (first,     |

| <next></next>                | rest). The defaults are 18 cycles and 2 cycles.    |

| -mem:width < bytes>          | Specify width of memory bus in bytes. The          |

|                              | default is 8 bytes.                                |

| -tlb:lat <cycles></cycles>   | Specify latency (in cycles) to service a TLB miss. |

|                              | The default is 30 cycles.                          |

The cache configuration involves the name, number of sets, block size, associativity, and replacement policy. The meaning for each of these fields is listed in Table 2.3. The cache configuration (<confg>) is formatted as follows:

<name>:<nsets>:<bsize>:<assoc>:<repl>.

Table 2.3. Cache configuration fields.

| Field Name      | Description                                                       |

|-----------------|-------------------------------------------------------------------|

| <name></name>   | Cache name, must be unique                                        |

| <nsets></nsets> | Number of sets in the cache                                       |

| <bsize></bsize> | Block size (for TLBs, use the page size)                          |

| <assoc></assoc> | Associativity of the cache (power of two)                         |

| <repl></repl>   | Replacement policy (I f r), where I=LRU, f=FIFO, r=random replac. |

The cache size is the product of <nsets>, <bsize>, and <assoc>. To have a unified level two cache in the memory hierarchy, the instruction cache has to be pointed to the name of the data cache in the corresponding level. The defaults used are listed in Table 2.4.

Table 2.4. Default cache configuration.

| Name                 | Configuration    | Size        |

|----------------------|------------------|-------------|

| L1 data cache        | dl1:256:32:1:l   | 8 KB        |

| L1 instruction cache | il1:256:32:1:l   | 8 KB        |

| L2 unified cache     | ul2:1024:64:4:l  | 256 KB      |

| Instruction TLB      | Itlb:16:4096:4:I | 64 entries  |

| Data TLB             | dtlb:32:4096:4:I | 128 entries |

Choosing the following flag with one of the six subsequent arguments specifies the type of branch prediction (*i.e.*, -bpred <type>). The default mode is a bimodal predictor with 2048 entries.

Table 2.5. Specifying the branch predictor.

| Туре     | Description                                                                |

|----------|----------------------------------------------------------------------------|

| nottaken | Always predict not taken.                                                  |

| Taken    | Always predict taken.                                                      |

| Perfect  | Perfect predictor.                                                         |

| Bimod    | Bimodal predictor, using a branch target buffer (BTB) with 2-bit counters. |

| 2lev     | 2-level adaptive predictor.                                                |

| comb     | Combined predictor (bimodal and 2-level adaptive).                         |

Table 2.6. Predictor-specific command-line options.

| Line Option                              | Description                                                                                                                                                                  |  |  |  |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| -bred:bimod <size></size>                | Set the bimodal predictor table size to be <size> entries.</size>                                                                                                            |  |  |  |

| -bpred:2lev <config></config>            | Specify the 2-level adaptive predictor.                                                                                                                                      |  |  |  |

| -bpred:comb <size></size>                | Set the meta-table size of the combined predictor at <size> entries. The default is 1024.</size>                                                                             |  |  |  |

| -bpred:ras <size></size>                 | Set the return stack size to <size>. The default is 8.</size>                                                                                                                |  |  |  |

| -bpred:btb <sets> <assoc></assoc></sets> | Configure the BTB to have <sets> sets and an associativity of <assoc>. The defaults are 512 sets and an associativity of 4.</assoc></sets>                                   |  |  |  |

| -bpred:spec_update <stage></stage>       | Allows speculative updates of the branch predictor in the decode or writeback stages ( <stage>=[ID WB]). The default is non-speculative updates in the commit stage.</stage> |  |  |  |

The SimpleScalar out-of-order issue simulator offers flexibility to create and test different configurations. The values a user can specify and the tests for performance tradeoffs are infinite. Simulation time of *sim-outorder* is dependent upon a particular task or application (*e.g.*, less than 1 sec, without application). In the following section, processor performance and comparison techniques are discussed.

#### 2.2.3 Processor Performance Estimation

In comparing design alternatives, where the user is interested in reducing response time, the chip architect will often relate the performance of two different processors. The response time is the time between the start and completion of an event. Increasing performance implies decreasing execution time. To avoid confusion between increasing and decreasing, we will use the terms "improve performance" or "improve execution time". Execution time can be defined as elapsed time to complete a task. For a processor, CPU time refers to the time the CPU is computing a task or group of tasks, not including I/O or other processes.

Most computers define speed or performance using a clock running at a constant rate. The discrete time events of a clock running at a constant rate are called clock cycles. Chip architects refer to the time of a clock period by its duration (e.g., 2 ns) or by its rate (e.g., 500 MHz). CPU time for a program or task can then be expressed two ways:

or

CPU time = CPU clock cycles for a task

$$\div$$

clock rate. (2.2)

In addition to the number of clock cycles needed to execute a task, a count can be taken of the number of instructions executed – the instruction path length or instruction count (IC). If the number of clock cycles and the instruction count are known, the average number of clock cycles per instruction (CPI) can be calculated as

CPI = CPU clock cycles for a task

$$\div$$

IC. (2.3)

Therefore CPU execution time is the product of the number of instructions executed, clock cycles per instruction and clock cycle time. Since we are making comparisons of different configurations within the same hardware technology and compiler, the only needed metric for performance is CPI, which is dependent on hardware organization and the instruction set architecture. The performance gain (speedup) that can be obtained by improving some portion of a processor can be calculated using Amdahl's Law [89]. Speedup is the ratio of execution time for the entire task (without using the enhancement) to the execution time for entire task (using the enhancement) and is given by

Speedup<sub>new conf</sub> =

$$CPI_{original} \div CPI_{new conf}$$

. (2.4)

SimpleScalar produces calculated results for CPI, IPC and IC along with other processor statistics. From this information, comparison of performance parameters can be made.

#### 2.2.4 Validation of Out-of-order Simulator

There have been four approaches to validating the results produced by *sim-outorder*: micro-benchmark validation, correlation with independent simulators, regression correlation, and code inspection. The SimpleScalar group has run a number of small programs (micro-benchmarks) to test various parts of the machine simulator [23]. For example they compared SimpleScalar ARM model to Intel's StrongARM SA-11XX processors and were within 4% of the real hardware performance. Table 2.7 shows the results of their comparison.

Table 2.7. Validation of performance (CPI) measures via benchmark testing [23].

| Benchmark         | SimpleScalar | SA-1110 | % Difference |

|-------------------|--------------|---------|--------------|

| cache_hit         | 1.02         | 1.01    | 0.9          |

| cache_miss        | 33.87        | 33.70   | 0.5          |

| br_taken          | 1.04         | 1.02    | 1.9          |

| br_nottaken       | 1.97         | 1.91    | 3.1          |

| bzip2.10          | 3.20         | 3.10    | 3.2          |

| cc1 –O cc1in.i    | 2.84         | 2.90    | 2.1          |

| fft.arm short.pcm | 1.45         | 1.44    | 0.1          |

Correlation with multi-scalar simulators, which were developed independently over the SimpleScalar framework, has been done for performance estimation using standard benchmarks [23]. The results were within 5% of the *sim-outorder* simulator. They also compared *sim-outorder* to other published results. However, this was less productive since *sim-outorder* is more detailed than many other dynamically scheduled processor simulators. Regression correlation was done between release versions one and two of *sim-outorder*. Any deviations were tracked down and fixed. Code inspections were run by researchers at University of Wisconsin-Madison and other schools [23]. This procedure has uncovered occasional performance bugs, which has increased the confidence of the SimpleScalar group that the code correctly models a reasonably detailed micro-architecture.

#### 2.3 Wattch Power Simulator Overview

Wattch is an architectural simulation tool built for analyzing and optimizing processor power dissipation [10]. Prior work on architecture-level techniques for power optimization has mainly focused on caches [24,25,26,27]. Historically, two factors led to this focus. For embedded processors, a large portion of their power consumption is budgeted to caches, in some cases up to 40% [28]. Also, since caches are regular structures (*i.e.*, bitline, wordline, sense amplifier, precharge) they are somewhat easier to model and quantify for power studies.

Some work on architectural-level power reduction has been addressed for other areas of the processor [29,30,31]. One of the major

shortcomings that was noticed by Brooks *et. al.* [30] in the area of architectural-level power reduction is the lack of a high-level, parameterizable, simulator framework that can accurately quantify power savings [10]. The point of their work was not to compete with lower-level tools but rather to expose the basics of power modeling at a higher level to computer architects and compiler writers. Brooks *et. al.* accomplished this goal by quantifying power consumption of all major units of the processor and integrating these power estimates into a high-level simulator (*e.g.*, SimpleScalar).

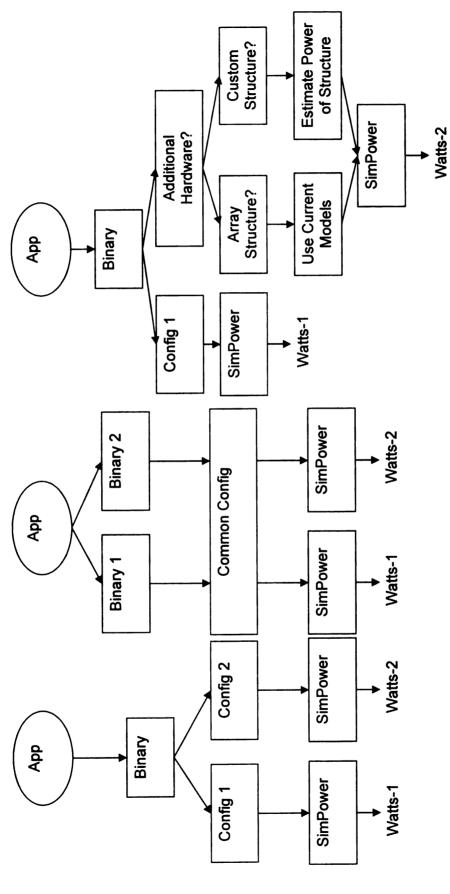

Figure 2.5 shows three possible ways Wattch can be used. The leftmost scenario applies to cases where the user is interested in comparing several design configurations that are achievable simply by varying parameters for hardware structures. The middle usage scenario is for software structures involved in compiler development, where a single hardware configuration is used and different compiler programs are simulated and compared. The rightmost scenario highlights Wattch's modularity, where additional hardware modules can be added to the simulator. For our purposes, we chose the first scenario for microarchitectural tradeoffs and exploration. In the following section, the power modeling methodology is described.

Figure 2.5. Three scenarios for using architecture-level power analysis [30].

## 2.3.1 Power Modeling Methodolgy

The basis for the power modeling tool is parameterized power models of common structures present in modern embedded processors. The main units that are modeled fall into four categories:

- Array Structures: Data and instruction caches, cache tag arrays,

all register files, register alias table, branch predictors, and large

portions of the instruction window and LSQ.

- Fully Associative Content-addressable Memories (CAM):

Instruction window/reorder buffer wakeup logic, load/store order checks, and TLB's.

- Combination Logic and Wires: Functional units, instruction window selection logic, dependency check logic, and result buses.

- Clocking: Clock buffers, clock wires, and capacitive loads.

Each model estimates capacitance based on the circuit and transistor sizing. In CMOS microprocessors, dynamic power consumption is the main source of power consumption and is defined as

$$P_{d} = \alpha C V_{DD}^{2} f \qquad (2.6)$$

where C is the load capacitance,  $V_{DD}$  is supply voltage and f is the clock frequency. The activity factor,  $\alpha$ , is a fraction between 0 and 1 indicating how often, on average clock ticks lead to switching activity. The supply voltage, clock frequency, and load capacitance are derived from 0.35 $\mu$

technology process parameters used from Palacharla, Jouppi, and Smith [32]. The activity factor is based on the execution of benchmark programs. For circuits that pre-charge and discharge on every cycle (i.e., double-ended array bitlines),  $\alpha$  = 1 is used. For other sub-circuits, such as single-ended array bitlines, the activity factors are estimated from the benchmark programs using the architectural simulator. For circuits where the internal nodes are unable to estimate switching activity (e.g., decoder and encoder), an assumption of 0.5 for random switching is used. Table 2.8 summarizes capacitance formulas used in the power analysis methodology [30].

Table 2.8. Capacitance formulas used in power analysis methodology [32].

| Node                         | Capacitance Equation                                           |

|------------------------------|----------------------------------------------------------------|

| Regfile Wordline Capacitance | C <sub>diff</sub> (WordlineDriver) +                           |

| _                            | C <sub>gate</sub> (CellAccess) * NumBitlines +                 |

|                              | C <sub>metal</sub> * WordlineLength                            |

| Regfile Bitline Capacitance  | C <sub>diff</sub> (PreCharge) + C <sub>diff</sub> (CellAccess) |

|                              | * NumWordlines + C <sub>metal</sub> *                          |

|                              | BLLength                                                       |

| CAM Tagline Capacitance      | C <sub>gate</sub> (CompareEn) * NumberTags +                   |

|                              | C <sub>diff</sub> (CompareDriver) + C <sub>metal</sub> *       |

|                              | TLLength                                                       |

| CAM Matchline Capacitance    | 2 * C <sub>diff</sub> (CompareEn) * TagSize +                  |

|                              | C <sub>diff</sub> (MatchPreCharge) +                           |

|                              | C <sub>diff</sub> (MatchOR) + C <sub>metal</sub> * MLLength    |

| ResultBus Capacitance        | 0.5 * C <sub>metal</sub> * NumALU * ALUHeight                  |

|                              | + 0.5 * C <sub>metal</sub> * RegfileHeight                     |

### 2.3.2 Array Structures

The array structure power model is parameterized based on the number of rows (entries), columns (width of each entry), and the number of read/write ports. These parameters affect the size and number of decoders, the number of wordlines, and the number of bitlines. The wordline driver and bitline discharge form the bulk of the power consumption in an array structure.

Modeling the power consumption of the wordlines and bitlines requires estimating the total capacitance on both of these lines. The capacitance of the wordlines includes three main components: diffusion capacitance of the wordline driver, the product of the gate capacitance of the cell access transistor and the number of bitlines, and the capacitance of the wordlines' metal wire. The capacitance of the bitline is modeled similarly, where the total capacitance is equal to the diffusion capacitance of the pre-charge transistor, the product of the diffusion capacitance of the cell access transistor and the number of wordlines, and the metal capacitance of the bitline. These capacitance models provide the option of use for single-ended or double-ended bitlines. It is assumed that register file array structures use single-ended bitlines and that cache array structures use double-ended bitlines.

Multiple ports on the array structure have been taken into account for power consumption in three ways. First, additional ports require an additional transistor connection which will add more capacitance on the wordlines. Second, each additional port requires up to two additional bitlines (each bit and its complement), both of which must precharge/evaluate on every cycle. Finally, as each core cell becomes larger

it will lead to longer word- and bitlines, thus incurring additional wire capacitance.

In the power model, certain transistors are automatically sized based on the model parameters to achieve reasonable delays. For example, the wordline driver is scaled based on the amount of capacitance on the wordlines. Longer wordlines require more capacitance to carry a signal. For other transistors, the sizing is based on the work from Palacharla et. al. [32] and Wilton et. al. [38].

## 2.3.3 Content-addressable Memory Structures

The analysis of Content-addressable Memory (CAM) structures is very similar to that of array structures. However, instead of modeling bitlines and wordlines, taglines and matchlines are modeled. The number of rows (number of tags), columns (number of bits per tag to match) and ports on the CAM are taken into account.

The key sizing parameters in the CAM are: the issue/commit width of the matchline (number of match or taglines in each core cell); the instruction window size (CAM's overall height); and the physical register tag size which equals  $\log_2$  of instruction window size (CAM's width). The CAM's overall height is each core (RAM) cell multiplied by the instruction window size. The CAM's overall width is the number of bits in the physical register tag, which share a common wide-OR for the final match that signals when the instruction is ready to issue. The wordlines are used to write new tag values into the CAM structure.

### 2.3.4 Complex Logic Blocks

The complex logic blocks are modeled by the following structures: instruction selection logic (instruction window), dependency check logic (register renaming unit), result buses, and the functional units. The selection logic and dependency check logic is based on the circuit structures modeled in Palacharla et. al. [32] and Bishop et. al. [33]. The power consumption of the result buses are modeled by estimating the length of the result buses using the same assumptions about functional unit height made by Palacharla et. al.

Previous work of Borah et. al. [34] and Zimmerman et. al. [35] has investigated the power consumption of various functional units. Their results regarding the power numbers are scaled for process and frequency in order to estimate the power consumption of the functional units.

### 2.3.5 Clocking Network

The clocking network of a high performance microprocessor can be the most significant source of power consumption [30]. Three sources of clock power consumption are considered: global clock metal lines, global clock buffers, and clock loading. The global clock metal lines are modeled as a modified H-tree network in which the global clock signal is routed to all portions of the chip using equivalent length metal wires and buffers in order to reduce clock skew. This method is similar to that used for the Alpha 21264 [36]. The global clock buffers are large transistors that are

used to drive the clock signals throughout the processor at a faster rate. The size and number of transistors are estimated similar to the methods of Fair et. al. [36] and Bowhill et. al. [37]. Explicit and implicit clock loading is considered. Explicit clock loads are the values of the gate capacitances of pre-charge transistors and other nodes that are directly connected to the clock within the units that are modeled. Implicit clock loads include the load on the clock network due to pipeline registers.

The models described are implemented as a C program using the Cacti tool [38] as a starting point. A summary of the major hardware structures and the correlation for the type of model used is given in Table 2.9.

Table 2.9. Common processor hardware structures and the model used by Wattch.

| Hardware Structure           | Model Type                |

|------------------------------|---------------------------|

| Instruction Cache            | Cache Array (2x bitlines) |

| Wakeup Logic                 | CAM                       |

| Issue Selection Logic        | Complex Combinational     |

| Instruction Window           | Array/CAM                 |

| Branch Predictor             | Cache Array (2x bitlines) |

| Register File                | Array (1x bitlines)       |

| Translation Lookaside Buffer | Array/CAM                 |

| Load/Store Queue             | Array/CAM                 |

| Data Cache                   | Cache Array (2x bitlines) |

| Integer Functional Units     | Complex Combinational     |

| FP Functional Units          | Complex Combinational     |

| Global Clock                 | Clock                     |

#### 2.3.6 Validation of Wattch Simulator

Brooks et. al. [10] presents details on the power models and simulator

infrastructure required to perform architectural-level power analysis. They verified the power models against industry circuits and found their results to be within 10% for low-level capacitance estimates, and within 10-13% on average for architectural models of tradeoffs between different structures. Baseline configuration models and the configuration of industry processors are shown in Table 2.10.

Table 2.10. Configuration for base and industry models.

| Parameter                           | Base    | Alpha   | Pentium | MIPS    |

|-------------------------------------|---------|---------|---------|---------|

| INT Instruction Window Size         |         | 20      |         | 16      |

| FP Instruction Window Size          |         | 15      |         | 16      |

| MEM Instruction Window Size         |         |         |         | 16      |

| UOP Instruction Window Size         | 64      |         | 20      |         |

| INT Physical Register Size          |         | 2x80    |         | 64      |

| FP Physical Register Size           |         | 72      |         | 64      |

| UOP Physical Registers Size         | 32      |         | 40      |         |

| Memory Order Queue Size             | 8       | 32      | 20      | 8       |

| Number of Inst. Fetched per Cycle   | 4       | 4       | 3       | 4       |

| Number of Inst. Decoded per Cycle   | 4       | 4       | 6       | 4       |

| Number of Inst. Issued per Cycle    | 4       | 6       | 3       | 4       |

| Number of Inst. Committed per Cycle | 4       | 4       | 3       | 4       |

| Number of Integer Funct. Units      | 5       | 4       | 4       | 3       |

| Number FP Funct. Units              | 3       | 2       | 1       | 3       |

| L1 Dcache Size                      | 64 K    | 64 K    | 8 K     | 8 K     |

| L1 Dcache Associativity             | 2-way   | 2-way   | 2-way   | 2-way   |

| L1 Icache Size                      | 64 K    | 64 K    | 8 K     | 8 K     |

| L1 Icache Associativity             | 2-way   | 2-way   | 2-way   | 2-way   |

| DTLB Size (fully assoc.)            | 128     | 128     | 64      | 64      |

| ITLB Size (fully assoc.)            | 128     | 128     | 32      | 64      |

| Local History Table                 |         | 1024x10 | NA      | NA      |

| Local Predict                       | 1024x2  | 1024x3  | 512x4   | 512x2   |

| Global History Register             | 10      | 12      | NA      | NA      |

| Global Predict                      | 4096x2  | 4096x2  | NA      | NA      |

| Choice Predict                      | 4096x2  | 4096x2  | NA      | NA      |

|                                     | 0.05    | 0.05    | 0.05    | 0.05    |

| Feature Size                        | 0.35 um |         |         | 0.35 um |

| Vdd                                 | 3.3 V   | 2.2 V   | 3.3 V   | 3.3 V   |

| MHz                                 | 600     | 600     | 200     | 200     |

Comparisons between modeled and reported power breakdowns of Pentium Pro and Alpha 21264 are shown In Tables 2.11 and 2.12.

Table 2.11. Comparison between modeled and reported total percentage of power breakdowns for the Pentium Pro [30].

| Hardware Structure        | Model  | Intel Data | % Difference |

|---------------------------|--------|------------|--------------|

| Instruction Fetch         | 21.00% | 22.20%     | 5.41%        |

| Register Alias Table      | 4.90%  | 6.30%      | 22.22%       |

| Reservation Stations      | 8.90%  | 7.90%      | 12.66%       |

| Reorder Buffer            | 11.90% | 11.10%     | 7.21%        |

| Integer Exec. Unit        | 14.60% | 14.30%     | 2.10%        |

| Data Cache Unit           | 11.50% | 11.10%     | 3.60%        |

| Memory Order Buffer       | 4.70%  | 6.30%      | 25.40%       |

| Floating Point Exec. Unit | 8.00%  | 7.90%      | 1.27%        |

| Global Clock              | 10.50% | 7.90%      | 32.91%       |

| Branch Target Buffer      | 3.80%  | 4.70%      | 19.15%       |

Table 2.12. Comparison between modeled and reported total percentage of power breakdowns for the Alpha 21264 [30].

| Hardware Structure        | Model  | Alpha<br>21264 | % Difference |

|---------------------------|--------|----------------|--------------|

| Caches                    | 15.30% | 16.10%         | 5.23%        |

| Out-of-order Issue Logic  | 20.60% | 19.30%         | 6.31%        |

| Memory Management Unit    | 11.70% | 8.60%          | 26.50%       |

| Floating Point Exec. Unit | 11.00% | 10.80%         | 1.82%        |

| Integer Exec. Unit        | 11.00% | 10.80%         | 1.82%        |

| Total Clock Power         | 30.40% | 34.40%         | 13.16%       |

The limitations of the models of Brooks *et. al.* [30] are that they do not necessarily model all of the miscellaneous logic present in real processors. The models are scaled and not the actual numbers for process parameters. Also, all of the parameter specifications are not given for each individual processor, which sometimes makes exact correlation to ideal processors difficult.

#### **CHAPTER 3**

## **Overview of Search Algorithms**

Search methods are used in many different areas including scientific computing applications and, in our case specifically, for design automation. The objective of a search algorithm is to systematically examine states to find the optimum. The search produces a path from start state to goal state. The output of a search is a unique solution to the problem which represents the best solution among those evaluated.

Mathematically, the state space can be represented as a graph G, which may be defined as a pair (V, E), where V is a set of vertices and E, the edges, is a set of unordered pairs of elements from V [39]. The elements of V are denoted  $V_i$  and the elements of E are denoted  $E_{ij}$ , to represent unordered pairs of vertices  $\{v_i, v_j\}$ . Equivalently, the graph can be thought of as the search space; the vertices are states and the edges are connections between states. In the search space, each state is defined as a set of parameters which are evaluated by the objective function E(X), where the evaluation of the function is achieved through computer computation.