#### LIBRARY Michigan State University

This is to certify that the dissertation entitled

## EFFICIENT TECHNIQUES FOR MODELING AND MITIGATION OF SOFT ERRORS IN NANOMETER-SCALE STATIC CMOS LOGIC CIRCUITS

presented by

Srivathsan Krishnamohan

has been accepted towards fulfillment of the requirements for the

| Ph.D.                       | degree in | Electrical and Computer Engineering |  |  |  |

|-----------------------------|-----------|-------------------------------------|--|--|--|

|                             |           |                                     |  |  |  |

| Dhospal                     |           |                                     |  |  |  |

| Major Professor's Signature |           |                                     |  |  |  |

|                             | 12        | /16/2005                            |  |  |  |

|                             |           | Date                                |  |  |  |

MSU is an Affirmative Action/Equal Opportunity Institution

## **PLACE IN RETURN BOX** to remove this checkout from your record. **TO AVOID FINES** return on or before date due. **MAY BE RECALLED** with earlier due date if requested.

| DATE DUE | DATE DUE | DATE DUE |

|----------|----------|----------|

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

2/05 p:/CIRC/DateDue.indd-p.1

## EFFICIENT TECHNIQUES FOR MODELING AND MITIGATION OF SOFT ERRORS IN NANOMETER-SCALE STATIC CMOS LOGIC CIRCUITS

By

Srivathsan Krishnamohan

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

#### DOCTOR OF PHILOSOPHY

Department of Electrical and Computer Engineering

#### ABSTRACT

## EFFICIENT TECHNIQUES FOR MODELING AND MITIGATION OF SOFT ERRORS IN NANOMETER-SCALE STATIC CMOS LOGIC CIRCUITS

Bv

#### Srivathsan Krishnamohan

Soft errors are changes in logic state resulting from the latching of single-event

transients (SETs) caused by high-energy particle strikes or electrical noise. Due to scaling of minimum feature size, supply voltage, and clock frequency, soft error rate (SER) is expected to increase by several orders of magnitude in combinational and sequential logic circuits in the near future. In this dissertation, we address the following three important issues related to logic soft errors: (1) modeling of SETs generated in combinational logic blocks (CLBs), (2) efficient design techniques to reduce the SER of CLBs, and (3) analysis and design of soft-error hardened latches. Our main contributions in modeling and mitigation of soft errors in logic circuits are as follows. (1) A fast and accurate lookup-table (LUT) based approach to estimate SET width, which is necessary to gauge the effectiveness of time-redundancy based SER mitigation techniques. The LUT provides more than 1000 times speedup over HSPICE simulations and has less than 10% error compared to existing techniques which have 15% or more error, without significantly increasing LUT size. (2) An efficient and systematic error masking (EM) technique that samples selected noncritical primary outputs (POs) of a CLB three times using delay-chain-generated control signals and then majority votes on them within the slack available in a cycle to mask errors. Hence, it incurs no performance overhead, does not perform redundant computation, and can mask SETs of width less than half the slack available at a PO. The average SER reduction from EM on ISCAS85 circuits is 82.67%. Other significant features of this technique include: (a) efficient triple sampling and majority voting and (b) exploitation of circuit timing dependence upon input vector and using non-uniform slack passing/borrowing in pipelined circuits to further reduce SER. (3) A method that supports error masking plus efficient error detection and recovery (EM+EDR) and is suitable for CLBs with a small fraction of non-critical POs. In this case, EM is applied to POs with sufficient slack and EDR to critical or nearcritical POs. EM+EDR can tolerate SETs with width up to half the clock period and provides an average SER reduction of 93.78% on ISCAS85 circuits. When a soft error occurs, a very low-likelihood event for an application run, and is detected, EM+EDR recovers from it within a single clock cycle. (4) Design of an efficient and robust delay chain to produce phase-shifted clock signals for use in our EM/EM+EDR techniques. (5) Finally, a comprehensive analysis of a number of existing soft-error hardened latch designs using a variety of metrics and some new designs, the best of which is vulnerable to only single-event multiple upsets, and which has a delay overhead of 12% and consumes only 70% power compared to a standard latch.

Our SER mitigation work represents a significant advancement over previous approaches which, in contrast, rely on introducing explicit hardware or time redundancy or on redundant computation, often both. Consequently, our methods provide substantial energy and performance/hardware advantages while significantly reducing logic SER.

#### Acknowledgements

It has been an enriching experience working with my advisor over the course of my Ph.D. and also interacting with him during the courses he has taught me. I deeply appreciate his patience with me and being very liberal with his time while I was looking around for a dissertation problem, as I used to discuss with him in every meeting a new topic that I had got excited about. His positive outlook, view that every problem is solvable, and attention to detail are things that I have admired, and have tried to imbibe some of these qualities in myself. His insistence on concise and precise writing, whose importance though initially lost on me, has led me to much learning of this skill.

I would like to thank Professors Anthony Wojcik, Michael Shanblatt, Peixin Zhong, and Shantanu Chakrabartty for consenting to be on my Ph.D. committee. I'm also grateful to them for being very co-operative with the scheduling of my proposal and dissertation defense and for reviewing my dissertation at short notices. Their valuable technical suggestions during my proposal defense, and their advice on the importance of good writing helped me to improve this final dissertation. Also, the courses taught by Professor Wojcik on computer architecture and Professor Chakrabartty on low-power mixed signal design helped broaden my knowledge in these areas.

I would like to thank Dr. Rajeev Murgai for providing me an opportunity to do my internship at Fujitsu Labs, which has been a valuable experience and has helped me to improve the dissertation research tremendously. My interaction with Dr. Rajeev Murgai taught me the rigors of industrial research and also showed that "Most of us"

can easily do two things at once; what's all but impossible is to do one thing at once". He has been more than a technical mentor to me, and my interaction with him has helped me to develop many positive qualities (least of which is my fore hand smash in ping-pong!). Also, I would like to thank William Walker for his guidance and funding during my internship, Subodh Reddy for helping me to improve my coding skills and making my stay in and outside of Fujitsu labs enjoyable. I'm grateful to Dr. Dipesh Patel, Stuart Biles, and Dr. Daryl Bradley for offering me the opportunity to investigate my ideas with them in ARM R&D during Summer 2005, and for their invaluable inputs. Also, I appreciate Dr. Dipesh Patel's kindness in offering to extend my internship at their Sunnyvale office.

Also thanks are due to the other members of my lab Krishnan, Gandhi, Sandeep, for making my stay at MSU memorable and for all the fun we had over the last two years. It was a pleasure working on my Ph.D. along side these guys and the productive working atmosphere provided by them made my stay in the ACAC lab enjoyable.

My experience at STMicroelectronics was an enriching one which gave me a deeper insight into the field of chip design and one which developed me professionally. My colleagues Murthy, Paolo, Wreeju, Arvind, Vijay and others in CMG-MCD made my ST years memorable. My colleague Vijay has been a great friend since my STMicro days and I'm deeply grateful for his kindness in providing all sorts of help and for his enjoyable company whenever I have visited Bay area. I am also grateful to Shanker and my other undergraduate friends from BITS Pilani in Intouch, for their great

<sup>&</sup>lt;sup>1</sup>Mignon McLaughlin, The Second Neurotic's Notebook, 1966

company and support during my BITS years and through my graduate study. Many thanks also to Dr. Sridhar from SUNY Buffalo, whose words of encouragement and advice have helped me in many of my endeavors.

My brother Srikanth has been a beacon through my life. The confidence he instilled in me early on and his constant motivation through the Ph.D. have been a big driving force for my timely completion of the dissertation. Also my parents have helped me reach me this far by instilling in me right from the beginning that "The virtue of all achievement is victory over oneself", and by supporting me in whatever endeavor I have taken up. This dissertation is dedicated to my parents and brother for their support and affection all these years. None of this would have been possible without the guidance and inspiration from my brother Srikanth and my parents.

## TABLE OF CONTENTS

| LI | ST ( | OF TABLES                                        |                      |  |  |  |  |  |  |

|----|------|--------------------------------------------------|----------------------|--|--|--|--|--|--|

| 1  | INT  | TRODUCTION                                       |                      |  |  |  |  |  |  |

|    | 1.1  | Radiation-Induced Soft Errors: Causes, SET C     | Generation, and SER  |  |  |  |  |  |  |

|    |      | Calculation                                      |                      |  |  |  |  |  |  |

|    | 1.2  | 2 SET Propagation, Masking, and Latching in Log  | gic Circuits         |  |  |  |  |  |  |

|    | 1.3  | B SER Scaling Trends for Combinational Logic, La | atches, and Memories |  |  |  |  |  |  |

|    | 1.4  | Our Contributions                                |                      |  |  |  |  |  |  |

|    |      | 1.4.1 Logic Circuit SER Estimation               |                      |  |  |  |  |  |  |

|    |      | 1.4.2 Efficient Soft-Error Mitigation Techniqu   | es for Combinational |  |  |  |  |  |  |

|    |      | Logic                                            |                      |  |  |  |  |  |  |

|    |      | 1.4.3 Robust Delay Chain Construction            |                      |  |  |  |  |  |  |

|    |      | 1.4.4 Hardening of Latches for Soft Errors       |                      |  |  |  |  |  |  |

|    | 1.5  | Dissertation Outline                             |                      |  |  |  |  |  |  |

| 2  | Mo   | odeling and Analysis of Soft Errors in Logic     | Circuits             |  |  |  |  |  |  |

|    | 2.1  | Simulation Setup                                 |                      |  |  |  |  |  |  |

|    |      | 2.1.1 HSPICE Modeling of I(t)                    |                      |  |  |  |  |  |  |

|    | 2.2  | 2 Sensitivity of SET Width                       |                      |  |  |  |  |  |  |

|    |      | 2.2.1 Gate Inputs                                |                      |  |  |  |  |  |  |

|    |      | 2.2.2 Output Load Capacitance                    |                      |  |  |  |  |  |  |

|    |      | 2.2.3 Charge Collected                           |                      |  |  |  |  |  |  |

|    |      | 2.2.4 Gate Size                                  |                      |  |  |  |  |  |  |

|    | 2.3  | B Lookup Table                                   |                      |  |  |  |  |  |  |

|    | 2.4  | -                                                |                      |  |  |  |  |  |  |

|    | 2.5  | Regression for Supply Voltage Variation          |                      |  |  |  |  |  |  |

|    | 2.6  | Conclusion                                       |                      |  |  |  |  |  |  |

| 3  | Err  | ror Masking for SER Mitigation                   |                      |  |  |  |  |  |  |

|    | 3.1  | Introduction                                     |                      |  |  |  |  |  |  |

|    | 3.2  | Related Work                                     |                      |  |  |  |  |  |  |

|    |      | 3.2.1 Self-Checking Designs                      |                      |  |  |  |  |  |  |

|   |     | 3.2.2 Architectural Techniques                                     |

|---|-----|--------------------------------------------------------------------|

|   |     | 3.2.3 Gate and Circuit-Level Techniques                            |

|   | 3.3 | Time Redundancy Based Error Masking                                |

|   |     | 3.3.1 Output Sampling and Majority Voting                          |

|   | 3.4 | Delay Chain                                                        |

|   | 3.5 | Simulation Results                                                 |

|   |     | 3.5.1 Extension of LUT to Calculate SET Width at Primary Output 50 |

|   |     | 3.5.2 Critical Charge and Transient Pulse Width Calculation 51     |

|   |     | 3.5.3 SER Calculation of Complete Circuit                          |

|   |     | 3.5.4 SER Reduction Using Error Masking                            |

|   | 3.6 | Conclusion                                                         |

| 4 | Cor | mbining Error Masking and Error Detection Plus Recovery 56         |

|   | 4.1 | Introduction                                                       |

|   | 4.2 | Related Work                                                       |

|   |     | 4.2.1 Error Masking                                                |

|   | 4.3 | Techniques to Combine Error Masking and Error Detection Plus Re-   |

|   |     | covery                                                             |

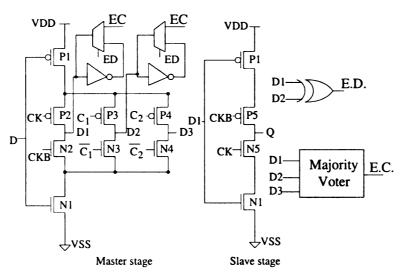

|   |     | 4.3.1 Error Detection and Recovery on a Single Path 60             |

|   |     | 4.3.2 Circuits for Error Detection and Recovery 62                 |

|   | 4.4 | Techniques to Enhance Error Masking 65                             |

|   |     | 4.4.1 Exploiting Circuit Timing Dependence on Input Vector 65      |

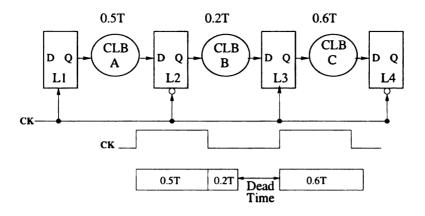

|   |     | 4.4.2 Slack Redistribution to Enhance Error Masking 67             |

|   | 4.5 | Simulation Results                                                 |

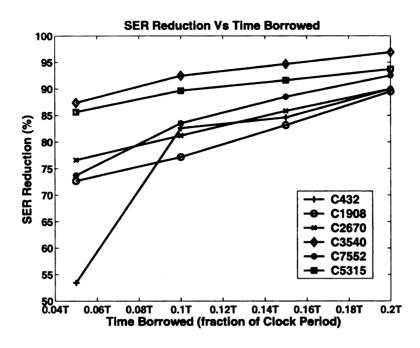

|   |     | 4.5.1 SER Reduction Using Slack Redistribution                     |

|   | 4.6 | Conclusion                                                         |

| 5 |     | oust Delay Chain Construction 77                                   |

|   | 5.1 | Introduction                                                       |

|   |     | 5.1.1 Delay Elements                                               |

|   | 5.2 | Yield Definition                                                   |

|   | 5.3 | Parameters Studied                                                 |

|   | 5.4 | Simulation Methodology                                             |

|   | 5.5 | Delay Element Analysis and Yield Results                           |

|   |     | 5.5.1 Transmission Gate Based Delay Element                        |

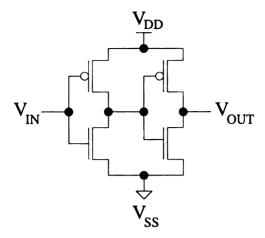

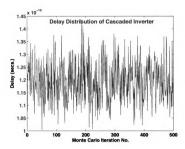

|   |     | 5.5.2 Cascaded Inverter Based Delay Element                        |

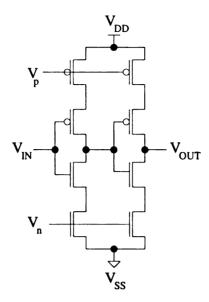

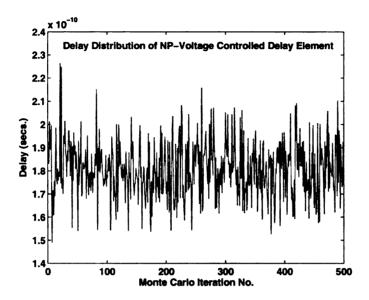

|   |     | 5.5.3 NP-Voltage Controlled Delay Element                          |

|   | 5.6 | Comparison of Delay Elements                                       |

|   |     | 5.6.1 Effect of $V_{\rm DD}$ and Gate Length Variation             |

|   |     | 5.6.2 Effect of $V_{\rm DD}$ and Width Variation                   |

|   | 5.7 | Control Signal Generation and Distribution from Delay Chain        |

|              | 5.8  | Conclu   | asion                                                      | 97  |

|--------------|------|----------|------------------------------------------------------------|-----|

| 6            | Ana  | alysis a | and Design of Soft Error Hardened Latches                  | 98  |

|              | 6.1  | Simula   | ation Methodology                                          | 99  |

|              |      | 6.1.1    | Latch Delay and Power Calculation                          | 99  |

|              | 6.2  | Comp     | arison of Latch Designs                                    | 101 |

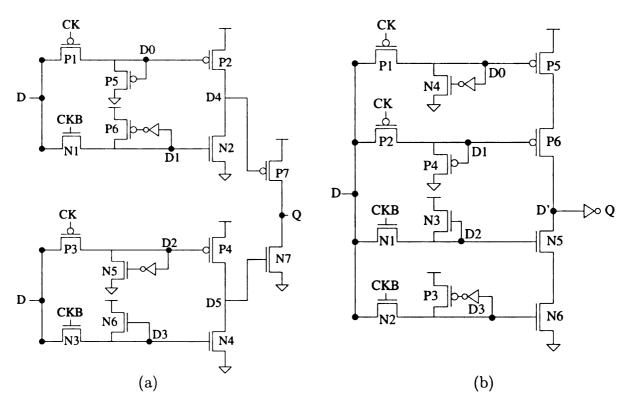

|              |      | 6.2.1    | SEU Tolerant Latch                                         | 101 |

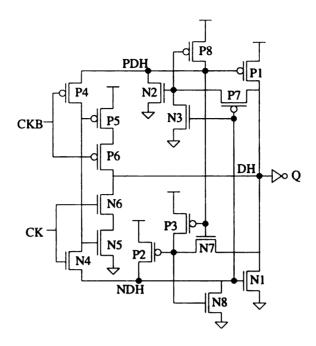

|              |      | 6.2.2    | Soft Error Hardened Latch Scheme for SoC                   | 103 |

|              |      | 6.2.3    | Dual Interlocked Storage Cell                              | 105 |

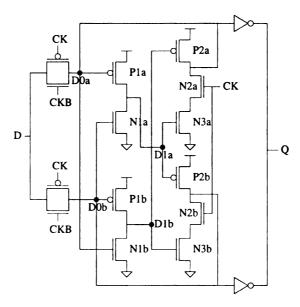

|              |      | 6.2.4    | Single Event Resistant Topology Latch                      | 106 |

|              |      | 6.2.5    | Other Latch Designs                                        | 108 |

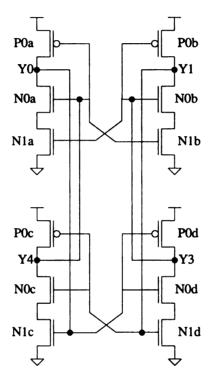

|              | 6.3  | New L    | Eatch Designs with Soft-Error Immunity                     | 109 |

|              |      | 6.3.1    | Customizing Latches for Performance and Power Requirements | 114 |

|              | 6.4  | Conclu   | usion                                                      | 115 |

| 7            | Cor  | clusio   | n                                                          | 116 |

|              | 7.1  | Key C    | Contributions                                              | 116 |

|              | 7.2  | Future   | e Work                                                     | 119 |

| $\mathbf{B}$ | IBLI | OGRA     | РНУ                                                        | 121 |

### LIST OF FIGURES

| 1.1 | Mechanism for SET generation                                              | 5  |

|-----|---------------------------------------------------------------------------|----|

| 1.2 | Delay fault and latching window of gates in a logic circuit               | 7  |

| 1.3 | Long-term estimates from ITRS for the supply voltage, and clock frequency |    |

|     | of DRAMs, microprocessors, and ASICs used in high performance and low-    |    |

|     | power applications [1]                                                    | 10 |

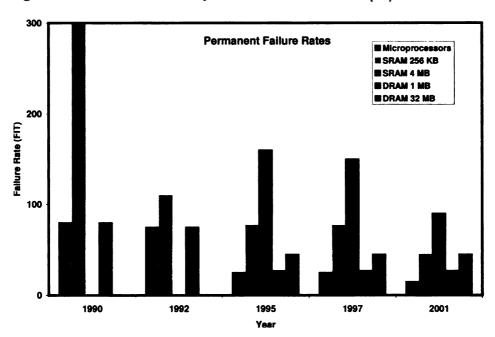

| 1.4 | Permanent fault FIT rates for microprocessors, SRAMs and DRAMs            | 12 |

| 2.1 | Circuit setup used to measure the sensitivity of SET width to various     |    |

|     | parameters                                                                | 24 |

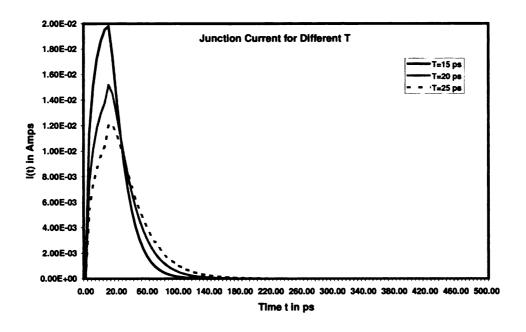

| 2.2 | Junction current waveform for different time constants                    | 25 |

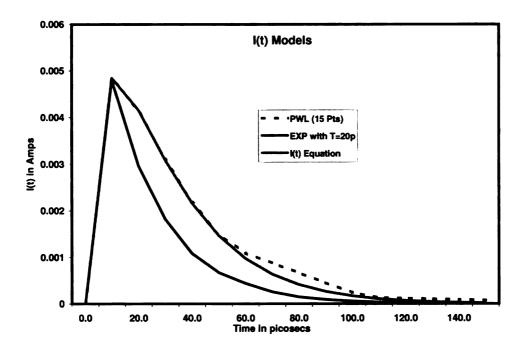

| 2.3 | Current waveform for different models                                     | 26 |

| 2.4 | $Q_{ m crit}$ dependence on input vectors applied                         | 28 |

| 2.5 | SET width variation for various output loads                              | 29 |

| 2.6 | SET width variation for different gate drive strengths                    | 30 |

| 2.7 | Surface described by three co-ordinates X, Y, and Z corresponding         |    |

|     | to $Q$ , $C_L$ , and SET width. $Q$ and $C_L$ values in the middle of LUT |    |

|     | indices are used to test the accuracy of the LUT. The figure shows the    |    |

|     | neighboring points and the surface formed by them, when the LUT is        |    |

|     | indexed using $Q = 10$ fC and $C_L = 25$ fF                               | 33 |

| 2.8 | Variation of SET width for supply voltage perturbation                    | 35 |

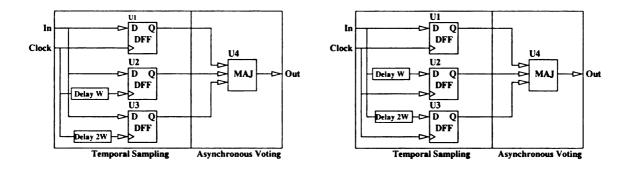

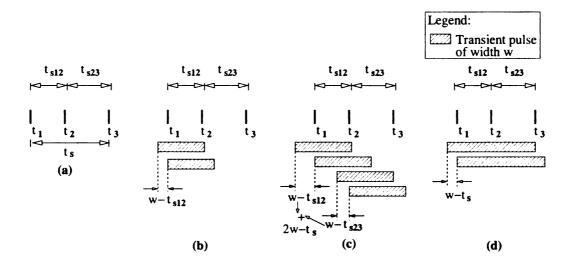

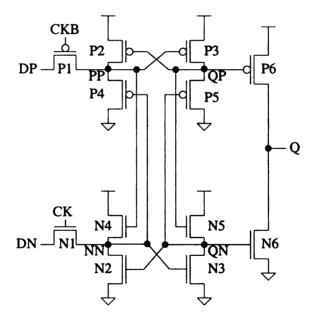

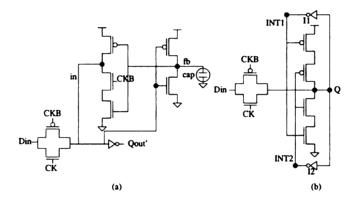

| 3.1 | Existing temporal sampling latches                                        | 40 |

| 3.2 | Latching window probability for SETs using multiple sampling error        |    |

|     | masking schemes                                                           | 43 |

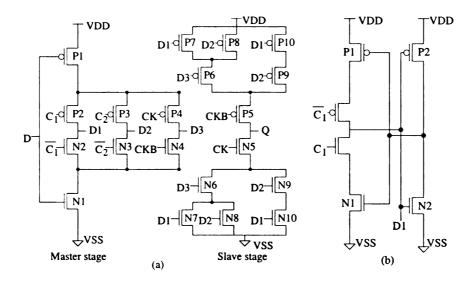

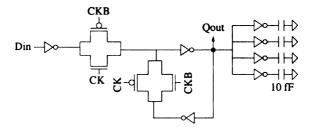

| 3.3 | Flip-flop for error masking                                               | 45 |

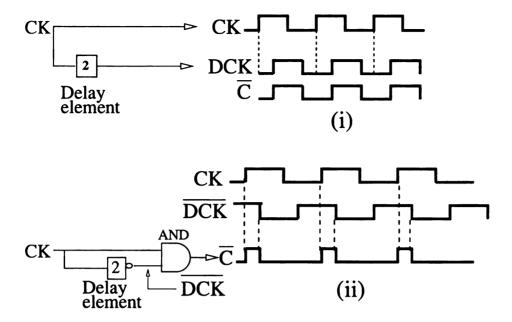

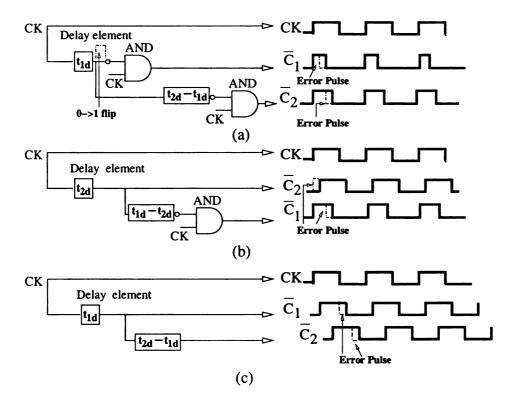

| 3.4 | Generation of control signals C and $\overline{C}$                        | 47 |

| 3.5 | Effect of particle strikes on delay chain                                 | 48 |

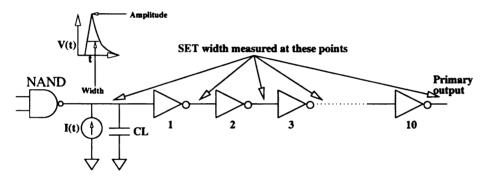

| 3.6 | Simulation setup for generating three dimensional LUT                     | 51 |

| 4.1 | Flip-flop used for error detection and recovery                           | 61 |

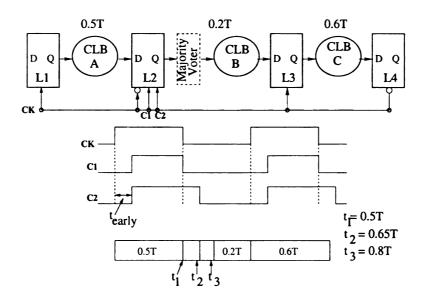

| 4.2 | Latch-based pipeline with dead time                                       | 69 |

| 4.3 | Latch-based pipeline with dead time being used for error masking          | 70 |

| 4.4 | SER reduction results for time borrowing                                  | 74 |

| 4.5  | Algorithm for time borrowing to reduce SER                               | 76  |

|------|--------------------------------------------------------------------------|-----|

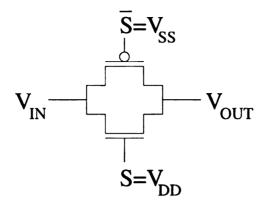

| 5.1  | Schematic diagram of a transmission gate                                 | 82  |

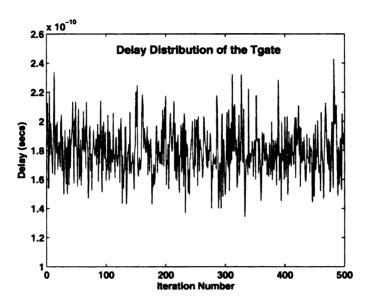

| 5.2  | Delay of transmission gate for different iterations of a MCS             | 83  |

| 5.3  | Schematic diagram of a cascaded inverter                                 | 84  |

| 5.4  | Delay of cascaded inverter for various Monte Carlo iterations            | 86  |

| 5.5  | Schematic diagram of a NP-voltage cascaded inverter                      | 87  |

| 5.6  | Delay distribution of NP-voltage controlled delay element for various    |     |

|      | Monte Carlo iterations                                                   | 88  |

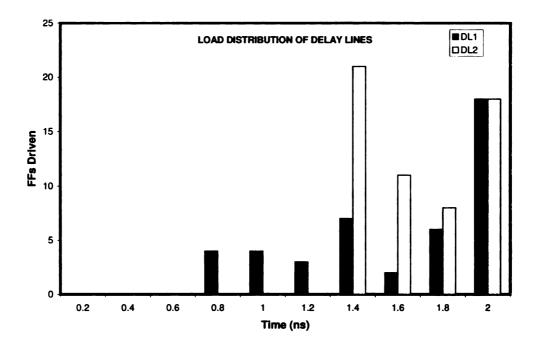

| 5.7  | The number of flip-flops driven by each delay tap in the delay line of   |     |

|      | c7552. Two separate delay chains -DL1, DL2- are used to prevent soft     |     |

|      | errors from occurring due to particle strikes on the delay chain itself. | 93  |

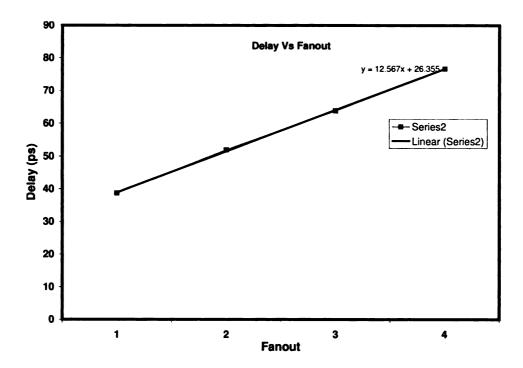

| 5.8  | Delay versus fanout for an inverter in TSMC 0.18 micron technol-         |     |

|      | ogy. The absolute value of the parasitic delay of an inverter is the     |     |

|      | Y-intercept of the line shown, and has a value of 26.4 ps                | 95  |

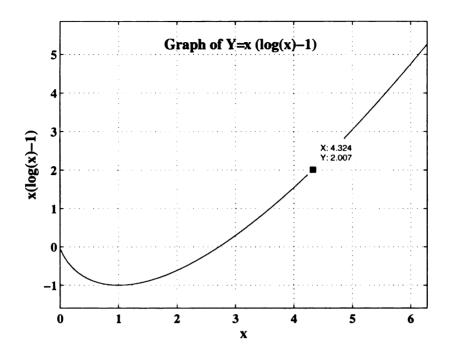

| 5.9  | Graph used to find the best stage effort                                 | 96  |

| 6.1  | Basic transmission gate latch used to normalize delay and power values   |     |

|      | of other latch designs. The delay and power values were measured by      |     |

|      | connecting a FO4 inverter at the latch output                            | 100 |

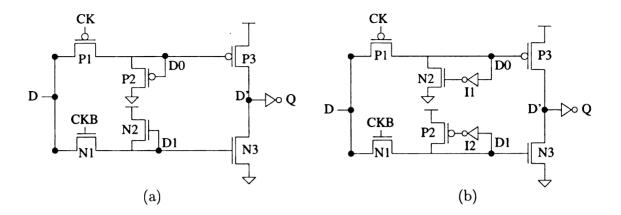

| 6.2  | Schematic of single event upset tolerant latch                           | 101 |

| 6.3  | Schematic of soft error hardened latch                                   | 104 |

| 6.4  | Schematic of dual interlocked storage cell                               | 105 |

| 6.5  | Schematic of single event resistant topology                             | 107 |

| 6.6  | Hardening of the feedback node in a latch                                | 108 |

| 6.7  | Proposed latch designs for soft error tolerance                          | 110 |

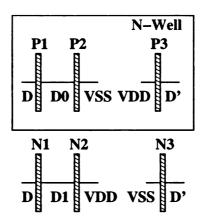

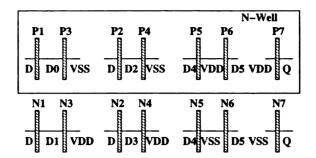

| 6.8  | Stick diagram for layout of latch A                                      | 111 |

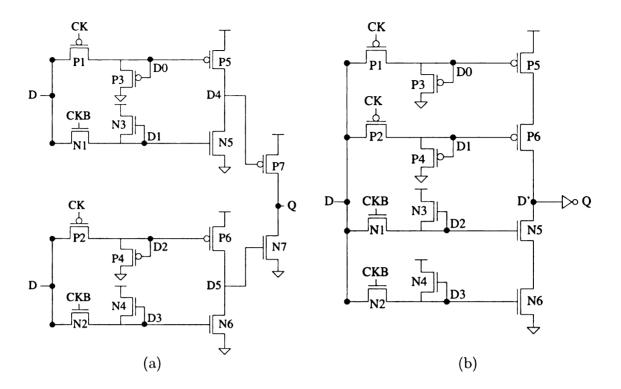

| 6.9  | Improved latch designs with higher soft error tolerance                  | 112 |

| 6.10 | Stick diagram for layout of latch C                                      | 113 |

| 6.11 | Customized latch designs trading off speed and power                     | 115 |

## LIST OF TABLES

| 1.1        | $Q_{crit}$ and $Q_s$ in it of combinational logic, latches, and SRAMs for different technology nodes                                                                                                                                                                                                                                                                                                                         | 11  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1<br>2.2 | Percentage error for both PWL and exponential current sources Percentage error for interpolation from a LUT with both uniform and                                                                                                                                                                                                                                                                                            | 27  |

|            | non-uniform interval between indices                                                                                                                                                                                                                                                                                                                                                                                         | 33  |

| 3.1        | SER reduction for ISCAS85 circuits due to error masking                                                                                                                                                                                                                                                                                                                                                                      | 54  |

| 4.1        | SER reduction for ISCAS85 circuits. The power overhead in practice would be lower than the one presented above due to: (1) The original power has been estimated using zero delay model, which does not take into account glitchy or partial transitions. (2) The leakage energy, which has not been taken into account, consumed by the overhead circuit is far lower than the leakage of the CLB, due to fewer components. | 72  |

| 5.1        | Parameter variations for the process considered                                                                                                                                                                                                                                                                                                                                                                              | 80  |

| 5.2        | Mean delay and variability of the delay elements when $V_{DD}$ variation is 10% and 20%, and gate length variation is 10%                                                                                                                                                                                                                                                                                                    | 88  |

| 5.3        | Mean delay and variability of the delay elements when $V_{\rm DD}$ and gate width variation are 10%                                                                                                                                                                                                                                                                                                                          | 89  |

| 6.1        | Delay and power overhead of the proposed latch designs                                                                                                                                                                                                                                                                                                                                                                       | 114 |

| 6.2        | Delay and power overhead of the customized latch designs                                                                                                                                                                                                                                                                                                                                                                     | 114 |

### CHAPTER 1

## INTRODUCTION

Designers strive to deliver ever-higher performance systems cost-effectively by leveraging technology scaling to meet end-user application needs. However, with unprecedented levels of device integration ( $\sim 10^9$  transistors/chip) and scaling of minimum feature size (~ 10s of nm), clock frequency (~ 10s of GHz), and supply voltage  $(V_{DD} < 1 \text{ V})$ , the transient fault or soft-error rate (SER) of logic circuits is becoming a dominant reliability challenge even in commodity processors. Soft errors are changes in logic state resulting from the latching of single-event transients (transient voltage fluctuations at a logic node or SETs) caused by electrical noise or external radiation. Unlike hard errors (arising from, say, electromigration, hot carrier effects, or dielectric breakdown), they do not result in permanent damage of components. In this dissertation, we are concerned with static CMOS circuit soft errors. Although most of our discussion and mitigation techniques apply to soft errors due to either source (i.e., electrical noise or external radiation), our focus is on radiation-induced errors, particularly, those resulting from high-energy neutron strikes. This is because, as explained in Sec. 1.1, high-energy neutron strikes represent the most important source of soft errors and their effects are well modeled, allowing us to accurately analyze the effectiveness of our soft error mitigation techniques. Background on radiation-induced soft errors and a brief discussion of our contributions relative to previous work follows next.

# 1.1 Radiation-Induced Soft Errors: Causes, SET Generation, and SER Calculation

Soft errors are caused by electrical noise (e.g., due to crosstalk and IR or Ldi/dt supply noise), electromagnetic interference, and external radiation, with the latter being the most important source and our main focus. The operating environment of a semiconductor chip contains background radiation from cosmic rays, low energy thermal neutrons, and radioactive traces present in chip packaging material. These radiations comprise electrons, protons, neutrons, pions, muons, alpha, and other particles. The following two types of effects have been observed from these radiations.

• Total dose effects (TDEs): These result from the interaction of ionizing radiation with device materials. TDEs can cause changes in transistor threshold voltage and decrease the mobility of carriers in the channel, and hence the transconductance and gain of a transistor. Gain degradation results in increased propagation delay of a gate. TDEs cause changes in the transistor and circuit characteristics over a long period of time, which do not lead to failure in commodity chips. Hence, they are not considered in this dissertation.

• Single event effects (SEEs): These result from the interaction of a highenergy particle passing through a device. SEEs can cause single event upsets (SEUs) or single event latchups (SELs). SEUs are reversible bit-flips in a latch or memory element that change the logic state of a circuit. The change in the logic state of a circuit due to SEUs are called soft errors in contrast to hard errors which are irreversible. Soft errors are reversible since their effects can be removed by resetting or rewriting the memory elements. SEL occurs when the injected charge activates the parasitic PNPN structure that exists in bulk CMOS transistors. SEL is not a threat to SOI devices and can be prevented in bulk CMOS by using thin epitaxial layers or guard rings [2].

Various ionizing particles generate electron-hole pairs through different mechanisms. An alpha particle ionizes the atoms in a chips's substrate through electromagnetic force between itself and the valence electrons. However, high-energy cosmic-ray neutrons and protons collide with nuclei within silicon substrate and generate secondary particles capable of ionizing silicon atoms. A neutron has to encounter, on an average, 10<sup>10</sup> atoms before it hits a nucleus. Based on the density of silicon (which is 2.3 gm/cm<sup>3</sup>) and the absorption length for neutrons, the average distance a neutron has to travel in silicon substrate before it hits a nucleus is on the order of tens of centimeters. This explains the fact that neutrons, which have enough energy to pass through shields that are hundreds of centimeter thick, do not easily cause logic upsets at multiple nodes in a circuit block.

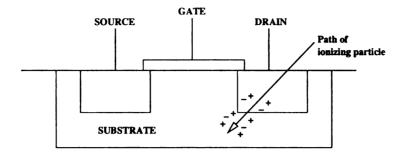

The secondary particles generated by neutrons traverse and ionize the silicon substrate, in the process creating a track of excess electron-hole pairs, with average ionization energy (i.e., the average energy needed of the particle to ionize a silicon atom) being 3.6 eV/electron-hole pair in silicon. Some of these electron-hole pairs can eventually reach a reverse-biased pn junction of a sensitive node, such as a gate output as shown in Figure 1.1. When that happens, the majority carriers are reflected from the depletion region of the pn junction while the minority carriers are swept across the junction through the drift mechanism. This causes a net current across the depletion region that can either charge or discharge a logic node. For example, electrons created near the drain node of an NMOS transistor connected to  $V_{\rm DD}$  pull the drain node to GND. In the case of static nodes, the electrons recombine with holes shortly thereafter, and the drain node is charged back to  $V_{\rm DD}$ . For static nodes, this creates a transient glitchy pulse called single-event transient (SET), whose amplitude and duration depend upon the strength of the driving gate and the output capacitance that it drives. Recently, Sun and Intel announced that chip packages with alpha-particle emitting lead have been minimized. Therefore, high-energy cosmic rays and the neutrons present in them are expected to become the primary source of soft errors in the future. The methodology and schemes we propose in this dissertation are applicable to soft errors caused by sources other than neutrons too. But, we evaluate most of our proposed schemes based on radiation-induced errors, particularly, those resulting from high-energy neutron strikes, since SET generation mechanisms due to neutron strikes have been studied for a long time and are well-understood. As a result, sufficient information for calculating SERs of CMOS process technologies are available for neutron strikes.

Figure 1.1. Figure shows an ionizing particle passing through a silicon substrate generating holes and electrons. SET is generated when the holes and electrons collect around a pn junction of a drain node as shown.

The basic or raw soft-error rate (SER) of CMOS circuits due to cosmic ray neutrons can be calculated using the following equation from [3]:

$$SER(Q_{crit}) = K \times F \times A \times e^{\left(\frac{-Q_{crit}}{Q_s}\right)}, \tag{1.1}$$

where K is a technology-independent constant, F is the neutron flux, A is the sensitive device area,  $Q_{\rm crit}$  is the critical charge, and  $Q_s$  the charge collection slope for the technology, which is strongly dependent on doping and supply voltage. The critical charge  $Q_{\rm crit}$  is defined as the minimum charge required to cause a logic upset in memory elements, and in logic circuits, it is the minimum charge which generates SETs that can change the value stored in a latch or flip-flop. The sensitive device area is equal to the sum of node areas where charge collection can lead to SET generation in logic gates, or logic upset in latches and memory elements.

## 1.2 SET Propagation, Masking, and Latching in Logic Circuits

Soft errors can occur in both sequential circuits (latches and flip-flops) and combinational logic blocks (CLBs). A particle strike causing a single event upset (SEU) at a latch, when the latch is in hold mode, results in an error. However, SEU at a gate leads to generation of a single-event transient (SET). SETs are transient voltage fluctuations, such as a  $1\rightarrow 0$  or  $0\rightarrow 1$  logic flip, occurring at a gate output. Such SETs, apart from being generated by radiation, can also occur due to electrical noise such as crosstalk and IR and Ldi/dt supply noise. Soft errors in CLBs result from SETs changing the value stored in memory elements, such as latches, flip-flops, or register files. For a SET originating in CLB to cause a soft-error, it must propagate to a primary output (PO) gate and be finally captured by an output latch. However, a soft error will not occur if the SET is either: (1) logically masked: some other input of a gate in the SET propagation path determines its output instead of the SET; (2) timing window masked: the SET does not arrive around the closing clock edge and hence is not captured by the output latch; (3) electrically masked: the amplitude of the SET is not sufficient to cause a state change at one of the propagating gates or at the output latch.

In a static CMOS circuit, since the SET can get latched only if it arrives around the clock closing edge, soft errors in combinational circuits are synchronous. Synchronous soft errors can be further classified into the following two types [4].

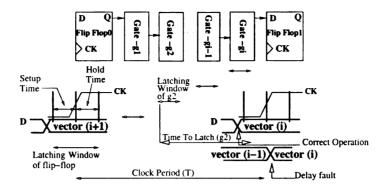

1. Delay faults: These are caused by transient pulses with width smaller than

Figure 1.2. Delay fault and latching window of gates in a logic circuit. The figure shows both correct and incorrect operation of a logic circuit. During correct operation, the data corresponding to vector *i* transitions a setup time before the clock closing edge. Incorrect operation results due to a delay fault, which pushes the data D of flip-flop1 to transition after the clock closing edge. Also, the figure shows latching window of gates in a pipeline stage. Latching window of gates located farther from the PO occurs earlier in the clock cycle time.

the latching window time (sum of latch setup and hold times). Such transients cause an error by delaying the arrival of the PO signal at the output latch. This leads the PO to transition after the setup time as shown in Figure 1.2.

2. Functional faults: These occur when the transient pulse is wider than and overlaps the latching window of the output latch. The value stored in the output latch gets flipped, which changes the logic state.

An SET has two properties associated with it that determine whether it gets latched at the primary output:

Spatial: whether the SET originates on a critical or non-critical path of the CLB. 2. Temporal: whether the SET originates at a gate output before or after the output has settled.

These two properties strongly influence the likelihood of an SET not getting masked due to the latching window effect. Each gate has a latching window as shown in Figure 1.2, during which time the error pulse has to pass through the gate in order not to get latching window masked. The latching window of a gate extends approximately from  $t_{\rm clk,edge} - t_{\rm setup} - t_{\rm TTL}$  to  $t_{\rm clk,edge} + t_{\rm hold} - t_{\rm TTL}$ , where  $t_{\rm clk,edge}$  is the time of clock closing edge,  $t_{\text{setup}}$  and  $t_{\text{hold}}$  are the setup and hold times of a latch, respectively, and  $t_{\text{TTL}}$  is the time to latch or the propagation delay from the gate output to a latch. Any SET with width w passing through the gate has to completely overlap this latching window to cause a logic flip at the output latch. Latching window of a gate can begin at or after the time the actual output of the gate passes through it. For gates on a critical path, the latching window overlaps with the time when actual gate output settles, while for gates on non-critical paths, latching window occurs after actual gate output settles. An SET generated at any gate before its output settles would get latching window masked, unless its pulse width extends to overlap the complete latching window of the gate.

The SER of a system is usually measured in failures in time (FITs) or mean time between failures (MTBF). FIT is defined as the number of failures in one billion hours of operation, while MTBF is the mean time between two successive failures.

For example, an MTBF of 1000 years equals a FIT rate of 114  $(10^9/(24 \times 365 \times 1000))$ . A fault-tolerant system with infinite MTBF corresponds to zero FIT. FIT is

more commonly used by VLSI designers because it is additive (i.e., the FIT rate of a system is obtained by adding the FIT rates of individual components), unlike MTBF.

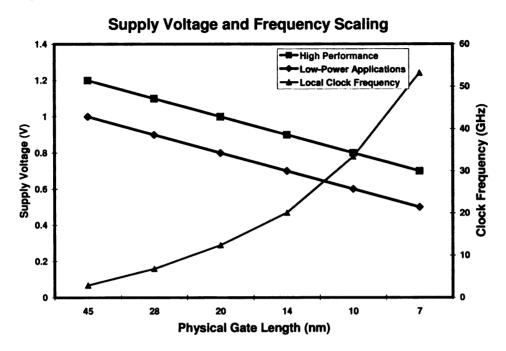

## 1.3 SER Scaling Trends for Combinational Logic, Latches, and Memories

The scaling of SER for memories, latches, and combinational logic differ with advancing process generations; minimum physical gate length is used to demarcate different process generations. As can be seen from Eqn. 1.1, SER is: (i) linearly proportional to the sensitive device area A and (ii) exponentially dependent on the ratio  $Q_{crit}/Q_s$ . When  $Q_{crit}/Q_s$  is close to one, SER scaling is dominated by the sensitive device area. The sensitive device area decreases quadratically with shrinking feature size and, based on scaling trends, is 50% smaller compared to that for the immediately previous process generation. The critical charge depends only on the charge stored  $(Q_{stored} = C \times V_{DD})$  at a dynamic node, and on both  $Q_{stored}$  and the charge dissipation capability at a static node. Critical charges are decreasing nonlinearly **wi**th each process generation due to diminishing  $Q_{stored}$ . This can be seen from the International Technology Roadmap for Semiconductors (ITRS) prediction of supply voltage and clock frequency scaling shown in Figure 1.3. The supply voltages for high-performance and low-power applications are expected to drop to 0.7 V and 0.5 V, respectively, at the 7 nm technology node, while the clock frequency scales to 55  $\mathbf{GH}_{\mathbf{Z}}$ . This would lead to significant reduction in  $Q_{crit}$ , which implies particles of 10 wer energy, with higher flux, can cause SEUs. In addition, it has been experimentally verified that SER of logic circuits increases linearly with clock frequency [5]. Thus, decreasing  $V_{\rm DD}$  and increasing clock frequency lead to higher SERs in future technologies.

Figure 1.3. Long-term estimates from ITRS for the supply voltage, and clock frequency of DRAMs, microprocessors, and ASICs used in high performance and low-power applications [1].

The charge collection efficiency  $Q_s$  scales approximately linearly with device size in a log-log scale [3]. The value of  $Q_{crit}$  and  $Q_s$  for both logic and memories for different technology nodes, reproduced from [6], is given in Table 1.1. The first five rows give the critical charge for combinational logic, latches, and SRAMs in femto Coulombs (fC). The last row gives the value of charge collection slope in fC for different process generations. The value of  $Q_{crit}$  for latches and SRAM cells becomes smaller than  $Q_s$  at 100 nm and 180 nm technology nodes, respectively, and hence as feature size and the device area scale down, the SER of memory elements reduces. However, in logic gates,  $Q_{crit}$  is more than  $Q_s$ , due to which a small decrease in critical charge increases

SER by orders of magnitude.

| Circuit Element                     | 600  | 350  | 250  | 180  | 130  | 100  | 70   | 50    |

|-------------------------------------|------|------|------|------|------|------|------|-------|

|                                     | nm    |

| Q <sub>crit</sub> of Logic: 16 FO4s | N/A  | 676  | 489  | 250  | 116  | 61.3 | 24.0 | 10.40 |

| Q <sub>crit</sub> of Logic: 4 FO4s  | 4160 | 509  | 336  | 131  | 63.9 | 35.2 | 16.0 | 7.02  |

| Q <sub>crit</sub> of Logic: 0 FO4s  | 1130 | 386  | 265  | 99.3 | 48.8 | 27.3 | 13.2 | 5.57  |

| $Q_{crit}$ of Latches               | 360  | 120  | 82.4 | 31.9 | 15.0 | 7.96 | 3.73 | 1.66  |

| $Q_{crit}$ of SRAM                  | 146  | 48.8 | 33.7 | 12.9 | 6.31 | 3.43 | 1.52 | 0.67  |

| $Q_s$                               | 52.3 | 34.6 | 26.8 | 17.2 | 12.2 | 9.53 | 7.19 | 5.54  |

Table 1.1.  $Q_{crit}$  and  $Q_s$  in fC of combinational logic, latches, and SRAMs for different technology nodes.

In current technologies, soft-error contribution of latches and SRAMs far exceeds the soft-error contribution of CLBs. Mitra and others estimate the contribution of combinational logic, latches, and unprotected SRAM for a commercial state-of-the art processor to be 11%, 49%, and 40%, respectively [7]. But as technology scales and clock frequencies increase, SET from a CLB has a higher likelihood of latching because of diminishing  $Q_{crit}$  and latching-window probability. This is expected to make SER contribution of logic much more than that of memories. Shivkumar and others have shown that SER per chip of combinational logic circuits will increase nine orders of magnitude when minimum feature size scales from 600 nm to 50 nm, becoming comparable to SER per chip of unprotected memory elements [6]. In addition to logic SER scaling, the SER per latch or SRAM bit is expected to stay the same or decrease in future technology generations [8, 9]. Although the critical charge per latch or SRAM bit decrease, smaller cross section area of these devices reduces the probability of SEU occurring. However, due to the increasing number of latches and SRAM nodes per chip, in the future, the contribution of memory elements to total

chip SER is estimated to increase, but at a rate lower than that of combinational logic circuits [10].

The advances made in semiconductor process technology have reduced manufacturing related failures in chips. The trends observed in permanent fault rates for microprocessors, SRAMs, and DRAMs are shown in Figure 1.4 [11]. This plot shows that the FIT rate due to permanent faults has clearly decreased over the period 1990-2001. In the case of 256 KB SRAM, the FIT rate has fallen by six times reaching 50 in 2001 from an initial value of 300 in 1990. This rapid decline in permanent fault FIT rates and technology scaling are expected to make soft errors very critical in sub-100-nm designs. In fact, soft-errors, if unmitigated, are expected to become the primary source of failures for sub-90 nm chips, causing a failure rate of 50,000 FITs, exceeding that of all other reliability mechanisms combined [12].

Figure 1.4. Permanent fault FIT rates for microprocessors, SRAMs, and DRAMs [11].

The impact of soft errors at the system level has been reported in diverse applications, ranging from satellites to sea-level computer systems, a few of which are summarized next. A detailed historical review of experiments done by *IBM* on radiation-induced soft fails and failures observed in memories due to soft errors, in the time period 1978-1994, is reported in [13]. This paper reports all the major memory suppliers of the time, such as *Intel*, *IBM*, and *Hitachi*, observing soft failures in their memories due to both alpha particles and cosmic rays. As early as 1978, evidence of sea-level soft fails on 16 Kb DRAMs, from alpha particles present in the memory packaging materials, was provided by May and Woods of *Intel* [14]. Similarly, in 1980, *Hitachi* announced that some of their bipolar RAMs failed under alpha-particle bombardment [13]. In addition, in 1981, *IBM* discovered reliability problems with their 16 Kb DRAM memory chips. *Sun Microsystems* also observed cosmic ray strikes on unprotected cache memories causing random crashes at major customer sites in its Enterprise server line [15].

In addition to the memory errors reported above, Fujitsu announced that they have protected 80% of the 200,000 latches in their fifth generation SPARC64 processor fabricated in 130 nm SOI CMOS [16]. Other logic errors in processors have been reported by iROC Technologies when they performed radiation testing on an 8-bit logic core processor called ROC-CR11 [7]. The processor was manufactured for French space agency CNES in 180-nm technology. During radiation testing, they observed eleven logic errors in the processor datapath.

The increase in logic SER not only affects high-performance microprocessors (HPMs), such as Pentiums, Opterons, SPARCs, and Power PCs used in worksta-

tions and enterprise servers, with core frequencies greater than 1 GHz and with more than 100 million transistors on-chip, but also embedded processors (such as those from ARM, MIPS Technologies, and Tensilica) used in consumer, automotive and networking applications [17]. The push for tackling soft errors in HPMs is due both to application factors and the large number of chip transistors. In the case of embedded processors, application factors, increase in the number of transistors per chip, and the number of chips used in a system (such as a mobile phone) are expected to play an important role in scaling the SER of these systems. For example, when a semiconductor vendor ships a million units of a product with 100 components in each product, the total FIT over the entire shipment would be hundreds of errors every few hours. The number of product recalls due to soft errors would lead to significant loss in the vendor's revenues and reputation.

#### 1.4 Our Contributions

In this dissertation, we address the following three important problems posed by the dramatic increase in logic SER: (1) modeling of SETs generated in CLBs, (2) efficient design techniques to reduce the SER of CLBs, and (3) analysis and design of soft-error hardened latches. These issues and how we have addressed them are briefly outlined and compared to previous work next.

#### 1.4.1 Logic Circuit SER Estimation

Tackling SER along with various conflicting nanometer objectives of power, performance, and area increases design cost, which has been identified as an important

factor with the potential to limit the semiconductor roadmap. Calculation of logic SER is essential to devise efficient SER mitigation techniques and can be used to optimize the different conflicting nanometer objectives, such as power, performance, and reliability. It can also be used to isolate and apply the design techniques to the most vulnerable circuitry.

The SER of SRAM caches can be calculated by determining the  $Q_{crit}$  of each cell from SPICE simulation and using it in Eqn. 1.1. However, estimating the critical charge of a combinational logic gate requires the width of the SET generated at a gate output. We describe a fast and accurate lookup-table (LUT) based methodology to calculate both SET width due to particle strikes and the SER reduction that can be obtained with time-redundancy based mitigation techniques. Previous techniques for SET width calculation use complex expressions or large LUTs and have greater than 15% error for inputs not close to pre-characterized points. We study the sensitivity of an SET to various gate and circuit characteristics and determine the parameters to be used, their spacing, and their lower and upper-bounds for constructing the LUT. The proposed LUT uses non-uniform spacing and surface-based interpolation between its indices to obtain the SET width generated at a gate and primary output. It provides more than 1000 times speedup over HSPICE simulations and has less than 10% error compared to existing techniques which have 15% or more error.

# 1.4.2 Efficient Soft-Error Mitigation Techniques for Combinational Logic

For memories, due to their regular array structures, efficient soft-error detection and correction techniques have been developed. Commonly used techniques in memories are error correcting codes or parity codes for detection. Using these techniques to protect combinational logic circuits requires high cost due to their irregular structure. Other techniques for logic soft-error protection, such as triple modular redundancy (TMR) and RE-computing with triplication and voting, rely on explicit spatial or temporal redundancy. However, most of these techniques suffer from significant short-comings such as: (1) they are meant primarily for error detection only; (2) they are applicable only to specific classes of circuits such as arithmetic units; and/or (3) they incur high power, performance, and area overheads. This necessitates an efficient design approach that would make logic circuits used in commodity as well as other applications soft-error resilient without adversely affecting other design considerations such as power and performance.

We propose an efficient and systematic error masking (EM) technique that can be applied to combinational logic circuits which have a significant fraction of non-critical primary outputs (POs) with sufficient slack. This error masking technique prevents an SET pulse of width less than approximately half of the slack available in the propagation path from latching and turning into a soft error, without any performance overhead. Previous techniques incur a performance overhead of 2W for masking an SET pulse of width W. We perform error masking only at PO flip-flops

with sufficient slack, which ensures that the delay increase caused by the addition of majority voter and control transistors to the flip-flops does not affect the timing of the circuit. Additionally, our technique uses a single delay chain to produce phase-shifted signals and sample POs of a CLB. The results obtained on ISCAS85 benchmark circuits show an average SER reduction of 82.67% from the original unprotected circuit.

For CLBs with a small fraction of non-critical POs, we proposed a method that supports error masking plus efficient error detection and recovery (EM+EDR). In this case, EM is applied to POs with sufficient slack and EDR to critical or near-critical POs. EM+EDR can tolerate SETs with width up to half the clock period and provides an average SER reduction of 93.78% on ISCAS85 circuits. When a soft error occurs, a very low-likelihood event for an application run, and is detected, EM+EDR recovers from it within a single clock cycle.

#### 1.4.3 Robust Delay Chain Construction

An important component of our EM and EM+EDR techniques is a delay chain used to generate phase-shifted clock signals for sampling POs. Delay chains are also used in a variety of other applications too. With technology scaling, sub-90 nm process technologies are introducing increasing variations in designs. This process variation leads to delay uncertainty. Therefore, delay chains need to be constructed with robust delay elements. We analyze three different families of delay elements in terms of their robustness to process variation, and then determine the appropriate delay

element for delay chain construction. The three different delay element families are:

(1) transmission gate based, (2) cascaded inverter based, and (3) voltage-controlled ones. We compare the delay element's effectiveness in terms of yield, which is defined as the number of circuits within the specified delay range. The delay variations are obtained through HSPICE Monte Carlo simulations and the delay sensitivity to different process and environmental variations are studied using simulation results. A design methodology used to construct a delay chain that produces control signals phase shifted from the system clock by every 200 ps is presented. Finally, construction of a buffer chain with least delay to distribute the phase shifted clock signals based on the logical effort method is explained. This work will help designers to construct robust delay elements and chains.

#### 1.4.4 Hardening of Latches for Soft Errors

Many different latch designs to prevent soft errors due to particle strikes on the latch nodes have been proposed. We analyze and compare these designs based on some existing and new metrics. This work will help designers to select latches for applications where soft errors are an important design metric. We also propose new latch designs, the best of which is vulnerable only to SEMUs with a delay overhead of 12% and power consumption of 70% compared to a standard transmission gate latch. The proposed latches can also be customized in accordance with application requirements for power consumption, performance, and soft-error resilience. In addition, some of the proposed latch designs can also be used to protect CLBs.

#### 1.5 Dissertation Outline

The remainder of the dissertation is organized as follows. Chapter 2 presents the LUT-based model for determining the width of SET generated at a gate output. The sensitivity of SET width to different circuit and striking particle's parameters are studied and then appropriate LUT indexes are determined. The lower and upper bound for each LUT parameter, and the number and interval between LUT indices are determined based on accuracy requirements. This chapter also explains interpolation performed within the LUT and the accuracy of the SET width estimated. The LUT-based model is further extended in chapter 3 and used to calculate the SER reduction obtained using the time-redundancy techniques presented in the next two chapters.

In the next three chapters, we present our work on soft-error mitigation of combinational logic circuits. In Chapter 3, we first review existing methods to mitigate soft errors in combinational logic circuits and their drawbacks. Then our error masking technique is explained and the SET width tolerated is determined. Finally, the methodology used to calculate the SER of the original and the error-masked circuits and results for SER reduction are presented. Next, Chapter 4 describes how the error masking technique can be improved by combining it with error detection and recovery in critical and near-critical paths. The pulse width tolerated using the EDR technique and the SER reduction obtained are calculated. Later, steps to improve the SER reduction obtained from the proposed error masking technique by increasing the slack available in the CLBs are presented: first, by exploiting critical path delay dependence upon the input vector and second, through slack redistribution in

pipelined circuits. Finally, Chapter 5 discusses construction of the delay chain used to generate phase-shifted clock signals for PO sampling in our EM and EM+EDR techniques. Robustness to process variation and power consumption of different delay elements are studied and guidelines for selecting appropriate delay elements for delay chain construction are given.

Chapter 6 analyses existing soft-error hardened latches and studies the trade-offs involved in using these latches to protect CLBs. Some new latch designs that are only SEMU vulnerable, and which can be customized based on application requirements are also presented.

Finally, Chapter 7 summarizes the important contributions of this dissertation and discusses directions for future research.

### CHAPTER 2

## Modeling and Analysis of Soft

## **Errors in Logic Circuits**

Soft error rate estimation of logic circuits requires accurate and efficient estimation of electrical, logical, and temporal masking effects. To evaluate the electrical masking of a path, the amplitude and duration (AD) of an SET generated at a gate output, due to a particle strike, needs to be calculated. Here, amplitude refers to peak voltage, and duration is the width of SET measured at  $V_{\rm DD}/2$ . The width and amplitude of an SET, for a specific charge collected, depends on gate drive strength, output load capacitance, supply voltage, and shape of the current waveform. For an SET with amplitude greater than  $V_{\rm DD}/2$ , the duration of the pulse determines the SET width during propagation. Hence, for all SETs which reach a voltage greater than  $V_{\rm DD}/2$ , we approximate the amplitude to be  $V_{\rm DD}$ . Further, this approximation yields the minimum charge that can cause a soft error. In this chapter, a methodology to calculate the SET width as a function of the charge collected at a gate output is

proposed. In Chapter 3, we extend this methodology, to take into account electrical masking, for calculating the SET width at the output of a path. The extension helps to calculate the worst-case width of the SET reaching a PO. Once the SET width at a gate output is known, other masking effects can be calculated as follows. (1) Commercial noise simulators such as Pacific [18] can be used to characterize electrical masking and get the nominal SET width at a PO. (2) The logical masking probability can be calculated through gate-level simulations of the circuit as described in [19]. (3) The temporal masking probability can be calculated using analytical expressions presented in Chapter 3. As all these tasks are well understood, here we just focus on calculation of SET width at a gate output.

Both lookup table (LUT) based approaches and closed form expressions for the shape of the SET pulse have been presented recently. A closed form expression for the output voltage of a gate  $V_{out}(t)$  due to charge collection was presented in [20].

$$V_{out}(t) = \frac{Q}{T \times C_L} \times e^{(-t/\tau)} \left( \frac{e^{(t/\tau)} \cdot e^{(-t/T)} \Big|_0^t}{1/\tau - 1/T} \right), \tag{2.1}$$

Where T is the time constant of charge collection, Q is charge collected,  $C_L$  is the load capacitance,  $\tau = f(Q, C_L)$ , gate size is a time constant of the gate, and f is a function obtained by doing linear regression on a table of  $\tau$  values indexed using  $Q, C_L$ , and gate size. This leads to a complex expression for calculating  $V_{out}(t)$ , and the error for points not close to the table index have been reported to be more than 15% [20]. A uniform LUT was used for determining the width of the SET at a gate output in [21]. The LUT was constructed for different gate types, fan-ins, sizes, channel lengths,

supply voltages, threshold voltages, load capacitances, and for a particular charge collected at the gate output. Our experiments on the sensitivity of SET width show that it varies non-linearly with increasing gate sizes and load capacitances. As the SET width varies non-linearly for some parameters, the distance between the LUT indices needs to be non-uniform (and hence the interpolation for points not close to LUT index needs to be non-linear), which has not been considered in [21]. Moreover, constructing a single LUT for many different parameters results in a big LUT size and leads to a significant loss of accuracy during LUT interpolation. In addition, constructing a LUT for power supply variation leads to a large number of points in the LUT, which is handled through regression in our methodology.

The sensitivity of SET width to gate drive strength, output capacitance, and the charge collected around a gate's output is first studied through HSPICE simulations. Based on the sensitivity of SET width to different parameters, we determine the LUT indices and the interval between them. Additionally, the lower and upper bound for each LUT parameter and, the number and interval between each LUT index are determined based on accuracy requirements. The accuracy of the LUT and the time required for interpolation within the LUT are measured, and compared with HSPICE simulation.

## 2.1 Simulation Setup

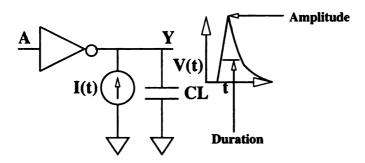

The simulation setup for studying the sensitivity is shown in Figure 2.1.  $C_L$  is the total load capacitance at a gate output, and is equal to the sum of fanout gate capacitance and lumped wire capacitance driven by the gate. The current source

Figure 2.1. Circuit setup used to measure the sensitivity of SET width to various parameters.

connected to the gate output models the current flowing across the P-N junction due to charge collection. The direction of the current source for a  $0\rightarrow 1$  output flip (charge collection around a PMOS drain) is as shown in Figure 2.1, while it is reversed for a  $1\rightarrow 0$  flip (charge collection around a NMOS drain). The current source is modeled by a single time constant and is given by equation 2.2 [22]:

$$I(t) = \frac{2Q}{T\sqrt{\pi}}\sqrt{\frac{t}{T}}e^{(\frac{-t}{T})},\tag{2.2}$$

where Q is the charge collected at a gate output and T is the charge collection time constant. The time constant T depends on the technology and if the drain is P or N-type. It is a measure of how fast the electrons recombine in the drain node. The current has sharp rise time, which models the drift mechanism through which the minority carriers are swept across the P-N junction, and it reaches its maximum value at T/2. The fall time is more gradual, due to the diffusion of carriers across the P-N junction and is determined by the exponential term with time constant T.

The value of T for different CMOS technologies was determined through device

Figure 2.2. Junction current waveform for different time constants.

simulations and tabulated in [3]. We determine the value of the time constant for TSMC 180 nm, which is the technology used in our experiments, by scaling the time constant values given in [3]. The values used for the P and N-type drain time constants are 45.2 and 46.4 ps, respectively. The shape of the current waveform for different values of T is shown in Figure 2.2. As can be seen from Figure 2.2, for smaller T peak value of I(t) is higher, and current decreases rapidly leading to a smaller current pulse width. Higher peak value of I(t) results in lower  $Q_{\rm crit}$ , and the smaller current pulse width leads to faster gate output recovery and hence smaller SET width. If the exact value of T for a specific technology is not known, then the LUT can be characterized for different T values. Later, the LUT can be indexed with the time constant for which  $Q_{\rm crit}$  is being calculated.

Figure 2.3. Current waveform constructed using values from Eq. 2.2, PWL model with 15 points, and exponential HSPICE model for Q=200 fC.

# 2.1.1 HSPICE Modeling of I(t)

The current waveform in Eq. 2.2 can be modeled as a piece-wise linear (PWL) or exponential current source in HSPICE. I(t) values for a PWL model with 15 points, and an exponential model from HSPICE were compared to the values computed from Eq. 2.2. The experiments were repeated for two different charges Q=100 and Q=200 fC. The current waveforms for Q=200 fC using the PWL, exponential model, and values from Eq. 2.2 are shown in Figure 2.3.

The percentage error for both the PWL and the exponential model was calculated as follows:

$$Error(\%) = \frac{\left|I(t) - I(t)_{PWL \text{ or } EXP.}\right|}{I(t)} \times 100. \tag{2.3}$$

The maximum error for PWL and exponential models between t=0 and 50 ps is given in Table 2.1. Error is only measured between t=0 and 50 ps, as the value of current, after t=50 ps, falls to less than 70% of peak value of I(t). The maximum error for the PWL model with 15 points was found to be just 1.7% as compared to 117% for the exponential model. Hence, the PWL model is used for modeling the current across P-N junction, due to charge collection, in HSPICE.

|                 | Q=200 fC | Q=295 fC |

|-----------------|----------|----------|

| PWL (%)         | 1.34     | 1.7      |

| Exponential (%) | 100      | 117      |

Table 2.1. Percentage error for both PWL and exponential current sources.

## 2.2 Sensitivity of SET Width

In this section, the sensitivity of SET width to different gate characteristics is studied. The indices of the LUT are determined based on the sensitivity studies.

# 2.2.1 Gate Inputs

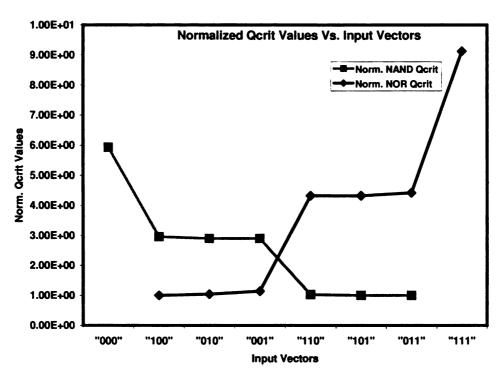

The critical charge required to cause a  $1\rightarrow 0$  or a  $0\rightarrow 1$  flip depends on the input vector applied to the gate. Figure 2.4 shows the normalized  $Q_{crit}$  for different input vectors in a three input NAND and NOR gate, respectively. As can be seen from the Figure 2.4, the  $Q_{crit}$  considering only the  $1\rightarrow 0$  flip at the output of NAND3 gate varies by six times. This is due to two reasons: (1) The strength of the pull-up or pull-down network that is ON, which determines how fast the deposited charge is dissipated by the gate. (2) If the top transistor in a stack is conducting. When the top transistor is ON, the effective output capacitance is equal to sum of actual output

Figure 2.4.  $Q_{crit}$  of a NAND3 gate for a  $1\rightarrow 0$  flip, and a NOR3 gate for a  $0\rightarrow 1$  flip, normalized with respect to the minimum  $Q_{crit}$  among the input vectors considered.

node capacitance and the capacitances at the internal nodes. The larger capacitance increases the charge required to generate an SET, which means the SER of the input vectors - "101", "110", "100" - are much lower compared to other inputs.

# 2.2.2 Output Load Capacitance

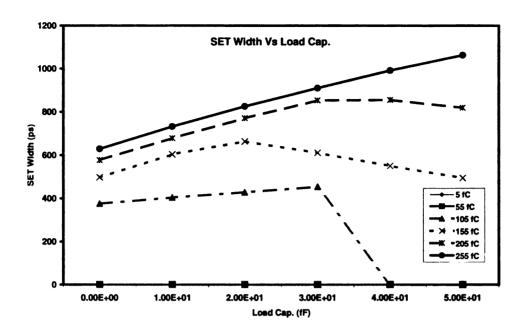

The initial charge stored at a gate output node is equal to the load capacitance  $(C_L)$  times the supply voltage  $(V_{DD})$ . The effect of the load capacitance on SET width is shown in Figure 2.5. Increasing  $C_L$ , increases SET width for a particular charge Q. However,  $C_L$  also determines if Q results in an SET with amplitude greater than  $V_{DD}/2$ . For example, this can be seen from the plot for Q=105 fC, where SET width falls to zero when  $C_L$  increases from  $30\rightarrow 40$  fF. This shows that the effect of  $C_L$  on

Figure 2.5. The width of SET measured at an inverter output for different charges, when the output load capacitance is varied from 0 to 50 fC.

SET width to be highly non-linear.

# 2.2.3 Charge Collected

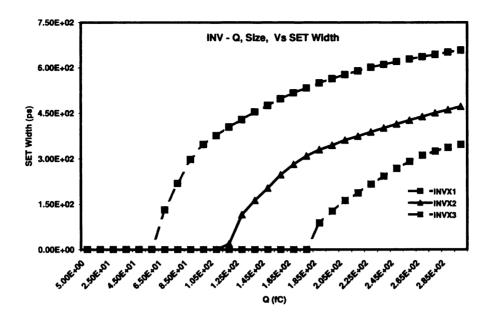

The generation of SET depends on the charge collected around the P-N junction of a drain node. The minimum or threshold charge  $(Q_{\rm th})$ , defined as charge required to produce an SET whose amplitude exceeds  $V_{\rm DD}/2$ , depends on the gate drive strength and load capacitance. Once the charge collected exceeds  $Q_{\rm th}$ , the SET width increases non-linearly with increasing Q. This can be seen from Figure 2.6, which shows the SET width as a function of increasing Q. For example, in the case of INVX1, SET width increases from zero to 600 ps when Q increases from  $0\rightarrow 295$  fC.

Figure 2.6. The width of SET measured for different drive strengths of an inverter when charge Q varies form  $0\rightarrow300$  fC.

#### 2.2.4 Gate Size

The gate size or drive strength determines the  $Q_{\rm th}$  required to generate an SET of width W. The drive strength determines how quickly the charge collected around the P-N junction is dissipated. Higher drive strength gates have higher output capacitances, which also increase  $Q_{th}$ . The effect of different drive strengths on the SET width can be seen from Figure 2.6, which plots the SET width for increasing Q at the output of an inverter. For example,  $Q_{th}$  increases from 60 to 180 fC when the drive strength of an inverter increases from  $1X \rightarrow 3X$ . In addition, the maximum SET width reduces from approximately  $600 \rightarrow 300$  ps when the inverter strength increases from  $1X \rightarrow 3X$ . The drive strength has a bigger and non-linear impact on the scaling of  $Q_{th}$  and SET width than  $C_L$  and Q, due to which it is not used as an LUT index.

#### 2.3 Lookup Table

A two-dimensional LUT was constructed with output load capacitance and the critical charge as indices, for different gates. We first determine the lower and upper bound for the parameters in the LUT, and then find the number of points to be used for less than 10% error in SET width looked up. The lower and upper bound of  $C_L$  is determined by the minimum and maximum load values driven by the gates in the design. In the case of synthesized designs, this value can be determined from the standard-cell library models for delays. For our experiments, we bound the load capacitance of a gate to  $0{\to}4{\times}C_g$ , where  $C_g$  is the gate input capacitance. The maximum charge collected around a P-N junction is determined as follows. The magnitude of the charge collected around a P-N junction depends on the energy of the particle passing through the silicon substrate, as well as the path length over which the charge is collected. The energy of ionizing particles is measured by the metric linear energy transfer (LET), which is the energy per unit mass per unit area transferred from an ionizing particle to the material through which it passes, expressed in MeV-cm<sup>2</sup>/mg. It has been estimated that 1 MeV-cm<sup>2</sup>/mg of neutrons deposit 10.8  $fC/\mu m$  of charge [23]. The flux of particles decreases exponentially with increasing LET, and there are far fewer particles with LET > 15 MeV-cm<sup>2</sup>/mg [24]. Therefore, the maximum LET of ionizing particles considered is 15 MeV-cm<sup>2</sup>/mg. The length over which the charge is collected depends on the technology and is approximated to be 2 microns for TSMC 180 nm technology [23]. Therefore, the maximum charge collected is approximated to be 300 fC (= 15 MeV-cm<sup>2</sup>/mg \* 10 fC/ $\mu$ m \* 2  $\mu$ m), and

the minimum charge is 0 fC.

Once the lower and upper bound for the parameters were determined, the initial LUT was created by choosing six and thirty points for Q and  $C_L$ , respectively. The actual points were uniformly spaced apart within the lower and upper bound mentioned above. For each gate, the total number of points in the LUT were 180 and hence an equal number of HSPICE simulations were done. In each HSPICE run, the SET width for a particular Q and  $C_L$  was recorded. Surface described by three co-ordinates X, Y, and Z corresponding to Q,  $C_L$ , and SET width, respectively, is used to do interpolation when the LUT is indexed with Q and  $C_L$  not in the LUT. The SET width is obtained by solving equation 2.4.

$$Z = \alpha + \beta X + \gamma Y + \delta XY \tag{2.4}$$

The value of the co-efficients were obtained by solving four such equations using gaussian elimination. The four equations correspond to four neighboring points shown in Figure 2.7.

# 2.4 Accuracy of the LUT Model

The accuracy of the LUT model was tested using  $C_L$  and Q located in the middle of the LUT indexes as shown in Figure 2.7. The SET width from the LUT table was compared to that of HSPICE simulations. The percentage error in the LUT interpolation was calculated as follows:

$$Error(\%) = \left(\frac{|(LUT\ value - Spice\ result)|}{LUT\ value}\right) * 100$$

(2.5)

Figure 2.7. Surface described by three co-ordinates X, Y, and Z corresponding to Q,  $C_L$ , and SET width. Q and  $C_L$  values in the middle of LUT indices are used to test the accuracy of the LUT. The figure shows the neighboring points and the surface formed by them, when the LUT is indexed using Q = 10 fC and  $C_L = 25$  fF.

The percentage error for Q values closer to  $Q_{th}$ , where the maximum error occurs, are shown in Table 2.2.

| $C_L$ | Q    | Max. Error (%) |         |  |  |

|-------|------|----------------|---------|--|--|

| (fF)  | (fC) |                |         |  |  |

|       |      | Uniform        | Non-    |  |  |

|       |      |                | Uniform |  |  |

| 5     | 80   | 2.31           | 1.05    |  |  |

| 15    | 90   | 7.05           | 4.3     |  |  |

| 25    | 100  | 17.02          | 9.18    |  |  |

| 35    | 110  | 10.14          | 6.45    |  |  |

| 45    | 120  | 15.37          | 8.6     |  |  |

Table 2.2. Percentage error for interpolation from a LUT with both uniform and non-uniform interval between indices.

The width of an SET changed significantly for values of Q near  $Q_{\rm th}$ , which led to the

LUT interpolation producing errors greater than desired 10%. The accuracy can be improved by increasing the number of points in the LUT. For example, increasing the number of points for Q to forty would improve accuracy, but with a huge increase in LUT size. To reduce the error and to keep the complexity of the LUT within bounds, it was decided to use non-uniform spacing between charges, instead of increasing the number of points and maintaining an uniform interval between charges. The spacing between charges from  $60\rightarrow120$  fC was reduced to 5 fC, while maintaining 10 fC spacing for other charges. The percentage error for the new LUT is also given in Table 2.2, in the column titled non-uniform spacing. The time taken to interpolate and lookup the SET width was found to be 12 ms for 1000 points, while it takes 3 hours for the same in HSPICE simulations. The model offers a speed-up of > 1000x compared to HSPICE simulations.

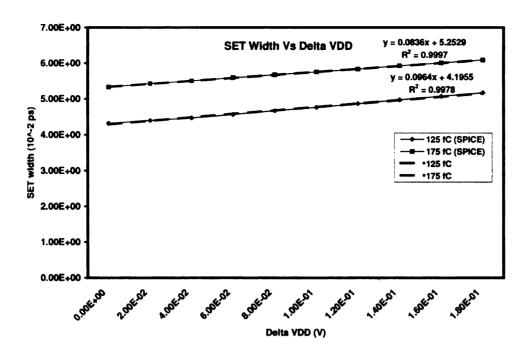

## 2.5 Regression for Supply Voltage Variation

Power supply variation also causes the SET width to change. The SET width for a 10% variation in  $V_{\rm DD}$  is shown in Figure 2.8. As can be seen, the SET width varies linearly over  $\pm 10\%$  range. We tried linear regression over this small range and found that it gave a good fit. The R<sup>2</sup> value was found to be 0.99 for both Q=125 fC and 175 fC. The straight line equation shown in Figure 2.8 can be used to scale the characterized SET width while operating voltage varies by 10%. This avoids costly HSPICE simulations required for re-characterizing the LUT for variations in supply voltages.

Figure 2.8. Variation of SET width for supply voltage perturbation of  $\pm 10\%$  from the nominal value of 1.8 V.

#### 2.6 Conclusion

In this chapter, we first analysed the sensitivity of SET width to gate drive strength, output load and charge collected at the gate output. A LUT, which is indexed using output load and charge Q, was proposed to calculate the SET width. The variation in the SET width for increasing Q is non-linear. Hence, spacing between Q values was varied to improve the accuracy of LUT. The error from the LUT interpolation was found to be less than 10%. A regression based model for scaling SET width due to  $V_{\rm DD}$  variation was also presented. Further in Chapter 3, this LUT is extended to interpolate for SET width occurring in different points of a path.

# CHAPTER 3

# Error Masking for SER Mitigation