# This is to certify that the dissertation entitled

# MULTILEVEL INVERTERS AND THEIR APPLICATIONS IN POWER SYSTEM

presented by

Jin Wang

has been accepted towards fulfillment of the requirements for the

Doctoral degree in Electric Engineering

Major Professor's Signature

Aug. 26, 2005

Date

MSU is an Affirmative Action/Equal Opportunity Institution

LIBRARY Micnigan State University

# PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due. MAY BE RECALLED with earlier due date if requested.

| DATE DUE     | DATE DUE | DATE DUE |

|--------------|----------|----------|

| JUN 1 9 2007 |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

|              |          |          |

2/05 p:/CIRC/DateDue.indd-p.1

# MULTILEVEL INVERTERS AND THEIR APPLICATIONS IN POWER SYSTEM

BY

Jin Wang

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

**DOCTOR OF PHILOSOPHY**

Department of Electrical and Computer Engineering

#### **ABSTRACT**

Multilevel Inverters and their Applications in Power Systems

by

#### Jin Wang

A power system composes three interconnected subsystems: generation, transmission, and distribution. With the ongoing expansion and deregulation, there are also three major trends to reform the power systems: 1) to utilize distributed generation (DG) to meet the increasing power demands; 2) to utilize Flexible AC Transmission devices (FACTs) to improve the transmission and distribution systems; and 3) to utilize Custom Power devices to improve the power quality to the end users at the distribution level.

Power electronics inverters are enabling parts of DG and core parts of FACTs and Custom Power devices. In the power electronics inverter family, multilevel inverters are the newest breed. Compared with other inverters, multilevel inverters have two distinguished features that make them more suitable for the aforementioned power system applications: 1) the multilevel structures enable the utilization of low voltage rating power semiconductor devices in high voltage applications; 2) and the almost near sinusoidal output voltage waveforms from the multilevel inverters make it

possible to eliminate the output filters and zigzag transformers, which are often connected after traditional inverters. Three major issues involved with multilevel inverters in power systems are DC bank voltage maintenance, balance of DC banks, and harmonics optimization of the inverters' output voltage.

This dissertation first summarizes the previous works on FACTs, Custom Power, DG and multilevel inverters, and discusses the major application issues for cascade multilevel inverters. A new harmonics elimination method for multilevel inverters is proposed. Then, in the main part of the dissertation, two applications of cascade multilevel inverters in FACTs devices — a new Unified Power Flow Controller (UPFC) and a Universal Static Synchronous Compensator (U-STATCOM) — are proposed. Unlike conventional UPFC, in the proposed UPFC, cascade multilevel inverters can be used without compromising power flow controllability. proposed U-STATCOM can be used to compensate not only reactive power and harmonics but also load current imbalance. The circuit structures, control methods. comparisons with conventional solutions, and simulation results are shown for both cases. Furthermore, new applications of multilevel inverters in Custom Power and DG are presented as the extended applications of cascade multilevel inverters in power systems.

In the end, the realization of the control unit for a seventeen level cascade multilevel inverter is described. Experimental results based on the inverter are shown to prove the validity of proposed harmonics elimination method.

To my mother, father, and wife

## **ACKNOWLEDGEMENTS**

Foremost, I would like to acknowledge all the invaluable help from my advisor, Dr. Fang. Z. Peng, without whom this work would not have been possible. This dissertation comes from numerous discussions with him, from his keen insight and guidance in a fruitful research area. I would like to thank all my committee members, Dr. Schlueter, Dr. Strangas, and Dr. MacCluer. Their insightful comments and suggestions have enhanced the technical soundness of this dissertation. I am grateful to my friends and colleagues from the Power Electronics and Motor Drive Laboratory. Not only the knowledge, but also the research experience and friendship I gained here will be beneficial for the rest of my life. I would like to express my great appreciation to Mr. Zhiguo Pan, Mr. Alan Joseph, and Mr. Eduardo I. Ortiz for the assistance in the tests of cascade multilevel inverter, and Mr. Joel Anderson for helping revising my dissertation.

My thanks go to my family, especially my wife and my parents. Without their years of encouragement and continuous support, I would not have reached this point.

# **TABLE OF CONTENT**

| I. INTRODUCTION                                                           | 1  |

|---------------------------------------------------------------------------|----|

| 1. 1. Background                                                          | 1  |

| 1. 2. Flexible AC Transmission Systems                                    | 3  |

| 1. 3. Custom Power                                                        | 4  |

| 1. 4. Distributed Generation                                              | 5  |

| 1. 5. Multilevel Inverters                                                | 7  |

| 1. 6. Outline of the Dissertation                                         | 9  |

| II. SUMMARY OF PREVIOUS WORKS                                             | 12 |

| 2. 1. Introduction                                                        | 12 |

| 2. 2. FACTs Devices                                                       |    |

| 2. 2. 1 Structures and Functions of FACTs      2. 2. 2 History and Trends |    |

| 2. 2. Custom Power Devices                                                |    |

| 2. 3. Distributed Generation [126-138]                                    |    |

| 2. 4. Multilevel Inverters                                                |    |

| 2. 4. 1. Diode Clamped Inverter [13-23]                                   |    |

| 2. 4. 2. Flying Capacitor Multilevel Inverter [24-30]                     | 29 |

| 2. 4. 3. Cascade Multilevel Inverter [31-42]                              |    |

| 2. 5. Applications of Multilevel Inverters in Power System                |    |

| 2. 6. Summary                                                             | 36 |

| III. REAL APPLICATION ISSUES OF MULTILEVEL INVERTERS                      | 37 |

| 3. 1. Introduction                                                        | 37 |

| 3. 2. DC Bank Voltage Maintenance and Balance                             | 38 |

| 3. 2. 1. DC Bank Voltage Maintenance                                      |    |

| 3. 2. 2. Balance of DC Bank Voltages                                      |    |

| 3. 3. Harmonics Elimination                                               |    |

| 3. 3. 2. Proposed Harmonics Elimination Method                            |    |

| 3. 4. Summary                                                             | 55 |

| IV. A NOVEL UPFC WITH CASCADE MULTILEVEL INVERTER                         | 56 |

| 4. 1. Introduction                                                        | 56 |

| 4. 2. The Conventional UPFC                                               | 57 |

| 4. 3. Two Problems of the Conventional Configuration         | 61       |

|--------------------------------------------------------------|----------|

| 4. 3. 2. The Problem with Cascade Multilevel Inverter        |          |

| 4. 4. The Proposed Configuration                             | 65       |

| 4. 5. Comparison of the New and Conventional Configurations  | 70       |

| 4. 7. Simulation Results                                     | 84       |

| 4. 8. Summary                                                | 86       |

| V. DELTA-CONNECTED UNIVERSAL STATCOM                         | 87       |

| 5. 1. Introduction                                           | 87       |

| 5. 2. The Circuit Candidates of STATCOM                      | 88       |

| 5. 3. The Proposed U-STATCOM                                 | 91       |

| 5. 3. 1. Proposed U-STATCOM                                  |          |

| 5. 3. 2. The compensation theory [91]                        |          |

| 5. 4. Control Scheme and Reference Current Detection         | 94       |

| 5. 4. Simulation Results                                     | 98       |

| 5. 5. Summary                                                | 101      |

| VI. EXTENDED APPLICATIONS OF MULTILEVEL INVERTERS            | 102      |

| 6. 1. Introduction                                           | 102      |

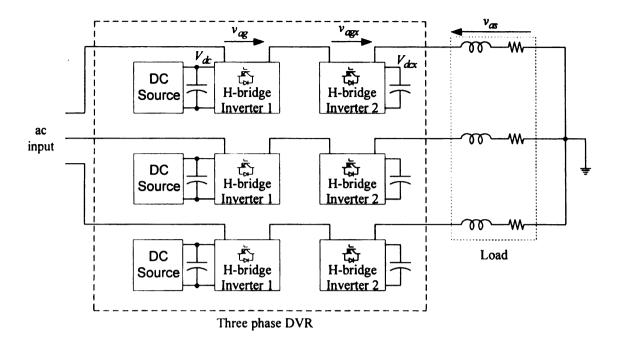

| 6. 2. DVR Circuits                                           | 102      |

| 6. 3. Proposed DVR Circuit.                                  | 104      |

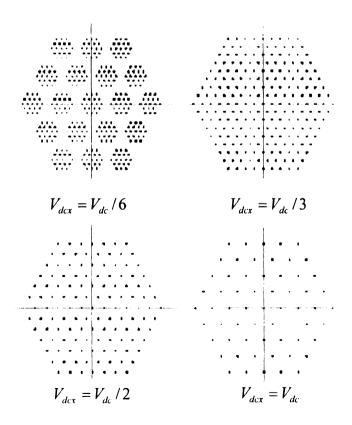

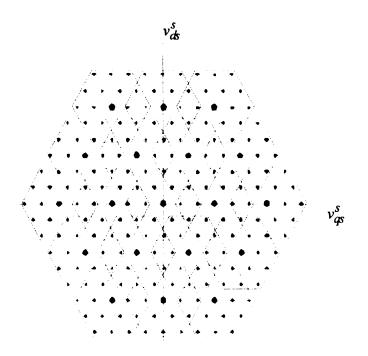

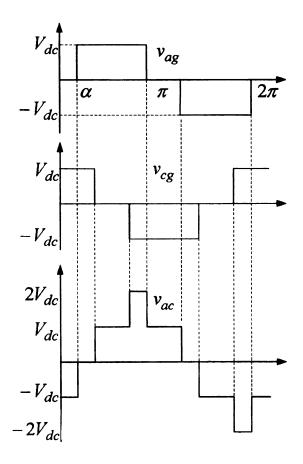

| 6. 3. 1. The Theory of Two Non-identical Inverter in Cascade | 104      |

| 6. 3. 2 Control of Proposed DVR System                       |          |

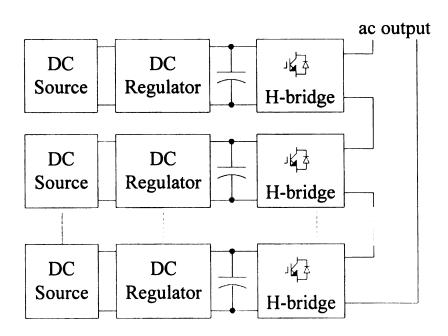

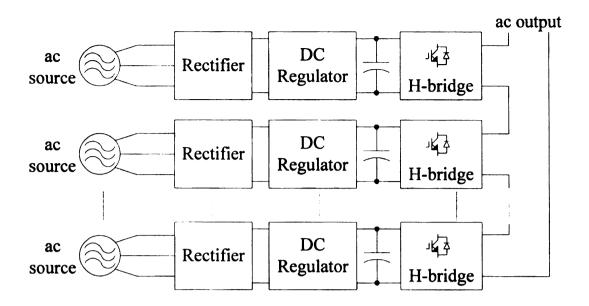

| 6. 4. Applications of Cascade Multilevel Inverters in DG     |          |

| 6. 4. 1. Proposed Applications Examples                      |          |

| 6. 4. 2 DC-DC Circuit Selection                              |          |

| 6. 4. 4 Experimental Verification                            |          |

| 6. 5. Summary                                                |          |

| VII. A 17 LEVEL CASCADE MULTILEVEL INVERTER AND EXPE         | RIMFNTAI |

| RESULTS                                                      |          |

| 7. 1. Introduction                                           |          |

| 7. 2. The 17 Level Cascade Multilevel Inverter               | 130      |

| 7. 3. The Realization of the Control Unit                    | 132      |

| 7. 3. 1. Hardware of the Control Unit                        |          |

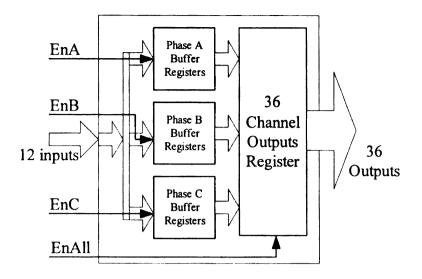

| 7. 3. 2. Control Signal Generation                           | 135      |

| 7 3 3 Inverter Module Voltage Ralancing                      | 140      |

| 7. 3. 4. Fault Protection Scheme      | 141 |

|---------------------------------------|-----|

| 7. 4. The Experimental Results        | 145 |

| 7. 4. Summary                         |     |

| VIII. CONCLUSIONS                     | 149 |

| 8. 1. Conclusions                     |     |

| 8. 2. Contributions                   | 151 |

| 8. 3. Recommendations for Future Work | 153 |

2.1: Su

2.2: Th

23: Ti

3.1: S

4.1: P

6.1: T

6.2: T

7.1: ]

7.2: ]

# LIST OF TABLES

| 2.1: Summary of FACTs Configurations                                   | 18  |

|------------------------------------------------------------------------|-----|

| 2.2: The DGs and their interface to grid                               | 25  |

| 2.3: The feasible applications of multilevel inverters in power system | 35  |

| 3.1: Switching angles examples                                         | 51  |

| 4.1: Part of the simulation results of the new configuration           | 85  |

| 6.1: The efficiency comparison                                         | 126 |

| 6.2: The summary of the comparisons                                    | 127 |

| 7.1: The gate drive CPLD decoding table                                | 140 |

| 7.2: The switching angles for MI=0.84                                  | 145 |

# **LIST OF FIGURES**

| 1.1: The two bus power system diagram                                 |

|-----------------------------------------------------------------------|

| 1.2: The nine level waveform                                          |

| 2.1: The VSI structure                                                |

| 2.2: STATCOM Configuration                                            |

| 2.3: SSSC configuration                                               |

| 2.4: UPFC Configuration                                               |

| 2.5: IPFC configuration. 17                                           |

| 2.6: BTB DC Link configuration.                                       |

| 2.7: The installation of FACTs devices in United States               |

| 2.8: The basic Online-UPS system.                                     |

| 2.9: The DVR structure                                                |

| 2.10: The six level diode clamped inverter and its line-line waveform |

| 2.11: The 6 level flying capacitor multilevel inverter                |

| 2.12: 11 level cascade multilevel inverter                            |

| 2.13: The phase voltage of an 11 level cascade multilevel inverter    |

| 3.1: The DC bank voltage maintenance for shunt connected inverter     |

| 3.2: Example of real power flow in UPFC                               |

| 3.3: 11 level voltage waveform and general current waveform           |

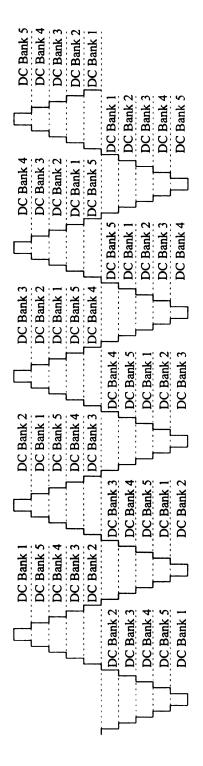

| 3.4: Rotation for DC bank balancing                                   |

| 3.5: 11 level voltage waveform and equal area criteria                |

| 4.1: Conventional circuit configuration of UPFC                       |

| 4.2: Basic UPFC control function                                      |

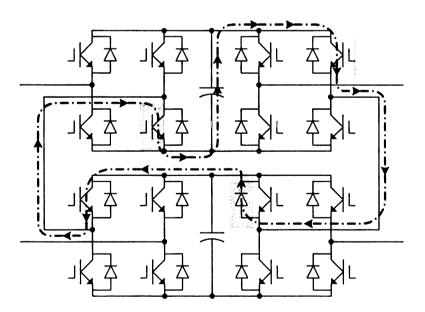

| 4.3: The 48 pulse inverter                                            |

| 4.4: The short connection when cascade multilevel inverters are connected back-to-                                          |        |

|-----------------------------------------------------------------------------------------------------------------------------|--------|

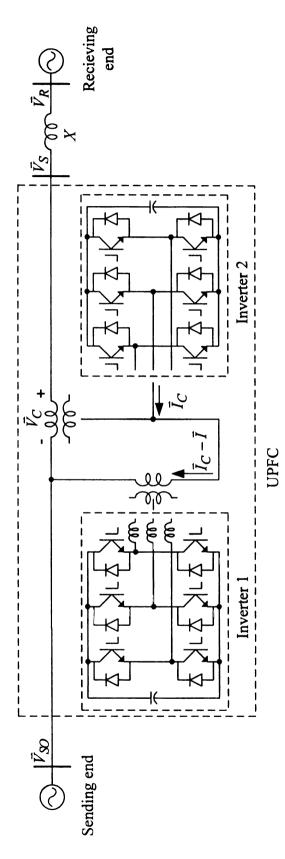

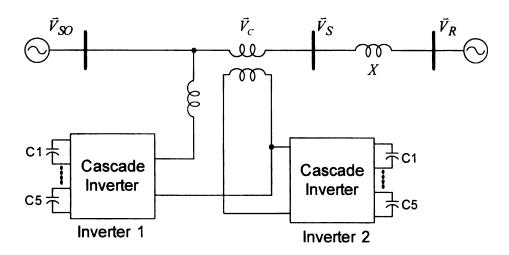

| 4.5: The proposed circuit configuration of UPFC                                                                             |        |

| 4.6: The proposed UPFC with cascaded multilevel inverter.                                                                   | 67     |

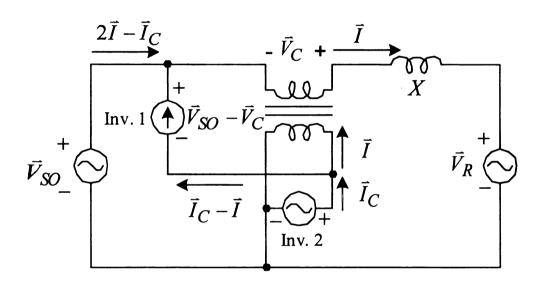

| 4.7: The equivalent circuit of UPFC.                                                                                        | 68     |

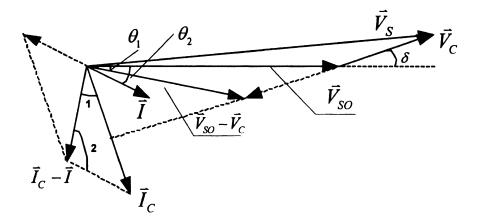

| 4.8: The relationship between $\vec{V}_C$ and $\bar{I}_C$                                                                   | 69     |

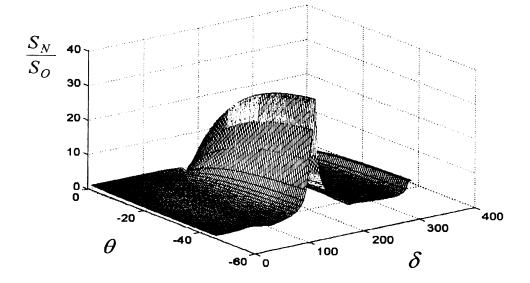

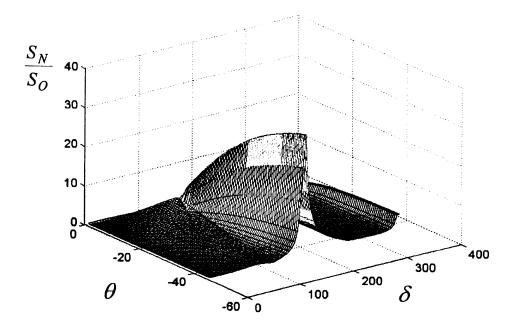

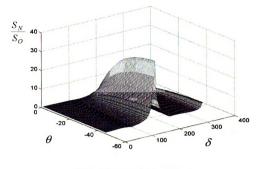

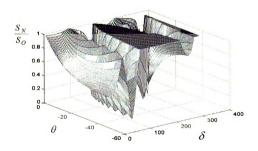

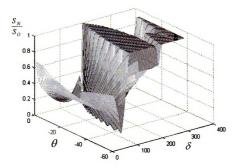

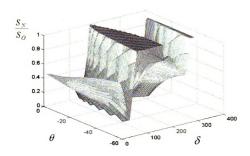

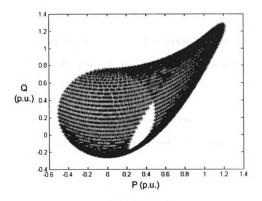

| 4.9: The full view of total VA rating between the new and conventional configuration                                        | ion 73 |

| 4.10: The ratio of total VA rating between the new and conventional UPFC config                                             |        |

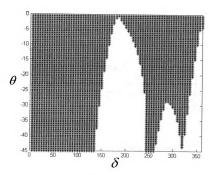

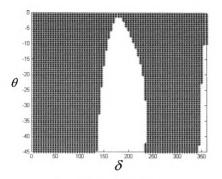

| 4.11: The $\theta - \delta$ projects of the Figure 4. 9.                                                                    | 77     |

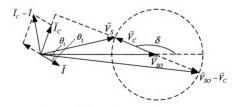

| 4.12: The vector diagram of the system.                                                                                     | 77     |

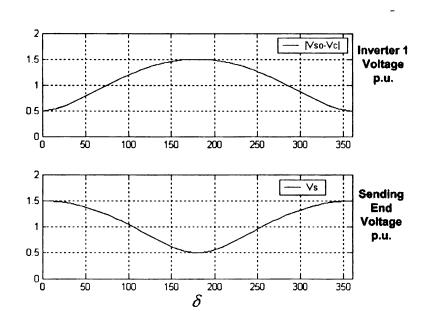

| 4.13. The relationship between inverter voltages and $\delta$                                                               | 78     |

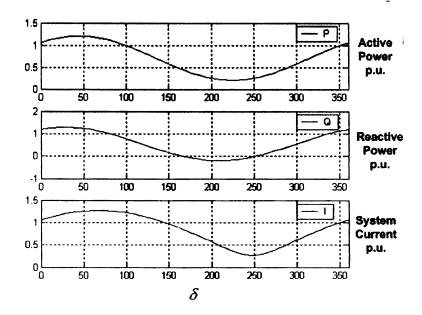

| 4.14: The active power, reactive power and receiving end line current when $\theta = \delta$ changes from 0° to 360°        |        |

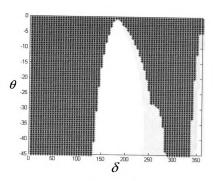

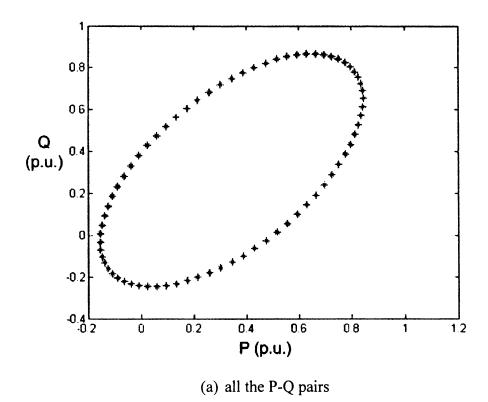

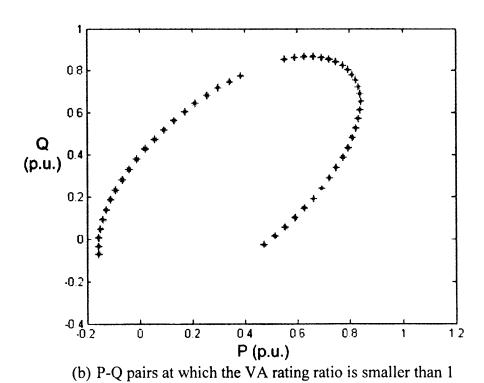

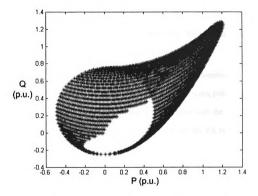

| 4.15: The P-Q pairs when $\theta = -25^{\circ}$ , $V_C = 0.5$ p.u. and $\delta$ rotates from $0^{\circ}$ to $360^{\circ}$ . | 80     |

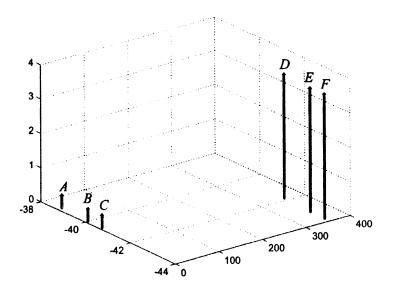

| 4.16: The P-Q pairs when $\theta$ changes 0° to -45°, $V_C = 0.5$ p.u. and $\delta$ rotates from 359.4°.                    |        |

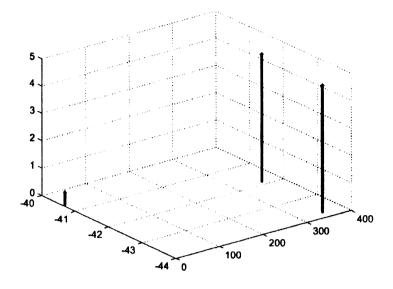

| 4.17: Operating points that have the same power but different VA rating ratio                                               | 84     |

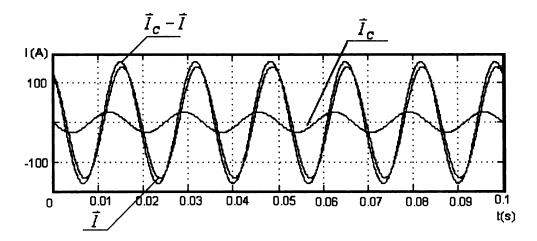

| 4.18: Currents through both inverts and the line in the new configuration                                                   | 85     |

| 5.1: The system configuration of wye connected STATCOM.                                                                     | 89     |

| 5.2: The imbalance compensation with wye structure.                                                                         | 90     |

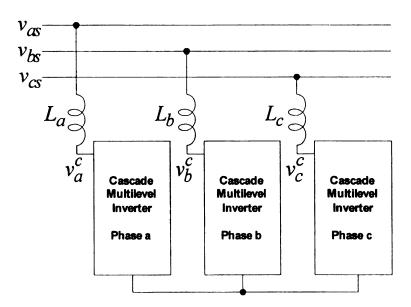

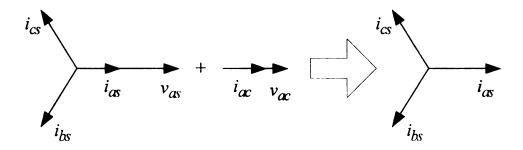

| 5.3: The U-STATCOM structure and one phase voltage waveform                                                                 | 92     |

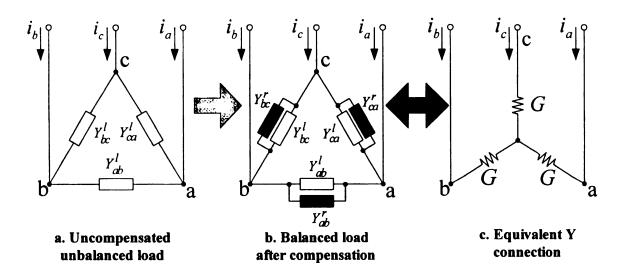

| 5.4: The general three-phase compensationnetwork                                                                            | 93     |

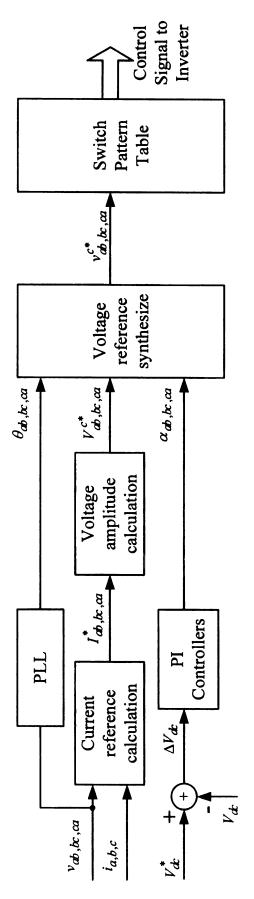

| 5.5: Control diagram                                                                                                        | 96     |

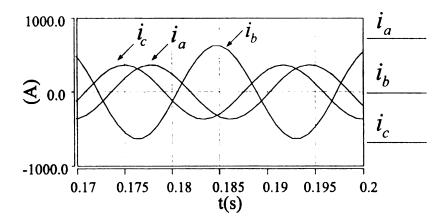

| 5.6: The uncompensated system current.                                                                                      | 99     |

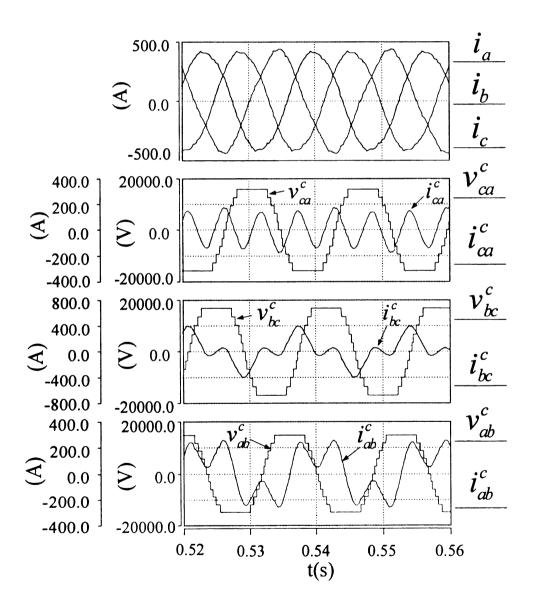

| 5.7: The compensated system current and inverter voltages and currents                                                      | 100    |

6.1: The c

6.2: The p

6.3: Casc

6.4: The

6.5: The

6.6: Cor

6.7: The

6.8: The

6.9: The

6.10: T

6.11: T

6.12: T

6.13: 1

6.14: ]

6.15: 7

7.1: T

7.2: T

7.3: T

7.4: P

7.5: T

7.6: 1

7.7

7.8:

7.9

7.14

| 6.1: The cascade multilevel inverter based DVR                                    | 103   |

|-----------------------------------------------------------------------------------|-------|

| 6.2: The proposed DVR system.                                                     | 105   |

| 6.3: Cascade 3/3 vector plots.                                                    | 107   |

| 6.4: The vector plots of maximal distention.                                      | 108   |

| 6.5: The staircase control of the bulk inverter (Inverter 1)                      | 109   |

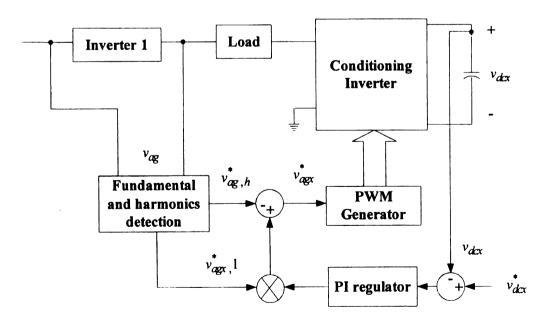

| 6.6: Conditioning inverter control diagram                                        | 110   |

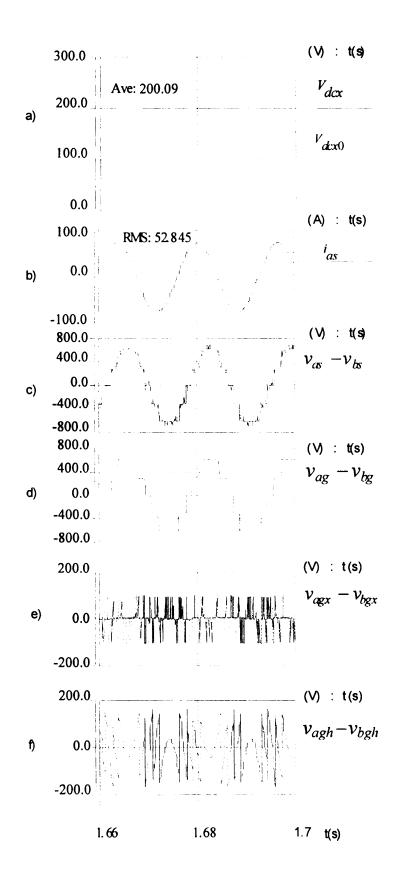

| 6.7: The simulation result of the separate control.                               | 112   |

| 6.8: The proposed topology 1.                                                     | 113   |

| 6.9: The proposed topology 2.                                                     | 114   |

| 6.10: The proposed topology 3.                                                    | 114   |

| 6.11: The general diagram of isolated dc-dc converter                             | 116   |

| 6.12: Two configurations of the secondary side in the isolated dc-dc converter    | 119   |

| 6.13: The transferred power and RMS current on the transformer in these two cases | s 123 |

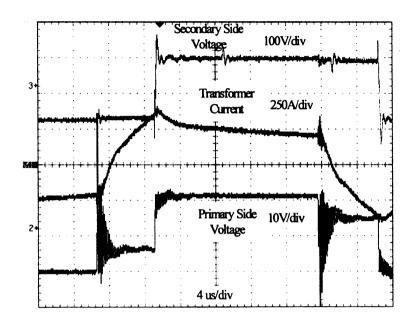

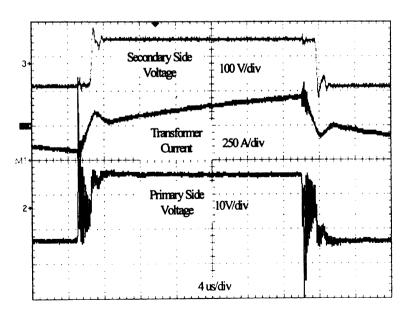

| 6.14: The experimental waveforms of the two different cases.                      | 125   |

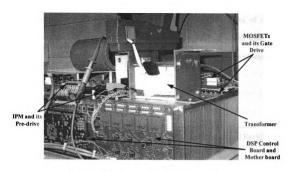

| 6.15: Test setup of the DC-DC converter.                                          | 126   |

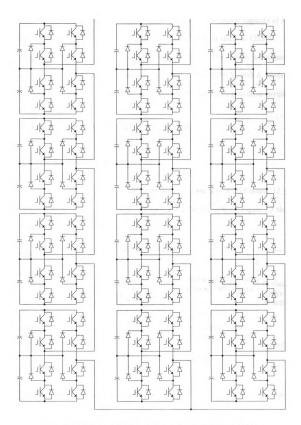

| 7.1: The 17 level cascade multilevel inverter.                                    | 130   |

| 7.2: The schematic of the 17 level cascade multilevel inverter.                   | 131   |

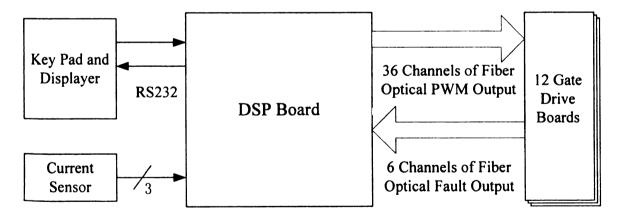

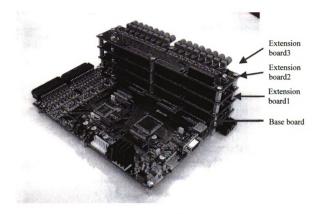

| 7.3: The control unit diagram                                                     | 172   |

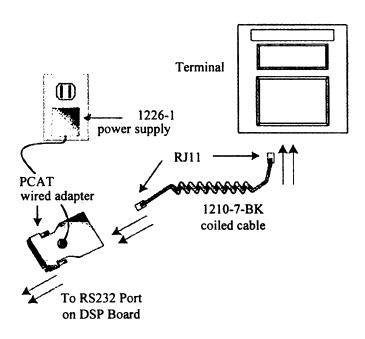

| 7.4: Picture of the DSP board.                                                    | 133   |

| 7.5: The connection of the keyboard/displayer                                     | 134   |

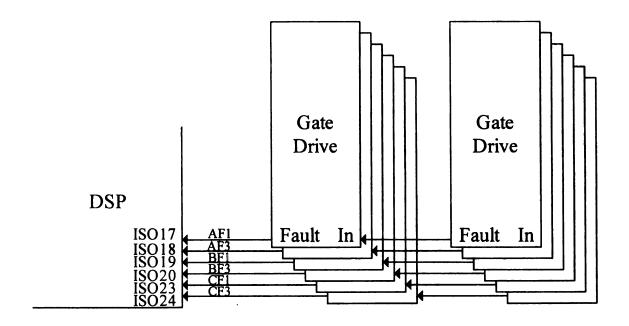

| 7.6: The connection of fault signal                                               | 135   |

| 7.7: The storage unit in the table                                                | 136   |

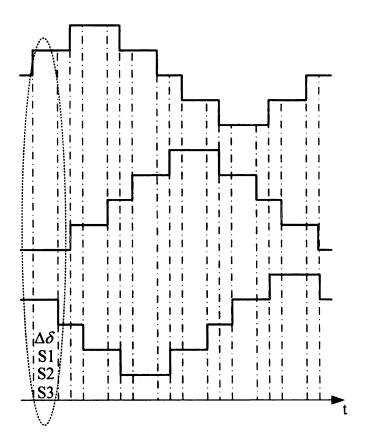

| 7.8: The detailed functional diagram of the CPLD.                                 | 138   |

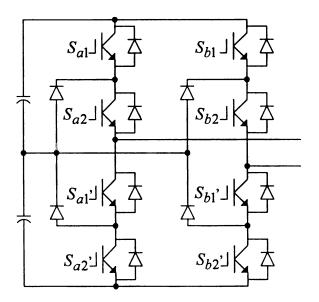

| 7.9: The inverter module structure.                                               | 139   |

| 7.10: Rotation of switch states between modules                                   | 142   |

7.11:

7.12:

7.13:

7,14:

| 7.11: The fault protection scheme                     | 143 |

|-------------------------------------------------------|-----|

| 7.12: The detailed function block of the control unit | 144 |

| 7.13: The phase voltage when MI=0.84                  | 146 |

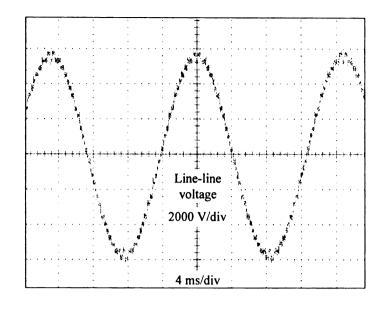

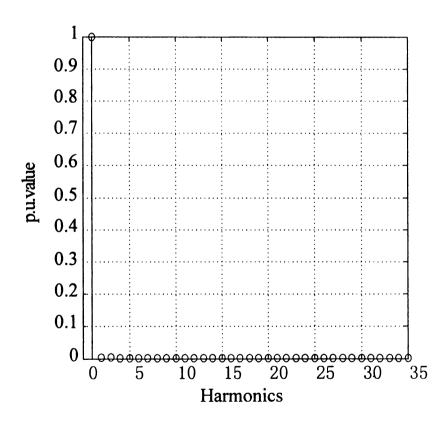

| 7.14: The line-line voltage when MI=0.84.             | 147 |

C ľ

1.

it: pu

P0

lar Th

$R_{()}$

es;

air. Tib

# **CHAPTER 1**

# INTRODUCTION

# 1. 1. Background

With the ongoing expansion and growth of the electric utility industry, including deregulation in many countries, the generation and transmission systems are being pushed closer to their stability and thermal limits. Meanwhile the focus on quality of power distribution has become greater than ever. Environmental impacts also play a larger role than ever in investment decision makings, in all levels of power systems. Thus, at the beginning of the 21st century, with major blackouts threatening the whole world, power systems are now at a dawn of reformation. Optimization of the already established transmission system, implementation of new technologies to ensure power quality, and utilization of renewable energy, now become three major reformation directions. And in this global battle of power system reformation, power semiconductor

based l

answer

Th

Alexar

ac-ac c

the ap

semico

(IGBT

4500 V

solid d

now, t

bonst

mega :

been v

based Power Electronics, a new technology with a history less than three decades long, answers the call.

The very beginning of Power Electronics can be traced back to 1912, when E.F.W Alexanderson of General Electric patented his magnetic amplifier, which worked like an ac-ac converter [12]. Modern power semiconductor based Power Electronics started with the applications of thyristors in 1960s. Since then, several generations of power semiconductor devices have been developed. Now the Isolated Gate Bipolar Transistor (IGBT) has become the major device used in high power conversions. IGBT rated at 4500 Volts, 900 Amperes are already available in the market. With the development of solid devices, Power electronics circuits also evolve. Summarized in big categories, till now, there have been DC-DC converters, DC-AC inverters, and AC-AC converters. The power range of the converters and inverters varies from several watts to hundreds of mega watts. Nowadays, converter and inverter based power electronics equipments have been widely used in all levels of power systems:

- 1) for the *transmission systems*, Flexible AC Transmission Systems (FACTs) are adopted to control the system voltage, compensate reactive power, and improve system stability and transmission capacity;

- 2) for the *distribution system*, numerous Custom Power devices are used to improve the power factor, compensate voltage sags, and eliminate harmonics;

- 3) for the *distributed power generation*, the power electronics equipments are utilized as interfaces between the renewable energy sources and the grid

1.

Ši

e

e)

ţ

F

þ

0

ii

(

(

# 1. 2. Flexible AC Transmission Systems

In transmission systems, to avoid over stable and thermal limitations, the traditional solution has been to construct more transmission lines and substations. However, experience throughout the last several decades proves that it has been more and more expensive, time consuming and controversial to construct new transmission lines. It has been widely recognized that more efficient utilization and better control of the existing power system is the only way to achieve both operational stability and financial profitability. To achieve these goals, Flexible AC Transmission Systems (FACTs) is the only right choice [44-49].

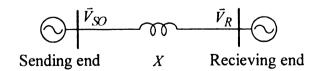

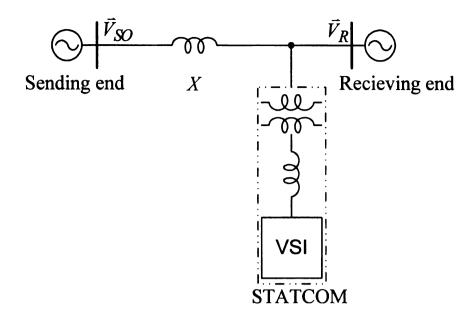

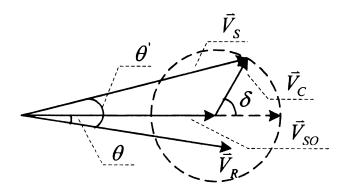

FACTs devices provide improved transmission system operation with minimal infrastructure investment, environmental impact, and implementation time. To better illustrate how FACTs devices improve operation of the transmission line, some basics of the power system will first be introduced. Figure 1.1 is the well-known power system diagram. When considering the power flow and voltage stability, a two bus power system can be simply described as the sending end voltage,  $\vec{V}_{SO}$ , and the receiving end voltage,  $\vec{V}_R$ , connected together by the transmission line impedance, X.

Figure 1.1: The two-bus power system diagram.

and

des<sub>w</sub>

sec

cor

•

Ġ,

. 1

a,

ľ

Equations

$$P = \frac{V_{SO}V_R \sin \theta}{X}, \qquad (1.1)$$

and

$$Q = -\frac{(V_R \cos \theta - V_{SO})V_{SO}}{X}$$

(1.2)

describe real and reactive power transferred from the sending end to the receiving end, where  $\theta$  is the angle difference between  $\vec{V}_{SO}$  and  $\vec{V}_R$ . From these equations, it can be seen that in transmission system, there are three basic variables that can be used to control the active and reactive power flow:

- Voltage (both Sending and Receiving ends);

- Angle; and

- Impedance.

FACTs devices indeed are devices that enhance the transmission capacity by dynamically changing these three variables. Depending on functions, FACTs devices are usually installed at the ends or the middle point of the transmission line. Compared with the corridor needed by a new transmission line, installations of FACTs devices require almost no additional space [44-49].

# 1. 3. Custom Power

The term 'Custom Power' is usually used to describe advanced equipments that installed in distribution systems to improve power quality for end-user customers.

Power quality is related to reliability issues in power system. A power quality problem is an occurrence manifested in a nonstandard voltage, current, or frequency

devial

distrib

Altho

bons.

desire

of me

R

medic broad,

1.4.

Īŗ

deviation that results in the failure or mis-operation of end-user equipments. In the distribution system, power quality now has become a major concern for the end users. Although, in the last two decades, numerous efforts have been put in place to increase the power quality of existing systems, it seems that power quality still has not reached the desired levels to be consistent with the high degree of automatization and sophistication of modern electronic equipments. The major power quality problems are [93-97]:

- voltage sag

- voltage swell

- voltage flicker

- momentary interrupt

- impulsive transient voltage

- oscillation transient voltage

- voltage harmonics

- three-phase voltage unbalance.

Recently, more and more special attention has been focused on critical loads, such as medical centers, automobile manufacturing plants, the semiconductor industry, broadcasting facilities, and commercial buildings.

#### 1. 4. Distributed Generation

Traditionally, the focus of power generation has been on large central stations. Power

is hu ga g is generated from central power plants and transmitted to end users, which generally are

hundreds of miles away. With the world wide rapid increase of demands on power

generation, 80,000 MW per year, and deregulation in most regions, small and local

generation-Distributed Generation (DG), will play a more and more important role in

power system. Research by Electric Power Research Institute (EPRI) indicates that, by

year 2010, 25% of the new generation will be DG [129].

DG technology includes [126-129]:

**Combustion Turbines**: 1-30 MW

Reciprocating Engines: 10 kW-10 MW

Micoturbines: 1-300 kW

Fuel Cells: 1 kW-20 MW

**Biomass**: 5 MW maximum

Wind turbines: 1 kW-1 MW

Photovoltaic: 1 kW-1 MW

Due to environmental concerns, more effort has now been put into the clean DG

methods, such as, geothermal, solar thermal, photovoltaic, and wind generation, as well

as fuel cells that use hydrogen, propane, natural gas, or other fuels to generate electricity

without increasing pollution.

For solar, wind and fuel cell based DG, Power electronics is one of the enabling

technologies. Power electronics equipments are used as interfaces between the power

sources and the grid to distribute the generated power and provide ancillary services.

6

One of the main obstacles in the commercialization of aforementioned types of DG is the high installation cost. The converters or inverters used in the DG are usually the most expensive parts in the systems. So to reduce the cost of the power electronics interface and at the same time achieving maximum power efficiency and quality, now has become very important and urgent.

### 1. 5. Multilevel Inverters

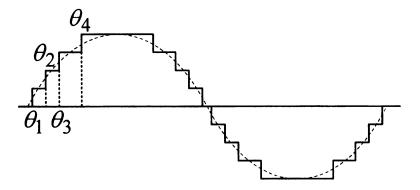

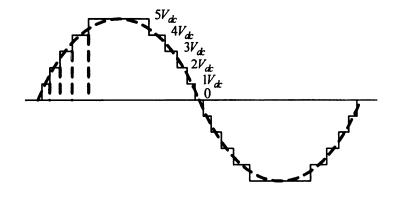

Multilevel Inverters were first introduced in 1981 by Nabae [13]. Now there are three major types of the multilevel inverters: diode-clamped, flying-capacitor clamped and cascade multilevel inverter. The general concept of multilevel inverters involves producing an AC waveform from small voltage steps by utilizing a bank of series capacitors or separated DC sources. To visualize the idea, a general nine level waveform is shown in Figure 1.2.

Figure 1.2: The nine level waveform.

The small voltage steps shown in Figure 1.2, yield several of the advantages of the multilevel inverters [1, 2]:

- 1) very low dv/dt and distortion in the voltage output waveform;

- 2) low distortion in the input current;

- 3) enable the utilization of low voltage devices in medium voltage applications;

- 4) low switching frequency; and

- 5) low common mode voltages.

These advantages lead to a promising future of multilevel inverters in medium voltage drives and power system applications.

Being a new breed of inverters, multilevel inverters attract researches on themselves as well as their industrial applications. The ongoing research topics of multilevel inverter include [1-12]:

- 1) maintenance and balance of DC bank voltages;

- 2) output voltage harmonics elimination;

- 3) PWM control method, especially at low modulation index;

- 4) circuit structures and soft switching; and

- 5) applications in power systems.

1.

in

a;

Þ.

đ

ł.

(

C.

3

I

## 1. 6. Outline of the Dissertation

This dissertation mainly proposes two feasible applications of cascade multilevel inverters in transmission systems. The real application issues of multilevel inverters are discussed. One practical harmonics elimination method is proposed. Extended applications of multilevel inverters in power systems are also presented.

<u>Chapter 2</u> reviews the most current developments in FACTs, Custom Power, DG, and multilevel inverter technologies. The feasible applications of multilevel inverters in power system are summarized.

<u>Chapter 3</u> discusses the real application issues of multilevel inverters in FACTs devices. Current solutions are summarized and a new harmonics elimination method is proposed.

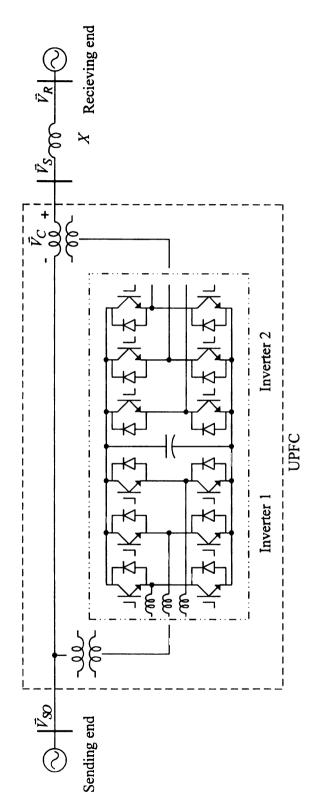

<u>Chapter 4</u> proposes a novel Unified Power Flow Controller (UPFC) circuit configuration. The proposed configuration has several unique features and advantages over the conventional configuration. As a result, cascade multilevel inverter can be used in the new configuration to lower the cost, volume, and increase the reliability. Detailed comparison between the new and conventional configuration is made. Analytical and simulation results are also presented.

<u>Chapter 5</u> introduces a Universal Static Synchronous Compensator (U-STATCOM) based on a delta-connected cascade multilevel inverter. It is believed that the cascade multilevel inverter will be the major circuit to be used in STATCOM. Recently, all the researches regarding STATCOM have been focused on the wye-connected cascade

multilevel inverters. But STATCOM with this kind of circuit structure can only compensate reactive power and harmonics. Other than reactive power and harmonics compensation, the proposed U-STATCOM can also be used to compensate negative sequence current caused by unbalanced loads. The compensation theory based on delta-connected compensation network is illustrated. The operation principle and control scheme are verified by simulation results. For extended applications, the proposed circuit structure also can be used in D-STATCOM (STATCOM in distribute system).

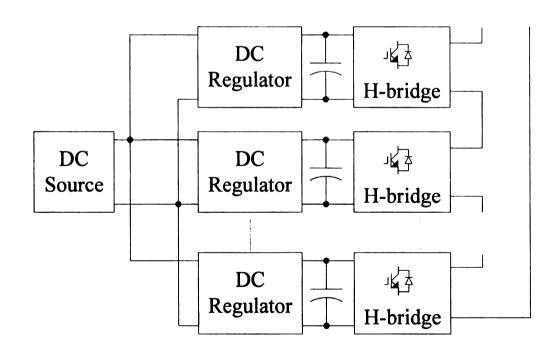

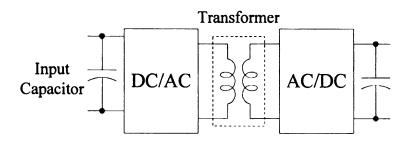

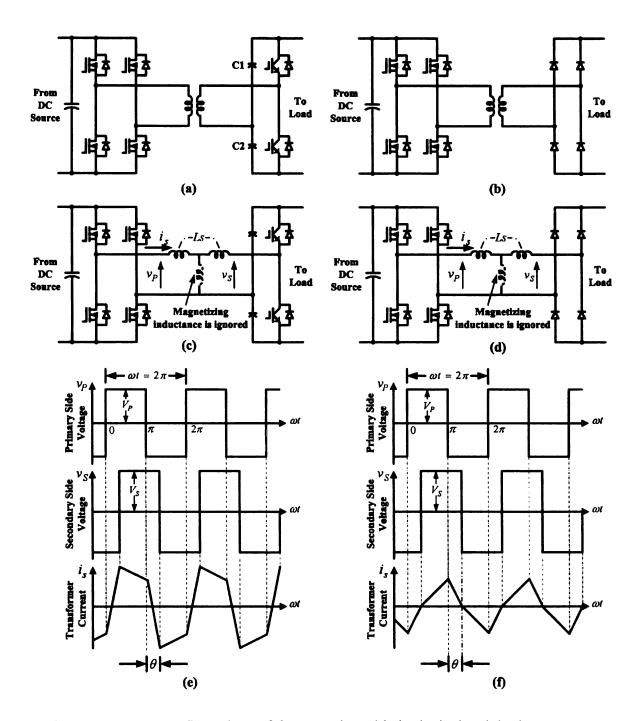

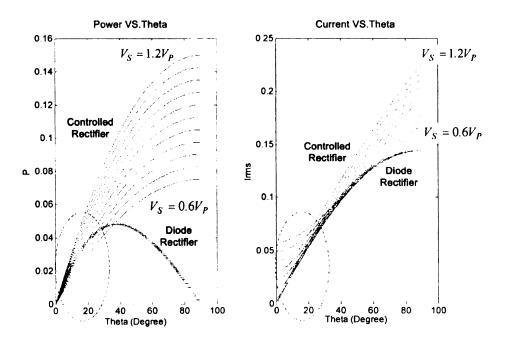

Chapter 6 shows extended applications of multilevel inverters in Custom Power and DG. For Custom Power, a non-traditional cascaded multilevel inverter structure is proposed for a Dynamic Voltage Restorer (DVR). The non traditional multi-level inverter is created by cascading two uneven H-bridges. In this way, the inverter structure can operate as a nine-level cascade multilevel inverter and naturally splits the power conversion into two parts: 1) a higher-voltage lower-frequency power inverter, and 2) a lower-voltage higher-frequency conditioning inverter. The control strategy of the uneven cascade multilevel inverter is presented. For DG, three applications cascade multilevel inverters are proposed. The DC voltage regulator that used to transfer power from DC source to the cascade multilevel inverter is discussed in detail. An optimized circuit of the DC voltage regulator is identified. The analysis and comparisons between different circuits are shown to support the selection. The experimental results are also presented at the end of the chapter.

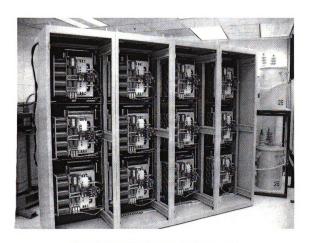

<u>Chapter 7</u> shows a 17 level 1 MVA cascade multilevel inverter and the realization of its control unit. Experimental results from the inverter are shown to verify the proposed harmonics cancellation method.

<u>Chapter 8</u> summarizes the content and the contributions of this work. Some recommendations for future work are also presented.

CH.

SUN

2. 1.

Sir attenti

system

STAT

bonsi

Link [

invert

T

of J:

67.b°

apr.

## **CHAPTER 2**

# **SUMMARY OF PREVIOUS WORKS**

## 2. 1. Introduction

Since their initial introduction, multilevel inverters have received much research attention in all industrial areas. The first applications of multilevel inverters in power system are three level diode clamped inverters, which at the time were used in STATCOMs and UPFCs [76-78]. The newest trend of multilevel inverter applications in Power system are the multilevel inverter based STATCOM [85-88], Back-to-Back DC Link [62-64], and DVRs [114, 115].

This chapter reviews the technical literature regarding the applications of multilevel inverters in power systems. First, the basic system structures and newest developments of different types of FACTs, Custom Power devices and DG interfaces are shown and explained. Then, technical literature of developments of multilevel inverters and their application in power system are fully reviewed and summarized.

2. 2

2. 2

tum

VA!

Wide

reac

#61

âre

com

Figu

hav

пои

•

•

## 2. 2. FACTs Devices

### 2. 2. 1 Structures and Functions of FACTs

Started in the 1970s, after more than two decades developments, FACTs devices have turned from concepts presented in papers to real Mega watts devices around the world.

The early FACTs devices were mostly thyristor controlled devices. By far, the most widely installed FACTs device is the thyristor controlled reactor or capacitor based Static VAR Compensator (SVC), which mainly controls voltage by injecting or absorbing reactive power to and from the grid. Till now, more than 1000 SVCs have been installed world widely [45-49].

With the development of power electronics, nowadays researches on FACTs devices are mainly focused on Voltage Source Inverter (VSI) based devices. VSI utilizes self-commutated power electronics devices, such as GTOs and IGBTs, to inverter DC to AC. Figure 2.1 shows a general three-phase VSI with IGBTs.

Compared with thyristor controller FACTs devices, the VSI based FACTs devices have better dynamic response and more versatile functions. That is the reason they are now also popularly called as FACTs controllers.

Major FACTs devices includes:

- Static Synchronous Compensator (STATCOM)-Controls voltage;

- Static Synchronous Series Compensator (SSSC)-Controls voltage, angle and impedance;

• Uni

• Int

• Ba

tra

each.

ab/

ż, .

- Unified Power Flow Controller (UPFC)-Controls voltage, angle and impedance;

- Interline Power Flower Controller (IPFC)- Controls voltage, angle and impedance;

- Back to Back DC Links (BTB)-Controls the power transmission between two transmission systems.

Figure 2.1: The VSI structure.

Figure 2.2 through Figure 2.6, together with a short description of the functions of each device gives the basic idea of how the FACTs devices benefit the grid.

## **a. STATCOM** [78-92]

STATCOM is a VSI shunt connected to the grid. The VSI is controlled to inject or absorb reactive current to or from the grid, thus supporting the voltage and improving the system stability.

volt.

Figure 2.2: STATCOM Configuration.

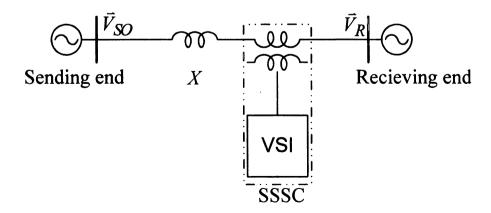

## b. SSSC [59-61]

SSSC is a VSI connected in series with the grid through a transformer. It acts like a voltage source cascaded with the receiving end of the system. Thus by changing the receiving end's voltage, phase, and impedance, it changes the power flow over the grid.

Figure 2.3: SSSC configuration.

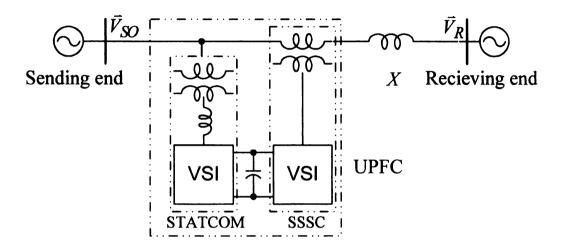

### c. **UPFC** [65-76]

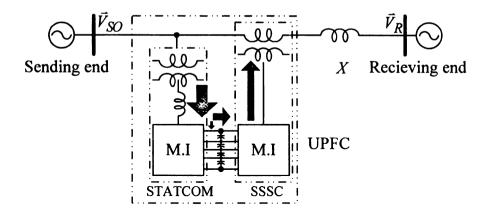

A UPFC is the combination of a STATCOM and a SSSC by back-to-back connecting them together with a common DC link. With this combination, the UPFC inherits all the functions of the STATCOM and SSSC and maximize the operational region [65-72].

Figure 2.4: UPFC Configuration.

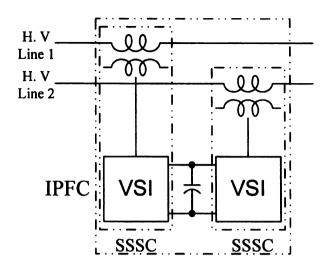

### d. IPFC [57, 58]

IPFC is designed for use in multi-line transmission system. The VSIs share the same DC link, and are series connected in different transmission line. In other word, an IPFC is a combination of several SSSCs with one common DC link. In this structure, power flows from line to line through the DC link. With proper control, the power exchange between different lines can be conditioned and optimized. Similar as the SSSC, an IPFC controls the grid's voltage, phase and impedance.

Viev

sour

DC

pow

com

Figure 2.5: IPFC configuration.

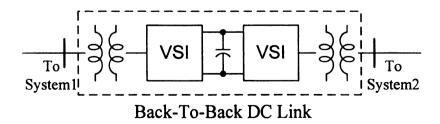

### e. BTB DC Link [62-64]

A Back-to-Back DC Link is used to connect two asynchronous systems together. Viewed from the each side of the systems, BTB DC link functions either as a voltage source or load depending on the direction of the power flow. The structure of the BTB DC Link is a combination of two STATCOMs with one common DC link. It controls the power flow between two asynchronous systems by allowing power flow through the common DC Link.

Figure 2.6: BTB DC Link configuration.

From the figures and descriptions above, it can be seen that the FACTs devices can be simply described as VSIs, either shunt or series connected to the grid through transformers. Table 2.1 summarizes circuit structures of FACTS devices.

Table 2.1: Summary of FACTs Configurations

| FACTs Device            | Number of VSI                              | Configuration                 |

|-------------------------|--------------------------------------------|-------------------------------|

| STATCOM                 | 1                                          | Shunt                         |

| SSSC                    | 1                                          | Series                        |

| UPFC                    | 2                                          | Shunt+Series back-<br>to-back |

| IPFC                    | N (number of the<br>High Voltage<br>Lines) | Series<br>back-to-back        |

| Back-to-Back DC<br>Link | 2                                          | Shunt<br>back-to-back         |

## 2. 2. 2 History and Trends

Though it is not quite widely recognized, the world's first functional STATCOM was installed in 1991, in Inuyama Substation, Japan. The STATCOM is rated at 80 MVA, and connected to 154 kV bus. It was built and installed by Mitsubishi Electric [63, 78].

The world's first UPFC was commissioned in Inez, Kentucky, USA, in 1998, by American Electric Power (AEP). The UPFC is composed of one  $\pm$  160 MVA STATCOM and one  $\pm$  160 MVA SSSC [76, 77].

In 1999, the wolrd's first VSI based Back to Back DC link was put into operation in Japan. The BTB conveys 53 MVA of power between one 50 Hz and one 60 Hz system at 275 kV [63, 64].

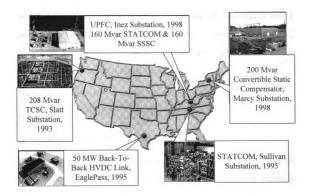

Figure 2.7 shows the major FACTs devices that already have been installed in United States.

Figure 2.7: The installation of FACTs devices in United States.

In the newest developments of FACTs devices, two major projects show the trends of the FACTs One is the ± 75 MVA STATCOM for the 400 kV British National Grid [86, 87]. The STATCOM was built by Alstom and installed at East Clayton, UK, in the year 2000. The highlight of this project is that a cascade multilevel inverter is used as the basic circuit structure for the STATCOM. This, from one aspect, shows that the cascade multilevel inverter would be one of the major circuit candidates for the new STATCOMs in the years to come.

Another project is the ± 200 MVA Flexible Multi-functional Compensator, also called Convertible Static Compensator, which was commissioned at Marcy Substation, NY, in year 2002 [53, 54]. This Compensator stands for the latest generation of FACTs devices. The Compensator has two 100 MVA inverters and can be configured into 11 different configurations for a total of four basic operating modes: STATCOM, SSSC, UPFC, and IPFC. This project shows that the one of the major requirements for the next generation of FACTs devices will be multi-functional.

The success of both projects shows that the trends of the FACTs are:

- 1) utilization of cascade multilevel inverters; and

- 2) realization of multi functions with one installation.

But one inconsistency exists in these two trends. That is cascade multilevel inverter can not be back-to-back connected. It is generally believed that cascade multilevel inverters can not be used in UPFC and IPFC. Trying to overcome this problem and widening the applications of cascade multilevel inverter, this work proposes a new UPFC circuit configuration and a Universal STATCOM in the following chapters.

## 2. 2. Custom Power Devices

As Custom Power devices are in their infancy, there are very few useful standards to enable customers and suppliers to communicate performance requirements on these devices. But with the high demand of better power quality, all types of Custom Power Devices have already been installed around the world for both industrial and residential purposes [93-99].

The most common Custom Power Devices include:

- Uninterrupted Power supply (UPS)-Corrects voltage sag, momentary interrupt,

and acts as backup power;

- Dynamic Voltage Restorer (DVR)-Corrects voltage sag;

- Shunt/Series Active Power Filter (APF)-Compensates harmonics and voltage unbalance;

- Unified Power Quality Conditioner (UPQC)-Compensates harmonics, voltage imbalance, reactive power, and voltage sag;

- **Distributed STATCOM-**Compensates reactive power, adjusts user end voltage.

Custom Power equipments are also based on VSIs. The configurations of Custom Power equipments are similar with the FACTs controllers. These two types of systems can be seen as applications of VSIs at different power system levels. Besides UPS, Custom Power devices are usually installed in medium voltage system (10 kV to 35 kV). The current ratings of Custom Power devices typically ranges from 300 A to 1200 A. The structures and operating principles of these devices are introduced as following.

a. U

(also

the pov

bat

*W*7

out

Ь.

c

Ь

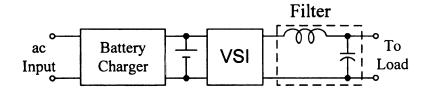

### a. Uninterrupted Power Supply (UPS)

UPS is the most widely used Custom Power devices. Currently there are three major types of UPS in the market: 1) Standby UPS; 2) Line Interactive UPS; and 3) Online UPS (also called 'True UPS').

Among these three, the Online UPS is the most promising and is receiving most of the research attentions. Figure 2.8 shows its basic structure. For this type of UPS, the power is sent to the load through the UPS all the time. During normal conditions, the battery in the UPS is charged, the power flows from the grid through the UPS to the load. When there is interrupt or voltage sag, the VSI is controlled to generate a stable voltage output. The battery is forced to supply partial or full power to the load.

Figure 2.8: The basic Online-UPS system.

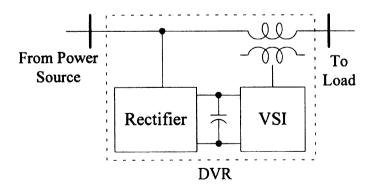

### b. Dynamic Voltage Restorer (DVR) [114-125]

A DVR's main function is to correct voltage sag. Research shows that voltage sags contribute 92% of the voltage disturbance in power systems. Besides DVR, there have been several other commercially available solutions for voltage sag:

1) Static Transfer Switch (STS), which utilizes thyristor switches to transfer the load from the main power supply to a backup line; the drawback is the need for two power line;

- 2) Superconducting Magnetic Energy Storage (SMES), which provides a ridethrough solution; high cost and the need for cooling are the main drawbacks;

- 3) Different storage type based UPS, like Flywheel UPS and battery UPS; the maintenance and cost are the limiting factors of their application.

DVR is usually used in medium voltage level and to compensate the voltage sag for all the loads that are connected to the feeder. Compared to other solutions mentioned above, DVRs have better performance, lower cost, less maintenance, and in some cases, have a comparatively smaller size. Figure 2.9 shows one basic structure of a DVR. It combines a VSI and a series-connected transformer to inject additional voltage during voltage sags. A grid connected rectifier or power storage device will supply the real power needed by the VSI.

In recent papers, it has been shown that the newest trend for the DVR is the utilization of cascade multilevel inverters [114, 115]. In Chapter 6, an uneven cascade multilevel inverter based DVR is also presented.

Figure 2.9: The DVR structure.

### c. Active Power Filters (APF) [105-110]

APFs are mainly used to compensate the harmonics in current and voltage. There are two kinds of APFs: shunt APF and series APF. The shunt APF is a VSI shunted with the grid. It injects harmonics current to neutralize the harmonics in the load current. Series APF is a VSI series connected to the grid to generate a harmonics voltage to correct the input voltage and block the harmonics in the load current.

The realization of the APF needs an effective harmonics detection method and a coordinated control strategy. The harmonics detection methods are always strongly related with instantaneous power theory. Thus, the history of APF is also a history of instantaneous power theory and other modern power theories. Though the first Shunt APF was built more than 16 years ago [105], the research on APF still remains a hot topic in the power electronics world. New circuit structures, new control strategies, and arguments of different power theories still can be seen very often [100-104].

#### d. Unified Power Quality Conditioner (UPQC) [111-113]

UPQC is a combination of Shunt and Series APF by connecting them back-to-back together. The circuit structure is exact the same as its FACTs relative: UPFC. The difference is that the UPQC is aimed at the distribution system and mainly compensates harmonics, reactive power and system imbalance.

### e. Distributed STATCOM (D-STATCOM)

p:

u

,

D-STATCOM is the application of STATCOM at the distribution level. A D-STATCOM is usually installed near critical load and only guarantees the voltage and stability of the load direct paralleled with it. In recent years, D-STATCOM has become very popular as more and more end users begin to understand the damage that can be caused by the voltage problems [91].

# 2. 3. Distributed Generation [126-138]

As mentioned in Session 1.4, power electronics equipments are interfaces between the distributed power sources and the grid to distribute the generated power and provide ancillary services. Table 2.2 summarizes the types of DGs that involve power electronics interfaces.

Table 2.2: The DGs and their interface to grid

| DG           | Interface to Grid |  |

|--------------|-------------------|--|

| Photovoltaic | dc-ac inverter    |  |

| Wind turbine | ac-ac converter   |  |

| Microturbine | ac-ac converter   |  |

| Fuel Cell    | dc-ac inverter    |  |

With the proper interface with the grid, DG can benefit the power system from all perspectives. The benefits are summarized as following [126-129]:

### utility perspective

> transmission capacity relief

|  |  | , |

|--|--|---|

|  |  | , |

|  |  | e |

|  |  | ì |

|  |  | ì |

|  |  | C |

|  |  | , |

|  |  | , |

|  |  |   |

|  |  | ! |

|  |  |   |

|  |  |   |

|  |  | ! |

|  |  | i |

|  |  |   |

- > distribution capacity relief

- > hedge against high market prices

#### end-user perspective

- > efficient use of energy from combined heat and power

- improved reliability by having backup generation and ancillary services (reactive power, voltage sag compensation, etc)

- > incentives from utility to provide capacity reserve or power market hedge

### commercial power producer perspective

- > owner market (to sell power)

- > to sell ancillary services (reactive power, standby capacity, etc.).

Recent research about DG includes maximum power tracking of photovoltaic and wind turbine, low cost inverter system, stability and other problems when connected with grid, and applications of cascade multilevel inverter.

## 2. 4. Multilevel Inverters

## **2. 4. 1. Diode Clamped Inverter** [13-23]

The multilevel inverter family started with the 3 level diode clamped inverter in 1981 [13]. The first industrial application of the diode clamped inverter was for the bullet train in Japan. After two decades' of development, the diode clamped inverter has become the

mθ

bro

the line

ser

fol V<sub>d</sub>

$\Gamma_b$

ha

ap:

fol

W

ar

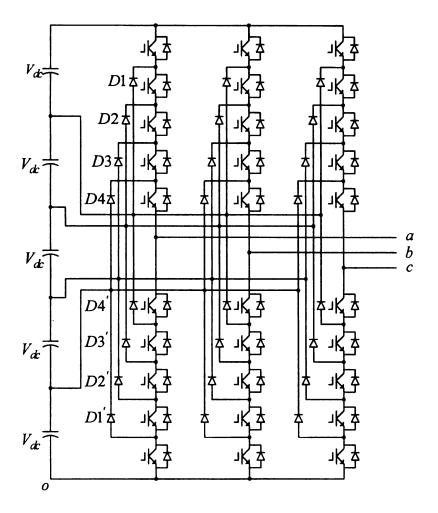

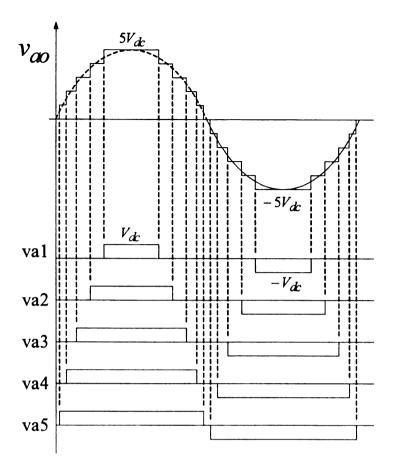

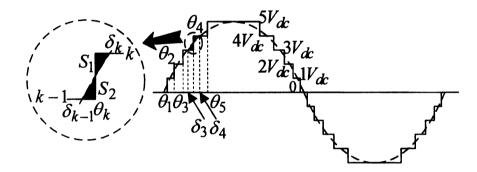

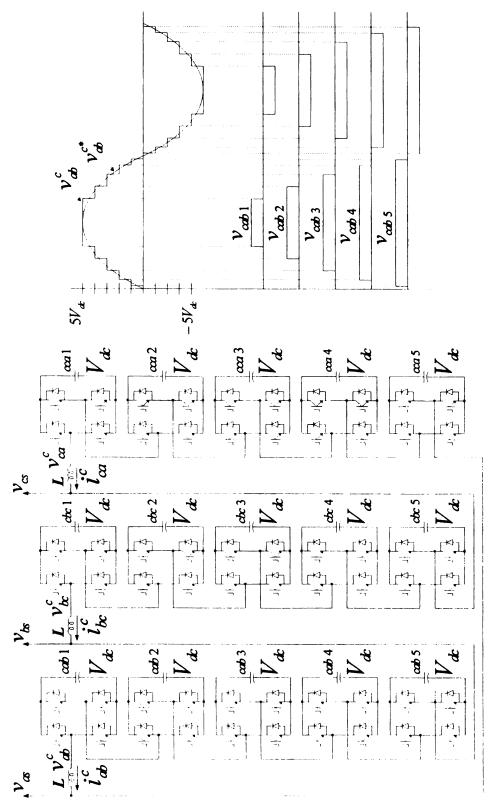

N

most widely used multilevel inverter in the world [14-23]. In the 1990's, people began to propose and build diode clamped inverters with more than 3 levels. Figure 2.10 shows the structure of a three phase, 6 level diode clamped multilevel inverter and its output line-line voltage waveform. In the DC bus of the inverter, there are five capacitors in series. The voltage cross each capacitor is  $V_{dc}$ . Thus by turning on and off the switches following a particularly sequence at pre-calculated angles, the phase voltage can be 0, 1  $V_{dc}$ , 2  $V_{dc}$ , 3  $V_{dc}$ , 4  $V_{dc}$ , and 5  $V_{dc}$  correspondently. By proper synthesizing  $V_{ao}$  and  $V_{bo}$  together, the line-line voltage,  $V_{ab}$ , can change from -5  $V_{dc}$  to +5  $V_{dc}$ . In real applications,  $\theta_1 \sim \theta_5$ , is usually calculated according to the desired modulation index and harmonics elimination. In multilevel inverters, the modulation index is defined as the following:

$$MI = \frac{V_{peak}}{\frac{4}{\pi} N \cdot V_{dc}},\tag{2.1}$$

where  $V_{peak}$  is desired peak value of fundamental frequency in the staircase waveform, N is the maximum number of the level. In equation (2.1), the coefficient  $\frac{4}{\pi}$  is the amplitude of the fundamental component of a unit square waveform.

(a). The 6 level diode clamped inverter.

Figure 2.10: The six level diode clamped inverter and its line-line waveform.

(b) The line-line voltage.

In the diode clamped inverter, three phases share the same DC bank, which makes the back-to-back connection possible. The switching frequency of the inverter is minimized to the fundamental frequency. Each active switching device has same voltage and current stress. However, each clamping diode in the circuits needs to clamp different voltage levels. For example, the clamping voltage for D1 and D1 is  $V_{dc}$ , whereas D4 and D4 clamp  $4V_{dc}$ .

In summary, the major advantages and disadvantage of the diode clamped inverter are:

#### Advantages:

- ♦ Low switching frequency;

- ♦ Feasibility for back-to-back connection;

### Disadvantage

• Different voltage ratings for different clamping diodes.

Till now, diode clamped inverters have mostly been used in medium voltage drives [15-17]. The major power system applications of this kind of inverter include STATCOM, interface between DC and AC transmission line, and back-to-back connected power conditioners [18-20].

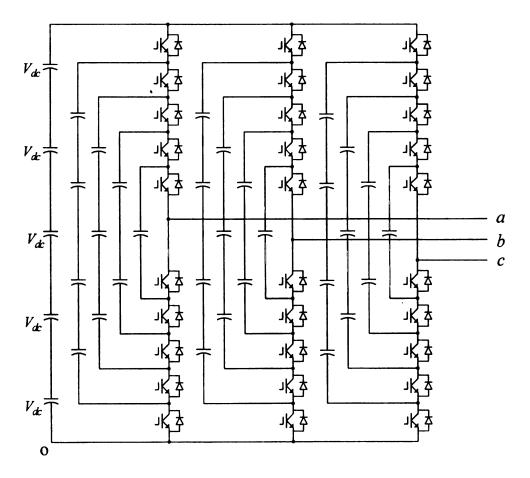

## 2. 4. 2. Flying Capacitor Multilevel Inverter [24-30]

Flying capacitor multilevel inverters were first introduced by Meynard and Foch in 1992 [24]. A three-phase, 6 level flying capacitor multilevel inverter is shown in Figure

2 d

į

I

c

2.11. Each capacitor shown in Figure 2.11 has the same voltage. All the switching devices have the same voltage and current stress.

This kind of inverter has similar structure as the diode clamped inverter. The difference is that it utilizes capacitors other than diodes to clamp the voltage. With this kind of structure, the flying capacitor multilevel inverter has more switching state redundancy in producing the staircase waveform. But at the same time, the bulky capacitors also make the system more expensive and difficult to build. The charge and balance of the capacitors in the inverter also makes the control more complex [25-28].

Figure 2.11: The 6 level flying capacitor multilevel inverter.

summ

T

Advar

•

Disaa

suitab

Fl

2. 4.

inven,

C

desire

and  $\pm$

the nu

three-p

The advantages and disadvantages of flying capacitor multilevel inverter are summarized as following:

#### Advantages:

- ♦ More switch state redundancy;

- Large number of capacitors, which enables better performance during voltage sags;

#### Disadvantages:

- High cost and high volume caused by the large number of the capacitors;

- More complex control required to balance the voltages cross each capacitor.

Flying capacitor multilevel inverters are suitable for all the applications that are suitable for diode clamped inverters. But due to their disadvantages, applications of this type of inverters are seldom reported [29, 30].

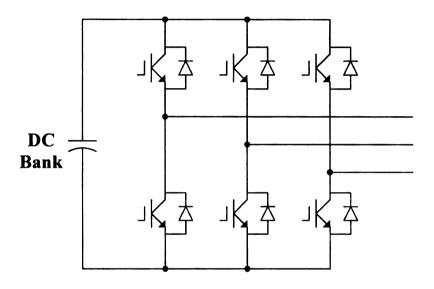

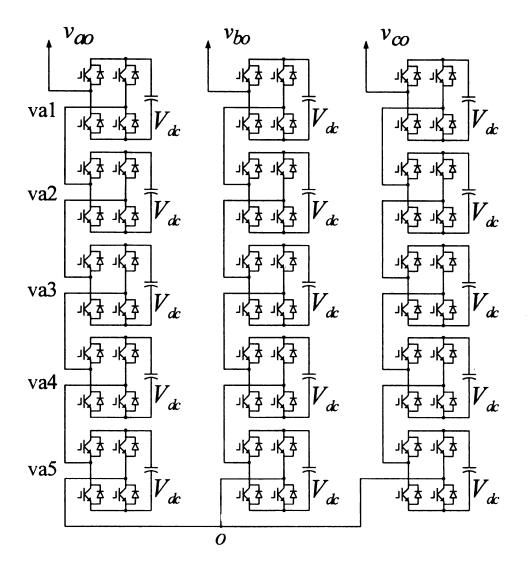

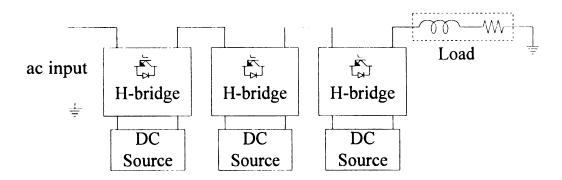

# 2. 4. 3. Cascade Multilevel Inverter [31-42]

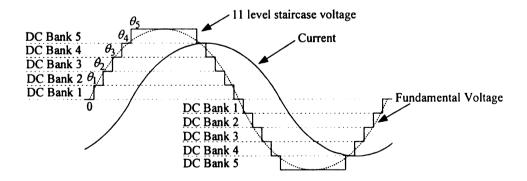

Cascade multilevel inverter is quite different from the aforementioned two multilevel inverters. It utilizes H-bridge inverter units by cascading them together to produce desired staircase waveform. Each H-bridge has a separated DC source and can produce 0 and  $\pm 1~V_{dc}$  voltage levels. Thus, the phase voltage would have 2N+1 levels, where N is the number of separated DC sources per phase. Figure 2.12 shows the wye-connected three-phase 11 level cascade multilevel inverter.

Figure 2.12: 11 level cascade multilevel inverter.

Each module in Fig 2.12 produces a three level staircase waveform at different duty cycle. As modules' outputs are cascaded with each other, the phase waveform as shown in Figure 2.13 can be achieved.

(

the

CO

pro

Figure 2.13: The phase voltage of an 11 level cascade multilevel inverter.

Because the H-bridge can be modularized, the cascade multilevel inverter is now the most favored circuit for new designs of power system compensation and large motor drives. Applications of cascade multilevel inverters in HEV are also proposed [41].

As for power system applications, Peng, Lai, Joo, Visser and other authors have demonstrated that cascade multilevel inverters can be either shunt or series connected to the grid to act as power conditioners such as STATCOM and DVR [36-40]. Full comparisons between different circuit candidates for STATCOM are made in [85]. It is proved that the cascade multilevel inverter is by far the best choice for STATCOM.

2.

inv

Sun

One of the most important features of the cascade multilevel inverter is that separated DC sources are needed. This feature, on one hand, prevents connecting two cascade multilevel inverters back-to-back together; on the other hand, makes cascade multilevel inverters the best choice for many conditions that a lot of DC sources that are used for generation purpose, such as fuel cells and photovoltaic cells in DG.

The main advantages and disadvantages are summarized as following:

#### Advantages:

- Utilization of modularized H-bridges, which lowers the cost and makes the manufacture and maintenance much easier;

- ♦ Maximal utilization of the DC sources by producing 2N-1 level phase voltage;

- The best choice for HEV, fuel cell and photovoltaic applications where many small DC power cells are involved;

#### Disadvantages

The need for separate DC sources, which makes it not infeasible for back-to-back connection applications.

## 2. 5. Applications of Multilevel Inverters in Power System

After the above review of FACTs device, Custom Power, DG and the multilevel inverters, the feasible application of multilevel inverters in power systems can be summarized in Table. 2.3.

|  |  | ï           |

|--|--|-------------|

|  |  | !<br>!<br>! |

|  |  |             |

|  |  |             |

|  |  |             |

|  |  |             |

|  |  |             |

|  |  |             |

|  |  |             |

Table 2.3: The feasible applications of multilevel inverters in power system

| FACTs                                   |              |              |                 |              |                         |  |  |  |

|-----------------------------------------|--------------|--------------|-----------------|--------------|-------------------------|--|--|--|

|                                         | STATCOM      | SSSC         | UPFC            | IPFC         | Back-to-Back DC<br>Link |  |  |  |

| Diode Clamped<br>Multilevel Inverter    | 1            | ٧            | 7               | 7            | ٧                       |  |  |  |

| Flying Capacitor<br>Multilevel Inverter | √            | 1            | 1               | ٧            | <b>√</b>                |  |  |  |

| Cascade Multilevel Inverter             | √            | 1            | Х               | Х            | х                       |  |  |  |

| Customer Power                          |              |              |                 |              |                         |  |  |  |

|                                         | UPS          | DVR          | APF             | UPFC         | D-STATCOM               |  |  |  |

| Diode Clamped<br>Multilevel Inverter    | <b>V</b>     | 1            | <b>V</b>        | <b>√</b>     | 1                       |  |  |  |

| Flying Capacitor<br>Multilevel Inverter | √            | 1            | <b>V</b>        | 1            | 1                       |  |  |  |

| Cascade Multilevel Inverter             | <b>V</b>     | ٧            | <b>V</b>        | Х            | ٧                       |  |  |  |

| DG                                      |              |              |                 |              |                         |  |  |  |

|                                         | Photovoltaic | Fuel<br>Cell | Wind<br>Turbine | Microturbine |                         |  |  |  |

| Diode Clamped<br>Multilevel Inverter    | <b>V</b>     | 1            | 1               | <b>V</b>     |                         |  |  |  |

| Flying Capacitor  Multilevel Inverter   | <b>V</b>     | 1            | 1               | <b>V</b>     |                         |  |  |  |

| Cascade Multilevel Inverter             | <b>V</b>     | √            | 1               | <b>V</b>     |                         |  |  |  |

## 2. 6. Summary

In this chapter, the developments of FACTs, Custom Power and DG were reviewed first. Then three major multilevel inverters were introduced one by one. Their circuit structures, advantages and disadvantages were explained. The literature about their developments and applications were reviewed. In the end, their feasible power system applications of multilevel inverters were summarized.

By utilizing multilevel inverters in power system applications, the bulky transformers usually used for traditional inverters can be eliminated, whereas the stresses on the switches can be greatly reduced. Because of its modular structure, among the three major types of the multilevel inverters, cascade multilevel inverter is the most suitable one for power system application.

All the applications of multilevel inverters in power systems have some common implemental issues. So before breaking into detailed application cases, the next chapter will first address the following most common implemental issues of multilevel inverters: maintenance and balance of DC bank voltages and harmonics elimination in output voltage.

## **CHAPTER 3**

## REAL APPLICATION ISSUES OF MULTILEVEL INVERTERS

## 3. 1. Introduction

DC bank (capacitor) voltage maintenance and balance, and output voltage harmonics elimination are the three most important issues for real applications of multilevel inverters in power systems. Without well maintained and balanced DC banks, the synthesis of a stable staircase voltage waveform would be impossible. To meet the THD requirement of the power system, the switching angles of multilevel inverters must be optimized to eliminate the lower order harmonics.

This chapter introduces the methods to maintain and balance the DC bank voltages, and proposes a practical harmonics elimination method.

## 3. 2. DC Bank Voltage Maintenance and Balance

## 3. 2. 1. DC Bank Voltage Maintenance

In all the power system applications of multilevel inverters, it is always crucial to maintain DC bank voltages at a certain value. But depending on different applications, the ways to maintain the voltages are also different. Summarized in the nature of the applications, basically, there are three different conditions for DC bank voltage maintenance:

- 1) pure reactive and harmonics compensation;

- 2) back-to-back connected applications; and

- 3) distributed generations applications.

### a) pure reactive and harmonics compensation

In the case of STATCOM, SSSC, and APF, the multilevel inverter only outputs or absorbs reactive power. Ideally, no real power is consumed by the inverter. Thus, the DC bank voltage should automatically maintain. But in the real applications, there is always power loss in the multilevel inverters. Besides power loss on parasitic resistance in the bus bar, wires, inductors and capacitors, the switches and diodes have switching loss and conduction losses. In most cases, the major power loss of multilevel inverters is from the switches and diodes. Without compensating for the power loss in the inverter, the DC bank voltages will drop gradually, and the desired functions of the inverter can not be realized.

To co

value, the

power. I

needed b

In th

STATO

line is r

Figure 3

\_

Ass

voltage

bank vo

the need

voltage

To compensate for the power loss and adjust the DC bank voltages to the desired value, the inverter needs to be controlled to absorb or output a small amount of real power. Usually, a simple PI controller would be used to decide how much real power is needed by the inverter.

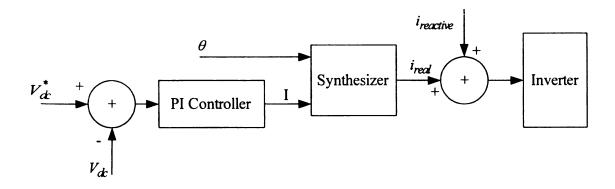

In the cases where multilevel inverters are shunt connected to the utility line, such as STATCOM and Shunt-APF, the real power exchange between the inverter and the utility line is realized by controlling the inverter to send and absorb real current as shown in Figure 3. 1.

Figure 3.1: The DC bank voltage maintenance for shunt connected inverter.

Assuming all the DC banks in the multilevel inverter are balanced, only one DC bank voltage is monitored. The monitored voltage,  $V_{dc}$ , is compared with the desired DC bank voltage,  $V_{dc}^*$ . The result is fed into the PI controller to calculate the amplitude of the needed real current. Then, together with the detected phase angle of the utility phase voltage,  $\theta$ , an instantaneous real current reference,  $i_{real}$ , can be synthesized. The

multilevel inverter would be controlled by the combination of the reactive current command,  $i_{reactive}$ , and real current reference,  $i_{real}$ .

Similarly, in the series connected cases, such as SSSC and Series-APF, the multilevel inverters could be controlled to output a voltage in phase with the utility phase current to absorb or output real power to maintain the DC bus voltage.

Another commonly used method for shunt connected inverter is to control the shunt inverter to output a voltage, which has a slight angle difference from the grid voltage. In this method, the inverter and grid can be seen as two AC voltage sources connected together through the inductor. Thus, the power flow in these cases will obey equation (1.1) and (1.2). With the slight angle difference between inverter voltage and grid voltage, real power can flow into or out of the inverter.

#### b) back-to-back connections

In the back-to-back connection systems like UPFC, UPQC, IPFC, and BTB, the DC bank acts as a link to transfer the real power from one inverter to another.

For example, in UPFC, the SSSC is controlled to inject a voltage to the utility line. If the phase angle difference between the injected voltage and utility phase current is not 90°, real power flow will occur between the SSSC and the utility line. Thus, the SSSC will charge or discharge the DC link. To maintain the DC link voltage, the STATCOM should be controlled to absorb or output the same amount of real power to charge or discharge the DC link to make the total charge or discharge to zero. At the same time, the power loss in both inverters will tend to lower the DC link voltage. So the STATCOM also needs to be controlled to compensate for the power losses. Figure 3.2

show

the re

c)

an re

re

Do

3.

Vo

th

ba]

shows one example of the real power flow in the UPFC. The shadowed arrows indicate the real power flow in the UPFC.

Figure 3.2: Example of real power flow in UPFC.

#### c) distributed generations

In DG, the DC banks of the inverters are powered by energy sources like fuel cells and wind turbines. Between a DC bank and an energy source, there always is a voltage regulator to regulate the input voltage to the DC bank. Depending on applications, the regulator can be a dc-dc converter or a rectifier cascaded with a DC-DC converter. The DC-DC converter will be discussed in detail in Chapter 6.

## 3. 2. 2. Balance of DC Bank Voltages

Though the circuit structure and applications of multilevel inverters may be different, the methods to balance the DC bank voltages can be the same. In this section, an 11 level voltage waveform and corresponding general current waveform is used to show how to balance the DC bank voltages.

As shown in Figure 3.3, each level of the voltage waveform is realized by utilizing the voltage on different DC banks. The current has a phase angle difference from the fundamental of the voltage waveform. Thus, the current has both reactive and active components, which stands for a general condition. The power consumption on each DC bank can be calculated as:

$$P_{n} = \frac{1}{2\pi} \left( \int_{\theta_{n}}^{\pi - \theta_{n}} V_{dc} \cdot i(\theta) \cdot d\theta + \int_{\pi + \theta_{n}}^{2\pi - \theta_{n}} V_{dc} \cdot i(\theta) \cdot d\theta \right). \tag{3.1}$$

Since  $\theta_n$  is different for each level, the power consumption on each DC bank during one fundamental cycle is also different. Further more, the conduction loss and switching losses that faced by each DC bank are also different too. So, without any voltage balance procedure, the DC bank voltages in the multilevel inverter would be different from each other.

Figure 3.3: 11 level voltage waveform and general current waveform.

One simple solution to avoid the unbalance between the DC banks is to rotate the switching angles between DC banks, as shown in Figure 3.4. By rotating the switching

Figure 3.4: Rotation for DC Bank balancing.

angles through each DC bank, after five fundamental cycles, each DC bank would have experienced exactly the same amount of power consumption. Thus, the DC bank voltages will be balanced.

### 3. 3. Harmonics Elimination

Since the first introduction of the multilevel inverters, many harmonics elimination methods have been proposed [6, 9, 139-143]. But harmonics elimination still remains as a major and hot topic for the multilevel inverters. A simple and practical way to solve this problem is still needed.

To answer the call of a simple solution, a new practical harmonics elimination method is proposed in this dissertation. Unlike other methods published before, the proposed method does not need to solve high order polynomials. Only four simple equations and minimum calculation time are needed to realize the elimination of selected harmonics. Experimental results based on the proposed method will be shown in Chapter 7.

## 3. 3. 1. Existing Harmonics Elimination Methods

Till now, there are two major types of harmonics elimination methods: 1) PWM methods, which include both sinusoidal PWM and space vector PWM methods [140-143]; and 2) optimized switching angles methods [6, 9, 139].

The PWM methods are usually used when the number of voltage steps is quite limited, e.g., 2 or 3 steps. The performance of these methods is decided by the switching

frequency. The higher the switching frequency, the lower the harmonics content in the lower frequency range.

Optimized switching angle methods are often used for cases with more voltage steps.

The switching frequency in these methods is the same as the fundamental frequency. The number of eliminated harmonics is decided by the number of voltage steps.

In this section, only optimized switching angle methods are discussed. The general 11 level voltage waveform is shown again in Figure 3. 5 as an example to explain how the optimized switching angle methods work.

Figure 3.5: 11 level voltage waveform and equal area criteria.

The Fourier series expansion of the voltage waveform shown in Figure 3.5 is

$$V(\omega t) = \sum_{m=1,3,5,\cdots}^{\infty} \frac{4V_{dc}}{m\pi} \left(\cos(m\theta_1) + \cdots \cos(m\theta_N)\right) \sin(m\omega t), \qquad (3.2)$$

where N is the number of switching angels and m is the harmonic order.

Based of

found by so l

In this where  $V_F$

eliminatio

switching

.

group we

Meth

group (

equatio

1)

2)

3)

4

Based on equation (3.2), ideally, the optimized switching angles,  $\theta_1 - \theta_5$ , can be found by solving the following equation groups

$$\begin{cases} \frac{4V_{dc}}{\pi}(\cos(\theta_{1}) + \cos(\theta_{2}) + \cos(\theta_{3}) + \cos(\theta_{4}) + \cos(\theta_{5})) = V_{F} \\ \cos(5\theta_{1}) + \cos(5\theta_{2}) + \cos(5\theta_{3}) + \cos(5\theta_{4}) + \cos(5\theta_{5}) = 0 \\ \vdots \\ \cos(13\theta_{1}) + \cos(13\theta_{2}) + \cos(13\theta_{3}) + \cos(13\theta_{4}) + \cos(13\theta_{5}) = 0 \end{cases}$$

(3.3)

In this equation group, the first equation will guarantee the desired modulation index, where  $V_F$  is the desired fundamental voltage. The followed equations will ensure the elimination of 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, and 13<sup>th</sup> harmonics. To eliminate more harmonics, more switching angles and more voltage steps are needed. But with more angles, the equation group would have more equations and higher orders.

Methods proposed in [6, 9, 139] essentially are methods that try to solve the equation group (3. 3) with different approaches. Due to the high order polynomial nature of the equation groups, there are several disadvantages of these kinds of methods:

- 1) these methods usually involve complex algorithm and huge calculation time; when the number of switching angle increases, the capability limitation of contemporary computer algebra software would be easily reached;

- 2) the number and order of polynomial equations increase with the switching angles;

- 3) only N-1 harmonics can be eliminated;

- 4) the algorithms in these methods are often based on special theories, which makes it difficult for users to re-perform the methods.

Researches shows that to solve the simplest case like equation groups (3. 3), it still takes special algorithm and long calculation times to solve. For larger and higher order equation groups, there would be a point that to find the solutions becomes impractical [6, 9, 139].

### 3. 3. 2. Proposed Harmonics Elimination Method

#### A. The Basic Idea of the Proposed Method

The proposed method in this work tries to solve the harmonic elimination problems from a totally different approach. No high order multi-variable polynomial equations would be involved in proposed method.

Unlike all the other methods, the proposed method is not originated from equations, but from the basic ideas of switching angle initialization and utility line harmonics compensation.

To better illustrate the proposed method, equal area criteria and harmonics compensation principle of APF are first introduced and restated as following:

#### 1) The equal area criteria for switching angle calculation.

In the earlier papers about multilevel inverters, the equal area criterion is introduced as one method to calculate the initial value of switching angles. The calculated initial values will be used in the process of solving equation group (3. 3). The basic idea of equal area criteria is also shown in the circled area of Figure. 3.5.

The initial switching angle,  $\theta_k$  is found by solving

$$S1 = S2$$

, (3.4)

where S1 and S2 are the areas of the shadowed part in Figure. 3. It has been proven that by using the equal area criteria, the fundamental of the stair case waveform would resemble the sinusoidal modulation waveform. However, with only equal area criteria, no harmonics elimination can be realized.

The proposed method tries to answer the question of how to utilize the initial values from equal area criteria to find the optimized angles without solving the high order multivariable polynomials equations.

#### 2) Harmonics injection in Active Power Filters

As mentioned in Chapter 2, Active Power Filter (APF) is used to eliminate voltage and current harmonics in utility line.

APFs will inject new harmonic voltages or currents into the utility line to eliminate harmonics that already exist in the utility line. The injected harmonics would have the same amplitudes but opposite phase angles of the selected harmonics they are intended to eliminate. Thus the harmonics in the utility line are neutralized.

The key point of harmonics elimination in APF is to realize harmonics elimination by injecting new harmonics. Combining equal area criteria and the idea of harmonics injection together, a new method to find optimum switching angles can be found.

#### **B.** The Proposed Method

The proposed method indeed is a combination of equal area criteria and harmonics injection. The basic idea behind this method is described as following:

- 1) by using equal area criteria, pure sinusoidal modulation waveform,  $h_1 = v \sin \omega t$ , will derive a set of angles  $\theta_1 \theta_N$ ;

- 2) the staircase waveform formed by  $\theta_1 \theta_N$  will have the fundamental component,  $h_1'$ , and harmonics content  $h_3, h_5, h_7 \cdots h_m$ , the fundamental component,  $h_1'$ , will resemble the sinusoidal modulation waveform,  $h_1$ ;

- 3) ideally, if take  $(-h_5 h_7 \cdots h_m)$  as the modulation waveform, by using equal area criteria, another set of angles,  $\theta_1^h \theta_N^h$ , can be found; the staircase waveform formed by  $\theta_1^h \theta_N^h$  would have component  $-h_5^{'} h_7^{'} \cdots h_m^{'}$  and other higher order harmonics; due to the nature of equal area criteria,  $-h_5^{'} h_7^{'} \cdots h_m^{'}$  will resemble  $-h_5 h_7 \cdots h_m$ ;

- 4) so if use  $h_1 h_5 h_7 \cdots h_m$  as the modulation waveform to find a series of switching angles, the selected harmonics content in the resulted staircase waveform would be around  $h_5 + h_7 \cdots + h_m h_5' h_7' \cdots h_m'$ ; because  $-h_5' h_7' \cdots h_m'$  resembles  $-h_5 h_7 \cdots h_m$ , the harmonics elimination is partly realized.

5) if the same process in 2)-4) is iterated, the harmonics elimination can finally be realized.

To implement this idea, the following five steps need to be followed.

- 1) first, based on equal area criteria, find the initial switching angles  $(\theta_1 \theta_N)$  for a given modulation waveform,  $h_1$ , at a certain modulation index;

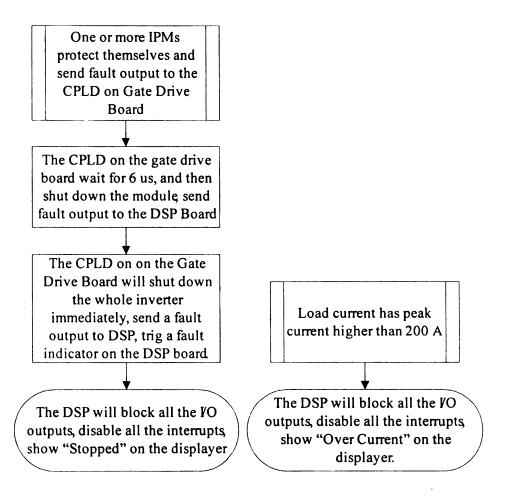

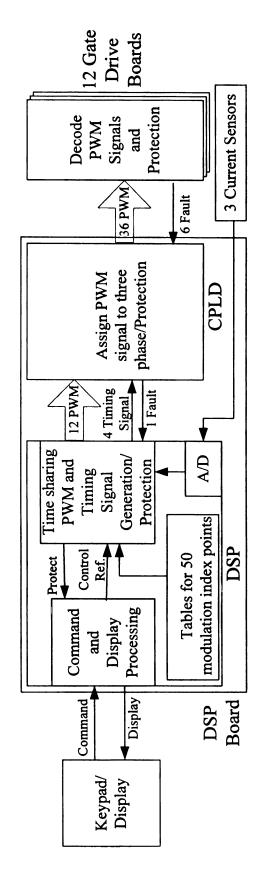

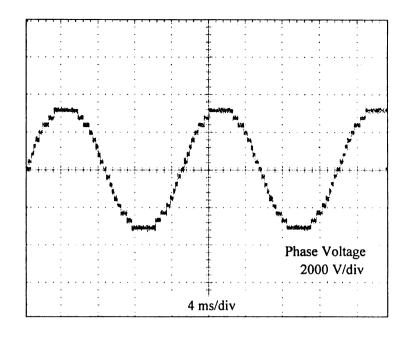

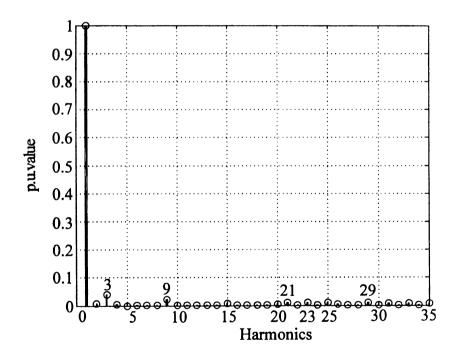

- 2) then find the non-third harmonics content  $(h_5, h_7 \cdots h_m)$  of the staircase waveform formed with switching angles,  $\theta_1 \theta_N$ ; the 5<sup>th</sup>, 7<sup>th</sup>, and all the way to the m<sup>th</sup> harmonics are the selected harmonics for elimination;