THE PATH CHECKING METHOD APPLIED TO MULTIPLE FAULT ANALYSIS OF SWITCHING CIRCUITS

Dissertation for the Degree of Ph. D. MICHIGAN STATE UNIVERSITY TZE TZONG CHEN 1976

This is to certify that the

thesis entitled

THE PATH CHECKING METHOD APPLIED TO MULTIPLE FAULT ANALYSIS OF SWITCHING CIRCUITS

presented by

Tze Tzong Chen

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Computer Science

Carl V. Page Major professor

Date\_Dec. 7. 1976\_\_\_\_

**0**-7639

#### ABSTRACT

## THE PATH CHECKING METHOD APPLIED TO MULTIPLE FAULT ANALYSIS OF SWITCHING CIRCUITS

By

Tze Tzong Chen

In this thesis, the path checking method is presented for the fault detection and diagnosis of switching circuits, both combinational and sequential. In the case of sequential circuits, signal flows in the circuits and their relevance to the state diagram can be exposed by this method which further facilitate the fault analysis.

Using this method, every path of the switching circuit is checked for its ability to pass both signals, 0 and 1. The same approach is applied to both combinational and sequential circuits, with the sequential circuits treated as an extension of the combinational circuits. Thus, for sequential circuits, the fault analysis is conducted at the circuit level rather than at the state diagram level.

The only restriction imposed on the types of circuits that are considered is that every path of the circuits be sensitizible. Although the EXCLUSIVE OR logical gate is excluded from this study, its exclusion is mainly for the purpose of a straightforward presentation of the path checking method, rather than any theoretical difficulties involved. Thus the method can easily be extended to include this gate.

Based on this method, four algorithms are presented for fault detection and fault diagnosis of combinational and sequential circuits. For both cases, combinational and sequential, the results obtained from the fault detection algorithms are used as a basis for the fault diagnosis algorithms. The diagnosis process will proceed down to the level of equivalent faults. However, the diagnosis process can terminate at any stage if the level of diagnosis is satisfactory.

The path checking method, as presented in this thesis, can be extended to cover switching circuits which include unsensitizible as well as partially sensitizible paths, i.e., circuits containing redundant circuitry. The extended method will then be applicable to most switching circuits, including LSI circuits, that are encountered in current fault analysis studies.

# THE PATH CHECKING METHOD APPLIED TO MULTIPLE FAULT ANALYSIS OF SWITCHING CIRCUITS

By

Tze Tzong Chen

### A DISSERTATION

Submitted to Michigan State University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

Department of Computer Science

### ACKNOWLEDGMENTS

I am grateful to Dr. Carl V. Page, the chairman of my guidance committee, for his guidance and encouragement during the course of this thesis. My thanks also go to Dr. Richard J. Reid, Dr. Richard C. Dubes, the late Dr. Leo Katz, Dr. Weinberg Bernhard, Dr. Christie G. Enke, and to Dr. Morteza A. Rahimi for serving on my guidance committee and for reviewing this work.

I wish to express my thanks to the Division of Engineering Research for their financial support during the early stage of the writing of this thesis.

Finally, I am deeply indebted to my parents for their patience and encouragement.

ii

## TABLE OF CONTENTS

|         | 1                                                                                | Page     |

|---------|----------------------------------------------------------------------------------|----------|

| LIST OF | TABLES                                                                           | vi       |

| LIST OF | FIGURES                                                                          | vii      |

| CHAPTER |                                                                                  |          |

| I.      | INTRODUCTION AND THE STATE OF THE ART                                            | 1        |

|         | <pre>1.1 Definition of Reliable Computing 1.2 Forms and Causes of Hardware</pre> | 2        |

|         | Failure in Digital Systems                                                       | 3<br>3   |

|         | <pre>1.3 Examples of Logical Faults</pre>                                        | -        |

|         | Failure in Digital Systems                                                       | *6       |

|         | <pre>1.4.1 Preventive Type Approaches 1.4.2 Corrective Type Approaches</pre>     | 6<br>8   |

|         | 1.5 Contribution and Organization of<br>the Thesis                               | 11       |

| II.     | SWITCHING CIRCUITS AND THEIR FAULT<br>ANALYSIS                                   | 14       |

|         | 2.1 Mathematical Models for Switching                                            |          |

|         | Circuits                                                                         | 14<br>20 |

|         | 2.3 Methods of Test Generation for<br>Combinational Circuits                     | 22       |

|         |                                                                                  |          |

|         | 2.3.1 Truth Table Method                                                         | 23<br>23 |

|         | 2.3.3 The D-Algorithm                                                            | 27       |

|         | 2.3.4 Poage's Method                                                             | 35       |

|         | 2.3.5 Boolean Difference Method                                                  | 37       |

|         | 2.3.6 Chang's CGEM Method                                                        | 38       |

|         | 2.4 Methods of Test Generation for<br>Sequential Circuits                        | 41       |

|         | bequentiat circuits                                                              |          |

|      |     | 2.4.1 Poage's Method                                                                | • | • | 42<br>46 |

|------|-----|-------------------------------------------------------------------------------------|---|---|----------|

| 111. | BI  | T DETECTION AND DIAGNOSIS OF COM-<br>NATIONAL CIRCUITS BY THE PATH CHECKING<br>THOD | • | • | 48       |

|      | 3.1 | Some Network Properties of Com-<br>binational Circuits                              | _ |   | 49       |

|      | 3.2 | Path Sensitization of Combinational<br>Circuits                                     | • | • | 53       |

|      |     |                                                                                     | • | • |          |

|      |     | 3.2.1 Sensitizing a Path                                                            | • | • | 54       |

|      |     | binational Circuits                                                                 | • | • | 55       |

|      |     | 3.2.3 Maximal, Non-Maximal and                                                      |   |   |          |

|      |     | True Sensitization                                                                  | • | • | 59       |

|      | 2 2 | Faults of Combinational Circuits                                                    |   |   | 69       |

|      |     | Fault Detection of Combinational                                                    | • | • | 05       |

|      | 5.1 | Circuits                                                                            | • | • | 75       |

|      |     | 3.4.1 The Path Sensitization Table                                                  |   |   |          |

|      |     |                                                                                     | • | • | 77       |

|      |     | 3.4.2 The Path Checking Fault                                                       |   |   |          |

|      |     | Detection Algorithm                                                                 | • | • | 87       |

|      |     | 3.4.3 An Example                                                                    | • | • | 89       |

|      |     |                                                                                     |   |   |          |

|      | 3.5 | Fault Diagnosis of Combinational                                                    |   |   | • •      |

|      |     | Circuits                                                                            | • | • | 99       |

|      |     | 3.5.1 The Diagnosis Approach                                                        |   |   | 99       |

|      |     | 3.5.2 The Path Checking Fault                                                       | • | • |          |

|      |     | Diagnosis Algorithm                                                                 | _ | _ | 109      |

|      |     | 3.5.3 An Example                                                                    | • | • | 113      |

|      |     |                                                                                     | • | • | 220      |

|      | 3.6 | Characteristics of the Method as<br>Applied to Combinational Circuits .             | • | • | 116      |

| IV.  |     | T DETECTION AND DIAGNOSIS OF                                                        |   |   |          |

|      |     | QUENTIAL CIRCUITS BY THE PATH<br>IECKING METHOD                                     | • | • | 119      |

|      | 4.1 | Some Network Properties of Sequential                                               |   |   |          |

|      |     | Circuits                                                                            | • | • | 121      |

|      | 4.2 | Path and Path Sequence Sensitization                                                |   |   |          |

|      |     | of Sequential Circuits                                                              | • | • | 128      |

|           |       | 4.2.1               | Sensitizi | ng a Pa  | th and   | а     |            |     |   |      |

|-----------|-------|---------------------|-----------|----------|----------|-------|------------|-----|---|------|

|           |       |                     |           | equence  | • • •    |       | •          |     | • | 128  |

|           |       | 4.2.2               | Unsensiti | zible P  | aths in  | n     |            |     |   |      |

|           |       |                     |           | ial Cir  |          | • •   | • •        | •   | • | 132  |

|           |       | 4.2.3               | Maximal a |          |          | tizat | ior        | n   |   |      |

|           |       |                     | of Path   | Sequen   | ces .    | • •   | •          | •   | • | 136  |

|           | 4.3   | Faults              | of Sequer | tial Ci  | rcuits   |       | •          |     |   | 142  |

| 4         |       |                     | ning the  |          |          |       |            |     |   |      |

|           |       | in a                | Desired,  | Known S  | tate .   | • •   | •          | •   | • | 144  |

| 4         | 4.5   |                     | etection  | of Sequ  | ential   |       |            |     |   |      |

|           |       | Circu               | its       | • • • •  | • • •    | • •   | •          | • • | • | 150  |

|           |       | 4.5.1               | The Path  | Sequence | <u>م</u> |       |            |     |   |      |

|           |       | 7 • J • T           | Sensiti   |          |          |       |            |     |   | 151  |

|           |       | 4.5.2               | The Path  |          | e Checl  | king  | •          | ••• | • | 101  |

|           |       |                     |           | etectio  |          |       |            |     | • | 162  |

|           |       | 4.5.3               | An Exampl | .e       | • • •    | • •   | •          | • • | • | 166  |

| ,         | 4.6   | Foult D             | viagnogia | of Som   | ontial   | Circ  |            |     |   | 179  |

| •         | 4.0   | rault D             | iagnosis  | or sequ  | encial   | CIIC  | uri        | 5   | • | 1/9  |

|           |       | 4.6.1               | The Diagr | nosis Ap | proach   |       | •          |     | • | 180  |

|           |       | 4.6.2               | The Path  |          |          |       |            |     | • |      |

|           |       |                     |           | jagnosi  |          |       | <b>1</b> . |     | • | 186  |

|           |       | 4.6.3               | An Exampl | .e       | • • •    | • •   | •          | •   | • | 190  |

|           |       | <b>a</b> 1 <b>i</b> | • • •     | <b>-</b> |          |       |            |     |   |      |

| 4         | 4.7   |                     | eristics  |          |          |       |            |     |   | 196  |

|           |       | Appii               | ed to Sec | luential | CIFCUI   | LTS   | • •        | • • | • | 190  |

| v. (      | CONCL | USIONS              | AND SUGGE | STIONS   | FOR FU?  | TURE  |            |     |   |      |

|           | WOR   |                     | • • • •   |          | • • •    | • •   | •          |     | • | 198  |

|           |       | _                   |           |          |          |       |            |     |   |      |

|           |       | Conclus             |           | • • • •  | • • •    | • •   | •          | •   | • | 198  |

| 5         | 5.2   | Suggest             | ions for  | Future   | Work .   | • •   | •          | •   | • | 199  |

| BIBLIOGRA | ADHA  |                     |           |          |          |       |            |     |   | 202  |

|           |       |                     | • • • •   |          | • • •    | • •   | • •        | •   | • | ~~~~ |

## LIST OF TABLES

| Table |                                                                            | Page |

|-------|----------------------------------------------------------------------------|------|

| 2.1.  | The flow table of the machine of<br>Figure 2.3                             | 20   |

| 2.2.  | Single propagation D-cubes of the com-<br>binational circuit of Figure 2.5 | 31   |

| 2.3.  | Flow tables for good and faulty circuits<br>for example of Poage's method  | 44   |

| 2.4.  | Product tables for example of Poage's method                               | 45   |

| 3.1.  | The PST for Example 3.5                                                    | 82   |

| 4.1.  | The PSST for Example 4.5                                                   | 157  |

.

## LIST OF FIGURES

| Figure |                                                                             | Page |

|--------|-----------------------------------------------------------------------------|------|

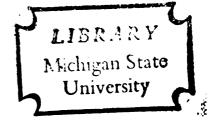

| 1.1.   | An open diode in an AND circuit                                             | . 4  |

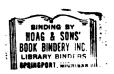

| 1.2.   | A transistor-diode OR circuit                                               | . 5  |

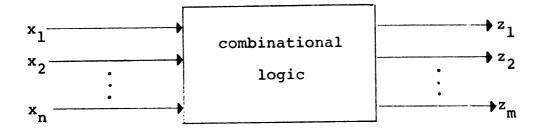

| 2.1.   | A basic model for combinational circuits                                    | . 15 |

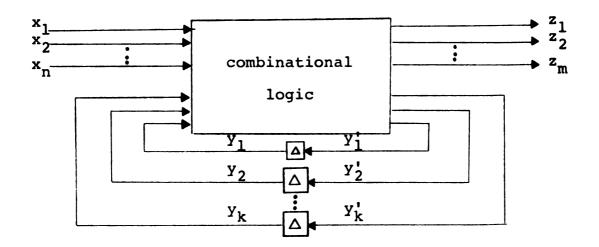

| 2.2.   | A basic model for sequential circuits                                       | . 16 |

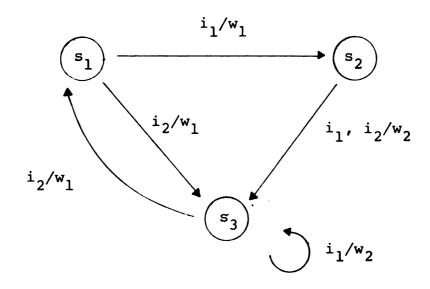

| 2.3.   | A Mealy type state diagram                                                  | . 19 |

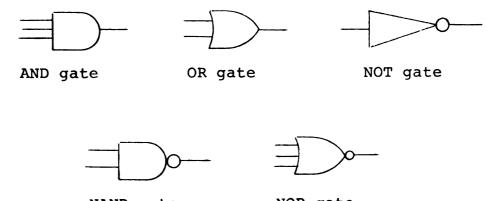

| 2.4.   | Decision elements                                                           | . 21 |

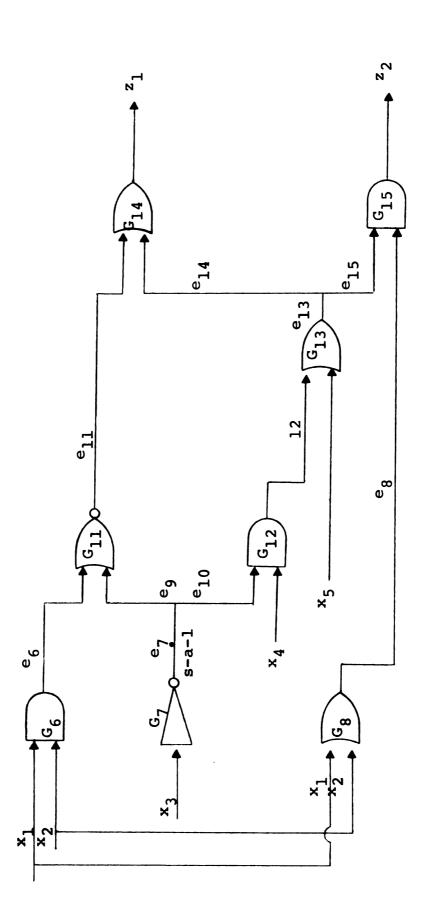

| 2.5.   | A combinational circuit for the path sensitizing method                     | . 25 |

| 2.6.   | An OR gate and its singular cover and propagation D-cubes                   | . 28 |

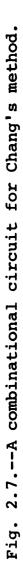

| 2.7.   | A combinational circuit for Chang's method                                  | . 39 |

| 2.8.   | A sequential circuit for Poage's method                                     | . 43 |

| 3.1.   | Examples of paths, subpaths, subcircuits, partial circuits, and constituent |      |

|        | circuits of a combinational circuit                                         | . 53 |

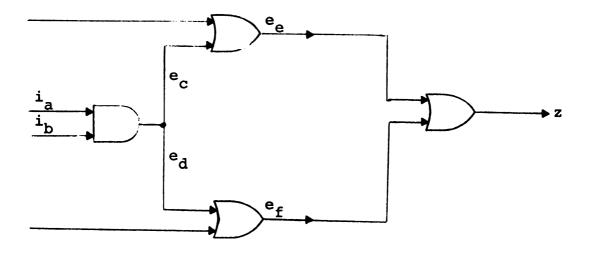

| 3.2.   | A simple combinational circuit with fan-out reconvergence                   | . 56 |

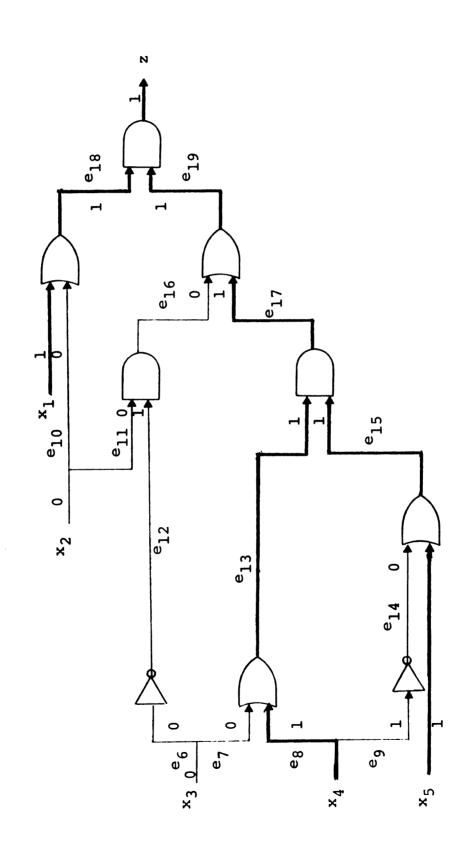

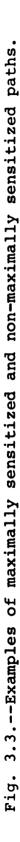

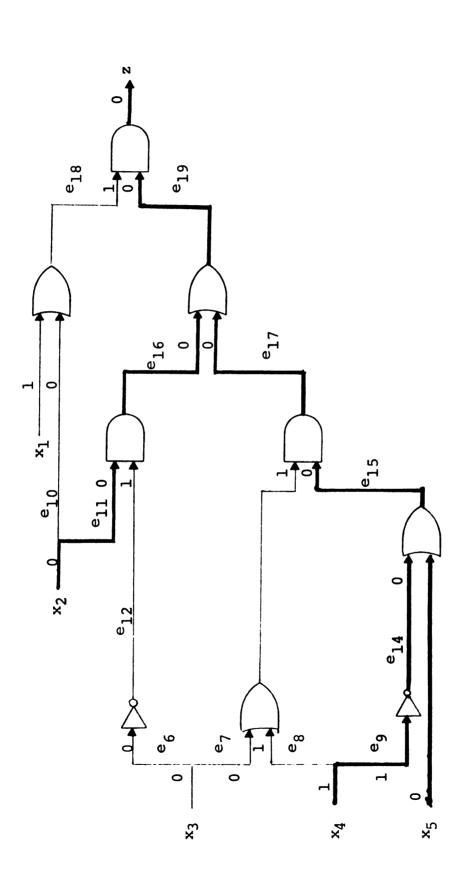

| 3.3.   | Examples of maximally sensitized and non-maximally sensitized paths         | . 65 |

| 3.4.   | Examples of truly sensitized paths                                          | . 68 |

| 3.5.   | Examples of multiple and equivalent faults                                  | . 76 |

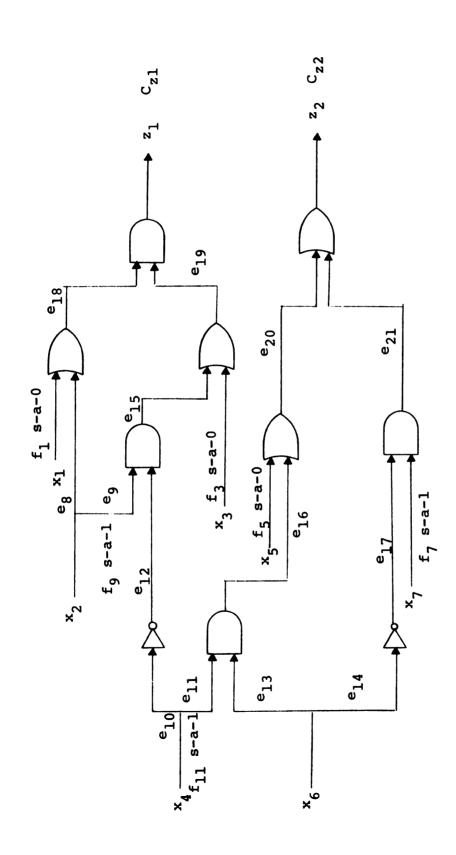

| 3.6.   | A combinational circuit with fan-out reconvergence for Example 3.5          | . 80 |

# Figure

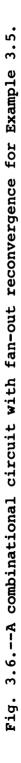

| 3.7. | Graphical representation of the diagnosis process                                                                              | 110 |

|------|--------------------------------------------------------------------------------------------------------------------------------|-----|

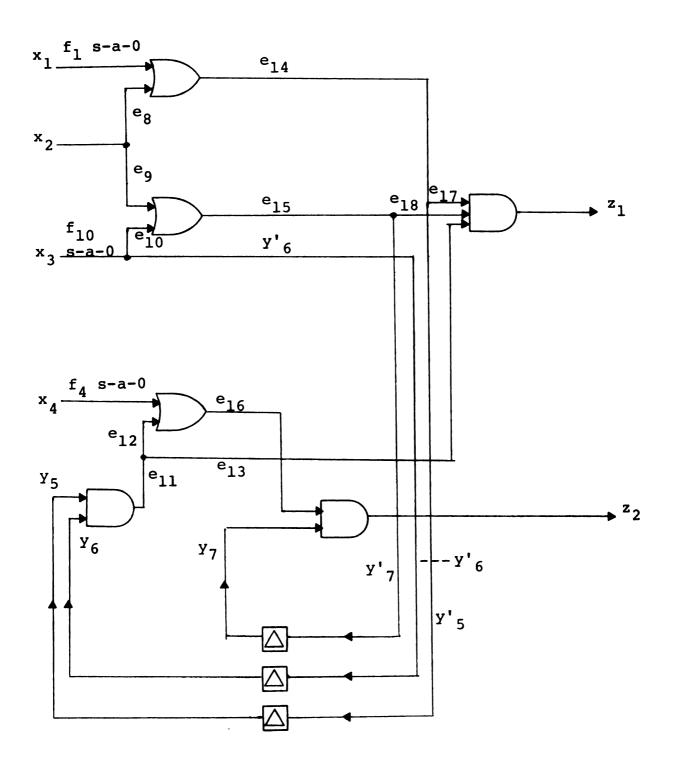

| 4 1  | A sequential circuit for Example 4.1                                                                                           |     |

| 7.1. | A sequencial circuit for Example 4.1                                                                                           | 120 |

| 4.2. | A sequential circuit containing partially<br>unsensitizible path sequences                                                     | 133 |

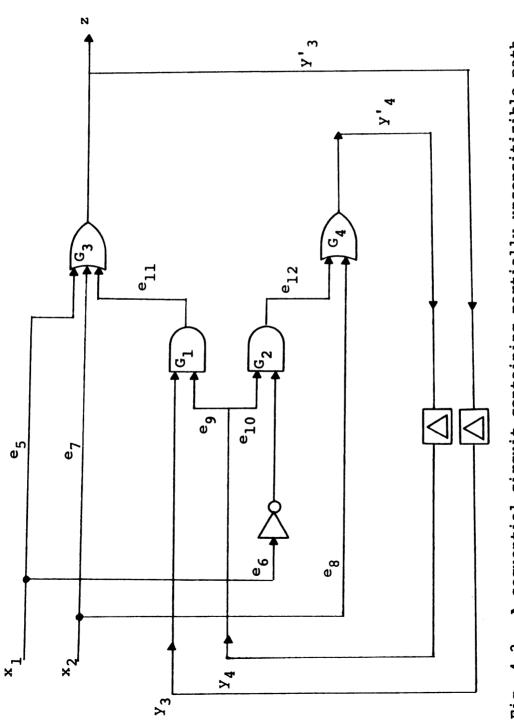

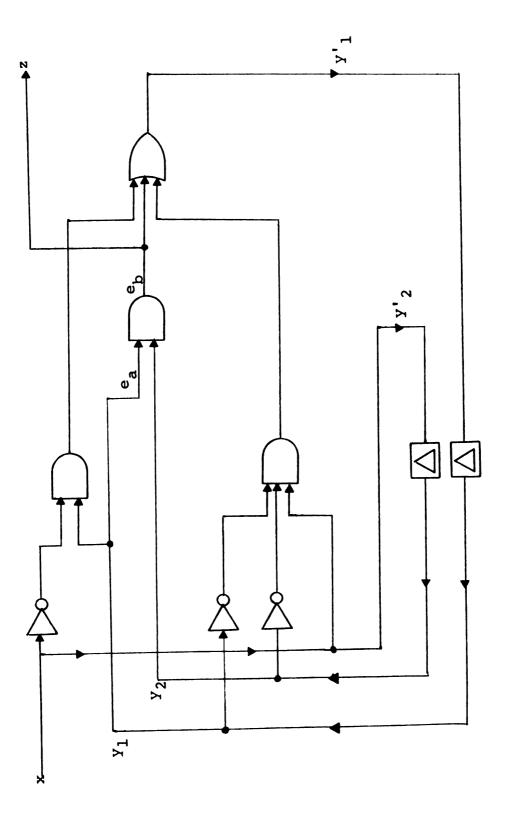

| 4.3. | A sequential circuit with all paths sensitizible                                                                               | 137 |

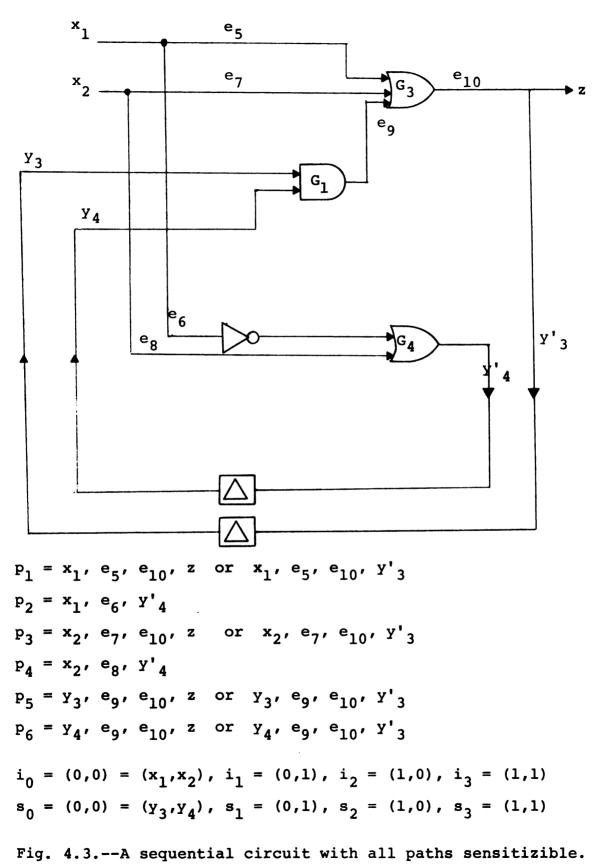

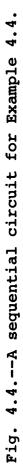

| 4.4. | A sequential circuit for Example 4.4                                                                                           | 149 |

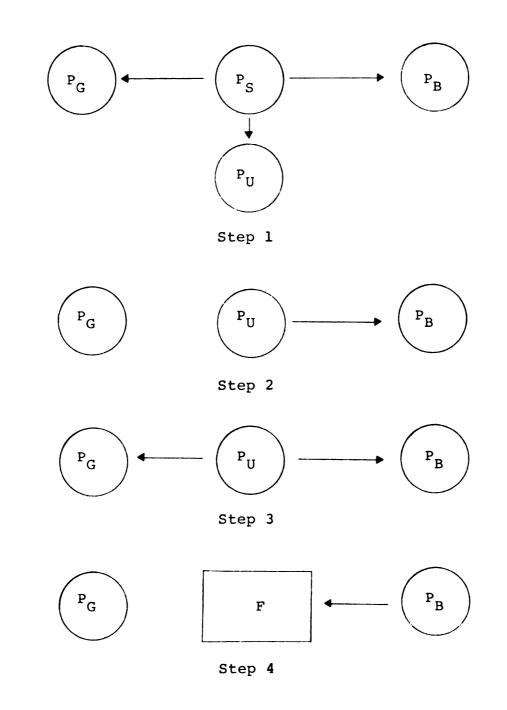

| 4.5. | A sequential circuit for Example 4.5                                                                                           | 154 |

| 5.1. | Partially sensitizible paths result<br>from concatenating circuits C<br>and C <sub>II</sub> to form an integrated <sup>I</sup> |     |

|      | circuit                                                                                                                        | 201 |

Page

#### CHAPTER I

INTRODUCTION AND THE STATE OF THE ART

Digital computers are increasingly being relied upon as an integral part in the day-to-day operations of various sectors of modern societies. The speed and efficiency of computers in processing massive amounts of information have found their applications in almost any branch of modern life, from government agencies to private industries, from weather predictions to patient diagnosis, from research laboratories to factory assembly lines.

A more sophisticated application of computers is found in the field of system monitoring and control where computers are programmed to perform a task independently. A few examples of these might be highway and urban traffic control, satellite flight control, and factory production line control.

With the increasing reliance on digital systems, the problems of their reliability have become a topic of practical concern and have developed to be an area of academic interest. In addition, the current trend toward higher speed, more complexity, and more miniaturization in digital systems introduces more stringent requirements on

reliability standards. The significance of the reliability of digital systems is self-evident and needs no further justification.

### 1.1 Definition of Reliable Computing

Various definitions [31] have been proposed for the term "reliability" of computers. Even though their phrasings are quite different, they all agree in the more generic sense. A typical definition is given here as "the ability to perform its functions correctly and on schedule even in the presence of errors." In the definition, the emphasis on "on schedule" and "in the presence of error" should not be overlooked. "On schedule" introduces the timing factor which is critical for accurate computing, especially in real-time computing. The presence of errors in a digital system is allowed provided it does not affect the system's ability to perform its functions correctly. This provides for the possibility of introducing additional hardware to enhance the levels of reliability of computing. The definition of reliability given is very general and ambiguous and hence some specific measures of reliability are desirable to allow for practical analysis of reliability problems. Some of the commonly used reliability parameters are lifetime and mean time between average failure-rate.

## 1.2 Forms and Causes of Hardware Failure in Digital Systems

Errors in the digital system hardware result from a variety of causes. The following causes are responsible for most of the circuit faults in the system [31].

- a. External environmental interference such as heat and humidity.

- b. Internal environmental interference such as noise.

- c. Inappropriate design or construction.

- d. Aging and deterioration of hardware with time.

The circuit faults resulting from these causes can take on various forms. However, the type of faults which are most widely studied and are also the concern of this thesis are called "logical faults." These are the faults which affect the intended logical behavior of circuits. These faults might be permanent or intermittent. Physical failures such as an opened or closed circuit in a component, or a broken wire in connections, or erroneous design or construction might cause permanent faults. On the other hand, noise interference, close design tolerances, aging and deterioration of components are some causes of intermittent faults.

#### 1.3 Examples of Logical Faults

The following are typical examples of hardware failure which are represented by logical stuck-at type faults.

#### Example 1.1

Figure 1.1 shows a diode AND circuit and its logical representation. The output at y will register 1 volt whenever both inputs  $x_1$  and  $x_2$  have a voltage of 1 volt simultaneously. However, if the diode at  $x_1$  is open, the output would be at 1 volt whenever input  $x_2$  is at 1 volt. This situation is equivalent to  $x_1$  sticking at 1 volt, or logically  $x_1$  sticking at 1 if positive logic is assumed.

Fig. 1.1.--An open diode in an AND circuit.

## Example 1.2

Consider a transistor-diode OR circuit in Figure 1.2. In this circuit, returning the base voltage to  $-V_B$ will reverse biase the emitter-base and collector-base junctions and the two diodes and the output voltage  $V_{CE}$

Fig. 1.2.--A transistor-diode OR circuit.

will be approximately equal to the supply voltage  $V_0$ . When 1 volt is applied to either or both inputs at  $x_1$  and  $x_2$ , the transistor will turn on and the output voltage  $V_{CE}$  will drop to zero indicating the presence of inputs at  $x_1$  or  $x_2$  or both. In this case, negative logical values are adopted for the output. Here an open collector lead will cause the output voltage  $V_{CE}$  to be equal to  $V_0$  resulting in the output sticking at a 0 logical fault. On the other hand, a short between the collector and emitter leads will create a sticking at 1 fault on the output.

Although not all hardware errors can be translated into stuck-at type logical faults, stuck-at type faults constitute the main portion of hardware failures encountered in actual experience.

## 1.4 Strategies to Circumvent Hardware Failure in Digital Systems

There are numerous approaches available to cope with the reliability problems caused by the factors listed in section 1.2. However, they can be categorized into two types of approaches, namely preventive and corrective.

1.4.1 Preventive Type Approaches

This type of approach seeks to prevent the causes of errors from the digital system, or if errors should occur in the system, finds methods to mask them so that normal functions of the system still can be maintained in the presence of these errors.

- 1. Ensuring proper operational environments and appropriate operational procedures. Suitable computer room temperature, humidity control and use of suitable transmission lines are a few examples of precautions needed to ensure proper performance of the system. Establishment and observance of operational guidelines often would considerably reduce system down times and failure rates.

- Use more reliable components and design. Higher design and manufacturing specifications to sustain noise levels and power supply fluctuations, heat

and humidity variations are desirable in a reliable system. But this approach is dictated by available technology and economic constraints.

3. <u>Redundancy</u>. This approach uses additional hardware to mask certain circuit faults and thus still maintain correct logical functions in the presence of these faults. Through this method, any desirable degree of reliability can be obtained, however, at correspondingly higher costs.

Considerable research work has been devoted to this approach to study various redundancy techniques. It appears that this approach is widely adopted in systems where higher reliability is desired and repair work is difficult or impossible.

The first important study on this method was done by Von Newmann [40] and published in <u>Automata Studies</u>. In which he proposed two configurations of redundancy; one of which is called "multiplexing." In this configuration more than one wire is used to carry a single signal. The outputs of each logical operation (each signal of which is carried by more than one wire) are woven through a "restoring organ" to enhance the reliability of these outputs for later stages of logical operations. Later Moore and Shanon [28] introduced "quadrupling" method which was applied to relay-type networks. This method was extended by Tryon [39] to develop a method called "quadding"

which applies to logical gate-type circuits with AND, OR, and NOT decision elements. It requires four times as many circuits and masks all single faults. There are other types of redundancy techniques such as the statistical decision approach by Pierce [31] and the coding theory by Armstrong [1].

## 1.4.2 Corrective Type Approaches

Even with the added protection of redundancy, a computer system cannot be guaranteed to be error-free during its entire life span. A single signal error in all its redundant wires, for example, would be detectable at the outputs of the circuit and thus could cause system malfunction. It is through the continuing testing and correcting approach that a system can be ensured to maintain normal operations at all times.

The corrective procedures in these approaches involve three stages.

- Applying the developed tests to the system to determine whether it is functioning properly (error detection).

- Determining the causes of malfunction and locations of faults in case the system is malfunctioning (error diagnosis).

- Taking corrective measures to restore the system to normal operations.

Of the three stages, the third stage is most straightforward and is a simple task once the initial two stages have been accomplished. While the first and second stages involve complicated circuit functional analyses and testing and have been subjects of research. Numerous methods in error detection and diagnosis of digital circuits have been developed. However, the work is far from complete, especially in the area of sequential circuits.

The common underlying approach of all the methods is designing a test set for the circuit which will detect all faults in the circuit. They differ only in the methods by which these tests are obtained. Examples of these methods will be presented in Chapter II, while a brief discussion now will set the stage for them.

The most simple and straightforward method in error detection and diagnosis is the truth table method. In this method an error is assumed, the truth tables for the fault-free circuit and for the faulty circuit are compared. This comparison will reveal the inputs which detect this fault. This is done for each fault to be investigated. This method is effective only for relatively small circuits, but not for medium or bigger size circuits due to the considerable amount of computations and storage needed.

The path sensitizing method is more effective and faster than the truth table method. It has been widely

investigated and its ideas are extended to develop new methods. The idea is to propagate an assumed error to an output terminal along a sensitized path in a forwardtracing phase, and to trace back from assigned signal points to the inputs to find input tests for the error in the backward-tracing phase. One disadvantage of the pathsensitizing method is that a test may not always be found even though it exists.

Roth's [35] D-algorithm method represents a sophisticated extension of the path sensitizing method. Sophisticated because, instead of treating the error itself as a unit of operation, this method puts all the tests of all possible errors at a logical gate in a "D-Cube." The tests of the circuit are calculated by applying a set of operational rules called "D-Calculus" on these cubes in the "D-Drive" phase (forward-tracing phase) and in the consistency operation (backward-tracing phase). This method has the advantage that it can detect a wider range of faults than stuck-at type faults. The number of D-cubes in a circuit is directly proportional to the number of logical blocks. This fact would impose less demands on storage in computations. Also it is shown that the algorithm will always find the test for a given error, if it exists.

Other algebraic methods by Poage [32], Sellers et al. [36] and Chang [5] for finding the tests for

combinational circuits have also been developed. They all utilize the algebraic properties of the Boolean expressions of the circuits to obtain the tests. As is with most of the previous cases, the big disadvantage of these methods lies in the storage requirements in the computations of these tests.

Relatively few papers on the fault detection and diagnosis of sequential circuits have been published. Hennie [14] proposes a general procedure for synthesizing checking experiments on sequential circuits having a distinguishing sequence. His procedure is based on the logical behavior of the circuit. Other papers by Moore [29], Seshu and Freeman [37], Meyer [25], Hsieh [15] also approach this study at the logical behavior level.

The path checking method, which is an extension of the path sensitizing method, is the topic of this thesis. The advantage of this method is that this method can be applied to both combinational and sequential circuits and thus allows error analysis of sequential circuits at the network level.

## 1.5 Contribution and Organization of the Thesis

Although a considerable amount of research has been devoted to fault analysis of combinational circuits with respectable results, not very much attention has been given to sequential circuits, even though they constitute the

basic foundation of digital computing circuitry. This results partly from the complexities involved in the analysis of sequential circuits. Also in those published works in this area, the approach used in the diagnosis process has mostly been at the state diagram level of the sequential circuit. Yet, it seems that an approach which studies the fault problems at the circuit level possesses advantages.

This thesis studies fault analysis of combinational and sequential circuits at the circuit level using the path checking method. It appears that the path checking method is a suitable approach for attacking the complexities of signal flows in sequential circuits caused by feedback. Through this method, a systematic view of the complex signal flows in the circuit can be obtained, especially in the case of sequential circuits, where signal flows and their relevance to the state diagram become apparent. Although the combinational case is also treated in the thesis, the sequential case is intended to be the major contribution.

Chapter I defines the problem area and gives a brief discussion of published works in this area. Chapter II presents some background materials, preliminaries and terminology of the field. Examples of published methods are also presented in this chapter. Chapter III will include all the related materials in the detection and diagnosis of combinational circuits by the path checking

method. The sequential circuit case is treated in Chapter IV. Chapter V presents a summary and conclusion of the thesis, discusses unsolved problems and suggests materials for future research.

#### CHAPTER II

# SWITCHING CIRCUITS AND THEIR FAULT ANALYSIS

This chapter is devoted to a review of the related background materials in switching theory and fault analysis of switching circuits. Some representative examples of published results in the field are also included to show various methods used to approach the subject matter. This review, however, is far from complete and interested readers are referred to the original works for more detailed discussions.

## 2.1 Mathematical Models for Switching Circuits

The term "switching circuits" is used to include both combinational and sequential circuits which together form the basic computing hardware of digital systems. These circuits are usually represented by a mathematical model which describes their functional behavior in Boolean algebra. In the case of sequential circuits, another mathematical model called the <u>sequential machine</u> is used to describe the logical behavior of sequential circuits. The sequential machine can be projected into a schematic

diagram called the <u>state diagram</u> which is a convenient way to express the logical behavior of the sequential circuit [27].

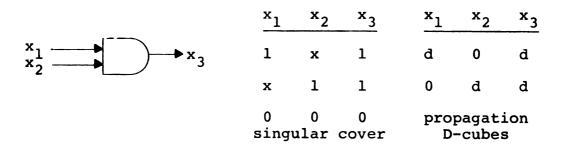

Consider a combinational switching circuit having n inputs  $x_1$ ,  $1 \le i \le n$ , and m outputs  $z_j$ ,  $1 \le j \le m$ , as shown in Figure 2.1.

Fig. 2.1.--A basic model for combinational circuits.

## Definition 2.1

A switching circuit is a <u>combinational switching</u> <u>circuit</u> (or <u>combinational circuit</u>) if its output variables  $z_j$ ,  $1 \le j \le m$ , can be expressed as m Boolean functions of its input variables,  $x_i$ ,  $1 \le i \le n$ ,

$z_{j} = f_{j}(x_{1}, x_{2}, \ldots x_{n}) \quad 1 \le j \le m.$

The outputs of a combinational circuit depend entirely on the current inputs and thus are time independent. In a sequential switching circuit (or sequential circuit), however, the outputs are functions not only of present inputs, but also of past inputs as well. These past inputs are stored in a set of delay elements and are fed back as part of the inputs in the next input-output reaction. These feedback variables are called <u>state</u> <u>variables</u> [27, 23].

Consider a switching circuit with n inputs  $x_i$ ,  $l \le i \le n$ , m outputs  $z_j$ ,  $l \le j \le m$ , and p state variables  $y_k$ ,  $l \le k \le p$ , as shown in Figure 2.2.

Fig. 2.2.--A basic model for sequential circuits.

## **Definition 2.2**

A switching circuit is a <u>sequential switching</u> <u>circuit</u> (or <u>sequential circuit</u>) if its output and next state variables can be expressed by two sets of Boolean functions. The output variables  $z_j$ ,  $1 \le j \le m$ , are expressed by m Boolean functions of input and <u>present state variables</u>  $x_i$ ,  $1 \le i \le n$ ,  $y_k$ ,  $1 \le k \le p$ . The next state variables  $y'_k$ ,  $1 \le k \le p$ are expressed by k Boolean functions of input and present state variables.

$$z_{j} = f_{j} (x_{1}, x_{2}, \dots, x_{n}, y_{1}, y_{2}, \dots, y_{k}) \quad 1 \le j \le m$$

$$y'_{k} = g_{k} (x_{1}, x_{2}, \dots, x_{n}, y_{1}, y_{2}, \dots, y_{k}) \quad 1 \le k \le p$$

Sequential circuits are classified as either "synchronous" or "asynchronous." Synchronous sequential circuits are characterized by the use of clock pulses to synchronize the signal propagation in the circuit. Asynchronous sequential circuits are not provided with such synchronization control and thus sometimes possess <u>race</u> <u>conditions</u> caused by asynchronized reaction times which causes circuit malfunction.

Another mathematical model used to logically describe a sequential circuit is commonly adopted [27]. Consider the same sequential circuit with input variables  $X = \{x_i; 1 \le i \le n\}$ , output variables  $Z = \{z_j; 1 \le j \le m\}$ , and state variables  $Y = \{y_k; 1 \le k \le p\}$ . Let

- $i = X|_{X=a}$  be an input,

- $w = Z |_{Z=b}$  be an output,

- $s = Y |_{Y=c}$  be a present state and

$s' = Y|_{Y=C}$ , be a next state of the sequential circuit, where a, b, c, and c' are vectors of signal values which the sequential circuit assumes. The sequential circuit as given by Definition 2.2 can now be interpreted as follows. Given the sequential circuit originally in state s at time t, it will produce an output w and enter into the next state s' at time t+l after being given an input i.

Formally, this can be described in a mathematical model called the sequential machine.

## Definition 2.3

A <u>sequential machine</u> M is defined as an ordered 5tuple (Q, I, W,  $\tau$ ,  $\omega$ ) where

- 1. Q is a finite set of internal states,

- 2. I is a finite set of inputs,

- 3. W is a finite set of outputs,

- 4.  $\tau$  is a transition mapping of a subset of Q x I onto a subset of Q,

- 5.  $\omega$  is an <u>output mapping</u> of a subset of Q x I onto a subset of W.

The transition mapping  $\tau$  defines the next state s'cQ and the output mapping defines the output  $\omega cW$  of the machine originally in state scQ with input icI.

A sequential machine is <u>connected</u> if given  $s_1 \epsilon Q$ , there exists  $s_2 \epsilon Q$  and an input sequence i\* such that

$\tau$  (s<sub>1</sub>, i\*) = s<sub>2</sub>.

A sequential machine is strongly connected if given  $s_1, s_2 \in Q$ , there exists i\* such that  $\tau$  ( $s_1, i^*$ ) =  $s_2$ .

A sequential machine can be represented in a graphic form called the <u>state diagram</u>. In a state diagram, every state is represented by a circle, and every transition mapping represented by a directed line between the corresponding circles with the corresponding input and output shown along the line. Figure 2.3 shows a Mealy type state diagram.

Fig. 2.3.--A Mealy type state diagram.

A sequential machine can also be represented in a tabular form called the <u>flow table</u> [27]. Every state of the machine is represented by a row and every input is represented by a column. The next state and output are then placed in the entry as specified by the transition mapping like s/w. Table 2.1 shows the flow table of the sequential machine of Figure 2.3.

The basic logical elements used to realize the switching circuits are of two types; relay contacts type and decision elements type. The decision elements type is more popular in practical applications and is the only type

|                | <sup>i</sup> l                 | i <sub>2</sub>                 |

|----------------|--------------------------------|--------------------------------|

| s <sub>l</sub> | s <sub>2</sub> /w <sub>1</sub> | s <sub>3</sub> /w <sub>2</sub> |

| s <sub>2</sub> | s <sub>3</sub> /w <sub>2</sub> | s <sub>3</sub> /w <sub>2</sub> |

| s <sub>3</sub> | s <sub>3</sub> /w <sub>2</sub> | s <sub>l</sub> /w <sub>l</sub> |

Table 2.1.--The flow table of the machine of Figure 2.3.

considered in the thesis. This type generally includes AND, OR, NOT, NAND, and NOR. These elements are enough to realize most of the switching circuits found in real applications. Their schematic notations are shown in Figure 2.4.

### 2.2 Logical Faults of Switching Circuits

A physical fault is a physical defect of a component or wire in a circuit which may cause the circuit to malfunction. Such a fault is called a <u>logical fault</u> if it affects the proper logical behavior of a switching circuit. Most of the logical faults (or simply faults) can be interpreted as stuck-at type faults in which a line input to or output from a decision element sticks at a fixed signal value and thus is not assuming the proper signal values as expected.

NAND gate NOR gate

Fig. 2.4.--Decision elements.

The following definitions present some of the important concepts found in many fault analysis studies [4, 28, 31].

## Definition 2.4

A <u>test for a fault</u> (or faults) of a combinational circuit is an input vector which, when applied to the combinational circuit, can detect the presence or absence of the fault (or faults) through the comparison of the output vector thus produced with the output vector of the same test applied to a fault-free copy of the combinational circuit. A test for a fault (or faults) of a sequential circuit is similarly defined with the distinction that the test may be a sequence of input vectors.

The same meaning for detection as used in Definition 2.4 applies to the following definitions.

#### Definition 2.5

A fault is <u>detectable</u> if there exists at least one test which detects this fault. A fault is <u>undetectable</u> if it is not detectable.

## Definition 2.6

Two faults are <u>equivalent</u> if there does not exist a test which detects one but not the other.

#### Definition 2.7

A <u>test for a combinational circuit</u> is a set of input vectors such that:

- It detects all detectable faults of the combinational circuit,

- No subset of it can detect all the detectable faults of the combinational circuit.

### Definition 2.8

A test for a sequential circuit is a sequence of input-state vectors such that

- It detects all detectable faults of the sequential circuit,

- No subset of it detects all detectable faults of the sequential circuit.

## 2.3 Methods of Test Generation For Combinational Circuits

Most of the published methods of test generation apply to combinational circuits only. In this section, a review of some of the best known methods is presented to show the different approaches available for generating tests for combinational circuits.

## 2.3.1 Truth Table Method

The <u>truth table method</u> is the most basic and straight-forward way to generate tests. Assuming a single fault in a combinational circuit, the truth tables of both the good and the faulty copy of the circuit are compared to obtain the input vectors which produce different output vectors for both circuits. The same procedure is done for every detectable fault. Complete detection tests can then be built from these results.

Though simple and straight-forward, the considerable amount of storage and computations involved make this method unattractive for even circuits of moderate size.

### 2.3.2 Path Sensitizing Method

The one-dimensional <u>path sensitizing method</u> has been widely studied and applied in developing other methods for fault analysis of combinational circuits. Armstrong [1] of Bell Telephone Laboratories and Stieglitz of IBM are prominently linked with this method even though they never published their works on this method.

The idea is first to arbitrarily find a sequence of gates starting from the site of fault leading to an output edge so that the fault can travel along this path to the

output edge. This portion of the method is called the <u>forward tracing phase</u>. In the forward tracing phase, all the input edges to the gates along this path are assigned signal values such that the output edge at the end of the path responds solely to the signal value at the edge of fault. In this way the path is sensitized.

After setting up the sensitized path in the forward tracing phase, a primary input vector to the circuit must be found which realizes the signal values assigned to the input edges of the gates along the path. This portion of the method is called the <u>backward tracing phase</u>. The input vectors thus found are tests for the fault. An example will best illustrate the procedure.

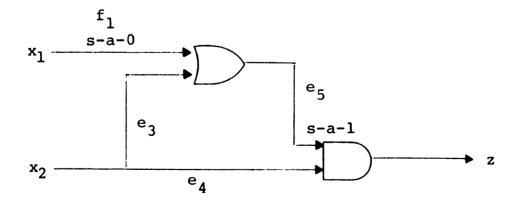

## Example 2.1

Consider the circuit in Figure 2.5 in which edge  $e_7$  sticks at 1 (s-a-1). Suppose the sequence of gates selected is  $G_7$ ,  $G_{12}$ ,  $G_{13}$ ,  $G_{15}$  with the corresponding path of edges  $p_1 = e_7$ ,  $e_{10}$ ,  $e_{12}$ ,  $e_{13}$ ,  $e_{15}$ ,  $z_2$ . To sensitize the path and test if  $e_7$  can assume the signal value 0, let

$e_7 = e_{10} = e_{12} = e_{13} = e_{15} = z_2 = 0$ ,  $x_4 = 1$ ,  $x_5 = 0$ , and  $e_8 = 1$ ,

where  $x_4$ ,  $x_5$ , and  $e_8$  are so assigned such that the path is sensitized. This completes the forward tracing phase. In the backward tracing phase, one or more primary input vectors are to be found which yield the signal values assigned thus far. To do this, the components  $x_1$ ,  $x_2$ , and  $x_3$  of the input vector have to be decided to satisfy  $e_7 = 0$  and  $e_8 = 1$ . To satisfy  $e_7 = 0$  let  $x_3 = 1$ . To realize  $e_8 = 1$ , there are three possibilities,

$$x_1 = 1, x_2 = 0;$$

$x_1 = 0, x_2 = 1;$

or  $x_1 = 1, x_2 = 1,$

which can form three different input vectors. Each of these can be used for sensitizing the chosen path. They are

> $(1, 0, 1, 1, 0) = (x_1, x_2, x_3, x_4, x_5),$ (0, 1, 1, 1, 0), and (1, 1, 1, 1, 0).

Applying one of the three tests to the combinational circuit, one finds

a.  $e_7 \text{ s-a-l if } z_2 = 1$ , or

b.  $e_7$  does <u>not</u> s-a-1 if  $z_2 = 0$ .

Several observations concerning this method are made as follows.

- a. Since sometimes it is necessary to make a choice out of several possibilities in assigning signal values during the backward-tracing phase, it can happen that inappropriate choice may lead to a conflict with assigned signal values. If this occurs, one must back up and try the other alternatives until the conflict is resolved and a test is found.

- b. The method is not algorithmic. It has been shown that a test cannot be found using this method for a combinational circuit even though it exists.

- c. Finally, this method has been proven very useful in practice and the computer running time and storage requirements are economical.

The failure of the path sensitizing method to find a test for a combinational circuit where there is one is caused by the fact that only one path is sensitized at one time using this method. To overcome this defect, Roth develops a method which sensitizes all possible paths simultaneously from the site of fault to the circuit outputs.

# 2.3.3 The D-Algorithm

Roth's <u>D-algorithm</u> [35] represents the first algorithmic approach in generating tests for combinational circuits. The formulation of the method is in terms of a calculus called <u>D-calculus</u> for <u>cubical complexes</u> formed for the logical elements of the circuit. The concepts and terminology as used by him are briefly explained as follows.

a. Singular cover

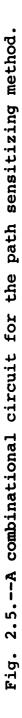

A <u>singular cover</u> of a gate is a compact truth table of the gate which can be used to describe any logical element. A singular cover of a two-input OR gate is shown in Figure 2.6 in which x represents a "don't care" signal value.

Fig. 2.6.--An OR gate and its singular cover and propagation D-cubes.

b. Propagation D-cube

The propagation D-cubes of a gate contain all of the possible sensitized paths through that gate and are derived from the singular cover of the gate. For the OR gate in Figure 2.6, two propagation D-cubes are obtained as shown in the same figure where d represents the "variable" on that path. c. Primitive D-cube of a fault

The <u>primitive D-cubes</u> of a fault on a gate are identical to the propagation D-cubes for the gate. However, the primitive D-cubes of a fault represent the tests for that fault.

d. D-Intersection

Sensitized paths starting from the sites of faults to the output edges of a combinational circuit are formed by interconnecting propagation D-cubes using D-intersection operations.

Roth uses a binary operator  $\Omega$  to define the Dintersection. Some of the binary operations are shown as follows.

$d \Omega \mathbf{x} = d$   $1 \Omega \mathbf{x} = 1$   $\mathbf{x} \Omega \mathbf{0} = 0$   $d \Omega \mathbf{d} = d$   $\mathbf{x} \Omega \mathbf{d} = d$

The discussions of the D-algorithm are best given through an example.

# Example 2.2

Consider the circuit of Figure 2.5 with fault  $f = e_7$  s-a-l. The propagation D-cubes of all the gates in the

circuit are shown in Table 2.2 where d' represents the complement of d.

The D-algorithm is divided into two phases, the <u>D-drive phase</u> and the <u>Consistency phase</u>. In the D-drive phase, all possible sensitized paths for a fault are formed leading from the fault site to the circuit output edges. Input vectors to the circuit compatible with the signal values assigned thus far are then found in the consistency phase.

- A. The D-drive phase.

- 1. Label the primitive D-cube of the fault as test cube 0,  $tc^0$ .

$$tc^0 = 1$$

d' d' d'

The variable d' means that the corresponding edge should have a signal value of 0 if the fault is absent and 1 otherwise.

2. Define the <u>D-fanout</u> set of a test cube tc as the set of gates fed by the edges of tc having signal variable d or d'. The D-fanout set  $df^0$  of  $tc^0$  is

$$df^0 = \{11, 12\}.$$

3. The next step is to D-intersect the test cube with the propagation D-cubes of each gate of its Dfanout. The propagation D-cubes of {11} are

| edges<br>gates | 1 | 2 | 3 | 4 | 5 | 6 | 7  | 8 | 9  | 10 | 11 | 12 | 13 | 14 | 15 | z <sub>1</sub> | z2 |

|----------------|---|---|---|---|---|---|----|---|----|----|----|----|----|----|----|----------------|----|

| 6              | 1 | đ |   |   |   | đ |    |   |    |    |    |    |    |    |    |                |    |

| 6              | đ | 1 |   |   |   | đ |    |   |    |    |    |    |    |    |    |                |    |

| 7              |   |   | d |   |   |   | d' |   | d' | d' |    |    |    |    |    |                |    |

| 8              | 0 | đ |   |   |   |   |    | d |    |    |    |    |    |    |    |                |    |

| 8              | đ | 0 |   |   |   |   |    | đ |    |    |    |    |    |    |    |                |    |

| 11             |   |   |   |   |   | 0 |    |   | d  |    | d' |    |    |    |    |                |    |

| 11             |   |   |   |   |   | đ |    |   | 0  |    | d' |    |    |    |    |                |    |

| 12             |   |   |   | 1 |   |   |    |   |    | đ  |    | d  |    |    |    |                |    |

| 12             |   |   |   | đ |   |   |    |   |    | 1  |    | d  |    |    |    |                |    |

| 13             |   |   |   |   | 0 |   |    |   |    |    |    | đ  | đ  | đ  | đ  |                |    |

| 13             |   |   |   |   | đ |   |    |   |    |    |    | 0  | đ  | đ  | đ  |                |    |

| 14             |   |   |   |   |   |   |    |   |    |    | 0  |    |    | d  |    | d              |    |

| 14             |   |   |   |   |   |   |    |   |    |    | đ  |    |    | 0  |    | đ              |    |

| 15             |   |   |   |   |   |   |    | 1 |    |    |    |    |    |    | đ  |                | d  |

| 15             |   |   |   |   |   |   |    | đ |    |    |    |    |    |    | 1  |                | đ  |

Table 2.2.--Single propagation D-cubes of the combinational circuit of Figure 2.5.

$$tc^{01} = \frac{3}{1} \frac{6}{0} \frac{7}{0} \frac{9}{0} \frac{10}{10} \frac{11}{10},$$

$$tc^{02} = \frac{3}{10} \frac{4}{10} \frac{7}{0} \frac{9}{10} \frac{10}{12} \frac{12}{100}.$$

4. The D-drive phase continues with successively repeating steps 2 and 3 for each new test cubes obtained at each stage until either the test cube reaches an output edge or ends in a non-output edge. The final test cubes obtained for the example are

$tc^{012} = \frac{3}{1} \frac{6}{0} \frac{7}{0} \frac{9}{10} \frac{11}{d'} \frac{14}{d} \frac{z}{0} \frac{1}{d}, C$   $tc^{0111} = \frac{3}{1} \frac{4}{1} \frac{5}{0} \frac{6}{0} \frac{7}{0} \frac{9}{10} \frac{11}{d'} \frac{12}{d} \frac{13}{d'} \frac{14}{d'} \frac{15}{d'},$   $tc^{0112} = \frac{3}{1} \frac{4}{1} \frac{6}{0} \frac{7}{0} \frac{9}{10} \frac{11}{11} \frac{12}{14} \frac{14}{z} \frac{z}{1}, C$   $tc^{0221} = \frac{3}{1} \frac{4}{1} \frac{5}{0} \frac{6}{0} \frac{7}{0} \frac{9}{10} \frac{11}{11} \frac{12}{13} \frac{14}{14} \frac{15}{15},$   $tc^{0222} = \frac{3}{1} \frac{4}{1} \frac{5}{0} \frac{7}{0} \frac{9}{10} \frac{11}{11} \frac{12}{13} \frac{14}{14} \frac{15}{15} \frac{z}{1}, C$   $tc^{0223} = \frac{3}{1} \frac{4}{1} \frac{5}{0} \frac{7}{10} \frac{9}{10} \frac{11}{12} \frac{13}{14} \frac{14}{15} \frac{15}{2}, C$   $tc^{01111} = \frac{3}{1} \frac{4}{1} \frac{5}{0} \frac{6}{1} \frac{7}{8} \frac{9}{10} \frac{10}{11} \frac{11}{12} \frac{13}{14} \frac{14}{15} \frac{15}{2}, C$

Those test cubes reaching an output edge as indicated by a C above represent the sensitized paths between the fault site and an output edge. These test cubes are now ready for the consistency phase.

B. The Consistency phase.

In this phase, one traces along each test cube reaching an output edge, from those edges of known signal values towards the input edges of the circuit in order to determine signal values for those edges not yet assigned. To do this, one starts with D-intersecting the test cube with the singular cover of the gate whose output edge is the highest numbered edge of known signal value (0 or 1) on the test cube. The process is repeated for all other edges of known signal value on the test cube. This is done in descending numerical order until either all the input edges of the circuit have been assigned signal values or a conflict of signal assignments exists, in which case, the path cannot be sensitized.

Considering  $tc^{012}$ , one finds, from the circuit of Figure 2.5

$$e_{14} = 0 \neq e_{13} = e_{15} = 0.$$

The D-intersection of  $tc^{012}$  with the singular cover of G<sub>13</sub> results in

$$x_5 = e_{12} = 0$$

.

Similarly, the D-intersections of tc<sup>012</sup> with other singular covers concerned find

$x_4 = 0,$ and  $x_1 = 0, x_2 = 0,$ or  $x_1 = 1, x_2 = 0,$ or  $x_1 = 0, x_2 = 1.$

Thus the computations of the consistency phase on tc<sup>012</sup> result in three tests which sensitize the path  $P_{012} = x_3, e_7, e_9, e_{11}, z_1$ . The tests are

> $t_{012}^{1} = (0, 0, 1, 0, 0) = (x_{1}, x_{2}, x_{3}, x_{4}, x_{5}),$   $t_{012}^{2} = (0, 1, 1, 0, 0),$  $t_{012}^{3} = (1, 0, 1, 0, 0).$

Since  $e_7$  and  $z_1$  have different signal values as can be seen on tc<sup>012</sup>, the fault f will show up as  $z_1$  assuming the signal value 0 upon applying one of the tests above to the circuit.

Different tests can be obtained from the other test cubes, all of which will detect the same fault.

This concludes the example and the discussions of the procedures of the D-algorithm method. The computations for even a single fault are still quite lengthy as demonstrated in the example. In actual situations, tests for multiple faults are more frequently demanded. It is possible to apply the D-algorithm on multiple faults by computing tests for each individual fault and then concatenating these tests. However, the total computations needed will be quite substantial.

#### 2.3.4 Poage's Method

Poage [32] developed a mathematical method for generating a minimal set of tests to detect all single and multiple faults. His method applies to both gate and relay contact combinational circuits. He also developed a method for test generation for sequential circuits which will be discussed later in this chapter.

His method is a sort of calculus for faults. For every edge in the combinational circuit, three Boolean variables called fault parameters are defined as follows.

j<sub>0</sub> = 1 iff edge j s-a-0

j<sub>1</sub> = 1 iff edge j s-a-1

j<sub>n</sub> = 1 iff edge j is fault-free

At any given time, only one of the three fault parameters can exist. Then if edge j carries a signal having the Boolean value w, a w\* is defined for the edge as:

$$w^* = w \cdot j_n \nabla j_1.$$

The expression means that edge j will have a signal value of 1 either it is fault-free carrying the signal value 1 or it s-a-1. Similarly, a w\*' is defined for edge j to give the conditions for its signal value to be 0 as

$$\mathbf{w*'} = \mathbf{w'} \cdot \mathbf{j}_{\mathbf{n}} \mathbf{V} \mathbf{j}_{\mathbf{0}}$$

This last expression can also be obtained by complementing w\* using the following relations.

$$j_{n}' = j_{0} \vee j_{1}$$

$$j_{1}' = j_{0} \vee j_{n}$$

$$j_{0}' = j_{1} \vee j_{n}$$

$$j_{n} \cdot j_{1} = j_{n} \cdot j_{0} = j_{1} \cdot j_{0} = 0$$

Now, for a given fault-free combinational circuit realizing some Boolean function f, the corresponding f\* and f\*' can be calculated by successively substituting each edge of the circuit with its \* expressions. The formulations of f\* and f\*' can start either from the input edges working towards the output edges or from the output edges working backward towards the input edges. After complete substitutions, the f\* and f\*' will be functions of input variables and fault parameters of the circuit edges. The \* expressions for a given set of faults are then obtained by substituting the corresponding fault parameters with the faulty signal values to realize the fault conditions. Let  $\overline{f}^*$  and  $\overline{f}^*$  be the \* expressions of the combinational circuit with the given set of faults, a test t which detects these faults is calculated using the following relation

$$t = (f^* \cdot \bar{f}^{*}) V (f^{*} V \bar{f}^{*}).$$

Poage's method is easy to use for relatively small combinational circuits. But for large scale combinational circuits, the computations required in calculating the \* expressions would be quite substantial. Also the method is based on the assumption of the existence of tests. Such is not the case in real situations.

# 2.3.5 Boolean Differen

Sellers et al. [36] developed another mathematical method called the <u>Boolean difference method</u> for generating tests for combinational circuits. For a combinational circuit with an output variable f and input variables  $x_1$ ,  $x_2$ , ...,  $x_n$ , the Boolean difference of the output variable with respect to one of the input variables  $x_i$  is defined as

$$\frac{df}{dx_{i}} = f(x_{1}, x_{2}, \dots, x_{i-1}, 0, x_{i+1}, \dots, x_{2}) + f(x_{1}, x_{2}, \dots, x_{i-1}, 1, x_{i+1}, \dots, x_{n})$$

where + is the EXCLUSIVE OR operation. If  $\frac{df}{dx_i} = 0$ , then f is independent of  $x_i$ . On the other hand, if  $\frac{df}{dx_i} = 1$ , f will be a function of  $x_i$  and then

$$x_i \frac{df}{dx_i}$$

is a test for  $x_i$  s-a-0

and  $x_i^{\dagger} \frac{df}{dx_i}$  is a test for  $x_i$  s-a-1.

Tests for all the input variables and edges of the circuit are then combined to form tests for the entire circuit.

#### 2.3.6 Chang's CGEM Method

Chang [5] developed a mathematical model called the Complete Gate Equivalent Model for combinational circuits. Using this model, a set of Boolean expressions in the form of sums of products are formulated to completely describe the logical functions realized by a combinational circuit. Each product term of the expressions represents a set of paths which he calls a  $z_{i-1}$  or  $z_{i-0}$  set depending on the signal value at the output when such a set is sensitized. Faults occurring on the set will cause shrinkage or growth of the product term of the set corresponding to a decrease or increase of the number of logical gates covered by the set. To detect the faults, every product term must be investigated for shrinkage or growth. The tests for the combinational circuit are thus obtained from testing every product term for shrinkage or growth. The method is explained using one of his examples as follows.

# Example 2.3

The Boolean expressions for the circuit in Figure 2.7 as obtained from its CGEM model are:

$$E_{1}^{"} = \bar{x}_{1}x_{3} + \bar{x}_{2}x_{3} + \bar{x}_{3}x_{4} + x_{5},$$

$$\bar{E}_{2}^{"} = \bar{x}_{1}\bar{x}_{2} + x_{3}\bar{x}_{5} + \bar{x}_{4}\bar{x}_{5},$$

where  $\bar{x}_i$  means  $x_i$  assumes 0 and  $E_i$  is the Boolean expression for  $z_i$ .

To detect shrinkage on  $\bar{x}_1 x_3$  of  $E_1^*$ , for example, an input vector,  $M_1$ , can be found by intersecting this term with the complement of every other term of  $E_1^*$ .

$$M_1 = \overline{x}_1 x_3 \quad (\overline{\overline{x}_2 x_3}) \quad (\overline{\overline{x}_3 x_4}) \quad \overline{x}_5 = \overline{x}_1 x_2 x_3 \overline{x}_5$$

Since  $\bar{\mathbf{x}}_1 \mathbf{x}_3$  will cause  $\mathbf{z}_1$  to assume 1 as indicated by  $\mathbf{E}_1^{"}$  assuming 1 under a fault-free situation, the above calculation can be interpreted as  $\mathbf{M}_1$  will detect a shrinkage of  $\bar{\mathbf{x}}_1 \mathbf{x}_3$ , i.e., stuck-at-0 faults on paths represented by  $\bar{\mathbf{x}}_1 \mathbf{x}_3$ , if all other terms assume 0. In effect  $\bar{\mathbf{x}}_1 \mathbf{x}_3$  is sensitized with  $\mathbf{M}_1$ .

To detect a growth on  $\bar{x}_1 x_3$ , i.e., stuck-at-1 faults, every variable of  $\bar{x}_1 x_3$  must be investigated since a growth can occur to each variable. The calculations are as follows,

$$M_{8} = x_{3} \quad \bar{E}_{1}^{"} = x_{1}x_{2}x_{3}\bar{x}_{5},$$

$$M_{9} = \bar{x}_{1} \quad \bar{E}_{1}^{"} = \bar{x}_{1}\bar{x}_{3}\bar{x}_{4}\bar{x}_{5}.$$

Thus  $\{M_1, M_8, M_9\}$  will detect all faults on paths of  $\overline{x}_1 x_3$ . Doing this for every term of the expressions and finding a minimum covering for all the M's terms obtained, a test is formed.

Chang's method is straightforward and his CGEM model is flexible to suit a wide range of combinational circuits. However, separate tests are needed for fault location when using his method.

# 2.4 Methods of Test Generation for Sequential Circuits

Fault analysis of sequential circuits is a more involved and complicated task than that of combinational circuits. First, tests must be generated for every possible state of the sequential circuit. Hence the amount of computations required to generate the total set of tests for the sequential circuit is proportional to the number of states it possesses. Second, there is the problem of initiating the sequential circuit to some known state before testing can be performed on it. This initialization procedure is in itself a necessary portion of any fault detection technique for sequential circuits.

Most methods known for fault detection of sequential circuits approach the problem at the state level; while relatively few methods treat the problem at the circuit level. The approach of Poage's method can be classified as belonging to the latter category.

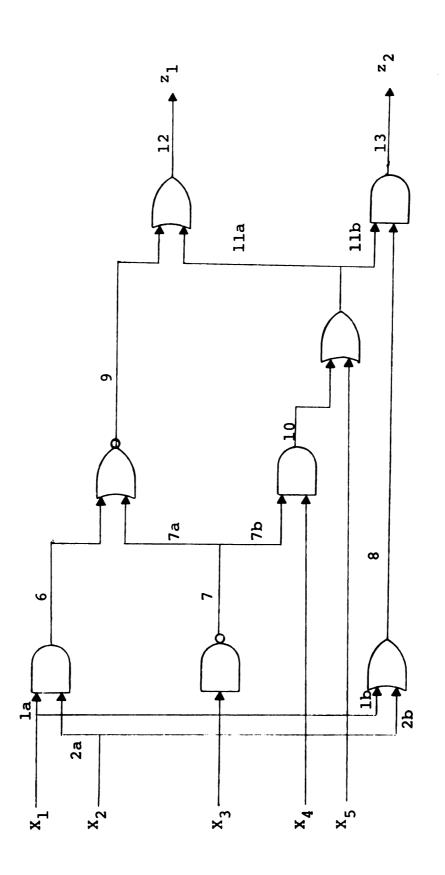

#### 2.4.1 Poage's Method

Poage's method [33] for test generation for sequential circuits is essentially an extension of his method for combinational circuits. The feedback loops of the sequential circuit are assumed open to make the circuit combinational. The formulation of the good and faulty circuits are then done using his method for combinational circuits. Also a reset mechanism is assumed to be available to set the circuit to some known starting state. After these initial steps, the flow tables corresponding to the good and faulty circuits are built. The main part of Poage's method involves combining these flow tables into a composite fault table from which optimal test sequences for given faults are derived. The method is demonstrated using an example as follows.

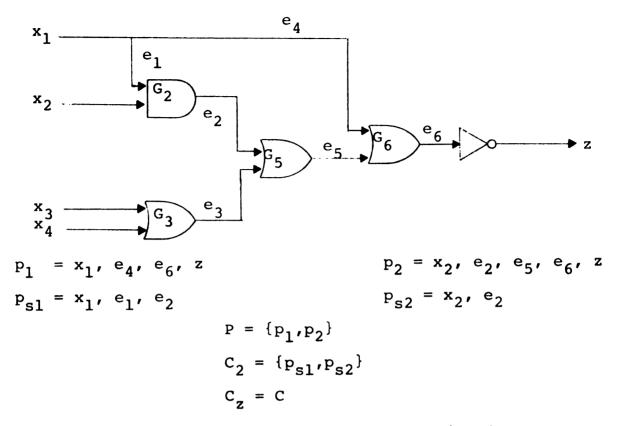

#### Example 2.4

The circuit for the example is shown in Figure 2.8 with the set of faults T,

$$T = \{e_2^1, e_3^1, e_4^1, e_5^0\}$$

where  $e_i^1$  and  $e_i^0$  indicate  $e_i^1$  s-a-1,  $e_i^1$  s-a-0 respectively.

Conceptually opening the feedback and applying Poage's method for combinational circuits to the resulting circuit, one gets the output and next state expressions for the good and each faulty circuit as follows.

Fig. 2.8.--A sequential circuit for Poage's method.

| For good circuit<br>M        | Y = x'y V xy'<br>f = xy                                                                                  |

|------------------------------|----------------------------------------------------------------------------------------------------------|

| For $e_2^1$ circuit<br>$M_2$ | $\begin{array}{l} \mathbf{Y}_{2} = \mathbf{x}'\mathbf{y} \\ \mathbf{f}_{2}^{2} = \mathbf{x} \end{array}$ |

| For $e_3^1$ circuit<br>$M_3$ | $\begin{array}{l} Y_{3} = x'  V  y' \\ f_{3}^{3} = xy \end{array}$                                       |

| For $e_4^1$ circuit $M_4$    | $\begin{array}{l} Y_{4} = x V y \\ f_{4}^{4} = xy \end{array}$                                           |

| For $e_5^0$ circuit $M_5$    | $\begin{array}{l} Y_{5} = xy'\\ f_{5}^{5} = xy \end{array}$                                              |

Corresponding to these Boolean expressions, the flow tables for the good and faulty circuits are built as shown in Table 2.3.

| Table | 2.3Flow | tables   | for   | good   | and   | faulty | circuits | for |

|-------|---------|----------|-------|--------|-------|--------|----------|-----|

|       | exam    | ple of I | Poage | e's me | ethod | 1.     |          |     |

|   |   | x   |     |   |                | х   |     |   |                | x   |     |

|---|---|-----|-----|---|----------------|-----|-----|---|----------------|-----|-----|

|   | Т | 0   | 1   |   | <sup>т</sup> 2 | 0   | 1   |   | т <sub>3</sub> | 0   | 1   |

| У | 0 | 0/0 | 1/0 | У | 0              | 0/0 | 0/1 | У | 0              | 1/0 | 1/0 |

|   | 1 | 1/0 | 0/1 |   | 1              | 1/0 | 0/1 |   | 1              | 1/0 | 0/1 |

|   |                | x   |     |   |   | x   |     |

|---|----------------|-----|-----|---|---|-----|-----|

|   | т <sub>4</sub> | 0   | 1   |   |   | 0   |     |

| У | 0              | 0/1 | 1/0 | У |   | 0/0 | 1   |

|   | 1              | 1/1 | 1/1 |   | 1 | 0/0 | 0/1 |

The main idea of Poage's method is to find input sequences which will produce different outputs for the good and the faulty circuits. To do this, the next step is to form a set of <u>product tables</u> by pairwise concatenating the flow table of the good circuit with that of each of the faulty circuits. This concatenating procedure starts with the common starting state of the sequential circuit. The procedure terminates as soon as a product output with different components appears in the product table.

The product tables thus formed for the example are shown in Table 2.4 where the product outputs with different components are marked in circles.

Test sequences for a given fault are derived from the corresponding product table. The test sequences are

|                 |                    | x     |       |                 |                    | x     |       |

|-----------------|--------------------|-------|-------|-----------------|--------------------|-------|-------|

|                 | <u>T x T</u> 2     | 0     | 1     |                 | тхт <sub>3</sub>   | 0     | 1     |

| <sup>уу</sup> 2 | 0 0                | 00/00 | 10/01 | уу <sub>3</sub> | 0 0                | 01/00 | 11/00 |

|                 |                    |       |       |                 | 0 1                | 01/00 | 10/01 |

|                 |                    |       |       |                 | 11                 | 11/00 | 00/11 |

|                 |                    | x     |       |                 |                    | x     |       |

|                 | T x T <sub>4</sub> | 0     | 1     |                 | T x T <sub>5</sub> | 0     | 1     |

|                 | 0 0                | 00/00 | 11/00 |                 | 0 0                | 00/00 | 11/00 |

| УУ <b>4</b>     | 1 1                | 11/00 | 01/11 | уу <sub>5</sub> | 11                 | 10/00 | 00/11 |

|                 | 0 1                | 01/00 | 11/01 |                 | 10                 | 10/00 | 01/10 |

|                 |                    |       |       |                 |                    |       |       |

Table 2.4.--Product tables for example of Poage's method.

v

simply input sequences which, when applied to the corresponding product table, yield the product output with different components. For example, the test sequences for product table T x T<sub>2</sub> detecting  $e_2^1$  can readily be seen as

$t_{21} = 0^n, 1 \quad n \ge 0.$

To find a single optimal test sequence to detect all of the given faults of the sequential circuit, Poage forms the <u>sequential fault table</u> which is simply a composite table of the product tables. The optimal test sequence can then be found from this sequential fault table. Using his technique, the optimal test sequence is found to be

3.7

# t = 0, 1, 0, 1, 1,

in which 0, 1 covers T x  $T_2$  and T x  $T_3$ ,

0, 1, 0, 1 covers T x  $T_2$ , T x  $T_3$  and T x  $T_5$  and 0, 1, 0, 1, 1 covers T x  $T_2$ , T x  $T_3$  and T x  $T_4$ .

Poage's method in finding optimal test sequences provides a closer look at the fault detection problem at the circuit level. It is also straightforward and easy for computer implementation. But his method involves calculations for each individual fault and hence is not very economical from a practical viewpoint.

# 2.4.2 Other Methods of Fault Detection of Sequential Circuits

Most other methods in designing test sequences for sequential circuits are based on the input-output relations of the corresponding sequential machine. The earliest work using this approach is done by Moore [29] in his <u>gedankenexperiments</u>. In this experiment, he treated the sequential machine under test as a <u>black box</u> on which input sequences are to be applied. Considering the set of sequential machines consisting of the fault-free machine and its failed copies each containing one of the permissible faults, the input-output experiment induces a partition on the set with respect to the outputs obtained. Successive experiments will refine the partition and will finally identify each machine of the set with one of the permissible faults or as fault-free.

Moore's approach was widely applied by other researchers in designing other methods for generating test experiments called checking experiments for sequential machines. In most cases, these methods apply to sequential machines possessing certain characteristics. Hennie [14] introduced the transition checking approach for generating checking experiments for sequential machines which possess a distinguishing sequence (an input sequence used to identify the initial state of the machine) and do not increase the number of states from malfunction. Hsieh [15] developed several procedures for generating checking experiments for sequential machines which do not possess any distinguishing sequences. His methods, however, are based on other types of characteristic sequences; the compound distinguishing sequence, the resolving sequence, the compound resolving sequence, and the simple I/O sequence.

Researchers like Kime [17], Kohavi [18, 19], and others have published their results along the same line.

Some authors have suggested addition of extra external hardware, modification of the sequential machine or embedding the machine in a larger equivalent machine [17, 18, 22] to create certain desirable characteristics for designing checking experiments. Detailed discussions of these methods will not be presented in the paper.

#### CHAPTER III

# FAULT DETECTION AND DIAGNOSIS OF COMBINATIONAL CIRCUITS BY THE PATH CHECKING METHOD

The path checking method approaches the task of fault detection and diagnosis of switching circuits by checking all the paths of the circuits to ensure that they propagate the signals correctly. Through this process, a set of detection tests are obtained which can be used for detection purposes. The detection phase will locate the given faults to some general areas of the circuits. The diagnosis phase will then proceed based on these results.

In this chapter, the path checking method as used in the fault detection and diagnosis of combinational circuits is presented. Two algorithms for fault detection and diagnosis are formulated using this method.

The type of combinational circuits treated using this method possesses the following characteristics:

- a. Multiple inputs and multiple outputs.

- b. Path fan-out reconvergence allowed.

- c. All paths being sensitizible.

Thus the only restriction imposed on the type of combinational circuits is that every path of the circuit be sensitizible. This, however, will not place any limitations on the range of real applications of this method, since unsensitizible paths represent redundancy and their removal will not affect the logical behavior of the circuits.

Faults treated are both single and multiple, but are of permanent stuck-at type. The type of logical elements considered are as discussed in Chapter II.

# 3.1 Some Network Properties of Combinational Circuits

A brief study of some of the network structural properties of the combinational circuits as they relate to the path checking method will be presented here. This discussion will help one visualize the combinational circuits from the "path" point of view.

A combinational circuit can be viewed as a set of interconnected paths such that the <u>leading</u> and <u>trailing</u> edges of the paths form the input and output edges of the circuit. For a single-output combinational circuit all of its paths will eventually converge to the single trailing edge. All fan-out paths residing in it will have to meet one another before reaching the trailing edge. But in the case of a multiple-output combinational circuit, fan-out paths need not meet one another, since they may lead to different output edges of the circuit. The multiple-output combinational circuit is characterized by the existence of fan-outs branching to different output edges of the circuit. Such fan-outs do not reconverge. Other fan-outs may lead to the same output edges thus forming fan-out reconvergence.

Consider a combinational circuit C with n input edges  $x_i$ ,  $1 \le i \le n$ , m output edges  $z_j$ ,  $1 \le j \le m$  and the set of q labelled edges  $E = \{e_k, 1 \le k \le q\}$ . The edges are so labelled such that the output edge of any logical element will have a label with higher order than that of the label assigned to any input edge of the logical element. Also fan-out edges (edges which are branches of a common edge) are assigned different labels. A path and a <u>subpath</u> are defined as follows.

#### Definition 3.1

A path p of C is a sequence of edges  $p = l_1, l_2, \ldots, l_p$  such that

- l, the leading edge of the path, is an input edge of C,

- 2. l<sub>p</sub>, the trailing edge of the path, is an output edge of C, and

- 3. l<sub>i</sub> and l<sub>i+1</sub>, 1≤i≤p-1, are either respectively an input edge and the output edge of the same logical element or l<sub>i+1</sub> is a fan-out edge of l<sub>i</sub>.

#### Definition 3.2

A subpath  $p_s$  of C is a section of a path p such that  $p_s$  includes either the leading edge or the trailing edge of p.

The number of paths in a multiple-output combinational circuit is of interest in estimating the amount of computation needed in designing tests. For a multipleoutput combinational circuit possibly with fan-out reconvergence, the number of paths is found in the following theorem.

#### Theorem 3.1

The number of paths in a multiple-output combinational circuit C with n input edges, m output edges, k fan-outs and l logical elements are

$$n_{p} = n + \sum_{i=1}^{k} (n_{Fi} - 1) = m + \sum_{i=1}^{\ell} (n_{Gi} - 1)$$

where  $n_{Fi}$  is the number of branches at fan-out  $F_i$  and  $n_{Gi}$  is the number of edges feeding logical element  $G_i$ .

Proof: To compute the number of paths from the number of input edges, since every path must start with an input edge, the number of paths is the sum of this value plus extra paths introduced with fan-out branches. For a fan-out F branching into  $n_F$  paths,  $n_F - 1$  will be the extra paths introduced with this fan-out. To obtain the number of paths from the number of output edges, interchange the roles of inputs and outputs, with each logical element playing the role of a fan-out. Q.E.D.

The concepts of <u>subcircuits</u>, <u>partial circuits</u>, and <u>constituent circuits</u> of a combinational circuit are presented here as they will prove useful in later discussions.

#### Definition 3.3

A <u>subcircuit</u> within a combinational circuit includes all the subpaths of the circuit leading to an edge (need not be a trailing edge) of the circuit.

#### Definition 3.4

A <u>partial circuit</u> within a combinational circuit includes a set of paths sharing an output edge of the combinational circuit as their common trailing edge.

#### Definition 3.5

A <u>constituent circuit</u> of a multiple-output combinational circuit includes all the paths sharing an output edge of the combinational circuit as their common trailing edge.

#### Example 3.1

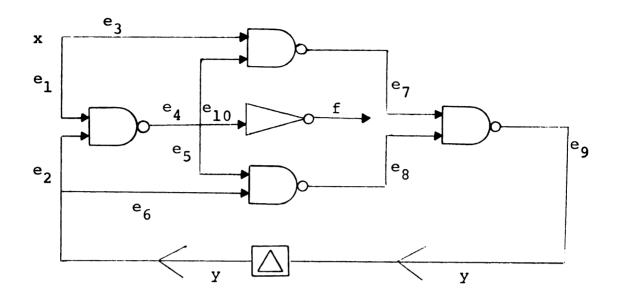

These definitions are illustrated in the combinational circuit C of Figure 3.1. Paths include  $p_1$  and  $p_2$ ; subpaths include  $p_{s1}$  and  $p_{s2}$ ; P is the partial circuit formed from  $p_1$  and  $p_2$ ; while  $C_2$  is the subcircuit formed

# Fig. 3.1.--Examples of paths, subpaths, subcircuits, partial circuits, and constituent circuits of a combinational circuit.

from  $p_{s1}$  and  $p_{s2}$  with the subscript 2 indicating that the edge  $e_2$  is its output edge and the constituent circuit  $C_z$  corresponds to the combinational circuit C itself.

# 3.2 Path Sensitization of Combinational Circuits