# This is to certify that the

dissertation entitled

Minority Carrier Injection in Schottky Barrier

Diodes

presented by

Mohsen Alavi

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Electrical Engineering

D. K. Renkard

Major professor

Date <u>August 12, 1986</u>

MSU is an Affirmative Action/Equal Opportunity Institution

0-12771

RETURNING MATERIALS:

Place in book drop to remove this checkout from your record. FINES will be charged if book is returned after the date stamped below.

# MINORITY CARRIER INJECTION IN SCHOTTKY BARRIER DIODES

ву

Mohsen Alavi

## A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Electrical Engineering and Systems Science

#### ABSTRACT

#### "MINORITY CARRIER INJECTION IN SCHOTTKY BARRIER DIODES"

Ву

#### Mohsen Alavi

For low to moderate current densities, current flow in Schottky barrier diodes (SBDs) is primarily due to majority carrier injection over the metal-semiconductor interface. However, at high current densities, such as are encountered in advanced integrated circuits, minority carrier effects become significant. The objective of this study was to experimentally verify and quantify minority carrier injection in platinum-silicide SBDs, develop boundary conditions expressing carrier injection at the metal-semiconductor interface which extend to high injection conditions, and correlate the results with numerical simulation. Two experimental measures of minority carrier injection have been investigated, minority carrier storage and conductivity modulation. Also, new methods have been devised to accurately determine the barrier height of the SBD from its I-V characteristics.

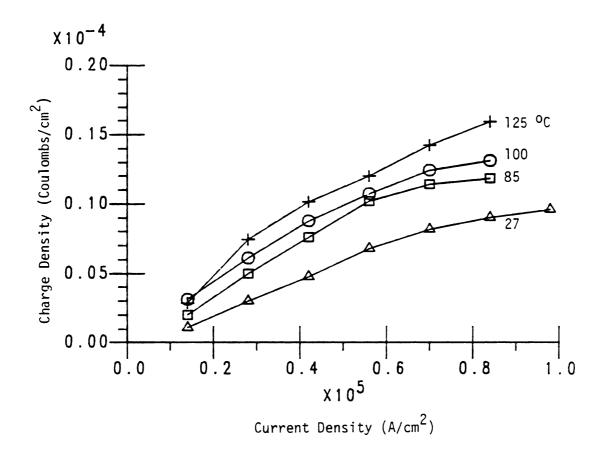

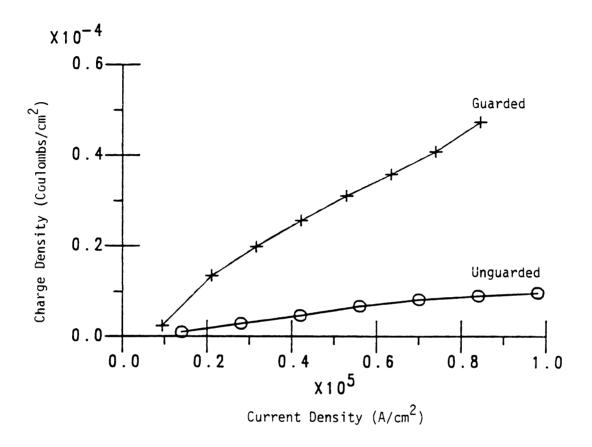

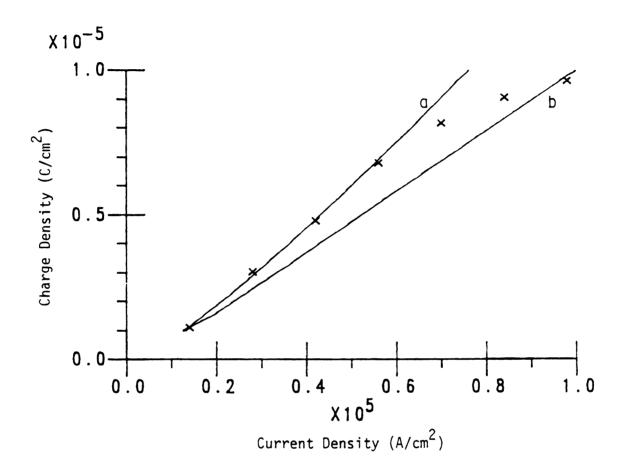

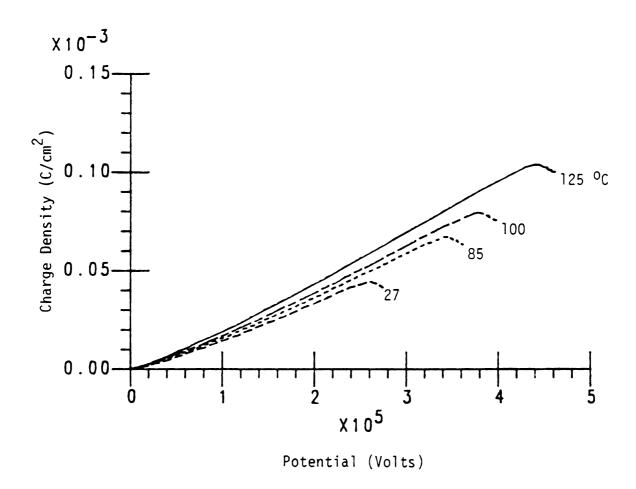

Minority carrier storage has been experimentally determined by integration of the reverse bias switching current which, after correction for capacitance stored charge, yields the minority carrier charge removed from the diode on switching from forward to reverse bias. The stored charge was found to increase monotonically both with temperature and forward biased current over the experimental range of  $27^{\circ}\text{C}$  to  $125^{\circ}\text{C}$  and  $10^4 \text{A/cm}^2$  to  $10^5 \text{A/cm}^2$ . For 12.5X12  $\mu\text{m}$  unguarded SBDs fabricated on a 1  $\mu\text{m}$  thick n-type epitaxial layer, stored minority carrier charge at  $10^5 \text{A/cm}^2$  was on the order of  $10^{-5} \text{C/cm}^2$ . For guarded SBDs, the stored

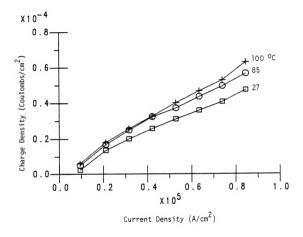

minority carrier charge was higher, on the order of  $5 \times 10^{-5}$  C/cm<sup>2</sup> at  $10^5$  A/cm<sup>2</sup>. Conductivity modulation was investigated by current-voltage measurements at current densities up to  $4 \times 10^5$  A/cm<sup>2</sup> and was found to be appreciable, causing the series resistance of the diode to decrease by approximately a factor of 5 at the higher currents.

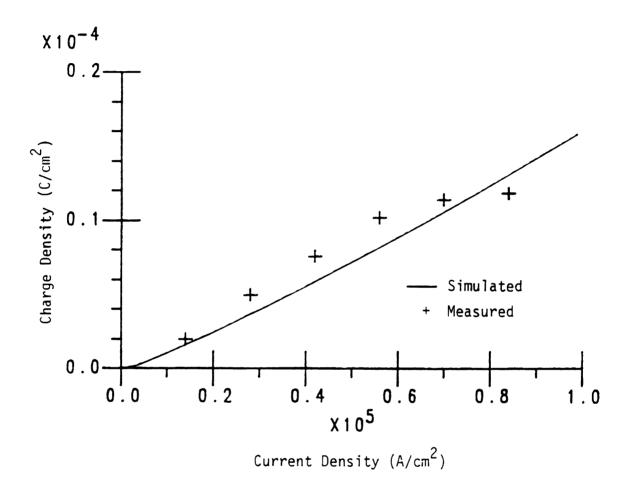

One dimensional numerical simulation results using traditional boundary conditions agree well with both charge storage and conductivity modulation measurements up to  $5 \text{X10}^4 \text{ A/cm}^2$ . At higher current densities, however, there is significant difference between simple simulation results and experiment, and additional phenomena including hole tunneling, image-force induced band-gap shrinkage, hole barrier height lowering at high injection, Auger recombination, and lateral voltage drop are considered.

#### ACKNOWLEDGEMENT

I wish to express my greatest appreciation to my parents for their continued support and encouragement throughout my studies. To Dr. D.K. Reinhard, my thesis advisor, I express my deep gratitude for his guidance throughout this project. Special thanks are also due to C.C. Yu for providing the numerical simulation results and helpful discussions, and to my guidance committee members, Dr. P.D. Fisher, Dr. J. Asmussen, Dr. C. Foils, and Dr. J. Freeman. This work was supported by the International Business Machines Corporation.

#### TABLE OF CONTENTS

|                                                                                                                                                                                                                                                                                                                                                                                                                             |            | page                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------|

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                              |            | vi                                                       |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                             |            | vii                                                      |

| CHAPTER ONE: INTRODUCTION 1.1 Statement of Problem 1.2 Preview of Contents 1.3 Main Contributions of this Work                                                                                                                                                                                                                                                                                                              |            | 1<br>1<br>4<br>6                                         |

| CHAPTER TWO: BACKGROUND 2.1 Introduction 2.2. Structure of a Planar SBD 2.3 Current Transport Mechanisms 2.4 Effects of Minority Carrier Injection 2.5 Review of Previous Work on Minority Carrier Injecti 2.5.1 Theory 2.5.2 Experiment                                                                                                                                                                                    | <br><br>on | 8<br>8<br>10<br>10<br>14<br>18<br>18<br>21               |

| CHAPTER THREE: EXPERIMENT  3.1 Introduction  3.2 Test Devices  3.3 Measurement of Minority Carrier Storage  3.3.1 Experimental Method  3.3.2 Correction for the Parasitic Capacitance  3.3.3 Experimental Limits and Accuracy  3.3.4 Minority Carrier Storage Results  3.4 Measurement of Current-Voltage Characteristics  3.4.1 Experimental Method  3.4.2 Experimental Limits and Accuracy  3.4.3 Current-Voltage Results |            | 27<br>27<br>29<br>29<br>35<br>38<br>39<br>48<br>48<br>51 |

| CHAPTER FOUR: THEORETICAL SIMULATION 4.1 Introduction 4.2 Basic Theory 4.2.1 Basic Equations 4.2.2 Carrier Generation 4.2.3 Carrier Recombination 4.2.4 Traditional Boundary Conditions 4.3 The Effect of Image Force on Boundary Conditions 4.3.1 Energy Bands Near the Barrier 4.3.2 Low Bias Condition                                                                                                                   |            | 56<br>56<br>57<br>57<br>59<br>60<br>62<br>63<br>63<br>64 |

|           |                                                       | page       |

|-----------|-------------------------------------------------------|------------|

| 4.4       | Reference of Municipal on Descriptions                | 70         |

| 4.4       | Effect of Tunneling on Boundary Conditions            | 74         |

| 4.6       | Correction for the Lateral Voltage Drop               | 78         |

| 4.0       | Method of Approach                                    | 78         |

|           |                                                       | 78         |

|           | 4.6.2 Approach of this Work                           | 79         |

|           | 4.6.3 Parameter Determination                         | /9         |

| CHAPTER E | FIVE: BARRIER HEIGHT DETERMINATION                    | 81         |

| 5.1       | Introduction                                          | 81         |

| 5.2       | Barrier Height Lowering and the Ideality Factor       | 82         |

| 5.3       | The Activation Energy Method                          | 88         |

| 5.4       | The Richardson's Constant Method                      | 89         |

| 5.5       | Modified Norde's Method                               | 90         |

| 5.6       | Results and Discussions                               | 94         |

| 5.7       | Chapter Summary and Conclusions                       | 104        |

|           |                                                       |            |

| CHAPTER S |                                                       | 106        |

| 6.1       | Introduction                                          | 106        |

| 6.2       | Basic Simulation                                      | 108        |

|           | 6.2.1 Simulation Method                               | 108        |

|           | 6.2.2 Current-Voltage Comparison                      | 108        |

|           | 6.2.3 Stored Minority Carrier Comparison              | 111        |

| 6.3       | Simulation Corrected for Lateral Voltage Drop         | 114        |

|           | 6.3.1 Simulation Method                               | 114        |

|           | 6.3.2 Current-Voltage Comparison                      | 115        |

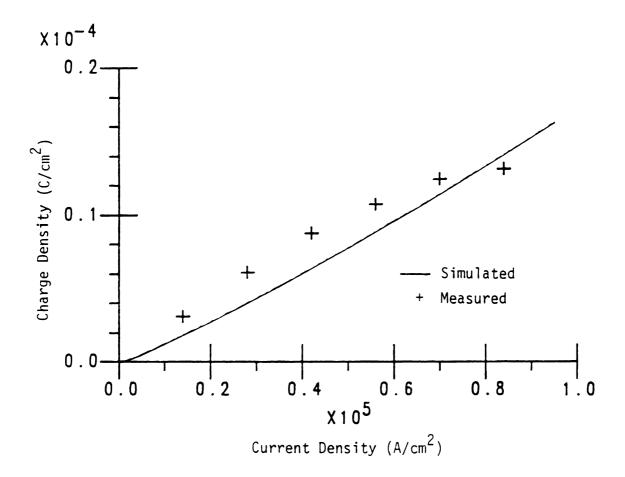

|           | 6.3.3 Stored Minority Carrier Comparison              | 115        |

|           | 6.3.4 Additional Remarks                              | 120        |

| 6.4       | Boundary Condition Corrections                        | 122        |

|           | 6.4.1 The simulation method                           | 122        |

|           |                                                       | 122        |

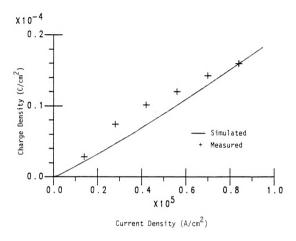

|           | 6.4.3 Stored Minority Carrier Comparison              | 124        |

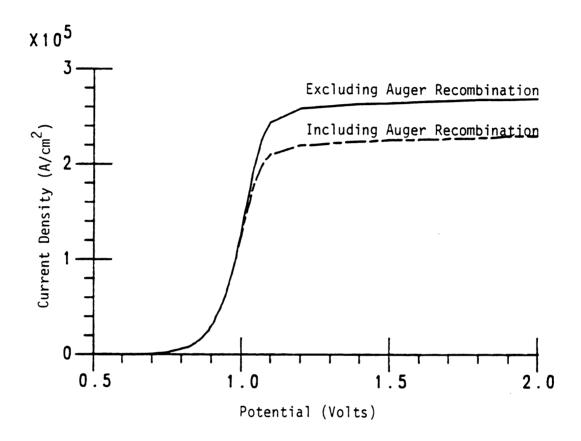

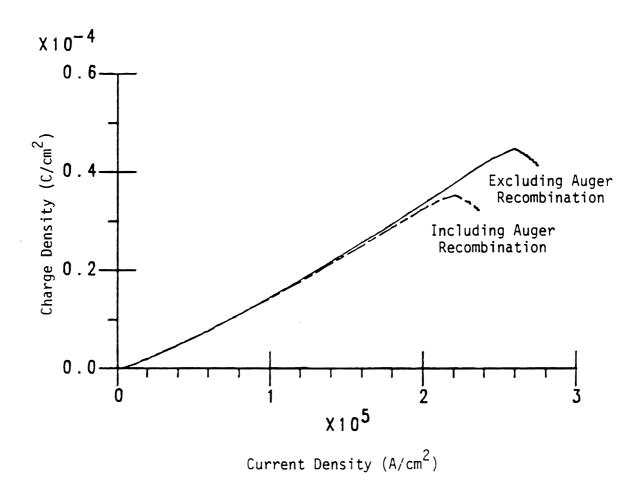

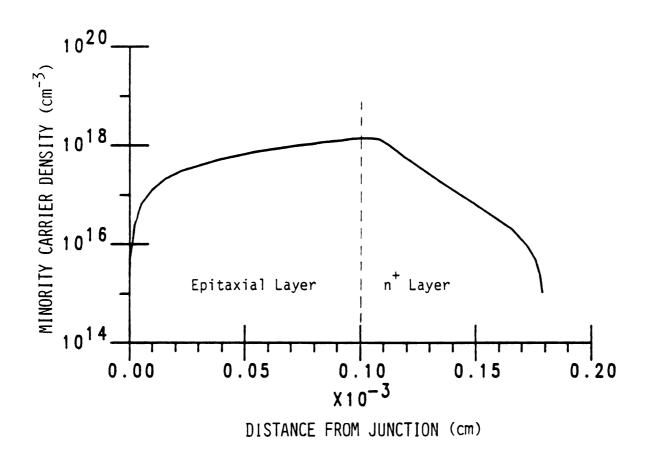

| 6.5       | Consideration of Auger Recombination                  | 128        |

|           | 6.5.1 The Simulation Method                           | 128        |

|           | 6.5.2 Effect of Auger Recombination on the Simulation | 128        |

|           | 6.5.3 Effect of Auger Recombination on Experiment     | 131<br>136 |

| 6.6 Н     | igh Temperature Comparison                            | 136        |

| CHAPTER S | SEVEN: CONCLUDING REMARKS                             | 145        |

| 7.1       | Summary of Major Results and Conclusions              | 145        |

| 7.2       | Suggestions for Further Investigations                | 148        |

|           |                                                       |            |

| APPENDIX  |                                                       | 150        |

| A.1       | Krakauer's Method                                     | 150        |

| A.2       | Charge Integration Measurement                        | 152        |

|           | A.2.1 The Circuit                                     | 152<br>155 |

|           | A.2.2 Data Acquisition                                | 157        |

| A.3       | Sample Mounting                                       |            |

| A.4       | Current-Voltage Measurement                           | 158<br>159 |

| A.5       | Test Device Integrity                                 | 159        |

| APPENDIX  | B: DERIVATION OF THE HIGH INJECTION HOLE TUNNELING    |            |

|           | BOUNDARY CONDITION                                    | 161        |

| ALIENDIA  | C: DERIVATIONS CORRESPONDING TO BARRIER HEIGHT MEASUREMENT METHODS | 165 |

|-----------|--------------------------------------------------------------------|-----|

| C.1       | Modified Richardson's Constant Method                              | 165 |

| C.2       | Modified Norde's Method                                            | 166 |

| ITST OF I | REFERENCES                                                         | 169 |

## LIST OF TABLES

| Table |                                                                                                                                                                                                                                                                | page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5-1   | Experimentally determined current density axis intercepts and ideality factors                                                                                                                                                                                 | 96   |

| 5-2   | Barrier height values obtained from; (a) original Richardson's constant method using Equation 5-7, (b) modified Richardson's constant method using Equation 5-17.                                                                                              | 97   |

| 5-3   | Barrier height values obtained from; (a) original Norde's method, (b) Norde's method modified by Schwartz et. al. [47] to account for the ideality factor $\eta$ , (c) Norde's method modified to account for barrier lowering $\Delta\Phi$ , as in this work. | 99   |

| 6-1   | Hole Auger lifetimes and Auger diffusion lengths in silicon under various conditions. (a) For Auger coefficient, $g = 10^{-31}$ cm <sup>6</sup> /s, (b) for $g = 7 \times 10^{-31}$ cm <sup>6</sup> /s.                                                        | 132  |

#### LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                                                   | page |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

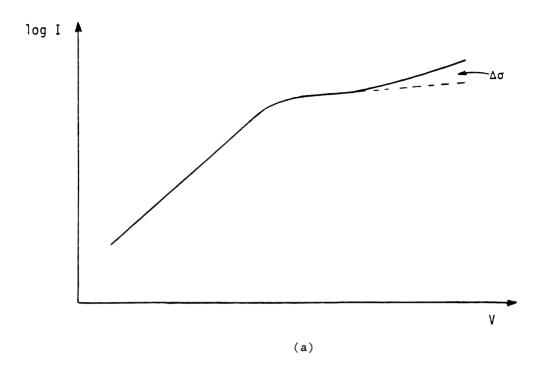

| 1-1    | Minority carrier injection results in excess carrier storage which changes device characteristics in two principal ways. (a) The bulk conductivity is modulated. (b) Switching delay is induced.                                                                                                                  | 3    |

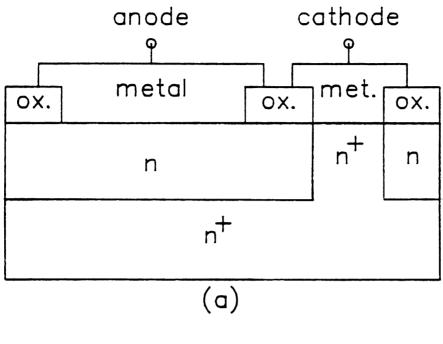

| 2-1    | Structure of a planar SBD. (a) Unguarded. (b) Guarded                                                                                                                                                                                                                                                             | 11   |

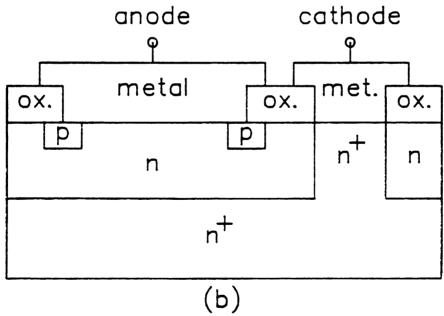

| 2-2    | Energy band diagram of a planar SBD neglecting the effects of image-force at the metal-semiconductor interface                                                                                                                                                                                                    | 12   |

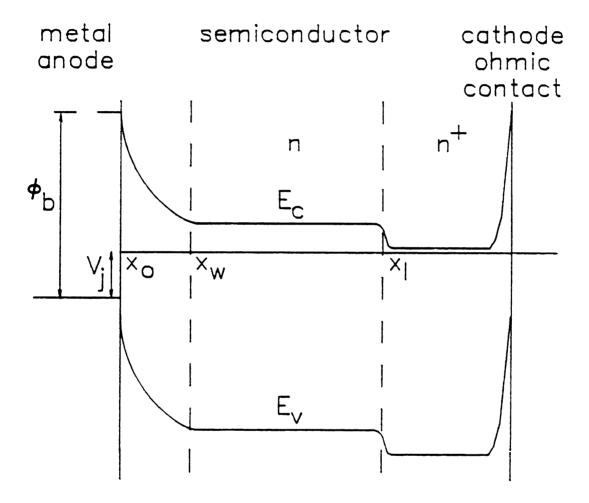

| 2-3    | Current transport mechanisms over the metal semiconductor interface.                                                                                                                                                                                                                                              | 13   |

| 2-4    | Dynamics of reverse-recovery for a semi-infinite device initially under low to moderate forward bias. (a) Hole concentration profile. (b) Switching current.                                                                                                                                                      | 16   |

| 2-5    | SPICE simulation results for the current through a diode excited by a sinusoidal signal when minority carrier storage is not present.                                                                                                                                                                             | 24   |

| 2-6    | SPICE simulation results for the current through a diode excited by a sinusoidal signal when minority carrier storage in the diode is significant.                                                                                                                                                                | 25   |

| 3-1    | Metallization layout of the unguarded SBD                                                                                                                                                                                                                                                                         | 30   |

| 3-2    | Doping profile of silicon under the anode of the SBD. Data from C.C. Yu [4]                                                                                                                                                                                                                                       | 31   |

| 3-3    | Response of a 30 $\mu\text{m}^2$ unguarded test device to sinusoidal excitation at room temperature. (a) Shows the response at a peak current density of 2.67 X 10^4 A/cm² and does not show a significant amount of minority carrier storage. (b) Shows the response at a peak current density of 10^5 A/cm² and |      |

|        | evidence of minority carrier storage is clearly observed                                                                                                                                                                                                                                                          | 32   |

| 3-4    | Diagram of the circuit for minority carrier charge storage measurement along with its equivalent circuit                                                                                                                                                                                                          | 34   |

| Figu | ce                                                                                                                                                                                                  | page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

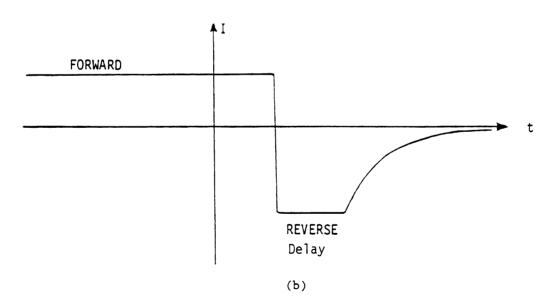

| 3-5  | Idealized reverse-recovery waveforms. (a) Corresponds to a purely capacitive response while (b) shows the minority carrier induced switching delay                                                  | 37   |

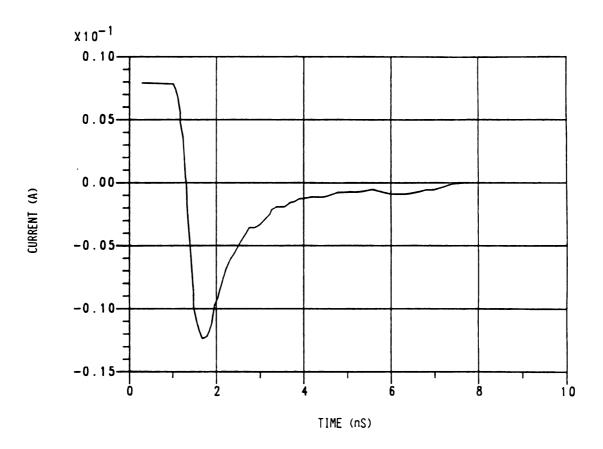

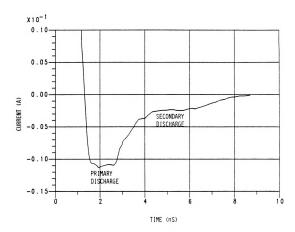

| 3-6  | diode at room temperature, corresponding to a forward                                                                                                                                               |      |

|      | current density of 5.6 X 10 <sup>3</sup> A/cm <sup>2</sup> prior to switching                                                                                                                       | 40   |

| 3-7  | diode at room temperature, corresponding to a forward                                                                                                                                               |      |

|      | current density of 7 X 10 <sup>4</sup> A/cm <sup>2</sup> prior to switching                                                                                                                         | 41   |

| 3-8  | Measured reverse-recovery waveforms of the unguarded test diode at room temperature. Values of current density prior                                                                                |      |

|      | to switching are (a) $5.5X10^3$ A/cm <sup>2</sup> , and (b) $4.2X10^4$ A/cm <sup>2</sup> .                                                                                                          | 43   |

| 3-9  |                                                                                                                                                                                                     |      |

|      | diode corresponding to a current density of 4.2 X $10^4$ A/cm <sup>2</sup> prior to switching. (a) Shows the response at 27 °C, and (b) shows the response at 125 °C                                | 44   |

| 3-10 | Measurement results for the charge density associated with stored excess minority carriers at four temperatures. The results correspond to average of the data obtained for four unguarded devices. | 45   |

| 3-11 | Measurement results for the charge density associated with stored excess minority carriers at three temperatures for a guarded device                                                               | 46   |

| 3-12 | Comparison of room temperature results of the stored minority carrier charge density between guarded and unguarded devices.                                                                         | 47   |

| 3-13 | Switching response of a guarded diode at room temperature                                                                                                                                           |      |

|      | corresponding to a current density of 4.2 X 10 <sup>4</sup> A/cm <sup>2</sup> prior to switching                                                                                                    | 49   |

| 3-14 | Current-voltage measurement circuits. (a) The low bias circuit; (b) the high bias circuit (above 1 mA)                                                                                              | 50   |

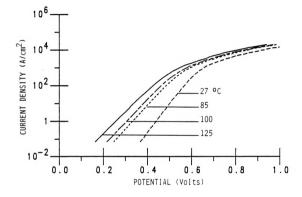

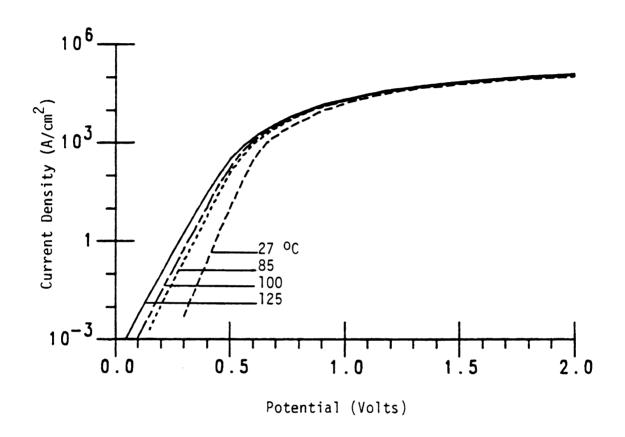

| 3-15 | Measured J-V characteristics of an unguarded device at four temperatures                                                                                                                            | 52   |

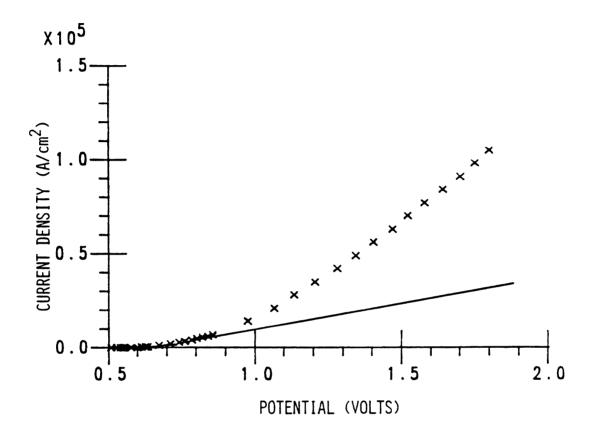

| 3-16 | Linear plot of the room temperature J-V characteristics of the unguarded device emphasizing high current densities                                                                                  | 53   |

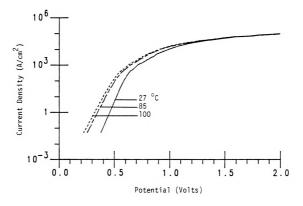

| 3-17 | Measured J-V characteristics of a guarded device at three temperatures                                                                                                                              | 55   |

| Figu | Figure                                                                                                                                                                                                                                                               |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

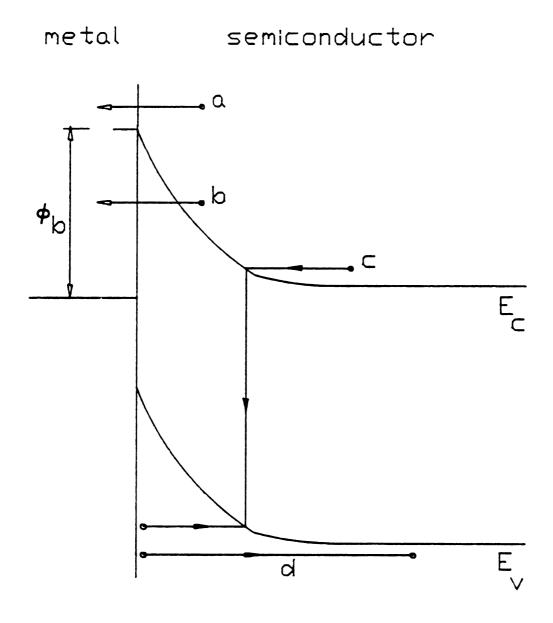

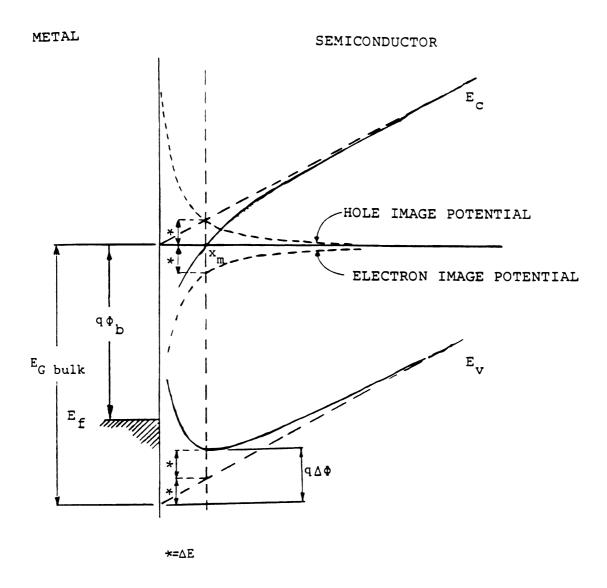

| 4-1  | Energy band diagram of the device near the metal-<br>semiconductor interface under low bias conditions                                                                                                                                                               | 65  |

| 4-2  | Energy band diagram of the device near the metal-<br>semiconductor interface under high bias conditions (beyond<br>flatband)                                                                                                                                         | 69  |

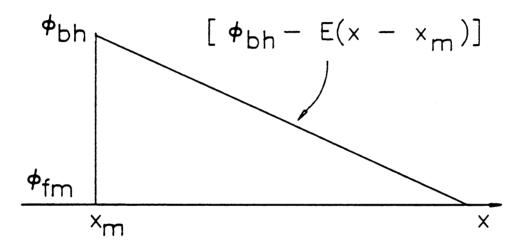

| 4-3  | A triangular approximation of the potential barrier for holes at the metal-semiconductor interface under high bias conditions (beyond flatband)                                                                                                                      | 72  |

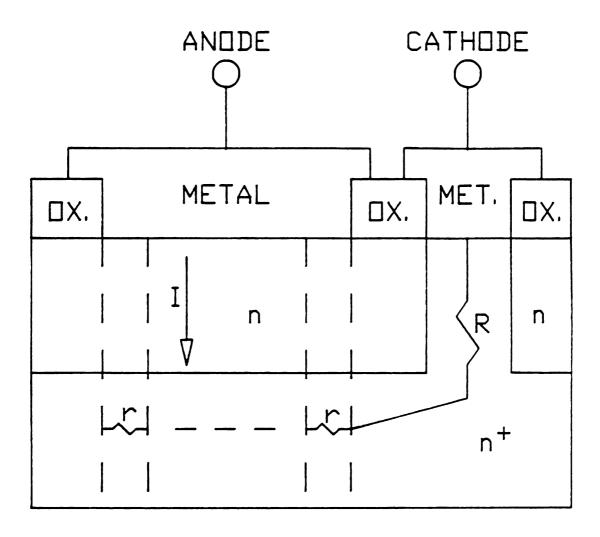

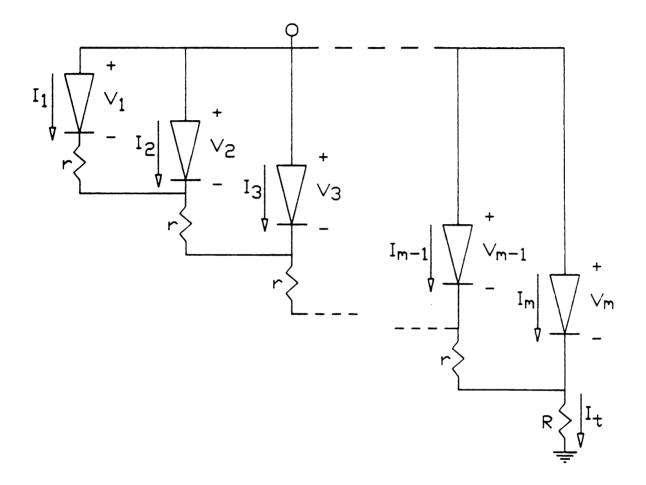

| 4-4  | Cross section of the unguarded diode and the parasitic resistances involved, used as a model for the lateral resistance correction to the simulation                                                                                                                 | 75  |

| 4-5  | The diode equivalent circuit used to correct the lateral                                                                                                                                                                                                             |     |

|      | voltage drop in the n <sup>+</sup> buried layer                                                                                                                                                                                                                      | 76  |

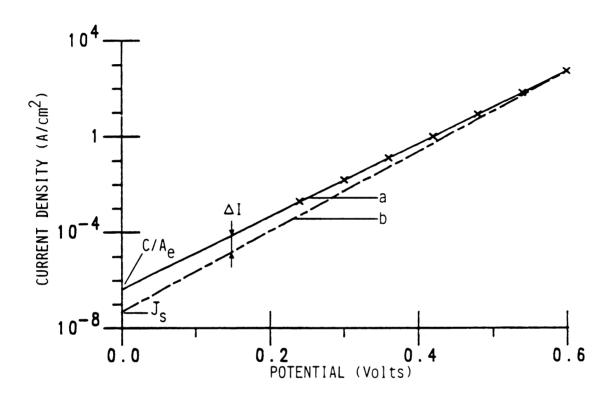

| 5-1  | A hypothetical set of observed data with exaggerated non-ideal effects.                                                                                                                                                                                              | 85  |

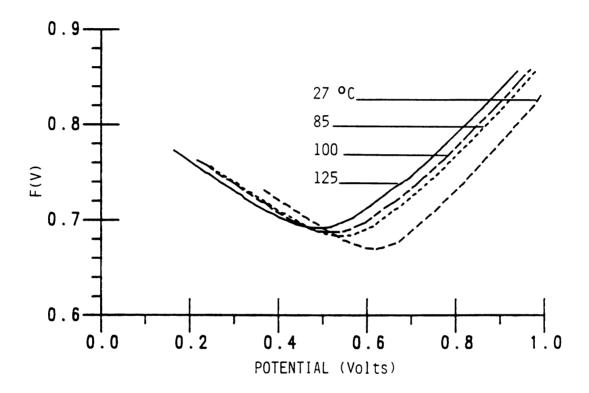

| 5-2  | Plots of $F(V)$ as defined by Equation 5-20 for $\alpha=1.5$ using the experimental data of Figure 3-15                                                                                                                                                              | 100 |

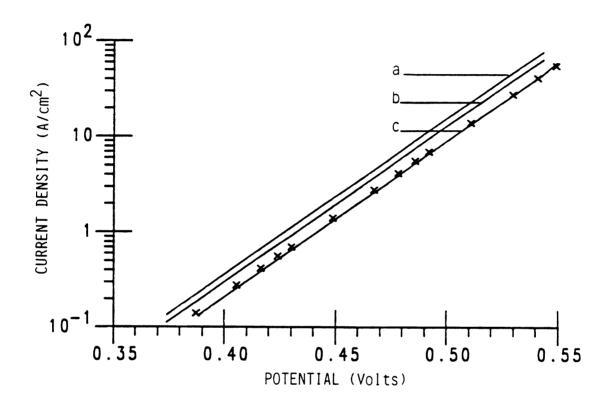

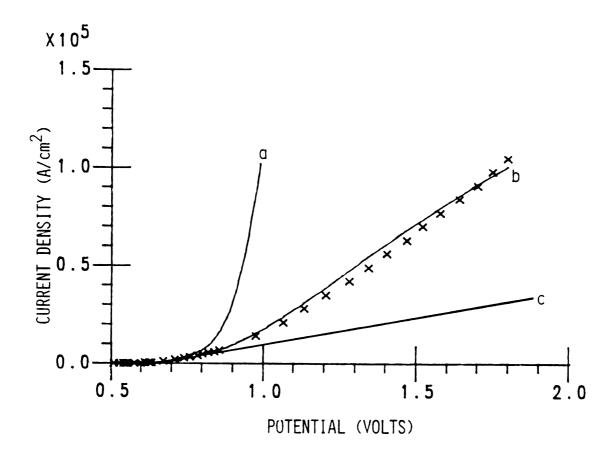

| 5-3  | Plots of Equation 5-5 at 27°C using the barrier height value of; (a) original Norde's and Richardson's constant method (0.866 V), (b) modified Richardson's constant method (0.871 V), (c) modified Norde's method (0.881 V). The experimental data is marked with X | 101 |

| 5-4  | Comparison of experiment with plots of Equation 5-5 at elevated temperatures using the barrier height values obtained from modified Norde's method and experiment. The experimental data is denoted by X                                                             | 103 |

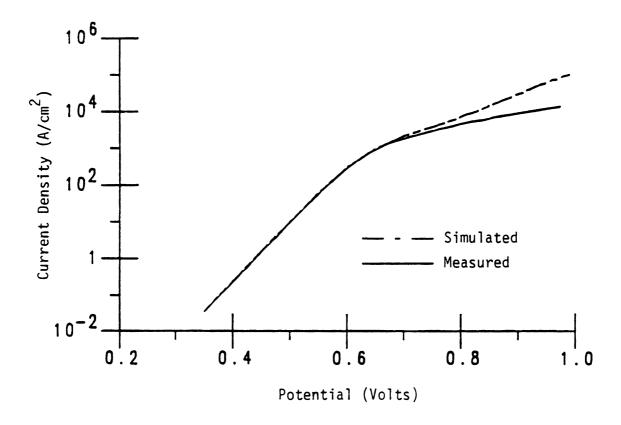

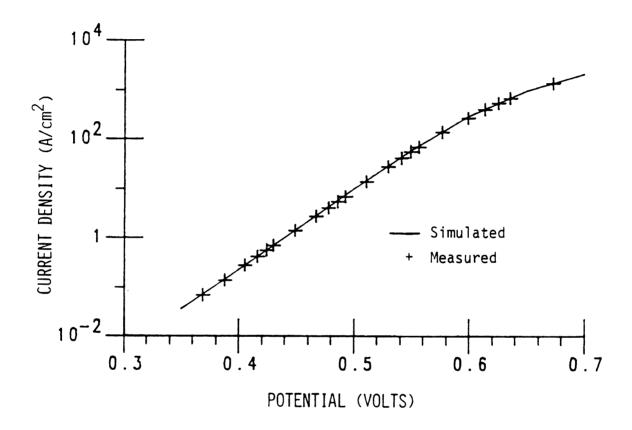

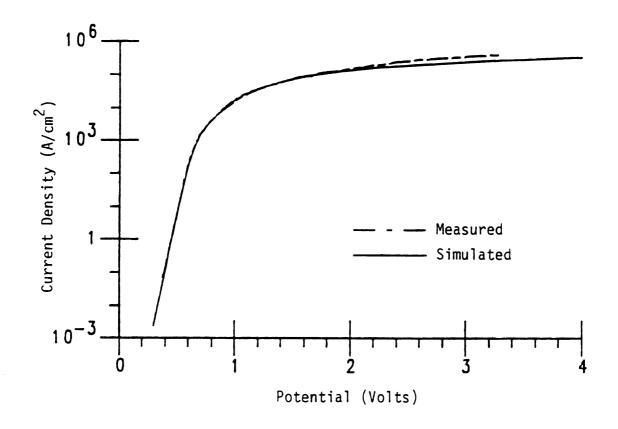

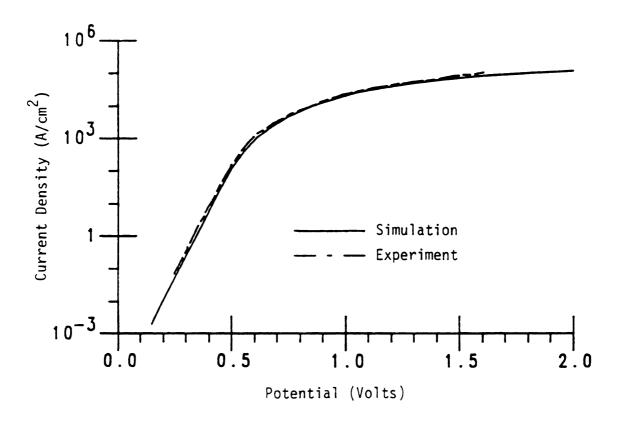

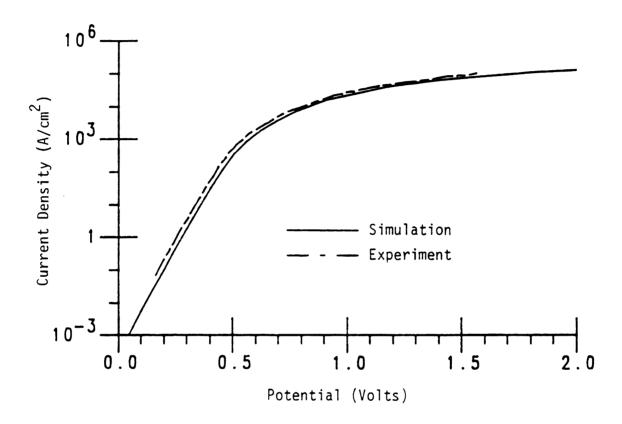

| 6-1  | Comparison between current-voltage characteristics of the experiment and the traditional simulation for bias up to one volt.                                                                                                                                         | 109 |

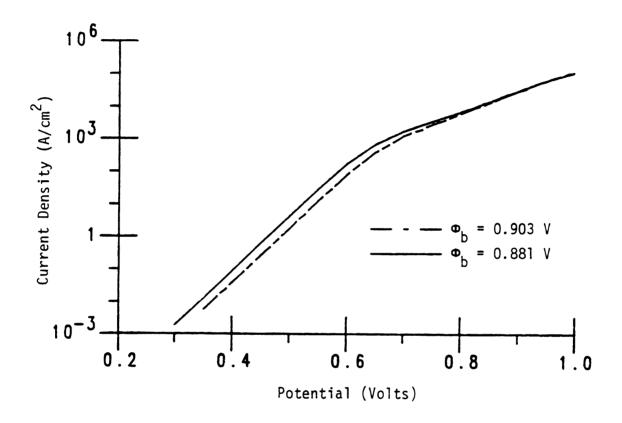

| 6-2  | Simulation results of the J-V characteristics showing the sensitivity of the simulation on the value of the barrier height.                                                                                                                                          | 110 |

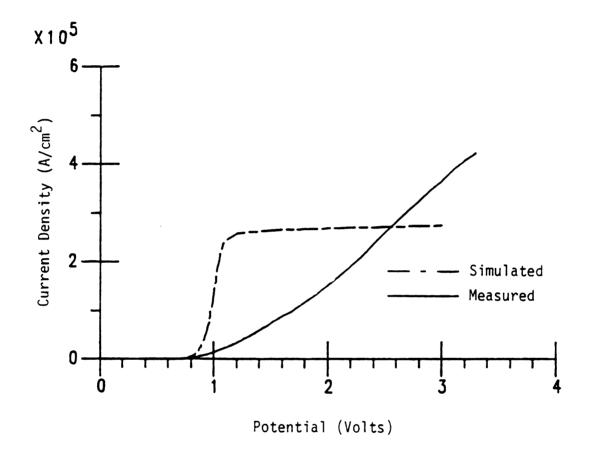

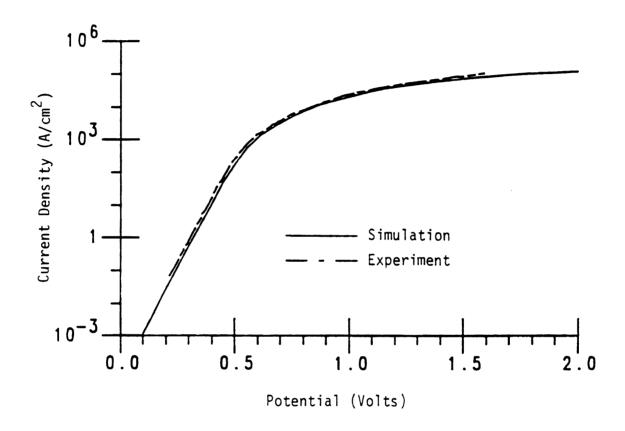

| 6-3  | J-V comparison between the experiment and the traditional simulation for high injection conditions.                                                                                                                                                                  | 112 |

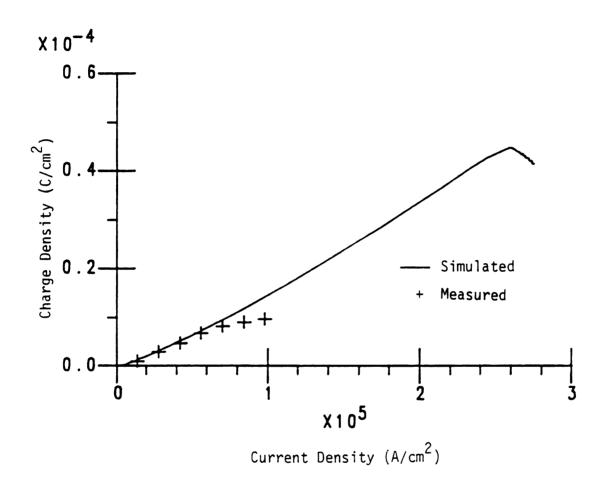

| 6-4  | Comparison between the experiment and the traditional simulation for the charge density associated with minority carrier storage in the unguarded device                                                                                                             | 113 |

| 6-5  | Low bias comparison of the measured J-V characteristics with the simulation corrected for lateral voltage drop                                                                                                                                                       | 116 |

| Figu | ce                                                                                                                                                                                                                                                                                                                  | page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

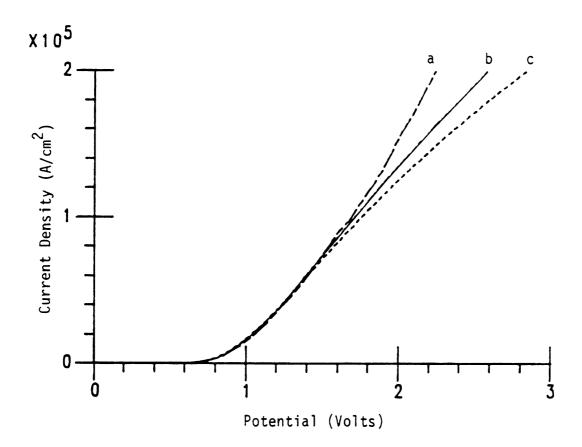

| 6-6  | Effect of lateral voltage drop correction to the simulation for current densities up to $10^5~{\rm A/cm}^2$                                                                                                                                                                                                         | 117  |

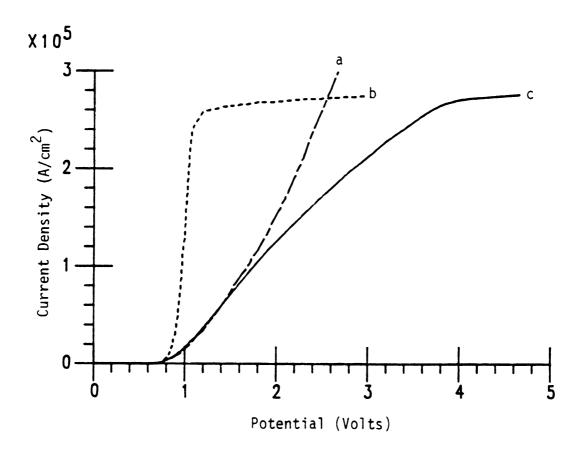

| 6-7  | Comparison of the lateral voltage drop corrected simulation and experiment for an extended bias range                                                                                                                                                                                                               | 118  |

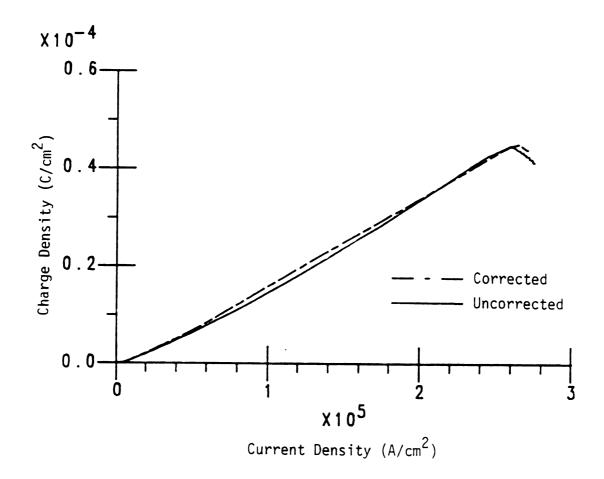

| 6-8  | Simulation results for the charge density of stored minority carriers with and without correction for the lateral voltage drop.                                                                                                                                                                                     | 119  |

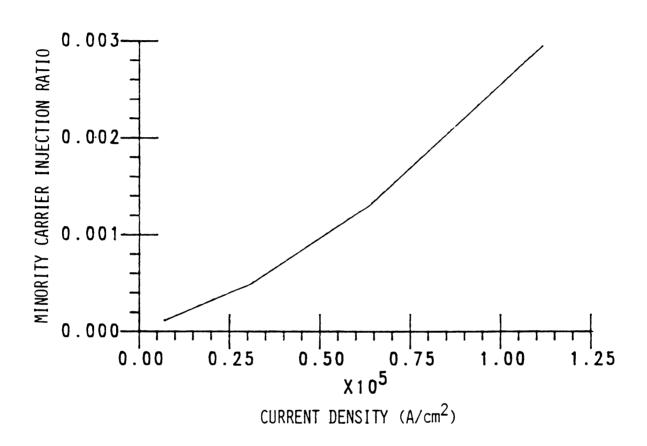

| 6-9  | Traditional simulation results for the minority carrier injection ratio                                                                                                                                                                                                                                             | 121  |

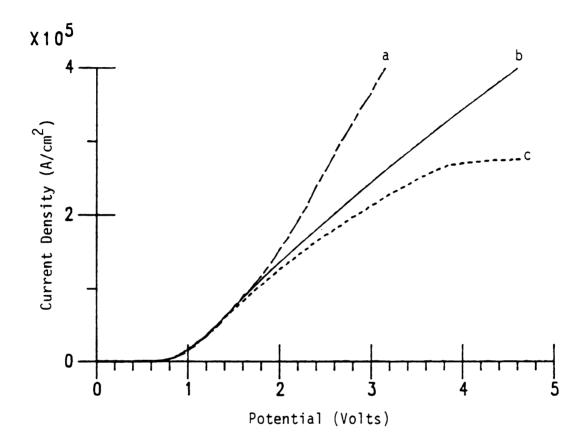

| 6-10 | Comparison of simulated and measured J-V characteristics with the simulation including the effects of lateral voltage drop, image-force induced bandgap shrinkage, and hole barrier height lowering.                                                                                                                | 123  |

| 6-11 | Linear plot of the current-voltage characteristics comparing the measured results, the simulation corrected for the lateral voltage drop only, and the simulation corrected for lateral voltage drop as well as the image-force induced bandgap shrinkage and the hole barrier height lowering                      | 125  |

| 6-12 | Plot of the current-voltage characteristics over an extended range and comparing the measured results, the simulation corrected for the lateral voltage drop only, and the simulation corrected for lateral voltage drop as well as the image-force induced bandgap shrinkage and the hole barrier height lowering. | 126  |

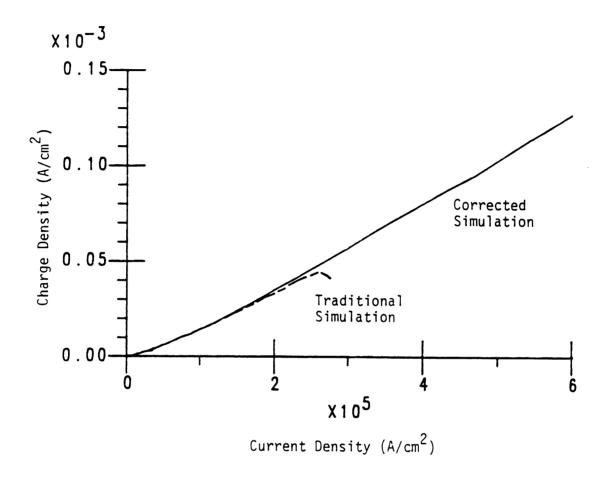

| 6-13 | Comparison of minority carrier charge-storage results between the traditional simulation and the simulation corrected for image-force induced bandgap shrinkage and hole barrier height lowering.                                                                                                                   | 127  |

| 6-14 | Current-voltage characteristics resulting from the traditional simulation with and without consideration of Auger recombination.                                                                                                                                                                                    | 129  |

| 6-15 | Minority carrier stored-charge density results from the traditional simulation with and without consideration of Auger recombination.                                                                                                                                                                               | 130  |

| 6-16 | Traditional simulation results for minority carrier profile at a forward current density of 1.1 X $10^5$ A/cm <sup>2</sup>                                                                                                                                                                                          | 134  |

| 6-17 | Comparison of minority carrier stored-charge density results of the traditional simulation and experiment                                                                                                                                                                                                           | 135  |

| 6-18 | Traditional simulation results for the J-V characteristics of the device at four temperatures                                                                                                                                                                                                                       | 137  |

| Figur       | re                                                                                                                                                                                                           | page |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 6-19        | Traditional simulation results for the minority carrier stored-charge density at four temperatures                                                                                                           | 138  |

| 6-20        | Comparison of the J-V characteristics obtained from the traditional simulation and experiment at 85 °C                                                                                                       | 139  |

| 6-21        | Comparison of the J-V characteristics obtained from the traditional simulation and experiment at 100 °C                                                                                                      | 140  |

| 6-22        | Comparison of the J-V characteristics obtained from the traditional simulation and experiment at 125 °C                                                                                                      | 141  |

| 6-23        | Comparison of the minority carrier stored-charge density obtained from the traditional simulation and experiment at 85 °C                                                                                    | 142  |

| 6-24        | Comparison of the minority carrier stored-charge density obtained from the traditional simulation and experiment at 100 °C                                                                                   | 143  |

| 6-25        | Comparison of the minority carrier stored-charge density obtained from the traditional simulation and experiment at 125 °C                                                                                   | 144  |

| A-1         | Diagram of the circuit for measurements using Krakauer's method                                                                                                                                              | 151  |

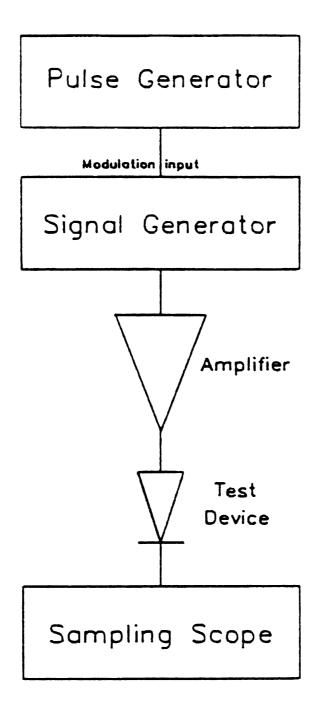

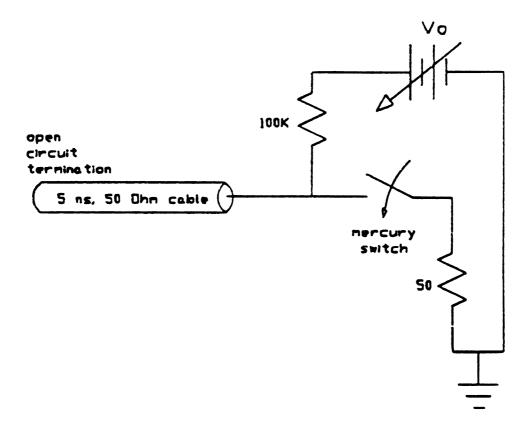

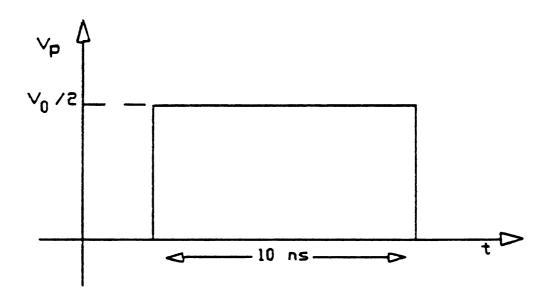

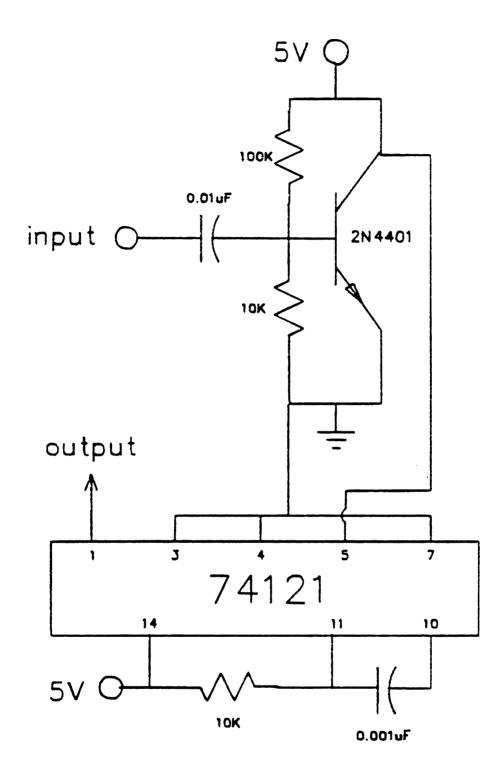

| A-2         | A simplified schematic of the pulse generator circuit and the resulting pulse                                                                                                                                | 153  |

| <b>A</b> -3 | Diagram of the circuit used to condition the retrace portion of the horizontal sweep raster of the sampling oscilloscope to generate a 7 $\mu$ s down-going pulse suitable for triggering the A/D converter. | 156  |

#### CHAPTER ONE

## INTRODUCTION

## 1.1 Statement of Problem

Schottky barrier diodes (SBDs) are widely used in electronic circuits for a variety of functions. Current flow in these diodes, at low to moderate current densities and temperatures, is primarily due to majority carrier injection from the semiconductor to the metal over the metal-semiconductor interface. The lack of minority carrier injection, and therefore lack of minority carrier storage, leads to considerable SBD speed advantages as compared to p-n junction diodes. At sufficiently high current densities or temperatures, however, minority carrier effects in Schottky barrier diodes become significant.

The issue is of current interest in advanced bipolar logic circuits that utilize SBDs. As bipolar integrated circuits are scaled down in size, higher current densities are necessary to exploit

advantages of scaling related improvements in speed. This is in part because the junction voltages required to turn on a bipolar junction transistor do not scale down since they are already low. Gate delay times in a digital circuit may be expressed in general form as

$$t_{d} = C_{0}V/J \tag{1-1}$$

where  $C_0$  is the capacitance per unit area to be charged and discharged over a voltage range V by a current density J. Since  $C_0$  increases with scaling due to decreasing depletion layer widths, the current density must also increase to avoid increased delay times. The combination of higher current densities and unscaled voltages result, in turn, in a higher density of dissipated power and hence, larger operating temperatures.

Current densities as high as  $1.3 \times 10^5$  A/cm<sup>2</sup> have been reported in high performance bipolar switching circuits that have been fabricated with VLSI device dimensions [1]. At such current levels, SBD models which incorporate minority carrier injection effects are required. Minority carrier injection is further pronounced in guarded SBDs in which p-type guard rings are used to avoid undesirable effects associated with high electric fields at the electrode edge.

Injection of minority carriers leads to excess carrier storage in the bulk of the device. The stored excess carriers, in turn, change SBD characteristics in two principal ways, as illustrated in Figure 1-1. Static current-voltage characteristics are altered because of conductivity modulation induced by excess carriers, and dynamic properties are modified due to carrier-storage induced switching delay times. So, in circuits operating at high current densities, minority

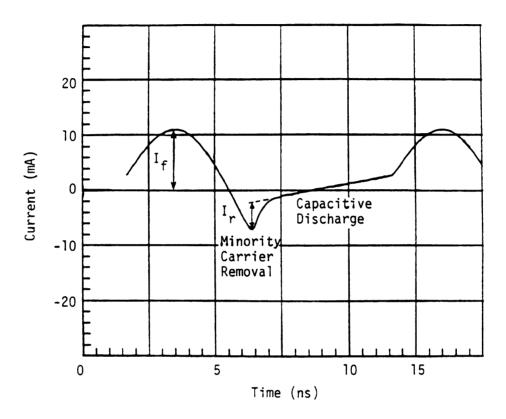

Figure 1-1 Minority carrier injection results in excess carrier storage which changes device characteristics in two principal ways. (a) The bulk conductivity is modulated. (b) Switching delay is induced.

carrier injection has to be properly considered for its effects on the value of the bulk conductivity as well as the added switching delay. Another motivation for understanding the phenomenon is the possible latching of an integrated circuit Schottky diode and an adjacent npn transistor caused by minority carrier injection, due to a mechanism similar to the latching of a silicon controlled rectifier (SCR), [2].

The this study is to provide experimental purpose of quantification of minority carrier injection in planar platinumsilicide Schottky barrier diodes and to correlate the results with a numerical device simulation in order to aid in establishing correct device models. Specifically, two experimental measures of minority carrier injection are investigated. First, the charge due to stored minority carriers is measured by current integration during the diode switching transient from forward to reverse bias. Secondly, the conductivity modulated forward I-V characteristics of the device are measured under large forward bias conditions. The results are then correlated with a numerical simulation of the basic equations governing carrier transport in the device.

## 1.2 Preview of Contents

Chapter 2 covers the background material, starting with a brief discussion of the physical structure of an SBD and various mechanisms of current transport in the device. Then, the attention is focused on minority carrier injection in SBDs, discussing its effects and reviewing the previous theoretical and experimental studies of the phenomenon.

Chapter 3 presents the experimental part of the study. Specifically, a measurement technique is described which detects the pico-coulombs of charge associated with minority carrier storage, which discharge in nanosecond time frames, for current densities as high as  $10^5$  A/cm<sup>2</sup>. Additionally, a method is described to measure conductivity modulated forward J-V characteristics for current densities as high as  $4 \times 10^5$  A/cm<sup>2</sup>. The experimental results, along with the experiment's limits and accuracy are presented after the discussion of each measurement method.

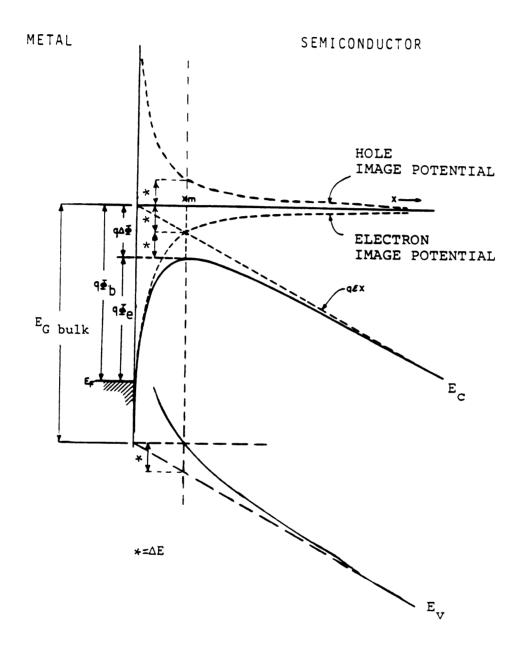

Chapter 4 describes the theoretical simulation, starting by discussing the basic theory of carrier transport in the device. Then the approach to the solution of the problem by previous investigations is briefly discussed and finally, other phenomena beyond the previous work are explored and new corrections are made to the traditional theory. Specifically considered are energy gap shrinkage, hole barrier height lowering, and hole tunneling at high injection, all of which result from the effect of the image-force on the valence-band in silicon near the junction. Additionally, a method is presented to correct the one dimensional simulation for the lateral voltage drop in the n<sup>+</sup> buried layer.

An important parameter in the numerical simulation is the value of the barrier height of the device. Since the value of the barrier height depends on the processing involved in the fabrication of the device, It must be measured for the devices under study. Chapter 5 describes various I-V methods for the measurement of barrier height and demonstrates shortcomings of each method theoretically as well as experimentally. A modification of one of the methods is then proposed which provides highly accurate results for the value of the barrier

height. This method is then used to determine the barrier height at four temperatures.

Chapter 6 is devoted to the comparison of the experiment and simulation results. First, the correlation between experiment and theory based on the traditional simulation is examined and shortcomings of the simulation are demonstrated. Subsequently, lateral voltage drop, hole barrier height lowering, image-force induced energy-gap shrinkage, and Auger recombination are considered separately and the effect of each phenomenon on correlation of simulation and experiment is observed Finally, high temperature comparison of simulation and experiment is discussed.

Chapter 7 includes the summary and conclusions of the work and discusses recommendations for further studies of the phenomenon. The chapter is followed by three appendices which contain the details of various experimental procedures (Appendix A), and derivations of some of the theoretical results developed in this work (Appendices B, C).

#### 1.3 Main Contributions of this Work

This thesis presents a comprehensive study of minority carrier injection in Schottky barrier diodes by direct measurement of both minority carrier storage and forward J-V characteristics, correlated with numerical simulation. Such a study has not been previously reported. Furthermore, the experiment extends reverse-recovery minority carrier storage measurements to current densities several orders of magnitude higher than previously reported [3].

Theoretically, modifications of some forward I-V methods for determining the barrier height of an SBD are developed to improve their

performance, and one modification is shown to generate highly accurate results. The numerical simulations were performed by C.C. Yu [4] at IBM corporation. The contributions of this work to the simulation were the inclusion of effects due to hole barrier lowering, energy gap shrinkage, Auger recombination, and buried-layer lateral voltage drop.

#### CHAPTER TWO

#### BACKGROUND

#### 2.1 Introduction

A metal-semiconductor contact may show rectification properties or the characteristics of an ohmic contact depending on the choice of metal and semiconductor as well as the impurity concentration in the semiconductor and the processing involved in its fabrication. The asymmetric nature of electrical conduction between metal contacts and semiconductors such as copper and iron sulphide was first discovered in the late 19<sup>th</sup> century and while the rectification mechanism was not understood, contacts between metal points and metallic sulphides were used extensively as detectors in early experiments on radio. The rapid growth of broadcasting in the 1920s owed much to the "cat's-whisker" rectifier which consisted of a tungsten point in contact with a crystal, usually of lead-sulphide [5].

In 1938, Schottky and, independently Mott, pointed out that the observed direction of rectification in a metal-semiconductor contact could be explained by supposing that majority carriers from the semiconductor passed over a barrier through the normal processes of drift and diffusion. Mott assumed that the barrier region of the semiconductor was devoid of charged impurities so that the electric field was constant and the electrostatic potential varied linearly as the metal was approached. In contrast, Schottky supposed that the barrier region contained a constant density of charged impurities so that the electric field increased linearly and the electrostatic potential quadratically [5].

Schottky's assumption on the shape of the barrier conforms fairly closely to what usually occurs in practice, so that barriers associated with metal-semiconductor contacts are often referred to as Schottky barriers and contacts which have rectifying properties are referred to as Schottky barrier diodes. Modern planar SBDs are extended area contacts formed by the deposition of metal films in high-vacuum. Such planar contacts are much more stable and reproducible than point contacts. The SBD is usually fabricated using n-type semiconductors since a larger barrier height and consequently, more rectification is achieved.

This chapter discusses the structure of a planar SBD, considers various mechanisms of current transport in the SBD, and then focuses on minority carrier injection, discussing its effects and reviewing the previous theoretical and experimental studies of the phenomenon. Throughout the remainder of this work, n-type devices are considered while similar arguments could be made and parallel conclusions could be drawn for p-type devices.

#### 2.2 Structure of a Planar SBD

In bipolar silicon integrated circuits, SBDs are fabricated as follows. A lightly to moderately doped n-type epitaxial layer is grown on a p-type substrate on top of which is a heavily doped n-type (n<sup>+</sup>) area, and then a metal layer is deposited on the epitaxial layer to form the anode. A metal contact to an n<sup>+</sup> region that is connected to the n<sup>+</sup> buried layer forms the cathode ohmic contact. A p-type guard ring is sometimes fabricated around the anode to eliminate undesirable leakage currents caused by the high electric fields present at the edge of the metal. Figure 2-1 shows examples of the cross sections of the guarded and unguarded SBDs and Figure 2-2 shows the energy band diagram of the planar SBD, neglecting the effect of the image force at the junction. As will be shown later, minority carrier injection is much more profound in guarded devices due to the presence of the guard ring as an additional source of minority carriers.

## 2.3 Current Transport Mechanisms

The various ways in which electrons can be transported across the junction of an SBD under forward bias are shown schematically in Figure 2-3. The mechanisms include the emission of electrons from the semiconductor over the top of the barrier into the metal, quantum-mechanical tunneling through the barrier, recombination in the space charge region and minority carrier injection [5].

The principle mechanism of current flow in the SBD is the emission of majority carriers over the barrier which is governed by the thermionic emission, as well as diffusion and drift in the depletion

Figure 2-1 Structure of a planar SBD. (a) Unguarded. (b) Guarded.

Figure 2-2 Energy band diagram of a planar SBD neglecting the effects of image-force at the metal-semiconductor interface. The horizontal axis is not to scale. The position of the contact is denoted by  $\mathbf{x}_{o}$ , the position of the edge of the depletion layer is denoted by  $\mathbf{x}_{w}$ , and the interface of the epitaxial and the  $\mathbf{n}^{+}$  buried layers is denoted by  $\mathbf{x}_{1}$ .  $\mathbf{V}_{1}$  is the applied junction voltage and  $\Phi_{b}$  is the barrier height.

Figure 2-3 Current transport mechanisms over the metal semiconductor interface. (a) Thermionic emission. (b) Tunneling of majority carriers. (c) Recombination in the depletion region. (d) Minority carrier injection.  $\Phi_{\rm b}$  is the barrier height of the interface.

region of the device. The current-voltage relationship for the combined thermionic emission-diffusion process is developed by Crowell and Sze [6] and is given by

$$J - A^{**} T^2 \exp(-q\Phi_b/kT) \left(\exp(qV_j/kT) - 1\right)$$

(2-1)

where J is the current density,  $A^{**}$  is the modified Richardson's constant,  $V_j$  is the junction voltage, and  $\Phi_b$  is the barrier height of the diode as shown in Figure 2-3. In this work, Equation 2-1 is referred to as the ideal Schottky diode equation and the other processes of current transport shown in Figure 2-3 cause departures from this ideal behavior.

Quantum-mechanical tunneling of majority carriers through the barrier and carrier recombination in the depletion region are significant at low bias. Minority carrier injection, on the other hand, is significant at high injection and introduces additional delays in the switching response of the diode.

## 2.4 Effects of Minority Carrier Injection

Under forward bias, minority carriers are injected into the bulk of the semiconductor and travel for an average distance equal to their diffusion length before they recombine with electrons. For semiconductors with large diffusion lengths compared to the thickness of the epitaxial layer, such as silicon with a diffusion length on the order of tens to hundreds of micrometers, most of the minority carriers reach the cathode before being recombined. Therefore, minority carrier

injection leads to the presence of excess minority carriers throughout the bulk.

In a device that is heavily forward biased, the excess hole concentration in the bulk of the semiconductor can be substantially higher than the material's equilibrium concentration. These excess holes, in addition to the excess electrons stored in the bulk to maintain quasi charge neutrality, give rise to an increase in the the bulk conductivity  $\sigma$ . The increase in conductivity (or conductivity modulation),  $\Delta \sigma$ , is given by

$$\Delta \sigma = q(\mu_n \Delta n + \mu_p \Delta p)$$

(2-2)

where  $\Delta n$  and  $\Delta p$  are excess electron and hole concentrations and  $\mu_n$  and  $\mu_p$  are electron and hole mobilities. Conductivity modulation results in a decrease of the resistance of the epitaxial layer. Therefore, the diode conducts a larger value of current for a given voltage compared to the case of no modulation.

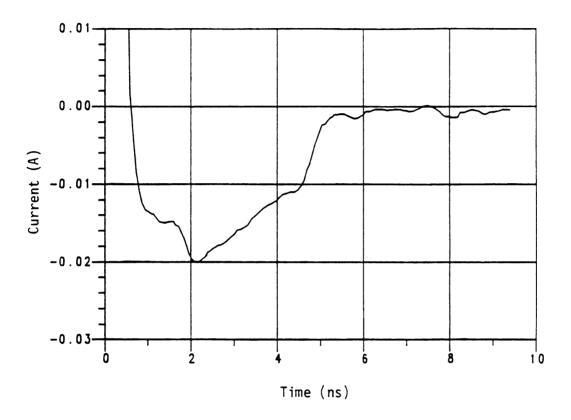

The excess holes also affect the switching characteristics of the device. Upon rapid switching from forward to reverse bias, a reverse transient current, much larger than the diode's steady-state reverse current, flows to sweep the excess holes out of the device. Figure 2-4 shows the minority carrier profile in the bulk during the transition from forward to reverse bias, and the current through the diode, during the reverse-recovery for a semi-infinite device initially under low to moderate forward bias. As shown in this figure, for times  $t_0$  to  $t_3$ , the reverse current remains relatively constant since the presence of minority carriers pins the junction voltage near its value prior to switching until the hole concentration at the edge of the space charge

Figure 2-4 Dynamics of reverse-recovery for a semi-infinite device initially under low to moderate forward bias. (a) Hole concentration profile. (b) Switching current.  $C_j$  and  $C_p$  correspond to the junction and parasitic capacitances respectively.

region,  $x_w$  as shown in Figure 2-2, becomes small. The pinning is due to the boundary condition [7];

$$P_{n}(x_{w}) = P_{no} \exp(qV_{j}/kT)$$

(2-3)

where  $P_{no}$  is the equilibrium minority carrier concentration in the bulk. The primary source of reverse current during the exponential decay after  $t_3$  in Figure 2-4 is the discharge of the junction and parasitic capacitances. Minority carrier removal, however, may also continue as the junction becomes reverse biased, as shown for time  $t_4$ .

The boundary condition of Equation 2-3 is based on the assumption that the minority carrier quasi-Fermi level at the edge of the depletion region,  $\mathbf{x}_{\mathbf{w}}$ , lines up with the metal Fermi level. This assumption is only valid at low to moderate injection levels and fails at high injection [8]. Additionally, the minority carrier profiles shown in Figure 2-4 correspond to a semi-infinite bulk. Therefore, the reverse-recovery response shown in this figure does not necessarily describe the exact switching behavior of a planar diode under high injection. As will be shown from switching measurements described in Chapter 3, however, the observed response is similar to that of Figure 2-4.

The value of reverse current upon switching ( $I_R$  as shown in Figure 2-4) is determined primarily by the equivalent resistance of the switching circuit as seen by the diode, as well as the final reverse voltage that the device reaches after switching. Therefore,  $I_R$  is independent of the amount of stored minority carriers. The effect of minority carrier storage is merely to lengthen the time involved in the reverse-recovery. Consequently, the time during which  $I_R$  is constant

(from  $t_0$  to  $t_3$  in Figure 2-4) is called the storage delay time and serves as a figure of merit for the amount of stored excess minority carriers.

## 2.5 Review of Previous Work on Minority Carrier Injection

## 2.5.1 Theory

Historically, the interest in minority carrier injection was initially focused on point contacts which were used as emitters in the early bipolar transistors. An example of the theoretical study of point contacts is the work by Braun and Henisch [9] who developed a closed form expression for the ratio of minority carrier current to the total current (minority carrier injection ratio). While the point contact is a good injector of minority carriers, the planar SBD shows much smaller values of minority carrier injection ratio. In 1965, Sharfetter analyzed the phenomenon in planar SBDs under steady-state dc bias and developed an expression for the minority carrier injection ratio in these devices [3]. The expression developed in his work for the excess minority carrier storage depends on the value of the recombination velocity for holes at the n-n interface originally introduced by Gunn [10]. His analysis was limited to low injection conditions. Others, including Chuang [7,11], Green and Shewchun [12], Wagner [13], Masszi et. al. [14], and C.C. Yu [4] have extended the analysis to the higher injection levels as well.

Chuang [7] solves the one dimensional steady-state dc carrier transport equations analytically and develops implicit equations to calculate the total amount of minority carriers stored in the device.

The boundary conditions used to obtain the analytical solution, however, limit the results to moderate injection levels. His solution is based on the use of boundary conditions at the edge of the depletion region  $x_w$ , and the n-n<sup>+</sup> interface,  $x_1$  (see Figure 2-2). In particular, he assumes a constant velocity, independent of the hole concentration, for holes at the  $n-n^+$  interface,  $x_1$ . This assumption is also used by Sharfetter for low injection conditions [3]. At  $x_{ij}$ , the boundary condition used in reference [7] is based on Equation 2-3. As discussed previously, this boundary condition is obtained by using the assumption that the quasi-Fermi level for holes is essentially the same as the metal's Fermi level. So, to the extent that the assumptions made to obtain these boundary conditions fail under high injection, Chuang's results are limited to moderate injection levels. In fact, in a recent publication [8], Chuang and Wagner reported that under high injection, the hole quasi-Fermi level is significantly lower than the metal's Fermi level. It must also be noted that the charge associated with the total excess minority carrier storage,  $Q_{D}$ , obtained from Chuang's equations, reflects the total charge between  $\boldsymbol{x}_{_{\boldsymbol{U}}}$  and  $\boldsymbol{x}_{_{\boldsymbol{1}}}$  and does not include the depletion region or the n region. In another paper [11], Chuang developed an analytical expression for the I-V characteristics of the planar SBD which was shown to give accurate results for current levels extending to high injection (up to  $10^4 \text{ A/cm}^2$ ). That work, however, did not produce a solution for the amount of charge associated with the stored excess minority carriers.

Green and Shewchun [12] solve the one dimensional equations numerically, under both steady-state dc and small signal ac conditions. The dc solution is used to get the the total minority carrier stored charge,  $Q_{\rm p}$ , and the ac solution is used to obtain a small signal

equivalent circuit model for the device. Their choice of device structure is somewhat different from what was previously discussed. Specifically, they do not have the  $n^+$  buried layer in their analysis. In other words, the cathode ohmic contact is assumed to be directly connected to the epitaxial region (see Figures 2-1, 2-2). Their boundary condition for electron current at x is originally due to Crowell and Sze [6] and is based on the assumption that excess electrons at  $x_0$  travel to the metal with an average velocity equal to their thermal velocity. The boundary condition used by Green and Shewchun on hole current at  $x_{\alpha}$  assumes that the above argument is true for holes at that point as well, and the boundary conditions applied at the ohmic contact assume no excess carriers there. The method presented by their work can be limited in two ways. First, by neglecting the  $n^+$ region, the effects of the n-n interface as well as the minority carrier storage in the n region are not accounted for. Secondly, the boundary condition on hole current applied at  $x_0$  does not consider the effect of image force on the valence band which results in an energy gap shrinkage near the barrier and also leads to hole barrier height lowering and tunneling of holes through the barrier at high injection. The effect of image force on the valence band near the barrier will be discussed in detail in Chapter 4.

The numerical simulation described above was later used by Clark et. al. [15] to explain the difference between minority carrier injection behavior of point contacts and planar devices. A simulation similar to the work of Green and Shewchun was also used by Wagner [13] to develop a large signal model for the device. His model consists of ideal diodes, resistors, capacitors, and a constant current source and, since the model was developed to match the simulation results, the

limitations of the simulation as described above, apply to the model as well. Recent modifications of the numerical simulation include the work by C.C. Yu [4] who considered the n<sup>+</sup> region of the device and the work by Mosszi et. al. [14] who considered the effect of hole barrier lowering at high injection on the hole current boundary condition.

#### 2.5.2 Experiment

Early experimental work on minority carrier injection in SBDs also focused on point contacts and is reviewed by Henisch [16] and Smith [17]. For example, the original Haynes-Shokley experiment studied hole injection from a metallic point rectifying-contact on n-type germanium [18].

Experimental observations of minority carrier induced conductivity modulation in planar epitaxial silicon SBDs have been reported in the literature. An example is the work by Jager and Koseak [19] on 45  $\mu$ m diameter devices for current densities up to  $10^3$  A/cm<sup>2</sup>. Also, metal emitter transistor structures have been used to measure minority carrier injection in planar silicon SBDs by Yu and Snow [20] and in GaAs SBDs by Chan et. al. [21].

Direct measurement of minority carrier storage in planar SBDs, based on the reverse-recovery experiment, has only been reported for low injection conditions (10 A/cm²) by Sharfetter [3]. The technique involves the integration of the reverse-recovery current with respect to time to obtain the total charge removed from the device upon switching. Subsequent correction of the total charge for the charge associated with the parasitic and junction capacitances then yields the charge associated with the excess minority carriers. The difficulty of

this measurement is due to the fact that, unlike p-n junctions, planar SBDs are primarily majority carrier devices and minority carrier injection corresponds only to a small fraction of the total current flow. Consequently, reverse-recovery of the switching response usually lasts, at most, on the order of nanoseconds and hence, high time resolution circuits and test devices with low values of parasitic capacitance are required for such measurements. The reverse-recovery method is used in this work to measure the excess minority carrier storage in the device and will be explained in greater detail in Chapter 3.

Various methods have been used to measure the storage delay time in p-n junctions and, while the time scales of interest for SBDs may be small compared to p-n diodes, the same experimental methods are applicable in principle to SBDs. The most common and straightforward method is to switch the diode from forward to reverse bias and observe the diode current during the transient [22]. As discussed in section 2.4, the storage delay time corresponds to the time between  $t_0$  and  $t_3$  as shown in Figure 2-4. Various circuits reported in the literature for this type of measurement differ mainly in the circuits used to control the amplitude of the forward and reverse current upon switching [23,24,25]. This method has been used by Zetter and Cowly [26] for qualitative observations of minority carrier injection in SBDs.

Dean and Nuese [27] reported a "refined" step recovery method in which the switching diode is the terminating load on a single 50  $\Omega$  coaxial line of arbitrary length. The method involves the observation of the incident and reflected waveforms of a single transmitted pulse using a high impedance probe. During the storage delay time, the diode is highly conductive, and the reflection coefficient is negative. After

the storage delay time, the diode approaches an open circuit in an exponential fashion and the reflection coefficient approaches unity. Consequently, the reflected signal can be used to obtain the storage delay time. This method was used by Dean and Nuese to measure storage delay times on the order of nanoseconds in GaAs p-n junctions. An advantage of this method is that only one electrical line is required to contact the test diode. The one-port connection makes it easy to vary ambient conditions, such as temperature. A disadvantage is the requirement of a high impedance probe. The fastest sampling probes are  $50\Omega$  rather than high impedance.

A double pulse experiment has been used by Silver et. al. [28], to avoid confusion between true storage delay currents and displacement currents due to capacitance. The method is useful for special cases where displacement currents are usually large, but it was not reported to achieve very high time resolutions.

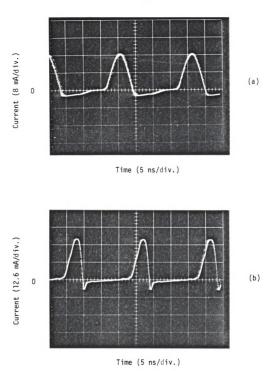

The last measurement method to be discussed here was developed by Krakauer [29]. Unlike the methods previously discussed, which observe the response of the diode to input pulses, this method excites the diode with a sinusoidal input. Figures 2-5 and 2-6 show SPICE simulation results of the response of a diode to sinusoidal excitation. Figure 2-5 shows the response of a device with purely capacitive charge storage corresponding to a linear reverse-recovery current. Figure 2-6, on the other hand, shows the response of a device in which some minority carrier storage is present. As shown in this figure, the reverse-recovery current due to excess minority carriers can easily be distinguished from the linear capacitive current. Krakauer developed an expression, for a figure of merit concerning the excess minority carrier storage in the device, which is related to the exciting

Figure 2-5 SPICE simulation results for the current through a diode excited by a sinusoidal signal when minority carrier storage is not present.

Figure 2-6 SPICE simulation results for the current through a diode excited by a sinusoidal signal when minority carrier storage in the diode is significant.

frequency, the voltage of the source, the impedances involved in the circuit, and the ratio of  $\rm I_f$  to  $\rm I_r$  as shown in Figure 2-6.

The advantages of this method are its ability to distinguish capacitive effects from excess carrier storage effects as well as the fact that the driving frequency need not be very high and, consequently, high time resolution measurement circuits are not needed. The method, however, is useful only for obtaining a figure of merit for minority carrier storage in the device and does not provide quantified information about stored charge, nor does it provide any information about conductivity modulation. Krakauer's method has been used in the literature for SBDs [30,31] as well as p-n diodes [32,33] and is also sometimes used by SBD manufacturers in their device specifications. In this study, as will be discussed in Chapter 3, the method is used for qualitative observations of the minority carrier storage phenomenon.

## CHAPTER THREE

# **EXPERIMENT**

## 3.1 Introduction

As previously discussed, the two major effects of minority carrier injection on SBD properties concern modification of the switching response of the diode and modification of the forward bias I-V characteristics. This chapter describes experiments which quantify both of these effects, and provide a basis of comparison with simulation.

For the switching experiment, the emphasis of both the experiment and simulation is on determining the total amount of stored excess carriers that are removed during the transient from forward to reverse bias. This is as opposed to determining the switching delay time, since there are problems with determining the delay time in both the experiment and simulation. Because of pulse noise and the effect of parasitic capacitance, an experimental determination of delay time is

to some degree subjective. Furthermore, delay time is a function of the test circuit. However, the fundamental cause of the delay time, which is the stored excess carriers, can be measured accurately and is not a function of the test circuit. For the simulation, a steady-state numerical solution provides values for the stored excess carriers but a time dependent solution, which is much more difficult to carry out, is required in order to obtain values for the delay time.

Therefore, the primary thrust of the switching measurements is to obtain values for the stored excess carrier charge, rather than switching delay times which result from the stored carriers. In the process of carrying out the experiments, approximate delay times are obtained but they do not form the basis of comparison with theory.

The effect of minority carrier injection on conductivity modulation is determined from the overall I-V characteristics which depend on junction characteristics as well as the characteristics of the series epitaxial layer. Direct comparison of the theoretically and experimentally determined I-V characteristics of the device provides the insight necessary to check the adequacy of the theory in treating the effects of conductivity modulation.

This chapter discusses experimental methods to measure the total excess carrier storage in the device for current densities extending to  $10^5~{\rm A/cm}^2$  at several temperatures. The conductivity modulated J-V characteristics are also measured for current densities as high as  $4 \times 10^5~{\rm A/cm}^2$ . Results of such experiments are presented for unguarded and guarded devices. The primary emphasis of the work, however, is on unguarded devices in which injection over the metal-semiconductor interface is the only source of minority carriers.

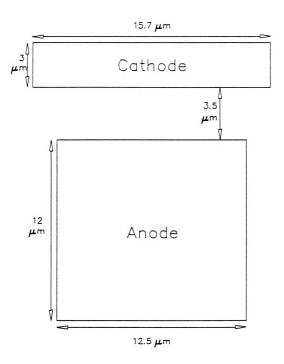

#### 3.2 Test Devices

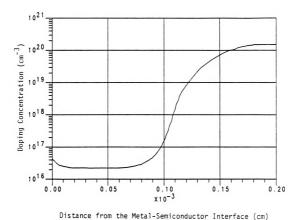

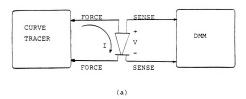

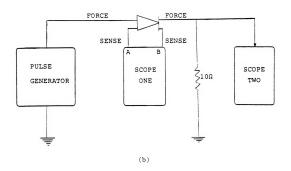

All experimental data was obtained from planar platinum-silicide epitaxial test diodes provided by IBM. The test device in the experiment using Krakauer's method was unguarded and had an anode area of  $30~\mu\text{m}^2$ . With that exception, the results reported here for unguarded devices are on devices with an anode area of  $150~\mu\text{m}^2$  and a 1  $\mu\text{m}$  thick n-type epitaxial layer doped approximately at  $2.5\text{Xl}0^{16}\text{cm}^{-3}$  and grown over an n<sup>+</sup> buried layer. The guarded SBD device area was  $189~\mu\text{m}^2$ . Each test diode, along with several other types of test devices, is fabricated on a  $0.15~\text{cm}^2$  chip. Except for the Krakauer experiment, test devices had two pairs of available terminals, allowing four terminal measurements. Fig. 3-1 shows the top view of the metallization layout of the  $150~\mu\text{m}^2$  unguarded SBD and Fig. 3-2 shows the doping profile of silicon under the anode of that device.

### 3.3 Measurement of Minority Carrier Storage

### 3.3.1 Experimental Method

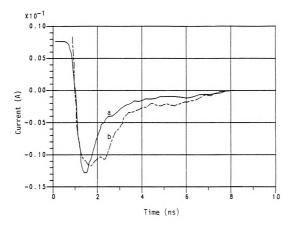

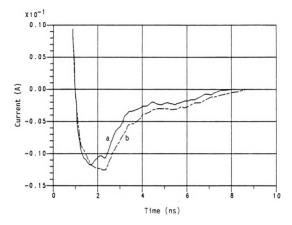

Before the excess minority carrier storage was measured, Krakauer's method, as described in Chapter 2, was used to obtain a qualitative knowledge of the current densities at which the phenomenon is significant in platinum-silicide SBDs. The sinusoidal signal which was used to excite the diode, had a frequency of about 50 MHz. Figure 3-3 shows the response of the diode for peak current values of  $2.5 \times 10^4$  and  $10^5$  A/cm<sup>2</sup>. As can be seen from this figure, for a peak current value of  $2.5 \times 10^4$  A/cm<sup>2</sup>, excess minority carrier storage is

Figure 3-1 Metallization layout of the unguarded SBD.

Figure 3-2 Doping profile of silicon under the anode of the SBD. Data from C.C. Yu  $\left[4\right]$ .

Figure 3-3 Response of a 30  $\mu\text{m}^2$  unguarded test device to sinusoidal excitation at room temperature. (a) Shows the response at a peak current density of 2.67  $\times$  10<sup>4</sup> A/cm<sup>2</sup> and does not show a significant amount of minority carrier storage. (b) Shows the response at a peak current density of 10<sup>5</sup> A/cm<sup>2</sup> and evidence of minority carrier storage is clearly observed.

not observed while, for  $10^5~{\rm A/cm}^2$ , evidence of excess carrier storage is clear. It must be noted, however, that these values of current density, which correspond to sinusoidal excitation, do not relate directly to what would be expected from switching measurements which correspond to excess minority carrier storage under the quasi steady-state dc conditions that hold when the diode is pulsed into the forward bias state.

As previously discussed in Chapter 2, if an appreciable fraction of the forward bias current in the device is due to minority carriers, then upon rapid switching to reverse bias, a reverse current flows while the excess carriers stored in the quasi-neutral regions are being swept out. Integration of the reverse-recovery current yields the total charge removed from the diode. In order to determine the charge associated with stored minority carriers, the total charge obtained from the integration must be corrected for junction and parasitic capacitance stored charge. With this correction, current integration yields the charge associated with excess minority carriers stored in the device prior to switching provided that the lifetime of excess carriers is much larger than the reverse-recovery time such that excess carrier recombination is negligible during reverse-recovery.

The reverse-recovery currents to be measured last on the order of nano-seconds. Therefore, the test circuit must have a high time resolution. Special care must also be taken in mounting the sample in order to avoid any significant parasitic capacitance exterior to the device. The test circuit along with its equivalent circuit is shown in Fig. 3-4. A 10 ns wide pulse at 375 Hz is used to forward bias the device from a fixed reverse bias of -2 V. The low duty cycle of the pulse helps avoid self heating in the device at high current densities.

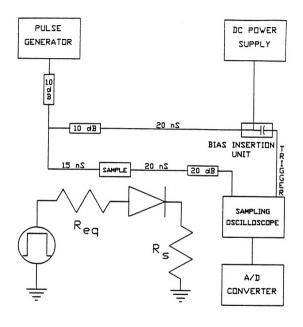

Figure 3-4 Diagram of the circuit for minority carrier charge storage measurement along with its equivalent circuit.  $R_{\rm eq}$  denotes the equivalent resistance of the driving circuit and  $R_{\rm g}$  corresponds to the input impedance of the sampling oscilloscope.

The reverse-recovery was observed on the falling edge of the pulse with a sampling oscilloscope and then digitized. The resulting fall time of the overall circuit was observed to be about 450 ps. Low-loss, lowdispersion coaxial cables with General Radio connectors were used for interconnections in the circuit. The length of the cables were chosen such that no reflections would arrive at the sampling oscilloscope while the step recovery was being observed. Additionally, the length of the cable going to the triggering input of the sampling oscilloscope was chosen such that sufficient delay for proper triggering was obtained. The coupling capacitor in the bias insertion unit provided the isolation of the oscilloscope's trigger input from the dc supply. Attenuators were used to improve impedance matching and to suppress reflections. The bare chip containing the diode was wire bonded in our laboratory and mounted in a modified General Radio coaxial sample insertion unit. The parasitics of the sample mount were observed to be negligible compared to the chip parasitics. To perform the experiment at elevated temperatures, the sample mount was heated using a hot plate controlled by a digital temperature controller which detected the sample temperature using an RTD (resistance temperature detector) sensor. Detailed information regarding the equipment used in each circuit, sample mounting, data collection, and test device integrity is provided in Appendix A.

#### 3.3.2 Correction for the Parasitic Capacitance

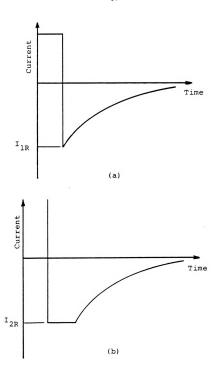

At low forward bias, the minority carrier injection level in a planar device is negligible [3], as verified by the Krakauer experiment previously described, and the entire switching current is due to the discharge of the junction capacitance and the parasitic capacitance. Therefore, integration of the low bias current waveform provides the means to correct for capacitive stored charge. Fig. 3-5 shows idealized waveforms of the reverse-recovery associated with the low injection, primarily capacitive case, and the high injection case which includes the discharge of minority carriers. If the dominant parasitic capacitance is in parallel with the junction capacitance of the diode, then the voltage across the capacitor remains relatively constant from low to high injection since the junction voltage of a forward biased diode does not change much with increasing current. Therefore, the reverse current upon switching remains approximately constant (i.e.  $\mathbf{I}_{2R} - \mathbf{I}_{1R}$  in Fig. 1) since the initial conditions for discharge are approximately equal. Specifically,

$$I_{1R} \approx I_{2R} \approx (V_{jf} - V_r)/(R_{eq} + R_s)$$

(3-1)

where  ${\bf v}_{\rm jf}$  is the voltage drop across the junction of the forward biased diode,  ${\bf v}_{\rm r}$  is the reverse bias voltage, and  ${\bf R}_{\rm eq}$  and  ${\bf R}_{\rm s}$  are the circuit's equivalent resistors as shown in Figure 3-4. In this case, integration of the low injection waveform provides a constant charge to be subtracted from high injection charge integrations. If, on the other hand, the voltage across the dominant parasitic capacitance changes considerably, then  ${\bf I}_{\rm R}$  increases as the forward bias level increases (i.e.  ${\bf I}_{\rm 2R} > {\bf I}_{\rm 1R}$ ) and the low bias capacitive charge must be multiplied by  ${\bf I}_{\rm 2R}/{\bf I}_{\rm 1R}$  before being subtracted from the high injection charge integration. For the device in this study,  ${\bf I}_{\rm R}$  was observed to remain relatively constant as forward bias changed and the low injection

Figure 3-5 Idealized reverse-recovery waveforms. (a) Corresponds to a purely capacitive response while (b) shows the minority carrier induced switching delay.

waveform integration was used as a constant correction to charge integrations.

### 3.3.3 Experimental Limits and Accuracy

Experimental conditions were varied to check the validity of the measurement technique. To verify that during the 10 ns of forward current the diode does reach its steady-state conditions, reverse-recovery after a 14 ns wide pulse was observed and found to be the same as results associated with the 10 ns wide pulse. Also, if the effect of parasitic capacitance is subtracted correctly, then results obtained for minority carrier storage should be independent of the dc reverse bias. To verify this, the experiment was performed using higher values of reverse voltage and agreement with the -2 V results was observed.