# This is to certify that the

# dissertation entitled

Performance Tradeoffs in the

Hierarchical Design of Regular VLSI Structures

presented by

Yu-Ying Jackson Leung

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Elect. Engr.

Michael Shan Clath

Major professor

Date 12/10/85

ن نیتیه:

RETURNING MATERIALS:

Place in book drop to

remove this checkout from

your record. FINES will

be charged if book is

returned after the date

stamped below.

# PERFORMANCE TRADEOFFS IN THE HIERARCHICAL DESIGN OF REGULAR VLSI STRUCTURES

By

Yu-Ying Jackson Leung

### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Electrical Engineering and Systems Science

1986

### **ABSTRACT**

# PERFORMANCE TRADEOFFS IN THE HIERARCHICAL DESIGN OF REGULAR VLSI STRUCTURES

By

### Yu-Ying Jackson Leung

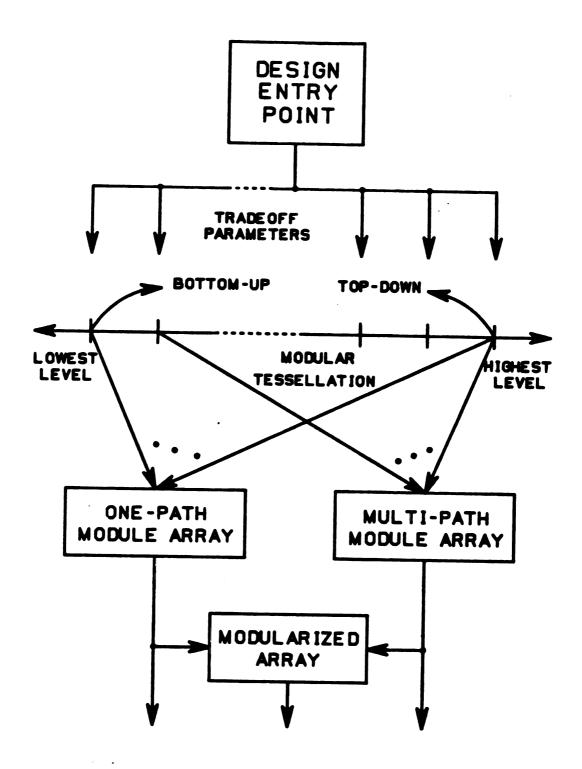

Hierarchical layout is the prevalent design methodology in the computer-aided generation of VLSI circuits. But, the tradeoff of design-complexity versus circuit performance among the various design paths of this hierarchy has yet to be fully assessed and compared numerically. This research provides a systematic and quantitative investigation of this tradeoff for regular structures.

Systolic array structures, for which regular levels of modularity are well defined, are used as testbed structures. The hierarchical regularity levels in a systolic structure are the transistor, gate, functional device, processing element (PE) and algorithmic levels. The investigation of modularity is pursued along two distinct paths — the bottom—up and top—down approaches.

Using the bottom-up approach and standard NMOS design techniques, several PE's are independently designed using the various design entry-points and pathways of the design hierarchy. Results provide a set of area-performance versus design-complexity index figures that represent the tradeoffs among the various design pathways. The general

expressions for the complexity, chip area and propagation time are numerically derived based on an infinite array model.

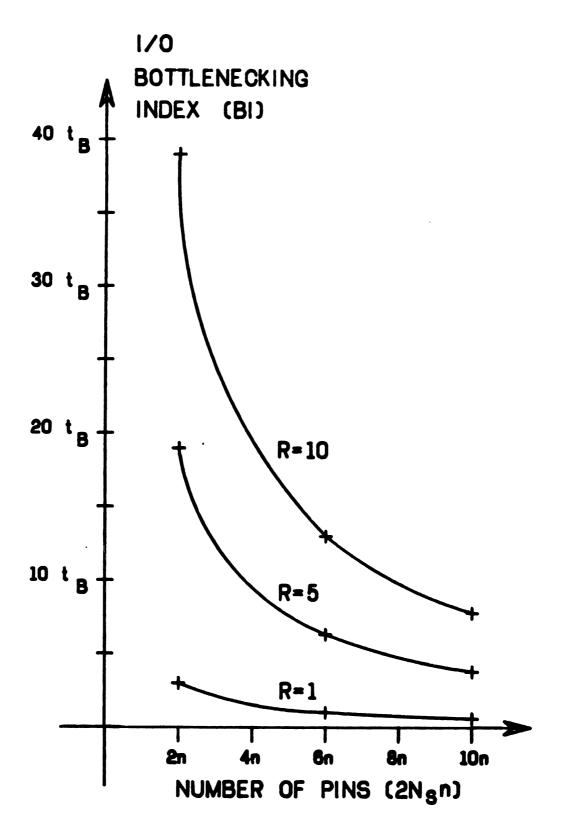

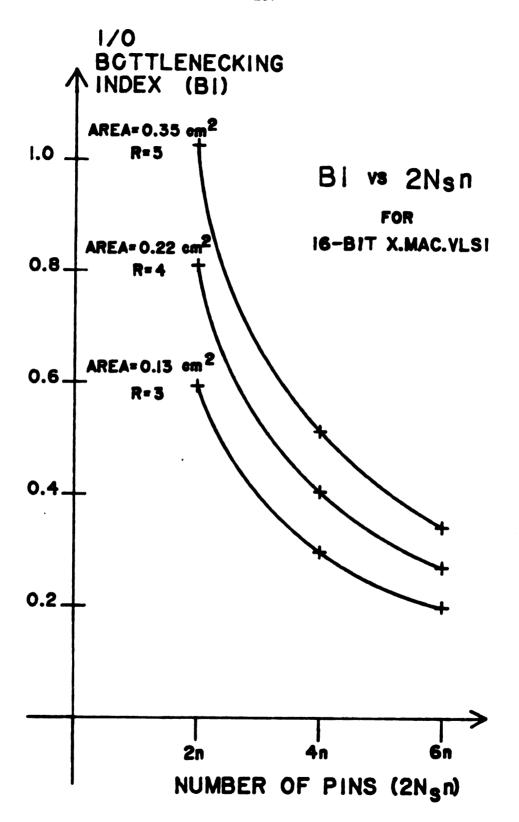

The top-down approach is applied to the algorithmic and PE levels where chip-wise modularity is desired. The various chip-wise decompositions of an array structure are parameterized by an I/O bottlenecking index (BI). Results show the relationship of BI to the number of pinouts, word size in number of bits and chip size.

Results obtained from the bottom-up and top-down approaches provide an analysis of several tradeoff parameters. An appropriate design pathway can thus be chosen with respect to the desired tradeoff parameters of the final design.

To my mother and eldest brother

Mdm. Me Chit and Mr. Wai-Ying Tommy Leung

### **ACKNOWLEDGEMENTS**

The author wishes to express his sincere appreciation to his major advisor, Dr. Michael A. Shanblatt, for his guidance and encouragement in the course of this research.

He also wishes to thank the committee members, Dr. E. Goodman, Dr. P. D. Fisher, Dr. R. A. Schlueter and Dr. D. Yen for giving the quidance, suggestions and comments in this work.

Other thanks are given to Dr. Goodman, Director of A. H. Case Center for Computer-Aided Design at MSU, for allowing the author to use the Computervision CADDS system, and Dr. Stephanie Shanblatt for the proofreading of this dissertation.

Finally, the author owes a special thanks to his wife, Jasmine, for her emotional encouragement and support, and especially, for her patience while the author was in East Lansing pursuing this work.

From alpha to omega, Glory to God for endlessly providing the love, wisdom, hope, faith and forgiveness.

# TABLE OF CONTENTS

|      |       |                                       | Page |

|------|-------|---------------------------------------|------|

| LIST | OF TA | BLES                                  | vi   |

| LIST | OF FI | GURES                                 | vii  |

| ī.   | INTR  | ODUCTION                              | 1    |

|      | 1.1   | Problem Statement                     | 3    |

|      | 1.2   | Approach                              | 6    |

|      |       | 1.2.1 The Bottom-up Approach          | 7    |

|      |       | 1.2.2 The Top-down Approach           | 9    |

| II.  | BACK  | GROUND                                | 11   |

|      | 2.1   | VLSI Design Methodology               | 12   |

|      |       | 2.1.1 IC Design Systems               | 14   |

|      |       | 2.1.2 Application-Specific IC Layout  | 16   |

|      |       | 2.1.3 Silicon Compilation             | 19   |

|      |       | 2.1.4 Hierarchical Design Methodology | 21   |

|      | 2.2   | VLSI Technologies                     | 22   |

|      | 2.3   | VLSI Systolic Array Structures        | 24   |

|      | 2.4   |                                       | 26   |

|      | 2.5   | Y-Chart Representation of VLSI        |      |

|      |       | Design Methodologies                  | 29   |

| III. | BOTT  | OM-UP APPROACH                        | 33   |

|      | 3.1   | Transistor and Gate Level Design      | 36   |

|      | 3.2   | Functional Device Level Design        | 39   |

|      | 3.3   |                                       | 43   |

|      | 3.4   | Systolic Arrays for Matrix            |      |

|      |       | Multiplication                        | 45   |

|      | 3.5   |                                       |      |

|      |       | Array Structures                      | 48   |

|     |                         |                                      | Page  |

|-----|-------------------------|--------------------------------------|-------|

| IV. | TRAD                    | EOFF PARAMETERS EVALUATION           |       |

|     | AND                     | JUSTIFICATION                        | 51    |

|     |                         | Chip Area and Propagation            |       |

|     |                         | Time Computation                     | 52    |

|     | 4.2                     | •                                    |       |

|     |                         | VLSI Structures                      | 56    |

|     |                         | 4.2.1 Module Placement Approach to   |       |

|     |                         | Design Complexity                    | 58    |

|     |                         | 4.2.2 Compactness Ratio Approach to  | -     |

|     |                         | Design Complexity                    | 60    |

|     |                         | 4.2.3 Tradeoff of Compactness Ratio  |       |

|     |                         | Versus Area-Time                     | 66    |

| V.  | mon.                    | DOWN APPROACH IN ARRAY DECOMPOSITION | 76    |

| ٧.  | 5.1                     |                                      | 76    |

|     | 2.1                     | oner                                 | 70    |

|     | - 0                     | Systolic Structures                  | 78    |

|     | 5.2                     |                                      |       |

|     |                         | and Pinout Limitations               | 82    |

| VI. | RESULTS AND CONCLUSIONS |                                      | 90    |

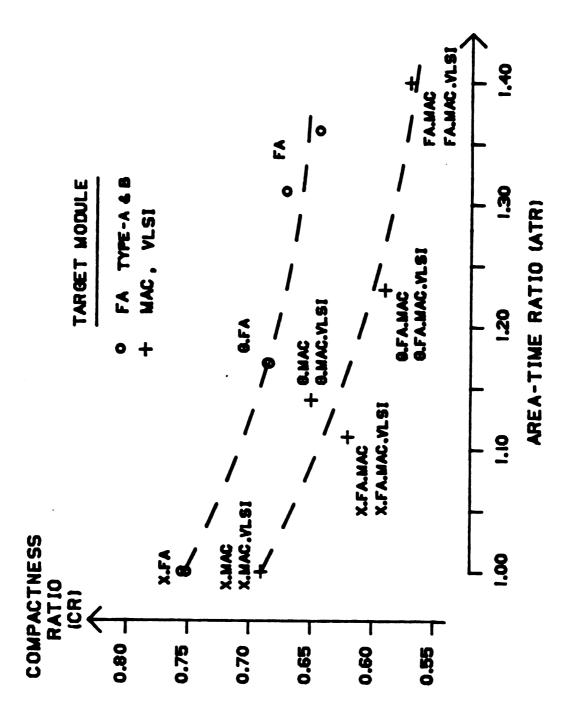

|     | 6.1                     | Compactness Versus Area-Time Ratios  | 90    |

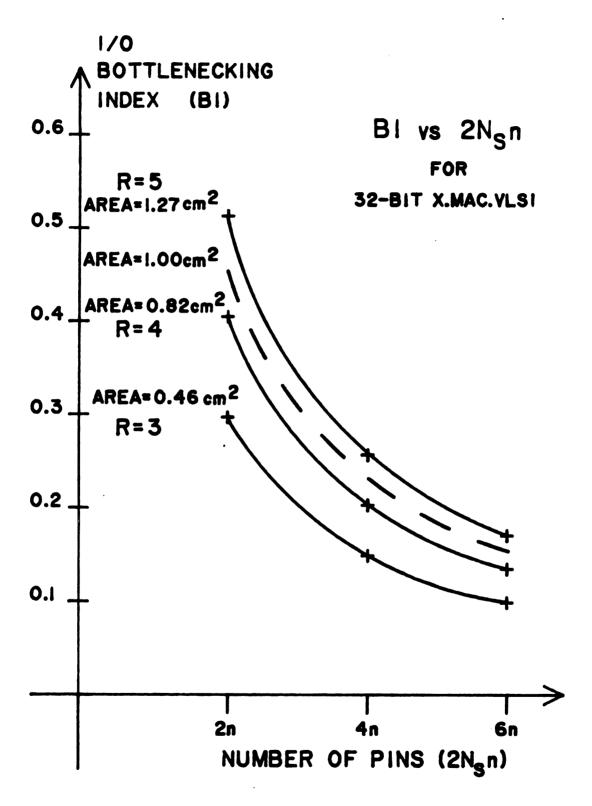

|     | 6.2                     | I/O Bottlenecking Index              | 101   |

|     |                         | Contributions                        | 108   |

|     | 6.4                     | Trends in VLSI and Future Study      | 111   |

|     | BIBL                    | IOGRAPHY                             | 114   |

|     | ADDE                    | Whix                                 | . 110 |

.

# LIST OF TABLES

| <u>Table</u> | •                                                                   | Page |

|--------------|---------------------------------------------------------------------|------|

| 6.1          | Area-time and compactness ratios of FA                              | 93   |

| 6.2          | The typical physical parameters of MOSFET technology                | 94   |

| 6.3          | Area-time and compactness ratios of MAC                             | 96   |

| 6.4          | Area-time and compactness ratios of various target modules          | 99   |

| 6.5          | Comparison of I/O bottlenecking index, pin limitation and chip area | 104  |

# LIST OF FIGURES

| <u> Figure</u> | ·                                                              | Page |

|----------------|----------------------------------------------------------------|------|

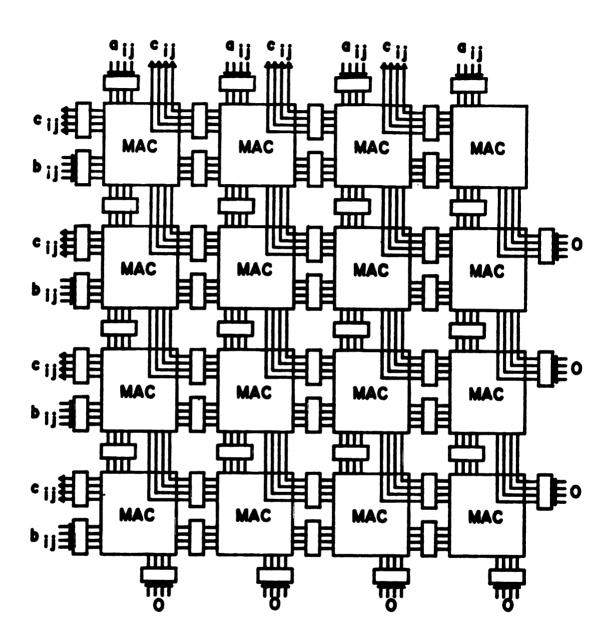

| 2.1            | Two types of MAC's                                             | 25   |

| 2.2            | Mesh-connected MAC's for matrix multiplication                 | 27   |

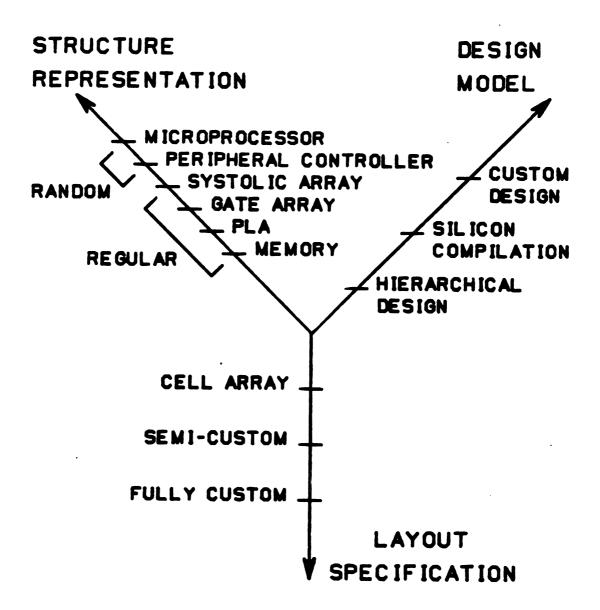

| 2.3            | A modified Y-chart representation of typical VLSI-based design | 31   |

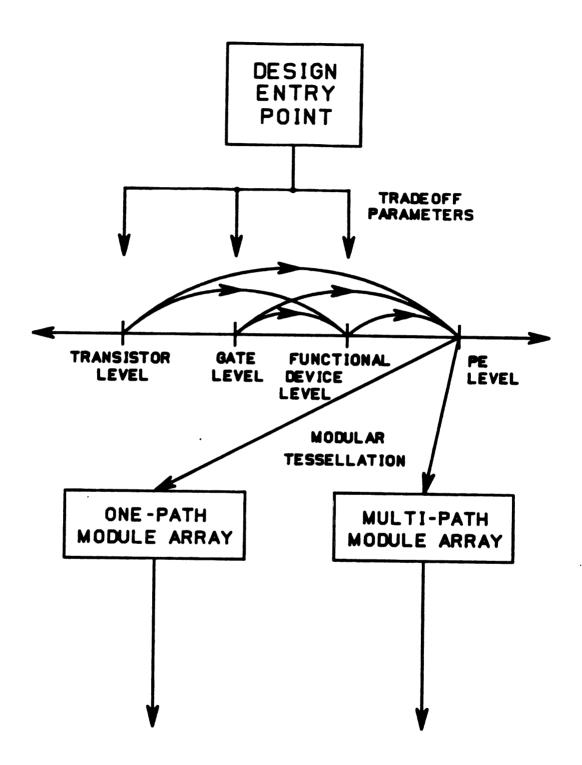

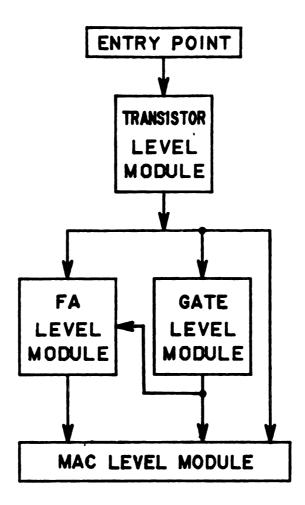

| 3.1            | An overview of the bottom-up approach                          | 34   |

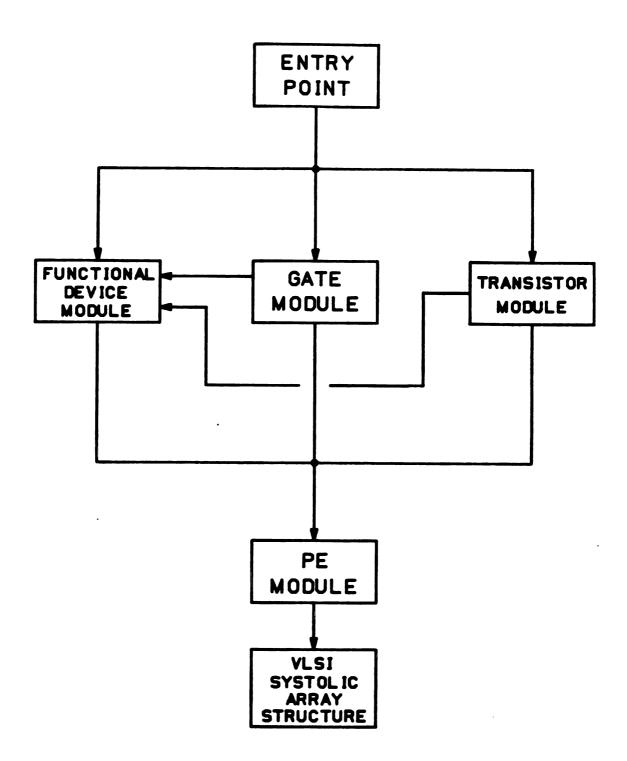

| 3.2            | Design hierarchy in the bottom-up approach                     | 35   |

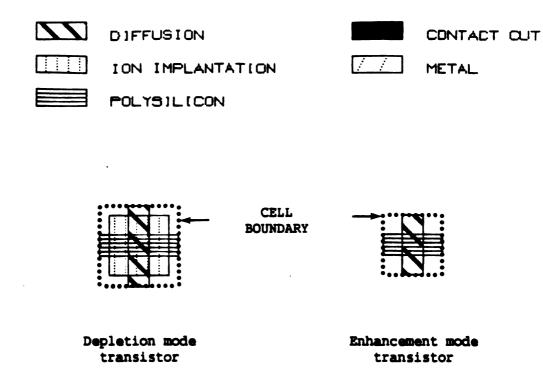

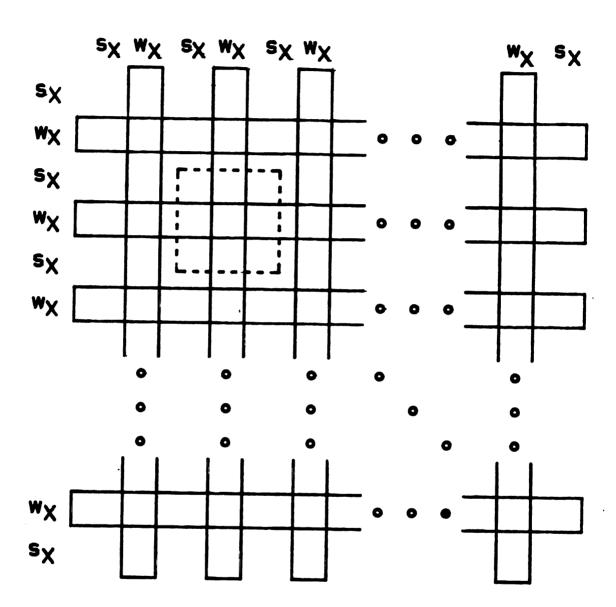

| 3.3            | Cell boundary of two transistor modules                        | 37   |

| 3.4            | Typical gate-level modules                                     | 38   |

| 3.5            | Logic diagram for the implementation of FA                     | 40   |

| 3.6            | Alternate version of Figure 3.5                                | 41   |

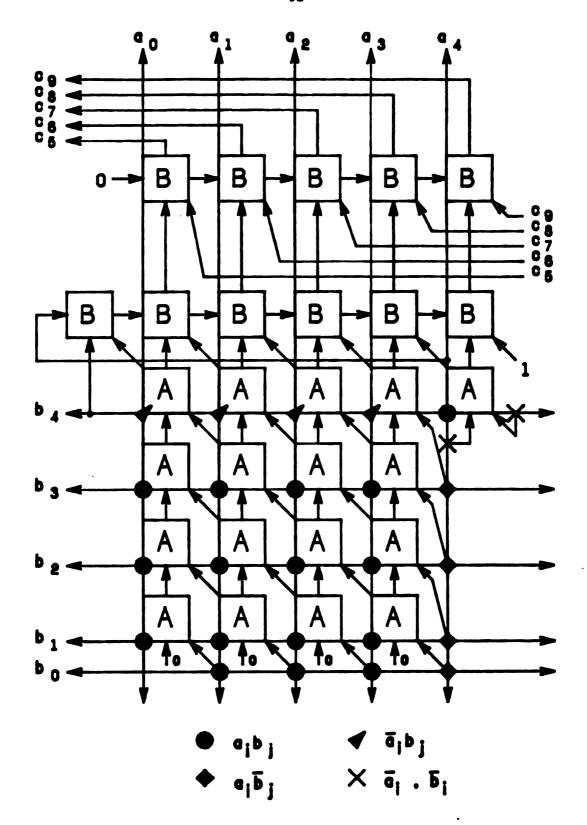

| 3.7            | Logic diagram of a 5-by-5 Baugh-Wooley based MAC               | 44   |

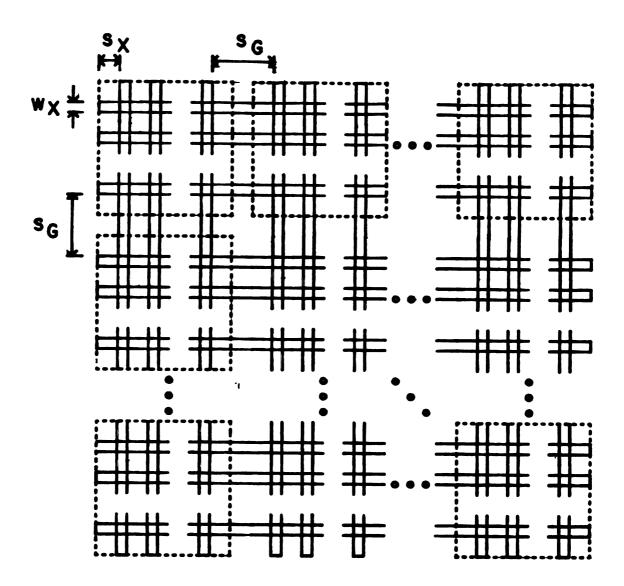

| 3.8            | Array network for C=AxB shown in Figure 2.2.                   | 47   |

| 3.9            | Design entry-point and pathway of various target structures    | 48   |

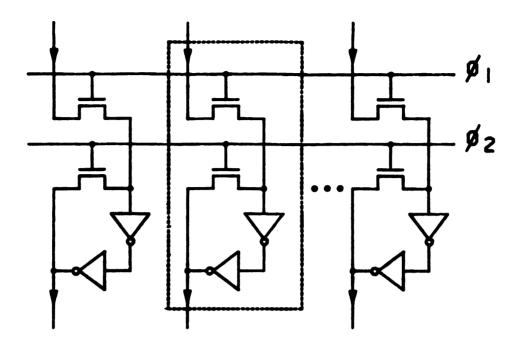

| 3.10           | Dynamic latches                                                | 49   |

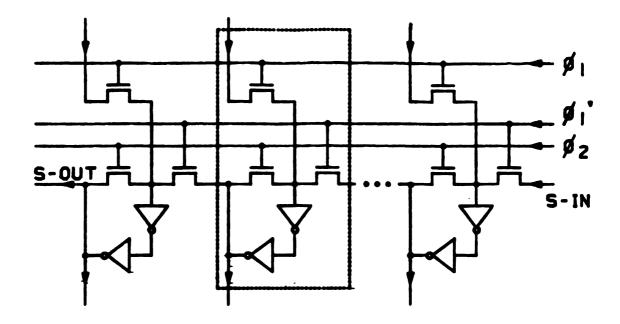

| 3.11           | Dynamic latches with scan design                               | 50   |

| <u>Figure</u> | igure                                                                           |     |

|---------------|---------------------------------------------------------------------------------|-----|

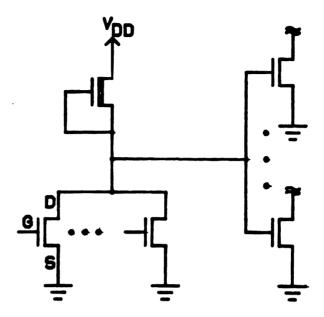

| 4.1           | An N,-input NMOS NOR gate driving No identical outputs                          | 53  |

| 4.2           | A transistor-level module                                                       | 62  |

| 4.3           | A gate-level module                                                             | 64  |

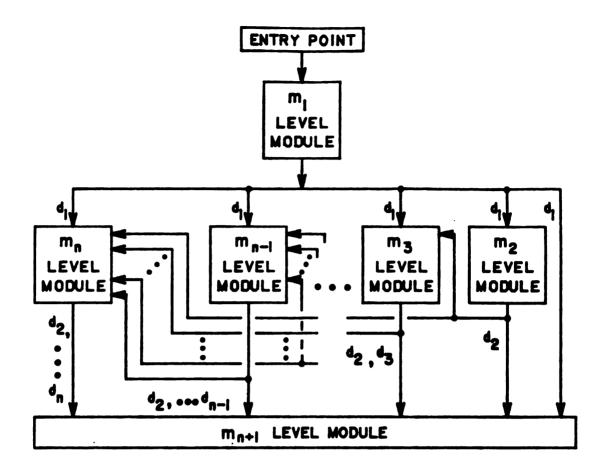

| 4.4           | Hierarchical design model of an n+1 level module                                | 67  |

| 4.5           | Hierarchical design model of a MAC level module                                 | 68  |

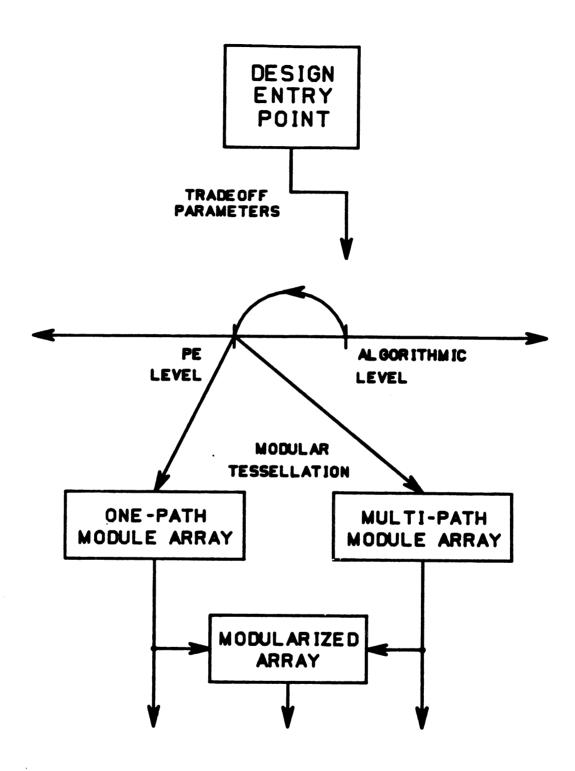

| 5.1           | An overview of the top-down approach                                            | 77  |

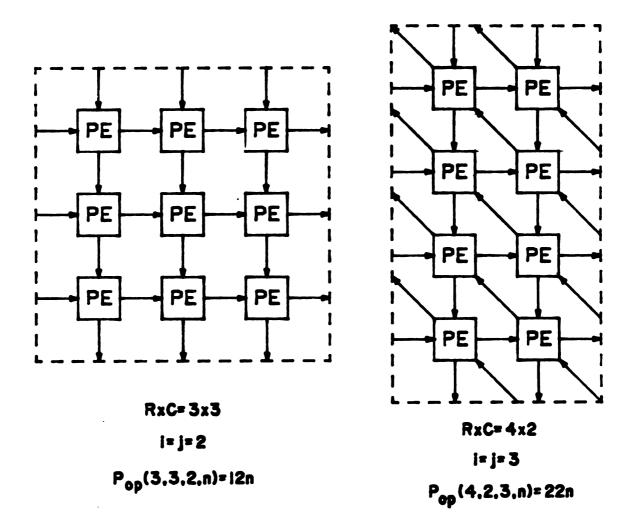

| 5.2           | Examples of partitioned arrays                                                  | 79  |

| 5.3           | Array of modularized chips having N <sub>S</sub> <i=j< td=""><td>83</td></i=j<> | 83  |

| 5.4           | Array of modularized chips having N <sub>s</sub> =i=j                           | 84  |

| 5.5           | I/O bottlenecking index versus number of pins                                   | 88  |

| 6.1           | Schematic layout of a 5-bit MAC                                                 | 92  |

| 6.2           | Compactness ratio versus area-time ratio                                        | 100 |

| 6.3           | BI versus 2N n for 32-bit "X.MAC.VLSI"                                          | 105 |

| 6.4           | BI versus 2N n for 16-bit "X.MAC.VLSI"                                          | 107 |

| 6.5           | A summary of bottom-up and top-down approaches.                                 | 110 |

| <u>Figure</u> |                                                         | Page |

|---------------|---------------------------------------------------------|------|

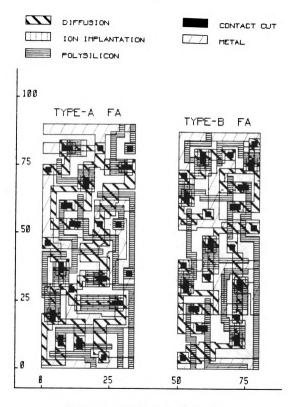

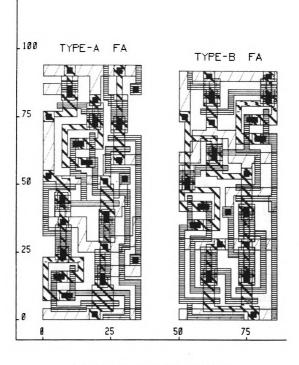

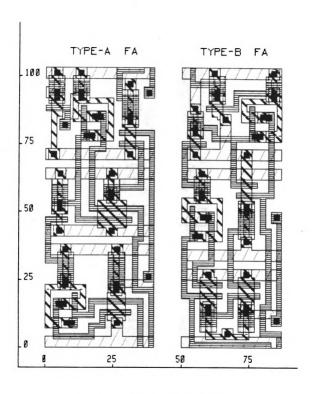

| <b>A.</b> 1   | Physical layouts of "X.FA"                              | 119  |

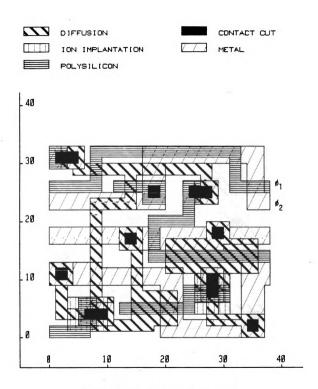

| A.2           | Physical layouts of "G.FA"                              | 120  |

| A.3           | Physical layouts of "FA"                                | 121  |

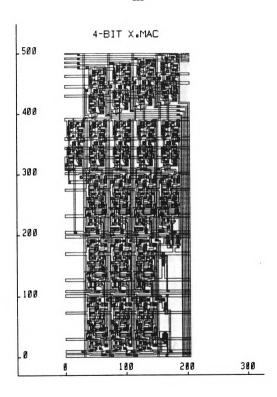

| A.4           | Physical layout of a 4-bit "X.MAC"                      | 122  |

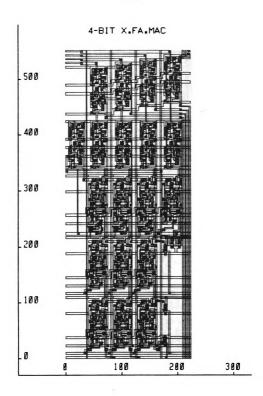

| A.5           | Physical layout of a 4-bit "X.FA.MAC"                   | 123  |

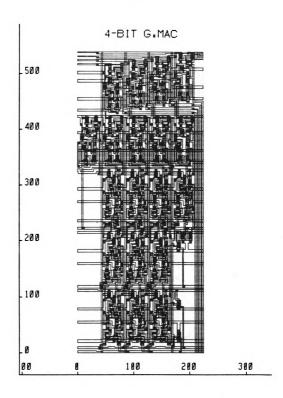

| A.6           | Physical layout of a 4-bit "G.MAC"                      | 124  |

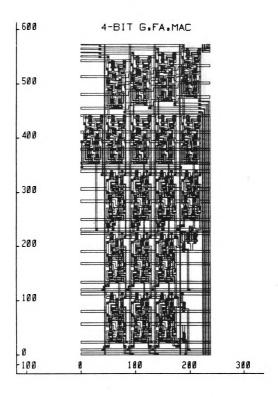

| A.7           | Physical layout of a 4-bit "G.FA.MAC"                   | 125  |

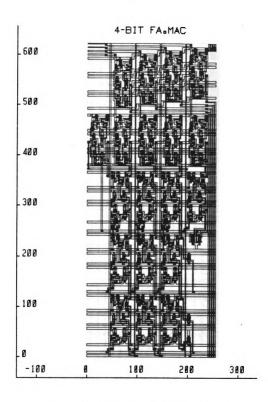

| A.8           | Physical layout of a 4-bit "FA.MAC"                     | 126  |

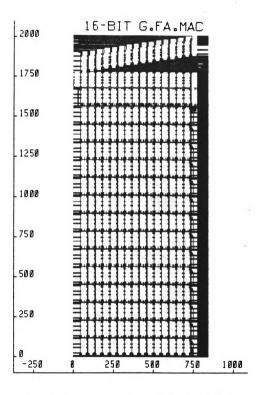

| A.9           | Physical layout of a 16-bit "G.FA.MAC" without "G.FA's" | 127  |

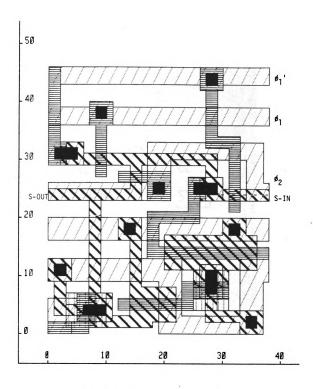

| A.10          | Physical layout of a latch without scanning ability     | 128  |

| A.11          | Physical layout of a latch with scanning ability        | 129  |

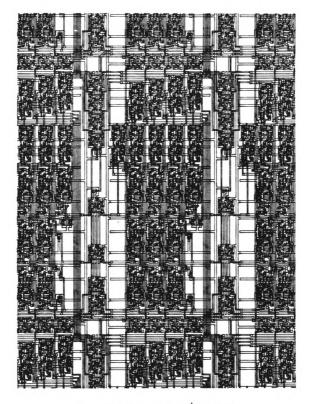

| A.12          | Physical layout of a 4x4 matrix-matrix multiplier       | 130  |

| A.13          | A zoom view of Figure A.12.                             | 131  |

### CHAPTER I

### INTRODUCTION

A methodology for VLSI (Very Large Scale Integration) circuit layout beyond the element level is rapidly emerging. Hierarchical circuit design for VLSI-based structures provides simplicity in both hardware specification and verification. These hierarchical design methodologies have become the prevalent technique in the computer-aided design (CAD) of VLSI circuits [1, 2]. In particular, a hierarchical technique provides designers with the flexibility of approaching a VLSI design via several different pathways, the choice of which corresponds to the final circuit performance. Moreover, circuits designed using different hierarchical levels will entail different design complexities which relate to a measure of design-time.

Specifically at higher levels in the design hierarchy, IC (Integrated Circuit) layout requires a relatively low design-time but tends to produce circuits larger in size and with slower propagation delay. At lower levels, however, layout requires more design-time but can be anticipated to produce more efficient circuits in terms of area and delay time parameters. In other words, there is an obvious tradeoff among design-time, final chip area, and circuit performance. This tradeoff is intimately related to the choice of the specific pathway traversed in the hierarchical design methodology.

This research further investigates and contributes to aspects of hierarchical circuit design techniques for regular structures and is aimed at enabling ultra-dense circuit design, layout and verification to become an efficient and routine task. Broadly, two major types of VLSI-based structures can be defined. They are regular structures, such as memory, logic-array and systolic array structures, and random (non-regular) structures such as microprocessor architectures. Since multi-level regularity and modularity are well defined in regular structures, the hierarchical design of this type of circuit is of particular interest in this work.

Regular structures contain arrays or meshes of interconnected modules which properties of modularity and local possess the connectivity. These regular modules can be subdivided into sub-modules. the sub-modules can further be subdivided and so on, such that the multi-level modularity of the design hierarchy is distinctly defined. Within this hierarchy, modules from the preceding level may be tessellated to form modules in the next level. For example, transistors can be tessellated to form gates, gates tessellated to form functional devices, and so on. Finally, high level functional devices, called processing elements (PE's) are tessellated to implement a particular algorithm. Tessellation implies that modules are designed and placed on the chip surface so as to "tile the plane" or fill the chip surface with minimum null interstitial space. In the literature, modules such as processing elements are depicted as circles or hexagons, but in actual circuit implementation, these devices usually do not possess such ideal geometric shapes.

The ultimate goal of this work is to define a set of general expressions using several defined parameters such as complexity, utilization of chip real estate, circuit performance, pin number and global input/output (I/O). Using this set of expressions, tradeoffs among the multiple levels of the design hierarchy can be observed. Therefore, a designer can choose an appropriate design pathway with respect to the desired tradeoff parameters of the final design.

### 1.1 Problem Statement

All current design methodologies tend to tradeoff design turnaround time for circuit performance. In general, fully custom designs produce IC's exhibiting the best performance and density but require the longest design time. On the other hand, standard cell and gate-array approaches provide much faster turnaround time but greatly degrade circuit performance and chip area utilization. Therefore, a methodology aimed at producing IC designs with optimal tradeoffs among design-time, circuit performance and chip area utilization is desired. Ideally, a well defined methodology must provide flexibility in design tasks and verification such that it is useful at any level of IC design.

A hierarchical methodology appears to be the best approach to achieve such flexibility. In addition, a methodology of hierarchical modularity corresponds to the current trend that requires increasing hardware regularity at successive levels to enable cost—and time-effective layout and verification. However, the tradeoff of

circuit performance versus design complexity among the various entry points of this hierarchy has yet to be fully assessed and compared numerically.

The testbeds for the hierarchical design of regular structures explored in this research are systolic array computing structures. Systolic structures consist of arrays of interconnected processing elements (PE's) which possess the properties of regularity (modularity), local communication, and parallelism and pipelining. The multi-level regularity of these structures makes them an ideal candidate for studying hierarchical design modularity. Regularity in systolic structures is present at the following levels of increasing complexity:

- -- transistor modules,

- -- gate modules,

- -- functional device modules,

- -- PE modules.

Systolic structures have already been shown to hold great promise in engineering systems and other applications including signal and image processing, matrix arithmetic and graph theoretic algorithms [3-8]. However, systolic arrays have yet to be widely accepted in industry due to a lack of sound and well defined design methodologies and a feasible solution to the chip level I/O limitation [9, 10].

The goals of this research are twofold as follows:

1. This research is to provide a systematic and quantitative investigation of the tradeoffs for several levels of

entry-points and paths within the hierarchical design of regular structures. In other words, design tradeoffs of systolic array or other similar structures can be parameterized in terms of design time or complexity, system performance and chip area utilization. This parameterization will vary depending on the levels at which the design is performed. Thus, the design-complexity/performance tradeoff of this design methodology depends on the level or levels that are chosen.

2. The second goal is to parameterize the highest level of regularity possible -- modular algorithmic decomposition onto chips. This is specifically to be examined with respect to I/O limitation parameters. Structural decomposition of systolic arrays presents the possibility of infinite dimension problems (bandwidth and/or word size) to be implemented by a set of chips. Decomposition of this type is physically constrained by near term IC lithographic linewidth and chip size limitations. In addition, the I/O bottleneck caused by limitation of the number of pinouts per chip, may result in degradation of overall system performance. Thus the goal of this phase of the research is to study the effect of I/O limits on the geometric decomposition of regular arrays.

As a whole, this research aims to define the tradeoffs among the various levels in hierarchical layout design for regular structures.

Two approaches will be presented — the bottom-up approach (Chapters 3 and 4) and the top-down approach (Chapter 5). In general, a top-down

approach is first used to design the functional circuit and then a bottom-up approach is applied to the design of the final layout [11].

# 1.2 Approach

In order to investigate and further define design tradeoffs and methodology for hierarchical modularity in VLSI circuits, structures possessing multi-level regularity and modularity are used as testbed or benchmarking structures. Of particular interest is the specification of systolic computing structures for matrix calculation. The levels of this hierarchy to be examined are:

- 1. The transistor level at which basic transistor modules (pull-up and pull-down) are defined and tessellated to form basic gates;

- The gate level at which basic gates (e.g. NAND, NOR, etc.) are defined and tessellated to form functional modules (e.g. functional devices);

- 3. The functional device level at which basic functional devices (e.g. full adders) are defined and tessellated to form processing elements (e.g. multiply-add cells);

- 4. The processing element (PE) level at which PE's are defined and tessellated to form numerical computing structures;

- 5. The algorithmic level at which numerical decompositions provide chip-wise modularity.

Levels 1, 2, 3 and 4 may be lumped together and considered as four on-chip device levels of increasing complexity and viewed externally as computational modules. Thus, the investigation of modularity can be pursued along two paths — the bottom-up and top-down approaches described in the following sections.

# 1.2.1 The Bottom-Up Approach

The bottom-up approach involves the specification of increasingly complex, tessellated functional modules. This implies designing modules at the transistor, gate, functional device and PE levels. These design tasks were performed on the Computervision CADDS 2/VLSI design system at Michigan State University. However, it will be shown later that the final results of this research do not depend on any particular CAD system.

Circuit simulation programs are developed to parameterize net propagation delays and chip area requirements. These results are used to specify the performance and chip area utilization of the structure when designed at specified levels. A heuristic assessment of the design task complexity with respect to the relative time required for the different hierarchical design paths are developed and justified. This assessment is based on a parameter of circuit complexity determined as a function of the number of building blocks or modules requiring placement, the number of interconnecting lines or wires requiring routing, or the compactness of the target circuit (active region/module size).

The final goal is to provide circuit designers with a choice of the best balance between the cost or design complexity versus the performance specifications for a given circuit.

Specifically, the tasks in the bottom-up approach are as follows:

- 1. As a basis to the study of tradeoffs among the various design levels, modules at several levels are designed and simulated using standard NMOS design rules. Transistor modules and gate level modules are first designed and stored in the cell library of the CADDS 2/VLSI design system. Next, independent full adders (FA's) are carefully crafted and tessellated based on the predefined transistor or gate modules. Then, five independent multiply-add cells (MAC's) are likewise designed corresponding to five different design paths of mixed levels. Finally, VLSI systolic array structures are tessellated from MAC's and dynamic latches.

- 2. Overall performance and total chip area of the conglomerate systolic array structures built from the combination of the various modules are obtained. Since the complete systolic array structure is merely a tessellation of MAC's and dynamic latches, its total chip area is simply the sum of the areas of all modules. The propagation time of the array is calculated by using a charging-discharging model. This model, taking communication path and effective load capacitance into account, provides an estimation of time delay accurate enough for comparative purposes [12]. As a result, five different sets of area and delay time data, corresponding to each different

design path, are obtained. These data are then normalized to provide index figures of the performance of the various ultimate systolic structures.

- 3. A heuristic measure assessing design cost is examined in terms of design complexity. The complexity of the structures is represented by the number of devices (modules) to be placed, the number of interconnecting lines to be routed or the compactness of circuit (active region/module size). A selected parameter is normalized in order to provide an index of the design complexity for the different hierarchical paths. Finally, a complete set of performance versus design complexity index figures is obtained.

- 4. An automated testing methodology for systolic array structures is investigated with respect to its specific effect on design complexity. Scan design used in level-sensitive scan design (LSSD) [13] and scan path techniques [14], which of course affects the chip area utilization and performance, is considered.

# 1.2.2 The Top-Down Approach

The top-down approach is applied to the algorithmic and PE levels where chip-wise modularity is desired. Chip level modularity, which is

necessary to alleviate the pinout limited I/O problem, is attacked by algorithmic decompositions. These decompositions are studied by evaluating the effect of various physical partitions to the array structure. The ideal size of a partition matches, in the sense of throughput, the maximum feasible I/O bandwidth.

The specific tasks performed here are as follows:

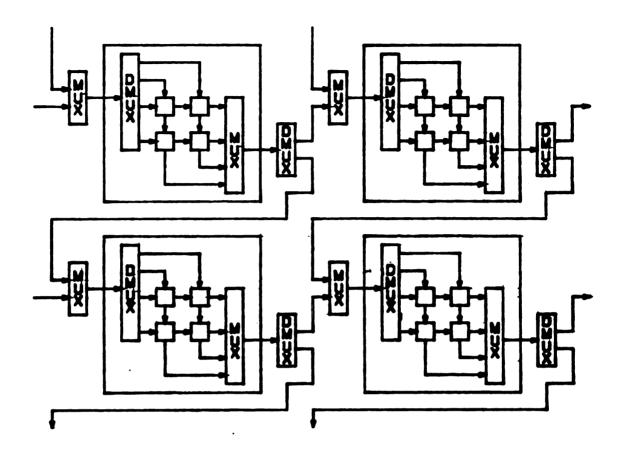

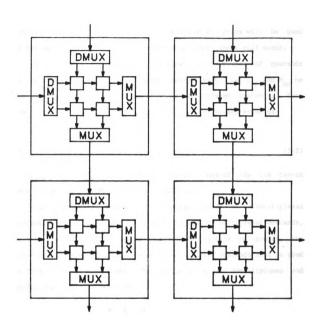

- 1. To study the decomposition of a final target systolic array structure; an optimal number of PE's that will fit on a single chip is determined. Too few PE's on a chip implies that the I/O bandwidth capacity is underutilized. On the other hand, too many PE's on a chip will cause an I/O bottleneck of operands. Next, MUX/DMUX schemes that affect the I/O bandwidth and the number of pinouts are examined. Finally, general parameters are developed for evaluating the effect of the structural decomposition of regular arrays with respect to I/O limitations.

- 2. Using the testbed systolic array, the general parameters are depicted graphically. As a result, the tradeoffs among the I/O bottleneck, the number of pinouts and the chip size limitation are explicitly shown.

### CHAPTER II

### BACKGROUND

During the 1950's, the photolithographic process for the fabrication of transistors on crystalline silicon was first developed. In the 1960's, the integrated circuit (IC) fabrication process including design and testing was largely manual. Process parameters, such as diffusion temperature and time, metal line widths and spacing were characterized primarily through trial-and-error. As the technology progressed through the 1970's, the number of devices per chip just about doubled every year (Moore's law) and design costs grew nearly as fast as complexity [15]. This increase in complexity and cost is largely responsible for the proliferation of design automation (DA) facilities and computer-aided design (CAD) for circuit layout and verification.

In the early 1980's, a new type of computerized tool, the computer-aided engineering (CAE) workstation with general IC layout editing capability was developed to help cope with the growth of IC complexity [16]. But, there are still many problems dealing with ultra-dense circuit design and verification. For example, circuit simulation or testing may run for weeks or months in order to obtain accurate results [17]. This and other reasons have promoted hierarchical design to rapidly become the prevalent approach in VLSI design [1, 2].

Today, numerous design systems or tools (either fully automated or computer-assisted) using various design methodologies are available commercially. In the following sections, aspects relating to the state-of-the-art in today's VLSI technology are discussed.

### 2.1 VLSI Design Methodology

VLSI design practices vary from the fully integrated, highly automatic gate array design capabilities of the large systems manufacturers to the computer-assisted but still somewhat manual methodologies of the designers of high-density custom MOS or bipolar microprocessors. A typical composite state-of-the-art design system includes interactive and graphics terminals, host mainframe computer, control and release system, multimode hierarchical data base and an automated verification system for design rule checking.

Modern design automation systems are powerful tools for the synthesis and analysis of VLSI circuits. Logic entry is an interactive task which is supported by intelligent engineering workstations. The verification of specifications of system behavior is accomplished through design reviews, emulation on existing hardware, and simulation using general— or special—purpose simulations. Simulators are used to verify a system design in terms of functional components. Ideally, a mixed—mode simulator capable of combining behavioral, unit logic and switch level, and analog circuit level models is desired [18, 19].

A mixed-mode simulator, which has proven to be flexible and cost-effective, is especially crucial to the hierarchical design methodology [18, 20]. It allows different elements of a complete circuit to be modeled and simulated at different levels of detail. In addition, it allows for digital macromodeling and mixing logic and timing simulation with transient analysis at device or macromodel levels. Most mixed-mode simulators can handle primitives ranging from high level devices (op-amps, registers, etc.) down to the transistor level. This is made possible by the use of the same program from logic verification down to transistor circuit design.

In mixed-mode simulation, a circuit can be simulated and evaluated in timing, unit delay or multiple delay mode [18, 19]. The rise and fall delays of a normal gate are computed automatically from the transistor current-voltage curves and load capacitances. For logic gate and functional primitives, the rise and fall delays (unit or multiple) are computed from user specified delay coefficients, gate types, routing capacitances and the number of fanouts. The mixed-mode simulation also allows the mode to be changed dynamically (i.e., a mode switching during simulation) providing a more cost-effective simulation [18-20].

Hierarchical design methods, utilizing the "divide and conquer" principle, are considered a means of managing the VLSI design and verification problems [1, 21]. The primary concepts are abstraction, repetition and the use of a database library. Abstraction is a method of replacing an object by a simplified version that only defines the interactions of the object with its environment while neglecting the internal organization of the object. The virtue of abstraction is data

reduction, often by one or more orders of magnitude [1]. Several levels of abstraction may be required for VLSI systems. Repetition is an easy and often applied method of simplifying design. It is most useful for regular (array type) architectures (RAM's, ROM's, PLA's and systolic arrays). The use of a database library avoids redesign.

### 2.1.1 IC Design Systems

Today, the practice of the VLSI circuit design is so broad that there is no single IC design system which universally meets the needs of every IC designer or engineer. Current IC design systems include computer-aided design (CAD) systems, design automation (DA) systems and computer-aided engineering (CAE) workstations. The differences and similarities among CAD, DA and CAE are described in the following paragraphs.

CAD systems range from the use of simple, interactive graphics and digitizing systems to individual programs used for circuit or logic simulation, mask layout, and data manipulation or reformatting [22]. CAD can also be characterized as a batch-oriented process with a designer guiding each design step such as functional, logic, test and layout design. In other words, CAD is a collection of hardware and software tools to provide the designer with assistance during each design step. Although there is often a lack of smooth links among those different tools used during the design cycle, a good CAD system provides a designer with a rapid and orderly method for consolidating and evaluating design ideas. In addition, it relieves the designer of

numerous mechanistic and sometimes very repetitive design steps.

Unlike the CAD system, all aspects or steps of a design automation (DA) system are interrelated. Every step in DA shares the same database and draws information from every other step [23]. Thus, DA smoothes the CAD design process by insuring that the completed work of each step properly relates to that of other steps and can be passed efficiently to the next. The tools used by a DA system depend on the design methodology. Basically, they are

- -- text editors and documentation systems for design specification;

- -- functional and logic simulators for initial checking;

- -- test analyzer, generator, simulator and grader for design testing;

- -- timing analyzer and waveform displays for timing analysis;

- -- layout graphic editors, routing and placement algorithms, layout compacter and design rule checker for circuit layout;

- -- tooling and art work programs for mask or pattern generation.

Computer-aided engineering (CAE) workstations are a combination of the CAD and DA system philosophies. A CAE workstation must be able to handle the tasks of schematic capture, logic simulation, timing analysis, data reformatting and manipulation, documentation and interfacing with other computers. Additionally, CAE systems contain other tools for analysis and automated layout [16]. Following the procedure of the schematic capture, where netlists having a special syntax are produced, the CAE station can immediately simulate and analyze the design automatically. The interfacing with another computer (mainframe) allows detailed simulation or other time-consuming tasks to

be handled more efficiently.

Ideally, a complete IC design system is composed of a host mainframe computer interconnecting with numerous standalone CAE workstations, high resolution color graphic terminals, technology independent DA tools or software packages, a silicon compiler for custom IC designs, mixed-mode simulators, and sufficient memory for database and cell libraries. Software packages must include aids for design specification and partitioning, system and circuit synthesis, system partitioning, simulation at various levels, IC mask layout, design verification, testability evaluation, test sequence generation and design documentation. In addition, hierarchical design must be fully supported and the design system should support functional (logic translation), testability (simulation) and physical (layout) designs to be done in parallel throughout the design process.

# 2.1.2 Application-Specific IC Layout

Application-specific IC design can be categorized by three approaches from the standpoint of design complexity and circuit performance. Arranged in decreasing order of design complexity and circuit performance, they are the fully custom, semi-custom and gate-array approaches.

The fully custom approach involves the placement and interconnection of devices at the transistor level so as to achieve maximum packing density and circuit performance. This approach, without using any predefined cell library, requires a complete set of unique

mask layouts to define the user-specific design. As a result, the fully custom approach represents the best method in terms of highest performance and chip area utilization. On the other hand, the high design costs coupled with long design and development time tend to limit the practicality of this approach.

Semi-custom design, which is also known as standard cell, building block or masterimage approach [24, 25], involves the use of fully characterized standard circuit cells extracted from a cell library to implement a desired design. Elements or cells, characterized in electrical and performance terms, are extracted from this library and arranged manually, or under automatic CAD control for placement and routing.

The different types of standard basic cells that are prevalent today include random logic cells (e.g. gates such as inverters, NAND, NOR and XNOR), storage cells (e.g. latches and flip-flops), I/O pads (e.g. tri-state and push-pull drivers) and analog cells (e.g. op-amps, A/D and D/A converters). Larger cells called macros are also commonly found in the library. These include, for example, full adders, shift registers, l-bit ALU's and decoders. Ideally, all cells should be technology independent and standardized in all design systems. But, due to the individual interests of the designers and manufacturers, such a library has yet to be realized.

Usually, once all the required cells have been specified, layout, simulation and mask generation are handled automatically by the CAD system and the prototype of the design can be obtained within several weeks or months depending on the chip complexity [24]. Thus, in

general, the design turnaround time of the semi-custom approach is faster than that of the fully custom approach due to the previously defined and characterized cells which allow faster layout and verification.

An unfortunate consequence, however, is that since the dimensions and I/O connections of all the individual cells are fixed, layouts using the semi-custom approach exhibit longer interconnection lines and lower packing density when compared to the fully custom approach. In addition, long lines and large sizes imply longer propagation delays and increased power requirements. Additional costs and time are required to update and maintain a complete standard cell library database since the predesigned cells and macros must keep up with the fast changing IC technology. Finally, although standard cell design uses predesigned library modules, it also requires a complete unique set of mask layouts delaying manufacturing turnaround time.

A gate-array (also known as uncommitted logic array, masterslice, cell array or universal array) consists of a prefabricated and fixed array of identical transistors or commonly used logic gates. These arrays of cells can be interconnected as required by appropriate customization of one or a few layers of metalization [26, 27]. In other words, the designer has only to specify an interconnection pattern to wire a sea of uncommitted transistors and/or gates arrays to form desired circuits. Therefore, the gate-array approach has the fastest turnaround time and lowest costs among the other custom IC designs since all the transistors and gates are made in mass production and it requires only a few mask layers to complete the chip design. In

addition, the regular characteristics of the gate-array approach allow most of the basic elements to be prechecked and the final testing is simplified.

But, like the semi-custom approach, the gate-array approach suffers from slow speed and poor chip area utilization due to long interconnection lines, large gate size and wasted (unused) gates. The large gate size is due to the requirement of more contacts on each gate for flexible I/O connections.

As a whole, the three approaches to custom IC design described in this section present tradeoffs among design complexity, design time, circuit size and performance. The fully custom approach provides a design with the best circuit performance and chip area utilization but suffers from the longest design-time and highest costs. The gate-array approach has fastest turnaround time and lowest costs but produces designs with slower speeds and larger chip areas with the semi-custom approach falling somewhere in between.

### 2.1.3 Silicon Compilation

Silicon compilation is defined as the process of translating a design description (behavioral or structural) into a geometric description (physical) [28, 29]. The behavioral description of a design is used to describe the relationship of the inputs and outputs in a common form such as timing diagrams or finite state machine descriptions. The structural design can be described in terms of nets (nodes) and components, where components can be decomposed into

primitive nets and devices such as transistors. The physical description of a design is a series of patterns on a set of masks, which may be organized in a hierarchy of geometrical descriptions. Therefore, a silicon compiler translates a high level language description of a circuit into layout information that allows an IC to be fabricated immediately [28, 29].

Current silicon compilers are broadly divided into "front-end" and "back-end" compilation processes [28]. The "front-end" process is the translation of a behavioral or functional description into a more precise intermediate description that is still implementation (technology) independent. The "back-end" process, which is implementation dependent, is the automatic generation of a chip layout from the intermediate description.

There are two major goals in the development of a good silicon compiler. The first is to overcome the drawbacks of fully custom, standard cell and gate-array approaches. That is, the intelligent software routines of the compiler should provide simple descriptions of the circuit behavior and the ability to manage design complexity while producing efficient layouts. Secondly, the same software routines should carry out logic and timing simulation to check overall function and performance. The compiler should check the layout against design rules and then generate the detailed silicon representation. Such a representation is generated in the Caltech Intermediate Form (CIF) [6] or Electronic Design Interchange Format (EDIF) [30] which are the prevalent formats for describing the IC layouts.

Like the standard cell approach, silicon compilation requires the database as well as software routines be kept up to date with IC fabrication technology. With this technique, the entire compilation process is transparent to the designer who has no direct control over the layout process. Therefore, in terms of chip area and performance, layouts designed by the compilation technique still tend to be less efficient than those done by handcrafted methods and in general are 10%-20% larger [31].

### 2.1.4 Hierarchical Design Methodology

Hierarchical design methods are considered as a means of managing the complexity of the VLSI design problem. Three systematic approaches to hierarchical systems design have been discussed in the literature [32]. They are the top-down and bottom-up approaches and schemes which combine the two.

Currently, top-down system design through silicon compilation is capable of producing a wide variety of VLSI circuits that are of market quality [28, 33]. This approach allows designers to work above the circuit element and layout levels. Once the behavioral and high-level architectural description of an integrated system are specified, a designer will be provided with physical layout, simulation, verification and documentation by the compiler. However, this generally implies bounds on the density of a structure because the designer has no direct control over the details below the circuit level.

In contrast to the top-down approach, bottom-up system design starts from the basic level of circuit layout [11]. Every circuit element (e.g. transistors or gates) within a circuit block or module is carefully designed, usually by trial-and-error, and placed so that the most efficient area-speed layout is obtained. However, as the number of circuit elements increases, the circuit complexity and thus the design time increase rapidly.

In practice a combination of the top-down and bottom-up approach is generally used. At one end, the complex system can be specified by high-level descriptions and by functional specifications from which lower level descriptions and ultimately parts of the layout will be compiled in an automatic or semiautomatic manner. At the other end, layout aided by graph theoretic techniques alleviates the problems of wasted chip area and long channel routing by closely clustering or tessellating modules. By combining both approaches, this design methodology provides an acceptably rapid, accurate development of VLSI systems with a reasonably small sacrifice of silicon and performance.

# 2.2 VLSI Technologies

Both bipolar junction transistor (BJT) and metal-oxide-semiconductor (MOS) IC technologies are used for the fabrication of VLSI circuits. Broadly, BJT technology is preferred for high speed digital applications and high gain, high bandwidth, low offset and low noise analog designs. MOS technology is favored for low power, high

complexity and high density digital designs. It is also most useful for high input impedance requirements and low power analog applications.

MOS technology is preferred over BJT technology for high performance, dynamic circuit implementation because the MOS transistor incorporates a near perfect input capacitor which permits input signals to be stored [26]. Inherently, MOS transistor structure is much simpler and smaller than the BJT structure. More essential, the scaling down of the device's surface dimension results in better time performance for MOS, but no corresponding change in BJT circuits. This is because the transit time in a MOS transistor is determined by the channel surface width whereas in a BJT it is proportional to the thickness of the base region instead of the base surface [6]. As a result, MOS technology has many advantages over BJT technology for digital VLSI applications requiring low power dissipation and high circuit packing density.

The two most widely used MOS technologies are n-channel MOS technology (NMOS) and complementary MOS technology (CMOS). Currently, CMOS tends to replace NMOS in high-density memory design due to the low standby power, high noise immunity, reliability and superior temperature characteristics of CMOS [34]. However, CMOS chips are generally 10%-20% larger than functionally identical NMOS chips [35]. Also, CMOS structures require one or two more mask layouts, which increase production costs and time. They also are more susceptible to encounter latchup problems when scaling down [36]. The latchup is caused by the extraneous currents in the gate channel which forward-bias the junction between the p-channel and n-channel devices. Pass transistor networks using NMOS have been found to have simplest topology, highest density

and best performance among MOS random logic designs [6, 37, 38].

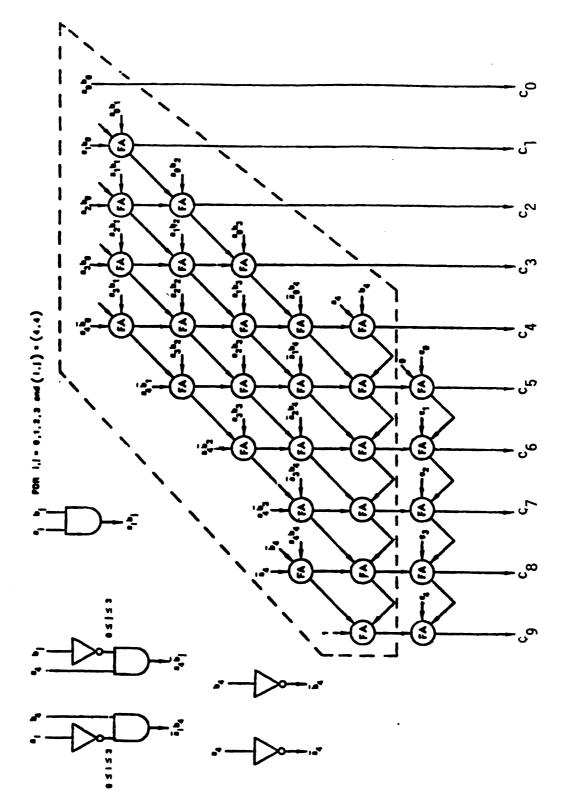

# 2.3 VLSI Systolic Array Structures

A promising outgrowth of VLSI capabilities is the prospect of designing high-speed dedicated computing structures using both parallel and pipelined processing concepts. These structures can be implemented on a single chip or a matched chip set. A number of VLSI systolic array algorithms and architectures have been proposed which show great promise in engineering problem applications such as signal and image processing, matrix arithmetic and graph theoretic algorithms [3-8].

A systolic array processor is a dedicated (non-programmable) computing subsystem having a one- or two-dimensional configuration of repeated processing elements (PE's) arranged in a parallel-pipeline fashion. The processor synchronously "pumps" data between levels of PE's performing part of an overall computation at each time step, thus the name "systolic". Latches, which are simple dynamic storage elements, are placed amid rows of PE's to provide synchronization and to assure that a regular flow of data is maintained.

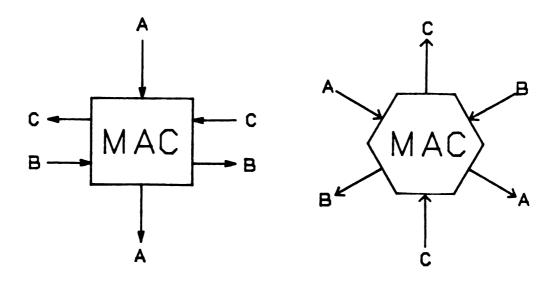

The majority PE commonly found inside many systolic array structures is the multiply-add cell (MAC), which is also known as the inner-product step processor. Two types of ideal geometries for MAC are shown in Figure 2.1 [3, 6]. Both types of MAC's perform the operation C=AB+C and transfer A=A and B=B. However, the type-1 MAC, shown on the left, is used for matrix-vector multiplication and backward substitution of triangular matrix system, whereas a type-2 MAC is used for matrix

Figure 2.1 Two types of MAC's.

inversion, multiplication, triangulation and L-U decomposition. Thus, one-dimensional (1-D) or two-dimensional (2-D) systolic array structures can be configurated by using these MAC's depending on the application.

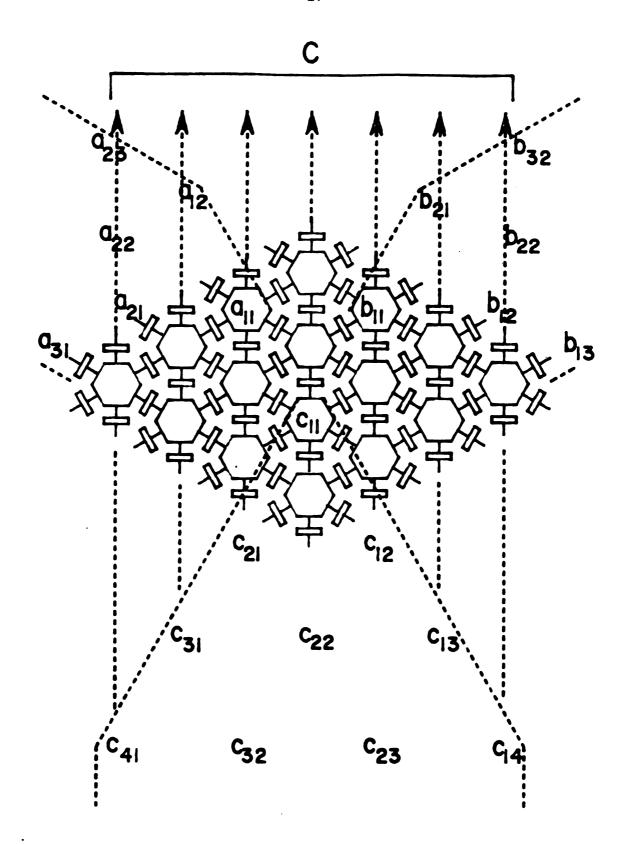

For example, consider a 2-D systolic array structure used for band matrix multiplication [3, 6]. The multiplication of two NxN matrices  $\underline{A}$  and  $\underline{B}$  with bandwidth of  $w_1=p_1+q_1-1$  and  $w_2=p_2+q_2-1$ , respectively, can be represented by

In this example, both  $w_1$  and  $w_2$  are equal to 4. Figure 2.2 shows the corresponding mesh-connected network of type-2 MAC's with the appropriate intermediate latches depicted by rectangular blocks. Elements of matrices  $\underline{A}$  and  $\underline{B}$  are pumped into the array network synchronously until all elements of  $\underline{C}$  are obtained. In general, the numbers of MAC's,  $N_{MAC}$ , and time steps,  $T_{MAC}$ , required for the multiplication of any two NxN matrices of bandwidth  $w_1$  and  $w_2$  are expressed as follows [3, 6],

$$N_{MAC} = W_1 W_2$$

(2-2)

and

$$T_{MAC} = 3N + \min\{w_1, w_2\}.$$

(2-3)

### 2.4 Design for Testability

The testability of a digital network is directly related to the difficulty of controlling and observing the logical values of internal nodes from external circuit ports [39, 40]. Thus, controllability and observability are the key concepts in the design and implementation of testability. In addition, accessibility, which is the measure of the ease of controllability and observability, is also important in testing complex VLSI circuits. The two basic approaches prevalent today in VLSI design for testability are the ad hoc and structured approaches [39].

The ad hoc approaches use techniques which can be applied to a given product, but are not directed at solving the general problem. Examples of these techniques, some of which evolved from MSI and LSI techniques, are partitioning, test points and signature analysis [39].

Figure 2.2 Mesh-connected MAC's for matrix multiplication.

Most structured testing approaches are built upon the concept that if the values in all the latches can be controlled and observed in a straightforward operation, then the test generation and simulation of a sequential network can be reduced to that of doing test generation and fault simulation for a combinational logic network. A control signal can switch the memory elements from their normal mode of operation to a mode that makes them controllable and observable. Techniques that use the structured approach are level-sensitive scan design (LSSD), scan path, scan/set logic, random-access scan, self-testing and built-in tests [39]. Among these, LSSD [13] and scan path [14] techniques have been the most popular approaches to VLSI testing.

In LSSD structures the memory elements or latches are threaded together to form a serial-in/serial-out shift register. The shift register latches (SRL's) are controlled by shift clocks for loading and unloading and by system clocks for latching logic values present at their data inputs. In testing the logic networks, test inputs are applied through primary inputs as well as SRL's through a "scan-in" operation. Outputs of the networks are observable at both primary outputs and SRL's through a "scan-out" operation.

The scan path technique has the same objectives as the LSSD approach. The memory elements used in the scan path approach are raceless D-type flip-flops. The scan-in and scan-out operations are controlled by the master/slave operations of the flip-flops. With proper adjustment to the delays of the flip-flops, race conditions can be avoided [14]. Therefore, only a single system clock is required in this technique.

In general, all designs for testing require additional hardware and I/O pinouts so as to achieve controllability and observability. Therefore, accessibility tends to trade off with hardware size and/or performance.

Design for testability of systolic arrays and other structures having similar regular and pipelined characteristics are relatively straightforward in comparison with other VLSI circuits. The functional and logic tests of these structures are directly related to algorithm implementation. Therefore, once the systolic or other similar algorithm has been correctly translated and implemented into a hardware algorithm, the remaining test required is just the physical testing of the chip. In addition, systolic structures use dynamic latches for pipelining and each pipelined segment is composed of combinational logic. Thus, scan design used in LSSD and scan path techniques can be applied to these structures without a significant increase in hardware or signal delay time.

# 2.5 Y-Chart Representation of VLSI Design Methodologies

A tripartite representation on a Y-chart has been used to define VLSI design methodologies [8, 41]. A Y-chart is a descriptive model using three axes. In general designs, the three axes of the Y-chart are associated with functional or behavioral representation (e.g., a Boolean expression), structural representation (e.g., the functional realization of the Boolean expression), and geometrical representation (i.e., the

physical implementation of a design) [41]. In the design of systolic algorithms, the three axes are related to algorithm representation (specified forms or levels of systolic algorithm), algorithm model (abstraction of the features of the algorithm) and architecture specification (physical description of the systolic array) [8].

Alternative Y-charts will be minimally related to each other if the axes among these Y-charts are not consistent in representation. However, all Y-charts utilize directed or feedback arcs to represent the transformations on the same axis or among the axes. The means for these transformations vary with the design methodologies. The means can be CAD tools, sets of parameters or even a direct mapping or transfer.

Design representations using Y-charts have many advantageous features. First, the three-axes as well as arcs are all user-defined so that the Y-chart can be used to clarify the explanation of a design approach. Secondly, the tradeoffs of the different design methodologies can be initially assessed by comparing the information gleaned from the Y-chart. (Of course, the axes of the compared Y-charts must be consistently defined.) Thirdly, Y-charts can be further subdivided into more detailed Y-charts such that informative details can be additionally depicted. This may be considered as a "hierarchical" Y-chart representation of VLSI designs.

As an example, a modified Y-chart describing the design of several VLSI structures mentioned in this chapter is shown in Figure 2.3 [8, 41]. In this Y-chart, the axis of STRUCTURE REPRESENTATION broadly shows two major types, random and regular, VLSI-based structures. Six typical random and regular structures are shown on this axis but,

Figure 2.3 A modified Y-chart representation of typical VLSI-based design [8, 41].

obviously, VLSI-based structures are not restricted to these six. This axis can also indicate the degree of either regularity or non-regularity of the structures. Regularity increases toward the origin while non-regularity or randomness increases with the direction of the axis. Note that the scales on this axis are not necessary in equal proportion.

The methodologies of custom design, silicon compilation technique and hierarchical design are depicted in the axis of DESIGN MODEL. The custom design model includes all other traditional design methodologies such as symbolic layout approaches, building-block techniques, etc. [17]. Design techniques must not be constrained to a single design model; therefore, a mixed design model can also be described. For example, silicon compilation techniques can also be used in some of the procedures in the hierarchical design model [29, 33].

The third axis for LAYOUT SPECIFICATION represents IC layouts in order of increasing complexity. The cell array approaches such as the gate-array and logic array, have the least complex layout while the fully custom layout has the highest complexity.

Any directed or self-looped arcs denoting a transformation through certain means such as simulators, compilers, sets of parameters, etc., can be placed on this Y-chart. Finally, a detailed Y-chart can be further developed for a particular structure or design model. For example, a detailed Y-chart can be developed for the description of the design of regular structures using a custom design approach.

#### CHAPTER III

#### BOTTOM-UP APPROACH

An overview of the bottom-up approach to the hierarchical design of systolic array structures is shown in Figure 3.1. The layout design starts from a selected design entry-point according to a set of desired parameters such as circuit complexity, size and performance. Design pathways can then traverse among the module levels of transistor, gate, functional device or processing element (PE) as desired. Finally, a "target" structure can be formed by modular tessellation.

Tradeoffs existing among the design hierarchy have yet to be fully assessed and compared numerically. In order to do so, the bottom-up approach presented here involves the layout and simulation of different target systolic array structures designed through different hierarchical design entry-points and paths. The thread of this hierarchy in the bottom-up approach is further shown in Figure 3.2.

The primary target systolic structure is the multiply-add cell (MAC), which is a commonly used and often the majority PE inside systolic array structures. Examples of systolic structures in which the MAC is the major component include arrays for matrix triangulation, multiplication and inversion. As an example in hierarchical design of layout, a MAC module considered at the PE level can be designed starting from transistor, gate or functional device level. Likewise, a full

Figure 3.1 An overview of the bottom-up approach.

Figure 3.2 Design hierarchy in the bottom-up approach.

adder (FA) module at the functional device level can be built of either gate modules or transistor modules.

As an initial approach to study the tradeoff among the various design levels, modules at several levels is designed and simulated using standard NMOS design rules. The choice of these design rules is due mainly to the widespread use and knowledge base of NMOS technology [6, 27, 37]. Other factors making NMOS attractive include high circuitry density, richness of available circuit functions and simple topological properties of circuit layout and simulation.

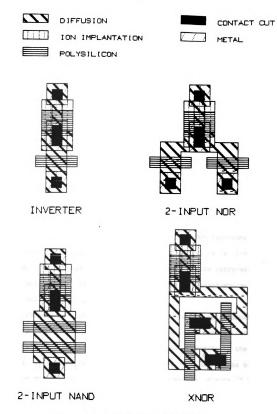

### 3.1 Transistor and Gate Level Design

The boundary of a circuit module at any level is simply defined as the rectangle which contains the complete planar layout of the functional circuit. Therefore, the area of a circuit module is simply the product of the length and width of the boundary of the module. Figure 3.3 illustrates the cell boundary of a depletion mode (pull-up) and an enhancement mode (pull-down) transistor modules. Figure 3.4 shows the four typical gate-level modules of inverter, 2-input NOR, 2-input NAND and XNOR. Both of these figures represent standard NMOS design [6, 27, 37].

In addition, due to the assumption of module tessellation, modification of predefined lower level modules is not considered when they are used to form higher level modules or circuits. Otherwise, there will be an increase in design complexity and design-time and the design parameters cannot be generalized. As an example, consider a

Figure 3.3 Cell boundary of two transistor modules.

gate-level FA which are tessellated by using a 2-input NAND gate as shown in Figure 3.4. During the tessellation, the pull-up and pull-down transistors inside the NAND gate can be shifted, rotated or/and reflected provided that all the transistors stay within the predefined gate boundary. Otherwise, the FA is considered to be a transistor-level FA ("X.FA") instead of a pure gate-level FA ("G.FA"). This is because the NAND gate is actually broken down into transistor modules which implies an increase in the number of modules requiring placement and lines requiring routing.

Transistor modules and gate level modules are defined and then "programmed", via a compilation technique, into a VLSI design oriented CAD system in order to establish a flexible cell library. Then, the

Figure 3.4 Typical gate-level modules.

layout of any transistor (pull-up, pull-down) or gate (NOR, NAND, XNOR, etc.) module can be generated automatically once the required specifications of the module, such as size, pull-up to pull-down transistor ratio or I/O and geometrical orientation, have been defined. Therefore, high-level modules can be designed by tessellating the predefined lower-level transistor modules or gate modules.

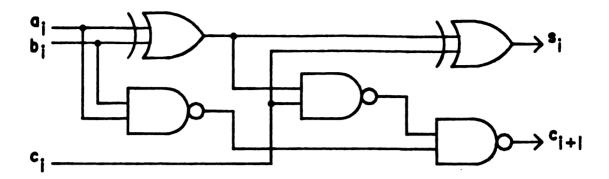

#### 3.2 Functional Device Level Design

Common circuits that can be considered as functional device modules include the half adder, full adder, comparator, complementer and counter cells. In general, the functional device module is composed of a certain number of transistors or gates and is the majority device module inside the higher level PE module. The most common functional device module found inside regular VLSI computing structures is a 1-bit full adder (FA). High speed arithmetic circuits such as the carry-save adder and fast multipliers, such as the Braun array and Baugh-Wooley array, are also built primarily of FA's [42, 43].

The FA adds two binary digits  $a_i$  and  $b_i$ , and a carry-input  $c_i$  to produce a sum-output  $s_i$  and a carry-output  $c_{i+1}$ . Conventionally, the implementation of the 1-bit binary FA module is according to the Boolean equations  $s_i = a_i \oplus b_i \oplus c_i$  and  $c_{i+1} = (a_i \wedge b_i) \vee (b_i \wedge c_i) \vee (a_i \wedge c_i)$ . The schematic logic diagram of this implementation is shown in Figure 3.5. The reasons for choosing this implementation are summarized as follows:

1. It contains various discrete and conventional gates—such that transistor and gate modules can be easily distinguished.

Figure 3.5 Logic diagram for the implementation of FA.

- Its simple interconnection and small number of fan-ins and fan-outs per gate allow flexible layout design, predictable circuit behavior, straightforward circuit simulation, and speed calculation.

- 3. It is not particularly biased against or toward any IC technology. (Note that NMOS is biased to NOR while CMOS and TTL (Transistor-Transistor Logic) are biased to NAND [26, 27].)

In designing an FA as a target structure, there are three distinct design paths as noted in Figure 3.2. Arranged in decreasing order of design complexity and circuit performance, they are "X.FA", "G.FA" and "FA", where 'X', 'G', and 'FA' represent the transistor, gate and functional device module level, respectively, and '.' denotes the design path between two levels. The terms of "functional device module level" and "FA module level" will be used interchangeably since the majority functional device is the FA in this research. Likewise, "PE level" and "MAC level" will be interchangeable because the majority PE is the MAC.

Therefore, "X.FA" represents a transistor-level FA module which is designed via the pathway of "entry point", "transistor module" and

"functional device module" as shown in Figure 3.2. Using only the transistor modules, this FA module is carefully crafted according to the logic diagram shown in Figure 3.5. In order to utilize the standard NMOS gates as shown in Figure 3.4, the XOR gate in Figure 3.5 is realized by an XNOR concatenated with an inverter as shown in Figure 3.6.

Since the layout positions of global I/O can affect overall module size and speed, different layouts of the FA with different I/O orientations are generated and compared. The I/O orientation is determined by the direction of data flow such that the module is best fit for tessellation. Finally, a preferred "X.FA", which is best in performance and chip area utilization, will be used as the building blocks for higher level modules.

Likewise, "G.FA" is a gate-level FA module designed through the path of "entry point", "gate module" and "functional device module" again as illustrated in Figure 3.2. This module is designed by placing gate modules only and routing the interconnection lines for I/O, power

Figure 3.6 Alternate version of Figure 3.5.

and ground. In the same manner as designing the "X.FA", layouts of "G.FA" with different global I/O positions are obtained and compared. Thus, "G.FA" modules heuristically optimal in both speed and area are obtained.

"FA", an functional device-level FA module, requires the least design time, thus representing the FA module with lowest design complexity. This module, mimicking a standard FA cell stored in the cell library, can be extracted and directly placed for tessellation. The actual design of this FA module uses the idea of the gate-array approach as discussed in Section 2.1.2. That is, the gates required to form an FA are simply packed as close as possible together in an array form and then I/O and power/GND lines are connected directly. Therefore, this design is completed in the shortest time compared to the other target FA's.

Once the three major types of FA's ("X.FA", "G.FA" and "FA") designed according to the above criteria have been obtained, they become part of the database of the CAD system as FA cells. Although the Computervision CADD 2/VLSI design system is used as a design aid in this work, any other basic CAD system or even paper and pencil can be used instead. This is because the final results and comparison will not be expressed in terms of absolute design time such as CPU seconds or man-hours but rather in relative ratios in terms of the number of modules or density of the modules. What's more, none of the basic layout designs utilized any placement or routing algorithms because of the assumed properties of regularity and local connectivity. As a result, these designs are machine independent.

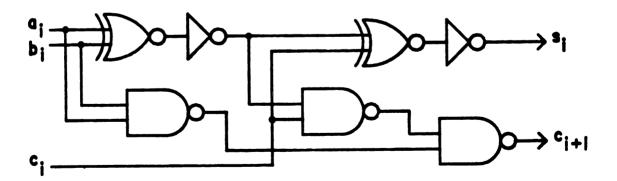

### 3.3 PE Level Design

The primary target structure in the design hierarchy is the multiply-add cell (MAC), which is the majority PE found in many systolic structures. The implementation of a MAC is based on the Baugh-Wooley array multiplier which allows fast and direct two's complement array multiplication [9, 42]. In addition, the Baugh-Wooley array is constructed entirely from the conventional 1-bit FA shown in Figure 3.5. For illustration, Figure 3.7 shows a 5-bit by 5-bit MAC which is merely a Baugh-Wooley array multiplier (enclosed by dotted lines) with an extra row of FA's at its bottom edge.

The design complexity and final performance of a MAC are again quite "dependent on the design entry-point and pathway. As shown in Figure 3.2, five distinct MAC's of different complexity corresponding to five design paths of mixed levels are possible. They are the "X.MAC", "X.FA.MAC", "G.MAC", "G.FA.MAC" and "FA.MAC". For example, "X.MAC" is a transistor-level MAC which is laid out using only transistor modules and "FA.MAC" is tessellated only by "FA" modules. Obviously, the design of a "FA.MAC" is less complex than that of "X.MAC" simply because the former is built using larger blocks without any concern given to details inside each block while the latter one is crafted from basic transistor modules. However, the chip area and propagation time of the "FA.MAC" are expected to be greater than that of "X.MAC" due to the relatively smaller interstitial space and shorter signal path inside the "X.MAC".

Figure 3.7 Logic diagram of a 5-by-5 Baugh-Wooley based MAC [9, 42].

Among the five different MAC's, "X.MAC", "G.MAC" and "FA.MAC" represent the transistor-level MAC, gate-level MAC and FA-level MAC, respectively. However, closer inspection of Figure 3.2 reveals two points-of-view with respect to the design entry-point and target-point as observed for "X.FA.MAC" and "G.FA.MAC". From the standpoint of design entry-point, or a straight bottom-up approach along the arrows shown in the figure, "X.FA.MAC" and "G.FA.MAC" are considered to be transistor-level MAC and gate-level MAC, respectively. However, from the viewpoint of design target-point (PE module), or a top-down approach reversely following the arrows shown in the figure, both "X.FA.MAC" and "G.FA.MAC" can be alternately considered as FA-level MAC's. In addition to these two points-of-view, both "X.FA.MAC" and "G.FA.MAC" can be simply treated as mixed-level MAC's. Therefore, the defined entry-level of "X.FA.MAC" and "G.FA.MAC" depends on the point-of-view of the observer.

As a whole, five independent MAC's corresponding to five distinct design paths of different complexity are constructed. They are stored in the CAD system and will be used to form the final target VLSI systolic array structures whose majority PE is an MAC.

#### 3.4 Systolic Arrays for Matrix Multiplication

A VLSI systolic array structure having the MAC as its majority PE can be designed directly by tessellating the required MAC's and other minority modules. As a testbed for benchmarking, the matrix-matrix

multiplier, shown in Figure 2.2 in Section 2.3, is considered. By tessellating arrays of any library MAC designed from the various combinations of module levels and the external latches, a matrix-matrix multiplier of any matrix dimension and word size can be constructed. Of course, it has been assumed that there is no limitation on single chip size. If such limitation exists, a top-down approach such as algorithm decomposition, must be considered. The top-down approach will be discussed in Chapter 5.

The rhombic shape of the overall connected network illustrated in Figure 2.2 is impractical for actual layout. Therefore, the layout of the network is "sheared" to a rectangular shape and the hex-shaped MAC's are changed to rectangular MAC's for better chip area utilization. This modified network is shown in Figure 3.8. All the small rectangular blocks shown in this figure are arrays of identical latches for data synchronization. The number of latches in each block is equal to the word size (the number of bits per word). These latches, however, are comparatively much smaller than the MAC's and thus have an insignificant effect on overall area and speed. The design of these latches will be presented in next section. Finally, five different designs of a VLSI matrix-matrix array multiplier are obtained with respect to the three distinct entry-points and five different design paths as shown in Figure 3.2. Specifically, "X.MAC.VLSI", "X.FA.MAC.VLSI", they are "G.MAC.VLSI", "G.FA.MAC.VLSI" and "FA.MAC.VLSI".

With all the target structures discussed in this chapter, the tradeoffs among chip area, circuit performance and design complexity of the proposed design hierarchy can be explored in next chapter. In

Figure 3.8 Array network for C=AxB shown in Figure 2.2.

summary, utilizing the bottom-up approach, the target structures designed previously are 1-bit full adder (FA), multiply-add cell (MAC) and VLSI matrix-matrix multiplier (VLSI) as shown in Figure 3.9.

| Ent<br>poi | _   | FA   | Та | •           | stru<br>MAC | ctures | VLSI          |

|------------|-----|------|----|-------------|-------------|--------|---------------|

|            |     |      | >  | <b>x</b> .1 | MAC         | >      | X.MAC.VLSI    |

|            | x>  | X.FA | >  | X.FA.       | MAC         | >      | X.FA.MAC.VLSI |

|            |     |      | >  | G.I         | MAC         | >      | G.MAC.VLSI    |

|            | G>  | G.FA | >  | G.FA.       | MAC         | >      | G.FA.MAC.VLSI |

| F          | 'A> | FA - | >  | FA.         | MAC         | >      | FA.MAC.VLSI   |

Figure 3.9 Design entry-point and pathway of various target structures.

# 3.5 Latch Design for Systolic Array Structures

Dynamic registers or latches are required for high speed, synchronous processor chip designs, especially using VLSI [6, 13, 39]. Therefore, dynamic latches using a feedback path as shown in Figure 3.10 are utilized in the design of the systolic array structure presented in this work [6]. These latches are designed as shown in the figure so that they can be directly tessellated either vertically or horizontally amid the PE's. An individual latch, enclosed by the dotted lines in the figure, uses a two-phase nonoverlapping clock to load  $(\phi_1)$  and refresh  $(\phi_2)$  the input data. As mentioned in the previous section, the number

Figure 3.10 Dynamic latches.

of individual latches inside each row or column of an array is dependent on the word size.

Scan design for testability of systolic arrays and other structures having similar regular and pipelined characteristics uses special latches to facilitate the scan-in and scan-out operation. Therefore, the latches shown in Figure 3.10 are modified in order to insure a proper scanning operation. These modified latches for scan design are shown in Figure 3.11. In this figure, the signals of  $\phi_1$  and  $\phi_1$ ' are exclusive to each another during normal and scanning operations. During a scan-in or scan-out operation,  $\phi_1$ ' and  $\phi_2$  are used to load the testing vectors through the line marked S-IN or unload the results through S-OUT while  $\phi_1$  is disabled. In normal operation,  $\phi_1$  and  $\phi_2$  provide the

Figure 3.11 Dynamic latches with scan design.

synchronism for the data pumping through the computing arrays while  $\phi_1$ ' is off.

The obvious difference between the latches with and without scan design is the addition of an extra signal line,  $\phi_1$ , and an extra pass transistor per latch. Thus, the increase in overall chip area and propagation time due to the additional scanning function is insignificant. What's more, the effect on the design complexity of a latch is so small that the overall increase in the complexity of the systolic arrays is negligible.

#### CHAPTER IV

#### TRADEOFF PARAMETERS EVALUATION AND JUSTIFICATION

The main purpose of the bottom-up approach in this work is to study the tradeoff of design complexity versus chip area and propagation time among the various design paths. This chapter first presents the measures for chip area and propagation time and design complexity. Then, the tradeoffs of the design complexity versus area-time based on a generalized layout model are developed.

The design complexity can be expressed by actual design time in terms of CPU seconds or man-hours [44, 45]. Unfortunately, these measures of design time are undesirable due to their dependence on the CAD or CAE system or the designer's expertise. Alternative approaches to parameterization of the design complexity will be discussed and justified in this chapter.

The design of input/output (I/O) circuits for the overall systolic array structure has been neglected in the bottom-up approach by assuming the area of I/O circuits is small and potential I/O bottlenecks are avoided. However, it is noted that if certain conditions exist, such as the domination of I/O time over the pipeline segment time of PE, an I/O bottleneck may be encountered which will eventually degrade the overall performance of the circuit [5, 9]. This I/O problem will be further addressed in the top-down design approach presented in Chapter 5.

# 4.1 Chip Area and Propagation Time Computation

Since the layout of any higher level module is done solely by tessellation of lower level modules which include communication lines, module areas are determined simply by the sum of the areas of all required lower level modules. In addition, the layout of each module uses standard NMOS design rules as per the technique of Mead and Conway [6]. Thus, the total chip area of a structure is the product of the width and length measured from the final layout of the structure in terms of the minimum lithographic linewidth,  $\lambda$ .

The fundamental limit on the switching speed of a MOSFET (MOS Field-Effect Transistor) is the transit time of a carrier between source and drain. In practical circuits, however, the switching speed is limited by the capacitance charge and discharge times. The capacitance of main concern is the effective load capacitance of an active gate, C<sub>L</sub>, which is due to the capacitance of the active gate and the input capacitance of the next gate(s), plus intercommunication lines, parasitic, fringing and Miller-effect capacitance [6, 12, 26].

As an example, Figure 4.1 shows an NMOS  $N_1$ -input NOR gate driving  $N_0$  identical outputs. By assuming one input of this gate is switched at a given time, the total effective load capacitance is expressed as

$$C_{L} = C_{\text{stray}} + (N_{i}+1)C_{\text{GDe}} + N_{i}C_{\text{DSe}} + C_{\text{GDd}}$$

$$+ C_{\text{DSd}} + N_{o}(C_{\text{GSe}} + 2C_{\text{GDe}}), \qquad (4-1)$$

where G, D, S, e and d refer to gate, drain, source, enhancement mode

Figure 4.1 An N,-input NMOS NOR gate driving No identical outputs [26].