## This is to certify that the

## dissertation entitled

# A MODULAR DISTRIBUTED MICROCOMPUTER SYSTEM FOR SCIENTIFIC INSTRUMENTATION

presented by

Bruce Hewitt Newcome

has been accepted towards fulfillment of the requirements for

Ph.D. degree in <u>Chemistry</u>

Major professor

MSU is an Affirmative Action/Equal Opportunity Institution

Date Feb. 5, 1984

0-12771

RETURNING MATERIALS:

Place in book drop to remove this checkout from your record. FINES will be charged if book is returned after the date stamped below.

## A MODULAR DISTRIBUTED MICROCOMPUTER SYSTEM FOR SCIENTIFIC INSTRUMENTATION

bу

Bruce Hewitt Newcome

## A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirments

for the degree of

DOCTOR OF PHILOSOPHY

Department of Chemistry

1983

#### ABSTRACT

## A MODULAR DISTRIBUTED MICROCOMPUTER SYSTEM FOR SCIENTIFIC INSTRUMENTATION

bУ

#### Bruce Hewitt Newcome

A hierircal computer system has been designed to meet the needs of chemical instrumentation. This system consists of a central minicomputer that is connected to several dedicated microcomputer systems. These microprocessor systems perform instrument control and data acquisition and then transfer the data to the host system for further data analysis. This separation of tasks allows each computer system to be specifically tailored to the tasks that it performs.

A modular microprocessor system was designed to permit the easy implementation and adaptation of the computer system to the needs of the instrument. A system is assembled from a set of standard single function modules which provided the needed functions for the control system by mounting them on a dual-bus board. This board provides the local bus to interconnect the different modules in the system. Examples of the systems that have been implemented are a laser lab data acquisition system, a diode array

spectrophotometer system, and a time dispersed magnetic sector mass spectrometer.

A distributed processing system was developed for instrumentation problems that require more processing power than a single microprocessor can provide. The use of several distributed microprocessors instead of a single larger processor has advantages in the areas of speed, non-interference, and flexibility. Dedicated interprocessor hardware was designed to implement the different modes of interprocessor communication. These modes of communication are block data transfer, task assignment, parameter transfer, and task coordination.

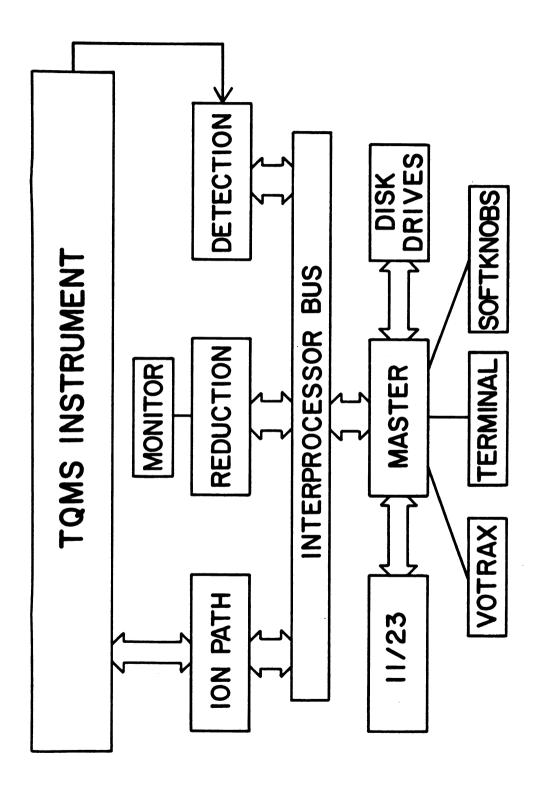

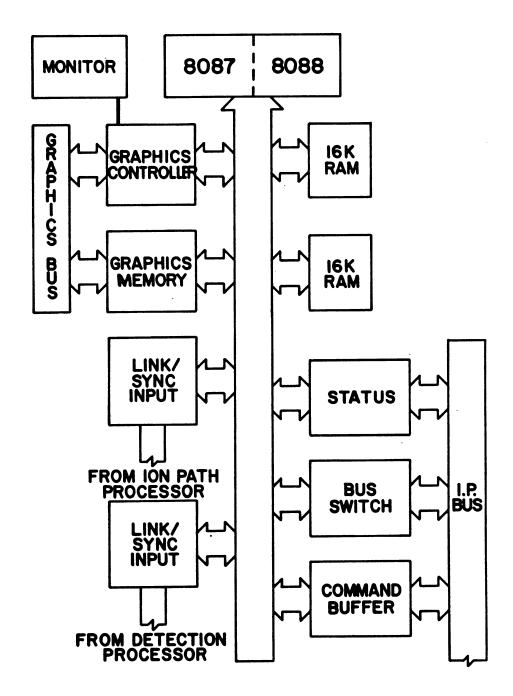

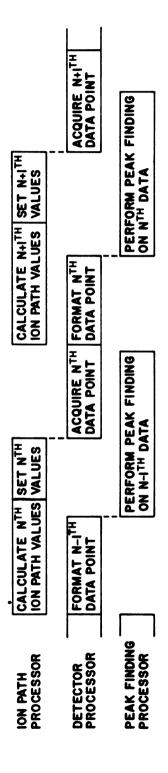

A four processor system was built to control a Triple Quadrupole Mass Spectrometer. The four processors in the system are a master processor, an ion path processor, a detection processor, and a reduction processor. The master processor handles the mass storage, communications with the operator, and controls the other three slave processors. The ion path processor controls the potentials of all of the elements in the ion path. The detection processor performs the data acquisition and the reduction processor performs peak finding in real time on the acquired data. This system is a significant improvement over a similar single processor system.

To that old curse

" May you live in interesting times."

## ACKNOWLEDGMENTS

I would like to thank Professor Christie Enke for his help and guidance. I am also indebted to him for the support and freedom that he provided for this work. I also thank Professor Stanley Crouch and the other members of my committee, Professor George Leroi and Professor David Fisher, for their contributions. I am also indebted to the many members of the Enke and Crouch groups for their friendship and assistance. The financial support of the Office of Naval Research and Extranuclear, inc. is gratefully acknowledged.

I would like to thank my parents for their guidance and support and Professor H. V. Malmstadt and Professor Jim Avery for their initial assistance and direction. I would like to acknowledge the help of the many members of the Chemistry Department Staff that assisted in this work.

Finally I acknowledge the help and friendship of my Co-conspirator Carl Myerholtz without whom this would not have been possible. For truly the whole is greater than the sum of the parts.

## TABLE OF CONTENTS

| LIST OF TABLES                                | Vi i |

|-----------------------------------------------|------|

| LIST OF FIGURES                               | viii |

| CHAPTER 1 -INTRODUCTION                       | 1    |

| COMPUTER IN CHEMICAL ANALYSES                 | 1    |

| SAMPLE PREPARATION                            | 1    |

| INTERACTION BETWEEN THE SAMPLE AND TRANSDUCER | 2    |

| RECORDING THE OUTPUT OF THE TRANSDUCER        | 3    |

| FROCESSING AND REDUCTION OF DATA              | 5    |

| HISTORICAL FERSFECTIVE                        | 5    |

| SEFARATION INTO ANALYSIS AND CONTROL SYSTEMS  | 8    |

| COMPUTER NETWORKS                             | 12   |

| LABORATORY MICROCOMPUTER SYSTEM DESIGN GOALS  | 13   |

| SUMMARY                                       | 16   |

| CHAPTER 2 - THE SINGLE MICROCOMPUTER SYSTEM   | 18   |

| USES OF THE SECOND BUS                        | 19   |

| THE BACKPLANE                                 | 22   |

| LOCAL BUS DEFINITION                          | 24   |

| STANDARD MODULES                              | 27   |

| PROCESSOR MODULES                             | 29   |

| MEMORY MODULES                                | 30   |

| SYSTEM SUPPORT MODULES                                      | 31              |

|-------------------------------------------------------------|-----------------|

| MASS STORAGE INTERFACE MODULES                              | 33              |

| LSI PERIPHERAL MODULES                                      | 33              |

| ANALOG FUNCTION MODULES                                     | 34              |

| MISC. MODULES                                               | 36              |

| DUAL HEIGHT MODULES                                         | 36              |

| SUMMARY                                                     | 37              |

|                                                             |                 |

| CHAPTER 3 - EXAMPLE MICROCOMPUTER SYSTEMS                   | 39              |

| LASER LAB DATA ACQUISITION SYSTEM                           | 39              |

| LINEAR DIODE ARRAY SPECTROMETER SYSTEM                      | 44              |

| MASS SPECTROMETER CONTROL SYSTEM                            | 48              |

| SUMMARY                                                     | 52              |

| CHAPTER 4 - DISTRIBUTED PROCESSING SYSTEMS                  | <b>5</b> 7      |

|                                                             |                 |

| MULTIPLE PROCESSOR SYSTEMS                                  | 56              |

| TASK COUPLING IN DISTRIBUTED SYSTEMS                        | 57              |

| TASK PARTITIONING                                           | 60              |

| INTERPROCESSOR TOPOLOGY                                     | 62              |

| INTERPROCESSOR COMMUNICATION MODES                          | 65              |

| DISTRIBUTED PROCESSOR DESIGN GOALS                          | 66              |

|                                                             |                 |

|                                                             |                 |

| CHAPTER 5 - INTERPROCESSOR HARDWARE                         | 72              |

| CHAPTER 5 - INTERPROCESSOR HARDWARE  THE INTERPROCESSOR BUS |                 |

|                                                             | 72              |

| THE INTERPROCESSOR BUS                                      | <b>72</b><br>72 |

| PERFORMANCE                             | 100 |

|-----------------------------------------|-----|

| CHAPTER 6 - TQMS CONTROL SYSTEM         | 102 |

| The TRIPLE QUADRUPOLE MASS SPECTROMETER | 102 |

| REQUIREMENTS FOR A TOMS CONTROL SYSTEM  | 107 |

| THE TOMS CONTROL SYSTEM                 | 110 |

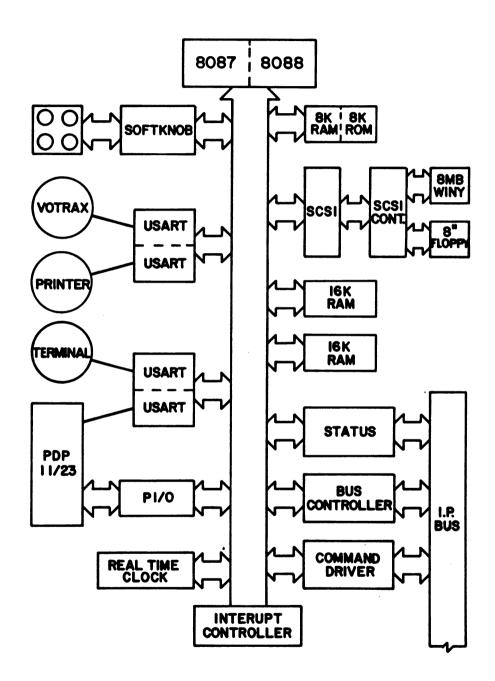

| MASTER PROCESSOR                        | 112 |

| ION PATH PROCESSOR                      | 115 |

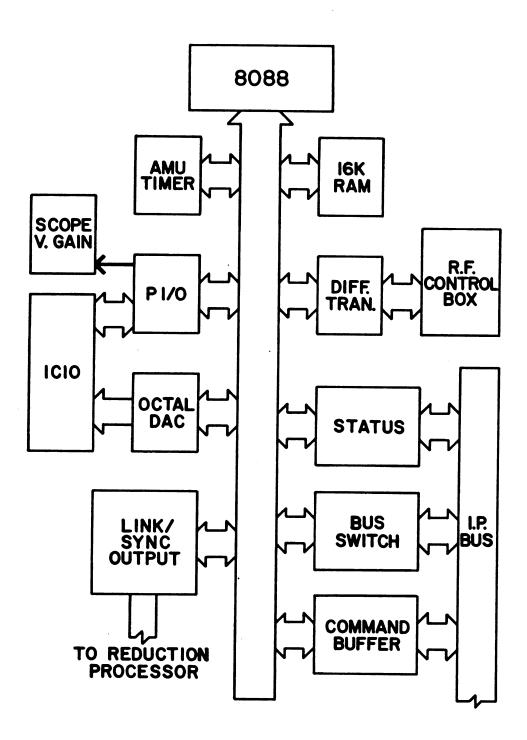

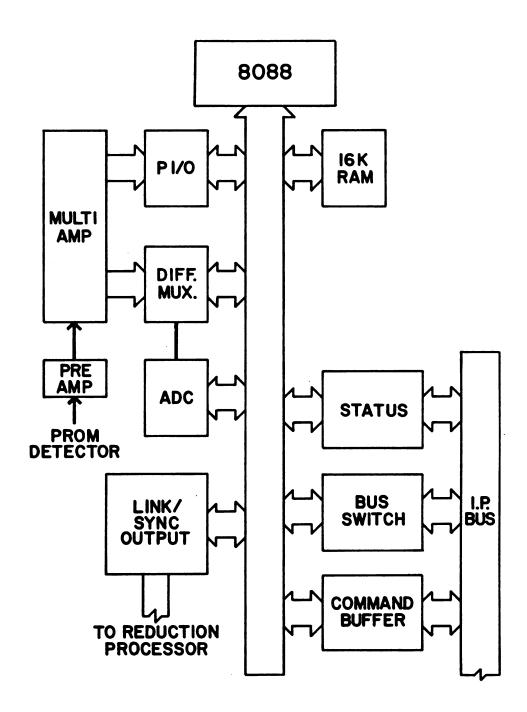

| DETECTION PROCESSOR                     | 118 |

| REDUCTION PROCESSOR                     | 121 |

| DATA ACQUISITION                        | 124 |

| USER INTERFACE                          | 126 |

| ENHANCED PERFORMANCE AND CAPABILITIES   | 128 |

| CHAPTER 7 - SOFTWARE                    | 133 |

| FORTH LANGUAGE                          | 133 |

| DISTRIBUTED FORTH                       | 135 |

| TOMS SOFTWARE                           | 137 |

| SUMMARY                                 | 138 |

|                                         |     |

| CHAPTER 8 - FUTURE DEVELOPMENTS         | 140 |

| IDEAS FOR THE SINGLE PROCESSOR SYSTEM   | 141 |

| INTERPROCESSOR HARDWARE MODULES         | 143 |

| TOMS CONTROL SYSTEM                     | 145 |

| PEEEDENCES                              | 147 |

## LIST OF TABLES

| TABLE | P.                                               | AGE |

|-------|--------------------------------------------------|-----|

| 1-1   | The Design Goals for the Microprocessor System . | 15  |

| 2-1   | A List of Standard Modules                       | 29  |

| 4-1   | Advantages of Distributed Processing Systems     | 56  |

| 4-2   | Distributed Microprocessor System Design Goals . | 67  |

| 5-1   | Finout of the Interprocessor Bus Cable           | 75  |

| 6-1   | Devices in the TQMS to be Controlled             | 109 |

| 6-2   | Component Modules of the Master Processor        | 114 |

| 6-3   | Modules in the Ion Fath Processor                | 117 |

| 6-4   | Modules in the Detection Processor               | 120 |

| 6-5   | Modules in the Reduction Processor               | 123 |

| 6-6   | Scanning Rates for the TOMS Control System       | 129 |

| 7-1   | Selected TQMS Control System Commands            | 138 |

## LIST OF FIGURES

| FIGURE | i                                                | PAGE |

|--------|--------------------------------------------------|------|

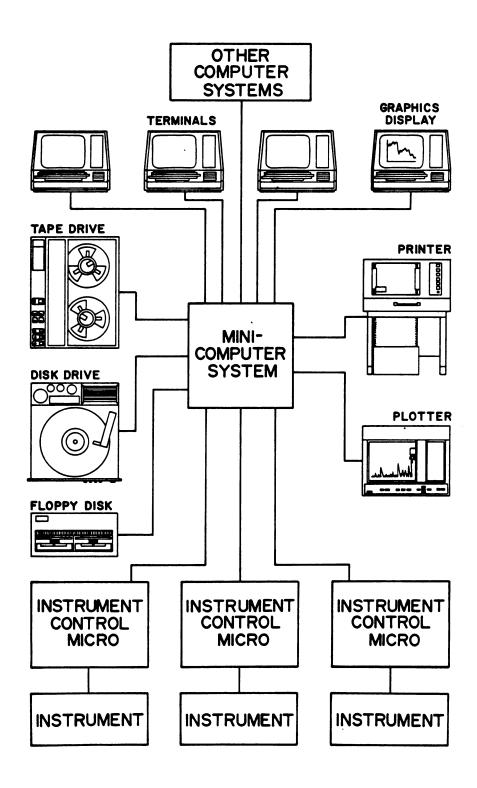

| 1-1    | A Typical Hierircal Computer System              | 11   |

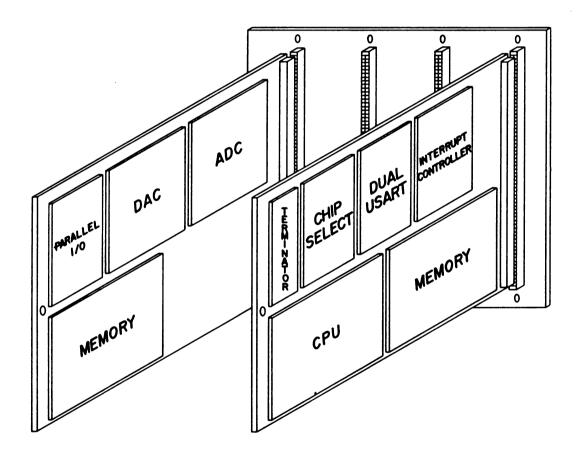

| 2-1    | A Typical Single Microprocessor System           | 20   |

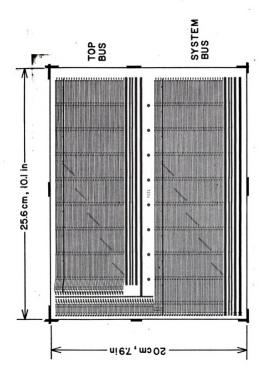

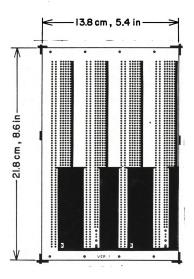

| 2-2    | The Foil Side of the Dual-Bus Board              | 21   |

| 2-3    | The Trace Side of the Backplane Board            | 23   |

| 2-4    | The Layout of the Local Bus                      | 25   |

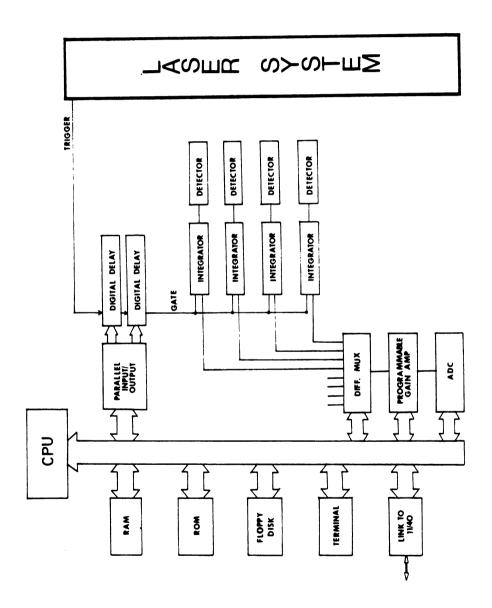

| 3-1    | Block Diagram of the Laser Lab Computer System . | 41   |

| 3-2    | Block Diagram of the Diode Array System          | 46   |

| 3-3    | Block Diagram of the BTOF Computer System        | 50   |

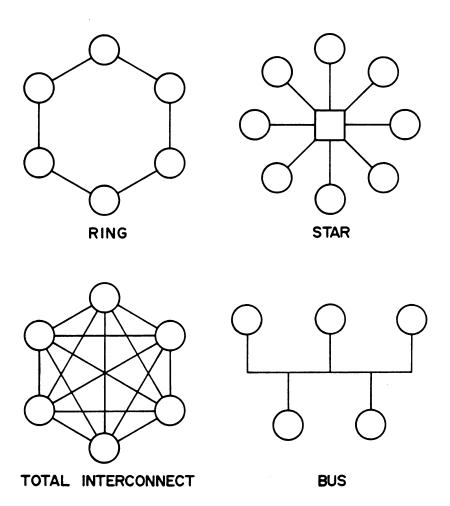

| 4-1    | Distributed System Topologies                    | 63   |

| 5-1    | A Typical Distributed Processing System          | 73   |

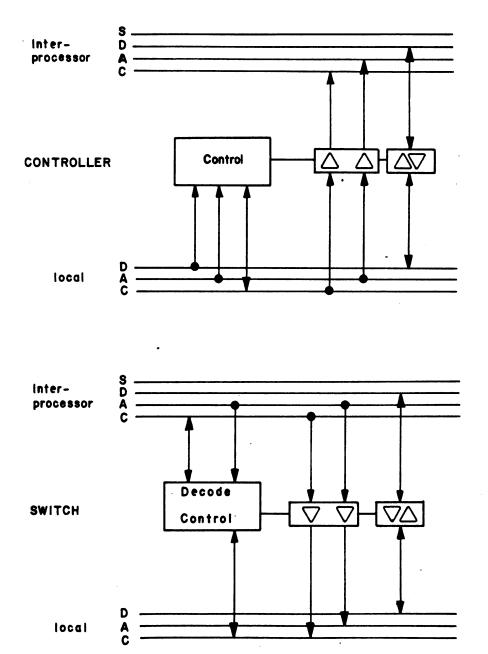

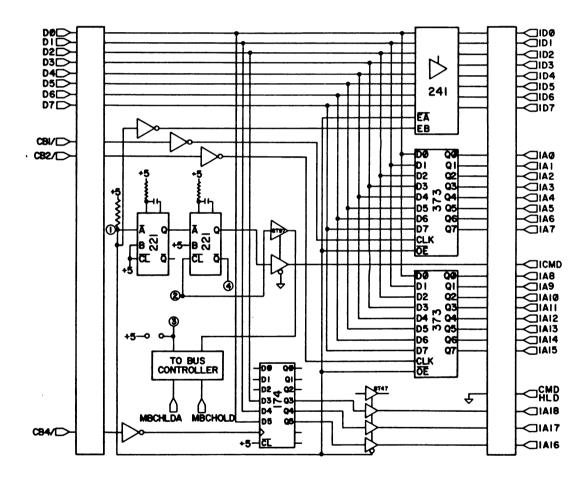

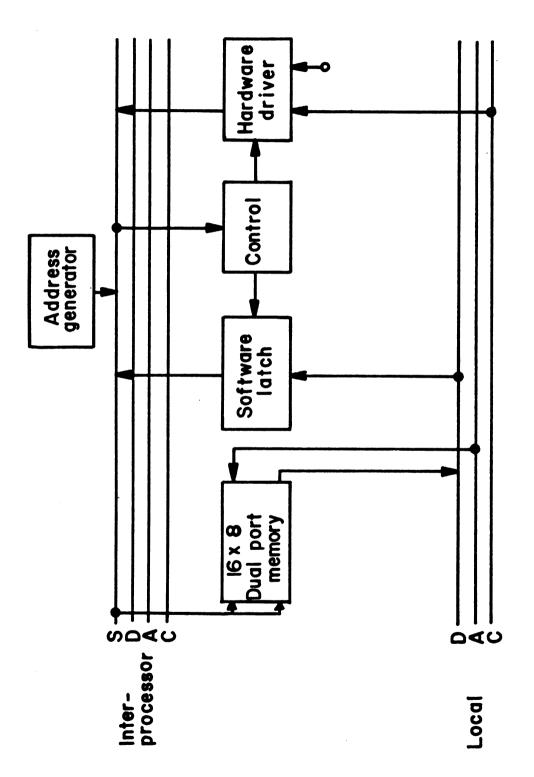

| 5-2    | Block Diagram of the Bus Controller and Switch . | 78   |

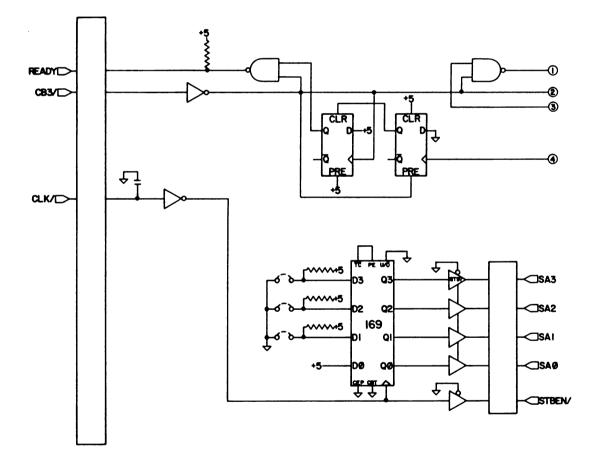

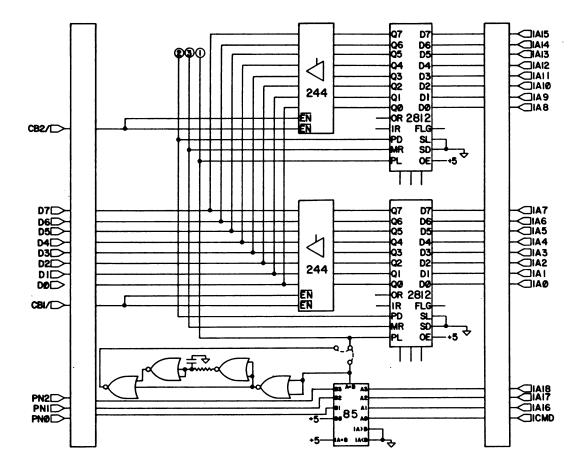

| 5-3A   | Schematic of the Bus Controller                  | 81   |

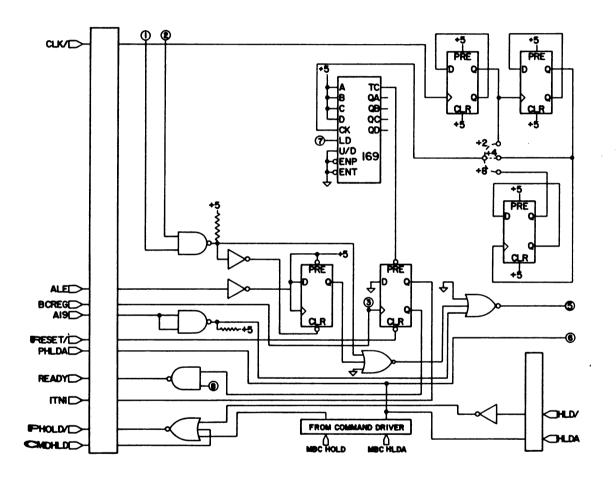

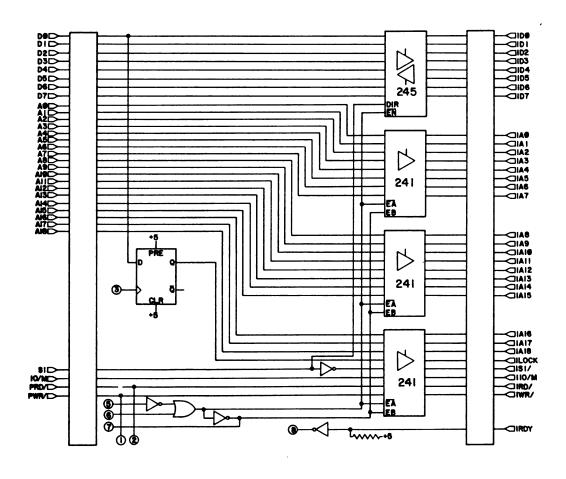

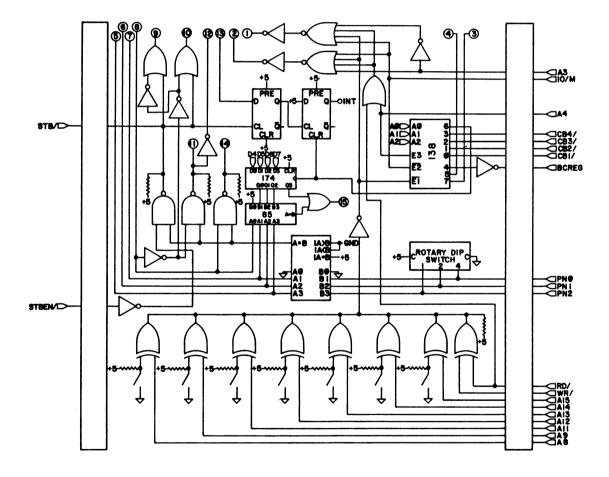

| 5-3B   | Schematic of the Bus Controller                  | 82   |

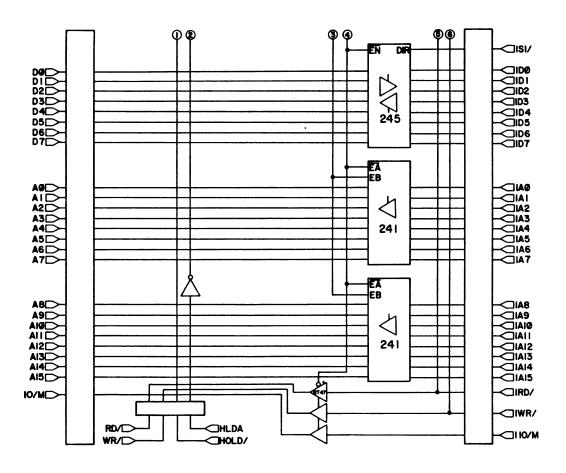

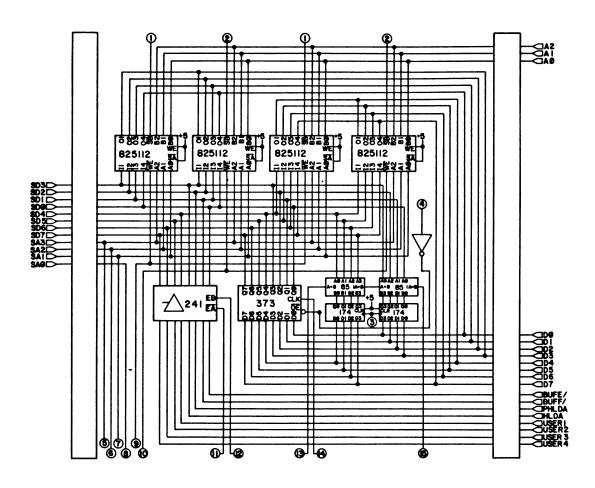

| 5-4A   | Schematic of the Bus Switch                      | 83   |

| 5-4B   | Schematic of the Bus Switch                      | 84   |

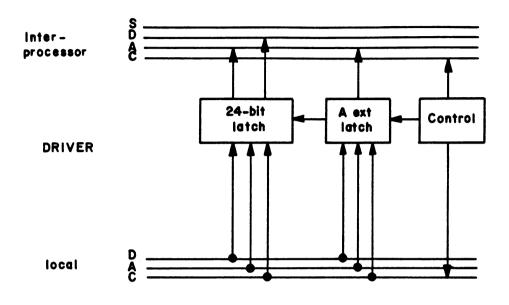

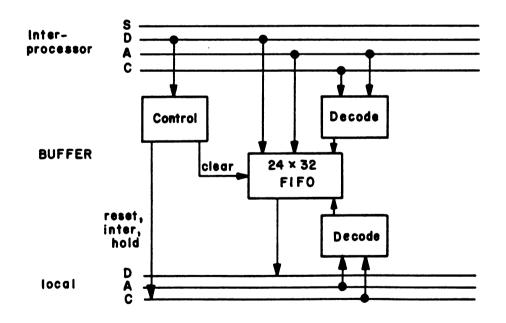

| 5-5    | Block Diagram of the Command Driver and Buffer . | 88   |

| 5-6A   | Schematic of the Command Driver                  | 89   |

| 5-6B   | Schematic of the Command Driver                  | 90   |

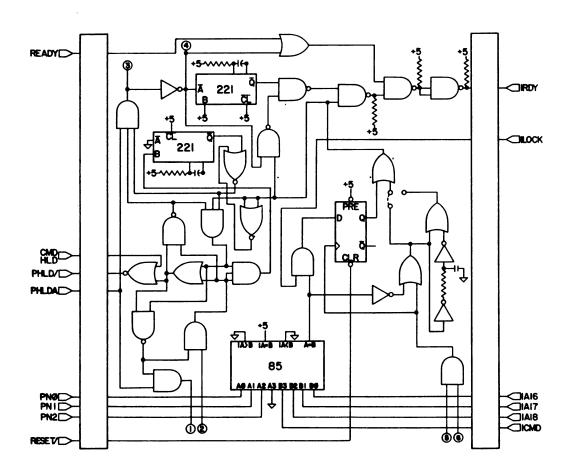

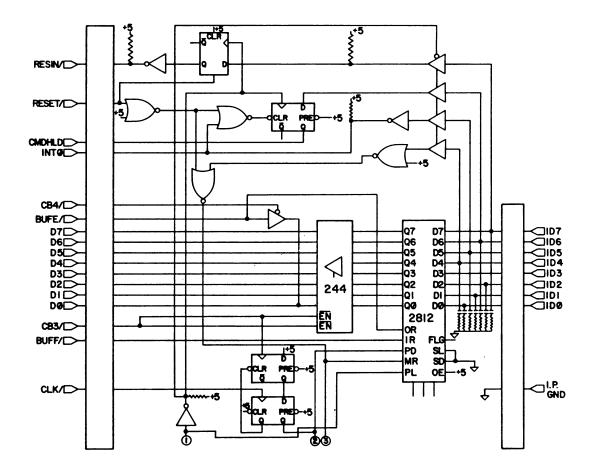

| 5-7A   | Schematic of the Command Buffer                  | 91   |

| 5-7B   | Schematic of the Command Buffer                  | 92   |

| 5-8  | Block Diagram of the Status Module       | 96         |

|------|------------------------------------------|------------|

| 5-9A | Schematic of the Status Module           | <b>9</b> 7 |

| 5-9B | Schematic of the Status Module           | 96         |

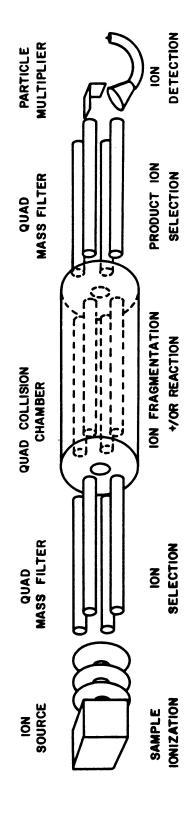

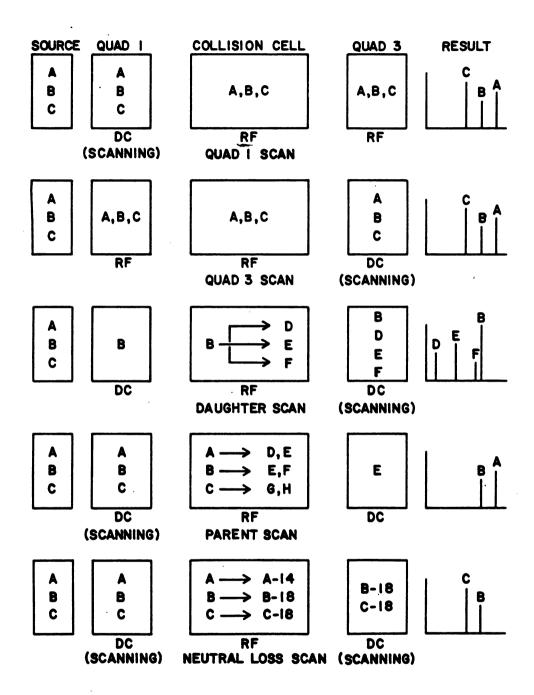

| 6-1  | The TQMS Instrument                      | 104        |

| 6-2  | The TQMS Operating Modes                 | 106        |

| 6-3  | Block Diagram of the TQMS Control System | 111        |

| 6-4  | Block Diagram of the Master Processor    | 113        |

| 6-5  | Block Diagram of the Ion Path Processor  | 116        |

| 6-6  | Block Diagram of the Detection Processor | 119        |

| 6-7  | Block Diagram of the Reduction Processor | 122        |

| 6-8  | Diagram of TOMS Data Acquisition         | 125        |

## CHAPTER 1 - INTRODUCTION-

## COMPUTER IN CHEMICAL ANALYSES

To answer the question of how computers can be used to help the analytical chemist it is useful to examine the general processes that occur during a typical chemical analysis. An analysis can be broken down into four general stages: sample preparation, interaction between the sample and a transducer(s), recording the output of the transducer(s) as a function of other controlled or measured variables, and processing and interpretation of the data.

## SAMPLE PREPARATION

The sample preparation stage involves operations which transform the raw sample into a state where it can effectively interact with the transducer and the elimination of substances in the raw sample that would interfere with the interaction of the transducer and the

component of interest. Examples of these operations include extraction, dissolution, vaporization, chemical reaction, irradiation, and gas and liquid chromatography. A computer used to assist in several ways with can be operations. For routine analyses computer controlled robots could be used to completely automate the sample handling involved in sample preparation. Computer control of GC and LC equipment greatly increases the ease with temperature and solvent programing can be accomplished. A less obvious way in which computers can simplify the task that they enable multiple of sample preparation is dimensions of information about the sample to be collected. When this information is cross-correlated it permits the desired information about the component of interest to be determined even in the presence of many other components. This added selectivity allows a much less pure sample to be analyzed thus decreasing the amount of sample purification that must be performed(1).

### INTERACTION BETWEEN THE SAMPLE AND TRANSDUCER

The second stage of an analysis is the interaction between the sample and a transducer. The transducer can take many forms such as electric and/or magnetic fields, the various types of electromagnetic radiation, or chemical

reactions. It can also be either a single step process, such as the interaction of the sample and electrode in an electochemical analysis or multiple step process, such as a mass spectrometer where the sample is ionized, interacts with an electric and/or magnetic field, and finally is detected by an electron multiplier. One way that computers can assist in this stage of the analysis is by allowing the use of highly nonlinear transducers. These transducers are difficult to employ without computer assisted correction of the transducer's response curve. Another possible way that computers can assist in the interaction of the sample and the transducer is that the computer can vary the conditions of the interaction in a rapid and intelligent fashion maximize the "real" information that is acquired from the sample while minimizing the amount of sample required. This can result in increased precision and sensitivity in the analysis.

## RECORDING THE OUTPUT OF THE TRANSDUCER

Recording the results of the interaction between the sample and the transducer is the third stage of an analysis. The use of a computer for recording the transducer's output has advantages over conventional techniques in a number of different situations. One of

these situations occurs when data are generated bУ transducer at high rates. A modern computer system can data at rates that are much higher that techniques. Another situation happens when large amounts of data are generated by the experiment. Computer systems can be very useful in this case because they allow the data from the experiment to be processed in real time. greatly reducing the amount of data that must be stored. A final example of a situation where computer acquisition of data is an advantage is when an experiment takes a long time to perform. Unlike most human beings, a computer take data for days at a time without ever getting bored. Also computers can simultaneously take related or temperature for corrective data. such as а data from temperature-sensitive transducer or transducers with different selectivity coefficients (2). The computer is also capable of evaluating the quality of data in real time and thus move to the next point when the signal-to-noise ratio is reached or if the present desired datum is not of interest. Α further advantage of computer data acquisition systems i s that data are recorded in a machine readable form. This allows the computer to assist directly in the further reduction and processing of data.

## PROCESSING AND REDUCTION OF DATA

A stage of the analysis where computers can have large impact is the reduction and analysis of the raw data from the experiment. An example of analytical techniques where the use of computers have had a large impact Fourier transform NMR and IR. The routine use of these techniques depends entirely on the use of computer systems to acquire data and to perform the Fourier transform operation. Other examples of computer assisted analysis of area for a number of data are the integration ρf peak instrumental methods, the deconvolution of overlapped peaks, and the use of computer searched libraries standard compounds. A future area that has a great deal of potential is the use of artificial intelligence systems for both data analysis and experiment definitions. experiment definitions would provide rules for intelligent real time optimization of the experimental parameters.

### HISTORICAL PERSPECTIVE

From an historical perspective the widespread use of computers for chemical instrumentation began with the

advent of the minicomputer. These were the first computers that could operate in the laboratory environment and which were directly accessible to the chemist. Minicomputers were, however, still much more expensive than many of the in the laboratory. Thus, the use of instruments dedicated minicomputer was only justified with large expensive instruments, such as NMR or mass spectrometers, with high data rates. In an attempt to share the cost of among several projects these minicomputer the computer systems were frequently connected to a variety of different instruments(3)(4)(5). Because of the complex and expensive interfaces between the computer and the instruments, only minor control over computer frequently had the instrument and was normally used just for data acquisition Even with these limitations the use of and analysis. minicomputers greatly increased the quantity and quality of information that could be obtained from an instrument.

The next major development in the use of computers for chemical instrumentation was the development of the microprocessor. The low cost of these processors has led to an explosion in the use of computers to control chemical instruments. The use of microprocessors has become so prevalent that most new chemical instruments either come with built-in computers or have them available as options. These systems are usually built from either commercial

microprocessor boards or are fully custom systems. These approaches can be justified because σf the needs commercial production. In the research laboratory where or custom instruments must be interfaced existing computer control systems, several different approaches have been employed(6),(7). The simplest of these approaches is the use οf "Fersonal Computers" to control chemical instruments(8),(9)(10). This method is attractive only a few experimental parameters need to be controlled and the resulting data rates and data volumes are small to moderate. The personal computer contains most of the needed components for a control system so only the interfaces to the instrument must be designed. The disadvantage of this approach is the lack of flexibility of the system and the cost of any unused features that are included as part of the basic computer.

A second approach is the use of standard industrial computer boards(11).(12) for instrument control systems. This is a more flexible approach than the use of personal computers since a wide variety of different functions are available from different manufacturers. However, many of the available boards contain more than one function due to the fixed board size, which sometimes results in the purchase of unwanted capabilities. A third approach that has been employed in research laboratories that are

interested in laboratory automation is the use of microcomputer systems that have been specially designed for laboratory control systems(13),(14). This approach offers the greatest flexibility in the configuration of the microprocessor system but requires a large investment of time and personnel to design the needed components. This investment of time is offset by the generation of efficient and economical microprocessor systems that are readily tailored to the specific needs of the instrument.

#### SEPARATION INTO ANALYSIS AND CONTROL SYSTEMS

From the initial discussion of the use of computers to aid chemical analyses, it can be seen that there are two general areas where computers can be of assistance. These two areas are real time instrument control and data acquisition, and the interactive analysis and reduction of data that result from an experiment. The two different classes of functions have different requirements from the computer system in terms of response time to external events and in the types of peripherals needed. The real time control applications require a rapid response time from the processor and need dedicated interfaces to the

instrument being controlled. The data analysis functions on the other hand require only a moderate response time utilize peripherals which are capable of storing amounts of data (e.q. disk and tape drives) or that are useful for presenting data to the operator (e.g. graphics displays, printers and plotters). These differences in requirements suggest that two different computers connected in a hierarchical configuration might best meet the needs of both types of functions. This would allow each of the computers to be tailored to the different requirements each class of functions.

Examples of data analysis functions are reference library searching, correction αf the raw data background effects, transform operations that change raw data into a more comprehensible form, signal-to-noise enhancement, correlation analysis, interactive graphical analysis of the data, and presentation and tabulation of the experimental results. A minicomputer or one of the new super-microcomputers have several features that are helpful in implementing these data analysis functions. These computers are capable of utilizing large amounts of memory, can be readily interfaced to large disk and tape drives, and can implement multi-user operating systems efficiently. This last feature allows the cost and capabilities of expensive peripherals to be shared by several users. These

computer systems are also capable of supporting specialized numeric and array processors which can greatly increase their number crunching ability. Interfaces for graphics displays and plotters are also readily available. Figure 1-1 shows a typical example of this type of computer that is used as a data analysis system for several different instruments. One final advantage of separating the control and data analysis functions into different processors is that the control system can be used to collect data for a new experiment while another user is analyzing the data from a previous experiment on the data analysis system.

Some examples of the types of functions that a control perform the control of instrument system can are parameters, the acquisition of data from the instrument, real time data reduction to eliminate extraneous data values, and rudimentary displays of the acquired data for use in optimization of the instrument parameters monitoring the course of an experiment. To perform functions the control system needs a variety of interfaces to the instrument and peripherals capable of supporting a "user friendly" interface with the operator. Modern microprocessors have several features which make ideally suited for implementing instrument control system. One feature is high performance at a low cost which allows the microcomputer to be dedicated to a single instrument.

Figure 1-1 A Typical Hierircal Computer System.

Another feature that these microprocessors have is a less complex bus structure than the minicomputers which allow simpler interfaces between the instrument and the computer to be constructed. The availability of LSI peripheral USARTs, parallel I/O ports, circuits, such as microprocessor compatible signal converters (ADCs and DACs), also simplifies the design of new interfaces to the instrument. The programmable nature of many of these LSI peripherals is another advantage because it allows a general purpose interface to be used for a variety of instruments by merely changing the controlling software. The low cost of these peripherals also increases the number of instrument parameters that can be controlled by the computer at a reasonable cost.

# COMPUTER NETWORKS

The advent of separate data analysis systems and instrument control systems has led to the development of a variety of laboratory networks which allow the different instrument control systems to communicate with other "host" computer systems(15),(16). These host computer systems provide the "data analysis" system functions while the

satellite systems provide individual instrument control and data acquisition. These heriarchical systems permit the different functions that are involved in an experiment to be performed on the computer that is most suitable for that task. The existence of these networks also assists in the combination of data from different types of instruments to obtain the answers to a single analytical problem. Modern control systems are developing in several directions such as intelligent systems(17) which employ the results of an experiment to determine the conditions for the next experiment, and the use of distributed processing systems to provide increased capabilities for instrument control.

## LABORATORY MICROCOMPUTER SYSTEM DESIGN GOALS

To meet the needs of our research group for instrument control systems, we decided to design a microcomputer system that would better meet the requirements of a research environment than commercial microprocessor boards or personal computers. This system was designed using experience gained with a microprocessor system designed by Jim Avery(18) and Dan Lovse(19) at the University of Illinois, and a previous microprocessor system designed at

Michigan State University by Erik Carlson(20) and Jim Hornshuh(21). To insure that the system would meet the needs of the research environment, a list of design goals was compiled. These goals are given in Table 1-1 and discussed below.

The requirement for the hardware to be modular on the single function level arises from the constantly changing nature of most research instruments. This modularity allows the control system to be easily modified as the experimental needs change. The single function nature of the modules permits the addition of just the capabilities that are required without wasting time, money, or board space on functions that are not needed. The design goal of operation with a wide range of configurations arises from the vastly different requirements of different instruments in a research laboratory. Another of the design goals is the need for the computer systems to be able to operate in a hierarchical system with other computers. This allows the to be used as a control system with a microcomputer separate minicomputer acting as a data analysis system.

The microcomputers also need to be inexpensive if they are to be dedicated to a large number of different instruments. The availability of graduate student labor permits the assembly of the microcomputers to be labor

Table 1-1. The Design Goals for the Microprocessor System.

- 1. Modular hardware on a single function level.

- Capable of operating over a wide range of configurations.

- 3. Should be able to operate in a hierarchical environment.

- 4. Inexpensive given low cost labor.

- Elimination of card edge connectors for improved reliability.

- Frovisions for I/O connections on the backplane.

- 7. Should be able to evolve gracefully from a single processor into a distributed processor system.

intensive and still result in an affordable microcomputer. To improve the reliability of the system, the elimination of printed circuit board edge connectors was a design goal. To be reliable these connectors require gold plated fingers on the FC board and accurate FC board routing. Attempts to use edge connectors had resulted in problems in previous systems since neither of these requirements could be easily met with the available in-house equipment. Another design goal that resulted from experience with previous systems was the desire that I/O connections would be made through the system backplane. This allows a board in the system to be easily removed extended for debugging without ordragging a mass of cable with it. A final design goal was the requirement that a single microprocessor system should be upgradable to a distributed processing system without complete redesign of the instrument interfaces.

### SUMMARY

This thesis describes a microcomputer system which meets these goals. The single processor implementation is described in Chapter 2 and several of the various applications to which it has been put are described in

The concept of distributed processing and the Chapter 3. advantages that it affords are discussed in chapter 4. Chapter 5 describes the specific hardware that was designed a multiple processor version to implement microcomputer system. This multiple processor system was used to implement a control system for an advanced mass spectrometer as described in Chapter 6. A short summary of the software that written for these systems is was presented in Chapter 7. This microcomputer system has been very successful in our department where it has been used to implement more than twelve different instrument control systems.

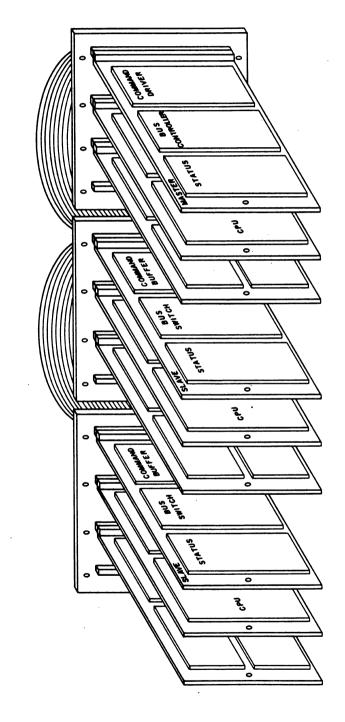

### CHAPTER 2 - THE SINGLE MICROCOMPUTER SYSTEM -

meet the design goals stated in Chapter 1 a modular microprocessor system was developed. This system composed of a series of single function modules which interconnected to form a computer system by mounting the modules on a dual-bus board. The dual-bus board has two sets of bus traces on it which connect the local processor bus to all of the modules in the system. Up to four of dual-bus boards can be plugged into a backplane to form a complete microprocessor system as shown in Figure 2-1. The two sets of bus traces on the dual-bus board can be seen in Figure 2-2, which shows the foil side of a dual-bus board. The signal traces on the dual-bus board are connected to the backplane by pin and socket connectors which mount in the holes shown on the left side of Figure 2-2. These connectors were used because of their high reliability compared to conventional edge connectors. can be seen in Figure 2-2, the lower set of bus traces is directly connected to the pin connector, while the top set of traces is left unattached. The uncommitted nature of the top set of bus traces provides a great deal of flexibility in designing different microprocessor system.

### USES OF THE SECOND BUS

On most of the dual-bus boards in a single processor the two sets of bus traces are joined by a series of vertical jumpers so that both sets of bus traces connected to the local processor bus. This allows standard function modules to be mounted on both the top bottom halves of the dual-bus board, which increases the modules that can be mounted on a single dual-bus number of However, the top bus can be used for more novel applications by jumper-connecting the traces to backplane instead of to the lower bus. This allows the top bus to used as an interprocessor bus, a hardware bе controlled peripheral bus, or as the local processor bus of another processor. The use σf the top bus as interprocessor bus is discussed in the second half of this The advantages of employing the top bus as a dissertation. peripheral bus are examined in chapter 3 where a linear diode array spectrophotometer control system is shown example. An example of the use of the top bus as the local bus of another processor would be the implementation of an intelligent data base controller. A module that connects to both of the busses would allow requests for information to be transferred to the data base control processor, which

Figure 2-1 A Typical Single Microprocessor System.

Figure 2-2 The Foil Side of the Dual-Bus Board.

would then search the data base for the requested information and return it to the main processor.

### THE BACKPLANE

The backplane board, which is shown in Figure 2-3, is capable of interconnecting up to four dual-bus boards. The backplane has a set of traces along it's lower edge which connects the local bus between the dual-bus boards and also distributes power. The signals from the connectors on the top half of the backplane are brought out to sets of pads which permits the mounting of different types of cable connectors. The latter are used to connect the computer system to the instrument that is being controlled and to the rest of the real world. Thus, the dual-bus boards can be removed or extended without having to disconnect any cables. Sets of pads are also provided for connecting the local bus to another backplane if more than four dual-bus boards are required to construct the system.

Figure 2-3 The Trace Side of the Backplane Board.

# LOCAL BUS DEFINITION

The local processor bus used in this system is a fully demultiplexed synchronous bus. The data and address signals active high while most of the control signals are active low to reduce problems with noise spikes. information on the signals generated by the 8085 and 8088 found processors is in the appropriate Intel manuals(22),(23). In addition to the normal bus signals, four additional signals have been provided for the use of the interprocessor modules. The layout of the processor bus is given in Figure 2-4. The definitions of the signals that make up the bus are as follows:

- D0-D7 Eight bidirectional data lines.

- A0-A15 The lower sixteen address lines.

- A16-A19 The four most significant address lines (8088 system only)

- ALE The falling edge of Address Latch Enable indicates that a stable address is available to be latched into the address latches. It is also used to indicate the start of a bus cycle.

- WR\ The active LO write signal is used to strobe data from the data bus into the addressed location.

25

```

Shield Gnd

SHIELD GND

HALT (A19)

(A18) PS1

PS2 (A17)

(A16) PS3

PHOLD\

PHLDA

PWR\

PRD\

HOLD\

HLDA

RESIN\

READY

RST7.5 (INT0)

(INT1) RST6.5

RST5.5 (TEST\)

INTR

RESET\

CLK\

INTA

IO/M

S1

RD\

WR\

ALE

A15

A14

A13

A12

A11

A10

A9

A8

AØ

A1

A2

A3

A4

A5

A6

Α7

DØ

D1

D2

DЗ

D4

D5

D6

D7

ANALOG GND

-24

+24

+5

DIGITAL GND

```

Figure 2-4 The Layout of the Local Bus.

- RD\ The read signal is used to enable a memory or peripheral device to drive the data lines. This signal is active LO.

- S1 This signal gives an advanced indication of the direction of information transfer on the data lines. A HI level indicates data are to be read into the processor.

- IO/M A HI level on this signal indicates an I/O transfer is to take place while a LO level indicates a memory transfer is to occur.

- INTA\ An active LO interrupt acknowledge from the processor.

- CLK\ The inverted processor clock.

- RESET An active LO reset signal from the processor which is used to initiallize all of the peripherals in the system.

- INTR An active HI general interrupt input to the processor. It is normally generated by an 8259A interrupt controller.

- RST5,5-RST7,5 Three interrupt signals to the 8085 processor which have predefined interrupt vector locations in memory.

- INT0,INT1 Two bussed inputs to an 8259A interrupt controller in an 8088 system.

- TEST\ An active LO signal that is tested by the 8088 CFU

- during the WAIT instruction.

- READY When this signal is LO the processor enters a wait state until the ready signal returns HI. It is used to slow down the bus cycle for slow peripherals.

- RESIN\ An active LO reset input to the processor.

- HLDA A hold acknowledge signal which indicates that the processor has released the local bus when HI.

- HOLD\ An active LO signal which requests the use of the local bus from the processor.

- PRD\,PWR\,PHOLD\,PHLDA Four signals used by the interprocessor modules to control the generation of the RD\, WR\, HOLD\, and HLDA signal on systems which have interprocessor modules.

- PS1-PS3 Peripheral status lines which are used by the 8085 CPU module and the interprocessor modules.

- HALT\ An indication that the 8085 CPU has executed a halt instruction.

### STANDARD MODULES

More than thirty different standard modules have been designed for use in this system. This wide range of functions greatly reduces the number of custom interfaces

that must be designed when a new instrument control system is constructed. Table 2-1 gives a list of the currently available modules. These modules are constructed in two single height modules that are 3.7 different heights, inches high and double height modules which are 7.7 inches high. The modules come in different widths depending on the amount of space that the function needs. The modules can be designed in one inch increments from a minimum of one inch to a maximum of nine inches. This modularity of size combined with the ability to pick up bus signals multiple locations on the module result in very efficient use of space.

## PROCESSOR MODULES

There are two different processor modules; one uses the Intel 8085 processor and the other uses the Intel 8088 processor. The 8085 CPU module has latches on it which demultiplex the data-address signals from the processor and tri-state drivers which buffer the data and control signal. This module also contains two switches which allow the processor to be reset and held. There are six LEDs on this module which provide indicators for the following signals, PS1,PS2,PS3,HLDA,HALT,and SOD (serial data out from the 8085). The 8088 processor module combines the functions of

Table 2-1. A list of Standard Modules.

| 8085 CPU                      | 9513 CTC *                 |

|-------------------------------|----------------------------|

| 8088 CFU                      | 58167A RTC                 |

| RAM/ROM                       | Octal 12 bit DAC (AD390)   |

| 8K RAM                        | Dual 8-bit DAC (AD558) *   |

| 8259A Interrupt Controller    | Dual 12-bit DAC (1230) *   |

| Chip Select                   | 12-bit ADC (AD574) *       |

| Address Extender              | Diff. Multiplexer *        |

| Wait State Generator          | Programable Gain Amp. *    |

| AC Terminator                 | Diff. Transceiver          |

| Active Terminator             | Softknobs Interface        |

| SCSI Interface                | 8087 Adapter               |

| 1771 Floppy Disk Controller * | 2",3" Wire Wrap            |

| Dual 8251A USART              | Bus Multiplexer            |

| 8255A PIO                     | Graphics Controller (7220) |

| 8253-5 CTC                    | Graphics Memory Plane      |

<sup>\*</sup> Modules that were designed by other people in the department.

the processor with an interrupt controller, chip select logic, and an active terminator on a single double height was necessary to combine these functions to module. Ιt provide enough space for the processor functions same area as an 8085 CPU module, an interrupt controller module, a chip select module, and an active terminator module. In addition to circuits which demultiplex the data and address sionals and buffer the data and control signals, the 8088 CPU module provides circuits which control the restart address of the processor and provide for the addition of zero, one, or two wait states for memory locations between XF000 and XFFFF. This wait state circuitry is necessary for the processor to access standard LSI peripheral modules. The functions the interrupt controller , the chip select logic, and the active terminator are the same as those provided by standard modules. An adapter module has also been designed which allows the 8087 numeric coprocessor to be used with the 8088 CPU module.

### MEMORY MODULES

There are two different memory modules that can be used with this system. The first provides up to 8 Kbytes of RAM memory using 2114 (4  $\times$  1K bit) memories. This module

has been largely replaced in recent systems by the second memory module. This module, called the RAM/ROM module, has sockets for eight 24-pin JEDEC standard RAM or ROM chips. It can provide a total of 8 KBytes of memory if 1 or 2 Kbyte chips are used or 16 Kbytes if 2 or 4 Kbyte memory chips are used.

### SYSTEM SUPPORT MODULES

Several modules have been designed to provide system support functions such as interrupt control, chip select logic, wait state generation and bus termination. The interrupt control is provided by a module which employs an Intel 8259A interrupt controller to provide eight vectored interrupts. This module can be used with both the 8085 and 8088 CPU modules. Flip/flops and inverters are provided on this module for use in transforming interrupt signals into the active HI level interrupt signals that the interrupt controller requires.

The address decoding for all the peripheral modules is performed by a separate chip select module. This module decodes 512 addresses in memory space into eight 64 byte unqualified chip selects, and the top unqualified chip select is decoded into eight 8 byte read/write qualified

chip selects. The unqualified chip selects are normally used by other LSI peripheral modules in the system while the qualified chip selects are used to control flip/flops and latches. By combining the address decoding onto a single module, the other modules are simplified and duplication of the chip select logic is avoided. To allow the entire 1 megabyte address space of the 8088 to be used, an address extender module was designed which decodes address lines A16 through A19. The address extender module may be used with all the chip select and memory modules.

wait state module is used in an 8085 system stretch the bus cycle by driving READY LO. Its function is provided on the 8088 CPU module because most of the LSI peripherals require a longer bus cycle than the normally provides. Bus termination is provided by two modules, an active terminator module and an AC terminator. The active terminator module terminates the bus signal a 1 kilohm resistor to a 2.6 volt source which is formed. from a zener diode and an emitter follower. The 1 kilohm resistance was chosen as a compromise between the need match the characteristic impedance of the bus traces (approximately 200 ohms) and the desire to keep required DC current levels as low as possible. The AC terminator was designed to permit additional termination to be added to a system without increasing the level DC

drive required. It terminates the bus lines with a 220 ohm resistor and a 10,000 pF capacitor in series. This combination matches the characteristic impedence of the bus traces at the frequencies that the processor uses.

### MASS STORAGE INTERFACE MODULES

Interfaces to mass storage devices are provided by two modules: a floppy disk controller and a SCSI(Small Computer Standard Interface) adapter module. The floppy disk controller was designed using a 1771 floppy disk controller chip and is capable of controlling up to four 8" floppy disk drives. This module was designed by Ralph Thiim(24). The SCSI adapter module can be used to interface the computer to a variety of intelligent disk and tape drive using the industrial standard SCSI controllers bus structure. The use of the SCSI controller greatly simplifies the software since it allows a single driver. program to control both floppy disk and Winchester disks.

# LSI PERIPHERAL MODULES

Serial ports are provided by a dual USART module that has two 8251A USARTs. The baud rates are set by jumpers

which control a baud rate generator chip. Two USARTs were used so that the baud rate generator and the line driver chips could be shared. A Farallel I/O module using an 8255A PIO chip provides parallel input and output ports for the system. Two different counter/timer modules have been designed for this system. One uses the Intel 8253-5 counter/timer chip while the other uses the Advanced Micro Devices 9513 counter chip. These two circuits differ in their complexity and capabilities. The 8253-5 is the simpler of the two and has 3 sixteen-bit counters and fewer operating modes than the 9513. The 9513, which has 5 sixteen-bit counters, is much more flexible than the 8253-5 and includes such features as an on-chip frequency source and a wide variety of operating modes. The 9513 module was designed by Gene Ratzlaff(25). A real time clock module has been designed to provide the computer with the time of day. This module, which uses the National 58167A clock/calendar chip provides both time of day and date for the processor.

## ANALOG FUNCTION MODULES

Analog interface functions are provided by a number of different modules. These include three different DAC modules, an ADC module, a programmable gain amplifier, and

a differential multiplexer module. The simplest of the DAC modules is a dual 8-bit DAC module which contains two AD558 unipolar DACS. The second DAC module is an octal 12-bit DAC module which uses two AD390 quad DAC chips. This module provides eight 2's complement bipolar DACs. The third module is the most flexible of the three modules. This module can be configured to use either 8 or 12 bit DACs; either DAC can be independently configured as unipolar bipolar with a full-scale range of 10.0, 7.5, 5.0, or 2.5 The ADC module uses an AD574 ADC which is a 12-bit 35 microsecond converter. This module also contains a AD583 sample and hold circuit. The differential multiplexer was constructed with a HI1-0507 which is an eight channel differential multiplexer. A Burr-Brown 3606B6 was used to implement the programable gain amplifier module. module is software programable for gains between 1 and 1024 in powers of 2. Most of these modules were designed other people in the department: the differential multiplexer and programable gain amplifier were designed by Lynn Jones (26), the ADC was designed by Gene Ratzlaff (25), the AD558 module was designed by John Stanley(27), and the dual 8/12 bit DAC board was designed by Norm Penix(28).

#### MISC. MODULES

in the construction of custom interfaces miscellaneous several modules have been designed. differential transceiver module was designed for use when the interfaces to the instrument needed to be physically distant from the computer system. This module allows subset of the local bus to be differentially driven to a remote location. The ability to place interfaces close to the instrument results in much shorter analog signal paths which leads to better accuracy and greater noise immunity. For use in prototyping interfaces, two wire wrap boards have been designed. These modules come in 2 inch and 3 inch widths with pads provided on the 2 inch module for connections to the local bus. A final miscellaneous module is a softknob interface which can interface up to four quadrature encoded rotary knobs to the computer system. These knobs are very useful in providing a convenient way. of controlling various instrument parameters.

### DUAL HEIGHT MODULES

Several modules have been designed which make special use of the top bus. The first of these is a bus exchanger

module which can switch the two sets of bus traces on a dual-bus board between the local bus and a second bus connected to the top of the backplane. This module is normally used to switch blocks of memory between two different busses. Two other modules use the top bus as a graphics memory bus. These modules are the oraphics controller and the graphics memory plane module. The graphics controller uses a NEC7720 graphics controller chip. This chip controls up to 256K bytes of private graphics memory and can draw points, lines, boxes, and circles. The graphics memory module can use either 16K or 64K DRAM chips which results in a 512 by 512 pixel display if 16K chips are used or a 1024 by 1024 memory plane if 64K memory chips are used.

### SUMMARY

This microcomputer system has been used to construct more than twelve systems in our department with excellent results. These systems have been very reliable with no development of contact problems that plagued previous microcomputer systems in the laboratory environment. The modular nature of this system has also allowed systems with

very different functions to be constructed with only minor amounts of custom interface design. Three of the systems that have been built with these modules will be examined in Chapter 3 to illustrate the power and flexibility of this system and the advantages it has for chemical instrumentation.

## CHAPTER 3 - EXAMPLE MICROCOMPUTER SYSTEMS -

The modular microprocessor system described in Chapter used to construct over twelve instrument control systems in our department. As examples of the different types of microprocessor systems that can be built, three of these control systems will be examined in detail. These three systems are a data acquisition diode system for a laser laboratory, a array spectrophotometer that is used for optical rotatory experiments, and a control system for a time-resolved magnetic dispersion mass spectometer. These three systems will also be used to demonstrate several ways the computer was used to improve the chemical information that is obtained from an experiment.

### LASER LAB DATA ACQUISITION SYSTEM

The first computer system that will be examined is the laser lab data acquisition system (29). The type of experiment this system was designed to control is the

investigation of saturation effects on absorption spectra. In these experiments, a sample is optically pumped by one wavelength of laser light and then the absorbance at a different wavelength is measured by a probe beam (26). To perform these experiments, four light intensities must be measured for each laser pulse. These four values are the intensity of the incident pump beam, the intensity of the transmitted pump beam, the intensity of the incident probe beam, and the intensity of the transmitted probe beam. A block diagram that shows the major components of this system is presented in Figure 3-1.

The system was constructed on three dual-bus boards using the following standard modules: an 8085 CPU module, two RAM/ROM modules, a dual USART module, an interrupt controller module, an active terminator, a floppy disk controller module, a parallel I/O module, a differential multiplexer module, a programmable gain amplifier module and a 12-bit ADC module. As can be seen in Figure 3-1 one of the USARTs is used to communicate with a terminal while the other USART is used to communicate with a DEC PDP-11/40 which performs advanced data analysis functions. The floppy disk is used to store both system software and acquired data. A "step through" of the stages involved in data acquisition will best illustrate the system operation. A data acquisition operation is started by the firing of the

Block Diagram of the Laser Lab Computer System. Figure 3-1

Nd/YAG laser system, which sends a trigger signal to the microcomputer. The trigger signal is connected to several digital delay cards where it is used to generate gate and signals to a set of four gated integrators. reset The length of time that the gate is delayed from the trigger and the width of the gate pulse are both programmable through the parallel I/O port that controls the digital The four light beams to be measured are converted to electrical current Ьy four photodiodes. and the resulting signals are integrated by four separate gated integrators. The end of the gate pulse causes an interrupt signal to be sent to the microprocessor. The microprocessor then acquires the four data values the four channels of the differential selecting each αf multiplexer sequentially, setting the programmable gain amplifier to the proper gain for the selected channel, and converting the resulting signals. This process is repeated for ten to one hundred pulses and then the data displayed along with the transmittance for each of the two The software also displays the mean transmittance, standard deviation of the mean, and the percent error.

The laser lab system is an excellent example of how a computer system can greatly increase the amount of chemical information that can be acquired. Before the computer system had been constructed a number of experiments were

attempted using an oscilloscope for readout. Polaroid the oscilloscope screen provided data photographs of immediately apparent that this approach Ιt was had serious shortcomings in several areas. The first these was the task of aligning the optical components in the system. This task was extremely tedious because after every change in the optical path, the ratio of the incident and transmitted signals had to be determined from oscilloscope display. With each measurement so tedious, the estimation of the error in the measurements was very difficult. Even greater problems were encountered in trying to determine accurate values for the transmittance of the pump and probe beams. Because the use of an oscilloscope allowed only one diode signal to be monitored at a time the transmittance of the two beams could be determined only average values of the incident and transmitted beams. This was a problem because the pulse-to-pulse variability of the laser power was quite large (factors of two or more are common). The error in the determination of the average beam intensities was larger than the small changes in probe beam transmittance that the experiment was trying to determine. Using the data system, these problems were easily overcome since the computer could measure all of the signals for each pulse of the laser thus providing a complete transmittance measurement for both beams as well

as an accurate measurement of laser power in each beam. The computer system also calculates the error in the measurements which is of great value in trying to align the optical components.

# LINEAR DIODE ARRAY SPECTROMETER SYSTEM

The second control system is a data acquisition system for a linear diode array spectrophotometer (30), (31). This system is used to determine optical rotatory dispersion spectra of various compounds. The ORD technique involves the determination of the optical rotation of circularly polarized incident light by optically active compounds as a function of the wavelength of the incident light. The diode array that is used as a detector has 512 diodes arranged in a linear array. In operation, light striking the diodes causes a decrease in the charge that is stored in each diode. After a programmable integration time, the charge on each diode is serially shifted out of the array, and the charge that must be added to return the diode to the original level is measured. This charge is proportional the amount of light that the individual diode received.

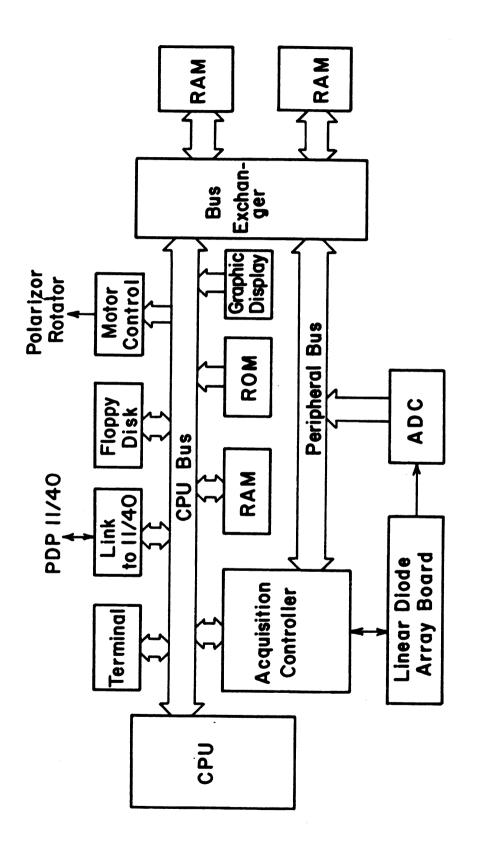

As can be seen from the block diagram of this system shown in Figure 3-2, the top bus on several of the dual-bus boards is used as a hardware-driven peripheral bus. reason that this configuration was chosen is that the diode generates data at a rate faster than can array accommodated by the processor. Normally the data could be access (DMA) stored in memory using a direct memory controller. However, this requires the use of the local bus which inhibits operation of the processor while the DMA transfer is going on. DMA storage was not a viable option in this case because there is insufficient time between blocks of data for the processor to load the integration time and acquisition parameters for the next block of data. These problems were avoided by using a bus exchanger module to switch two blocks of memory alternately between the local bus and the top bus. This allows the data to be stored in memory over the peripheral bus while the is loading the next set of acquisition processor parameters. After several blocks of data have been stored in the memory, the bus exchanger swaps the banks of memory so that the processor can process the data and store it disk.

The computer system was constructed on six dual-bus boards using the following standard modules: an 8085 CFU module, two RAM/ROM modules, two RAM modules, a dual USART

Block Diagram of the Diode Array System. Figure 3-2

module, an interrupt controller module, a floppy disk controller module, an active terminator module, and a bus exchanger module. In addition to the standard modules, a number of custom modules were designed for stepper motor control, control of the diode array board and the data acquisition hardware, and an interface to a commercial graphics display board. The stepper motor is used to rotate an optical polarizer so that the absorption at different rotations of light can be measured. The graphics display was provided so that the operator could check the data to determine if the instrument is working properly. The data can then be shipped up to the PDF 11/40 for further processing using one of the serial ports.

A unique feature of the acquisition hardware is an "autoranging" function which allows a wide dynamic range of data to be acquired with a moderate amount of memory. With this function, a scan of data is acquired and stored in memory using a short integration time. Then integration-time is then doubled, and a new scan of data acquired. However, the individual values are stored in memory only if they are below a preset threshold that is near full-scale for the analog-to-digital converter. By storing these new data points at the same memory addresses as the original data points, and also storing a code which indicates the integration time, the total amount of memory that is

required is only the original 1024 bytes of memory. The integration time is then doubled again and the processes is repeated until the desired dynamic range has been covered. The final result is a block of data that contains a pseudo floating point representation of the intensity at each wavelength. The dynamic range of this autoranging function is limited by the time that the integrations require and the dark current of the diode array. This hardware thus helps to overcome the dynamic range limitations of the diode array detector.

### MASS SPECTROMETER CONTROL SYSTEM

The microprocessor system that was built to control the time-resolved magnetic dispersion mass spectrometer is an example of a large single processor system(32). The time-resolved magnetic dispersion mass spectrometer (B-TOF) is a new type of tandem mass spectrometer that was invented at Michigan State University(33). In this mass spectrometer the sample to be analyzed is first ionized in the source region. The ions that are formed are then extracted from the source in a pulse and accelerated to several thousand volts of energy. These ions then enter a

collision chamber where some of the ions break apart due to collisions with neutral molecules. The ions and their fragments are then analyzed by the magnet sector which passes only ions of a given momentum to the detector. If the arrival times of the different ions are measured, it is possible to determine the masses of all the ions, both fragments and precursors, and which precursors are the source of each fragment.

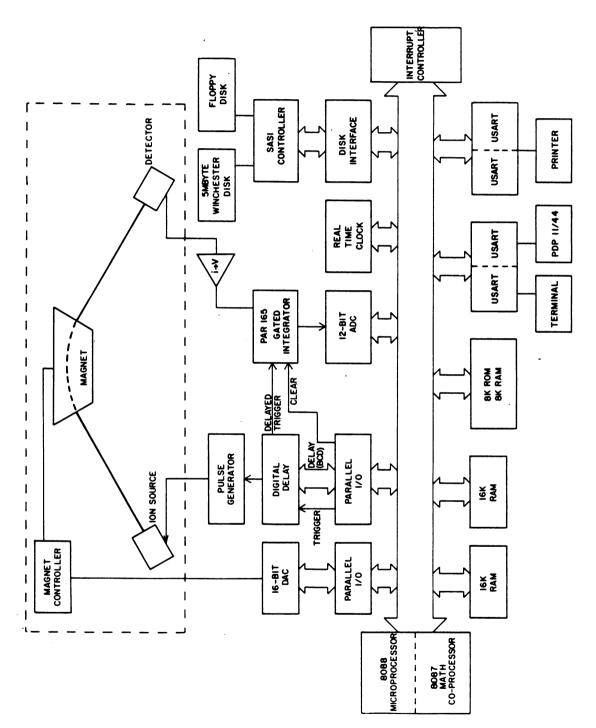

The B-TOF data system, shown in Figure 3-3, was constructed using the following standard modules; an 8088 CFU module with an 8087 numeric coprocessor adapter module, three RAM/ROM modules which provide 8 Kbytes of ROM and 40 Kbytes of RAM, two dual USART modules which provide serial ports for connection to a terminal, a printer, and a PDP 11/44, a real time clock module, an interrupt controller module, a SCSI adapter module which communicates with a SCSI disk controller that is controlling a 5 Megabyte Winchester disk and a floppy disk, a 12-bit ADC module, and two parallel I/O modules. One of the parallel I/O modules is used to control the magnetic field strength through a 16-bit DAC; the other parallel I/O port is used to control a digital delay module and a gated integrator. The digital delay module determines the time delay between the pulsing of the ions out of the source and the measurement of the ion current by the gated integrator. By changing the length

Block Diagram of the BTOF Computer System. Figure 3-3

of the time delay the ion current at different arrival times can be measured.

Initial experiments, which measured the flight times of ions through a magnetic sector mass spectrometer, were performed with oscilloscope to display an time-dependent ion current. These experiments confirmed the design concepts of the instrument, but to acquire the MS/MS spectra of a single compound was a prolonged task. microprocessor system has made it substantially easier to obtain the MS/MS spectrum of a compound. The computer system is also capable of converting the time and magnetic field strength into the two mass axes for more meaningful display of the data. The increased speed with which a spectrum can be obtained will greatly assist in the modification of the instrument to improve its usefulness for multi-dimensional spectroscopy. mass In the near future, a color graphics display will be added to the system to assist in data display. This graphics display. built on two dual-bus boards from a graphics will be controller module and three graphics memory plane modules. The memory modules will use 16K DRAM memory chips which will result in an 8-color 512 by 512 pixel graphics display.

### SUMMARY

As these examples illustrate, the use of microcomputers for instrument control and data acquisition can greatly increase the capabilities of the analytical chemist to acquire useful chemical information. The elimination of the routine drudgery involved in data collection and data analysis permits the chemist to concentrate on the important aspects of data interpretation and experimental design. It can also increase the accuracy and precision of the experimental results and permit new, previously infeasible experiments to be performed.

### CHAPTER 4 - DISTRIBUTED PROCESSING SYSTEMS -

more experience was gained with microcomputer systems for chemical instrumentation, the systems have evolved from their early role of the automation of data acquisition into full instrument control systems. These have taken over the responsibility for such systems functions as scan generation and temperature programing from dedicated hardware controllers. The control of these functions through software instead of hardware has led to greatly increased flexibility in the operation of instrument. An example of the increased capabilities that occur through the use of software is the generation of a mass control signal for a quadrupole mass spectrometer. The software can cause the mass spectrometer to scan rapidly until a peak is detected and then back up and scan over the allows the peaks to be determined. peak slowly. This accurately while greatly reducing the scan time and thus the amount of sample needed. Another advantage of computer control of all the instrument parameters is that computer is then able to create a data base that includes values of all of the instrument parameters along with the experimental data. This information is very helpful

analyzing the data and allows an experiment to be with the instrument in the same state as in the original As microcomputer systems were interfaced larger more complex instruments with all of the instrument parameters under computer control, the demands on the computer system for high speed data acquisition and intelligent instrument control became greater than the capabilities of a single microprocessor. To realize fully the potential of these instruments and to permit further advances in the development of intelligent control systems, it was imperative that a more capable computer system be designed.

obvious solution to the need for a more capable control system is the use of a larger more powerful computer such as a minicomputer. The use of a single faster computer to increase the capabilities of the control system has several drawbacks. The first problem with this approach is that the addition of more processing power becomes more and more expensive for each increment in performance. A second problem is that the interfaces between the computer and the instrument become more complex and expensive as larger computer systems are employed. These increases in cost and complexity reduce the number of instruments that can justify the use of such control systems. An alternative solution to the need for

computer power is the use of several small computers This connected together. results in a distributed processing environment where the different tasks needed to control the instrument are performed on several different processors. Distributed processing systems have a number of advantages for implementing advanced instrument control systems. These advantages, which are listed in Table 4-1, can be classified into three general areas: execution of tasks, independent execution of tasks, and increased modularity of hardware and software (34).

### MULTIPLE PROCESSOR SYSTEMS

Computer systems that contain more than one processor can be classified into two general types, multiprocessor systems and distributed processing systems(35). Multiprocessor systems generally consist of several "equal" processors which share the workload of the system. During operation, a task may be assigned to any unoccupied processor. This is called dynamic load sharing because the assignment of tasks takes place during program execution. On the other hand, distributed processing systems use static load sharing, where the assignment of tasks to the

## Table 4-1 Advantages of Distributed Processing Systems

### Faster Execution

- o Parallel execution

- o Less time spent in "overhead"

- o Simpler addition of hardware controllers and processors

### Independent Task Execution

- o Non-interference of tasks

- o Elimination of task interleaving programs

- o Elimination of priority assignment programs

- Simpler task program modification

## Modularity of Hardware and Software

- o Consolidation of related tasks

- o Simpler extension of instrument capability

- o Simpler debugging and troubleshooting

different processors in the system occurs during system design. Frequently the different processors in the distributed processing system are not identical, but have a variety of enhancements, such as special interfaces or numeric coprocessors, which are required for the performance of their assigned tasks. In systems with more than one processor, the processors can be said to loosely or tightly coupled depending on the means communication between the processors. Loosely-coupled processors communicate with each other through shared peripherials while tightly-coupled processors communicate through shared memory (36).

### TASK COUPLING IN DISTRIBUTED SYSTEMS

The ways in which tasks in a distributed processing system are linked or coupled can also be categorized into several different forms. These forms of coupling are tightly-coupled tasks, loosely-coupled tasks, and terminal tasks. Tasks that have no interaction with other tasks in the system after they have been started are classified as terminal tasks. These tasks are generally assigned to intelligent peripherals in the system. These intelligent

peripherals are usually small microcomputers that are used to off-load peripheral handling tasks from the main processor. Once they have been instructed to perform specific task, they need no further interaction with the main processor until they have completed the operation. example of this class σf task is a printer which incorporates a microcomputer to control its operation. Once the data has been transferred to a buffer in the printer the microcomputer controls the printing of all the data then notifies the main processor when it has finished.

Tasks that involve interaction between the processors that are executing the different subtasks can be classified as loosely or tightly coupled tasks depending on the degree and time frame of the interaction. Loosely-coupled tasks involve semi-autonomous subtasks which generally interact on a millisecond time scale during the execution of the main task. An example of this type of coupling is a two processor system where one processor would acquire a number of data points from the instrument and then transfer the block of acquired data to a second processor. The second processor would then format and store the data on a disk drive while the first processor was acquiring a new block of data.

In tightly-coupled tasks, on the other hand, the

different subtasks are a much smaller portion σf the overall task. This requires much more coordination the various processors on a faster time scale. An example of tightly-coupled tasks is a system where two processors are involved in data acquisition. In this system one processor would set the instrument parameters to new values then signal the second processor that the parameters had been changed. The second processor would then acquire data point from the instrument, signal the first processor that a point was acquired, and perform any necessary formatting operations. While the second processor acquiring a new value, the first processor would calculate a new set of instrument parameters and, upon receipt of the signal from the second processor, would change instrument parameters to the new values. As can be seen from this example the interaction between tightly-coupled tasks frequently occurs on the microsecond time scale. operation of a distributed processing system is not limited to a single type of task coupling, but frequently uses all of the different types of coupling.

### TASK PARTITIONING

One of the decisions that must be made during the design phase of a distributed processing system is how the different tasks in the system are going to be partitioned among the different processors. The partitioning of tasks in distributed processing systems can be performed in a variety of ways depending of the end use of the system and the critria that are used to separate tasks. Three of the major forms of partitioning are vertical partitioning, horizontal partitioning, and data access partitioning (37). Tasks that can be executed in any order or that can be executed concurently can be partitioned using horizontal Tasks that definite partitioning. have a predecessor-successor relationship can be partitioned using vertical partitioning. Data access partitioning separates tasks by what data they operate on without regard to temporal order, control, or direction of data flow. In real-time instrument control systems, vertical partitioning is usually the best choice because οf the many predecessor-successor relationships involved.

The different partitions that arise from the application of vertical partitioning to real time control

systems can be classified into three major types according to the data transform concepts proposed by Yourdon and Constantine (38). The terminology for the three different types of partitions (afferent, central, and efferent) is derived from the different functions of nerve cells in the nervous system. In afferent partitions, a data input stream is converted into a form which is suitable for use by the other partitions. Operations that fall into this class are: data acquisition, signal processing, and data conversion and formatting. The tasks involved in preparing internally generated data stream for output transmission are performed in efferent partition. These tasks involve the formatting and scaling necessary to prepare the data stream for the output interface. The central transform partitions perform all of the operations that come between the afferent and efferent partitions. This is where the main data processing operations, such as data reduction and interpretation, take place. These different classes of partitions may be utilized as criteria for assigning tasks to separate processors.

# INTERPROCESSOR TOPOLOGY

Another of the decisions that must be made during the design phase of a distributed processing system is what interconnection topology should be used to link the Several of the more common different processors(39). configurations for distributed processing system are shown in Figure 4-1. Each topology has different strengths and such areas as, cost of implementation, weaknesses in complexity of the interprocessor interface, communication bandwidth, and the ease with which another processor can be added. The loop configuration has a low to moderate level of complexity and can be implemented at a low to moderate In this system, a new processor can be added quite cost. easily by connecting just two communication paths. The communication bandwidth is low to moderate with the loop configuration because a message from a sending processor to must pass through all of the intervening a receiver An example of a low cost version of this processors. topology is the HF-interface loop (HF-IL)(40), which was designed to interconnect programmable calculators and their peripherals.

The star configuration, which consists of a central

Figure 4-1 Distributed System Topologies.

switch that is connected directly to each of the processors in the system, has a moderate cost of implementation and a moderate to high complexity. This system has a moderate to high communication bandwidth limited by the bandwidth of the central switch. The IBM network/440, which connects several remote 360 computers together through a central 360 mainframe computer, is an example of this topology. This topology is also frequently used to connect a central mini or main frame computer to a number of satellite processors, where the communication paths are used to upload data from the satellite processors to the host instead of being used for communications between different satellite processors.

The topology which has the highest cost and complexity is the total interconnect configuration where each computer has a direct link to every other computer in the system. The addition of another processor to the system is difficult since the new processor must be connected to each of the existing processors. The advantage of this topology is that it has a very high communication bandwidth due to the dedicated paths between the processors. An example of the type of system is a fully interconnected version of the IBM attached support processor system(41).

The fourth topology that is shown in Figure 4-1 is the common bus system which has a low to moderate cost and

complexity. In this system it is easy to add another processor and the resulting system has a moderate communication bandwidth which is limited by the bandwidth of the bus. The IEEE-488 GPIB instrumentation(42) and the military 1553 avionics bus(43) are examples of the common bus topology.

### INTERPROCESSOR COMMUNICATION MODES

facilitate the development of advanced control systems for complex instruments, the decision was made to develop the modules necessary to interconnect single processor systems, built from the standard modules. together to form a distributed processing system. implement this system, it was necessary to define the different modes of communication between the processors in the system. An examination of the tasks involved in real time control systems revealed the need for four modes of interprocessor communication. These modes are block data transfer, task assignment, parameter transfer, and task coordination. The block transfer of data is utilized download programs into the different processors and to move data sets between processors. The task assignment mode is

used to inform the different processors in the system what tasks they should be performing and in what order. The parameter transfer mode is used to transfer small amounts of information between the processors. These parameters are frequently used in conjunction with task assignment where they supply such information as the number of times a command should be executed or the limits that the command should utilize. The final mode of interprocessor communication involves the transfer of status information between the different processors so that tasks on the different processors can be coordinated with each other.

### DISTRIBUTED PROCESSOR DESIGN GOALS