# This is to certify that the dissertation entitled

# ACTIVITY-AWARE MODELING AND DESIGN OPTIMIZATION OF ON-CHIP SIGNAL INTERCONNECTS

presented by

#### KRISHNAN SUNDARESAN

has been accepted towards fulfillment of the requirements for the

Ph.D. degree in Electrical Engineering

Major Professor's Signature

12/7/2006

Date

MSU is an Affirmative Action/Equal Opportunity Institution

# ACTIVITY-AWARE MODELING AND DESIGN OPTIMIZATION OF ON-CHIP SIGNAL INTERCONNECTS

By

Krishnan Sundaresan

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

#### DOCTOR OF PHILOSOPHY

Department of Electrical and Computer Engineering

2006

#### ABSTRACT

# ACTIVITY-AWARE MODELING AND DESIGN OPTIMIZATION OF ON-CHIP SIGNAL INTERCONNECTS

#### By

#### Krishnan Sundaresan

On-chip global signal bus energy dissipation, thermal reliability, and latency are all dependent upon transmitted word values. Real-world microprocessor workloads cause bus traffic that exhibit significant spatial, temporal, and value locality. However, existing signal interconnect modeling and optimization schemes are oblivious of the correlated nature of such traffic and were developed with random or worse-case (highly-changing) traffic conditions in mind, which limits their effectiveness. To address this, we present activity-aware methods to model and optimize bus energy dissipation, thermal reliability, and latency.

In the area of modeling, we present an activity-aware bus energy and thermal model that permits monitoring of energy dissipation and temperature, both spatially (horizontally across wires and longitudinally along individual wires) and temporally, during microarchitectural simulation of real programs. We find that final temperatures of wires in global signal buses carrying data (instruction) in the processor core increase by as much as 37 (58) degrees Celsius during a simulation run of only a billion instructions in 130-nm (45-nm) fabrication technology. We also find that highly-active wires in these buses attain absolute temperatures of up to 104 (123.7) degrees in 130-nm (45-nm) processors that are higher than the 100 degrees temperature typically assumed during interconnect design. In addition, wire temperature gradients across the sending and receiving ends, with magnitudes between 16-25 degrees, were also

detected. These conditions were found to degrade processor performance by at least 4% (11.92%) in 130-nm (45-nm) processors.

In bus design, we present a traffic-profile-guided approach to optimize bus energy subject to designer-specified thermal constraints and to reduce worst-case bus crosstalk and latency conditions. Our methodology performs these by evaluating several options for signaling individual bit values and all possible ways of mapping bits to bus lines (bit ordering), and then choosing, based on traffic value characteristics, an optimal encoding scheme (the combination of bit signaling and ordering) statically at design time to support in hardware. Our energy-optimal static encoding techniques provide bus energy reductions of 30.2% (52.1%) for processor core data (instruction) buses, respectively, compared to existing more-complex dynamic encoding schemes that yield only 4.19% (5.32%) reductions for the same buses. Our static encoding technique with thermal constraints added during optimization reduces peak wire temperatures by up to 12.26 (12.96) degrees for data (instruction) buses, while still providing significant energy savings. Finally, we also present a static encoding technique that reduces worst-case bus crosstalk conditions by at least 29.35% and a variable-cycle bus architecture that takes advantage of this reduced crosstalk to improve bus performance by 17.42%.

Our work represents a significant advancement over existing approaches that are activity-oblivious and/or consider worst-case traffic conditions. The microarchitecture-level activity-driven spatiotemporal bus energy and thermal model we present is the first of its kind. Our static value-aware bit reordering and signaling techniques are also highly-novel solutions that work remarkably well in real applications.

Dedicated to Mom, Dad, and Deepa,

for their unending love, support, and encouragement

#### ACKNOWLEDGEMENTS

The completion of this research and writing of this dissertation has been one of the most significant academic challenges that I have ever had to face. Without the support, guidance, and patience of many people this endeavor would not have been possible. I owe my thanks to all of them.

I have been fortunate to learn from many excellent teachers, from grade to graduate school, and I am indebted to all of them for helping me reach where I am today. In particular, I thank my advisor, Dr. Nihar Mahapatra, for his technical guidance and support, over the last five years. His mentorship has instilled in me the skill and confidence to identify, analyze, and efficiently solve research problems and present results in a clear and lucid manner. I have also learnt much from his classes and from our research meetings and discussions. I also thank my dissertation committee members, Dr. Anthony Wojcik, Dr. Andrew Mason, and Dr. Peixin Zhong, for their very insightful review and comments which have helped me improve this work.

I have also been fortunate to be in the company of a lot of good friends, many of them my lab-mates, and I thank them all for their support. Jiangjiang Liu helped me get my feet wet in research and was a great colleague during the early years. Kaushal Gandhi and Srivathsan Krishnamohan have been great friends and lab-mates and I have benefited greatly from many technical discussions I have had with them. I cherish their friendship, the good times we had together, and look forward to more Friday-night pizza-and-beer get-togethers in the Bay area where all three of us are

starting our professional careers.

My family—Mom, Dad, and sister—has been a great source of encouragement through the years and their continuing love and affection has made me what I am today. I owe much more to them than what a few sentences can express. This dissertation is dedicated to them.

Last but not least, I thank all members of the Greater Lansing Bhagavad Gita group for their good thoughts and prayers. My association with them has helped me keep up my sanity during these years and taught me to live by the Bhagavad Gita's motto: yogah karmasu kausalam—"Efficiency in Action leads to (the Ultimate) Knowledge."

## TABLE OF CONTENTS

| L  | ST ( | OF TA  | BLES                                                              | x   |

|----|------|--------|-------------------------------------------------------------------|-----|

| L  | ST ( | OF FIG | GURES                                                             | xii |

| SI | ELEC | CTED   | LIST OF SYMBOLS                                                   | xix |

| 1  | INT  | ROD    | UCTION AND OVERVIEW                                               | 1   |

|    | 1.1  | Interc | onnect Scaling Trends: Delay, Power, Temperature, and Reliability | y 1 |

|    | 1.2  | Mater  | ial, Process, and Architectural Advances                          | 4   |

|    | 1.3  | Impac  | et of Interconnects on Architecture and VLSI                      | 6   |

|    |      | 1.3.1  | Wire Delay                                                        | 7   |

|    |      | 1.3.2  | Power and Temperature                                             | 8   |

|    |      | 1.3.3  | Computer-Aided Design Tool Requirements                           | 10  |

|    | 1.4  | Drawl  | oacks in Existing Techniques                                      | 11  |

|    | 1.5  | The N  | Weed for Activity-Aware Design                                    | 12  |

|    | 1.6  | Our C  | Contributions                                                     | 15  |

|    |      | 1.6.1  | Activity-Aware Design Methodology                                 | 15  |

|    |      | 1.6.2  | Accurate Energy, Temperature, and Delay Modeling                  | 16  |

|    |      | 1.6.3  | Profile-Guided Optimization Techniques                            | 17  |

|    |      | 1.6.4  | Novel Thermal Optimization Methodology                            | 18  |

|    |      | 1.6.5  | Performance-Oriented Adaptive Bus Design                          | 19  |

|    | 1.7  | Disser | tation Outline                                                    | 19  |

| 2  | PR   | ELIMI  | INARIES                                                           | 21  |

|    | 2.1  | Interc | onnect Analysis Methods                                           | 21  |

|    |      | 2.1.1  | Global, Semiglobal, and Local Wires                               | 22  |

|    |      | 2.1.2  | Interconnect Models: RC and RLC                                   | 22  |

|    |      | 2.1.3  | Effect of Inductance on Global Signal Lines                       | 23  |

|    |      | 2.1.4  | Energy Estimation                                                 | 24  |

|    |      | 2.1.5  | Delay and Performance                                             | 26  |

|    | 2.2  | Interc | onnect Optimization Techniques                                    | 28  |

|    |      | 2.2.1  | Data Encoding                                                     | 28  |

|    |      | 2.2.2  | Wire Spacing and Shielding                                        | 31  |

|    | 2.3  | Archit | tecture-Level Simulators and Early-Stage Design                   | 31  |

|    | 2.4  |        | Experimental Methodology                                          | 33  |

|    |      | 2.4.1  | Interconnect Geometry and Technology Data                         | 33  |

|    |      | 2.4.2  | Parasitic Capacitance Extraction                                  | 34  |

|   |               | 2.4.3  | Simulation Infrastructure and Verification of its Correctness . | 36           |

|---|---------------|--------|-----------------------------------------------------------------|--------------|

|   |               | 2.4.4  | Target Systems and Benchmarks                                   | 41           |

| 3 | AC'           | TIVIT  | Y-DRIVEN ENERGY AND TEMPERATURE MODEL                           | 43           |

| Ü | 3.1           |        | luction                                                         | 43           |

|   | 3.2           |        | ed Work and Our Contributions                                   | 47           |

|   | 3.3           |        | ine Energy Dissipation Model                                    | 50           |

|   | 0.0           | 3.3.1  | Energy Dissipated due to Line Self Capacitance                  | 51           |

|   |               | 3.3.2  | Energy Dissipated due to Inter-Wire Capacitance                 | 52           |

|   |               | 3.3.3  | Distributed-RC Line Energy Model                                | 53           |

|   | 3.4           |        | nal Model                                                       | 57           |

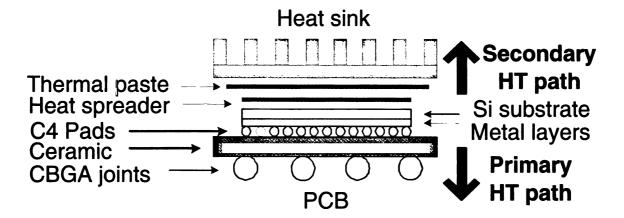

|   |               | 3.4.1  | Chip Thermal Structures and Heat Transfer                       | 58           |

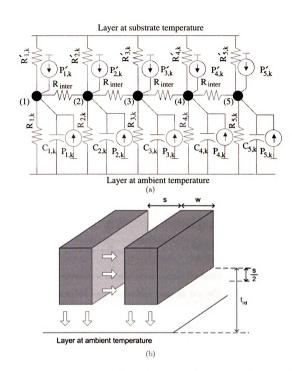

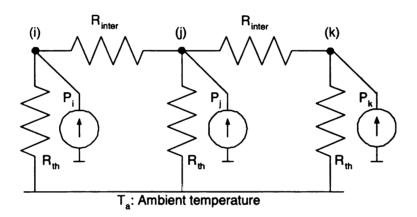

|   |               | 3.4.2  | Detailed Thermal Model                                          | 59           |

|   |               | 3.4.3  | Steady-State Thermal Model                                      | 64           |

|   | 3.5           |        | ation Environment and Methodology                               | 66           |

|   |               | 3.5.1  | Benchmarks and Sample Sizes                                     | 66           |

|   |               | 3.5.2  | Thermal Warmup and Initial Temperatures                         | 67           |

|   |               | 3.5.3  | Granularity of Thermal Simulation                               | 68           |

|   | 3.6           | Exper  | iments and Results                                              | 69           |

|   |               | 3.6.1  | Energy Dissipation in Processor Buses                           | 69           |

|   |               | 3.6.2  | Correlation between Energy and Temperature                      | 75           |

|   |               | 3.6.3  | Final and Peak Wire Temperatures                                | 76           |

|   |               | 3.6.4  | Wire Temperature Gradients                                      | 86           |

|   | 3.7           |        | nary                                                            | 89           |

|   | DA            | TD 4   |                                                                 |              |

| 4 |               |        | AND TEMPERATURE-DEPENDENT DELAY VARI-<br>MODEL                  |              |

|   | 4.1           |        | luction                                                         | <b>91</b> 91 |

|   | 4.1           |        | ed Work and Our Contributions                                   | 92           |

|   | 4.2           |        | erature Dependent Delay Variability Model                       | 94           |

|   | 4.5           | 4.3.1  | Wire Delay Considering Temperature Impact                       | 94<br>95     |

|   |               | 4.3.1  | Wire Delay Variability Considering Crosstalk and Temperature    | 95<br>96     |

|   | 4.4           |        | ·                                                               | 90<br>97     |

|   | 4.4           | 4.4.1  | ts and Discussion                                               | 98           |

|   |               | 4.4.2  | Frequency of Timing Violations                                  | 100          |

|   |               | 4.4.3  | Performance Impact                                              | 105          |

|   | 4.5           | Summ   |                                                                 | 105          |

|   | 4.0           | Sumi.  | аму                                                             | 100          |

| 5 | $\mathbf{AC}$ | TIVIT  | Y-AWARE ENERGY AND TEMPERATURE OPTI-                            |              |

|   | MI            | ZATIO  | ON                                                              | 109          |

|   | 5.1           | Introd | luction                                                         | 109          |

|    |       | 5.1.1  | Need for Energy and Temperature Aware Bus Design       | 110 |

|----|-------|--------|--------------------------------------------------------|-----|

|    |       | 5.1.2  | Key Contributions and Results                          | 112 |

|    | 5.2   | Relate | ed Work                                                | 114 |

|    | 5.3   | Metho  | $\operatorname{odology}$                               | 116 |

|    |       | 5.3.1  | Target Scenarios                                       | 117 |

|    |       | 5.3.2  | Bus Layout and Wire Geometry                           | 120 |

|    | 5.4   | Static | Techniques for Bus Energy and Temperature Optimization | 121 |

|    |       | 5.4.1  | Choice of Signaling Modes                              | 121 |

|    |       | 5.4.2  | Minimum Energy Signaling (MES)                         | 126 |

|    |       | 5.4.3  | Minimum Energy Bit Ordering (MEBO)                     | 127 |

|    |       | 5.4.4  | Simultaneous Bit Ordering and Signaling (SBOS)         | 129 |

|    |       | 5.4.5  | Thermal Optimization Methodology                       | 130 |

|    |       | 5.4.6  | Routing Overheads                                      | 134 |

|    | 5.5   | Result | ts and Discussion                                      | 136 |

|    |       | 5.5.1  | Energy Dissipation in Processor Buses                  | 138 |

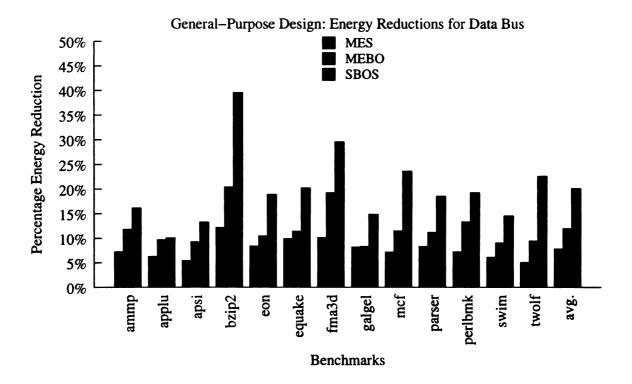

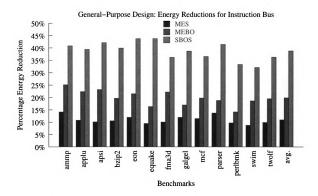

|    |       | 5.5.2  | Energy Reduction for General-Purpose Design            | 145 |

|    |       | 5.5.3  | Energy Reduction for Workload-Specific Design          | 145 |

|    |       | 5.5.4  | Energy Reduction for Program-Specific Design           | 147 |

|    |       | 5.5.5  | Wire Temperature Reduction                             | 154 |

|    | 5.6   | Summ   | nary                                                   | 161 |

| 6  | AC'   | TIVIT  | Y-AWARE PERFORMANCE OPTIMIZATION                       | 163 |

|    | 6.1   | Introd | luction                                                | 163 |

|    | 6.2   |        | ed Work                                                | 164 |

|    | 6.3   |        | iques for Performance Optimization                     | 165 |

|    |       | 6.3.1  | Variable Cycle Bus (VCB) Design                        | 165 |

|    |       | 6.3.2  | Minimum Crosstalk Bit Ordering (MCBO)                  | 168 |

|    |       | 6.3.3  | MCBO with Signaling (MCBOS)                            | 171 |

|    | 6.4   | Result | ts and Discussion                                      | 172 |

|    |       | 6.4.1  | Peak Crosstalk Reduction                               | 172 |

|    |       | 6.4.2  | Performance Improvement with VCB                       | 173 |

|    | 6.5   | Summ   | nary                                                   | 177 |

| 7  | CO    | NCLU   | SION                                                   | 178 |

| •  | 7.1   |        | ibutions and Key Results                               | 178 |

|    | 7.2   |        | ions for Future Research                               | 182 |

| RI | IRT.I | OGR A  | APHY                                                   | 183 |

## LIST OF TABLES

| 2.1 | Bus crosstalk conditions and models for a rising transition in the middle (victim) wire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Technology, wire geometry, and equivalent circuit parameters for top-most layer interconnect. Values in top eight rows are from the international technology roadmap for semiconductors (ITRS) document [1]. Values listed in the next three rows are from Mui et al. [2]. The values for the self and coupling capacitances were extracted using the FastCap tool and the value for $r_i$ was calculated using the formula $r_i = \rho_{Cu}/(w_i \cdot t_i)$ , where $\rho_{Cu} = 2.2 \times 10^{-8} \Omega$ -m. Values of $h$ and $k$ were found using expressions given in Section 2.1.5 and $r = c_{i, i \pm 1}/(c_{line} + h \times C_0)$ | 35  |

| 2.3 | Configuration of our target system and benchmarks. This processor-memory system configuration is based on the Alpha 21264 processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42  |

| 3.1 | Comparison of normalized energy dissipated in wire subsegments obtained using our model and Cadence Spectre simulations for 10 subsegments.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57  |

| 3.2 | Maximum wire temperatures in °C recorded during a simulation of one billion committed instructions for data and instruction buses using 130 nm and 45 nm parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87  |

| 4.1 | Maximum wire temperatures recorded for the ALU result bus. Ambient temperature is 318.15 K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 99  |

| 4.2 | Performance impact expressed as percentage IPC degradation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 107 |

| 5.1 | Optimization scenarios considered in this work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 118 |

| 5.2 | Correlation coefficients $r_{xy}$ between test and training set data for various signaling schemes discussed in Section 5.4.1. Since $r_{xy}$ values are close to 1, our training and test sets are well correlated                                                                                                                                                                                                                                                                                                                                                                                                                            | 120 |

| 5.3 | Number of iterations and running times for various problem types and sizes                                                                                                                                                                                                                                                                                                                                                                                                                                        | 137  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.4 | Optimal signaling and ordering obtained for workload-specific design of the data bus (0=LSB, 63=MSB). $\spadesuit = \text{org}$ , $\heartsuit = \text{inv}$ , $\diamondsuit = \text{trs}$ , $\clubsuit = \text{itr}$ , and $\triangle = \text{mm}$ .                                                                                                                                                                                                                                                              | 148  |

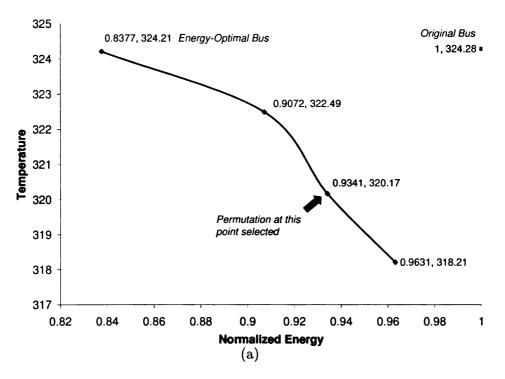

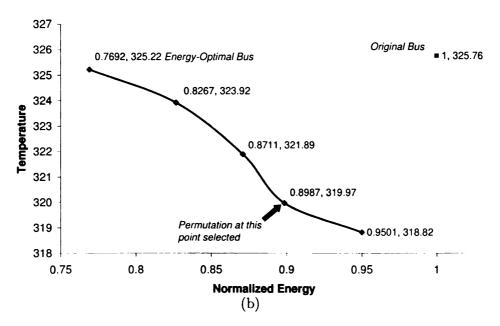

| 5.5 | Thermal Optimization Results. Peak wire temperatures (K) in data and instruction buses for SBOS scheme with and without thermal constraints (TC) applied during optimization. The methodology described in Section 5.4.5 was used to obtain the trade-off curves in Figures 5.16–5.20 and the wire permutations that resulted in bus energy reduction closest to $0.5(1-\frac{E_{opt}}{E_{orig}})$ were chosen from each benchmark's tradeoff curve. Results shown here are for detailed thermal simulations with | 1.50 |

|     | this permutation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 153  |

### LIST OF FIGURES

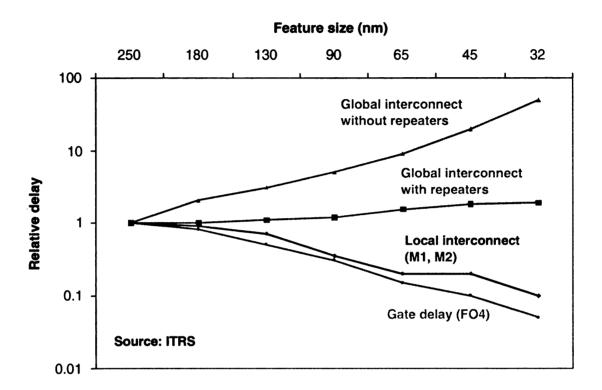

| 1.1 | Gate and interconnect delay scaling for current and future nanometer-<br>scale technologies. Local interconnects scale with gate delay whereas<br>global interconnect delays do not [3]                                                  | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

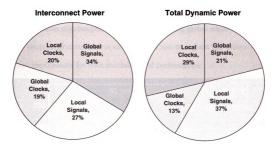

| 1.2 | Interconnect power dissipation due to global and local wires. Global lines are responsible for 21% of total dynamic power dissipation at 130 nm [4].                                                                                     | 3  |

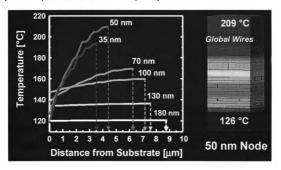

| 1.3 | Projected wire temperature rise in multi-layer interconnects for various technologies under worst-case conditions. Global metal lines will be the hottest, with temperatures expected to reach as much as 209°C in 45 nm technology [5]. | 4  |

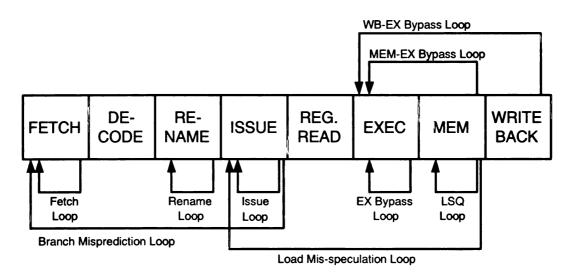

| 1.4 | Pipeline stages and loops in a typical out-of-order processor. More frequently used loops like fetch, LSQ, and bypass are affected strongly by wire delay.                                                                               | 7  |

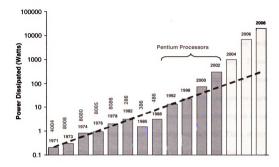

| 1.5 | Power dissipation in Intel processors showing an exponential trend [6]. Since 2001, low-power and power management techniques that have been used widely in microprocessors and have helped slow down the trend somewhat.                | 9  |

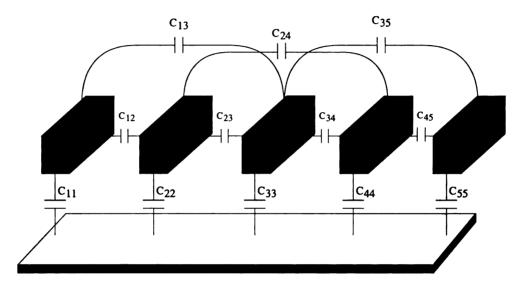

| 2.1 | Layout of wires routed in the top-most layer metal. Self and coupling capacitances are shown. The bottom plate represents the ${\rm V}_{DD}/{\rm GND}$ plane                                                                             | 33 |

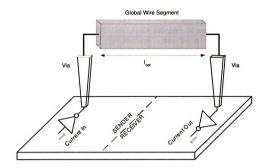

| 2.2 | Wire segment of length $l_{opt}$ between two repeaters                                                                                                                                                                                   | 34 |

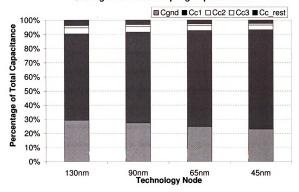

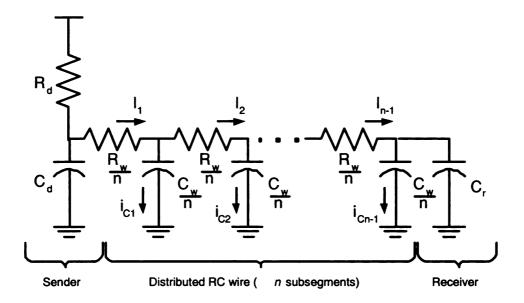

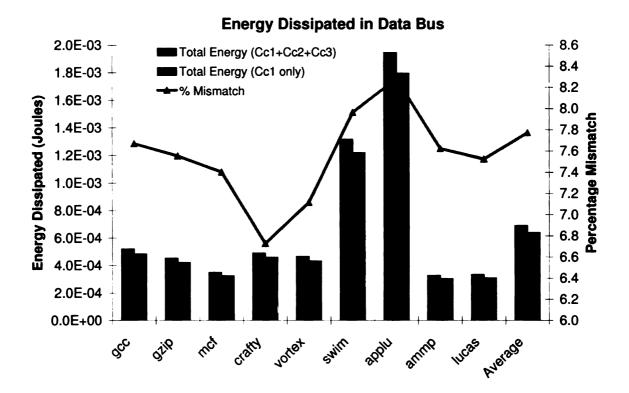

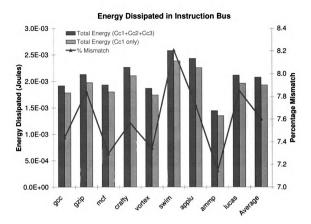

Distribution of self and coupling capacitance values for the middle wire of a 32-bit bus extracted using the FastCap tool [7]. Cgnd = self capacitance of the wire; Cc1 = coupling capacitance between the wire and its adjacent neighbor; Cc2 = coupling capacitance between the wire and a non-adjacent wire with 1 wire between them; Cc3 = couplingcapacitance between the wire and a non-adjacent wire with 2 wires between them; Cc\_rest = sum of coupling capacitances between the wire and other wires with 3 or more wires between them. For current and near-future ITRS technology nodes (up to 45 nm), non-adjacent coupling capacitances are somewhat non-negligible—they contribute 37 Distributed-RC model of the wire segment divided into n subsegments. 53 Figure shows the view of different thermal structures of a C4/CBGA chip and the primary and secondary heat transfer paths. . . . . . . . 58 3.3 Thermal model. (a) Complete equivalent thermal-RC network for a 5-wire bus.  $P'_{1,k} = P'_{2,k} = \ldots = P'_{5,k}, R_{1,k} = R_{2,k} = \ldots = R_{5,k},$  $C_{1, k} = C_{2, k} = \dots = C_{5, k}$ , and  $P_{1, k}, P_{2, k}, \dots, P_{5, k}$  are bus-activity dependent in the model shown. (b) Geometry for calculating equivalent thermal resistances for a wire based on previous work of Chiang et al. The lightly shaded regions and arrows represent heat flow between the conductors or between layers (from a hotter to a cooler one). 60 3.4 Steady state thermal equivalent circuit for three wires. Heat transfer between wires is modeled by  $R_{inter}$  and heat loss to surroundings by  $R_{th}$ .  $P_i$  represents power dissipated in each wire due to switching activity and it can found using a microarchitecture-level simulator. 65 3.5 Total energy dissipated in a 64-bit data bus for various benchmarks. 'Cc1 only' represents the existing energy models which consider only self and adjacent coupling capacitances. 'Cc1+Cc2+Cc3' represents our model that considers self capacitances, adjacent coupling capacitances (Cc1), and two non-adjacent capacitances (Cc2 and Cc3) on each side. The \% energy mismatch shown by the line is plotted with 71 Total energy dissipated in a 128-bit instruction bus for various benchmarks. The % energy mismatch shown by the line is plotted with 72

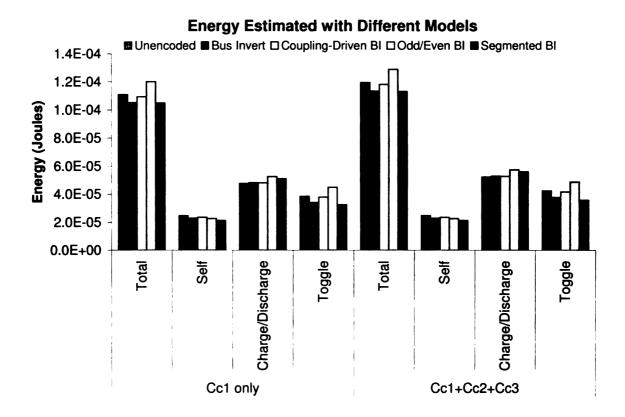

| 3.7  | Total energy dissipated in a 64-bit data bus with various encoding schemes. 'Self' denotes self energy, 'C/D' denotes the coupling charge/discharge energy and 'Toggle' denotes the coupling toggle energy dissipation. 'Cc1 only' refers to existing energy models that consider self and adjacent coupling capacitance only and 'Cc1+Cc2+Cc3' refers to our energy model that considers self, adjacent coupling, and two non-adjacent coupling capacitances | 73         |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

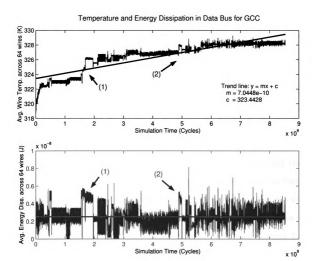

| 3.8  | This plot shows average energy dissipation and wire temperature of the bus for a simulation interval of 10 billion cycles. The continuing temperature rise can be clearly observed                                                                                                                                                                                                                                                                            | 77         |

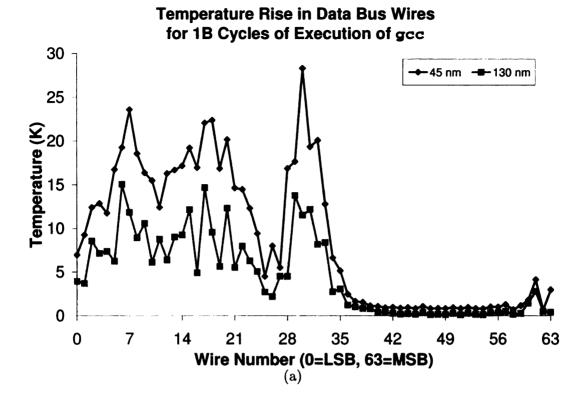

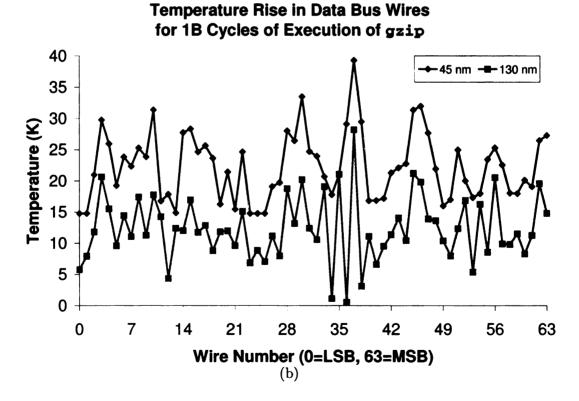

| 3.9  | Plots show the wire temperature rise recorded for benchmarks gcc and gzip for the data bus in 130 nm and 45 nm technology nodes over a simulation interval of one billion committed instructions for each benchmark                                                                                                                                                                                                                                           | <b>7</b> 9 |

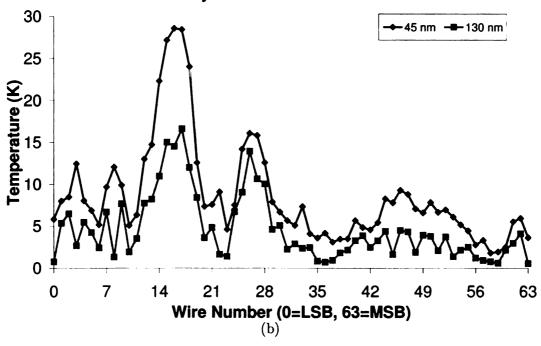

| 3.10 | Plots show the wire temperature rise recorded for benchmarks mcf and lucas for the data bus in 130 nm and 45 nm technology nodes over a simulation interval of one billion committed instructions for each benchmark                                                                                                                                                                                                                                          | 80         |

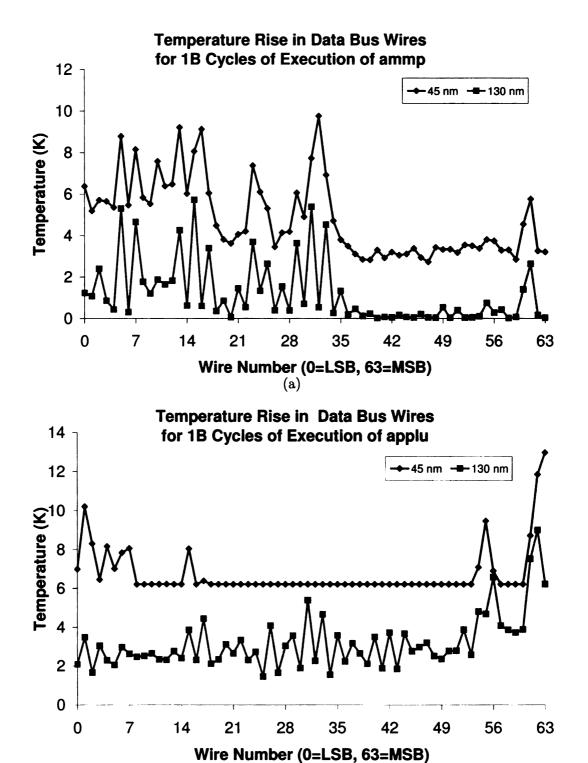

| 3.11 | Plots show the wire temperature rise recorded for benchmarks ammp and applu for the data bus in 130 nm and 45 nm technology nodes over a simulation interval of one billion committed instructions for each benchmark.                                                                                                                                                                                                                                        | 81         |

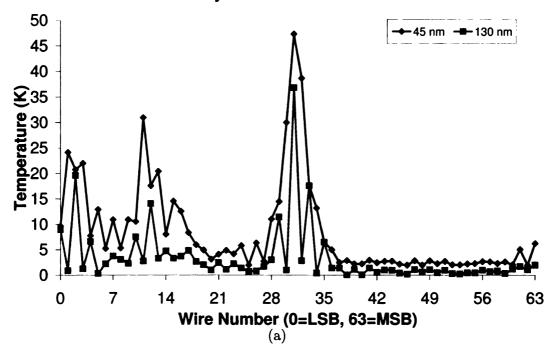

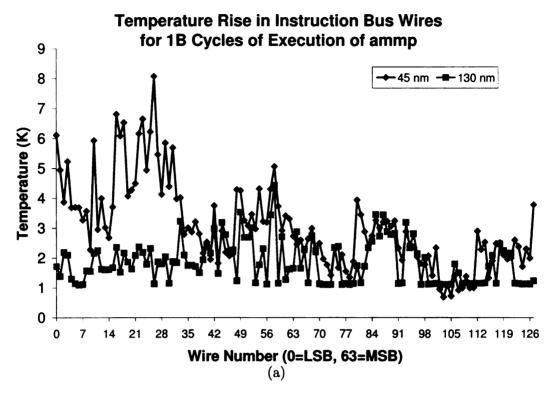

| 3.12 | Plots show the wire temperature rise recorded for integer benchmarks gcc and gzip for the instruction bus in 130 nm and 45 nm technology nodes over a simulation interval of one billion committed instructions for each benchmark.                                                                                                                                                                                                                           | 82         |

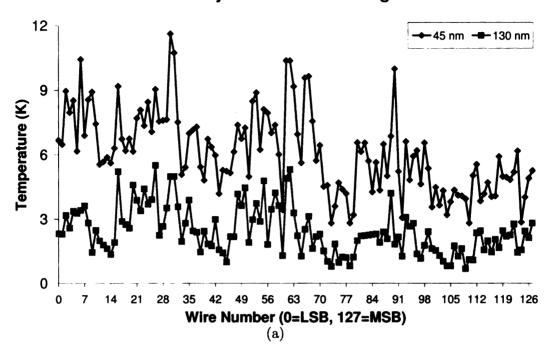

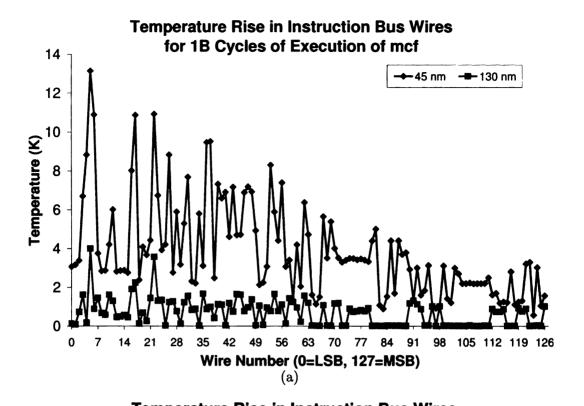

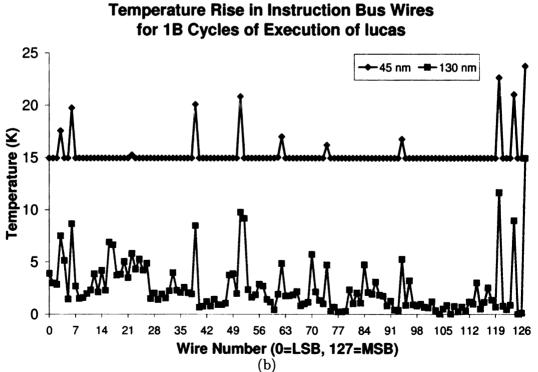

| 3.13 | Plots show the wire temperature rise recorded for integer benchmarks mcf and lucas for the instruction bus in 130 nm and 45 nm technology nodes over a simulation interval of one billion committed instructions for each benchmark.                                                                                                                                                                                                                          | 83         |

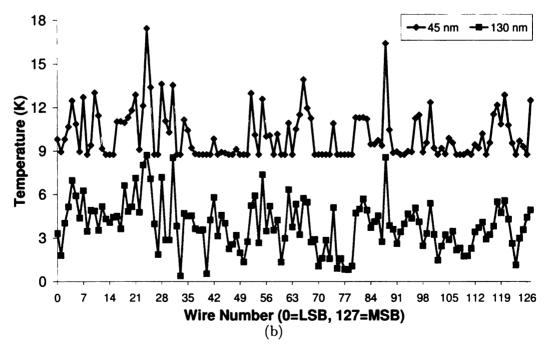

| 3.14 | Plots show the wire temperature rise recorded for integer benchmarks ammp and applu for the instruction bus in 130 nm and 45 nm technology nodes over a simulation interval of one billion committed instructions for each benchmark.                                                                                                                                                                                                                         | 84         |

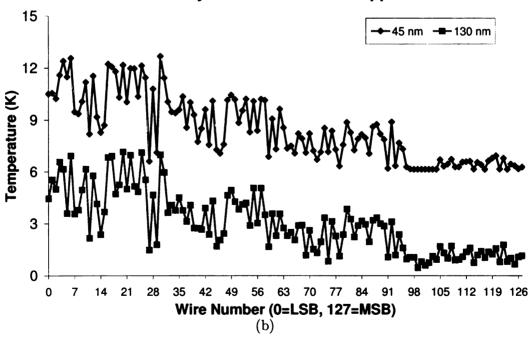

| 3.15 | A three-dimensional plot showing spatial and temporal variations in wire temperature for the lower-order 32 bits of the load/store data bus for the gcc benchmark.                                                                                                                                                                                                                                                                                                                                                                                                   | 85  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

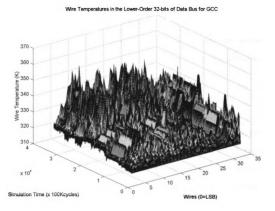

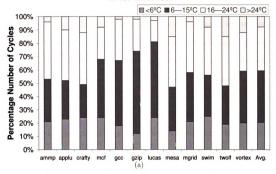

| 3.16 | Frequency distribution of maximum wire temperature gradients for 130 nm and 45 nm processor wires                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 88  |

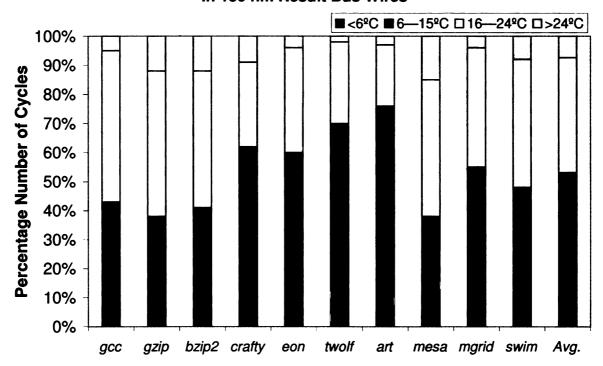

| 4.1  | Distribution of maximum wire temperature gradients in result bus wires for the 130 nm processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 100 |

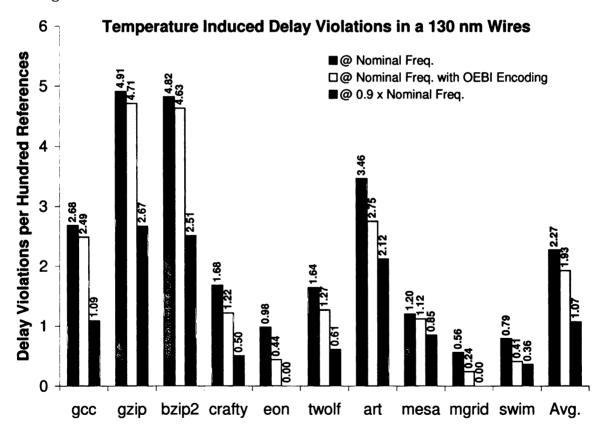

| 4.2  | The number of temperature-induced violations per hundred bus references occurring across ten benchmark programs in a 130 nm processor.                                                                                                                                                                                                                                                                                                                                                                                                                               | 101 |

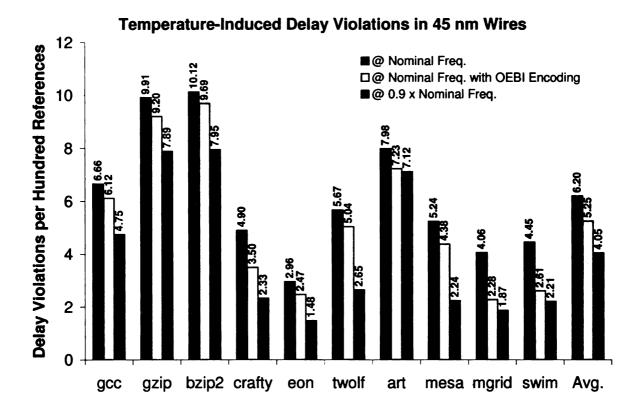

| 4.3  | The number of temperature-induced violations per hundred bus references occurring across ten benchmark programs in a 45 nm processor.                                                                                                                                                                                                                                                                                                                                                                                                                                | 102 |

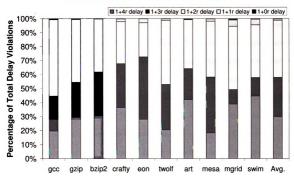

| 4.4  | This plot shows the frequency of occurrence of five different crosstalk conditions on the bus. See Section 4.3.2 and Table 2.1 for an explanation of these crosstalk conditions. The crosstalk condition determines the actual propagation delay without considering thermal effects                                                                                                                                                                                                                                                                                 | 103 |

| 4.5  | Figure shows the percentage of temperature-induced delay violations that correspond to a given crosstalk condition                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 104 |

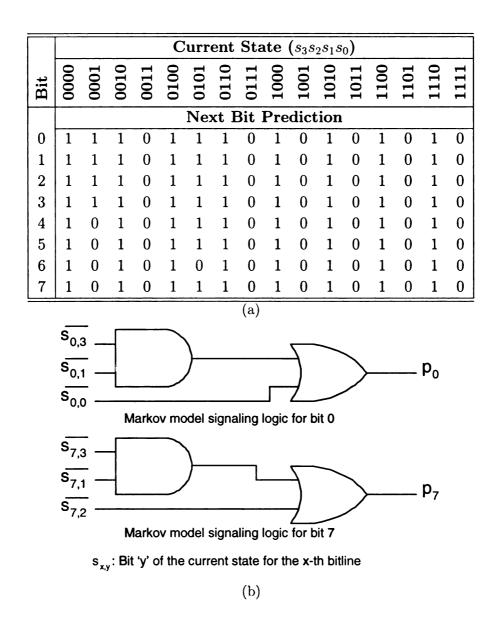

| 5.1  | Markov model-based signaling technique. (a) A 4-bit prediction table for the Markov model for bits 0–7 of the data bus obtained by analyzing training set benchmarks. Depending on which bits are selected for Markov model signaling, the corresponding row of the table can be translated to hardware using logic minimization tools. (b) Examples of sending end hardware that would be required for 2 bits (0 and 7) assuming these are chosen to be signaled using the mm scheme. As can be seen, the logic overhead required for mm signaling is very minimal. | 124 |

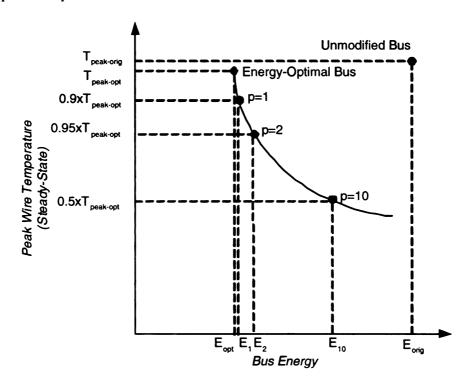

| 5.2  | Sample peak wire temperature versus bus energy trade-off curve. The thermal optimization steps can be used to obtain curves similar to the one shown here.                                                                                                                                                                                                                                                                                                                                                                                                           | 133 |

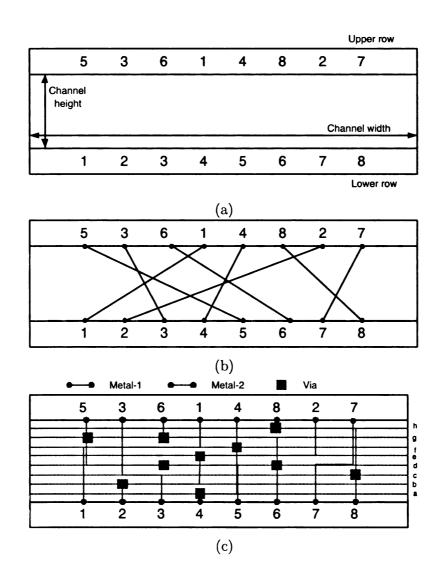

| 5.3  | Routing strategy and overheads for re-ordering. (a) Definition of the routing channel. (b) Matching diagram showing ten crossing points. (c) Two-layer routing strategy using eight horizontal tracks and ten vias.                                                                                                                                                                                                                                                                                                                                                  | 135 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 5.4  | Transition Densities for the 13 integer SPEC CPU2000 Benchmarks for 64-bit Data Bus.                                                                                                                                                                                                                                                                                                               | 139 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

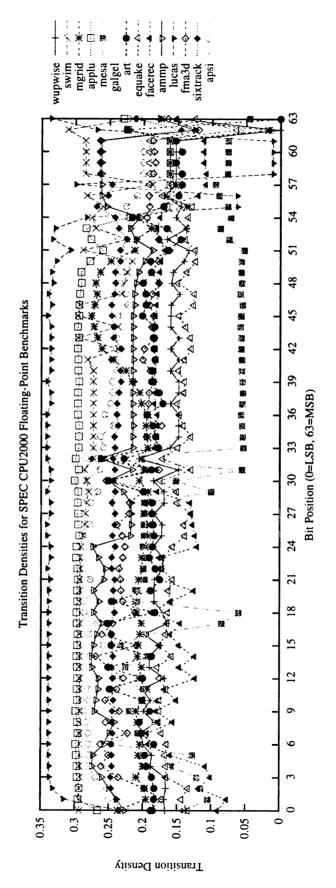

| 5.5  | Transition Densities for the 13 floating-point SPEC CPU2000 Benchmarks for 64-bit Data Bus                                                                                                                                                                                                                                                                                                         | 140 |

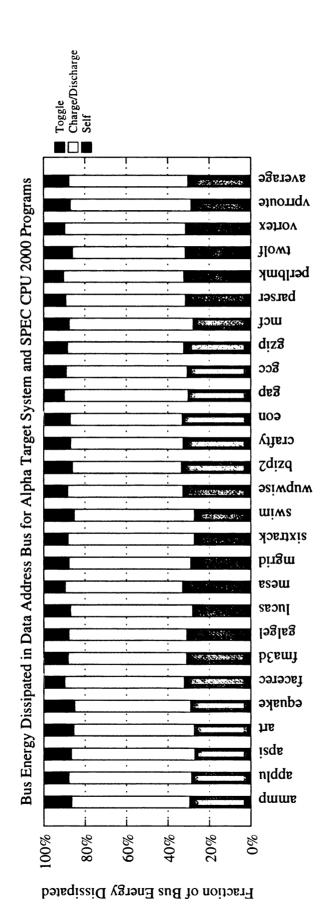

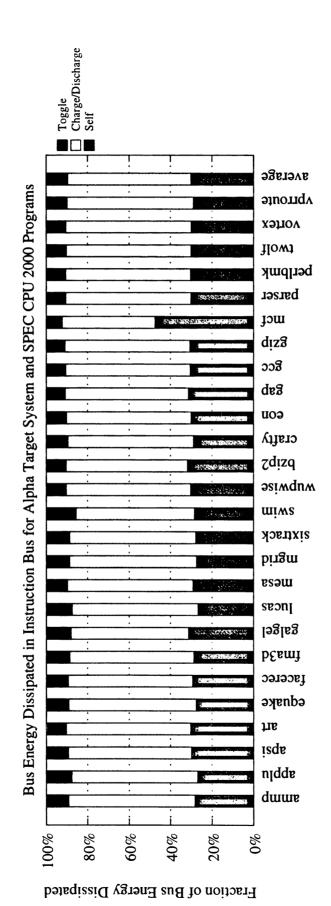

| 5.6  | Fraction of bus energy dissipated in self and coupling (charge/discharge+toggle) transitions for 32-bit data address bus in the Alpha 21264 target system while running SPEC CPU2000 programs                                                                                                                                                                                                      | 141 |

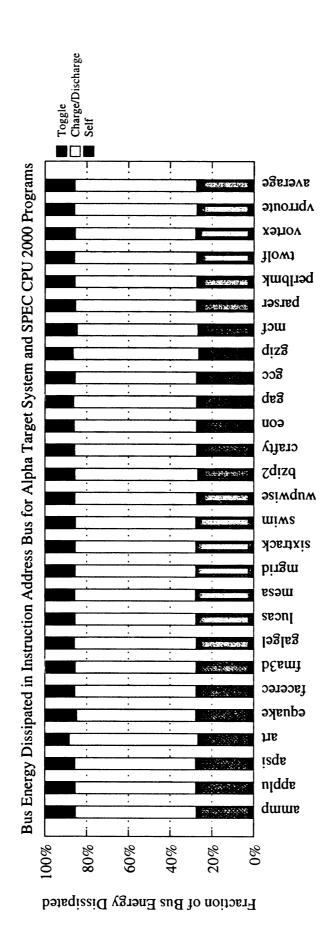

| 5.7  | Fraction of bus energy dissipated in self and coupling (charge/discharge+toggle) transitions for 32-bit instruction address bus in the Alpha 21264 target system while running SPEC CPU2000 programs                                                                                                                                                                                               | 142 |

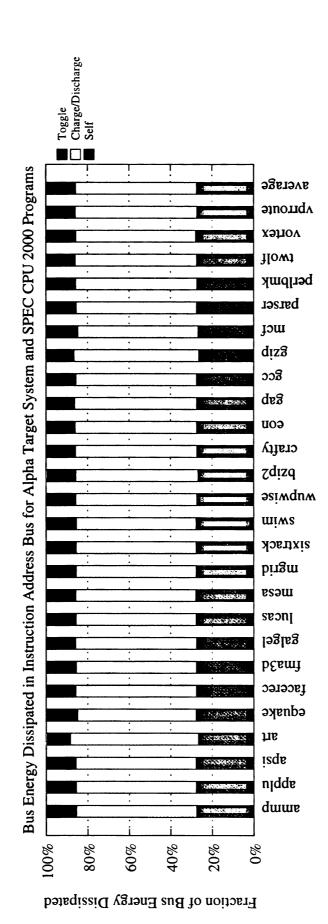

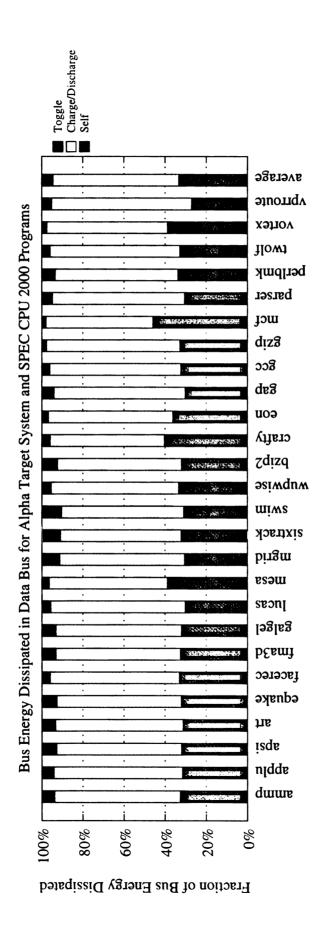

| 5.8  | Fraction of bus energy dissipated in self and coupling (charge/discharge+toggle) transitions for 64-bit data bus in the Alpha 21264 target system while running SPEC CPU2000 programs.                                                                                                                                                                                                             | 143 |

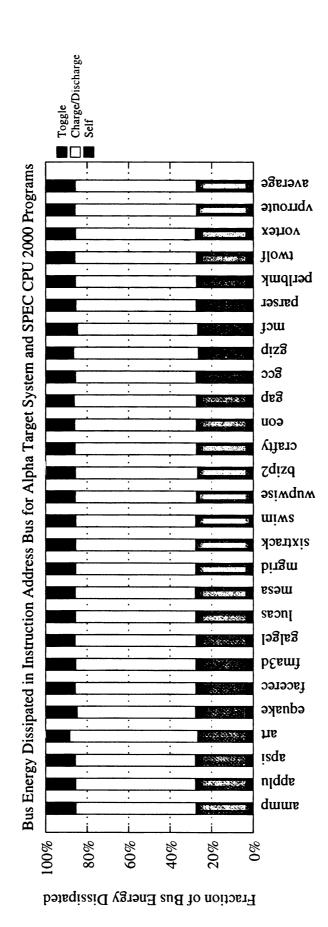

| 5.9  | Fraction of bus energy dissipated in self and coupling (charge/discharge+toggle) transitions for 128-bit instruction bus in the Alpha 21264 target system while running SPEC CPU2000 programs                                                                                                                                                                                                      | 144 |

| 5.10 | Energy dissipation results for general-purpose design for the 64-bit data bus. Statistics collected on 13 training set benchmarks were used to obtain the optimal static encoding schemes. These were tested on 13 other (test set) benchmarks. Average energy reductions are MES: 7.81%, MEBO: 11.91%, and SBOS: 20.04%                                                                           | 146 |

| 5.11 | Energy dissipation results for general-purpose design for the instruction bus. Average energy reductions are MES: 10.96%, MEBO: 19.85%, and SBOS: 38.78%.                                                                                                                                                                                                                                          | 147 |

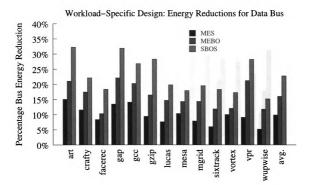

| 5.12 | Energy dissipation results for workload-specific design of the 64-bit data bus. Statistics collected for SimPoint samples from 13 training set benchmarks were aggregated and used to obtain the optimal static encoding schemes. These were then tested on a non-overlapping sample from the same set of benchmarks. The average energy reductions are MES: 9.73%, MEBO: 15.97%, and SBOS: 22.79% | 149 |

| 5.13 | instruction bus. The average energy reductions are MES: 10.43%, MEBO: 21.25%, and SBOS: 40.77%.                                                                                                                                                                                                                                                                                                                                                                                                        | 150 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

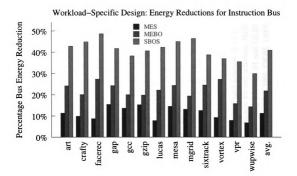

| 5.14 | Energy reduction results for program-specific design. Statistics collected for SimPoint samples of each benchmarks was used to obtain the optimal static encoding schemes specific to that benchmark for our schemes, MES, MEBO, and SBOS. These were then tested on the same sample. Results for dynamic encoding schemes BI and OEBI proposed in previous work are also shown. The average energy reductions for the data bus are BI: 4.19%, OEBI: 1.58%, MES: 19.7%, MEBO: 23.25%, and SBOS: 30.2%. | 151 |

| 5.15 | Energy reduction results for program-specific design. Statistics collected for SimPoint samples of each benchmarks was used to obtain the optimal static encoding schemes specific to that benchmark for our schemes, MES, MEBO, and SBOS. These were then tested on the same sample. Results for dynamic encoding schemes BI and OEBI proposed in previous work are also shown. The average results for the instruction bus are BI: 2.63%, OEBI: 5.32%, MES: 21.7%, MEBO: 32.1%, and SBOS: 52.1%.     | 152 |

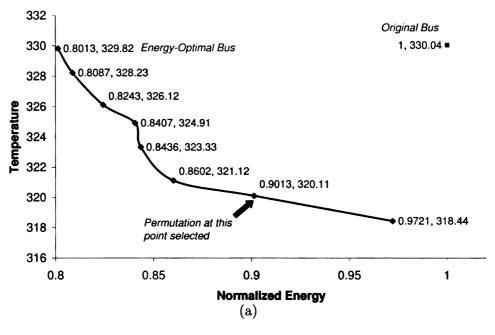

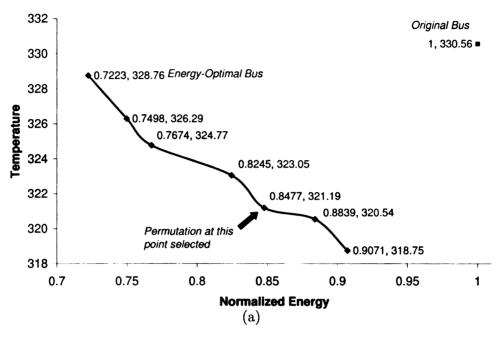

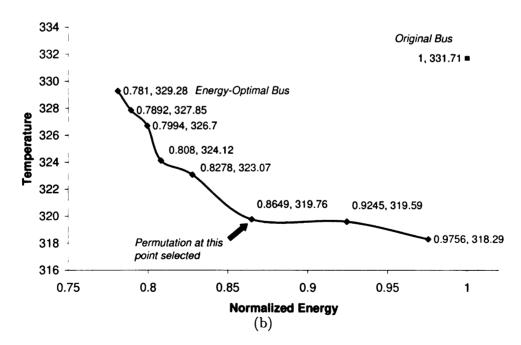

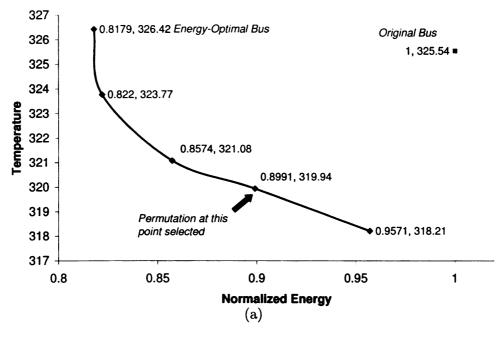

| 5.16 | Energy vs. temperature trade-off curves. Plots show the energy vs. temperature tradeoff curves obtained for the data bus for ammp and crafty. The permutation selected for each benchmark was the one that resulted in bus energy reduction closest to $0.5(1 - \frac{E_{opt}}{E_{orig}})$ compared to the original bus                                                                                                                                                                                | 155 |

| 5.17 | Energy vs. temperature trade-off curves. Plots show the energy vs. temperature tradeoff curves obtained for the data bus for eon and gcc.                                                                                                                                                                                                                                                                                                                                                              | 156 |

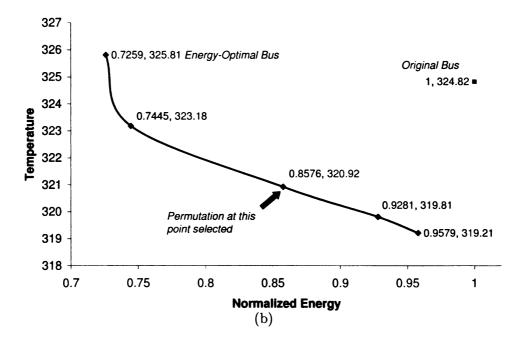

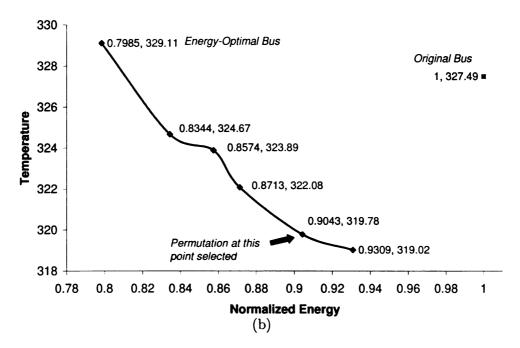

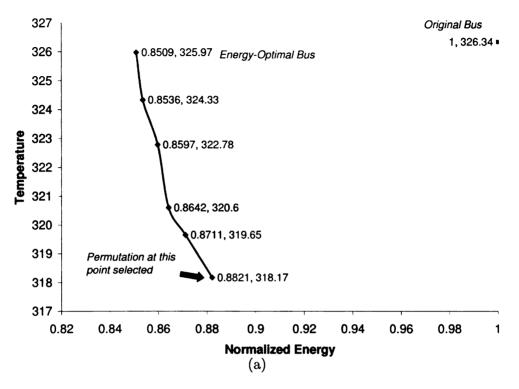

| 5.18 | Energy vs. temperature trade-off curves. Plots show the energy vs. temperature tradeoff curves obtained for the data bus for gzip and lucas                                                                                                                                                                                                                                                                                                                                                            | 157 |

| 5.19 | Energy vs. temperature trade-off curves. Plots show the energy vs. temperature tradeoff curves obtained for the data bus for mesa and mgrid                                                                                                                                                                                                                                                                                                                                                            | 158 |

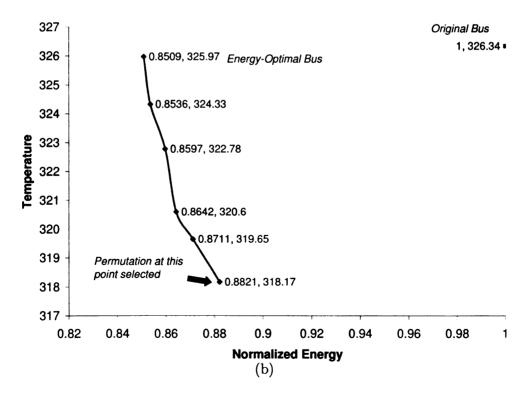

| 5.20 | Energy vs. temperature trade-off curves. Plots show the energy vs. temperature tradeoff curves obtained for the data bus for swim and twolf                                                                                                                                                                                                                                                                                                                                                            | 159 |

| 6.1 | Three-bit crosstalk analyzer truth table and circuit. (a) Truth table showing only the ON-set. "-" indicates a don't care input. (b) Logic circuit implementing the truth table                                                                                       | 166 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

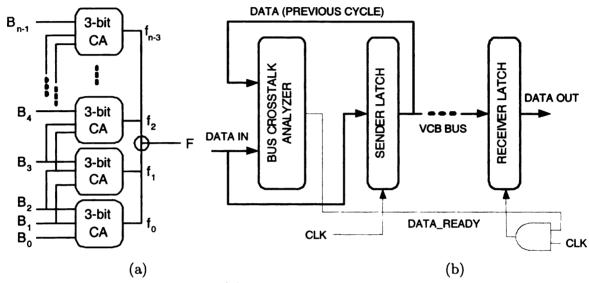

| 6.2 | Variable cycle bus. (a) Complete bus crosstalk analyzer for an <i>n</i> -bit bus. (b) Sender and receiver logic for VCB                                                                                                                                               | 168 |

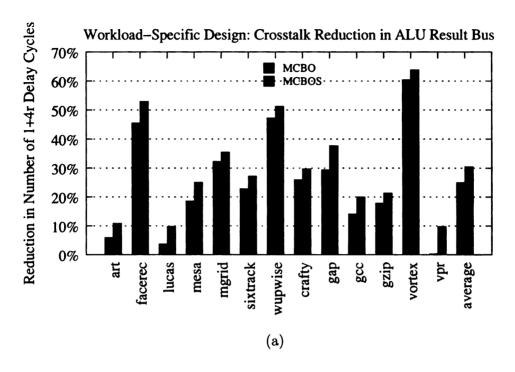

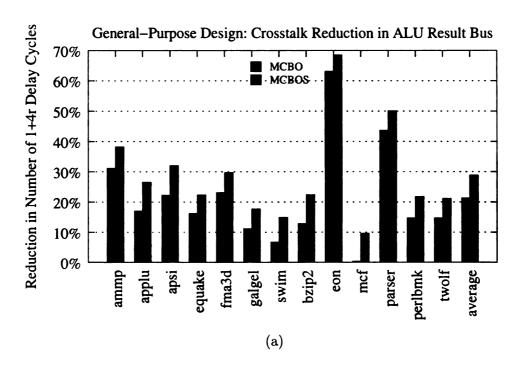

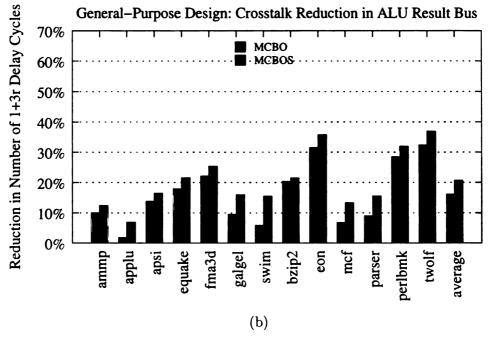

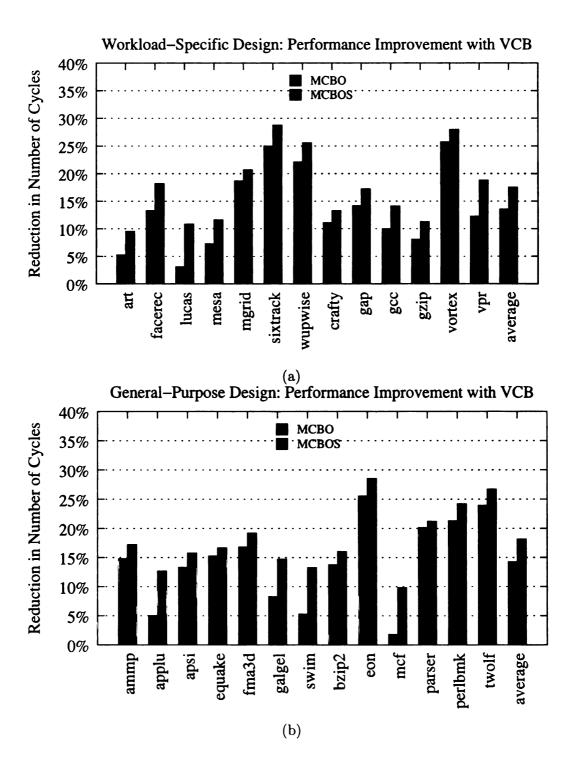

| 6.3 | Crosstalk reduction results for workload-specific design of the 64-bit ALU result bus. (a) Average reductions in number of 1+4r delay cycles. For MCBO: 24.89% and MCBOS: 30.61%. (b) Average reductions in number of 1+3r cycles. For MCBO: 19.21% and MCBOS: 23.42% | 174 |

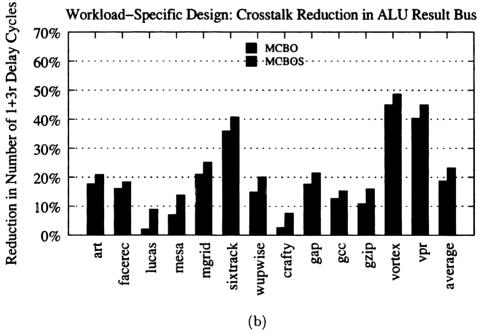

| 6.4 | Crosstalk reduction results for general purpose design of the 64-bit ALU result bus. (a) Average reductions in number of 1+4r delay cycles. For MCBO: 21.22% and MCBOS: 29.35%. (b) Average reductions in number of 1+3r cycles. For MCBO: 16.77% and MCBOS: 20.29%   | 175 |

| 6.5 | Reduction in the number of cycles taken to transmit the information with MCBO and MCBOS applied to the result bus. (a) Workload-specific optimization. (b) General-purpose optimization                                                                               | 176 |

#### SELECTED LIST OF SYMBOLS

- $C_{i,k}$  Thermal capacitance of the  $k^{th}$  subsegment of the  $i^{th}$  wire

- $\mathcal{R}_{i,\,k}$  Thermal resistance along the heat transfer path of the  $k^{th}$  subsegment of the  $i^{th}$  wire

- $\theta_0$  Ambient temperature inside the computer box (45°C)

- $\varepsilon_r$  Relative permittivity of dielectric

- $C_0$  Capacitance of minimum size inverter in fF

- $c_{i,\,i\,\pm\,1}$  Adjacent coupling capacitance per unit length in pF/m

- $c_{i,j}$  Coupling capacitance between line i and any other line j,  $i \neq j$

- $c_{line}$  Self/Area capacitance of wire per unit length in pF/m

- $f_{clk}$  Clock frequency

- $k_{ild}$  Thermal conductivity of dielectric

- $R_0$  Resistance of minimum size inverter in  $k\Omega$

- $r_{line}$  Resistance of wire per unit length in k $\Omega/m$

- $t_{ild}$  Thickness of the inter-layer dielectric

- $t_i$  Thickness of wire i

- $t_p$  End-to-end propagation delay of a wire

- $V_{DD}$  Supply voltage

- $w_i$  Width of wire i

# CHAPTER 1

# INTRODUCTION AND OVERVIEW

High-speed systems and circuits are increasingly facing the limitations posed by shrinking physical dimensions of transistors and their interconnections [8]. As circuits become denser, smaller transistors naturally speed up. But interconnects, in general, do the reverse and introduce delays that reduce or even cancel the speed gains due to smaller transistors. The problems due to interconnects are exacerbated by the fact that parasitic resistance, inductance, and capacitance (RLC) effects increase as wires scale to smaller dimensions, which in turn aggravates delay, power consumption, and cause signal integrity/reliability problems. Thus, on-chip interconnect design has been recognized as one of the most important challenge to address in nanometer-scale integrated circuits [9, 10].

# 1.1 Interconnect Scaling Trends: Delay, Power, Temperature, and Reliability

According to the data available from the international technology roadmap for semiconductors (ITRS) documents, the intrinsic gate delay has improved ten times, from 10 ps to 1 ps in the 20 years between 1980 and 2000. However, in the same period of time, the interconnect delay in a 1 mm line degraded 100 times, from 1 ps to 100 ps [1]. This growing disparity between gate and interconnect delays is also highlighted in Figure 1.1 for current and future technologies [3]. The figure shows that while local interconnect delays scale with gate delays, global interconnect delays do not. Such trends have forced costly performance compromises, like the allocation of two out of twenty pipeline stages for communication in the Pentium-4 microprocessor [11].

Figure 1.1. Gate and interconnect delay scaling for current and future nanometerscale technologies. Local interconnects scale with gate delay whereas global interconnect delays do not [3].

Interconnects are also responsible for about 50% of the power dissipation, as shown by results from studies on a 130 nm Intel microprocessor [4]. Figure 1.2 shows the distribution of power dissipation by the type of the net/wire. As can be seen, global signal lines account for 34% of the total interconnect power dissipated and hence 21% of the total dynamic (switching-related) power dissipation at 130 nm.

Due to increased Joule heating in the global wires, their temperatures are also increasing alarmingly. The spatial temperature distributions along the vertical direction

Figure 1.2. Interconnect power dissipation due to global and local wires. Global lines are responsible for 21% of total dynamic power dissipation at 130 nm [4].

from the Silicon (Si) substrate obtained using finite element models and simulations are shown in Figure 1.3 [5]. This analysis assumed that all wires in the interconnect stack carried currents with maximum rated current density for that technology which represents an extreme worst case. Nevertheless, the results show how temperatures will be distributed across interconnect layers. It can be observed that as technology scales down, the temperature gradient between the top metal lines and the substrate becomes larger. Global metal lines were found to be the hottest in all technologies using this worst-case analysis, with temperatures reaching as much as 209°C in 45 nm technology [5]. For the 35 nm node, the temperature gradient is smaller than that for the 50 nm node due to the larger fraction of metalization (Cu) layers compared to inter-layer dielectric (ILD) layers, an artifact of the ITRS scaling scenario that was used for this analysis. It should be noted that the total height of the (Cu+ILD)

layers decreases as scaling continues, due to the smaller vertical dimensions of wires and insulators despite increase in number of metal layers. It can also be observed that the maximum chip temperature occurs for the long global wires, which are most prone to electromigration failures and also give rise to highest RC delays. This has important implications for both reliability and performance.

Figure 1.3. Projected wire temperature rise in multi-layer interconnects for various technologies under worst-case conditions. Global metal lines will be the hottest, with temperatures expected to reach as much as 209°C in 45 nm technology [5].

# 1.2 Material, Process, and Architectural Advances

Many methods, such as utilizing Cu and low-k insulators [12–14], short-wire architectures [15,16], on-chip networks [17], optical interconnects [18], and three-dimensional interconnect structures [19,20] have been suggested to help alleviate the impact of interconnect scaling on current and future nanometer-scale fabrication. The pros and

cons of these techniques are discussed next.

Material and process enhancements: Copper interconnects in high speed microprocessors were introduced by IBM in its 400 MHz PowerPC750 processor. Although the resistivity of Copper is 40% less than that of Aluminum, the percentage of performance improvement from using the former is limited to about 15% [14]. The thickness and resistivity of the Tantalum (Ta) liner, used in the dual-damascene process for Copper electrodeposition, also limit the performance advantage of Copper interconnects. Low-k dielectrics also help improve chip performance. For example, the performance of a metal wire improves 25% for 0.25  $\mu$ m technology using a k=2.5 dielectric material compared to conventional silicon dioxide, which has k=3.9. However, the use of Copper metal and low-k dielectrics are known to aggravate thermal issues in interconnects and cause reliability problems, during both fabrication and chip lifetime [21].

Novel architectures: Short-wire architectures such as systolic arrays can be employed to overcome some of the problems imposed by long global interconnects [16]. Although these architectures are not applicable to all microprocessors, they can be useful in specific applications, such as pattern recognition, multiprocessor systems, and arithmetic computation. On-chip networks can be used instead of global interconnects to reduce the global interconnect congestion [22]. Since most of the global wires are not utilized in every clock cycle, it is more efficient to send packets over a global network rather than signals in global wires. However, this requires a completely new architecture, tools, and design methodology different from conventional microprocessors.

Optical interconnections and 3D integration: It has been shown that the optical interconnections have higher bandwidth and consume lesser power for long-distance communication compared to electrical interconnections [23]. However, because of incompatibility with standard CMOS technology, optical interconnects have not been widely deployed in current microprocessors. The primary application has been restricted to clock distribution networks in some designs [24]. Three-dimensional interconnection schemes are also expected to significantly reduce global wiring requirements and have a significant impact on reducing interconnect delay and power [25]. However, vertical pitch limitations resulting from alignment tolerances in the bonding of wafers [26] and heat removal capacity limitations [27] are some of the problems limiting the use of three-dimensional architectures.

# 1.3 Impact of Interconnects on Architecture and VLSI

Interconnect-related problems have affected chip design to such an extent that product roadmaps of almost all chip design companies have been drastically re-drawn as it is becoming evident that high-speed processors—with clock frequencies exceeding 10 GHz—are no longer economically viable, due to restrictions imposed by power, temperature, and reliability [28–30]. The impact of interconnect scaling and power and performance issues affects the very first architectural design decisions of today's processors [31,32].

### 1.3.1 Wire Delay

Processor clock speeds have increased continuously, due to faster transistors and also due to deeper pipelines. However, since global wire delays—for example, delay of register bypass wires—scale much slower than transistor delays, deeper superscalar pipelines have experienced increased latencies and a significant degradation in instruction throughput. Several studies have pointed out rising wire delays dictate that deeper pipelines will not perform better than shallower ones in future technologies and also conclude that superscalars do not have sufficient parallelism to tolerate the relative rise in wire delays [33, 34]. Hence the industry trend toward multi-core and multithreaded architectures [35].

Figure 1.4. Pipeline stages and loops in a typical out-of-order processor. More frequently used loops like fetch, LSQ, and bypass are affected strongly by wire delay.

We briefly examine next why wire delay trends affect architectural decisions. An out-of-order superscalar pipeline is composed of two in-order half-pipelines, called the *front-end* and *back-end*, connected by the issue queue. Figure 1.4 shows this configuration and the various loops in the pipeline [35]. Wire delay affects many of

these loops significantly as discussed next. The fetch loop is due to the fact that the current program counter (PC) is used to predict the next PC. The delay of this loop includes the instruction bus and cache delays. The rename loop is due to the dependence between a previous instruction assigning a rename tag and a later instruction reading the tag and the issue loop is due to the dependence between the producer and wakeup of a consumer instruction. The rename and issue loop delays are sensitive to the delay on the tag lines. The load misspeculation loop is due to use of speculation and the need for load-miss replay. The load/store queue (LSQ) loop is due the dependence between a previous store and a later load to the same address and includes the load/store bus and data cache delays. The various bypass loops—EX/EX, EX-MEM, and Writeback-EX—are all affected by the wire delays on the ALU result bus. Also, the more frequently a loop is used, the higher its impact on performance. The fetch, rename, issue, and bypass loops are all fairly frequent and hence have the highest impact. The load misspeculation and branch misprediction loops that are used only upon load misses and branch mispredictions, respectively, are relatively less frequent and have lesser impact.

## 1.3.2 Power and Temperature

Power has become a first-class constraint in the design of nanometer-scale ICs. Figure 1.5 shows the trend observed in the power dissipation of Intel microprocessors [6]. In 2001, it was predicted that with the scaling rates at that time, the power density in microprocessors will reach that of the Sun by 2015, following an almost exponential trend [6]. Since then various steps have been taken to reduce power dissipation in logic and memories with techniques at various levels of abstraction. These have resulted

in reducing the trend to a linear one, as shown by the dotted line in Figure 1.5.

Figure 1.5. Power dissipation in Intel processors showing an exponential trend [6]. Since 2001, low-power and power management techniques that have been used widely in microprocessors and have helped slow down the trend somewhat.

Among the three different sub-systems of a high-performance processor—

computation, storage, and communication—the communication or interconnect subsystem, which carries address, instruction, data, and control signals, is still responsible for a bulk of the on-chip power dissipation as discussed earlier, in part due

to interconnect scaling trends. With increasing interconnect power dissipation, wire

temperatures rise as a result of the Joule effect, wire resistance increases due to

temperature-dependent resistivity forcing performance to degrade further, and wire

reliability decreases sharply due to electromigration-induced breakage. Even with the

advent of multi-core processors, clock frequencies and datapath widths have continued

to increase and hence, all of the above effects are bound to worsen further. Hence,

interconnect power dissipation and temperature remains one of the primary issues facing microarchitects and VLSI designers.

Popular low-power and power-management techniques like fine-grained clock gating and power gating can also significantly affect on-chip temperature profiles by creating localized hot spots and/or temperature gradients on the chip. These gradients cause delay variabilities, setup and hold time violations and, in the worst case, failure of interconnects that are routed across regions with varying temperatures. Designing for these issues is almost impossible because accurate techniques to estimate temperature gradients in interconnects are currently unavailable. Thus, study of the thermal impact of architectural techniques is also becoming important.

## 1.3.3 Computer-Aided Design Tool Requirements

In conventional ASIC design, signal and power integrity were checked in later stages of the design cycle and the design was modified if these checks were found to be unsatisfactory. However, with explosion in the number of transistors and highly-complex designs in nanometer-scale technologies, iterating between upstream (architecture or high-level) design changes and layout to achieve design closure has becoming increasingly futile, leading to longer time-to-market schedules and higher design costs [9]. The design-productivity gap, exemplified by the lack of proper CAD tools to identify and correct issues at an early stage, exacerbates this problem. While the push toward ever-higher performance still drives the semiconductor industry, there is growing awareness now that winning designs need to balance multiple objectives: high performance, low power, low cost, robustness (noise immunity), and reliability. As such, it is becoming imperative to: (1) model interconnect-related effects accurately and

efficiently for different system architectures (superscalar, multi-core, and network-on-chip) and fabrication technologies (130 nm, 90 nm, etc.) and (2) design the interconnect system, at an early stage, to alleviate or mitigate these effects without incurring unsustainable performance, energy, and/or area/cost overheads.

# 1.4 Drawbacks in Existing Techniques

Next, we discuss some drawbacks of existing models and design techniques for signal interconnects. First, almost all existing work addressing signal interconnect analysis, design, and optimization is not activity-aware, i.e., such interconnect models and design techniques are not developed with an accurate knowledge of the characteristics of data that is transmitted on these interconnects. An average wire switching factor—such as 0.15 suggested in [36]—is used to estimate energy dissipation, wire temperature, delay impact, and/or reliability impact [37, 38]. As such, these average estimates lead to over-design because switching activity in interconnects is actually information and time dependent. It depends on the type of information (address, instruction, data, or control) being transmitted because the information type influences switching activity factors; for example, the activity factor is expected to be higher for data and instruction streams since they are more random in nature than addresses. It varies with time too because, during execution of most typical programs, there are substantial periods when a bus may remain idle; for example, when there are no level-one (L1) cache misses, the bus connecting to level-two (L2) cache will remain idle. These idle cycles help bring down wire temperatures and hence, may reduce wire delay and electromigration impact. Hence, to facilitate interconnect design that can be tuned to the requirements of different architectures, activity-aware modeling and design optimization techniques are necessary.

Second, as mentioned earlier, increasing the number of iterations between high-level design and physical layout to achieve design closure, has become exorbitantly costly, time-consuming, and impractical in nanometer designs. Hence, growing emphasis is being placed on making accurate early-stage design decisions obtained using microarchitecture-level simulations on benchmark programs. Interconnect models that have been built into existing execution-driven simulators lack the detail needed to accurately estimate the impact of interconnect power dissipation, temperature, and related effects, since many not consider the influence of wire coupling and thermal heat dissipation paths. For example, the amount of energy dissipated due to the parasitic coupling capacitance between wires is much greater than energy dissipated due to the area capacitance. Similarly, thermal coupling or heat transfer through the inter-metal dielectric occurs between adjacent wires, affecting temperatures in both wires.

# 1.5 The Need for Activity-Aware Design

Existing techniques that target bus energy and crosstalk reductions, perform well only when patterns that are transmitted on the bus are randomly distributed in time. However, this is rarely the case in actual microprocessor buses. Information transmitted on these buses show high degrees of correlation across programs as well as across sections of the same program, due to the presence of temporal, spatial, and value localities. Temporal locality describes the likelihood that a recently-referenced

item will be referenced again soon, while spatial locality describes the likelihood that a close neighbor of a recently-referenced item will be referenced soon. Value locality refers to the likelihood of a previously-seen value recurring repeatedly in the information stream.

Address, instruction, and data streams in microprocessor buses exhibit substantial amounts of temporal and spatial locality due to the reasons discussed next. Instruction addresses issued by the processor to the L1 cache are typically sequential, except when branches or jumps occur and even then the target addresses are not typically very far away from the last address. This is the reason why many instruction sets use PC-relative addressing with shorter-than-full-word-size offsets for branch and jump instructions. Data addresses issued by the processor are also exhibit these localities primarily because of scanning of data arrays in loops that are placed in contiguous memory locations.

The dynamic instruction stream executed by a processor corresponds to instruction addresses issued by fetch unit, and hence instructions exhibit the same temporal and spatial locality as instruction addresses. Also, not all instructions, instruction sequences, opcodes, register operands, and immediate constants are present equally frequently in the dynamic instruction mix, leading to more predictability in the instruction stream. The reasons for the presence of such redundancies are that all programs share certain basic characteristics: procedures and procedure calls, branches every few instructions—typically every six instructions [39], and loops and if-then-else clauses that lead to repetitive instruction sequences.

Data buses in the processor, such as load/store and ALU result buses, also exhibit temporal and spatial locality, although to a lesser extent than addresses and instruction buses. There is an additional element of redundancy present in the magnitude of values communicated by these buses and stored in registers, data caches, and/or CAM structures in the processor core. This redundancy is due to the fact that for any given type of data—character, integer, floating-point, etc.—not all values are equally likely. For instance, many programs do not tend to use the entire range of integer values possible, but rather the values used tend to be concentrated around certain values, especially, zero. For such small magnitude two's complement numbers, most high order bits of the data bus are likely to be either all zero (positive) or all one (negative) due to sign extension. The concept of value locality also adds to the redundancies present in data buses. For example, the number of times each static load (or store) instruction retrieves a value from (or writes to) memory that matches a previously seen value, is quite high. Studies have shown that this value is around 50% for most superscalar processors running standard benchmark applications [40].

The presence of temporal, spatial, and value localities in information streams opens opportunities for activity-aware design of high-performance buses, i.e., design that is tailored to the unique characteristics of different types of data that are transmitted on these buses, as well as to the typical applications that are executed on the processor. Such design can be achieved with the following steps: (1) profile the information transmitted on target buses using cycle-accurate microarchitecture-level simulators for a representative workload, (2) identify opportunities by correlating, for example, the number of self and coupling transitions with objective function (bus energy, temperature, crosstalk, etc.), (3) and design techniques that minimize the value of the objective function. Although, the technique is designed using a representative workload, it is likely to work well for any real application in the same

domain due to the similarities in program characteristics. In fact, computer architecture continue to use similar methodologies to design efficient branch, load-value, and other prediction-based techniques to improve instruction-level parallelism in modern superscalar processors.

## 1.6 Our Contributions

As presented earlier, accurate modeling and cost-effective design of global signal interconnects is a critical issue in current and future nanometer-scale design. Since interconnect performance (wire delay) and energy dissipation depend closely on switching

characteristics of the data stream, activity-aware modeling and design approaches

are important. Furthermore, the introduction of Cu and low-k dielectrics exacerbate

problems such as wire self-heating which need to be modeled, along with the impact

of temperature on wire delay variability. Finally, newer design techniques are needed

to deal with rising interconnect power dissipation and temperature since existing

techniques are not effective in most real architectures, workloads, and applications.

The objective of this research is to provide a methodology to model and design signal interconnects in nanometer-scale ICs and address power, temperature, and performance concerns during early-stage design. To accomplish this goal, four research tasks were identified and novel contributions are made in each.

# 1.6.1 Activity-Aware Design Methodology

Our research is perhaps the first attempt that proposes and examines activity-aware design techniques for global signal buses. Existing techniques rely on worst-case estimates to design high-performance buses, resulting in overly-pessimistic energy, temperature, and clock cycle time estimates. Due to lack of accurate models suitable for early stage design exploration, interconnect design is done late in the design cycle, offering very limited opportunities to optimize the architecture for performance, power, and cost. In contrast, the methodology we propose examines typical applications, collects statistics for different types of data, and optimizes the design of target buses, all using early stage simulation. Thus interconnect design can be completed early in the design cycle and it can be used as a parameter in design space exploration.

#### 1.6.2 Accurate Energy, Temperature, and Delay Modeling

We introduce accurate modeling techniques to help estimate the impact of activity-dependent interconnect energy dissipation, wire temperature rise due to Joule heating and delay variation due to temperature, using a microarchitecture-level simulator. In addition to self capacitance, our model incorporates the effects of capacitive coupling between adjacent as well as non-adjacent pairs of wires and repeater insertion on switching energy, the effect of lateral heat transfer between adjacent wires to estimate wire temperatures, and also estimates wire temperature gradients and its impact on wire delay, all of which were not available in earlier models. We estimate from simulations using our model for 130 nm technology node that, during the time interval taken to commit one billion instructions in the pipeline, high performance bus wire temperatures rise by 10-37°C for various SPEC CPU2000 benchmarks. This is solely due to Joule heat dissipated due to wire switching activities. In a future 45 nm technology node, wire temperature rise for the same set of benchmarks and simulation sample was found to be between 20-58°C. We observed that instruction and data