THS

# LIBRARY Michigan State University

This is to certify that the thesis entitled

# A COMPACT FULLY ON-CHIP IMPEDANCE SPECTROSCOPY SYSTEM

presented by

Daniel J. Rairigh

has been accepted towards fulfillment of the requirements for the

M.S. degree in Electrical Engineering

Major Professor's Signature

May 16 700 7

MSU is an affirmative-action, equal-opportunity employer

PLACE IN RETURN BOX to remove this checkout from your record.

TO AVOID FINES return on or before date due.

MAY BE RECALLED with earlier due date if requested.

| DATE DUE | DATE DUE | DATE DUE |

|----------|----------|----------|

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

6/07 p:/CIRC/DateDue.indd-p.1

### A COMPACT FULLY ON-CHIP IMPEDANCE SPECTROSCOPY SYSTEM

Ву

Daniel J. Rairigh

### **A THESIS**

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

MASTER OF SCIENCE

Department of Electrical Engineering

2007

#### **ABSTRACT**

#### A COMPACT FULLY ON-CHIP IMPEDANCE SPECTROSCOPY SYSTEM

By

#### Daniel J. Rairigh

Impedance Spectroscopy (IS) is a powerful technique for characterizing materials and interrogating many sensors, particularly within evolving nanotechnologies. Applications for this technique range from DNA identification to trace vapor detection. The instrumentation to support these emerging applications has, however, lagged far behind the materials and sensor research. To enable next-generation micro-scale systems based on nanotechnologies, on-chip IS instrumentation are needed. This thesis presents a new mixed-signal integrated circuit suitable for chip-scale implementation of IS instrumentation to support high density sensor arrays within a microsystem platform. The circuit is based on the frequency response analyzer approach for IS, which is best suited to the slow changing parameters measured by many sensors, including a model chemiresistor gas sensor array. In 0.5µm CMOS, the IS circuit occupies 205µm x 108µm and can operate from 33.3Hz to 1.66kHz. The results of this thesis demonstrate that high density sensor arrays and their readout circuitry can all be integrated on one low power low cost integrated chip, meeting the needs of many current and upcoming IS applications.

| Dedicated to my parents who have been my first and best teachers, not only or |  |  |

|-------------------------------------------------------------------------------|--|--|

| knowledge, but of a passion for learning, and the discipline crucial to both. |  |  |

| knowledge, but of a passion for learning, and the discipline crucial to both. |  |  |

| knowledge, but of a passion for learning, and the discipline crucial to both. |  |  |

| knowledge, but of a passion for learning, and the discipline crucial to both. |  |  |

| knowledge, but of a passion for learning, and the discipline crucial to both. |  |  |

| knowledge, but of a passion for learning, and the discipline crucial to both. |  |  |

| knowledge, but of a passion for learning, and the discipline crucial to both. |  |  |

| knowledge, but of a passion for learning, and the discipline crucial to both. |  |  |

| knowledge, but of a passion for learning, and the discipline crucial to both. |  |  |

| knowledge, but of a passion for learning, and the discipline crucial to both. |  |  |

| knowledge, but of a passion for learning, and the discipline crucial to both. |  |  |

| knowledge, but of a passion for learning, and the discipline crucial to both. |  |  |

iii

### TABLE OF CONTENTS

| Chapter 1: Impedance Spectroscopy       1         I. Introduction       1         II. Overview of IS       1         A. Applications       1         B. Impedance Spectroscopy Basics       3         III. Motivation for On-Chip IS       5         A. Literature Review       6         B. Goals of This Research       7         C. Requirements of On-Chip Applications       8         Chapter 2: Design Methodology       10         I. Possible Solutions       10         A. Frequency Response Analyzer       10         B. Fast Fourier Transform       10         C. Other Methods       11         D. The Best Solution       12         II. Approach       13         A. System Level Design       13         B. Matlab Simulations       14         i. Matlab Code       14         ii. Lessons Learned       14         C. Circuit Design       15         III. Challenges       15         Chapter 3: Circuit Implementation       16         I. Analog Components       16         A. Multiplier       16         i. Design       19         iv. Testing and Performance       19         ii.        | LIST OF FIGURES                        | vi |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----|

| I. Introduction.       1         II. Overview of IS.       1         A. Applications.       1         B. Impedance Spectroscopy Basics.       3         III. Motivation for On-Chip IS.       5         A. Literature Review.       6         B. Goals of This Research.       7         C. Requirements of On-Chip Applications.       8         Chapter 2: Design Methodology.       10         I. Possible Solutions.       10         A. Frequency Response Analyzer.       10         B. Fast Fourier Transform.       10         C. Other Methods.       11         D. The Best Solution.       12         II. Approach.       12         II. Approach.       13         A. System Level Design.       13         B. Matlab Simulations.       14         i. Matlab Code.       14         ii. Lessons Learned.       14         C. Circuit Design.       15         III. Challenges.       15         Chapter 3: Circuit Implementation.       16         I. Analog Components.       16         A. Multiplier.       16         ii. Design.       16         iii. Circuit.       17         iii. Layou        | Chanter 1: Impedance Spectroscopy      | 1  |

| II. Overview of IS       1         A. Applications.       1         B. Impedance Spectroscopy Basics.       3         III. Motivation for On-Chip IS.       5         A. Literature Review.       6         B. Goals of This Research.       7         C. Requirements of On-Chip Applications.       8         Chapter 2: Design Methodology.       10         I. Possible Solutions.       10         A. Frequency Response Analyzer.       10         B. Fast Fourier Transform.       10         C. Other Methods.       11         D. The Best Solution.       12         II. Approach.       13         A. System Level Design.       13         B. Matlab Simulations.       14         i. Matlab Code       14         ii. Lessons Learned.       14         C. Circuit Design.       15         III. Challenges.       15         Chapter 3: Circuit Implementation.       16         I. Analog Components.       16         i. Design.       16         ii. Circuit.       17         iii. Layout.       19         iv. Testing and Performance.       19         B. Integrator.       19                   | I Introduction                         | 1  |

| A. Applications       1         B. Impedance Spectroscopy Basics       3         III. Motivation for On-Chip IS       5         A. Literature Review       6         B. Goals of This Research       7         C. Requirements of On-Chip Applications       8         Chapter 2: Design Methodology       10         I. Possible Solutions       10         A. Frequency Response Analyzer       10         B. Fast Fourier Transform       10         C. Other Methods       11         D. The Best Solution       12         II. Approach       13         A. System Level Design       13         B. Matlab Simulations       14         i. Matlab Code       14         ii. Lessons Learned       14         C. Circuit Design       15         III. Challenges       15         Chapter 3: Circuit Implementation       16         I. Analog Components       16         A. Multiplier       16         i. Design       16         ii. Circuit       17         iii. Layout       19         iv. Testing and Performance       19         B. Integrator       19         i. Design       19 <td></td> <td></td> |                                        |    |

| B. Impedance Spectroscopy Basics       33         III. Motivation for On-Chip IS       5         A. Literature Review       6         B. Goals of This Research       7         C. Requirements of On-Chip Applications       8         Chapter 2: Design Methodology       10         I. Possible Solutions       10         A. Frequency Response Analyzer       10         B. Fast Fourier Transform       10         C. Other Methods       11         D. The Best Solution       12         II. Approach       13         A. System Level Design       13         B. Matlab Simulations       14         i. Matlab Code       14         ii. Lessons Learned       14         C. Circuit Design       15         III. Challenges       15         Chapter 3: Circuit Implementation       16         I. Analog Components       16         A. Multiplier       16         i. Design       16         ii. Circuit       17         iii. Layout       19         iv. Testing and Performance       19         B. Integrator       19         ii. Design       19         ii. Circuit       21                      |                                        |    |

| III. Motivation for On-Chip IS.       5         A. Literature Review.       6         B. Goals of This Research.       7         C. Requirements of On-Chip Applications.       8         Chapter 2: Design Methodology.       10         I. Possible Solutions.       10         A. Frequency Response Analyzer.       10         B. Fast Fourier Transform.       10         C. Other Methods.       11         D. The Best Solution.       12         II. Approach.       13         A. System Level Design.       13         B. Matlab Simulations.       14         i. Matlab Code.       14         ii. Lessons Learned.       14         C. Circuit Design.       15         III. Challenges.       15         Chapter 3: Circuit Implementation.       16         I. Analog Components.       16         A. Multiplier.       16         i. Design.       16         ii. Circuit.       17         iii. Layout.       19         iv. Testing and Performance.       19         B. Integrator.       19         i. Design.       19         ii. Circuit.       21         iii. Layout.       2                 |                                        |    |

| A. Literature Review                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |    |

| B. Goals of This Research.       7         C. Requirements of On-Chip Applications.       8         Chapter 2: Design Methodology.       10         I. Possible Solutions.       10         A. Frequency Response Analyzer.       10         B. Fast Fourier Transform.       10         C. Other Methods.       11         D. The Best Solution.       12         II. Approach.       13         A. System Level Design.       13         B. Matlab Simulations.       14         i. Matlab Code.       14         ii. Lessons Learned.       14         C. Circuit Design.       15         III. Challenges.       15         Chapter 3: Circuit Implementation.       16         i. Analog Components.       16         d. A. Multiplier.       16         i. Design.       16         ii. Circuit.       17         iii. Layout.       19         iv. Testing and Performance.       19         B. Integrator.       19         ii. Circuit.       21         iii. Layout.       22         iv. Design. Challenges.       23         C. Current Mirror.       24                                                  |                                        |    |

| C. Requirements of On-Chip Applications.       8         Chapter 2: Design Methodology.       10         I. Possible Solutions.       10         A. Frequency Response Analyzer.       10         B. Fast Fourier Transform.       10         C. Other Methods.       11         D. The Best Solution.       12         II. Approach.       13         A. System Level Design.       13         B. Matlab Simulations.       14         i. Matlab Code.       14         ii. Lessons Learned.       14         C. Circuit Design.       15         III. Challenges.       15         Chapter 3: Circuit Implementation.       16         I. Analog Components.       16         A. Multiplier.       16         i. Design.       16         ii. Circuit.       17         iii. Layout.       19         iv. Testing and Performance.       19         B. Integrator.       19         i. Design.       19         ii. Circuit.       21         iii. Layout.       22         iv. Design Challenges.       23         C. Current Mirror.       24                                                                     |                                        |    |

| Chapter 2: Design Methodology       10         I. Possible Solutions       10         A. Frequency Response Analyzer       10         B. Fast Fourier Transform       10         C. Other Methods       11         D. The Best Solution       12         II. Approach       13         A. System Level Design       13         B. Matlab Simulations       14         i. Matlab Code       14         ii. Lessons Learned       14         C. Circuit Design       15         III. Challenges       15         Chapter 3: Circuit Implementation       16         I. Analog Components       16         A. Multiplier       16         i. Design       16         ii. Circuit       17         iii. Layout       19         iv. Testing and Performance       19         B. Integrator       19         ii. Circuit       21         iii. Layout       22         iv. Design Challenges       23         C. Current Mirror       24                                                                                                                                                                                   |                                        |    |

| I. Possible Solutions.       10         A. Frequency Response Analyzer.       10         B. Fast Fourier Transform.       10         C. Other Methods.       11         D. The Best Solution.       12         II. Approach.       13         A. System Level Design.       13         B. Matlab Simulations.       14         i. Matlab Code.       14         ii. Lessons Learned.       14         C. Circuit Design.       15         III. Challenges.       15         Chapter 3: Circuit Implementation.       16         I. Analog Components.       16         A. Multiplier.       16         i. Design.       16         ii. Circuit.       17         iii. Layout.       19         iv. Testing and Performance.       19         B. Integrator.       19         i. Design.       19         ii. Circuit.       21         iii. Layout.       22         iv. Design Challenges.       23         C. Current Mirror.       24                                                                                                                                                                              | C. Requirements of On-Omp reprisations |    |

| A. Frequency Response Analyzer       10         B. Fast Fourier Transform       10         C. Other Methods       11         D. The Best Solution       12         II. Approach       13         A. System Level Design       13         B. Matlab Simulations       14         i. Matlab Code       14         ii. Lessons Learned       14         C. Circuit Design       15         III. Challenges       15         Chapter 3: Circuit Implementation       16         I. Analog Components       16         A. Multiplier       16         i. Design       16         ii. Circuit       17         iii. Layout       19         iv. Testing and Performance       19         B. Integrator       19         i. Design       19         ii. Circuit       21         iii. Layout       22         iv. Design Challenges       23         C. Current Mirror       24                                                                                                                                                                                                                                              |                                        |    |

| B. Fast Fourier Transform.       10         C. Other Methods.       11         D. The Best Solution.       12         II. Approach.       13         A. System Level Design.       13         B. Matlab Simulations.       14         i. Matlab Code.       14         ii. Lessons Learned.       14         C. Circuit Design.       15         III. Challenges.       15         Chapter 3: Circuit Implementation.       16         I. Analog Components.       16         A. Multiplier.       16         i. Design.       16         ii. Circuit.       17         iii. Layout.       19         iv. Testing and Performance.       19         B. Integrator.       19         i. Design.       19         ii. Circuit.       21         iii. Layout.       22         iv. Design Challenges.       23         C. Current Mirror.       24                                                                                                                                                                                                                                                                       |                                        |    |

| C. Other Methods.       11         D. The Best Solution.       12         II. Approach.       13         A. System Level Design.       13         B. Matlab Simulations.       14         i. Matlab Code.       14         ii. Lessons Learned.       14         C. Circuit Design.       15         III. Challenges.       15         Chapter 3: Circuit Implementation.       16         I. Analog Components.       16         A. Multiplier.       16         i. Design.       16         ii. Circuit.       17         iii. Layout.       19         iv. Testing and Performance.       19         B. Integrator.       19         i. Design.       19         ii. Circuit.       21         iii. Layout.       22         iv. Design Challenges.       23         C. Current Mirror.       24                                                                                                                                                                                                                                                                                                                   |                                        |    |

| D. The Best Solution       12         II. Approach       13         A. System Level Design       13         B. Matlab Simulations       14         i. Matlab Code       14         ii. Lessons Learned       14         C. Circuit Design       15         III. Challenges       15         Chapter 3: Circuit Implementation       16         I. Analog Components       16         A. Multiplier       16         i. Design       16         ii. Circuit       17         iii. Layout       19         iv. Testing and Performance       19         B. Integrator       19         i. Design       19         ii. Circuit       21         iii. Layout       22         iv. Design Challenges       23         C. Current Mirror       24                                                                                                                                                                                                                                                                                                                                                                           |                                        |    |

| II. Approach       13         A. System Level Design       13         B. Matlab Simulations       14         i. Matlab Code       14         ii. Lessons Learned       14         C. Circuit Design       15         III. Challenges       15         Chapter 3: Circuit Implementation       16         I. Analog Components       16         A. Multiplier       16         i. Design       16         ii. Circuit       17         iii. Layout       19         iv. Testing and Performance       19         B. Integrator       19         i. Design       19         ii. Circuit       21         iii. Layout       22         iv. Design Challenges       23         C. Current Mirror       24                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |    |

| A. System Level Design       13         B. Matlab Simulations       14         i. Matlab Code       14         ii. Lessons Learned       14         C. Circuit Design       15         III. Challenges       15         Chapter 3: Circuit Implementation       16         I. Analog Components       16         A. Multiplier       16         i. Design       16         ii. Circuit       17         iii. Layout       19         iv. Testing and Performance       19         B. Integrator       19         i. Design       19         ii. Circuit       21         iii. Layout       22         iv. Design Challenges       23         C. Current Mirror       24                                                                                                                                                                                                                                                                                                                                                                                                                                               | D. The Best Solution                   | 12 |

| B. Matlab Simulations       14         i. Matlab Code       14         ii. Lessons Learned       14         C. Circuit Design       15         III. Challenges       15         Chapter 3: Circuit Implementation       16         I. Analog Components       16         A. Multiplier       16         i. Design       16         ii. Circuit       17         iii. Layout       19         iv. Testing and Performance       19         B. Integrator       19         i. Design       19         ii. Circuit       21         iii. Layout       22         iv. Design Challenges       23         C. Current Mirror       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | II. Approach                           | 13 |

| i. Matlab Code.       14         ii. Lessons Learned.       14         C. Circuit Design.       15         III. Challenges.       15         Chapter 3: Circuit Implementation.       16         I. Analog Components.       16         A. Multiplier.       16         i. Design.       16         ii. Circuit.       17         iii. Layout.       19         iv. Testing and Performance.       19         B. Integrator.       19         i. Design.       19         ii. Circuit.       21         iii. Layout.       22         iv. Design Challenges.       23         C. Current Mirror.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                        |    |

| ii. Lessons Learned.       14         C. Circuit Design.       15         III. Challenges.       15         Chapter 3: Circuit Implementation.       16         I. Analog Components.       16         A. Multiplier.       16         i. Design.       16         ii. Circuit.       17         iii. Layout.       19         iv. Testing and Performance.       19         B. Integrator.       19         i. Design.       19         ii. Circuit.       21         iii. Layout.       22         iv. Design Challenges.       23         C. Current Mirror.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |    |

| C. Circuit Design.       15         III. Challenges.       15         Chapter 3: Circuit Implementation.       16         I. Analog Components.       16         A. Multiplier.       16         i. Design.       16         ii. Circuit.       17         iii. Layout.       19         iv. Testing and Performance.       19         B. Integrator.       19         i. Design.       19         ii. Circuit.       21         iii. Layout.       22         iv. Design Challenges.       23         C. Current Mirror.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | i. Matlab Code                         | 14 |

| III. Challenges       15         Chapter 3: Circuit Implementation       16         I. Analog Components       16         A. Multiplier       16         i. Design       16         ii. Circuit       17         iii. Layout       19         iv. Testing and Performance       19         B. Integrator       19         i. Design       19         ii. Circuit       21         iii. Layout       22         iv. Design Challenges       23         C. Current Mirror       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ii. Lessons Learned                    | 14 |

| Chapter 3: Circuit Implementation.       16         I. Analog Components.       16         A. Multiplier.       16         i. Design.       16         ii. Circuit.       17         iii. Layout.       19         iv. Testing and Performance.       19         B. Integrator.       19         i. Design.       19         ii. Circuit.       21         iii. Layout.       22         iv. Design Challenges.       23         C. Current Mirror.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | C. Circuit Design                      | 15 |

| I. Analog Components       16         A. Multiplier       16         i. Design       16         ii. Circuit       17         iii. Layout       19         iv. Testing and Performance       19         B. Integrator       19         i. Design       19         ii. Circuit       21         iii. Layout       22         iv. Design Challenges       23         C. Current Mirror       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | III. Challenges                        | 15 |

| I. Analog Components       16         A. Multiplier       16         i. Design       16         ii. Circuit       17         iii. Layout       19         iv. Testing and Performance       19         B. Integrator       19         i. Design       19         ii. Circuit       21         iii. Layout       22         iv. Design Challenges       23         C. Current Mirror       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Chanter 3: Circuit Implementation      | 16 |

| A. Multiplier       16         i. Design       16         ii. Circuit       17         iii. Layout       19         iv. Testing and Performance       19         B. Integrator       19         i. Design       19         ii. Circuit       21         iii. Layout       22         iv. Design Challenges       23         C. Current Mirror       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |    |

| i. Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1. Analog Components                   | 16 |

| ii. Circuit       17         iii. Layout       19         iv. Testing and Performance       19         B. Integrator       19         i. Design       19         ii. Circuit       21         iii. Layout       22         iv. Design Challenges       23         C. Current Mirror       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |    |

| iii. Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                        |    |

| iv. Testing and Performance.       19         B. Integrator.       19         i. Design.       19         ii. Circuit.       21         iii. Layout.       22         iv. Design Challenges.       23         C. Current Mirror.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                        |    |

| B. Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |    |

| i. Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                      |    |

| ii. Circuit21iii. Layout22iv. Design Challenges23C. Current Mirror24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |    |

| iii. Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                        |    |

| iv. Design Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |    |

| C. Current Mirror24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                        |    |

| ii. Circuit                             | 26 |

|-----------------------------------------|----|

| iii. Layout                             |    |

| II. Digital Logic                       |    |

| A. Cell Digital Logic                   |    |

| B. Chip Control Logic                   |    |

|                                         |    |

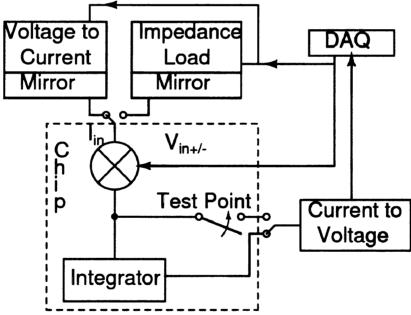

| Chapter 4: Test Results                 | 29 |

| I. Test Setup                           |    |

| A. Data Acquisition Card                |    |

| B. Voltage-to-Current Converter         | 30 |

| C. Impedance Load                       | 31 |

| D. Current-To-Voltage Converter         |    |

| E. Other                                |    |

| II. Multiplier Testing                  | 34 |

| III. Integrator Testing                 | 37 |

| IV. Full Impedance Measurement          |    |

| V. Other Components                     |    |

| •                                       |    |

| Chapter 5: Conclusions and Future Work  | 44 |

| I. Final Specifications                 |    |

| II. Contributions                       | 44 |

| III. Future Work                        | 45 |

| A. Multiplier                           | 45 |

| B. Alternative Integrators              |    |

| i. Log Domain                           | 45 |

| ii. Relaxation Oscillator               | 46 |

| C. On-Chip Current-to-Voltage converter | 47 |

|                                         |    |

| Appendix                                | 48 |

| I. Code Listings                        | 48 |

| A. eis3.m                               | 48 |

| B. lbm_sensor.m                         | 49 |

| C. gen_step.m                           | 51 |

| D. eis_system.m                         |    |

| E. makePlots.m                          | 53 |

|                                         |    |

| REFERENCES                              | 54 |

# **LIST OF FIGURES**

| Figure 1: Two typical equivalent circuits are shown. (a) is a possible equivalent circuit for gas sensors. (b) is a common equivalent for sensors in solution4 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: Bode Plot of tBLM sensor response, shows the change in Rm in both phase and magnitude                                                                |

| Figure 3: Nyquist plot of tBLM sensor response. (a) is on linear axes as is typical. (b) is on log-log axes to make the change in response clear               |

| Figure 4: System illustration of the FFT approach to IS for arrays. Each cell requires its own ADC if the sensors are to be monitored simultaneously           |

| Figure 5: System level schematic                                                                                                                               |

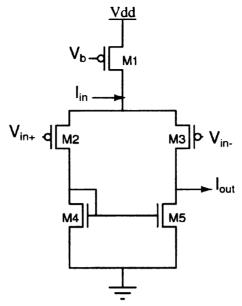

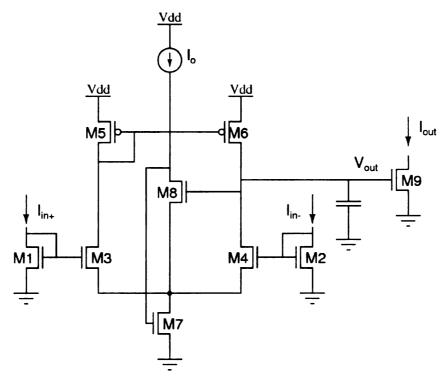

| Figure 6: Multiplier schematic                                                                                                                                 |

| Figure 7: Multiplier Layout. The multiplier dimensions are 16mm x 30mm19                                                                                       |

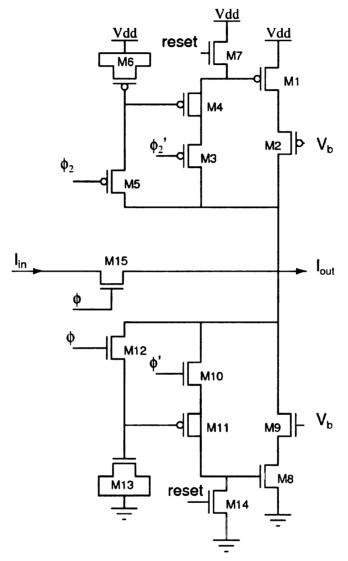

| Figure 8: Switched current integrator schematic                                                                                                                |

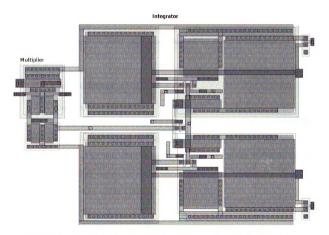

| Figure 9: Integrator with multiplier attached. The integrator dimensions are 81mm x 70mm.                                                                      |

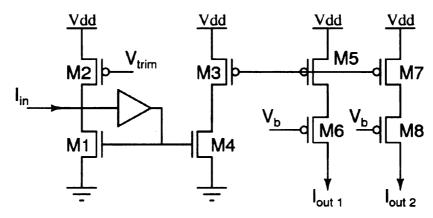

| Figure 10: Current mirror. Outputs 2 identical currents with an added DC offset from M2.                                                                       |

| Figure 11: Current mirror layout. The buffer is on the far left, and the two output branches are on the right                                                  |

| Figure 12: Complete IS array system27                                                                                                                          |

| Figure 13: Overview of test setup used                                                                                                                         |

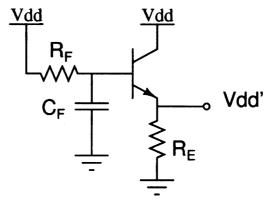

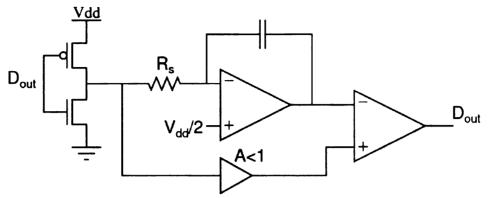

| Figure 14: Voltage-to-current converter used to generate very small currents30                                                                                 |

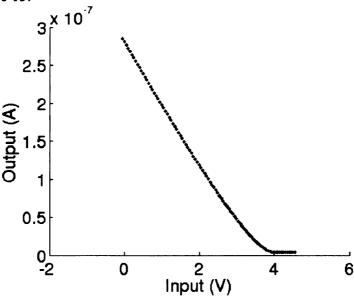

| Figure 15: Calibration curve for voltage-to-current converter. Shows that current can be generated between 7nA – 280nA, when RE is 2MW31                       |

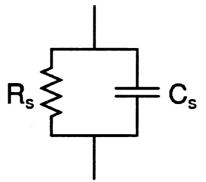

| Figure 16: Impedance load used for testing system32                                                                                                            |

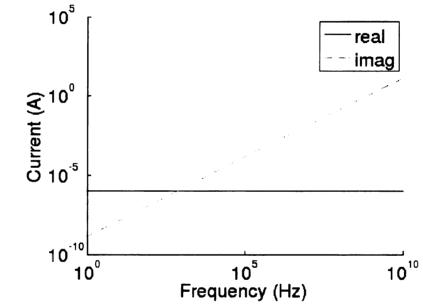

| Figure 17: The imaginary and real response of the impedance load is shown, given a 1 volt stimulus. For this simulation RS = 1MW and CS = 220pF32              |

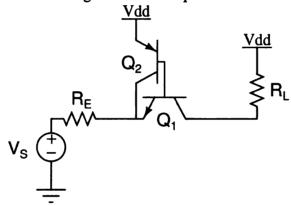

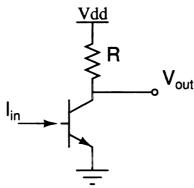

| Figure 18: Common emitter amplifier used for high gain current-to-voltage conversion 33                                                                        |

| figure 19: Power supply noise filter                                                                                                                                                                                               | 3 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

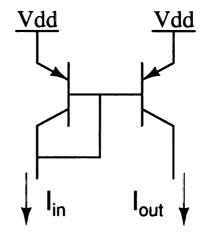

| igure 20: BJT Mirror used throughout the external instrumentation3                                                                                                                                                                 | 4 |

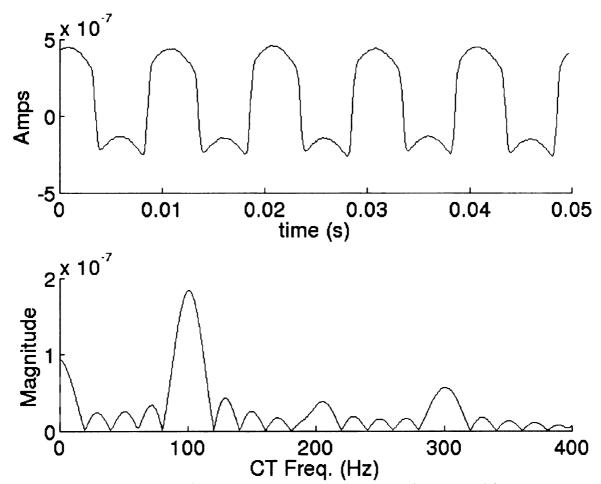

| igure 21: Output of multiplier given two 100Hz sine waves. The time and frequency omain values are shown here                                                                                                                      | 5 |

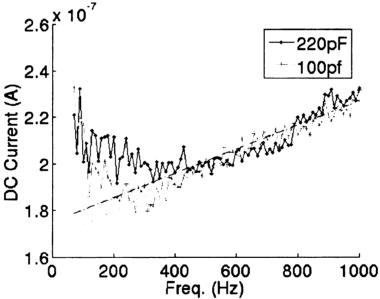

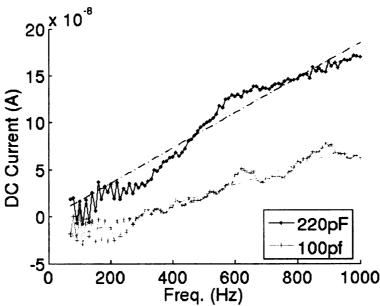

| rigure 22: DC value of multiplier output for product of two sine waves across a frequency range. The line slopes are 52.0pA/Hz (220pF) and 59.7pA/Hz (100pF). (The resistive omponent of the load was held constant at 1MW)        |   |

| rigure 23: DC value of multiplier output for product of a sine and cosine wave across a requency range. The line slopes are 187pA/Hz (220pF) and 104pA/Hz (100pF)3                                                                 | 7 |

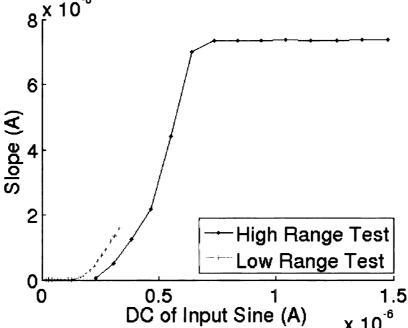

| igure 24: Results for integrating sine waves of varying DC offsets. This shows that the DC offset detection is nearly linear. The right shift of the 'High Range' curve is due in part of the use of a different current generator |   |

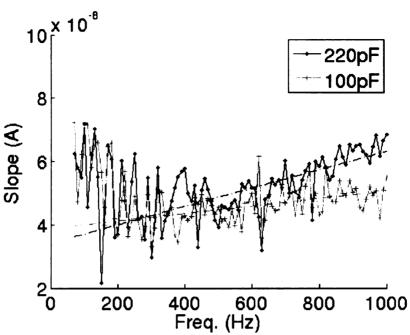

| igure 25: Full system integration showing the real component of the impedance load. As expected, there is little change in real component as capacitance changes. (The resistive component of the load was held constant at 1MW)   | 1 |

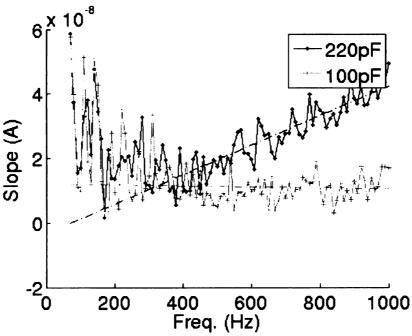

| igure 26: Full system integration showing the imaginary component of the impedance oad. As expected the slope decreases as capacitance decreases4                                                                                  | 2 |

| igure 27: Standard log domain integrator4                                                                                                                                                                                          | 6 |

| igure 28: Simple oscillator for resistance to time conversion4                                                                                                                                                                     | 7 |

# **Chapter 1: Impedance Spectroscopy**

#### I. Introduction

Impedance Spectroscopy (IS) is emerging as a powerful technique in the field of microscale sensing. IS is commonly used in many macro-scale applications such as monitoring electrochemical reactions, testing coatings [1], testing batteries [2] and many other applications [3],[4]. Recently, it has begun to be applied to micro-scale sensors across a wide variety of applications. These micro-scale applications hold great promise for biological research and medical applications. The explosive growth of potential applications for IS has jumped far ahead of the instrumentation necessary to enable these applications. The goal of this research is to begin work in developing the underlying circuitry that will be necessary to enable the potential applications to be realized.

### II. Overview of IS

Some general categories of micro-scale IS applications will be presented along with some representative literature. The goal is to introduce the scope of IS and consider the instrumentation requirements. After giving an overview of the applications, the fundamentals of IS will be presented.

## A. Applications

IS has been used for quite some time to investigate human tissue. For example, Peura, Ristic, Kun, et. al. have written a series of papers on detecting tissue ischemia (lack of oxygen and nutrients to tissue eventually resulting in the death of the tissue) [5], [6], [7], [8], [9]. Although, their work is not on the micro-scale, the ability to implement on-chip IS might greatly expand the applications of this work. For instance, [10] shows that IS can detect ischemia leading to organ failure in the intestine. For this to be brought to practical

application, an embedded sensor would be necessary. Additionally, IS has been applied for the detection of skin cancer [11] and skin irritation [12].

More recently, IS has been coupled with on-chip fluidics for particle detection. This research allows for differentiating various particle types [13], monitoring position of particles [14], and measuring the size of the particle [15]. One unique application is the testing of neural probes. It is necessary that the "cultured probes" be well covered and sealed by neural cells. IS was applied to inspect the probes and determine the state of their coating [16]. The use of IS in on-chip fluidics again naturally leads to the need for on-chip IS instrumentation circuitry.

Not only can particles be detect, but if the analyte is a cell, it has been shown that a great deal of information about cells can be extracted using IS. Work has been published showing that it is possible to detect and sort blood cells [17] based on abnormalities in the cells, this is applicable for use in cancer screening [18], [19]. Other authors have been able to inspecting cell's membranes and cytoplasm [20] and detecting bacterial viability [21]. Although, there are still some limitations of size, range, and sensitivity. [22] states that IS will become an important technique in impedance based single cell measurements. The goal of this research is to help address some of those issues, specifically size and sensitivity.

Biological sensors are a key area of application for IS. It has been used for "immunosensors, DNA sensors and biocatalytic enzyme-based biosensors" [23]. The DNA sensors have been used to classify unknown DNA strands [24] and for other applications [25]. Another key biosensor application is the use of proteins bonded to electrodes. As the proteins react to specific chemicals, the reaction can be measured using IS [26], [27], [28], [29]. The protein-based sensors offer a wide variety of possibilities because proteins are

very selective and proteins can be found that will react with many different chemicals.

Many of these sensors present the possibility of creating high density sensor arrays. Such arrays could use many different proteins to provide a wide range of analyte detection.

The protein-based sensors usually only operate in solutions; however there are other sensors capable of detecting chemicals in gas [30], [31]. These sensors are usually treated as simple resistive sensors, referred to as chemiresistors (CR), but research is being done to determine what extra information IS may yield. While an on-chip IS system is applicable to all of the above applications, this project specifically targets detecting the impedance information in gas sensors.

### **B.** Impedance Spectroscopy Basics

IS is the process of measuring a sensor's impedance (complex resistance) response over a wide range of frequencies. A great deal of information can be gathered from the impedance spectrum, and this has opened up many of the above exciting applications.

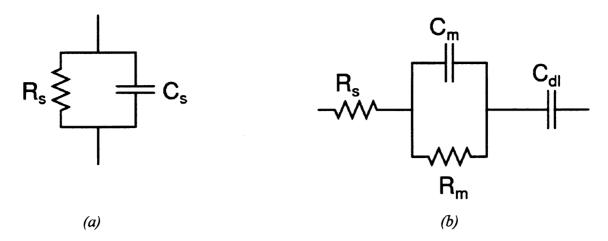

The reason IS provides so much information is that the response of the system changes with frequency. Thus, a broad range of information can be collected in a single measurement. The physical reasons for this vary between each system. To simplify the physical details a sensor is generally modeled using an equivalent circuit. (Two common equivalent circuit are shown in Figure 1.) The equivalent circuit is a model that gives the same impedance response as the system being measured. Typically the component values of the equivalent circuit can be mapped to the physical properties of the sensor.

Figure 1: Two typical equivalent circuits are shown. (a) is a possible equivalent circuit for gas sensors. (b) is a common equivalent for sensors in solution.

Generally, the sensor's equivalent circuit remains constant, but as it responds to its environment one or more component values change. For sensors this becomes a valuable tool, because once the equivalent circuit of a sensor is known, the interface circuitry need only identify the change in component values to detect a change in the system.

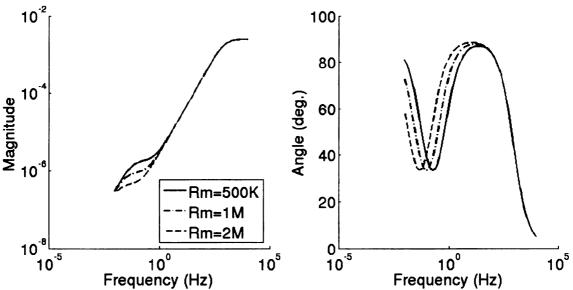

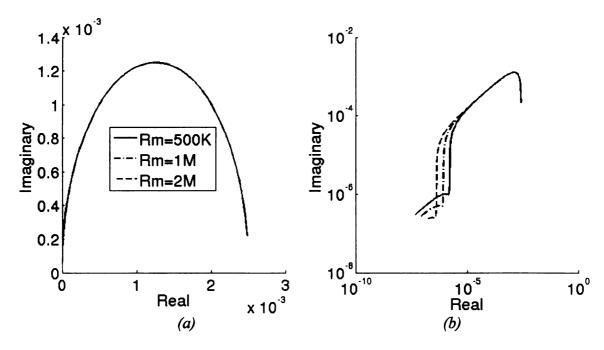

The response of a sensor is often visualized using a Bode (Figure 2) or Nyquist plot (Figure 3). Because the impedance values are complex numbers they can be represented in two different ways. A Bode plot shows the amplitude and phase values across the range of frequencies. The Nyquist plot shows the data as real vs. imaginary. The equivalent circuit values, ie. the sensor response, can be found from either plot.

As an example, a Tethered Bilayer Lipid Membrane (tBLM) sensor has an equivalent circuit like the one shown in Figure 1 (b) [26]. When the proteins in the tBLM react, this is reflected by a the change in the value of R<sub>m</sub>. The plots below show the response of the sensor for three values of R<sub>m</sub>. In the case of a tBLM sensor, the interface circuitry would need to be able to accurately detect the shift in response in the sub-Hertz range.

A good overview of IS from a chemists' perspective is given in [23].

Figure 2: Bode Plot of tBLM sensor response, shows the change in  $R_m$  in both phase and magnitude.

Figure 3: Nyquist plot of tBLM sensor response. (a) is on linear axes as is typical. (b) is on log-log axes to make the change in response clear.

# III. Motivation for On-Chip IS

Clearly many applications exist for IS, and much work has been done in testing and expanding these applications. Nearly all of the applications above attach on-chip probes to bench-top instruments (either some form of network analyzer or a PC with a DAQ) to do

the actual impedance measurement. While bench-top instruments are useful for initial research they present some serious limitations as well. Bench-top equipment can be very expensive, which severely limits any sort of large scale deployment or production of the IS systems. Some of the applications listed above present exciting possibilities for portable or even in vivo applications, however the size and power requirements of bench-top equipment make this impossible.

Some of the sensor applications (especially the DNA, protein, and chemiresistors sensors) offer the possibilities of a high density array of sensors. It is not possible to bring hundreds of sensor leads all out to a bench-top instrument. Multiplexing the raw signals is also not possible because of transistor leakage. In a typical CMOS process, the transistor leakage is around 10pA [32]. If one hundred channels are multiplexed, then the total leakage through the multiplexer will begin to approach the same magnitude as that of the signal [33]. Finally, long leads required for bench-top equipment increase the amount of noise coupled onto the system. The goal of this research is to begin to address these needs by providing a fully on-chip IS system capable of supporting high density arrays of sensors.

### A. Literature Review

There are a number of IS systems which have been developed which rely on computers for most of their computation. [34] uses discrete components on a PCB to perform measurements. In this case, a sinusoidal stimulus is applied and the output is amplified and read by a computer. It appears that only the amplitude is measured and the full sensor response is then inferred from the amplitude and a known equivalent circuit. In a similar manner, [5] uses discrete components to stimulate and read the sensor. The raw data from the sensor is then digitized and passed to a computer which computes the amplitude and

phase data from this. Instead of using a sinusoidal stimulus, [18] stimulated the sensor with an impulse. The response of the sensor to the impulse was once again passed to a computer which converted the data to the frequency domain using the Fast Fourier Transform. Computer based solutions, while useful for testing suffer from all of the benchtop limitations listed above.

Some more compact solutions have been presented. [1], replaces the computer with a commercial digital signal processor. However, a number of external amplifiers and other components are still required for this system. [35] discusses fully on-chip system but gives very few details as to the implementation. From the details that are given, it appears that only the impedance magnitude is measured and not the phase. While amplitude alone may be useful for some systems, in general, information is lost without the full complex response of the sensor. Thus no fully on-chip system that measures the full complex response of the sensor has been found.

None of the preceding systems are suitable for high density senor arrays. Too much bandwidth would be required to transmit all the raw information for processing by a computer. The more compact systems, once multiplied by many sensors would become too large for economical use. [36] is an on-chip sensor array system, however it only has programmable amplifiers, and no IS is actually done.

On-Chip IS is a very new field. No published research could be found which presented a fully on-chip system capable of computing complete impedance data.

### B. Goals of This Research

No known fully on-chip IS system currently exists, despite the many applications which need this technology. Thus, the primary goal of this research is to begin meeting the needs of the many new IS applications being proposed, by providing a fully on-chip IS system.

The goal is to develop an IS system that is not only fully integrated on an IC, but sufficiently compact to allow the system to support high density sensor arrays on a single IC.

Due to the lack of published research in this area, very little is known about the issues or requirements of on-chip IS. Some of the requirements of an on-chip IS system can be derived from the application research, but much is unknown about how best to build these systems. Also, there are a number of methods for implementing IS measurements (some are discussed in chapter 2). Beyond developing an IS system, this research also attempts to explore the possible solution space and identify which parameters are important and which solutions are practically realizable.

### C. Requirements of On-Chip Applications

Even when building a general baseline test system, some specifications are needed. A specific target application must be selected and requirements drawn from this. This project targets measuring the IS of chemiresistors (CR). The exact equivalent circuit for the system is not yet known, but a parallel RC circuit, like that shown in Figure 1(a) is assumed, with component values around  $1M\Omega$  and 40pF.

Drawing from this target, some specifications can be established. Depending on the exact component values, the sensor's break frequency is around 4kHz. To allow for a good interrogation range then, the system should be able to cover 100Hz - 10kHz, or a similar 2 decade range. It is typical that these systems exhibit large base resistances around  $100\text{k}\Omega$  to  $10\text{M}\Omega$  and can not be interrogated with voltages above 1V. This translates into small total currents on the order of 100nA. The actual sensor response may represent only a fraction of the base value. This system will target currents in the nano-amp range.

As noted earlier, many of the applications of IS require the use of high density sensor

arrays. This also raises some unique requirements. The first requirement, which has already been discussed, is that off-chip bandwidth is limited, so all of the sensor's responses must be processed to a sufficient extent that they can be easily transmitted off of the chip. Secondly, if hundreds of sensors are all multiplexed down to one interface circuit, leakage current becomes a serious issue, as each channel of the multiplexer will leak into the output. Thus, with the small sensor signals expected in this project it is not possible to multiplex hundreds of sensors down to one interface. Instead, the IS interface, or at least the front end, needs to be small enough so that it can be instantiated many times on the die.

# **Chapter 2: Design Methodology**

### I. Possible Solutions

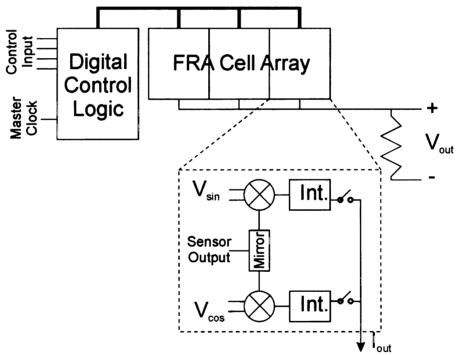

### A. Frequency Response Analyzer

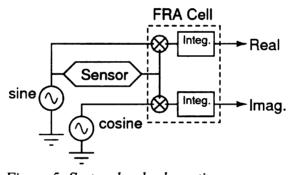

The Frequency Response Analyzer (FRA) is a common method for making IS measurements [37]. For instance, it is used for cell sorting in [17]. In this system, the sensor is stimulated with a single sine wave (See Figure 5 below). The output of the sensor is then multiplied by the same sine wave as well as a cosine wave of the same magnitude. The DC value of the multiplier output caries the sensor response, so it is then passed into a low pass filter. (Typically an integrator is used because it has a cutoff frequency at 0 Hz.) After filtering, the two outputs are proportional to the Real and Imaginary portions of the sensor's response. After the measurement is completed, a new measurement can be taken at the next frequency. The advantage of this system is that it is simple, which offers many hardware optimizations, such as implementing it in the analog domain.

The disadvantage of this system is that it is slow. It can only measure one frequency at a time and for each measurement the integrator must be given enough time to reach an accurate value. Because the integration time is a function of the signal period (1/f) the loss in speed is significant at the lower frequencies.

#### B. Fast Fourier Transform

A second method commonly used is based on the Fast Fourier Transform (FFT) [38], [39]. It has been used for instance in cell [18] and tissue [12] testing. This addresses the speed restrictions of the FRA method. Instead of measuring a range of discrete frequencies the sensor is stimulated with a wide-band signal, such as an impulse. The response of the sensor is digitized and transformed to the frequency domain using the FFT algorithm. This

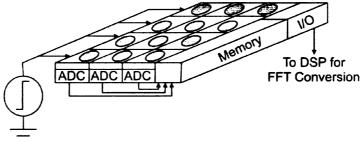

provides a speed boost because there is no integrator and all frequencies are measured at once. The process is illustrated in Figure 4.

Figure 4: System illustration of the FFT approach to IS for arrays. Each cell requires its own ADC if the sensors are to be monitored simultaneously.

The disadvantage of this system is that it makes many size and power trade offs in order to accomplish its speed goals. All components in this system are digital, which requires more area and power. This system requires a much faster ADC than the FRA because it must capture high frequency data. After the data is digitized, it needs to be processed using the FFT. If it is to be processed on-chip, a DSP unit will need to be included which would consume a lot of space. If the data is to be processed off chip, a very large amount of data would need to be transferred off chip. In either case with a high density array of sensors, a large amount of memory would be required to store the data until it could be processed or transmitted.

As an example of the hardware requirements, [40] presents the design of an 128 cell sensor array, where each cell has an ADC and shift register. However, the ADC on this chip is too slow for a FFT system. This design already requires a large chip (6.4mm x 4.5mm), adding a faster ADC and larger shift registers would make the chip area even larger yet.

### C. Other Methods

The two solutions mentioned above are the most commonly used IS systems. Sometimes

variations on these ideas are employed. For instance, there has been some work done to eliminate the integrator in the FRA solution by changing the algorithm [41].

Also, in some cases, when only the magnitude information is needed, very simple resistance or current readout circuits can be used [35]. This is acceptable for some applications, however the phase information is lost in this approach. Thus this approach is not acceptable for general IS.

#### D. The Best Solution

Chemiresistor systems do not usually change rapidly, as applying vapors and removing them takes some time. This means that speed is not a crucial restriction, instead area and power are the critical restrictions. So, the FFT solution becomes a poor option because it is very expensive in terms of area. The simplicity of the FRA solution now becomes very important.

The FRA solution has excellent potential for miniaturization. The two key components in this system are the multiplier and integrator. Both of these can be implemented in the analog domain, reducing the space and power requirements of the system. Also, because the integrator removes all harmonics from the DC signal, the multiplier used does not need to be very accurate, again allowing for further miniaturization.

For this project then, the FRA solution seemed the best choice. The multiplier and integrator can be bundled in a tight cell that can be instantiated many times. After integration, the output of the system is sufficiently large that it can be multiplexed. Also the output is a DC value which is then easily digitized and processed.

A more detailed comparison of the FRA, FFT, and some other approaches is presented in [33].

## II. Approach

# A. System Level Design

The system level design is shown in Figure 5. This system works using a dual phase variable frequency signal generator. The sine wave (as a voltage) is used to stimulate the sensor. The sensor's response (as a current) is then multiplied by the original sine and the cosine. The result of the multiplication is as follows:

$$[A\sin(\omega t + \phi) + C] \times B\sin(\omega t) = \frac{AB}{2} [\cos(\phi) - \cos(2\omega t + \phi)] + BC\sin(\omega t) \quad (1)$$

$$[A\sin(\omega t + \phi) + C] \times B\cos(\omega t) = \frac{AB}{2} [\sin(\phi) + \sin(2\omega t + \phi)] + BC\cos(\omega t) \quad (2)$$

Figure 5: System level schematic.

Where A is the amplitude of the sensor response,  $\omega$  is the frequency of the signal generator,  $\phi$  is the sensor phase shift, C is the DC offset of the sensor (this is introduced by the system, see "Current Mirror" below), and B is the magnitude of the stimulus signal. The DC portion of the resulting equations represents the Real and Imaginary response of the sensors. The AC portion of this system must be eliminated. To accomplish this, a low pass filter could be used, however for a low frequency stimulus, the filter must have a sharp cutoff, or a portion of the AC response will be included. In this case an integrator, which has a cutoff at 0Hz, provides a better filter.

### B. Matlab Simulations

After the system level design was complete, Matlab simulations were made to test the proposed system. For this system, the equivalent network shown in Figure 1(b) was used. The Matlab code calculated the response of the sensor to stimulus, multiplied that response by the correct sine waves and then applied a low pass filter to the result. Finally, it provided plots of key intermediate and final results.

#### i. Matlab Code

The source code for each of these scripts is shown in the appendix. They are explained briefly here.

- eis3.m This is the main application, it allows the initial values to be set such as

frequency range and sensor parameters.

- lbm\_sensor.m This generates the transfer function for the sensor network.

- gen\_step.m The calculations are done in steps, this sets up the necessary

frequency, time, and signal arrays for the current step.

- eis system.m This does the actual multiplication and filtering of the signal.

- makePlots.m This adds the current calculation step results to the final plot.

#### ii. Lessons Learned

A number of conclusions and lessons were drawn from the Matlab simulations. The first was that a simple chirp would not work for stimulating the system. It had originally been suggested that a signal that had a linearly increasing frequency would provide a good stimulus for the system. However, simulation results showed that because of the capacitance in the sensor, each frequency needed to be held for a short time to allow transient responses to settle out of the system. The simulations also showed that the necessary model parameters, representing the sensor response, could be computed from the

Nyquist plot. This can be seen in Figure 3.

The Matlab design used 1<sup>st</sup> and 2<sup>nd</sup> order low pass filters (LPF) instead of integrators to test the cut-off requirements on the system. It was found that the cut-off frequency of the filter needed to be at least a decade less than the minimum frequency being measured. It should be smaller yet for accurate measurements. The capacitance required to make a filter with a cut off less than 10 Hz was too large for the size restrictions of this system. Given a  $1M\Omega$  resistance, a first order filter would require 16nF capacitor, which would be much too large. An active filter is a possibility, but would still be difficult to design at such a low frequency. Also, the LPFs were also not significantly faster than the integrator.

## C. Circuit Design

After the Matlab simulations were complete, each component had to be designed and tested. Then each component was laid out and integrated together. These steps will be discussed in the next chapter.

# III. Challenges