## This is to certify that the thesis entitled

## DESIGN AND EVALUATION OF AN AUTOMATED TEST PLATFORM FOR LARGE-SCALE ANALOG FLOATING GATE ARRAY PROGRAMMING

presented by

Paul R. Kucher IV

has been accepted towards fulfillment of the requirements for the

| M.S. | degree in  | Electrical and Computer Engineering |

|------|------------|-------------------------------------|

|      | n- 1       | ,                                   |

|      | Major Prof | essor's Signature                   |

|      | 10/19/     | 2007                                |

|      | ,          | Date                                |

MSU is an affirmative-action, equal-opportunity employer

LIBRARY Michigan State University

# **PLACE IN RETURN BOX** to remove this checkout from your record. **TO AVOID FINES** return on or before date due. **MAY BE RECALLED** with earlier due date if requested.

| DATE DUE      | DATE DUE | DATE DUE |

|---------------|----------|----------|

| (A)Air page 1 |          |          |

|               |          |          |

|               |          |          |

|               |          |          |

|               |          |          |

|               |          |          |

|               |          |          |

|               |          |          |

|               |          |          |

|               |          |          |

6/07 p:/CIRC/DateDue.indd-p.1

## DESIGN AND EVALUATION OF AN AUTOMATED TEST PLATFORM FOR LARGE-SCALE ANALOG FLOATING GATE ARRAY PROGRAMMING

$\mathbf{B}\mathbf{y}$

Paul R. Kucher IV

### A THESIS

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

MASTER OF SCIENCE

Electrical and Computer Engineering

2007

## **ABSTRACT**

## DESIGN AND EVALUATION OF AN AUTOMATED TEST PLATFORM FOR LARGE-SCALE ANALOG FLOATING GATE ARRAY PROGRAMMING

By

#### Paul R. Kucher IV

Due to advances in microfabrication technology, modern digital systems can process large data sets using discrete algorithms with high precision. However, due to the increasing clock frequencies required to operate on data in real-time applications, analog circuit topologies have become attractive for computation. Such computational blocks require an analog data store that can achieve at least eight bits of accuracy for coarse classification. This work creates an automatic means of programming subthreshold floating gate circuits used as analog storage elements. The system consists of a test platform designed with a flexible configuration for both topology and process-neutral large-scale floating gate array programming. A system-on-chip with analog floating gates has been fabricated in a standard  $0.5\mu$ m CMOS process and is used to validate the performance of the test platform. A novel algorithm for floating gate programming has been developed based on experimental observation and the test unit is capable of programming analog floating gate arrays to within 0.5% accuracy.

## ACKNOWLEDGMENTS

I would like to begin by thanking my advisor, Dr. Shantanu Chakrabartty. I feel honored to have worked under his direction for the past two years, and have gained significant insight into designing mixed-signal VLSI systems for machine learning applications. He has provided me with the opportunity to pursue the areas of research I find most intellectually stimulating and has always guided me in accomplishing my goals. I look forward to continued collaboration and wish him the best in his own research endeavors.

I thank my committee members, Dr. Greg Wierzba and Dr. Andrew Mason, for taking time out of their busy schedules to be a part of my project. I also credit Dr. Mason with introducing me to research through working in his lab during my undergraduate career. I thank him for this opportunity and his thoughtful review of my thesis work. I thank Dr. Greg Wierzba for his advice and inspiration. I have enjoyed our many discussions and the advice he has given extending back to my undergraduate years. His courses have taught me many of the skills I needed to complete this work and I thank him for giving me these tools.

I thank my friend, Arthur Matteson, who helped in populating the test platform printed circuit board. I am impressed with his ability to work with fine-pitch, surface mount components and am grateful of being able to learn his technique. I also thank Arthur for his constant input and review of my thesis.

Finally, I thank my parents, Paul and Elaine Kucher, who have done their absolute best in raising and guiding me. They have always supported my interests and have never failed to help in time of need.

## TABLE OF CONTENTS

| LI | ST ( | OF TABLES                                          |

|----|------|----------------------------------------------------|

| LI | ST ( | OF FIGURES ix                                      |

| 1  | Intr | oduction                                           |

|    | 1.1  | Previous Work                                      |

|    |      | 1.1.1 Field-Programmable Analog Arrays             |

|    |      | 1.1.2 Support Vector Machine                       |

|    |      | 1.1.3 Imagers and Adaptive Sensors 6               |

|    | 1.2  | Motivation: Rapid Configuration of Analog Memories |

|    | 1.3  | EEPROMs for Analog Parameter Storage               |

|    | 1.4  | Floating Gate Test Station Design                  |

|    | 1.5  | Floating Gate Test Station Control                 |

|    | 1.6  | Testing and Results                                |

|    | 1.7  | Conclusions                                        |

| 2  | EE   | PROMs for Analog Parameter Storage 10              |

|    | 2.1  | History                                            |

|    |      | 2.1.1 PROM                                         |

|    |      | 2.1.2 EPROM                                        |

|    |      | 2.1.3 EEPROM                                       |

|    |      | 2.1.4 Flash Memory                                 |

|    | 2.2  | Floating Gate Transistors                          |

|    | 2.3  | Fowler-Nordheim Tunneling                          |

|    | 2.4  | Hot-Electron Injection                             |

|    | 2.5  | Analog Floating-Gate Programming Procedure         |

|    | 2.6  | Programming Precision                              |

|    | 2.7  | Charge Retention Characteristics                   |

|    | 2.8  | Temperature Dependency                             |

|    | 2.9  | Summary                                            |

| 3  | Floa | ating Gate Test Station Design                     |

|    | 3.1  | Noise and Shielding Considerations                 |

|    |      | 3.1.1 Shared Current Paths                         |

|    |      | 3.1.2 Shielding Techniques                         |

|    | 3.2  | System Architecture                                |

|    | 3.3  | Power Circuits                                     |

|    |      | 3.3.1 Voltage Regulation                           |

|   |      | 3.3.2     | Fowler-Nordheim Tunneling Supply and Control | 29        |

|---|------|-----------|----------------------------------------------|-----------|

|   |      | 3.3.3     | Hot-electron Injection Supply and Control    | 32        |

|   | 3.4  | Voltage   | e Digital-to-Analog Conversion               | 33        |

|   | 3.5  | Voltage   | e Analog-to-Digital Conversion               | 34        |

|   | 3.6  | Multi-    | channel Current Digital-to-Analog Conversion | 36        |

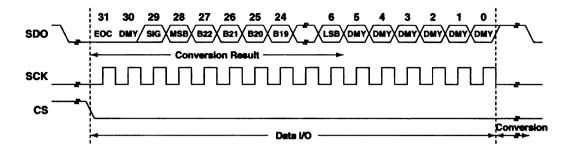

|   | 3.7  | Multi-    | channel Current A/D Conversion               | 38        |

|   | 3.8  | Testing   | g Considerations                             | 42        |

|   | 3.9  | Summa     | ary                                          | 43        |

| 4 | Floa | ting G    | ate Test Station Control                     | 45        |

|   | 4.1  | Instruc   | etion Decoding and Execution                 | 45        |

|   |      | 4.1.1     | Instruction Set                              | 48        |

|   | 4.2  | Digital   | Input/Output                                 | 49        |

|   | 4.3  | Digital   | Potentiometer Control                        | 50        |

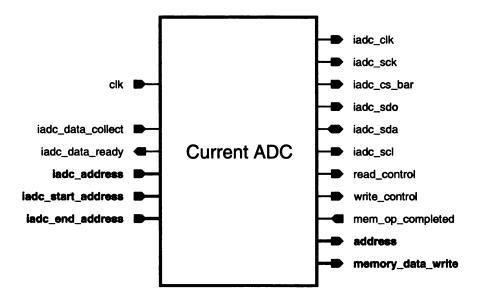

|   | 4.4  | Curren    | t Analog-to-Digital Conversion               | <b>52</b> |

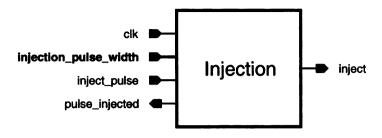

|   | 4.5  | Injection | on Control                                   | 54        |

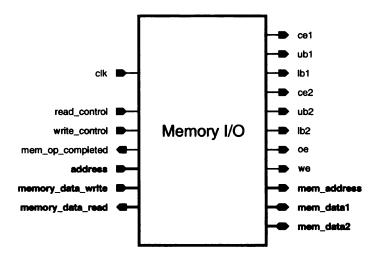

|   | 4.6  | Memor     | ry I/O                                       | 55        |

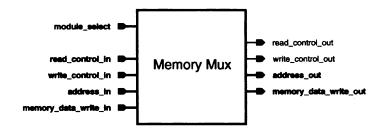

|   | 4.7  | Memor     | ry Multiplexer                               | 57        |

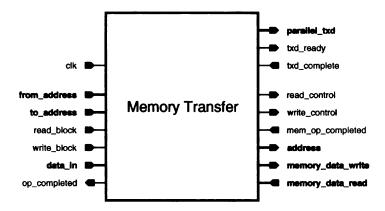

|   | 4.8  | Memor     | ry Transfer Control                          | 57        |

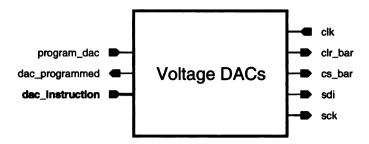

|   | 4.9  | Voltag    | e Digital-to-Analog Conversion               | <b>59</b> |

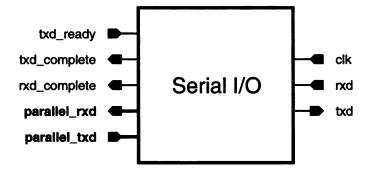

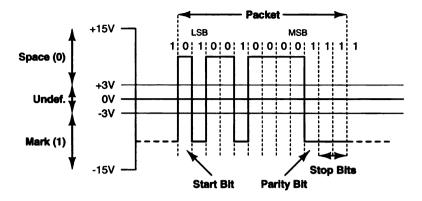

|   | 4.10 | Serial :  | I/O                                          | 61        |

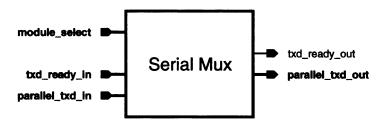

|   | 4.11 | Serial 3  | Multiplexer                                  | 64        |

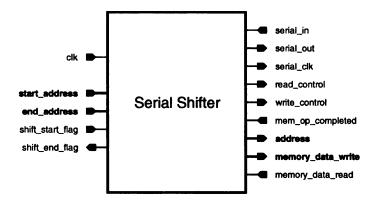

|   | 4.12 | Serial    | Shifter                                      | 64        |

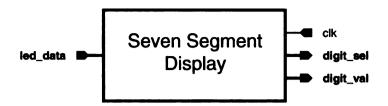

|   | 4.13 | Seven     | Segment Display                              | 66        |

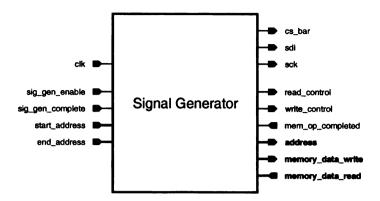

|   | 4.14 | Signal    | Generator                                    | 67        |

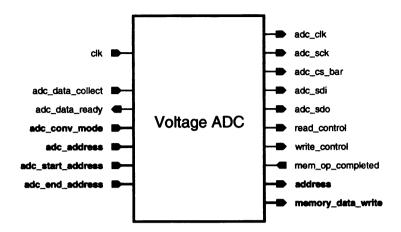

|   | 4.15 | Voltag    | e Analog-to-Digital Conversion               | 69        |

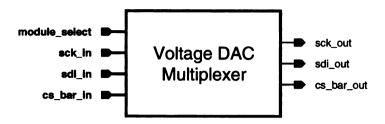

|   | 4.16 | Voltag    | e DAC Multiplexer                            | 71        |

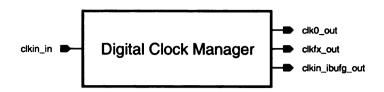

|   | 4.17 | Digital   | Clock Manager                                | 71        |

| 5 | Test | ing an    | d Results                                    | 74        |

|   | 5.1  | Test St   | tation Validation                            | 74        |

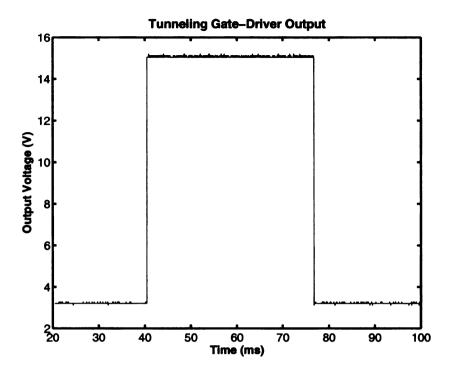

|   |      | 5.1.1     | Fowler-Nordheim Tunneling Pulse Response     | 74        |

|   |      | 5.1.2     | Hot-Electron Injection Pulse Response        | 75        |

|   |      | 5.1.3     | Voltage-Mode ADC Linearity                   | 76        |

|   |      | 5.1.4     | Signal Generator                             | 80        |

|   | 5.2  | Overvi    | ew of the Test Chip                          | 84        |

|   | 5.3  | Floatin   | ng Gate Testing Results                      | 86        |

|   |      | 5.3.1     | Floating Gate Current Equalization           | 86        |

|   |      | 5.3.2     | Adaptive Injection Characteristics           | 87        |

|   |      | 5.3.3     | Effects of Injection on Threshold Voltage    | 90        |

|   |      | 5.3.4     | Programmable Current Lookup Tables           | 92        |

| 6            | Conclusions                                                 | 94         |

|--------------|-------------------------------------------------------------|------------|

|              | 6.1 Accomplishments                                         | 94         |

|              | 6.2 Suggestions For Future Work                             | 95         |

|              | 6.2.1 Floating Gate Architectures                           | 95         |

|              | 6.2.2 Board-Level Modifications                             | 96         |

|              | 6.2.3 Microcontroller-Based Test Station                    | 97         |

| A]           | PPENDICES 10                                                | 00         |

| A            | Support Vector Machine SoC                                  | 00         |

|              | A.1 Layout                                                  | 00         |

|              | A.2 Pad Frame                                               | 03         |

| В            | Test Station Design Documentation                           | 05         |

|              | B.1 Test Station Parts List                                 | 05         |

| $\mathbf{C}$ | Test Station VHDL                                           | 27         |

|              | C.1 Digital Clock Manager: dcm.vhd                          | 27         |

|              | C.2 Instruction Decoder and System Controller: decode.vhd 1 | 29         |

|              | C.3 Multi-channel Digital Input/Output: digital_io.vhd      | 35         |

|              | C.4 Digital Potentiometer Control: digital_pots.vhd         | 38         |

|              | C.5 Current ADC Control: iadc.vhd                           | <b>4</b> 0 |

|              | C.6 Floating-Gate Transistor Injection: injection.vhd       | 44         |

|              | C.7 Memory Transfer Control: memory_block_transfer.vhd      | 45         |

|              | C.8 Memory Controller: memory_io.vhd                        | 47         |

|              | C.9 Memory Multiplexer: memory_mux.vhd                      | <b>4</b> 9 |

|              | C.10 Voltage DAC Controller: program_dacs.vhd               | 50         |

|              | C.11 RS-232 Serial Controller: serial_io.vhd                | 52         |

|              | C.12 Serial I/O Multiplexer: serial_mux.vhd                 | 57         |

|              | C.13 Serial Shifting Controller: serial_shifter.vhd         | 58         |

|              | C.14 Seven Segment Display: seven_segment.vhd               | 60         |

|              | C.15 Signal Generator: signal_gen.vhd                       | 62         |

|              | C.16 Voltage ADC Controller: vadc.vhd                       | 64         |

|              | C.17 Voltage DAC Multiplexer: vdac_mux.vhd                  | 67         |

|              | C.18 Top Module: top.vhd                                    | 68         |

|              | C.19 Implementation Constraints File: top.ucf               | 77         |

| D            | MATLAB Toolbox Overview                                     | 79         |

| E            | Test Station MATLAB Functions                               | 81         |

|              | E.1 FPGAInit.m                                              | 81         |

|              | E.2 FPGALoopback.m                                          | 82         |

|    | E.3            | FPGADigitalIO.m                                                  | 82 |

|----|----------------|------------------------------------------------------------------|----|

|    | E.4            | $FPGAInjectPulse.m \qquad . \qquad . \qquad . \qquad . \qquad 1$ | 83 |

|    | E.5            | FPGATunnel.m                                                     | 84 |

|    | E.6            | FPGASetBias.m                                                    | 84 |

|    | E.7            | FPGASetBiasCurrent.m                                             | 85 |

|    | E.8            | $FPGAReadVoltage.m \ . \ . \ . \ . \ . \ . \ . \ . \ . \$        | 85 |

|    | $\mathbf{E}.9$ | FPGAReadCurrent.m                                                | 87 |

|    | E.10           | FPGAEstimateCurrent.m                                            | 88 |

|    | E.11           | FPGAReadMemory.m                                                 | 89 |

|    | E.12           | FPGAReadMemoryBlock.m                                            | 89 |

|    | E.13           | FPGAWriteMemory.m                                                | 90 |

|    | E.14           | FPGAWriteMemoryBlock.m                                           | 91 |

|    | E.15           | FPGAWriteMemoryVector.m                                          | 92 |

|    | E.16           | FPGASerialShift.m                                                | 92 |

|    | E.17           | FPGAFunctionGenerator.m                                          | 93 |

|    | E.18           | FPGASignalGen.m                                                  | 95 |

| F  | Floa           | ting Gate Testing Code                                           | 96 |

|    | F.1            | •                                                                | 96 |

|    | F.2            | <del>-</del>                                                     | 96 |

|    | F.3            | -                                                                | 97 |

|    | F.4            | ·                                                                | 97 |

|    | F.5            |                                                                  | 98 |

|    | F.6            | SVM2GetCurrent.m                                                 | 99 |

|    | F.7            |                                                                  | 99 |

|    | F.8            | SVM2SetCurrent.m                                                 | 99 |

|    | F.9            |                                                                  | 01 |

|    | F.10           |                                                                  | 01 |

|    |                |                                                                  | 01 |

| Bl | BLIG           | OGRAPHY                                                          | 03 |

## LIST OF TABLES

| 3.1 | Jumper Descriptions                   | 42  |

|-----|---------------------------------------|-----|

| 4.1 | System Instruction Set                | 48  |

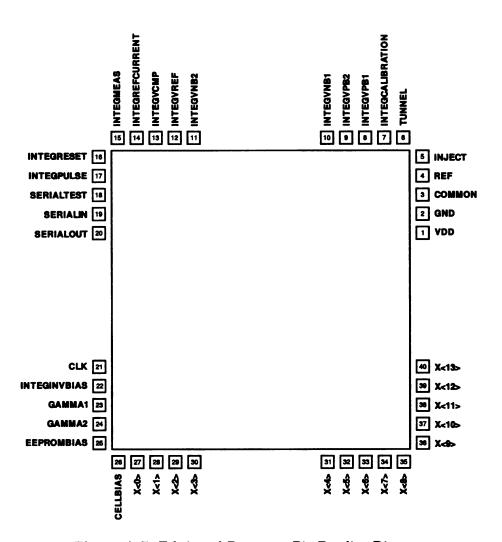

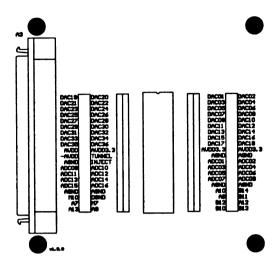

| A.1 | Fabricated Prototype Pin Descriptions | 104 |

| B.1 | Test Station Parts List               | 109 |

## LIST OF FIGURES

| 2.1<br>2.2 | Crossection of a Floating Gate nMOS Transistor              |

|------------|-------------------------------------------------------------|

| 2.3        | Floating Gate Cell Schematic                                |

| 2.4        | Floating Gate Cen Schematic                                 |

| 2.5        | Floating Gate Current Mirror                                |

| 2.0        | roating Gate Current Mirror                                 |

| 3.1        | Circuits with Ground Loops                                  |

| 3.2        | Local Return Paths Only                                     |

| 3.3        | Block Diagram of the Mixed-Signal Test Station              |

| 3.4        | Voltage Regulation                                          |

| 3.5        | Tunneling Control Circuit Schematic                         |

| 3.6        | MAX762 Simplified Schematic Diagram                         |

| 3.7        | Injection Comparator Circuit                                |

| 3.8        | LTC2600 Block Diagram                                       |

| 3.9        | 16-Channel Voltage ADC                                      |

| 3.10       | Precision Current Source                                    |

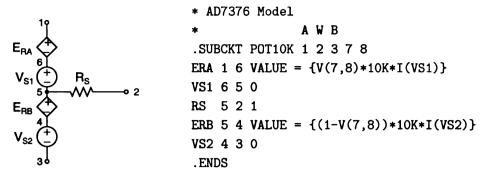

| 3.11       | AD7376 Digital Potentiometer SPICE Model Schematic and Code |

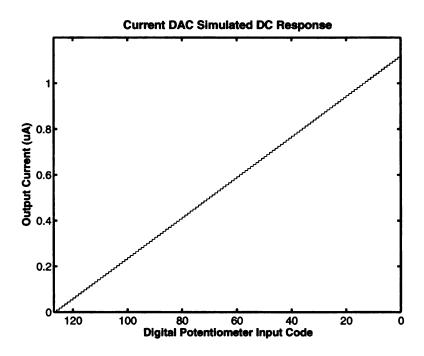

| 3.12       | Precision Current Source DC Response                        |

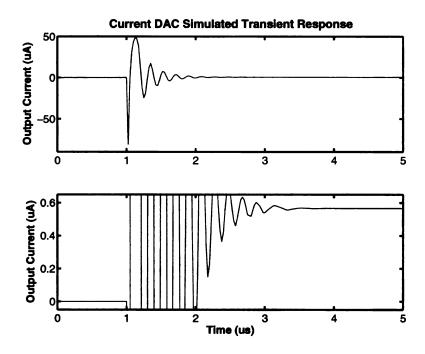

| 3.13       | Precision Current Source Transient Startup Response         |

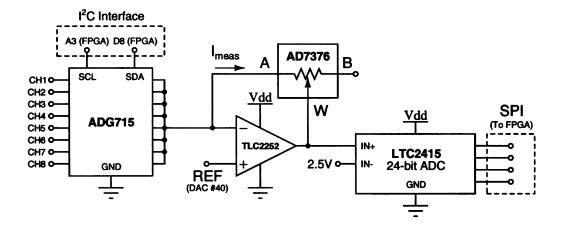

| 3.14       | Current Measurement Circuit                                 |

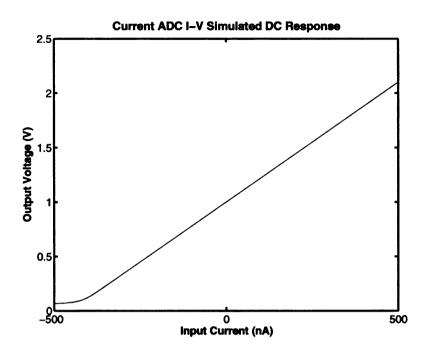

| 3.15       | Current ADC I-V Converter DC Response                       |

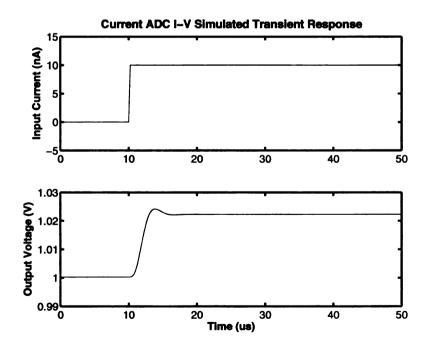

| 3.16       | Current ADC I-V Converter Transient Response                |

| 3.17       | Mixed-Signal Test Station Populated Printed Circuit Board   |

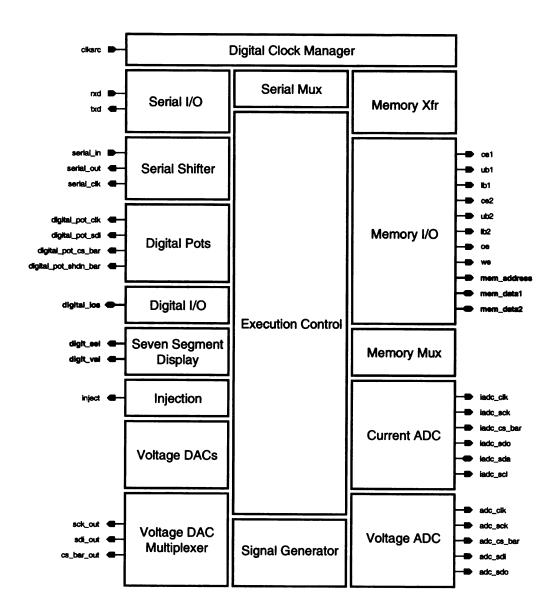

| 4.1        | System Controller Block Diagram                             |

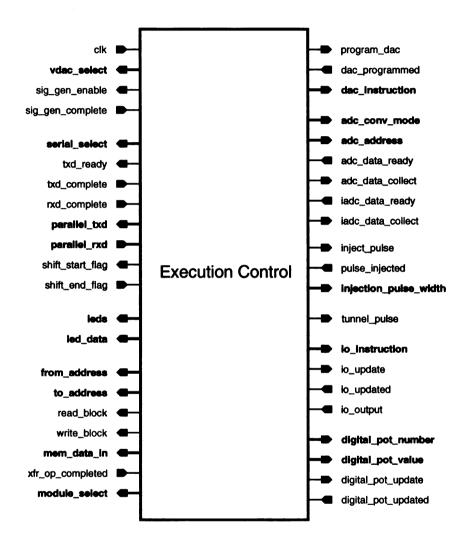

| 4.2        | The Instruction Decoding and Execution VHDL Module          |

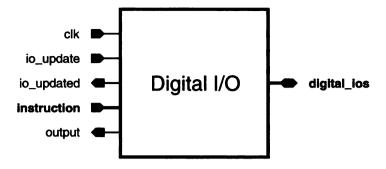

| 4.3        | Digital I/O VHDL Module                                     |

| 4.4        | Digital Potentiometer VHDL Module                           |

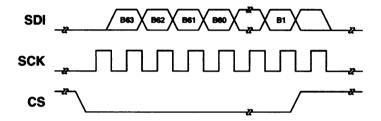

| 4.5        | Digital Potentiometer Serial Peripheral Interface           |

| 4.6        | Current ADC VHDL Module                                     |

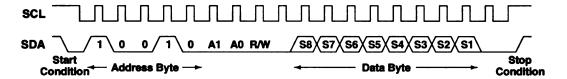

| 4.7        | Current Channel Multiplexer I <sup>2</sup> C Interface      |

| 4.8        | Current ADC Serial Peripheral Interface                     |

| 4.9        | Hot-Electron Injection VHDL Module                          |

|            | Memory I/O VHDL Module                                      |

|            | Memory Multiplexer VHDL Module                              |

|            | Memory Transfer VHDL Module                                 |

|            | Voltage DAC VHDL Module                                     |

| 4.13       | VOITAGE DAO VADD MOUNE                                      |

| 4.14        | Serial I/O VHDL Module 61                                                 |

|-------------|---------------------------------------------------------------------------|

| 4.15        | RS-232 Signal Timing Diagram                                              |

| 4.16        | Serial Multiplexer VHDL Module                                            |

|             | Serial Shifter VHDL Module                                                |

| 4.18        | Seven Segment Display VHDL Module                                         |

| 4.19        | Signal Generator VHDL Module                                              |

| 4.20        | Voltage ADC VHDL Module                                                   |

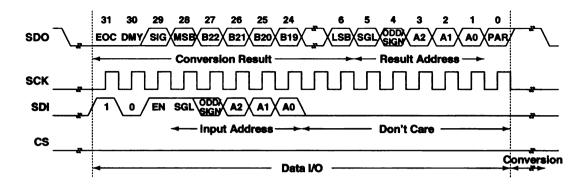

| 4.21        | Voltage ADC Serial Peripheral Interface                                   |

| 4.22        | Voltage DAC Multiplexer VHDL Module                                       |

| 4.23        | Digital Clock Manager Module                                              |

| 5.1         | Tunneling Pulse                                                           |

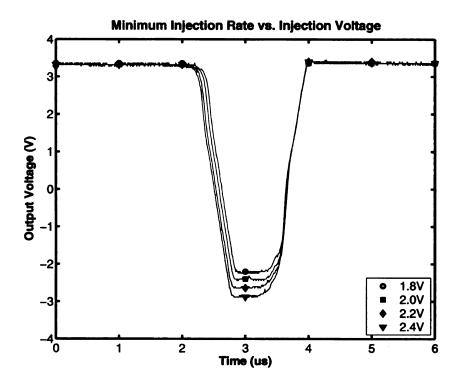

| 5.2         | Minimum Injection Width                                                   |

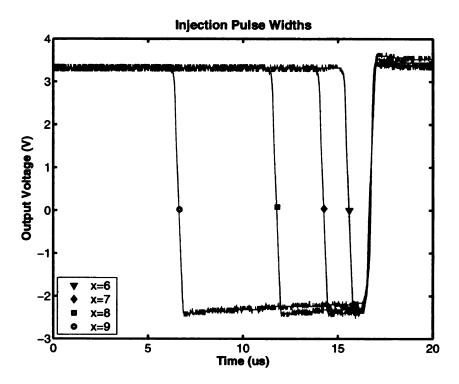

| 5.3         | Injection Widths                                                          |

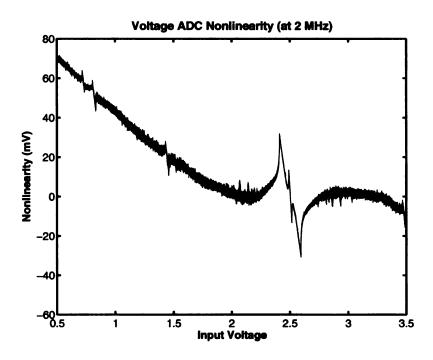

| 5.4         | Voltage ADC Linearity at 2 MHz                                            |

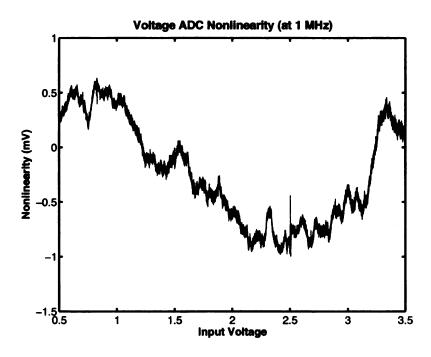

| 5.5         | Voltage ADC Linearity at 1 MHz                                            |

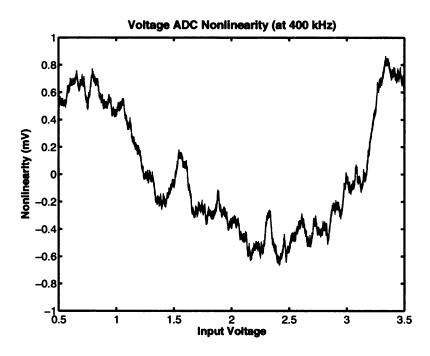

| 5.6         | Voltage ADC Linearity at 400 kHz                                          |

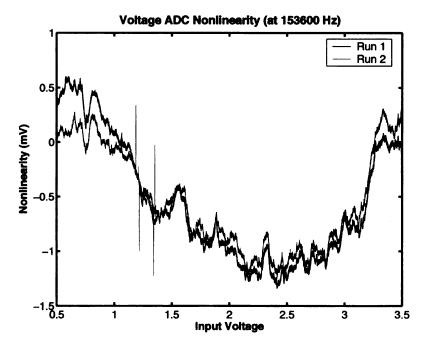

| 5.7         | Voltage ADC Linearity at 153600 Hz                                        |

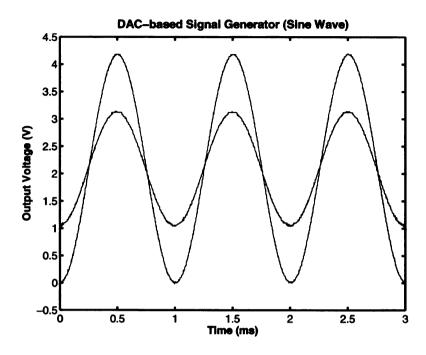

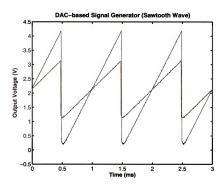

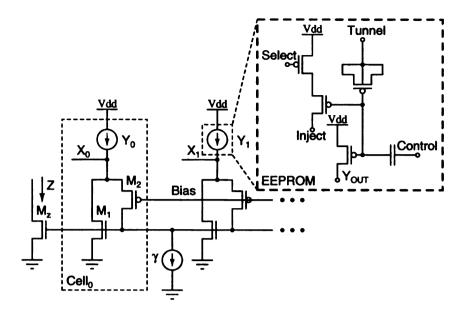

| 5.8         | Signal Generator Sine Wave at 1 kHz                                       |

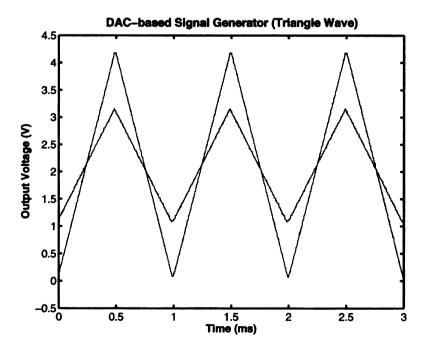

| 5.9         | Signal Generator Triangle Wave at 1 kHz                                   |

| 5.10        | Signal Generator Sawtooth Wave at 1 kHz                                   |

| 5.11        | Signal Generator Square Wave at 1 kHz                                     |

| 5.12        | Floating Gate Programming Test Setup                                      |

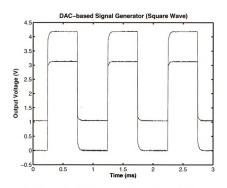

| 5.13        | Analog SVM Chip Photomicrograph                                           |

| 5.14        | Support Vector Simplified Schematic                                       |

| 5.15        | Floating Gate Cell Schematic                                              |

| 5.16        | Unequalized Array of Floating Gates                                       |

| 5.17        | Equalized Array of Floating Gates                                         |

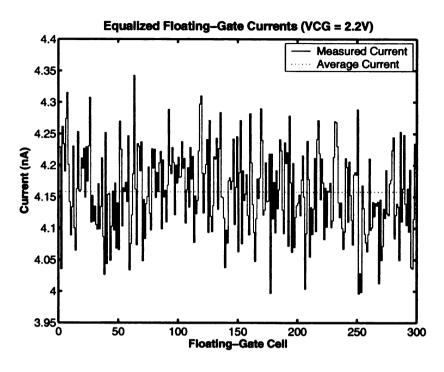

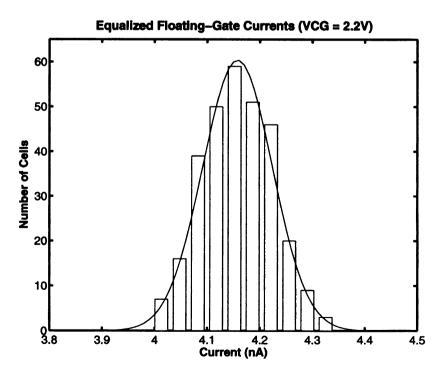

| 5.18        | Floating Gate Equalization Accuracy Histogram                             |

| 5.19        | Equalized Array of Floating Gates at VCG = 2.2 V 89                       |

| 5.20        | Floating Gate Equalization Accuracy Histogram at $VCG = 2.2 \text{ V}$ 89 |

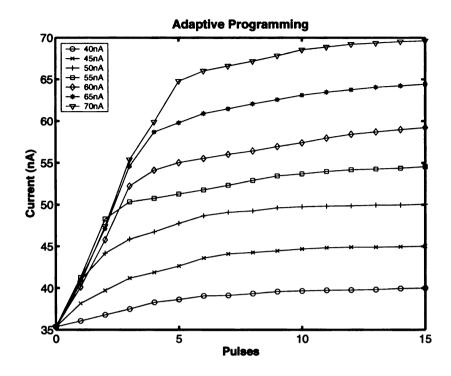

| 5.21        | Adaptive Programming used for Hot-Electron Injection                      |

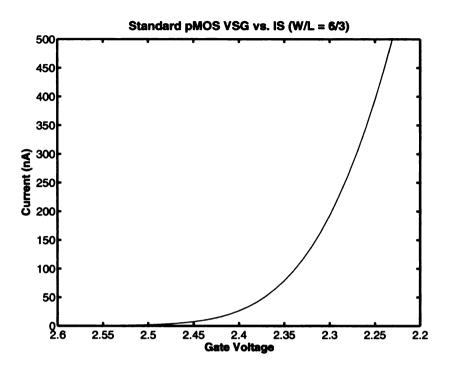

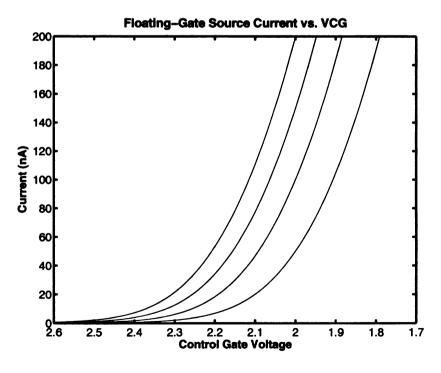

| 5.22        | pMOS Input Stage V-I characteristics                                      |

| 5.23        | Floating Gate MOS Threshold Voltage Modulation                            |

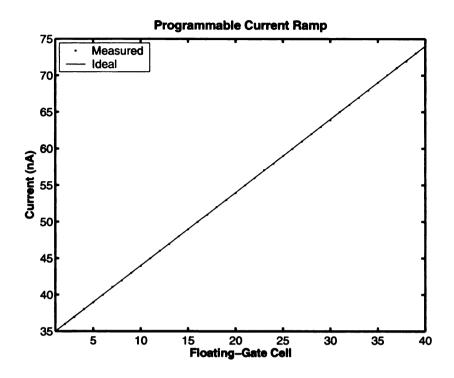

| 5.24        | Floating Gate Current Ramp                                                |

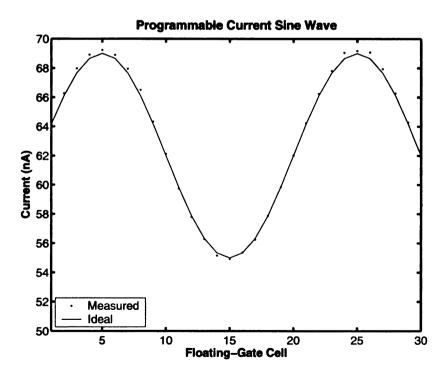

| 5.25        | Floating Gate Current Sine Wave                                           |

| <b>A</b> .1 | Floating-Gate Transistor Layout                                           |

| A.2         | Integrator Layout                                                         |

| A.3         | Shift Register Layout                                                     |

| <b>A.4</b>  | Support Vector Layout                                                     |

| A.5        | Output Stage Layout with Floating Gates and Shift Register | 101 |

|------------|------------------------------------------------------------|-----|

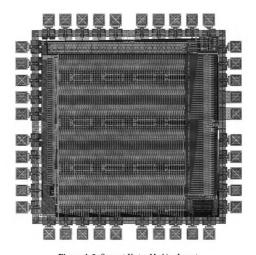

| <b>A.6</b> | Support Vector Machine Layout                              | 102 |

| A.7        | Fabricated Prototype Pin Bonding Diagram                   | 103 |

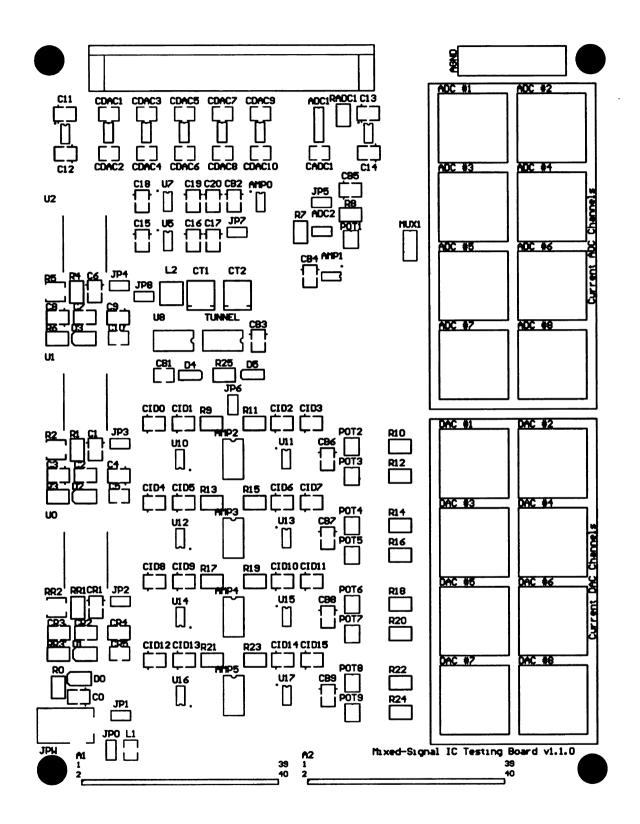

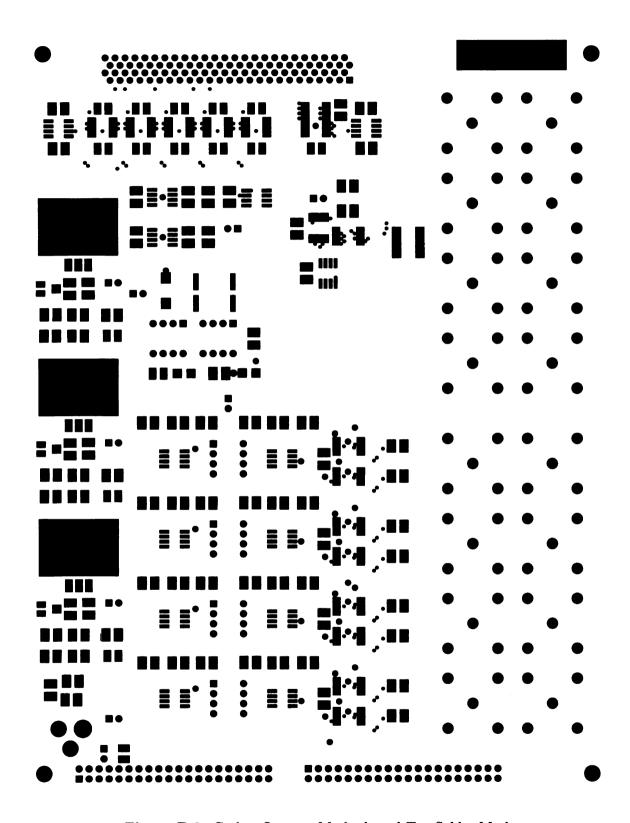

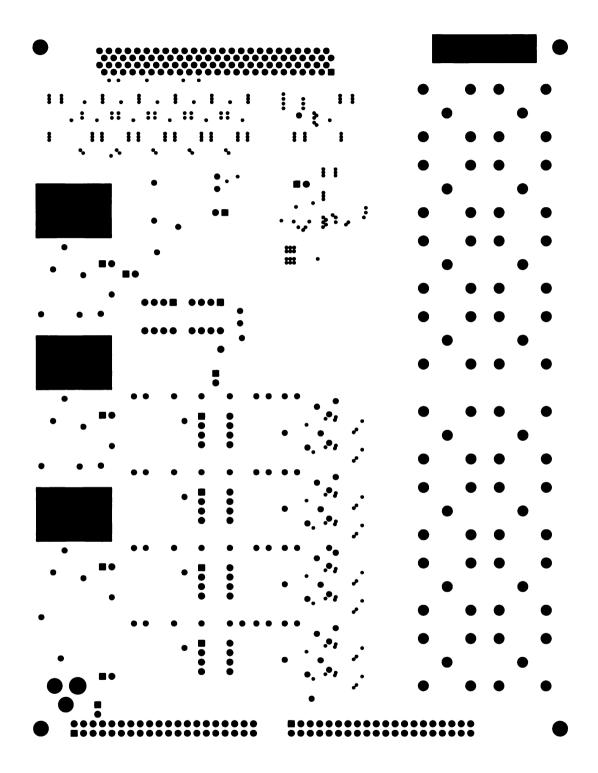

| B.1        | Gerber Output: Motherboard Top Silkscreen                  | 110 |

| B.2        | Gerber Output: Motherboard Top Solder Mask                 | 111 |

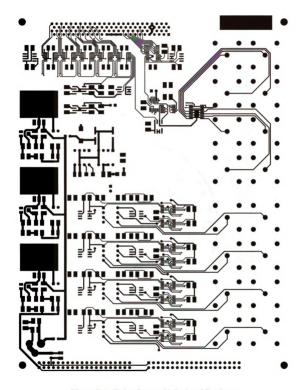

| B.3        | Gerber Output: Motherboard Top Layer                       | 112 |

| B.4        | Gerber Output: Motherboard Middle Layer 1                  | 113 |

|            | Gerber Output: Motherboard Middle Layer 2                  | 114 |

|            | Gerber Output: Motherboard Bottom Layer                    | 115 |

| B.7        | Gerber Output: Motherboard Bottom Solder Mask              | 116 |

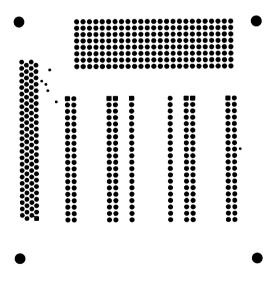

| B.8        | Motherboard NC Drill Output                                | 117 |

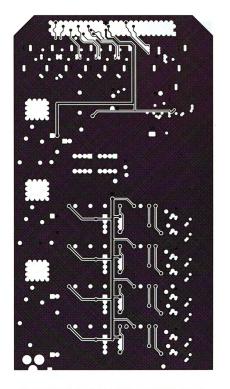

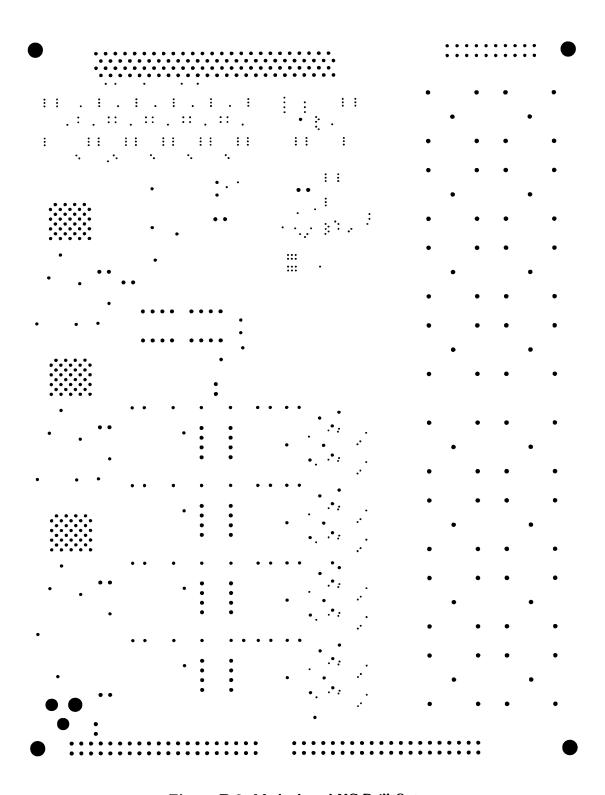

|            | Gerber Output: Daughterboard Top Silkscreen                | 118 |

|            | Gerber Output: Daughterboard Top Solder Mask               | 118 |

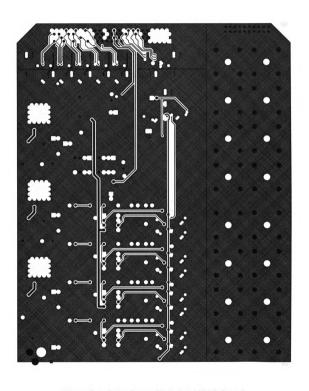

|            | Gerber Output: Daughterboard Top Layer                     | 119 |

|            | Gerber Output: Daughterboard Bottom Layer                  | 119 |

|            | Gerber Output: Daughterboard Bottom Solder Mask            | 120 |

|            | Daughterboard NC Drill Output                              | 120 |

|            | Test Station Connectors                                    | 121 |

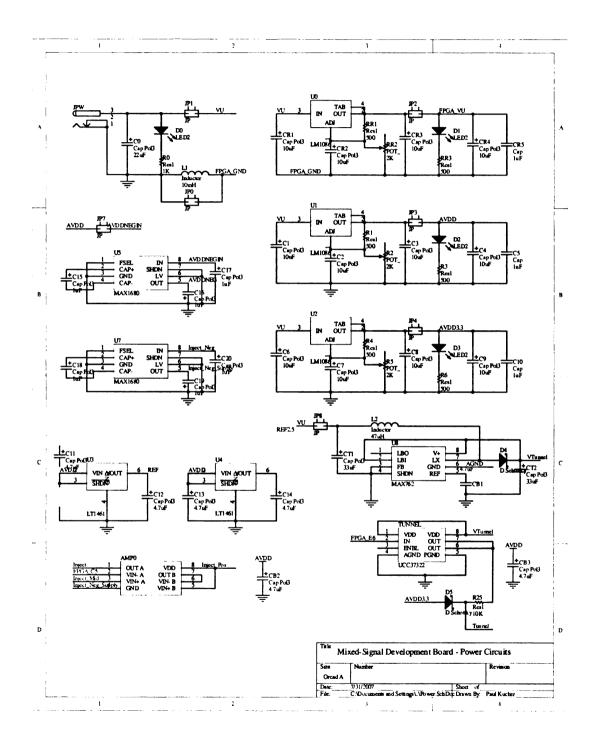

|            | Test Station Power Circuits                                | 122 |

|            | Test Station Voltage Digital-to-Analog Converters          | 123 |

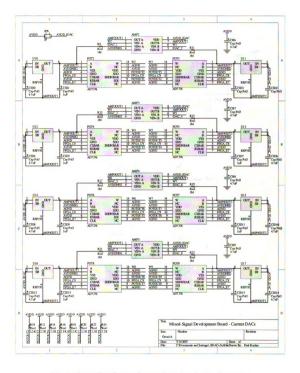

|            | Test Station Current Digital-to-Analog Converters          | 124 |

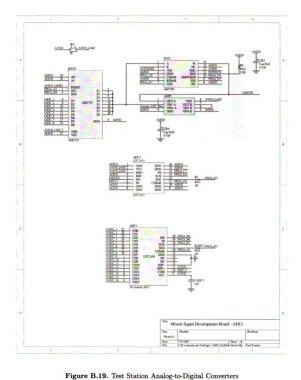

|            | Test Station Analog-to-Digital Converters                  | 125 |

|            | Test Station Daughterboard                                 | 126 |

## CHAPTER 1

## Introduction

Analog VLSI computational methods become an attractive alternative to comparable digital VLSI techniques when systems demand high computational density and do not require high precision [1]. The former is the case in any application whose data depends on multi-dimensional datasets, and generally takes the form of a matrix-vector multiplication (dot product) [2]. These two requirements are the case in many machine learning applications where the output is represented as the confidence of a decision-making algorithm. In the case of digital systems, these algorithms are generally sequential in their execution, and require computationally-intensive operations such as the above mentioned matrix-vector multiplication as well as implementing polynomial functions [3].

Creating ultra-low-power signal processors often requires a substantial portion of the architecture implemented in the analog domain [4]. Additionally, when the input has a resolution of around 10 bits or less, analog computation can have significant advantages when compared to an architecture implemented in the digital domain. For example, there are many application circuits that are both very elegant in their implementation and scalability as well as their power consumption. An example of such a circuit is the winner-take-all or maximum circuit [5]. What appears to be an O(n) problem in a computer science context becomes a parallel operation in analog.

Creating a parallel architecture requires a parallel data store that can allow trained

templates to be directly accessed by analog hardware. In the past, such parameters were implemented as external potentiometers that had to be tuned by hand. Furthermore, this method also used a significant number of external I/O channels, increasing package size and reducing the number of available diagnostic pins [6]. One increasingly popular method involves the use floating gates to store bias currents on-chip. These circuits have the advantage of eliminating off-chip, configurable biases such as DACs or potentiometers, and of implementing them directly in the signal path, eliminating the need for transmission gate multiplexers to share these sources. Additionally, because these circuits are simple in their architecture, they may be densely integrated.

### 1.1 Previous Work

Floating gate devices are traditionally divided into three primary areas: as analog memory elements; as adaptive circuit elements; and as capacitive circuit elements [7]. This section provides an overview of previous work in important selected applications incorporating these three primary uses for floating gate devices. Interestingly, however, many applications fully realize the potential of floating gates. For example, field-programmable analog arrays incorporate both analog memory and trimming elements, as well as capacitive elements. Likewise, SVMs incorporate floating gates as analog memories and as adaptive circuit elements.

#### 1.1.1 Field-Programmable Analog Arrays

Analog integrated circuit (IC) design often requires substantial expertise in the field to design, fabricate, and test a system successfully. Additionally, such work sometimes requires several design iterations, and is therefore expensive and time consuming. The digital design flow includes several tools for the designer, such as hardware description languages, synthesis tools, and field-programmable gate arrays (FPGAs) to test

designs before they are synthesized on-chip for fabrication. However, such tools for the analog designer do not exist, making it difficult to study non-ideal effects such as noise and mismatch.

Modeling and simulation provide a first principle approach for sub-system implementation. Yet, testing will ultimately be required, and for some large-scale designs, is the only means of verifying the entire design. Field-programmable analog arrays (FPAA) have been proposed [8, 9, 10] to alleviate some of these design challenges to allow rapid prototyping of analog designs using reconfigurable hardware.

Reconfigurable analog hardware may sound like an attractive alternative to traditional analog VLSI. However, it has the disadvantage of requiring a larger die area to achieve similar functionality, a problem shared by FPGAs. Additionally, FPAAs have additional parasitics due to switch matrices necessary to route signal paths. These shortcomings lead to higher power consumption and reduced bandwidth, making them impractical for some designs.

Floating gates are attractive for FPAAs because they may be used as switches in the configuration network and may be used directly as analog elements [11]. The impedance of a floating gate is inversely proportional to the number of electrons on the floating node. Thus, the quality of the switch is determined by its finite on and off impedances. FPAAs are comprised of computational analog blocks (CAB), which are analogous to slices in FPGA terminology. The use of floating gates as in-circuit elements leads to a dense architecture, reducing the size of these CABs. This is possible by eliminating the need for on-chip resistors that consume significant area. Additionally, without fixed-value resistors, signal routing complexity is further reduced as a floating gate may act as a variable resistor.

Basic analog building-blocks such as current summation and subtraction, integration, differentiation, amplification, and thresholding may be integrated into a single CAB with few transistors. These CABs include floating gates combined with operational transconductance amplifiers to perform these tasks. Furthermore, floating gates have been used directly in operational amplifiers for offset cancellation through on-chip trimming circuits [12, 13, 35].

Matrix vector multipliers have also been included on FPAAs [14]. The charge on the floating gate can act as a weight and its control gate can act as the input. Signed numbers are represented using a differential pair configuration and if cascaded together across multiple CABs, a matrix vector multiplier may be realized.

Since matrix vector multiplication (MVM) provides the foundation for many machine learning-related operations, specialized hardware for this task has been developed to exceed the performance of a general purpose FPAA hardware. One realization of this approach is in the form of a support vector machine.

#### 1.1.2 Support Vector Machine

A support vector machine (SVM) is a type of supervised learning method for creating functions based on a set of labeled training data. These functions could be for classification or generalized regression [15]. For machine learning applications, SVMs are applied to the classification task, and have been used extensively for recognition with image [16, 17], acoustic [18, 19, 20], olfaction [21, 22], temperature [23], acceleration or vibration [24], and even biomedical signature [25] front-ends. However, these applications have largely been confined to software implementations and on digital signal processors, where speed and storage capabilities are not the limiting factor as on a system-on-chip.

SVMs have only recently been mapped onto analog structures [28], which are becoming viable alternatives to digital signal processors as a means of implementing SVMs in hardware. Utilizing parallel architectures, it is possible to compute the decision score as a single operation, based on the DC response of the system. Furthermore, where speed is not critical, it is possible to bias these circuits in the subthreshold re-

gion at reduced voltage headroom to dramatically reduce power consumption beyond that of digital implementations.

Floating gates become very important template storage elements for analog SVMs since they may be placed directly in the signal path for continuous time classification. Since SVM parameters are represented as floating-point values, they may be directly mapped onto analog hardware as configurable current sources. Additionally, SVM performance may be controlled directly through the bias of the global control gate voltage, which capacitively couples with the floating node to set bias current.

However, before realizing an SVM using analog structures, it is important to understand the training methods used and how they affect chip architecture and floating gate programming. SVM training involves finding the maximum margin between data classes, which means that the classifier attempts to maximize the distance between data points of different classes along the decision boundary (hyperplane), which in turn minimizes error when classifying incoming data points. This topic, along with soft-margin regularization theory, are important when developing the training algorithm [26].

Furthermore, these topics are critical for the designer as they have implications on any hardware implementations, which have both limited resolution and linearity, as well as device imperfections. For example, noise robustness and temperature sensitivity at the circuit-level can affect the generalized performance of an SVM by corrupting SVM parameters through capacitive coupling or temperature-dependent offsets. This often leads to deterioration of the equal error rate, a common figure of merit for SVM performance.

Analog SVMs may also implement a modified variant of the general SVM formulation. One such implementation involves working in the log domain where floating gate parameters are not stored as linear mappings of their floating point representations [27]. Here, the decision surface becomes warped due to circuit topology, resulting in a need for floating gate support vector compensation. The log domain SVM also has the unique advantage of simplifying the hardware implementation by not having to implement the SVM formulation directly and has no inherent temperature dependency. However, it still relies on floating gates for parameter storage, leading to nonlinear noise and temperature dependency.

Analog SVMs are an ideal application for large-scale floating gate programming due to the high demand for accurate and high-density parameter storage to achieve performance on par with digital SVM implementations. However, the need for a large number of support vectors has lead to increasing requirements on die area. In addition, increasing density can also result in reducing the size of the floating gate capacitors, which has implications on resolution, and is discussed in Section 2.6.

In the design of neuromorphic systems [29], SVMs have broad applications. Consequently, analog SVMs are of direct interest to this work, which will be validated through the testing of an analog SVM's floating gate array. Further details on the test chip are given in Section 5.2.

#### 1.1.3 Imagers and Adaptive Sensors

Floating gates also have applications in the feature front-end space of neuromorphic systems. One such application is in active pixel sensors (APS), where traditional machine vision systems separate the image acquisition and processing modules. Inspired from biology, a vision chip that can integrate adaptive elements directly on the imager has the advantage of higher speed and parallelism, and higher integration.

Bandyopadhyay et al. proposed a CMOS transform imager [30] with on-chip floating gates capable of programmable matrix operations and filtering. Here, the floating gates store arbitrary analog waveforms for image transforms and nulling mismatch during matrix operations. These basis function bias generators are stored in a matrix and are multiplexed to the active row of the imager. I-V converters are used to

provide voltage-mode output.

In addition to on-chip filtering, mismatch cancellation is another area of interest in designing APS imagers. Process variation can create undesirable artifacts in the image from a phenomenon called fixed pattern noise (FPN). This leads to random, deterministic spacial noise across the pixel array. FPN has traditionally been eliminated through the use of correlated double sampling, but Wong et al. has proposed a current-mode imager with self-adapting mismatch reduction [31]. Here, floating gates were added at the pixel level. During a calibration step, uniform light was shown on the imager and the pixel output voltages were read. Each pixel was adapted through hot-electron injection to produce a desired constant output voltage under these conditions.

## 1.2 Motivation: Rapid Configuration of Analog Memories

Due to the proliferation of analog floating gate technology and its applications, it becomes increasingly important to have a generalized framework for precision programming of floating gate arrays. As will be discussed in Chapter 2, both circuit topology and process technology will determine programming methods. Thus, a configurable programming interface is necessary to accommodate different mixed-mode designs.

This work aims to provide a testing platform for mixed-signal systems incorporating analog floating gates. This system will implement a generic interface that is easy to use for rapid testing, and is both modular and customizable in its software and firmware interfaces. Finally, the work will validate the performance of the system on a mixed-mode system-on-chip in the form of an analog support vector machine. This thesis will cover the following topics in detail.

## 1.3 EEPROMs for Analog Parameter Storage

This chapter covers the background of non-volatile semiconductor memory technology, how it has been used in the past in the digital domain and the evolutionary steps that have led to the use of floating gates as analog memory elements. The theory of these devices are discussed, including the important hot-electron injection and Fowler-Nordheim tunneling programming and global erasure methods, as well as previous work in the area of floating gate characterization and device limitations.

## 1.4 Floating Gate Test Station Design

This chapter covers the design considerations and implementation of the testing platform required for floating gate programming. Noise and shielding considerations are

discussed, as well as the circuits required on the periphery of a mixed-mode design

incorporating floating gates. Important topics include the design of a precision current measurement system, a tunneling and injection supply and associated control

schemes, a voltage-mode digital-to-analog converter bank for bias and signal generation, and digital interfaces to mixed-signal designs.

## 1.5 Floating Gate Test Station Control

Chapter 4 covers the design of a hardware-based controller using the Xilinx Spartan-3 XC3S200 FPGA. This controller is responsible for providing all serial interfaces to the sub-modules of the test station, as well as instruction interfacing with a PC-based host. All logic has been written using the VHSIC Hardware Description Language (VHDL) and was optimized to minimize slice utilization.

## 1.6 Testing and Results

This chapter begins with the validation of the mixed-mode test platform. Such tests are necessary for calibration of the measurement circuits acting on the periphery of the floating gate chip. Next, the test chip is discussed, outlining the programming methods and some architectural considerations in the testing process. Finally, floating gate results are provided, demonstrating functionality of the complete system.

### 1.7 Conclusions

This thesis concludes with an overview of the work accomplished and some suggestions for future work. Also, further resources are available in the appendices, including layouts from the fabricated test chip, schematics and component lists for the test station, all code used in the hardware controller and PC-based interfaces, as well as testing scripts for the floating gate experiments. A brief tutorial is given on using the software interface.

## CHAPTER 2

## **EEPROMs** for Analog Parameter Storage

An Electrically Erasable Programmable Read-Only Memory (EEPROM) is a non-volatile storage medium typically used to store configuration parameters. EEPROMs have been used for many years in digital systems but have only recently made their way into the field of analog computation. Additionally, EEPROMs have the advantage of data retention for prolonged periods of time, typically ten years or more. This chapter covers the history of PROM technologies through the first digital EEPROM devices, as well as the theory of floating gate transistors and their limitations. This basis will then be used to design an interface for a floating gate programming test platform.

## 2.1 History

#### 2.1.1 PROM

One of the earliest forms of programmable memory is the Programmable Read-Only Memory (PROM), invented in 1956 by Wen Tsing Chow at the American Bosch Arma Corporation for the US Air Force's Atlas ICBM. This memory device utilizes fuses and anti-fuses to either establish an open or short circuit connection, respectively, effectively writing a one or zero permanently to that cell of the device.

For example, if the PROM initially contained all cells programmed to logic zero,

burning an anti-fuse would bridge a connection between the output of the given cell and the chip's supply voltage, establishing a digital high or '1' at the output node. A fuse will likewise produce the opposite effect. It is important to remember that the breakthrough of PROM technology meant that configuration data could be stored onto the integrated circuit post-fabrication for the first time. PROM's greatest advantage is therefore its permanent data retention capability. However, what became PROM's greatest advantage is also its greatest limitation, which lead to the development of erasable non-volatile memories.

#### 2.1.2 **EPROM**

Next came the Erasable Programmable Read-Only Memory (EPROM), invented by Dr. Dov Frohman in 1971. EPROM technology utilizes floating gate transistors, which are described in greater detail in Section 2.2. EPROMs are erased by exposing the die to an ultra-violet light source. This is accomplished by penetrating light with a typical wavelength of 235 nm through a quartz erasing window in the packaging.

Many EPROM chips are mounted inside a plastic rather than ceramic package to reduce costs. These types of EPROM-based circuits are OTP or One-Time-Programmable in that they do not include a quartz window.

#### 2.1.3 **EEPROM**

EEPROM technology is similar to EPROM technology, but does not require an ultraviolet light source for erasure. The methods required for writing and erasing these types of memory cells include injection and tunneling, which are discussed in greater detail in Sections 2.3 and 2.4.

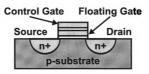

Figure 2.1. Crossection of a Floating Gate nMOS Transistor

#### 2.1.4 Flash Memory

Flash memory has become standard in many consumer electronic devices that require large non-volatile data stores. Flash memory utilizes the same technology of EEPROMs, except they allow erasure of all cells simultaneously. This differs from regular EEPROMs that may program and erase each cell individually. By this definition, analog floating gates with a single erase may be termed analog flash memory, as the tunneling operation is a global function of the programming process.

#### 2.2 Floating Gate Transistors

Figure 2.1 illustrates the crossectional structure of a floating gate transistor. Floating gate transistors are constructed using a traditional MOSFET with an additional gate layer (ELEC in the AMI  $0.5~\mu m$  fabrication technology). Thus, a floating gate is a polysilicon layer encapsulated by silicon dioxide. Charge may then be stored on the polysilicon gate indefinitely, provided that no charge may leak through the surrounding insulator.

Figure 2.2. Energy band of a structure influenced by Fowler-Nordheim tunneling

The voltage of the floating gate is determined by the capacitively coupled input voltage, called the control gate voltage. The amount of charge on the floating gate determines the potential difference between the floating node and the control gate voltage. By increasing the amount of charge on the floating node, the potential across the POLY1-POLY2 capacitor increases, thus decreasing the voltage of the floating node with respect to ground, and increasing the current in a floating gate pMOS device and decreasing current in a floating gate nMOS device. Increasing the charge of the floating node is achieved through a process called hot-electron injection. Charge is removed through a process called Fowler-Nordheim tunneling.

## 2.3 Fowler-Nordheim Tunneling

Fowler-Nordheim (FN) tunneling is a field-assisted electron tunneling method used to remove negative charge from the floating node [32]. When a large potential is applied across a polysilicon-silicon dioxide-silicon structure, typically implemented as a MOS-capacitor, its band structure will be modified as shown schematically in Figure 2.2.

In the presence of a high electric field, electrons in the conduction band of the floating gate electrode will see a triangular energy barrier whose width is a function of the applied electric field. Adequately high electric fields will cause the barrier to become small enough for electrons to tunnel through the barrier and into the  $SiO_2$  conduction band. Equation (2.1) gives the Fowler-Nordheim tunneling current density where h is Planck's constant,  $\hbar = h/2\pi$ ,  $\phi_b$  is the energy barrier at the Si-SiO<sub>2</sub> interface (3.2 eV),  $E_T$  is the electric field at the tunneling interface, q is the charge of an electron (1.6 x 10<sup>-19</sup> C), m is the mass of a free electron (9.1 x 10<sup>-31</sup> kg), and  $m^*$  is the effective mass of an electron in the band gap of  $SiO_2$  (0.42 · m).

$$J = \frac{q^3}{8\pi h \phi_b} \frac{m}{m^*} E_T^2 exp \left[ \frac{-4\sqrt{2m^*} \frac{\phi_b^{3/2}}{3\hbar q}}{E_T} \right]$$

(2.1)

The tunneling mechanism is independent of temperature. However, the number of electrons available for tunneling in the conduction band of the polysilicon gate is dependent on temperature. In addition, the Fowler-Nordheim tunnel current density is exponentially dependent on the applied electric field.

Using Equation (2.1), it is possible to calculate the current density in the AMI C5N process, which has a 13.5 nm gate oxide thickness [33]. Equation (2.2) shows a numerical expression of the tunneling current density with respect to applied tunneling voltage ( $V_T$ ). For 15 V applied at the tunneling pin (and 0 V at the floating gate), it is expected that the Fowler-Nordheim tunneling current density will be 176.2 A/m<sup>2</sup> or 176.2 pA/ $\mu$ m<sup>2</sup>, which translates to 158.6 pA through the 1.5 $\mu$ m/0.6 $\mu$ m MOS capacitor.

$$J[A/m^{2}] = 1.147 \cdot 10^{-6} \left[ \frac{F}{Wb} \right] \left[ \frac{V_{T}}{13.5 \cdot 10^{-9}} \right]^{2} \left[ \frac{V^{2}}{m^{2}} \right] exp \left[ \frac{-25.34 \cdot 10^{-9} \left[ \frac{N}{C} \right]}{\left[ \frac{V_{T}}{13.5 \cdot 10^{-9}} \right]^{2} \left[ V^{2}/m^{2} \right]} \right] (2.2)$$

Although the tunneling current may be estimated by multiplying the current density by the area of the MOS capacitor, this assumes that the current density is uniform across the interface. In fabricated devices, however, this is an unlikely scenario due to fringe fields and device mismatch.

## 2.4 Hot-Electron Injection

Hot-electron injection is a process by which electrons are put onto the floating node by gaining enough energy to surmount the SiO<sub>2</sub> barrier. When the minority carriers that flow through the channel of a MOS device are in the presence of a large source-to-drain bias (for a pMOS transistor), the carriers are heated by this large electric field and their energy distribution is increased. This leads to impact ionization at the drain of the device, generating both majority and minority carriers. The minority carriers are collected at the drain, and can overcome the SiO<sub>2</sub> barrier if they gain sufficient energy. This process moves these carriers from the drain and onto the gate, a process commonly called the hot-electron injection gate current.

It is important to note that with hot-electron injection, it is only feasible to move electrons onto the floating node and they cannot be removed by the same means. A mechanism called hot-hole injection has been demonstrated as a complementary operation to neutralize the negatively charged gate, but is not widely used due to its low hot-hole injection gate current.

There are several models that have been used to characterize the hot-electron injection current such as the lucky, effective electron temperature, and other physical models. However, unlike Fowler-Nordheim tunneling, there is no closed form expression for the gate current and therefore these models are simply quantitative. An empirical model that can be used for programming floating gate arrays was proposed by Bandyopadhyay et al. [34] and is given in Equation (2.3).

$$ln\left(\frac{\Delta I}{I_{S_0}}\right) = K_2\left(V_{DS}\right) \left[ln\left(\frac{I_{initial}}{I_{S_0}}\right)\right]^2 + K_1\left(V_{DS}\right) ln\left(\frac{I_{initial}}{I_{S_0}}\right) + K_0\left(V_{DS}\right) \quad (2.3)$$

Here,  $K_2$ ,  $K_1$ , and  $K_0$  are unitless functions of the source-to-drain voltage and  $I_{S_0}$  is a bias current. This expression has been used to accurately model the best source-to-drain voltage at the injection node during programming to minimize the

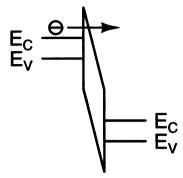

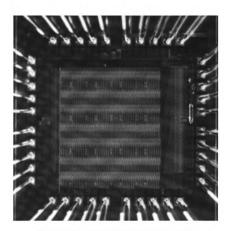

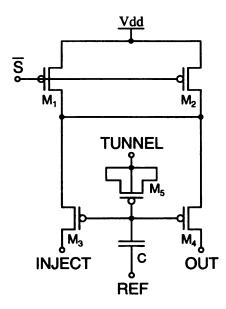

Figure 2.3. Floating Gate Cell Schematic

number of injection pulses.

Figure 2.3 shows the schematic representation of a floating gate cell. Hot-electron injection is achieved by pulsing the drain of transistor  $M_1$ . Transistor  $M_2$  is the MOS capacitor discussed in the Fowler-Nordheim tunneling section. The TUNNEL pin is a global erase, meaning it is tied to all floating gates in the array. In this example, the injection pin is also the cell output current. The REF pin is the control gate voltage which capacitively couples with the floating node to set the gate voltage of the device. The capacitance C is a parallel plate capacitor (shown in layout in Section A.1). It is comprised of a parallel plate (POLY1-POLY2) capacitor separated by an SiO<sub>2</sub> dielectric layer.

## 2.5 Analog Floating-Gate Programming Procedure

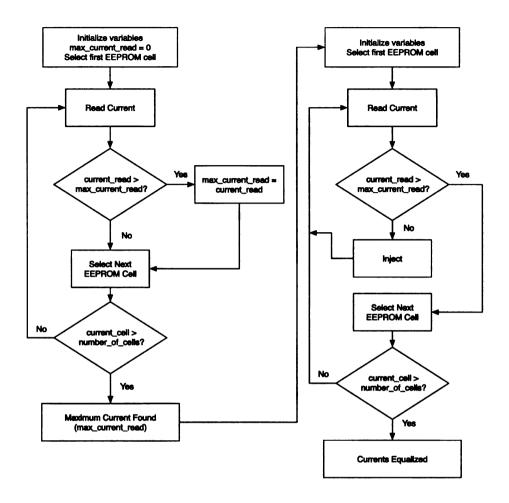

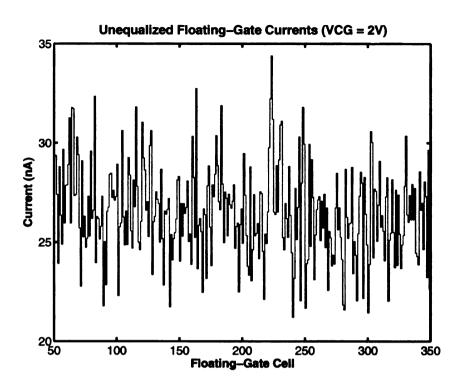

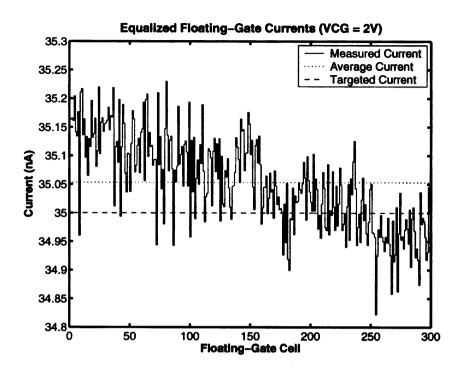

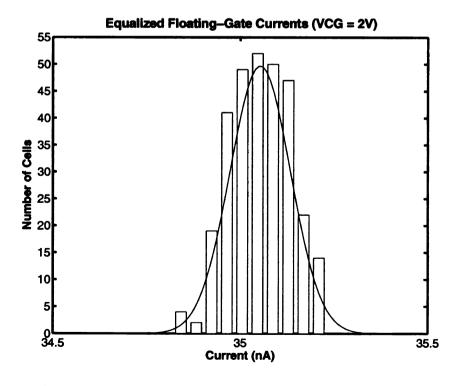

An algorithm to initialize floating gate arrays is given in Figure 2.4. First, the array characteristics must be determined to equalize the floating gate cells to a constant current. This is done by measuring the output source current of each floating gate cell. An initial control gate voltage is chosen such that all floating gates are conducting a measurable current. The maximum cell current in the array is then programmed to every floating gate.

Next, the control gate voltage is increased until the floating gate cells output a

Figure 2.4. Floating Gate Transistor Equalization Procedure

minimally resolvable current. Due to mismatch, not all cells will maintain the initial targeted current during control gate voltage scaling. Thus, the equalization procedure must be repeated. This process continues until the array is equalized at less than 10 nA at an unspecified control gate voltage. Finally, the array is programmed to its targeted current levels specified by the application using the previously discussed hot-electron injection methodology.

## 2.6 Programming Precision

It has been shown that floating gates can reliably achieve an equivalent accuracy of greater than 13 bits of resolution [6]. The accuracy of floating gate programming is highly dependent on the measurement circuit's ability to resolve drain current changes between injection pulses, as well as the minimum charge transfer possible using hot-electron injection. Srinivasan et al. [35] defined a figure of merit (FOM) given in Equation (2.4) and showed that programming accuracy was constant in the subthreshold region and improves in strong inversion.

$$FOM = -\log_2\left(\frac{\Delta I}{I}\right) \tag{2.4}$$

Here,  $\Delta I$  is the minimum change in drain current possible for a given I, or the existing bias current of the floating gate transistor. Essentially, the FOM shows the resolution of an injection pulse, which for the 0.5  $\mu$ m process is between 3.2-4.6 bits up to 1  $\mu$ A of current and increases quadratically beyond this limit. This increase is due to a modified  $\Delta I/I$  relationship as the drain current equation for strong inversion contains an overdrive term that depends on the initial floating gate voltage. Thus, to attain high accuracy, higher floating gate currents are required.

The precision is theoretically limited to the ability to inject a single electron onto the floating gate. In addition, resolution is also determined by the floating gate capacitance  $(C_{FG})$ . Since  $\Delta V_{FG} = \Delta Q/C_{FG}$ , the change in charge will produce a larger change in potential across the floating gate if capacitance is decreased. Thus, larger floating gate capacitors will increase resolution.

With a  $C_{FG}$  of 1 pF, [35] showed it is theoretically possible to achieve 17.82 bits of accuracy with a charge transfer of one electron in weak inversion and 20.09 bits in strong inversion. However, due to the probabilistic nature of hot-electron injection, it is difficult to achieve transfer of a single electron to the floating gate.

#### 2.7 Charge Retention Characteristics

Due to the high quality SiO<sub>2</sub> insulator surrounding the floating node, floating gates have the ability to store charge for long periods of time. Charge retention is limited only by defect densities, which increase under stress such as a high-temperature bake during PCB population or from a high number of injection/tunneling cycles [32]. Following an initial programming cycle, a slight drift in the floating gate current results from interface trap site settling. This loss of charge from the SiO<sub>2</sub> is when backtunneling to the silicon bands occurs. Interface trap density may be reduced substantially, however, through a hydrogen annealing step during device fabrication. Unfortunately, however, this step is not present in a standard digital CMOS process.

Thermionic emission is responsible for long-term charge loss in floating gate transistors and is a function of temperature and time. This phenomenon results when electrons are emitted over the energy barrier toward the control gate or substrate. Equation (2.5) expresses the fraction of charge lost where Q(t) is the floating gate charge at time t, Q(0) is the initial charge, k is Boltzmann's constant  $(1.38\cdot10^{-23}J/K)$ , T is temperature in Kelvin,  $\nu$  is the relaxation frequency of electrons in polysilicon, and  $\phi_B$  is the Si-SiO<sub>2</sub> barrier potential.

$$\frac{Q(t)}{Q(0)} = exp\left[-t\nu \cdot exp\left(\frac{-\phi_B}{kT}\right)\right] \tag{2.5}$$

It can be seen that thermionic emission increases with temperature. Therefore, retention tests typically use a series of accelerated conditions, such as storing the device at temperatures up to 350°C. From these experiments, the relaxation frequency and Si-SiO<sub>2</sub> barrier potential may be extracted. Srinivasan et al. [35] found a  $\phi_B$  of 0.9 eV and  $\nu$  of 60 Hz for the 0.5  $\mu$ m process by plotting Q(t)/Q(0) for temperatures between 250°C and 350°C and applying the data to the above model. Thus, over the course of ten years, a charge loss of 1.14 · 10<sup>-3</sup>% is expected at room temperature

(25°C). Even in extreme environments where device temperatures can reach 100°C, charge retention is still 98.5% over the same period of time. Consequently, floating gates are very attractive as long-term analog storage elements.

## 2.8 Temperature Dependency

Floating gates suffer from the same temperature dependency as a standard MOS device. The carrier mobility and threshold voltage are the predominant temperature-dependent parameters. These are evident in the source current equations for a pMOS transistor in both weak (2.6) and strong (2.7) inversion regions [36].

$$I_S \cong \frac{W}{L} I_{D0} exp\left(\frac{V_{DD} - V_{CG} + V_{FG}}{n(kT/q)}\right)$$

(2.6)

$$I_S = K' \frac{W}{L} \left[ (V_{DD} - V_{CG} + V_{FG} - V_T) - \frac{V_{SD}}{2} \right] V_{SD}$$

(2.7)

In subthreshold,  $I_{D0}$  is a process-dependent pre-exponential constant dependent on  $V_T$  and n is the subthreshold slope factor, which typically 1 < n < 3. Note that Equation (2.6) does not model the moderate inversion transition region. In strong inversion, K' is a process parameter that is dependent on the mobility and capacitance of the gate oxide layer. It can be seen in these equations that the pMOS transistor source current is directly proportional to temperature.

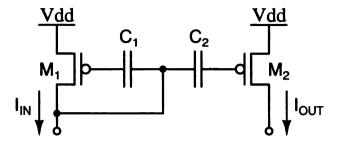

Various topologies have been used to offset temperature dependency in current references. However, these circuits traditionally involve fixing the operating point through fixed-width transistors. One proposed method [37] uses a floating gate as a trimmable element in a temperature-insensitive current source. However, such references will require current mirrors to bias the control gate voltage, and due to device mismatch, mirrors can suffer from offset errors. Figure 2.5 shows a floating gate-based topology for offset removal and was proposed in [38]. Here,  $C_1$  and  $C_2$  act

Figure 2.5. Floating Gate Current Mirror

as programmable multiplicative factors of the mirror. An ideal mirror can be realized by calibrating the floating gates such that both devices have the same threshold voltages.

Using a current reference instead of a fixed voltage bias for the control gate has an additional advantage of being supply voltage invariant, and thus increases the supply rejection capability of the floating gate cell. This is on account of the control gate reference  $V_{CG}$  tracking the source-to-gate voltage of a diode-connected pMOS transistor. Consequently, a direct relationship (neglecting mismatch) may be derived between the fixed reference current and the floating gate output current, scaled by the floating gate voltage  $V_{C2}$  as given in Equation (2.8) below.

$$\frac{I_{OUT}}{I_{IN}} = exp\left(\frac{V_{C2} - V_{C1}}{nkT/q}\right) \tag{2.8}$$

Equation (2.8) gives the output current scaling factor for weak inversion and is based on the difference in charge stored on the floating gate cell and the floating gate reference. Furthermore, it is possible to decrease floating gate currents in relation to the reference current through increasing the charge on  $C_1$ , which may be useful if the sink current  $I_{IN}$  is significantly large.

This analysis has shown that techniques exist to compensate for device and temperature variations in floating gate elements. Although these topologies solve some operational deficiencies, they create new problems such as increased circuit complexity, which leads to calibration and testing challenges. Also, these circuits offer reduced flexibility as the temperature-independent biases must be designed around a target current or a specific region of operation. Furthermore, such bias circuits add to the overall power budget of the chip and must be designed to meet the targeted specifications.

## 2.9 Summary

In this chapter, the fundamentals of erasable programmable solid-state memories were described. The history of non-volatile semiconductor memories was discussed, laying the foundation for an analog memory storage element. Floating gate devices have the ability to replace fixed current sources and sinks in analog integrated circuits. Their flexibility in reprogrammability allows them to be used for not only calibration and trimming, but as template storage, opening up the possibility for on-chip learning.

Next, the mixed-signal test station with automatic floating gate cell programming support will be described. It can be seen that mixed-signal systems-on-chip with floating gate cells require extensive peripheral circuitry. This work aims to provide this support in a modular fashion for rapid design evaluation and validation.

# CHAPTER 3

# Floating Gate Test Station Design

The need for a test station to automatically calibrate floating gate transistors and the difficulty in setting precision current sources for analog computation was outlined in Chapters 1 and 2. The system required to perform the operations of hot-electron injection and tunneling, as well as performing data acquisition for the forward-feedback process of floating gate programming has been carefully designed to meet the targeted specifications. In addition, this system must also be a fully-functional mixed-signal test station, and be able to set the bias conditions for the device under test and provide digital control interfaces. This chapter discusses the design of each subsystem and its targeted performance.

## 3.1 Noise and Shielding Considerations

When designing analog and mixed-signal systems, noise becomes an increasingly apparent limitation when trying to resolve signals in the millivolt and sub-millivolt range. Additionally, noise may not only be a random phenomenon, as detector systems can pick up correlated, spurious signals as well.

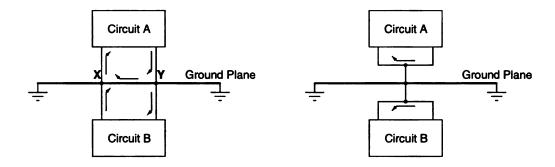

Figure 3.1. Circuits with Ground Loops

Figure 3.2. Local Return Paths Only

#### 3.1.1 Shared Current Paths

The most common type of unwanted signal transfer is caused by ground loops, also known as shared signal paths [39]. Figure 3.1 illustrates shared current paths for two independent circuits. Circuits A and B both have their own dedicated current return paths. However, because current will target the path of least resistance, it will flow through the ground plane. Large currents between nodes X and Y cause a potential difference across the ground plane, inducing an additional voltage at node X.

Figure 3.2 shows an improved layout of circuits A and B that limits current flow in the ground plane to currents entering or leaving circuits A and B only. Each circuit has its own dedicated current return path, so no shared DC path exists, thus limiting any transient spikes on circuit A to affect circuit B.

However, paths need not exist explicitly for ground loops to form. In time-varying signals, parasitic capacitances may exist between these nodes and the ground plane. Thus, spurious voltages are formed on the critical node as a result of AC coupling and charge injection with the ground plane. Furthermore, induction can cause charge injection onto critical nodes as well if they exist between time-varying signals and the return path. Therefore, it is essential to tightly route the signal and its return path, minimizing induction through field cancellation.

Shared current paths have been minimized in layout by connecting all ground and

power pins for each circuit to centralized nets [40]. These nets are connected to the power planes though single or concentrated vias. Furthermore, AC coupling through parasitic capacitance has been reduced by routing time-varying signals away from sensitive DC signals as well as through shielding techniques.

### 3.1.2 Shielding Techniques

One method to reduce the effects of electromagnetic interference is to use contiguous shielding. A contiguous shield is one that completely surrounds sensitive signals, thus attenuating and reflecting the majority of any incident wave. The fraction of the wave that is reflected is given by Equation (3.1).

$$E_{0,r} = E_0 \left( 1 - \frac{Z_{shield}}{Z_0} \right) \tag{3.1}$$

Reflection is high because the impedance of free space  $(Z_0)$  is approximately 377  $\Omega$  and the impedance of the conductor is much lower, thus  $E_{0,r} \approx E_0$ . Additionally, the signal is attenuated because any absorbed wave produces a local current whose magnetic field opposes the incident electromagnetic wave. The total current in the shield decreases as the wave penetrates deeper into the material, and the wave penetration depth  $(\delta)$  may be calculated by the equation given in (3.2) where f is the frequency of the incident electromagnetic wave,  $\mu_r$  is the permeability and  $\rho$  is the resistivity of the conductor.

$$\delta = \frac{1}{2 \cdot 10^{-4}} \left[ \sqrt{cm \cdot s^{-1}} \right] \sqrt{\frac{\rho}{\mu_r f}} \tag{3.2}$$

Thus, if a shield is adequately thick, has a high enough conductivity and low permeability, the majority of the incident electromagnetic interference will be isolated from the inside of the enclosure. Therefore, during testing, a contiguous shield will be placed over the test setup to reduce the effects of light and RF pickup.

In addition to contiguous shielding, additional internal shielding methods are employed to prevent capacitive coupling from transferring interference onto sensitive nodes. The technique employed is called field line pinning and works by placing a conductor between the interfering source and the critical node, thus absorbing the field lines and shielding the node.

This is implemented by placing all digital signals on the bottom layer and analog signals on the top layer. Two inner layers act as ground and supply planes, providing the intermediate conductor. The dielectric material between the outer signal layers and inner planes is fiberglass with a dielectric constant of approximately 4–4.9 and a thickness of 12 mils [41]. Furthermore, the inner planes are separated by a 28 mil core of laminate. Thus, a high capacitance exists between the interference node and the intermediate node, allowing the ground plane to absorb the field lines of noisy digital signals.

### 3.2 System Architecture

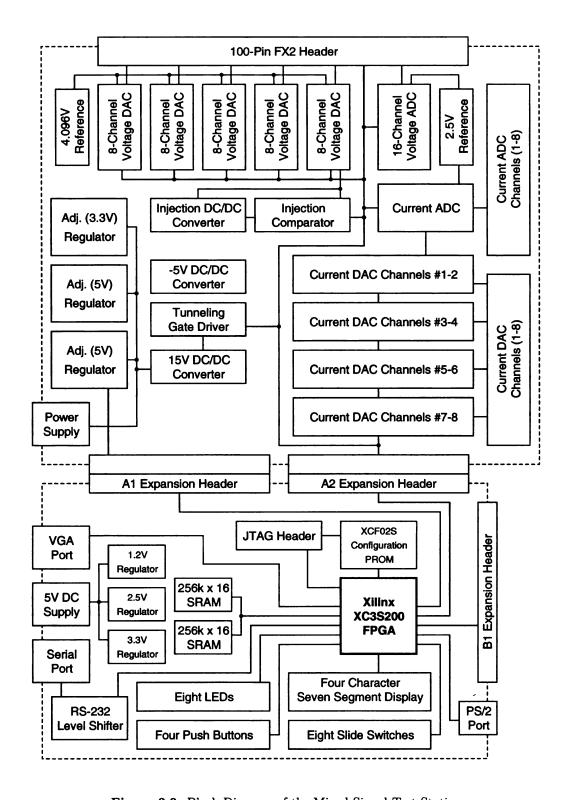

Figure 3.3 shows a block diagram of the mixed-signal floating gate test station and its interface with external digital control via a field-programmable gate array. All voltage-mode channels are passed through a 100-pin connector to an adjacent board that houses the device under test. Current-mode circuits interface through BNC connectors that provide contiguous shielding for noise reduction.

The main digital bus runs vertically on the underside of the board and is responsible for controlling all sub-circuits. In addition, 13 channels of digital I/O are reserved for the 100-pin header, and connect to the daughterboard. Each sub-circuit is discussed in the remaining sections. The FPGA-based controller is discussed in detail in Chapter 4.

Figure 3.3. Block Diagram of the Mixed-Signal Test Station

Figure 3.4. Voltage Regulation

### 3.3 Power Circuits

Proper supply regulation is important because it provides a stable voltage to sensitive analog circuits whose output may become distorted if the power supply rejection ratio is low. Furthermore, it is important to have separate supplies for both analog and digital signals, since Section 3.1 showed that digital switching can cause considerable noise on the supply rail. The board contains three linear voltage regulators and three DC/DC converters. A 15 V boost converter is required for Fowler-Nordheim tunneling in the AMI C5N 0.5  $\mu$ m CMOS process. Additionally, the digital potentiometers and operational amplifiers in the current ADC and DAC circuits require a -5 V VSS supply rail. The hot-electron injection circuit requires a -2 V VSS supply rail. These are provided by two switched-capacitor voltage converters.

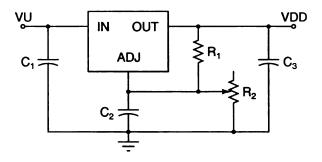

#### 3.3.1 Voltage Regulation

The board is powered by three LM1086 1.5 A low dropout positive voltage regulators [42] using the adjustable topology shown in Figure 3.4. The voltage VU is provided by a 9 V nominal unregulated power adapter with an open circuit voltage measured at 13 V. Capacitors  $C_1$ ,  $C_2$ , and  $C_3$  are 10  $\mu$ F tantalums rated for 16 V. Additionally, resistors  $R_1$  and  $R_2$  make up a voltage divider that allows adjustment of the regulated voltage.

Figure 3.5. Tunneling Control Circuit Schematic

Tuning the regulators becomes important when it comes to precision measurement because it determines the supply rails and reference voltages of the ADCs and DACs. Any small fluctuations will directly affect the scaling of any digital input/output codes.

The three voltage regulation circuits are shown in Appendix B.16. U0 is calibrated to 5 V and can provide power directly to the FPGA development board, eliminating the need for the board's own regulated 5 V supply. U1 also provides 5 V, but is used to supply the test station's own circuits. U2 provides 3.3 V to the test chip, as well as to the Fowler-Nordheim tunneling circuit for the idle voltage.

#### 3.3.2 Fowler-Nordheim Tunneling Supply and Control

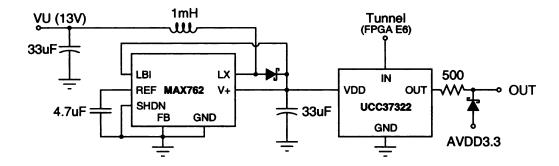

The tunneling supply is provided by the Maxim MAX762 15 V step-up switching regulator [43], which is capable of providing 150 mA of output current at an efficiency greater than 80%. Figure 3.5 shows the configuration of the tunneling supply connected to its control logic via the UCC37322 gate driver [44].

The input voltage range for the MAX762 is 2 V to 16.5 V. To reduce the load on the 5 V regulators, the unregulated supply is connected directly to the boost converter, which also increases the efficiency of the converter by reducing the switching frequency and increasing the gate-to-source voltage of the internal MOSFET. The device is

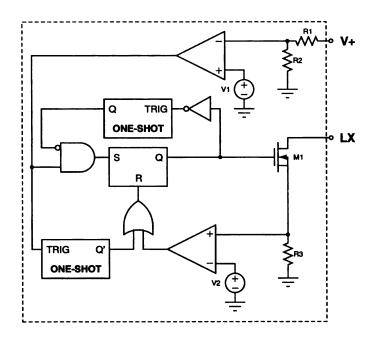

Figure 3.6. MAX762 Simplified Schematic Diagram

operated in the bootstrapped mode, meaning its supply current is drawn through the output node.

Figure 3.6 shows a block diagram of the MAX762's internals, simplified from the datasheet's own diagram to emphasize the features used in the circuit given in Figure 3.5. The basic theory of operation of the device is as follows. The regulated output voltage is set by charging up the 33  $\mu$ F output filter capacitor. This is accomplished by pulse-frequency modulating the LX line. First, LX is pulled to ground, causing current to ramp up inside the inductor. Next, LX is released and becomes a high-impedance node. Since current cannot change instantaneously inside an inductor, the current is forced through the Schottky barrier diode and charges up the output capacitor.

A closer look at Figure 3.6 reveals that there are two primary functions of the MAX762: to detect undervoltages as well as to limit the current flowing through the inductor. Resistors  $R_1$  and  $R_2$  act as a voltage divider and connect to the undervoltage

comparator. This output is fed to an S-R latch as well as a one-shot monostable timer. The purpose of the latch is to determine whether the internal N-channel power MOSFET  $M_1$  should be turned on.

When enabled, the power MOSFET allows the increased current in the inductor to flow through  $R_3$ . When the voltage across this resistor exceeds  $V_2$ , the peak current comparator output goes high. This causes the S-R latch's reset to go high and sets the output Q to low, turning off the power MOSFET. This prevents the chip from sinking more than its 1 A peak current limit.

In addition to a current limit, the MAX762 also limits the "on" pulse width through the one-shot monostable multivibrator at the output of the undervoltage comparator. When the comparator detects a low voltage at V+, the output of the timer goes low for 8  $\mu$ s. This sets the maximum time at which the LX pin is enabled through  $M_1$ . If the peak current is exceeded, the reset on the S-R latch is still tripped via the current comparator.

A minimum delay between pulses is controlled by the second one-shot monostable connected to the output of the S-R latch through an inverter. This disables the S input on the latch for a duration of 1.3  $\mu$ s. After this minimum time,  $M_1$  either remains off if the output is in regulation, otherwise the cycle repeats if the output is out of regulation.

The output of the MAX762 acts as the power supply to the Texas Instruments UCC37322 high-speed, low-side MOSFET driver. The UCC37322 provides an output of either 0 V or 15 V based on input logic issued from the FPGA. The output of this MOSFET driver is connected to a resistor and Schottky barrier diode in series. When the output of the driver is 0 V, the diode prevents the 'OUT' node in Figure 3.5 from falling below one diode drop less than the output of the 3.3 V regulator. The resistor provides a low current path back to the grounded output of the UCC37322.

When the output of the MOSFET driver is 15 V, the diode does not conduct

Figure 3.7. Injection Comparator Circuit

and the 'OUT' node is set directly to the output of the driver. Because the global tunneling pin is a high-impedance node and tunneling currents are on the order of picoamperes, the voltage drop across the resistor is primarily due to the reverse bias leakage of the Schottky barrier diode, which can be in excess of 1 mA.

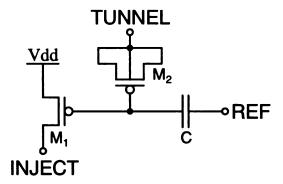

### 3.3.3 Hot-electron Injection Supply and Control

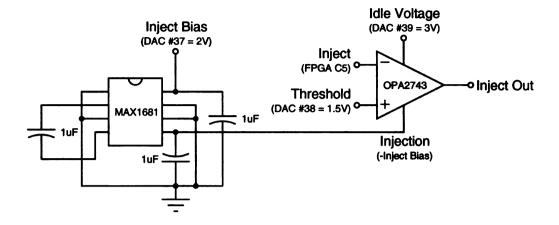

Hot-electron injection is the method used to add charge to the floating gate. Figure 3.7 shows the schematic of a comparator circuit to switch the global injection pin from a user-set idle voltage and the -2 V injection voltage.

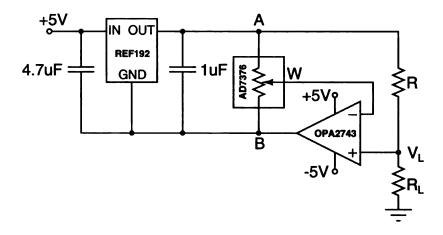

The MAX1681 [45] is a frequency-selectable, switched-capacitor voltage converter that inverts a 2 V input voltage to -2 V for the VSS supply rail on the OPA2743 [46] op-amp comparator. Since the injection current is proportional to the drain-to-source voltage drop across a floating gate transistor, the inverted voltage of the MAX1681 may be adjusted during runtime to modulate the amount of injection current. Thus, both amplitude modulation and pulse-width modulation programming methods are supported. However, the minimum input voltage is 2 V, therefore only larger injection currents are supported.

Since transistors can break down at 8 V in the AMI C5N process, it is not recommended to exceed a 4 V positive voltage input. This is prevented by the 4.096 V precision reference used in the voltage DAC, which is used to set the positive voltage supply of the MAX1681.

The OPA2743 is a high speed, rail-to-rail operational amplifier. The device has a slew rate of 10 V/ $\mu$ s, allowing injection pulse widths as small as 1  $\mu$ s. The positive supply rail is connected to voltage DAC channel #39, and is initialized to 3.3 V during test station startup. The negative supply rail is connected to the output of the MAX1681 and is controlled by DAC channel #37. The threshold voltage for the comparator is set by DAC channel #38 and is configured at startup to 1.5 V, a midpoint for FPGA logic signals.

The injection pulse is provided by the FPGA and uses negative logic. Therefore, when the negative terminal of the op-amp is set to low, no injection occurs and the 'Inject Out' node shown in Figure 3.7 is set to the positive, idle voltage. Likewise, a logic high on the negative input terminal produces the negative, injection bias as output.

### 3.4 Voltage Digital-to-Analog Conversion

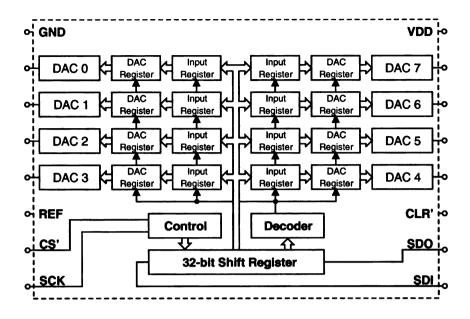

Five LTC2600 octal 16-bit voltage-output DACs [47] are used to provide 40 channels of voltage digital-to-analog conversion. A block diagram of the LTC2600 is shown in Figure 3.8.

The LTC2600 is programmed in a straightforward manner using a serial peripheral interface that is described in detail in Section 4.9. After receiving the update instruction in the 32-bit shift register, a decoder updates the DAC register associated with the selected channel. The ideal output voltage is given by the following transfer function:

Figure 3.8. LTC2600 Block Diagram

$$V_{OUT} = \left(\frac{x}{2^{16}}\right) \cdot V_{REF} \tag{3.3}$$

where x is the input code given in 24-bit binary and  $V_{REF}$  is the reference voltage set via the REF pin.

The REF pin is connected to an LT1461 precision voltage reference [48] set to 4.096 V, which sets the maximum voltage output of each DAC channel. In addition, each channel is capable of sinking or sourcing up to 15 mA, making it an ideal supply for the hot-electron injection circuit.

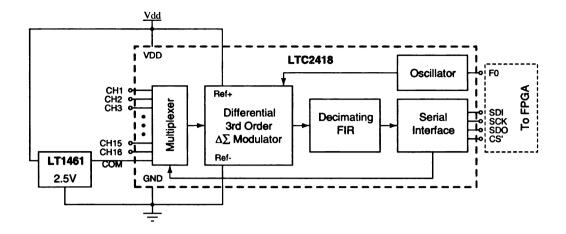

## 3.5 Voltage Analog-to-Digital Conversion