# LIBRARY Michigan State University

# This is to certify that the thesis entitled

# ELECTRICAL IMPEDANCE CHARACTERIZATION OF MICROPOROUS FILMS AT ELEVATED TEMPERATURES WITH INTERDIGITATED DESIGN

presented by

#### **ARJUN JAYARAMAN**

has been accepted towards fulfillment of the requirements for the

| M.S. | degree in  | Electrical and Computer Engineering |  |  |  |

|------|------------|-------------------------------------|--|--|--|

|      |            | <del>-</del>                        |  |  |  |

| ·    | Major Prof | essor's Signature                   |  |  |  |

|      | Ma         | ay 6, 2008                          |  |  |  |

|      |            | Date                                |  |  |  |

MSU is an affirmative-action, equal-opportunity employer

**PLACE IN RETURN BOX** to remove this checkout from your record. **TO AVOID FINES** return on or before date due. **MAY BE RECALLED** with earlier due date if requested.

| DATE DUE                              | DATE DUE | DATE DUE |  |  |

|---------------------------------------|----------|----------|--|--|

|                                       |          |          |  |  |

|                                       |          |          |  |  |

|                                       |          |          |  |  |

|                                       |          |          |  |  |

|                                       |          |          |  |  |

| · · · · · · · · · · · · · · · · · · · |          |          |  |  |

| ·                                     |          |          |  |  |

|                                       |          |          |  |  |

|                                       |          |          |  |  |

|                                       |          |          |  |  |

5/08 K:/Proj/Acc&Pres/CIRC/DateDue.indd

# ELECTRICAL IMPEDANCE CHARACTERIZATION OF MICROPOROUS FILMS AT ELEVATED TEMPERATURES WITH INTERDIGITATED DESIGN

By

Arjun Jayaraman

#### A THESIS

Submitted to

Michigan State University

In partial fulfillment of the requirements

For the degree of

MASTER OF SCIENCE

Department of Electrical and Computer Engineering

2008

#### ABSTRACT

# ELECTRICAL IMPEDANCE CHARACTERIZATION OF MICROPOROUS FILMS AT ELEVATED TEMPERATURES WITH INTERDIGITATED DESIGN

By

# Arjun Jayaraman

A new high temperature four point electrical measurement system was built in order to facilitate electrical impedance measurements on zeolite microporous materials over wide temperature and frequency ranges and particularly in vacuum and gaseous environments. The latter feature is important in sensing applications for microporous materials. Electrochemical impedance spectroscopy (IS) is a measurement technique that treats the sample under measurement as the dielectric in a capacitor. A central component of the system built in this work is an interdigitated planar capacitor (IDC) which was designed so that a large surface area of the material may be exposed to a changing environment. These IDCs were fabricated by combining a photolithographic 'liftoff' technique and Electron Beam Physical Vapor Deposition. Measurements were taken on the zeolite ZSM-5 and its hydrogen counterpart H-ZSM-5.

# **TABLE OF CONTENTS**

| LIST OF TABLES                                                                                                                                                                                         | iii                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| LIST OF FIGURES                                                                                                                                                                                        | iv                         |

| CHAPTER 1                                                                                                                                                                                              | •                          |

| 1.1 Introduction 1.2 A Review of Zeolites 1.2.1Structural Composition 1.2.2 ZSM-5 1.2.3 Applications of Zeoltes 1.2.4 Electrochemical Properties 1.3 Impedance Spectroscopy 1.3.1 Theory 1.4 Summation | 1<br>3<br>4<br>4<br>5      |

| CHAPTER 2 Room Temp Measurements and Interdigitated Design                                                                                                                                             | 14<br>16<br>19<br>21       |

| CHAPTER 3 HEISS Design and High Temperature Measurements. 3.1 System Capability                                                                                                                        | 35<br>36<br>43<br>49<br>55 |

| BIBLIOGRAPHY                                                                                                                                                                                           | 58                         |

# LIST OF TABLES

| Table 1: $\mu = j\omega C_C$ , where $C_C$ is the capacitance of the empty measurement           |    |

|--------------------------------------------------------------------------------------------------|----|

| cell                                                                                             | 7  |

| Table 2: Dimensions and capacitances of the darkfield IDCs                                       | 25 |

| Table 3: Calculated resistance values for the standard load Pt – heater/resistor vs. temperature |    |

# LIST OF FIGURES

| Figure 1: Framework of H-ZSM-5 viewed along [010]2                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: Ideal Cole-Cole impedance plot of the inset circuit8                                                                                                                                                                               |

| Figure 3: Frequency response of electric field on dielectric polarization [8]11                                                                                                                                                              |

| Figure 4: Janus Cryogenic Probe Station15                                                                                                                                                                                                    |

| Figure 5: ZSM-5 probe station results18                                                                                                                                                                                                      |

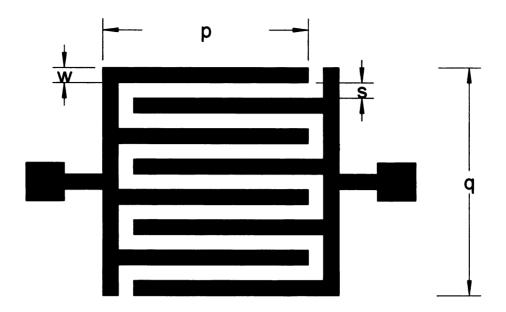

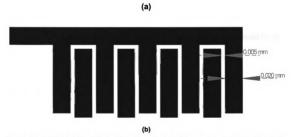

| Figure 6: Layout of the Interdigitated Capacitor. The width (w) of the strips and the spacing (s) between them are shown. The length of the strips is denoted (p), while (q) is the width of the striped area20                              |

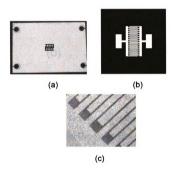

| Figure 7: Early Designs of IDCs. A hard mask is shown in (a), while (b) and (c) are the film mask and an image of the actual IDC used in the probe station experiments, respectively                                                         |

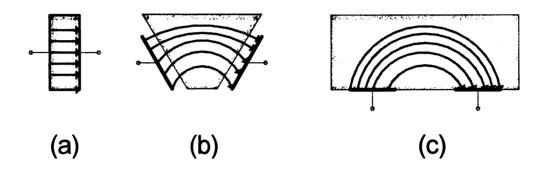

| Figure 8: An Interdigitated Capacitor can be visualized as: (a) a parallel plate capacitor whose (b) electrodes open up to provide (c) one sided access to the material under test. The shaded area represents the sample being measured .22 |

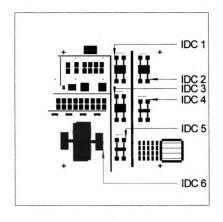

| Figure 9: (a) The Design for the darkfield mask. (b) 500x magnification of the top right corner of IDC 1. The colors are reversed for clarity. The unlabeled structures are for an unrelated project                                         |

| Figure 10: IDCs 1-4 on Quartz30                                                                                                                                                                                                              |

| Figure 11: IDC 2 at 1.063x magnification30                                                                                                                                                                                                   |

| Figure 12: IDC2 at 5x magnification31                                                                                                                                                                                                        |

| Figure 13: IDC 5 at 1.063x magnification                                                                             | 31                       |

|----------------------------------------------------------------------------------------------------------------------|--------------------------|

| Figure 14: Screen Printed H-ZSM-5 on IDC 2 at 1.063x                                                                 | 32                       |

| Figure 15: Screen Printed H-ZSM-5 on IDC 2 at 5x magnification                                                       | 33                       |

| Figure 16: Design of 'High-Temperature Environmental Impedance Spectros System'                                      |                          |

| Figure 17: Circuit schematic for the ceramic heaters (furnace)                                                       | 37                       |

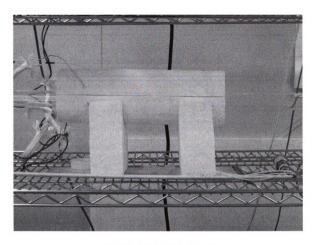

| Figure 18: Ceramic Heater Furnace                                                                                    | 38                       |

| Figure 19: (a) Stainless steel sample stage (b) heated section of the sample stage (c) electrical feedthrough hookup |                          |

| Figure 20, OF Orece                                                                                                  |                          |

| Figure 20: QF Cross                                                                                                  | 40                       |

| Figure 20: QF Cross  Figure 21: Cross-sectional view of the quartz tube                                              |                          |

|                                                                                                                      | 41                       |

| Figure 21: Cross-sectional view of the quartz tube                                                                   | 41<br>42                 |

| Figure 21: Cross-sectional view of the quartz tube                                                                   | 41<br>42<br>ection<br>44 |

| Figure 21: Cross-sectional view of the quartz tube                                                                   | 4142 ection44            |

| Figure 27: System test – 109 Ω resistor in parallel with a 30pF capacitor (compensated data)48                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 28: Test leads in the open circuit configuration. The copper leads are silver pasted49                                                     |

| Figure 29: Measured resistance values for the standard load Pt – heater/resistor vs. temperature51                                                |

| Figure 30: H-ZSM-5 measurements at 685K and 690K. The 690K measurement was taken after the HEISS system had gone through one temperature cycle 52 |

| Figure 31: H-ZSM-5 measurement at 873K53                                                                                                          |

| Figure 32 H-ZSM-5 screen printed on IDC 2 at 5x magnification – post run54                                                                        |

| Figure 33 Equivalent circuit diagram of a coated IDC56                                                                                            |

# **Chapter 1 – Background and Motivation**

#### 1.1 Introduction

This work evolved from a need to evaluate the electrical and ionic conductivity of microporous materials namely, zeolites. Impedance Spectroscopy is a relatively simple and inexpensive technique to characterize a material's dielectric polarization and conductivity. Microporous materials lend themselves to sensing applications because of their environmental sensitivity. Tracking changes in conductivity of zeolites when exposed to a variety of environments will lead to improved sensor designs.

The classic impedance spectroscopy measurement [1] sandwiches the sample under test between two electrodes – in the same configuration as a parallel plate capacitor. An AC signal is applied to the electrodes and a response is observed.

With zeolites as the sample under test, there is virtually no conduction across the electrodes at room temperature because of the high thermal activation energy. Therefore the objective of this thesis is to develop a high temperature measurement system that can take IS measurements at temperatures ranging from 25°C – 900°C. Furthermore, the conventional parallel plate design reduces the sensitivity of the microporous materials to environmental stimuli. Hence another important objective of this work is to develop electrodes which have a planar interdigitated design. The sample under test is used to coat the

electrodes making it possible to expose the sample to environmental stimuli such as vacuum, gas, and moisture.

#### 1.2 A Review of Zeolites

As stated in the introduction, zeolites are microporous materials (or, more accurately, a material which has a microporous continuous framework) [2]. Microporous materials have pour sizes of less than 2nm in size. The name 'zeolite' was coined in 1756 by Swedish Chemist Axel Fredrik Cronstedt using the Greek words that mean "boiling stone" when he heated the naturally occurring mineral Stilbite and observed the mineral 'jump' as the water inside its pores evaporated [2].

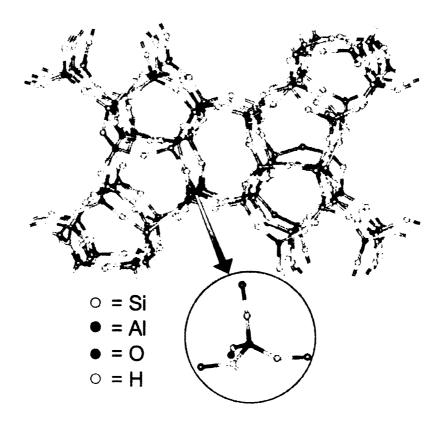

Figure 1: Framework of H-ZSM-5 viewed along [010]

#### 1.2.1 Structural Composition

The zeolites are crystalline aluminosilicates ( $SiO_2/Al_2O_3$  blends) – they are formed by linking the tetrahedra  $SiO_4$  and  $SiO_4$  [2,3,4]. This gives a three-dimensional framework structure in which each oxygen of a given tetrahedron is shared between five tetrahedra. The negative charge of the  $AlO_4^-$  is typically compensated by an exchangeable metal cation. This open framework (Fig.1) allows for water molecules as well as cations to move easily within the crystals leading to ion conduction/exchange and reversible sorption of water [2,3,4,5].

#### 1.2.2 ZSM-5

For these experiments, synthetic zeolites ZSM-5 and H-ZSM-5 have been selected. The reason for this is because of the availability of recent work using these materials [3,4] and also because there is a wide availability of information regarding their common structure.

ZSM-5 and H-ZSM-5 are very silicon like orthorhombic crystal structures. Their pore channels, parallel to [100] together with those parallel to [010], give rise to a three dimensional channel system that can be pictured, as in Fig.1, as a series of overlapping tubes. H-ZSM-5 is the hydrogen form of ZSM-5. This means that the charge compensating cation in H-ZSM-5 is hydrogen as opposed to an alkali metal [3,4].

#### 1.2.3 Applications of Zeolites

The most common applications for zeolites arise due to their ability to sorb gases, vapors, and liquids; to catalyze reactions; and to act as ion exchangers. Their selective pour size and regular pore structure makes it possible for zeolites to act as "molecular sieves" – selectively sorting molecules based on size. Specific uses of zeolites include: gas sensing, petrochemical cracking, oxygen extraction (from air), water purification (softening), solar thermal collection, adsorption refrigeration (wherein the reversible sorption of water is exploited), and desiccation [2].

#### 1.2.4 Electrochemical Properties

Most zeolites are ionic conductors and exhibit poor electrical conductivity with an electronic band gap of approximately 7eV [4]. In an ionic conductor the majority of charge carriers are charged ions rather than electrons – as is the case with metals. The metal cations or, in the case of H-form zeolites, protons are electrostatically bound to the polyanionic host lattice. The motion of exchangeable cations in the zeolite lattice is a "cooperative diffusion process over a heterogeneous system of potential barriers." [3]. Unlike electrical conductivity, ionic conductivity always involves a chemical reaction.

An expression for ionic conductivity in zeolites is derived from the Arrhenius relation:

$$\ln(\sigma T) = A + \frac{E_A}{k_B T} \tag{1}$$

where  $\sigma$  is "dc" ionic conductivity and A is a factor depending on the charge and the number of mobile species, its on-site oscillation frequency and hopping distance.  $E_A$  is the thermal activation energy of the chemical reaction,  $k_B$  is Boltzmann's constant and T is the absolute temperature of the system. The Nernst-Einstein relation correlates the Diffusion coefficient D with the ionic conductivity  $\sigma$ :

$$\frac{\sigma}{D} = \frac{nq^2}{k_B T} \tag{2}$$

where *n* is the number mobile species. Combining equations (1) and (2), Simon et al. have solved for the expression for temperature dependent conductivity in a cubic system which is [3,4]:

$$\sigma(T) = \frac{1}{3} \left[ z_e^2 / k_B T \right] n_i(T) a_0^2 v_0 \exp(-E_A / k_B T). \tag{3}$$

The charge of the mobile charge carriers is denoted as  $z_e$ ;  $n_i(T)$ , the temperature-dependent charge carrier density;  $\nu_0$ , the oscillation frequency of the located charge carrier (also the inverse lifetime of the ionic state);  $a_0$ , the hopping distance between an occupied and an unoccupied lattice site.

# 1.3 Impedance Spectroscopy

The most common method of studying the electrochemical properties of zeolites is known as complex impedance spectroscopy (*IS*). The process detects the dynamic changes of an electrode-sample system. The system is excited by a time-dependent perturbation (an external electric field or applied voltage) into a

non-equilibrium state. The system reacts with a time-dependent physically detectable response i.e. a polarization or current.

The impedance is derived by relating the response to the perturbation. Impedance theory is governed by linear differential equations. Therefore, the electrode-sample system under investigation must be a linear system. Most real world electrode-sample systems exhibit non-linear behavior and IS data is only valid in the range where the response is linear to the perturbation – meaning that a monochromatic perturbation signal must not generate any harmonic signals [1]. The electrode-material system may be modeled with passive circuit components where resistors are generally associated with conductivity paths while capacitors and inductors most often represent space charge polarization regions and specific adsorption and electro-crystallization at an electrode.

The basic impedance equation relates time-dependent voltage and current signals as follows:

$$Z(w) = \frac{v(\omega t)}{i(\omega t)} = R - jX = Z' - jZ''$$

(4)

where R is the "real" resistive component and X is the "imaginary" frequency capacitive component. There are other derived or measured quantities related to impedance and collectively they are known as immittance. IS may also be referred to as immittance spectroscopy. There are three basic immittance equations in addition to the impedance equation (4). The first is admittance:

$$Y = Z^{-1} = G + jB = Y' + jY''$$

(5)

in which G is referred to as the conductance and B is the susceptance. The two other quantities are the modulus function

$$M = j\omega C_C Z = M' + jM'' \tag{6}$$

and the complex dielectric constant or dielectric permittivity

$$\varepsilon = M^{-1} = \frac{Y}{j\omega C_C} = \varepsilon' - j\varepsilon'' \tag{7}$$

where  $C_C = \varepsilon_0 A_c/l$  is the capacitance of the empty measuring cell of electrode area  $A_c$  and electrode separation length l.

Table 1:  $\mu=j\omega C_C$  , where  $C_C$  is the capacitance of the empty measurement cell

| M           | Z                      | Y                                             | ε                                                             |

|-------------|------------------------|-----------------------------------------------|---------------------------------------------------------------|

| М           | μ                      | $\mu Y^I$                                     | $\varepsilon^{-1}$                                            |

| $\mu^{-1}M$ | Z                      | $Y^{I}$                                       | $\mu^{-1} \varepsilon^{-1}$                                   |

| $\mu M^T$   | $Z^{I}$                | Y                                             | μ ε                                                           |

| $M^{I}$     | $\mu^{-1}Z^{-1}$       | $\mu^{-1}Y$                                   | £                                                             |

|             | Μ<br>μ <sup>-1</sup> Μ | $M$ $\mu$ $\mu^{-1}M$ $Z$ $\mu M^{T}$ $Z^{T}$ | $M$ $\mu$ $\mu Y^I$ $\mu^{-I}M$ $Z$ $Y^I$ $\mu M^I$ $Z^I$ $Y$ |

The most common way of displaying IS data is in a Cole-Cole plot [1, 3, 6]. In this plot the two parameters (real and imaginary) of the complex conjugate of are plotted against each other. In general, it is customary to mark the plots with an arrow showing increasing frequency. Cole-Cole plots are two dimensional and does not show a linear distribution of frequency plot points even when they are logarithmically divided.

# 1.3.1 Theory

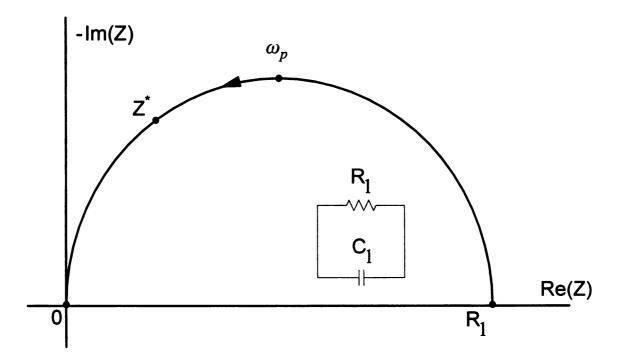

Figure 2: Ideal Cole-Cole impedance plot of the inset circuit

Figure 2 shows a basic ideal impedance arc of an electrode-material system with a geometrical capacitance C1 and a bulk resistance R1 which plots Z\*. The arrow indicates increasing frequency. There is a single time constant for this system which is simply,

$$\tau_D = R_1 C_1 \tag{8}$$

and is the dielectric relaxation time of the basic material.

$$\omega_p \tau_D = 1 \tag{9}$$

where  $\omega_p$  is the peak frequency of the semi-circle and by extension is the point where -Z'' is at its maximum.

There are two basic ways an electric field can interact with a solid material. The applied field can:

1. Transport charge through the material by the translational motion of charge carriers. This leads to a dc conductivity  $\sigma$  and, subsequently, a current density:

$$i = \sigma E \tag{10}$$

Lead to a displacement current resulting from the reorientation of electronic dipole moments (in electrochemistry this is related to complex defects in the material).

$$i = \frac{dD}{dt} \tag{11}$$

In which *D* is the electric displacement:

$$D = \mathbf{\epsilon_0} E + P \tag{12}$$

and E is the electric field and P is the polarization of the dielectric material. When an impedance arc is centered on the real axis, the time dependent polarization P(t) is governed by first-order kinetics resulting in a single relaxation time  $\tau$ .

The analysis of experimental data that produces a full semicircular arc in the complex plane (as in Figure 2) can provide estimates of  $R_1$  and  $C_1$  leading to quantitative results regarding conductivity, reaction rates, and relaxation times. However, experimental data rarely leads to a full semicircle with its center on the real axis. Common reasons as to why a semicircle may not be ideal are as such:

- Because the maximum resistance is greater than zero and leads to the arc not passing through the origin.

- 2. There may be multiple arcs present

- 3. Depressed arcs are frequently displaced below the real axis because of distributed elements in the system. This is caused by the relaxation time not being single valued. It is continuously or discretely distributed across a mean value.

- 4. Arcs can also be distorted by other relaxation times that do not involve the mean time constant being studied. Often, these extraneous relaxation times can vary from the mean time constant by two or three orders of magnitude.

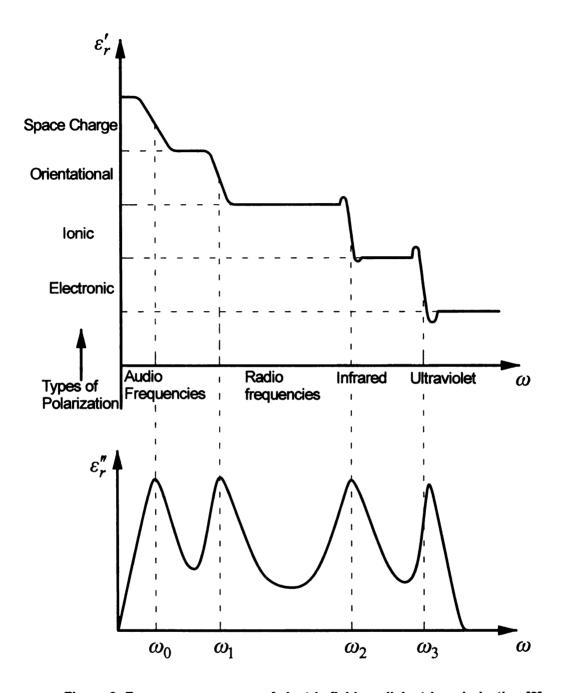

Figure 3: Frequency response of electric field on dielectric polarization [8]

A distribution of relaxation times or dielectric material polarizations may result from topological defects, adsorbed species, or a variation in composition and stoichiometry. There are four basic polarizations in a dielectric material –

electronic, ionic, orientational, and space charge – and are caused by the application of an external electric field. Electronic polarization arises in an atom when the negative electron cloud is displaced relative to the positive nucleus. When ionic bonds are broken, positive and negative ions are separated and ionic polarization results. Orientational polarization occurs when randomly oriented polarized molecules align with the applied external field. The movement of free-conduction electrons may be prevented from moving large distances by barriers such as grain boundaries. When the external field is applied, the electrons 'pile-up' against the barriers and produce a separation of charge that results in space charge polarization.

Figure 3 shows that properties of a pure dielectric material change rapidly at frequencies near a resonant frequency. There are separate resonance frequencies for each type of polarization. The dominant polarization in a material under test changes with frequency leading to a distributed relaxation time shown in its Cole-Cole plot.

These material properties contribute to microscopically small resistances and capacitances over a specific range of frequencies. When modeling a system that includes these some or all of these material properties, one can use transmission line theory or distributed circuit elements. The basic distributed element is the constant-phase element' (CPE) [1, 7].

In IS it is much more common to use distributed circuit elements in modeling systems. The CPE is given as:

$$Z_{CPE} = A(j\omega)^{-\alpha} \tag{13}$$

where A is a pre-exponential factor based on the distribution of time constants. If  $\alpha=0$  the CPE is a resistor and if  $\alpha=1$  then it is a capacitor.

The disadvantages of IS are associated with ambiguities in the circuit fitting process. Many circuit models may fit one material system. This means that all fitting must be correlated with previously obtained data and knowledge regarding the material under test.

Accurate circuit fitting and system characterization are both aided by the use of complex non-linear least squares fitting using the Levenberg-Marquardt algorithm.

#### 1.4 Summation

Recent studies [3,7] have utilized both zeolites and CPE theory to develop environmental sensors. The aim of this work is to demonstrate the design of an impedance spectroscopy measurement apparatus that is able to perform at high temperatures and thereby overcome the thermal activation energy of ionic conductive charges in zeolitic materials. The overall design of the apparatus incorporates a vacuum valve, gas inlet port, and planar interdigitated electrodes for the future creation of a gas sensor.

# Chapter 2 – Room Temp Measurements and Interdigitated Design

#### 2.1 Introduction

This chapter describes the initial room temperature measurements on ZSM-5. A review of Interdigitated Capacitors (IDC) is included to illustrate methods of solving for the IDC's capacitance. This is followed by demonstrating the proper circuit model for the electrode-material system and explaining why it was chosen (based on previous experimental work and theory).

# 2.2 Probe Station Data on Dehydrated and Non-Dehydrated ZSM-5

The first electrical impedance measurements on zeolite material were conducted in a micromanipulated ultra high vacuum system probe station (Figure 4). The probe station is connected to a roughing and turbo pump and can attain a vacuum of (>10<sup>-4</sup> Torr). In the main chamber there is a stage to place samples. The main stage has a small heater-resistor housed underneath it. The maximum temperature the heater resistor can go to is 450K. There are six probes in the chamber that can be adjusted individually in the x, y, z directions. Two of the probes are designed for high frequency microwave measurements. The other four probes are used in lower frequency measurements. These four probes were connected to a low frequency (5Hz – 13MHz) impedance analyzer.

The impedance analyzer has four output connections - an oscillating output, providing a (5Hz – 13 MHz) low voltage (<1V) AC signal designated I+, a low current output channel that was connected to ground in our setup (I–), and two

input voltage terminals (V+ and V-). The impedance analyzer measures the drop across the voltage terminals and divides this drop by the input current and displays the resulting impedance.

Figure 4: Janus Cryogenic Probe Station

The end probes were each arranged on the surface of a simple interdigitated capacitor (IDC), with each pair of digits connected to a contact pad. The sample used in this experiment was the commercially available product of Zeolyst Int. CBV 3024E ZSM-5. The sample  $SiO_2/Al_2O_3$  ratio is 30. Water was added to roughly 0.5g of the powder sample until a paste-like film is formed. The film is then coated evenly on top of the IDC digit pattern. The I+ and V+ probes were placed on one contact pad and the I- and V- were connected to the other.

#### 2.2.1 Measurements and Results

Impedance measurements were conducted across the full spectrum of frequencies (5Hz - 13MHz) with 100 data points, spaced logarithmically, collected on each run. Measurements were taken at room temperature under vacuum (around 6 x10<sup>-4</sup> Torr),

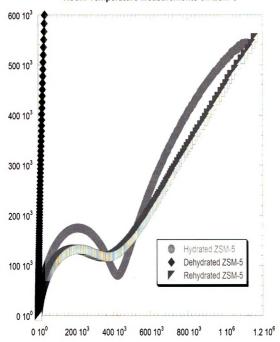

The measured impedance is presented in the form of a Cole-Cole plot (Figure 5). Dehydration of the ZSM-5 resulting from vacuum, leads to a sharp increase in the lossy part of the impedance. This proves that the conductivity of the zeolite material is higher when water is present.

If the objective is to quantify the changes in conductivity with changing levels of humidity present then it is possible to analyze the data in Figure 5 using the simple RC circuit presented in Chapter 1. Two assumptions must be made to facilitate this analysis – First, there can be only one dominant time constant. Second, because of the first constriction, only the higher frequency arc (right most arc) will be analyzed.

Recall from the first chapter that in a simple ideal lumped element RC circuit

$$\tau_D = RC \tag{14}$$

and subsequently

$$C = \frac{\frac{1}{\omega_p}}{R},\tag{15}$$

where  $\omega_p$  is the frequency corresponding to the highest y-data point on the arc. For the 'hydrated arc',  $\omega_{ph}=70.12Krad/s$ . The arc has been fitted with a fourth-order polynomial curve. This curve has been extrapolated to the right so as to find the x-intercept of the curve. This intercept is the approximation of the resistance of the RC circuit. For the hydrated arc  $R_h=435K\Omega$ , solving for the capacitance is simply a matter of plugging these values into equation (14) which gives  $C_h=32.27\,pF$ . Analysis of the 're-hydrated' arc yield these values –  $\omega_{pr}=70.12Krad/s$ ,  $R_r=455K\Omega$ ,  $C_r=30.86\,pF$ .

#### Room Temperature Measurements on ZSM-5

Figure 5: ZSM-5 Probe Station Results. Cole-Cole Plot – where the x-axis is Real(Z) and the y-axis is -lmag(Z).

This data analysis illustrates impedance spectroscopy technique and shows how ionic conduction in this material is facilitated by water. However,

additional studies must be made to this circuit to determine where and how the electrode/sample is most sensitive to environmental changes.

# 2.3 Review of the Interdigitated Capacitor (IDC)

An IDC is a pair of electrodes that resemble two "comb" like interlocking structures [9,11]. As shown in the example in Figure 6 where the black strips represent electrodes, the IDC is a planar device. The electrodes are deposited on a substrate. Over the past two decades there has been an increasing interest in IDCs. Applications of IDCs range from photosensitive detectors, Surface Acoustic Wave (SAW) filters and sensors for chemicals and gasses. Since the long-term goal of this work is to develop an environmental sensor using microporous materials, the IDC serves as an attractive choice for carrying out the impedance spectroscopy measurements. The material under test is usually deposited over the interlocking electrodes. The inherent advantage of the planar IDC in environmental sensing is apparent – only single-sided access to the test material is needed for penetrating the material with an electric field. This leaves the other side of the material open to the environment.

Figure 6: Layout of the Interdigitated Capacitor. The width (w) of the strips and the spacing (s) between them are shown. The length of the strips is denoted (p), while (q) is the width of the striped area.

There have been many generations of IDC designs created as part of this thesis. The first was based on a "hard mask" design that is shown Figure 7(a). This mask was created by etching out a pattern in stainless steel. The mask was placed over a substrate material in the physical vapor deposition chamber and metal was deposited. The metal etching tools that were used in creating mask could not yield an IDC pattern that had the large surface area and small finger size needed for impedance spectroscopy.

The next design investigated is pictured in Figure 7(b). It was created by printing out the desired pattern using a high definition laser printer on transparent film. The film was used in conjunction with the photolithographic liftoff technique that is detailed later in this chapter. The substrate was made out of UV fused silica. A photo of the resulting IDC is shown in Figure 7(c). This IDC was used in the probe station experiments. Sharp patterns on the substrate were achieved

as shown in Figure 7(c), however there were some challenges with these initial designs. The transparency film would degrade rapidly during the processing, and the spacing and width of the lines needed to be adjusted for improved coupling to the sample [9,10,11,12]. To build a more accurate circuit model, and understand how to optimize the design, the theory of interdigitated capacitors was studied.

Figure 7: Early Designs of IDCs. A hard mask is shown in (a), while (b) and (c) are the film mask and an image of the actual IDC used in the probe station experiments, respectively.

#### 2.3.1 Theory

As noted in the introduction, the classic Impedance Spectroscopy experiment utilizes the theory of a parallel plate capacitor – the material under test serves as the dielectric material separating two charge plates. A fringing field planar capacitor has the same principles as the parallel-plate model. Figure 8 shows a gradual transition from a parallel plate capacitor to the fringing field

design [11]. In each case, electric field lines penetrate the material under test – the capacitance and conductance between the two charged electrodes depends on the dielectric properties of the material between electrodes and also on the electrode material and geometry.

Figure 8: An Interdigitated Capacitor can be visualized as: (a) a parallel plate capacitor whose (b) electrodes open up to provide (c) one sided access to the material under test.

The shaded area represents the sample being measured.

In general, the capacitance between two coplanar electrodes (as shown in Figure 8(c)) is quite small and therefore necessitates repeating the pattern many times which increases the overall capacitance of the electrode structure – hence the 'comb' like structure.

The widths chosen for the digits and intervening spaces can affect the Impedance Spectroscopy properties of the device. If the electrode spacing is small, the alternating current flowing between them will sample only the region of the film immediately above them; if the spacing is large, the current will tend to spread out vertically throughout the film thickness, and sample a larger proportion of it.

Otter [10] has described an approximate analytical estimation of the capacitance of an IDC. His analysis is based on the basic equation of  $C = \frac{Q}{V}$ . In this case, C is capacitance, V is the potential, and Q is the charge. They are given by

$$V(x,y) = \frac{4V_0}{\pi} \sum_{n=1}^{\infty} \frac{1}{2n-1} J_0 \left( \frac{(2n-1)\pi s}{2a} \right) \times \sin\left( \frac{(2n-1)\pi x}{a} \right) \exp\left( \frac{(2n-1)\pi |y|}{a} \right)$$

(16)

$$Q = \int_{s/2}^{s/2+w} \sigma_p(x) dx = -\lim_{y \to 0} 2\varphi \int_{s/2}^{s/2+w} \frac{\partial V(x,y)}{\partial y} dx$$

(17)

$$C_{INT} = pq \frac{4}{\pi a} \varepsilon \sum_{n=1}^{\infty} \frac{1}{2n-1} J_0^2 \left( \frac{(2n-1)\pi s}{2a} \right)$$

(18)

where p denotes the length of the striped area and q is the width of the striped area (Figure 6). The sum of s and w is denoted as a.  $J_0$  is the zeroth order Bessel function of the first kind. Otter notes that equation (x) is a good approximation of the capacitance if  $\frac{s}{a} > 0.1$  and reflect a previous work [10] that requires complicated numerical methods.

Figure 9: (a) The Design for the darkfield mask. (b) 500x magnification of the top right corner of IDC 1. The colors are reversed for clarity. The unlabeled structures are for an unrelated project.

Table 2: The dimensions and calculated capacitances of the darkfield interdigitated capacitors

|       | S (µm) | w (μm) | s/a   | p (mm) | q (mm) | $C_{INT}(pF)$ |

|-------|--------|--------|-------|--------|--------|---------------|

| IDC 1 | 20     | 5      | 0.2   | 4.175  | 4.640  | 42.10         |

| IDC 2 | 20     | 20     | 0.5   | 4.160  | 2.920  | 10.22         |

| IDC 3 | 10     | 10     | 0.5   | 4.180  | 2.900  | 20.31         |

| IDC 4 | 50     | 5      | 0.909 | 1.475  | 5.300  | 10.14         |

| IDC 5 | 50     | 50     | 0.5   | 1.430  | 2.900  | 1.396         |

| IDC 6 | 500    | 100    | 0.167 | 7.500  | 17.00  | 12.38         |

# 2.3.2 Experimental Procedure

The current mask is a darkfield photomask (Figure 9). There are six IDCs. Their dimensions and calculated theoretical capacitances, based on equation (18), are shown in Table 2. The capacitance was calculated using Mathcad and the first 500 terms were summed. The dimensions of IDC 3 were based on an IDC designed in [13] which had a measured capacitance of 23*pF*.

#### Lithographic Procedure:

#### Quartz Clean

- 1. Soak substrate in the De-Metal bath  $HCl: H_2O_2: H_2O 1:1:6$  at 55°C for 1 minute

- 2. Soak substrate in the De-Grease bath  $NH_4OH: H_2O_2: H_2O-1:1:6 \text{ at } 55^{\circ}\text{C for 1 minute}$

- 3. Sonicate substrate in acetone for 5 minutes

- 4. Soak substrate in methanol for 45 seconds

- 5. Soak substrate in de-ionized water for 45 seconds

- 6. Bake substrate at 70°C for 25 minutes

# Photolithography

- Spin Shipley Microposit S1813 Positive Photoresist at 3000 rpm for 30 seconds

- 2. Bake substrate at 70°C for 25 minutes

- 3. Inspect with Zeiss differential interference contrast microscope

- Align substrate with soda-lime mask using Suss MJB3 Submicron

Mask Aligner

- 5. Expose substrate with UV light for 1 minute

- 6. Soak substrate in chlorobenzene for 1 minute

- 7. Develop in MF-319 Developer for 2.5 minutes

- 8. Rinse substrate with De-Ionized water for 1 minute

- 9. N<sub>2</sub> dry substrate

- 10. Inspect with Zeiss differential interference contrast microscope

# **Physical Vapor Deposition**

- Clean inside of the PVD chamber using methanol and clean-room wipe.

- 2. Unscrew the hold down ring from sample stage.

- 3. Place quartz substrate on sample stage and fastened using two razor blades that are screwed in to sample stage.

- 4. Start the system by turning main power switch to 'start'

- 5. Switch on motor switch on outside of chamber door.

- Carefully turn the sample stage so that substrate is facing down.

Make sure substrate does not fall.

- Turn of motor and return sample stage to its original position.

Close chamber door.

- 8. Turn on the N<sub>2</sub> tank that is attached to system

- 9. Open the e-beam target holder by unscrewing large set screws.

- 10. Open the e-beam shutter by turning appropriately titled knob on main panel.

- 11. Place individual graphite crucibles, one filled with gold other filled with tungsten, into two open slots in uncovered target holder.

- 12. Make sure to remove any excess debris in target holder area.

Close the shutter and return target holder to its original position and tighten set screws.

- 13. Make sure the HI-VAC throttle valve is open and HI-VAC valve is closed.

- 14. Pump down chamber to approximately 5X10<sup>-6</sup> Torr. Monitor pressure with ion gauge.

- 15. Once this achieved, turn on the water chiller unit. Set temperature to 20 deg C and the pressure to 65-70psi

- 16. Rotate stage approximately 45 degrees until stage mirror shows crucible holder.

- 17. Open the e-beam shutter and make sure the target metal is reflected in stage mirror.

- 18. Turn on the power switch at the bottom system. This is for e-beam gun.

- 19. Everything is working properly if all 5 interlock LEDs are turned on.

- 20. Turn up current very slowly to around 10mA or whenever e-beam becomes visible.

- 21. Position the beam on target metal (titanium) and turn off e-beam.

- 22. Rotate stage so that it is 180 degrees from its original position and turn on deposition monitor. Make sure displayed thickness has been reset to zero.

- 23. Turn on the e-beam current and slowly adjust so that displayed deposition rate is 0.5 Angstroms per second.

- 24. Once desired thickness has been achieved (10 nm), turn down current on the e-beam and shut it off. Wait until deposition rate is at zero before closing e-beam shutter.

- 25. Repeat steps 16-24 for a gold target (200 nm)

- 26. After final deposition, wait 45 minutes with chiller and vacuum running to allow for e-beam gun to cool down.

- 27. Turn off vacuum

- 28. Wait for green lights on vacuum control panel to turn off.

- 29. Vent system and turn off chiller.

- 30. Remove substrate from chamber and turn off system.

# Liftoff

- 1. Dry the substrate with N<sub>2</sub>

- 2. Soak and gently agitate gold covered substrate in acetone for 2 minutes

- 3. Inspect with Zeiss differential interference contrast microscope

- 4. If the interdigitated pattern does not look clean repeat steps 2-3

- 5. Rinse substrate with De-Ionized water for 1 minute

- 6. Dry the substrate with N<sub>2</sub>

- 7. Place in High Temperature Furnace (outlined in chapter 3). And anneal in vacuum at 450°C

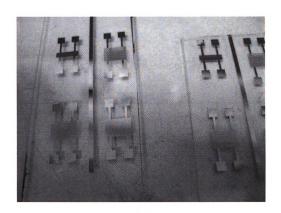

Figure 10: IDCs 1-4 on Quartz

Figure 11: IDC 2 at 1.063x magnification

Figure 12: IDC2 at 5x magnification

Figure 13: IDC 5 at 1.063x magnification

31

The results of the process are displayed above. Figure 10 shows two quartz substrates (2" x 1") which have IDC(s) 1-4 printed on top. The IDCs are cut into individual pieces using a diamond wheel saw. IDC 2 is shown in Figures 11 and 12 and IDC 5 is shown in Figure 13. Both of these Interdigitated capacitors produced small DC resistances (approximately  $10\Omega$ ) across electrically connected contact pads and open circuit conditions ( $<2M\Omega$ ) for contacts that were not connected. However, because of the smaller test area and capacitance of IDC 5, IDC 2 was chosen for the initial high temperature measurements.

Figure 14: Screen Printed H-ZSM-5 on IDC 2 at 1.063x magnification

Figure 15: Screen Printed H-ZSM-5 on IDC 2 at 5x magnification

#### 2.3.3 Zeolite Coatings

The new IDCs are coated with a zeolite/water suspension using a t-shirt silk screen. The suspension is made by measuring out 100ml of ZSM-5 powder with just enough water to ensure a 'paint like' consistency - usually around 20 ml of water. The contact pads of the electrodes are covered with Kapton tape so that the zeolite only covers the interdigitated 'fingers.' The screen is then placed onto the IDC and the zeolite suspension is spread on top of them. A squeegee is used to ensure that there is a zeolite layer of uniform thickness across the substrate. Much of the water is strained out of the pores of the zeolite by this process. This means that these new films will exhibit lower conductivity than the previous films.

It has been shown [13] that at a temperature of 493K, the ZSM-5 is completely dehydrated and at 673K the thermal activation of the material allows for ionic conductivity[3]. The next chapter deals with the design and implementation of high temperature measurement system to investigate the immittance parameters of ZSM-5 and H-ZSM-5 at elevated temperatures.

# **Chapter 3 – HEISS Design and High Temperature Measurements**

The thermal activation energy required for ionic conduction in dehydrated zeolites is quite high – for H-ZSM-5 this occurs around 400 °C [3, 4]. In order to facilitate the observation of this phenomenon it became apparent that the cryogenic probe station would need to be replaced by a high temperature measurement apparatus. The design, construction, and characterization of this system is discussed in detail here and is the hallmark of this work.

# 3.1 System Capability

The intent of the high temperature measurement apparatus is to accurately take a four-point electrical measurement at temperatures in excess of 400 °C. Specifically it must be able to house a planar interdigitated capacitor and raise the ambient temperature precisely – a digitally controlled measurement oven with a planar stage. This apparatus must contain heat effectively so as not to adversely influence the surrounding environment in particular the impedance analyzer. Such an apparatus will allow exploration of ionic conduction in microporous films. It is hoped that these results will be used to investigate how changing environmental conditions affect conductivity with the ultimate goal being the development of a gas sensing application. Therefore, the measurement apparatus contains a gas inlet valve and a vacuum port so as to create an isolated environment for electrical impedance measurements.

# 3.2. System Design

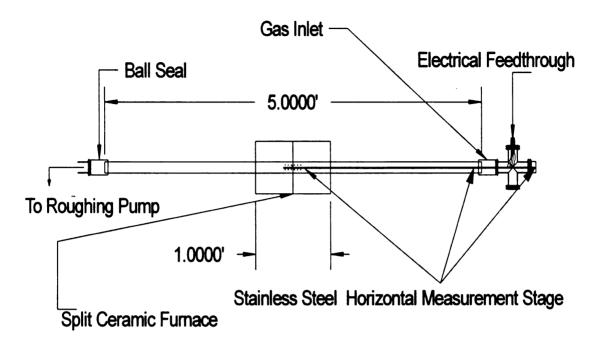

Figure 16: Design of 'High-Temperature Environmental Impedance Spectroscopy System'

The measurement system, which has been dubbed the 'High Temperature Environmental Impedance Spectroscopy System' (HEISS), is drawn in Figure 16. The system consists of a 5' quartz tube that has been inserted into two 1' long semi-cylindrical heaters. The quartz tube has a ball seal joint on either end of it that clamp into stainless steel quick flange (QF40) components. One end of the tube leads to a roughing pump and the other to a stainless steel quick-flanged cross that contains a multi-pin copper/nickel electrical feedthrough, a gas inlet valve, and a stainless steel horizontal stage which extends into the middle of the

furnace section of the tube.

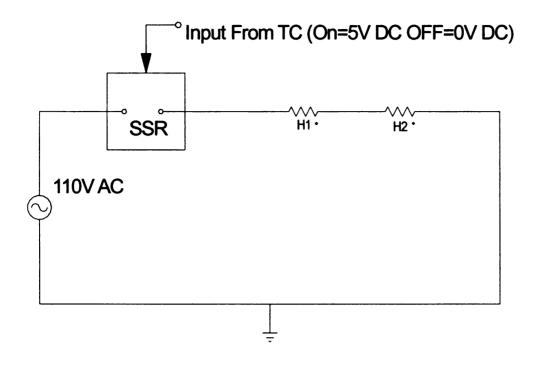

Figure 17: Circuit schematic for the ceramic heaters (furnace)

The ceramic semi-cylindrical heaters are evenly split sections of a tube furnace. They are made of ceramic fiber and imbedded with helically wound iron-chrome-aluminum heater wire and have been purchased from Omega Engineering. The heaters are connected in series as illustrated in Figure 17 – where they are represented by resistors H1 and H2. A solid state relay controls the current flow to the heaters via a temperature controller. The temperature controller determines the temperature of the furnace through a high temperature Type K thermocouple inserted between the two heater sections. If the ends of the heaters are filled with insulation, it is possible to raise the temperature inside the furnace to 950 °C.

Figure 18: Ceramic Heater Furnace

However, when the quartz tube is inserted (Figure 18) the maximum temperature is reduced to 650 °C. Quartz has a very low thermal conductivity [15], so the ends of the system remain near room temperature even when the furnace is set to its highest temperature.

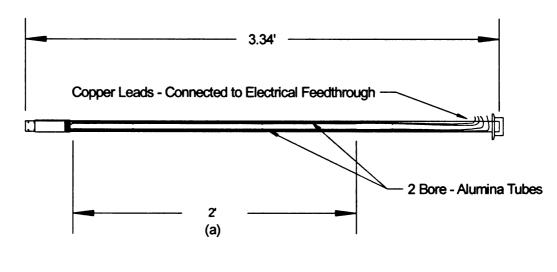

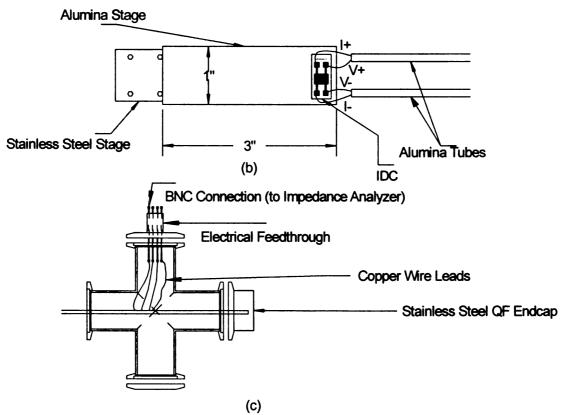

Figure 19: (a) Stainless steel sample stage (b) heated section of the sample stage (c) electrical feedthrough hookup

Figure 20: QF Cross

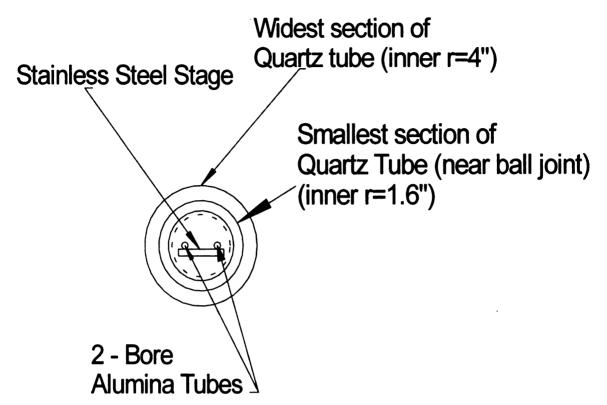

Figure 21: Cross-sectional view of the quartz tube.

Illustrated in Figure 19, this horizontal sample stage has two 2' 2-bore alumina tubes extending to the middle furnace section of the quartz tube that are tied down with 10 mil wire. These tubes contain four 10 mil copper electrical leads which are connected to the electrical feedthrough at the top at the quick flanged cross. Figure 21 shows a cross-sectional view of the quartz tube. The feedthrough has four BNC female adapters soldered to its outer pins; this allows the leads to be connected to the HP4192A LF impedance analyzer.

Figure 22: LabView Impedance Analyzer Program (front panel)

The impedance analyzer is controlled through a 'general purpose interface bus' (GPIB) by a LabView program that was initially designed by myself but was improved upon by Adam Downey. Figure 22 shows the front panel of this program. The program can set the analyzer measurement method (Impedance, Resistance, Inductance, or Capacitance). The frequency sweep mode: linear – where the difference between two adjacent frequency points is held constant throughout the sweep – or logarithmic – in which the sweep is logarithmically spaced. In addition, the user is able to select start and stop frequencies (anywhere from 5Hz to 13MHz), the total amount of points in a sweep, whether

or not to clear the analyzer's internal memory and how long to wait between setting a frequency in the analyzer and collecting the associated impedance value. The impedance sweep is collected in a comma delimited text file and saved to a user-specified location.

#### 3.3 Calibration and Results

The HEISS degrades the accuracy of the impedance analyzer by its characteristic impedance mismatch to the HP4192A. Error correction is needed to improve the signal. The HP4192A is equipped with an internal spot frequency Open/Short compensation function called the Zero-Offset Adjustment. It measures the residual impedance of a test fixture under short circuit conditions and stray admittance under open circuit conditions [16]. The HEISS is a custom-made test fixture with non-standard length cable test leads and so the Open/Short compensation would not provide adequate error correction. Adding a standard load to the compensation function improves the accuracy and repeatability of the measurement [17].

# 3.3.1 Room Temp Compensation

The calibration for the room temp uses solder to connect the I+ and I-leads and separately connect the V+ and V- leads for the open calibration. The first step is to see if the impedance analyzer works with the 2m BNC cables that are used in the system (Figure 20). The test uses a 47  $\Omega$  resistor for the standard load in the cable tests. The reason there is no plot of the open circuit is

because the analyzer senses that the resistance is greater than 1.28 M $\Omega$ . The analyzer displays "UCL" which designates an open load.

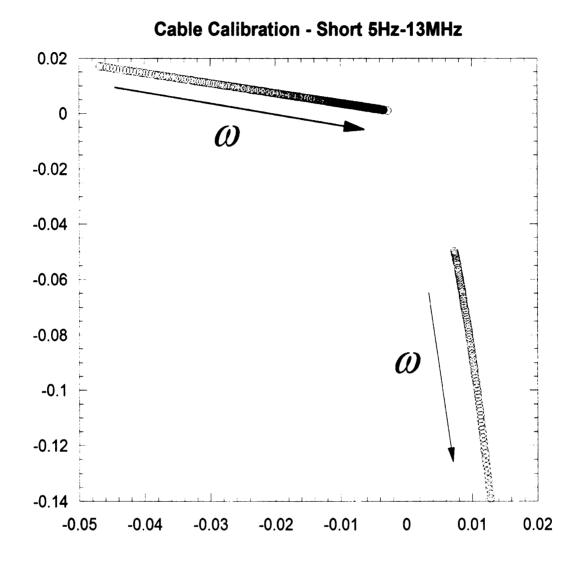

Figure 23: Cole-Cole plot – where the x-axis is Real{Z} and the y-axis is -lmag{Z}. BNC cable measurements – short 5Hz-13MHz.  $\omega$  shows the direction of increasing frequency.

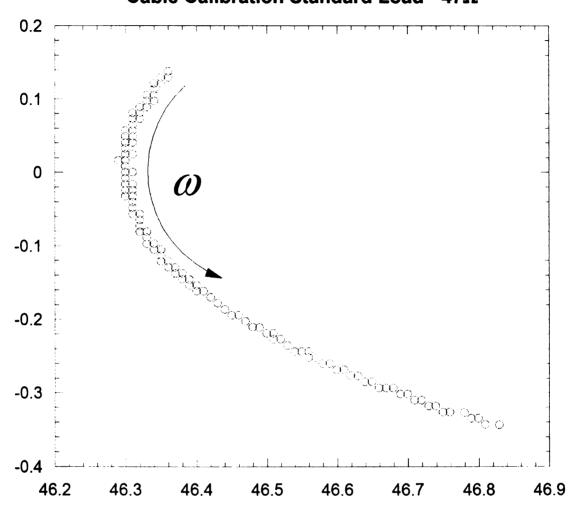

# Cable Calibration Standard Load - $47\Omega$

Figure 24: Cole-Cole plot – where the x-axis is Real{Z} and the y-axis is -lmag{Z}.BNC cable measurements – load 5Hz-13MHz

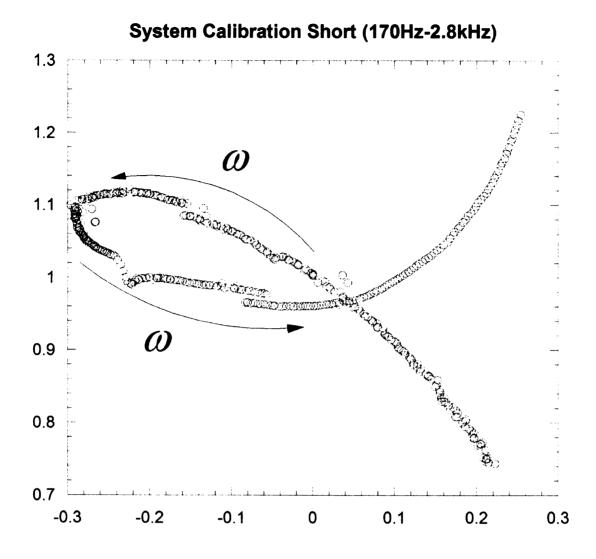

The analyzer locks and does not display any measurements between the frequency ranges of 5 Hz - 169Hz and 2.9KHz - 33KHz when the leads are shorted. Also, there is a significant amount of interference for the frequency range of 34KHz-13MHz. Therefore the data range for the HEISS is confined to 170Hz-2.8KHz. The standard load impedance is a  $100\Omega$  chip resistor.

Figure 25: Cole-Cole plot – where the x-axis is Real{Z} and the y-axis is -lmag{Z}. System Calibration Short 170Hz-2.8KHz

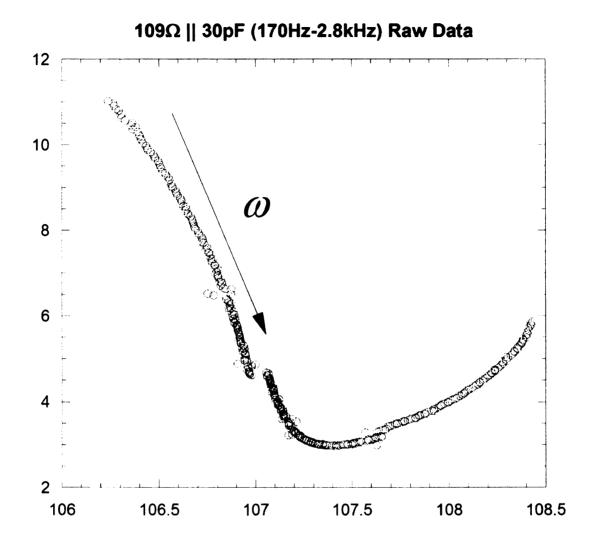

Figure 26: Cole-Cole plot – where the x-axis is Real{Z} and the y-axis is -lmag{Z}. System test –  $109\Omega$  resistor in parallel with a 30pF capacitor (raw data)

# Compensated 109Ω || 30pF (170Hz-2.8KHz) 0.7 00 @(D) () 00 0 0.6 000 000 ്ത $\circ \circ \circ$ 0.5 0 0.4 Ó 0 0.3 0.0000000 G(**0000**00) CC 000 0 G. COMPO 0.2 ೧೦**೦೦೦೦**೦೧ $\bigcirc$ 0 0.1

Figure 27: Cole-Cole plot – where the x-axis is Real{Z} and the y-axis is -lmag{Z}. System test –  $109 \Omega$  resistor in parallel with a 30pF capacitor (compensated data)

109.9

110

110.1

109.8

109.6

109.7

Figure 29 displays the raw data of a test load of 109  $\Omega$  resistor in parallel with a 30pF capacitor. Figure 30 displays the results of the open/short/load compensation of the data in the previous figure. The reason this circuit is chosen is because the test capacitance is on the same order of magnitude as the IDCs' capacitance.

#### 3.3.2 High Temperature Compensation and H-ZSM-5 Measurement

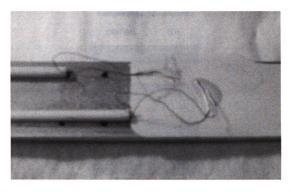

Figure 28: Test leads in the open circuit configuration. The copper leads are silver pasted

Table 2: Calculated resistance values for the standard load Pt – heater/resistor vs. temperature

| Temperature | Resistance |

|-------------|------------|

| (Kelvin)    | (Ω)        |

| 273         | 100.00     |

| 295         | 108.57     |

| 373         | 138.51     |

| 473         | 175.85     |

| 573         | 212.05     |

| 673         | 247.09     |

| 773         | 280.97     |

| 873         | 313.69     |

|             |            |

50

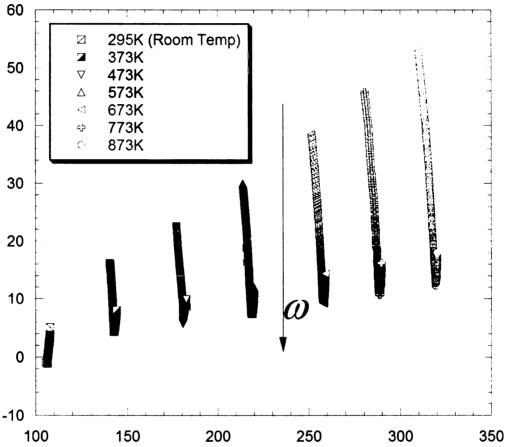

Figure 29: Cole-Cole plot – where the x-axis is Real{Z} and the y-axis is -lmag{Z}. Measured resistance values for the standard load Pt – heater/resistor vs. temperature

# H-ZSM-5 (170Hz-2.8KHz) 5 10<sup>5</sup> 685K X 690K (Second Run) 4 10<sup>5</sup> 3 10<sup>5</sup> $\omega$ 2 10<sup>5</sup> 1 10<sup>5</sup> 0 5 10<sup>5</sup> 6 10<sup>5</sup> 7 10<sup>5</sup> 8 10<sup>5</sup> 9 10<sup>5</sup> 1 10<sup>6</sup> 1.1 10<sup>6</sup>

Figure 30: Cole-Cole plot – where the x-axis is Real{Z} and the y-axis is -lmag{Z}. H-ZSM-5 measurements at 685K and 690K. The 690K measurement was taken after the HEISS system had gone through one temperature cycle.

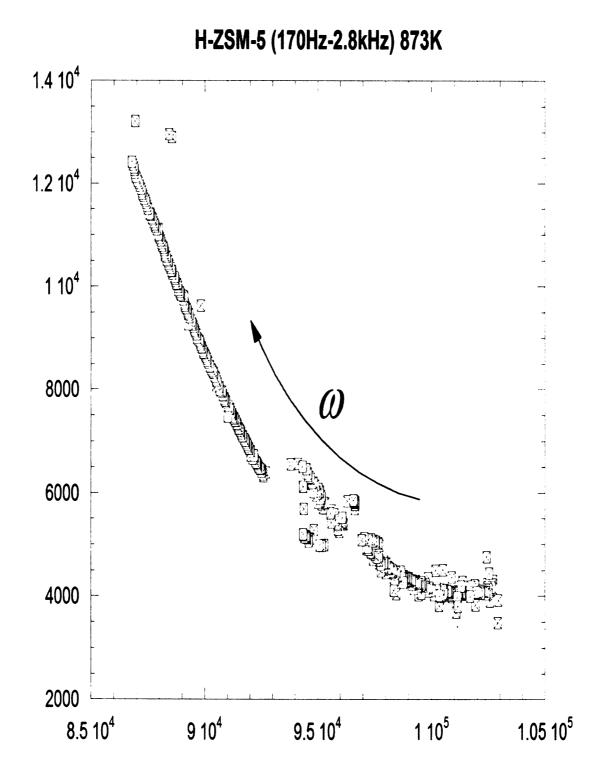

Figure 31: Cole-Cole plot – where the x-axis is Real{Z} and the y-axis is -lmag{Z}. H-ZSM-5 measurements at 873K

Figure 32: H-ZSM-5 screen printed on IDC 2 at 5x magnification - post run.

Silver paste was used to connect the leads for measurements done at high temperatures (Figure 31). The standard load was a Pt  $100\Omega$  (273K) heater/resistor. The temperature dependent resistance values were calculated using the Callendar-Van Dusen Equations [18].

H-ZSM-5 was measured on IDC 2 at temperatures ranging from 22K to 873K. The zeolite was measured to be an open circuit until 673K, when a measurable impedance spectra was observed (Figure 34). The temperature cycle was repeated and the results were the same. Comparing Figures 34 and 35, it is seen that the resistance of the zeolite decreases with increasing temperature.

#### 3.4 Conclusions

A prototype device has been constructed that can be used to measure impedance spectra for planar substrates over a frequency range of up to 2.8KHz at temperatures of up to 900K in a vacuum environment. The results obtained over this frequency for ZSM-5 compare well with literature data. This was achieved with the use of interdigitated capacitors designed and built in this work. The cost of building this unit was under \$1,500 in contrast to other high temperature measurement devices reported in the literature.

## 3.5 Recommendation for future work

The motivation for this project was to calculate the temperature dependent ionic conductivity of zeolite and to develop a gas sensor. The critical component that remains to be developed for this goal is an analytical model for environmental effects on ionic conduction in planar substrates.

## 3.5.1 Accurate Circuit Model

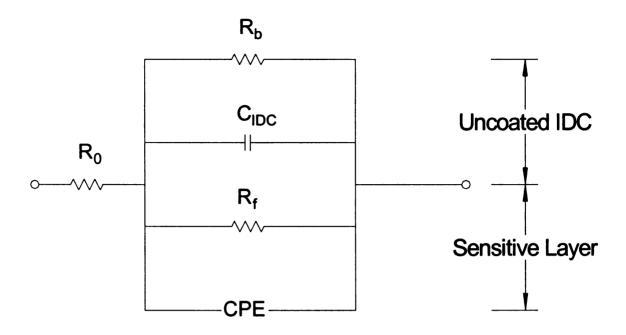

The new interdigitated capacitor along with the novel approach to zeolite coating have made it possible to use more advanced circuit models that utilize the constant-phase element outlined in Chapter 1. For a constant temperature Impedance Spectroscopy analysis the proposed circuit model shown in Figure 37 is suitable for the development of an accurate humidity sensor.

Figure 33: Equivalent circuit diagram of a coated IDC

This circuit model has been outlined in [6, 14]. The top half of circuit represents the IDC test circuit without a coating.  $R_b$  represents the resistance of the substrate while the series resistance  $R_0$  represents the electrode sheet resistance. The capacitance  $C_b$  is the capacitance of the IDC. The 'Sensitive Layer' represents the zeolite coating and its environmental interaction.  $R_f$  is the resistance of the coating. The constant phase element (CPE) represents a distribution of relaxation times due to zeolite interaction with the environment as well as a slight non-uniformity in the coating thickness. The 'Sensitive Layer' impedance is given by

$$Z_{SL} = \frac{R_f}{1 + (i\omega\tau)^{\varphi}} \tag{19}$$

where  $\varphi$  is the distorting parameter of the CPE and satisfies  $0 \le \varphi \le 1$ .  $\tau$  is the relaxation time. This modification of the circuit may be used to produce a gas/chemical/humidity sensor.

#### **BIBLIOGRAPHY**

- [1] J.R. Macdonald and E. Barsoukov, "Impedance Spectroscopy Theory, Experiment, and Application," Second Edition 2005, J. Wiley and Sons.

- [2] J.V. Smith, "Topochemistry of Zeolites and Related Materials," *Chemical Reviews*, 1988, Vol. 88, pp.149-182.

- [3] U.Simon and M.E. Franke, "Electrical properties of nanoscaled host/guest compounds," *Microporous and Mesoporous Materials*, 2000, Vol. 41, pp.1-36.

- [4] U.Simon and M.E. Franke, "Characteristic Proton Hopping in Zeolite H-ZSM-5," *Phys. Stat. Sol. (b)*, 2000, Vol. 218, pp.287-290.

- [5] I.M. Kalogeras and A. Vassilikou-Dova, "Electrical Properties of Zeolitic Catalysts" *Defect and Diffusion Forum*, 1998, Vol. 218, pp.1-36.

- [6] F. Josse and R. Lukas and R. Zhou and S. Schneider and D. Everhart "AC-Impedance-based Chemical Sensors for Organic Solvent Vapors" Sensors and Actuators B: Chemical, 1996, Vol. 35-36, pp.363-369.

- [7] K. Biswas and S. Sen and P.K. Dutta, "A constant phase element sensor for monitoring microbial growth" *Sensors and Actuators B,* 2006, Vol. 119, pp. 186-191.

- [8] E.C. Jordan and K.G. Balmain, "Electromagnetic Waves and Radiating Systems" Second Edition 1968, Prentice Hall Inc.

- [9] R.T. Kollipara and A.S. Mohammed and T.K. Plant and V.K Tripathi, "Modeling and Design of Interdigital Structures," *IEEE. Trans. On Electronic Devices* 1991, Vol. 38 pp.2575-2578.

- [10] M.W. Otter, "Approximate Expressions for the Capacitance and Electrostatic Potential of Interdigital Electrodes," *Sensor and Actuators A: Physical*, 2002, Vol. 96, pp.140-144.

- [11] A.V. Mamishev and K. Sundara-Rahan and F. Yang and Y. Du and M. Zhan, "Interdigital Sensors and Transducers," *Proceedings Of The IEEE*, 2004, Vol. 92, pp.808-845.

- [12] M.J. Toohey, "Electrodes for Nanodot-based Gas Sensors," Sensor and Actuators B: Chemical, 2004, Vol. 105, pp.232-250.

- [13] K. Alberti and F. Fetting, "Zeolites as Sensitive Materials for Dielectric Gas Sensors" Sensors and Actuators B: Chemical, 1994, Vol. 21, pp. 39-50.

- [14] H.E. Endres and S. Dross and F. Hutter, "Impedance Spectroscopy on Dielectric Gas Sensors" *Sensors and Actuators B: Chemical*, 1994, Vol. 22, pp. 7-11.

- [15] Yoon Y.G et. al, "Thermal conductivity of crystalline quartz from classical simulations" Physical Review B, 2004 Vol. 70, pp. 012302-1 012302-4

- [16] Agilent Technologies, "4192A LF Impedance Analyzer Operating and Service" 2000 (Revised), Part# 04192-90011

- [17] Hewlett Packard, "Effective Impedance Measurement Using OPEN/SHORT/LOAD Correction" 1998, Application Note# 346-3

- [18] Gureyev, Vladimir V. "High accuracy semiautomatic calibration of industrial RTDs" Conference Record IEEE Instrumentation and Measurement Technology Conference Instrumentation and Measurement, 2007, p 4258269