#### FAULT DETECTION: STATE BEHAVIOR, MACHINE DECOMPOSITION AND ECONOMICS

Dissertation for the Degree of Ph. D. MICHIGAN STATE UNIVERSITY LARRY LEE GROVER 1976

This is to certify that the

thesis entitled

FAULT DETECTION: STATE BEHAVIOR,

MACHINE DECOMPOSITION AND ECONOMICS

presented by

Larry Lee Grover

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Computer Science

Call V. Page

Major professor

Date August 9, 1976

**O**-7639

RETURNING MATERIALS:

Place in book drop to remove this checkout from your record. FINES will be charged if book is returned after the date stamped below.

SEP 5 1959 300 A 234

4;

LL PHDONI

#### ABSTRACT

FAULT DETECTION: STATE BEHAVIOR,

MACHINE DECOMPOSITION AND ECONOMICS

Вy

## Larry Lee Grover

Conducting checking experiments to detect faults in sequential machines inherently requires the use of specific sub-experiments. In this dissertation, these sub-experiments, or state identification sequences, are used to verify the (indirectly observable) transition function. Further, an algorithm for determining state identification sequences is constructed from a rigorous treatment of state distinguishability and equivalence. This algorithm detects the shortest state identification sequence for any state of a machine for which state identification sequences exist.

For machines lacking the desired behavior, procedures are derived such that these machines can be designed to possess the required behavior. The notion of inaccessible states is given serious attention to provide a means of detecting faults which increase the number of states in these machines. The number of states may be increased by

faults creating access to the inaccessible states. Design procedures are given to make possible the detection of this type of fault.

A machine notation is introduced to detect and eliminate redundancies in checking experiments by determining when sub-experiments overlap. This notation and reduction technique is used in an algorithm to detect faults which can occur in a sequential machine. In this algorithm, the use of state identification sequences which satisfy specific conditions assists in making the checking experiments as concise as possible.

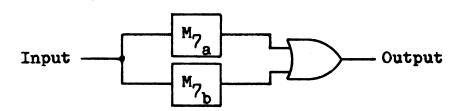

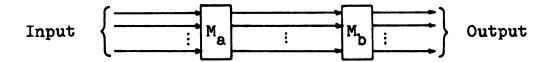

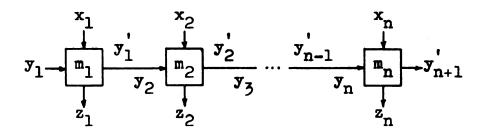

Machines which can be decomposed into serial or parallel connections of submachines possess certain structural properties which are beneficial to fault detection. These properties and their relationship to fault detection are presented and investigated to yield a fault detection method for decomposable machines. As a result of this method, both a savings in the amount of work required and other benefits are realized.

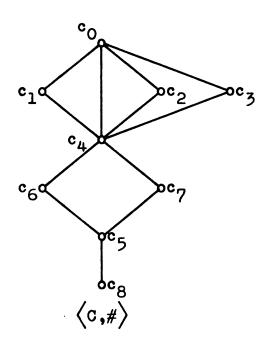

The cost (in a global sense) of fault detection is presented. Through a partial ordering of events which are encountered in fault detection, a cost model results. The use of this cost model establishes the overall fault detection program which has minimal cost.

# FAULT DETECTION: STATE BEHAVIOR, MACHINE DECOMPOSITION AND ECONOMICS

Ву

Larry Lee Grover

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Computer Science

1976

#### ACKNOWLEDGMENTS

My special thanks to Dr. Carl V. Page whose enthusiastic guidance made this work pleasurable. I have enjoyed the opportunity to freely exchange ideas with a person of such keen ability. My thanks also to Dr. Richard C. Dubes, Dr. Harry G. Hedges, Dr. Richard J. Reid, Dr. James H. Stapleton and Dr. Bernhard Weinberg for their service in reviewing and guiding my work.

# TABLE OF CONTENTS

| Cha | pter                                                    | Page     |

|-----|---------------------------------------------------------|----------|

| 1.  | INTRODUCTION                                            | 1        |

|     | 1.1 SEQUENTIAL MACHINE NOTATION                         | 2        |

|     | 1.3 BACKGROUND AND HISTORY                              | 5        |

|     | 1.4 DISSERTATION ORGANIZATION                           |          |

| 2.  | FORMALIZATION OF FAULT DETECTION PROPERTIES             |          |

|     | OF SEQUENTIAL MACHINES                                  | 11       |

|     | 2.1 STATE EQUIVALENCE AND DISTINGUISHABILITY            |          |

|     | 2.2 STATE BEHAVIOR SEQUENCES                            | 14       |

|     | 2.3 PROPERTIES REGARDING STATE IDENTIFICATION SEQUENCES | 18       |

|     | 2.4 DESIGN PROVISIONS TO ENSURE A COMPLETE              | 10       |

|     | IS SET                                                  | 24       |

|     | 2.5 CONCERNING INACCESSIBLE STATES                      | 28       |

|     | 2.6 INITIALIZING THE MACHINE                            | 31       |

|     | 2.7 CHAPTER SUMMARY                                     | 31       |

| 3.  | HOW TO MAKE A MACHINE MORE EASILY TESTABLE BY           |          |

|     | DESIGN                                                  | 33       |

|     | 3.1 DETERMINING STATE IDENTIFICATION SEQUENCES .        | 33       |

|     | 3.1.1 STATE IDENTIFICATION SEQUENCE                     |          |

|     | ALGORITHM                                               | 36       |

|     | 3.2 ALGORITHM FOR ADDITIONAL OUTPUTS                    | 41       |

|     | 3.3 ADDITIONAL INPUT ALGORITHM                          | 46       |

|     | 3.4 INACCESSIBLE STATE ASSIGNMENT ALGORITHM             | 47       |

|     | 3.5 CHAPTER SUMMARY                                     | 52       |

| 4.  | AN ALGORITHM FOR DETECTING FAULTS IN SEQUENTIAL         |          |

|     | MACHINES                                                | 54       |

|     | 4.1 STRONGLY CONNECTED AND REDUCED MACHINES             | 55       |

|     | 4.2 WORKING FORM NOTATION                               | 57       |

|     | 4.2 WORKING FORM NOTATION                               | 58       |

|     | 4.3 TRANSFER SEQUENCES                                  | 59<br>61 |

|     | 4.3.1 TRANSFER SEQUENCE MATRIX ALGORITHM                |          |

|     | 4.4 SUB-EXPERIMENT OVERLAPPING AND CONCATENATION        |          |

|     | 4.5 FAULT DETECTION ALGORITHM                           | 68       |

| Chapter                                                                      |                  |  |  |  |  |  |

|------------------------------------------------------------------------------|------------------|--|--|--|--|--|

| 4.6 EXAMPLES 4.7 BOUNDS ON EXPERIMENT LENGTH 4.8 CHAPTER SUMMARY             | 70<br>75<br>77   |  |  |  |  |  |

| 5. FAULT DETECTION THROUGH ABSTRACT REPRESENTATIONS .                        | <b>7</b> 9       |  |  |  |  |  |

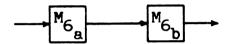

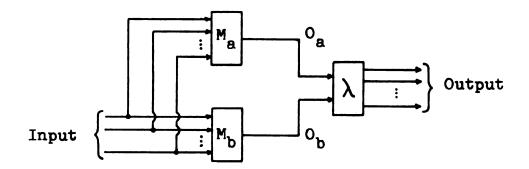

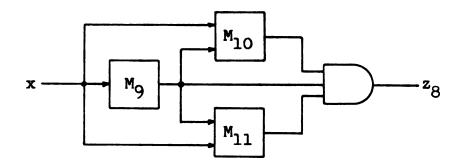

| 5.1 SERIAL AND PARALLEL DECOMPOSITION                                        | 91<br>102<br>111 |  |  |  |  |  |

| 6. ECONOMICS OF CHECKING EXPERIMENTS                                         | 117              |  |  |  |  |  |

| 6.1 EXPERIMENT COST                                                          | 120<br>121       |  |  |  |  |  |

| 6.2 COST MODEL 6.3 MULTIPLE USE OF A CHECKING EXPERIMENT 6.4 CHAPTER SUMMARY | 123<br>135       |  |  |  |  |  |

| 7. CONCLUSIONS AND SUGGESTIONS FOR FUTURE WORK                               | 139              |  |  |  |  |  |

| 7.1 CONCLUSIONS                                                              | 139<br>141       |  |  |  |  |  |

| TOT TOCOADUV 1/4                                                             |                  |  |  |  |  |  |

#### CHAPTER 1

#### INTRODUCTION

This dissertation is concerned with the detection of faults in sequential machines.

#### Definition 1.1

A <u>sequential machine fault</u> is any alteration which permanently changes the machine's logical operation.

Thus, failures which affect shapes of pulses, delay times or physical amplitudes, in the machine, but do not change its logical description, will not be considered. Also excluded are failures due to power sources and clock pulses.

Like other theories in science and engineering, the fault detecting theory presented here is mathematically based on the phenomena which characterize the subject.

Thus, the theory and algorithms herein developed, apply to any entity which can be represented as a sequential machine.

The remainder of this chapter is used to define the sequential machine mathematical structure used in this

dissertation, define the problem, give its history and state the organization of this dissertation.

#### 1.1 Sequential Machine Notation

The Mealy sequential machine model will be used in this dissertation (37).

#### Definition 1.2

A Mealy type sequential machine, M, is defined as a quintuple

$$M = (S, I, 0, \eta, \rho)$$

where

- 1) S is a finite nonempty set of states;

- 2) I is a finite nonempty set of inputs;

- 3) O is a finite nonempty set of outputs;

- 4)  $\eta$ : S x I  $\rightarrow$  S is called a transition function;

- 5)  $\rho$ : S x I  $\rightarrow$  0 is called the output function.

Let a single input symbol be denoted  $x_i \in I$ . A concatenation of k input symbols is denoted  $\bar{x}_k$  and  $(\bar{x}_k)_j$  implies the j<sup>th</sup> string of k inputs. A single output response is denoted as  $r_n \in O$ , while  $\bar{r}_k$  denotes a string of k responses. A transfer sequence from state  $s_i$  to  $s_j$  is a sequence of inputs denoted as  $T(s_i, s_j)$ . The next state for a machine in state  $s_i$  given the input  $x_j$ , is  $\eta(s_i, x_j)$ , while the output response is  $\rho(s_i, x_j)$ . The concatenation

of responses for a machine in state  $s_i$  given the input string  $\bar{x}_k$ , is  $\bar{\rho}(s_i, \bar{x}_k)$ .

This dissertation is concerned only with synchronous sequential machines. Sequential machines are classified as synchronous or asynchronous depending on whether or not the machine is operating under the control of clock pulses. In synchronous operation at most one internal state transition occurs in conjunction with the controling clock pulse. The output pulses are also in synchronism with the clock pulses.

Let x(t) and s(t) be the input and state of a synchronous sequential machine at time t. The state at time  $t' = t + \Delta t$  is

$$s(t') = \eta_c(s(t), x(t))c + \eta_{\overline{c}}(s(t), x(t))(1-c),$$

where c is the synchronizing clock pulse train and

The logical description of a synchronous sequential machine is typically given showing the c=l condition. When c=0, all states in the machine are stable for every  $x_1 \in I$ . Thus,

$$\eta_{\overline{c}}(s(t), x(t)) = s(t).$$

Suppose  $\eta_{\overline{c}}(s_j, x_m)$  is faulty such that

$$\eta_{\bar{\mathbf{c}}}(\mathbf{s}_{j}, \mathbf{x}_{m}) = \mathbf{s}_{f},$$

and

$$\eta_{\bar{c}}(s_f, x_m) = s_f.$$

Then the machine in any state s such that

$$\eta_{c}(s_1, x_m) = s_j,$$

will have  $s_j$  as a transient state on its way to  $s_{\hat{f}}$  when the clock pulse returns to zero. Thus,

$$\eta_{c}(s_1, x_m) = s_f$$

because when the machine is exposed to the next clock pulse it will be in  $s_f$ . Hence, faults in the  $\eta_{\overline{c}}$  portion of  $\eta$  appear as faults in  $\eta_c$ . Consequently, this dissertation is only concerned with the machine's description when the clock is present, following the tradition established in previous fault detection and automata theory. Therefore, any references to  $\eta$  will mean  $\eta_c$  in the remainder of this work.

The methods given in this dissertation can be extended to asynchronous machines, Friedman and Menon (15).

#### 1.2 The Problem of Fault Detection

We shall assume that only the output function,  $\rho$ , is observable; the transition function,  $\eta$ , is not. Consequently all information concerning a machine's behavior must come through the output. It is therefore necessary to conduct experiments using only the terminals of a machine to determine its behavior. The experiments are derived such that inputs are applied and outputs observed to determine correspondence between the machine and its flow table description. The entire experiment is referred to as a checking experiment.

## Definition 1.3

A checking experiment (CE) is a sequence of input symbols and their related output responses for the purpose of determining whether or not a sequential machine is functioning correctly.

A checking experiment may be either <u>preset</u>, in which the output response does not determine the next input symbol, or <u>adaptive</u>, in which the next input is determined from the present and past outputs.

Solving the fault detection problem is then a matter of devising a theory and algorithms by which checking experiments can be constructed such that they are concise and complete in detecting faults.

#### 1.3 Background and History

The first work in sequential machine fault detection was by Moore (39). He showed that any sequential machine with n states, p input symbols and q output symbols, can be distinguished, up to equivalence, from all other (n, p, q)-machines by a simple checking experiment. The approach is to construct a machine which is the direct sum of all possible (n, p, q)-machines and then find an experiment which will distinguish the object machine from all others.

Because Moore's procedure requires prohibitively long experiments, Poage and McCluskey (42), Roth et al. (44) and Seshu and Freeman (46) greatly restrict the number of machines in the direct sum to reduce experiment length. This is accomplished by selecting a fault or small set of faults to determine the machines for the direct sum. This, however, restricts the diagnostic capability of the experiment. This approach is referred to as the "circuittesting approach".

Hennie (23) seeks to devise experiments which identify a correct machine. The application of his experiment to any other machine of the same number of states or less produces a different response and hence, the experiment is a checking experiment.

Hennie's work on machine identification in fault detection is the basis for efforts by Boute (4), Farmer (13), Gönenc (19), Hsieh (27), Kime (31) and Kohavi et al. (34).

The chief result of their work has been to refine Hennie's procedures to make the resulting checking experiments more concise. The areas of refinement have been the removal of redundancy in the experiment and reduction in the length of certain input sequences used in Hennie's procedures.

Recently, work has been directed toward restricting the type of faults allowed e.g., Boute (5), Boute et al. (6), and Friedman et al. (14). Certain constraints are placed on the type of machine and internal logic interaction (states and output logic cannot be faulty simultaneously). The restrictions make techniques devised in this manner less potent than the machine identification approach but more general than the circuit-testing approach.

Aside from these works, fault detection has received much attention as evidenced by the literature. Five issues of the IEEE Transactions on Computers\* have been devoted exclusively to Fault-Tolerant Computing of which fault detection is a major area Carter (8). Five symposia on Fault-Tolerant Computing\*\* have been conducted and at least two texts (9), (15) dealing with fault detection and diagnosis in digital circuits have been written. Other texts which consider machine experiments and fault detection in their scope also exist (17), (24), (32) and

<sup>\*</sup> Vol. C-25, July 1976, vol. C-24, May 1975, vol. C-23, July 1974, vol. C-22, March 1973, vol. C-20, Nov. 1971.

\*\* IEEE International Symposium on Fault-Tolerant Computing, June 1975, June 1974, June 1973, June 1972, March 1971.

(48). Research in fault detection at Michigan State University has resulted in two publications, (10) and (29).

## 1.4 Dissertation Organization

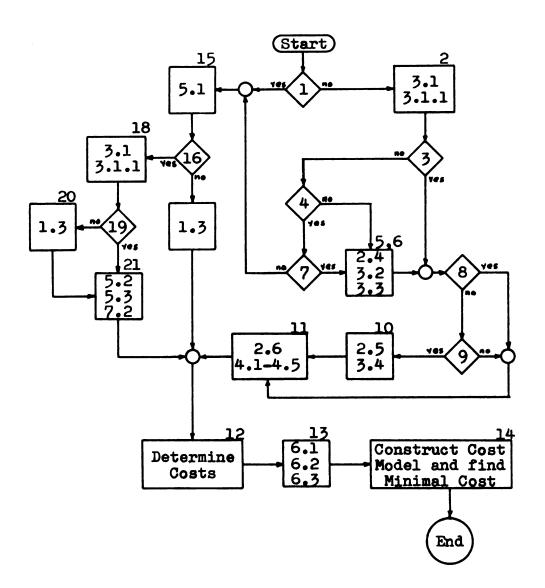

The following algorithm exhibits both the organization of this dissertation and the use of this thesis in fulfilling one's needs concerning fault detection. In the flowchart following the algorithm, the numbers in the decision operations refer to steps in the algorithm and the numbers in the process operations refer to sections of the dissertation:

- 1. If machine decomposition or partitioning is a strong consideration, go to 15; otherwise continue.

- 2. Refer to Sections 3.1 and 3.1.1 to determine whether or not a state identification sequence (Def. 2.6) exists for each state of the machine.

- 3. If the machine has a state identification sequence for each of its states, go to 8; otherwise continue.

- 4. If the machine is already constructed, go to 7; otherwise continue.

- 5. Refer to Sections 2.4, 3.2 and 3.3 for theory and design procedures which ensure an identification sequence for each state.

- 6. Consider adding inputs, outputs and testpoints and determine the machines for all three and go to 8.

- 7. If the machine can be altered for fault detection

through redesign, go to 5; otherwise go to 15.

- 8. Given that the machine has n states and v internal state variables which can have any of r values, if  $n=r^V$ , go to ll; otherwise continue.

- 9. If faults which can cause the r<sup>V</sup>-n inaccessible states to be entered are not of concern, go to 11; otherwise continue.

- 10. Refer to Sections 2.5 and 3.4 for the theory and design procedures to ensure that faults causing entry to inaccessible states are detected.

- 11. Refer to Sections 2.6 and 4.1-4.5 to determine a checking experiment for the machine using state identification sequences.

- 12. Determine the costs associated with fault detection (Section 6.1).

- 13. Refer to Sections 6.1-6.3 for economical analysis.

- 14. Construct cost model and find the best set of admissible costs and go to 22.

- 15. Refer to Section 5.1 and perform machine decomposition (Hartmanis and Stearns (22)).

- 16. If a nontrivial decomposition exists, go to 18; otherwise continue.

- 17. Refer to Section 1.3 for a guide to methods of deriving checking experiments using other than state identification sequences and go to 12.

- 18. Refer to Sections 3.1 and 3.1.1 to determine whether or not each submachine has a complete set of state

identification sequences.

- 19. If all submachines have a complete set of state identification sequences, go to 21; otherwise continue.

- 20. Refer to Section 1.3 for a guide to methods of deriving checking experiments for those machines not having a complete set of state identification sequences.

- 21. Refer to Sections 5.2, 5.3 and 7.2 for theory relating faults to machine decomposition and go to 12.

22. End.

#### CHAPTER 2

# FORMALIZATION OF FAULT DETECTION PROPERTIES OF SEQUENTIAL MACHINES

The transition function, 7, is not directly observeable by terminal measurements. However, the manner in which a machine responds to an input sequence does reveal information about its states. It is this state behavior that is of concern in this chapter.

## Definition 2.1

An <u>I/O</u> sequence is an input sequence (I) and its related output sequence (O).

From Definition 1.3, a checking experiment (CE) is an I/O sequence which serves to detect faults in the machine. The particular sequences which are defined in this chapter may eventually be used as part of a checking experiment. Hence, these sequences will constitute a sub-experiment for a checking experiment.

# Definition 2.2

Any I/O sequence incorporated in the construction of

a CE is a sub-experiment.

## 2.1 State Equivalence and Distinguishability

To devise a sequence (experiment) which will determine the behavior of the machine initially in a particular state, it is necessary to find some input sequence which will distinguish one state from the others. This becomes impossible if two or more states of the machine are equivalent.

## Definition 2.3

State s<sub>i</sub> and s<sub>j</sub> of a sequential machine are said to be equivalent, if

$$\bar{\rho}(s_i, (\bar{x}_m)_p) = \bar{\rho}(s_i, (\bar{x}_m)_p)$$

for all m and p, otherwise they are distinguishable.

## Definition 2.4

State  $s_i$  and  $s_j$  of a sequential machine are said to be k-equivalent, if

$$\bar{\rho}(s_i, (\bar{x}_m)_p) = \bar{\rho}(s_j, (\bar{x}_m)_p)$$

for all p, and m  $\leq$  k, otherwise they are <u>k-distinguishable</u>.

The following Lemma by Gill (17) says that if some

input sequence of length k, say  $\bar{x}_k$ , will distinguish states  $s_i$  and  $s_j$ , then any sequence  $\bar{x}_k\bar{x}_m$ ,  $m \ge 0$ , will also.

#### Lemma 2.1:

(a) If two states are k-equivalent, then they are j-equivalent for every  $j \le k$ . (b) If two states are k-distinguishable, then they are j-distinguishable for every  $j \ge k$ .

The search for input sequences which distinguish between states begins with the shortest possible input sequence and progressively concatenates inputs until the sequence is found. The notion of states which merge is also useful in determining rules for a process which is to be defined later.

# Definition 2.5

State  $s_i$  and  $s_j$  of a sequential machine are said to merge, if for some input symbol,  $x_1$ ,

$$\eta(s_i, x_i) = \eta(s_j, x_i).$$

# Theorem 2.1:

Suppose g states of a sequential machine respond identically for some input sequence  $(\bar{\mathbf{x}}_m)_j$ . Then, if these g states all merge given  $(\bar{\mathbf{x}}_m)_j$ , they are equivalent with

respect to every input sequence having  $(\overline{\mathbf{x}}_{m})_{\mathbf{j}}$  as a prefix.

This theorem follows immediately from Gill's lemma so the proof is omitted. Denote this type of equivalence as  $(\bar{x}_m)_{j}$ -prefix equivalence. These notions of equivalence and distinguishability are important to the rules which govern the process used to find state identification sequences.

## 2.2 State Behavior Sequences

This section is devoted to defining and discussing sequences (experiments) which determine state behavior.

## Definition 2.6

A state identification sequence (IS) for  $s_i$  is an I/O sequence  $(\bar{x}_{IS}/\bar{\rho}(s_i, \bar{x}_{IS}))$  such that

$$\bar{\rho}(s_i, \bar{x}_{IS}) \neq \bar{\rho}(s_i, \bar{x}_{IS})$$

for all  $j \neq i$ .

An identification sequence for state Q of a machine is denoted ISQ. If a machine possesses an identification sequence for each of its states, then it is said to have a complete IS set.

### Definition 2.7

A distinguishing sequence (DS) is an input sequence  $(\bar{\mathbf{x}}_{DS})$  such that for an n-state sequential machine,

$$\bar{\rho}(s_i, \bar{x}_{DS}) \neq \bar{\rho}(s_j, \bar{x}_{DS})$$

for all i and j,  $j \neq i$ .

Therefore, a distinguishing sequence is an input sequence which defines a state identification sequence for every state of the machine. Thus, it is possible to determine the initial state of the machine simply by observing the response of the distinguishing sequence.

Not every machine has a distinguishing sequence.

Certainly, machines which have equivalent states do not.

Also, not every machine has a complete IS set as will be shown in later examples. The set of machines which do have distinguishing sequences are properly contained in the set of machines which have complete IS sets.

Distinguishing sequences and state identification sequences can be used to verify that a machine was in a given state and if so, infer the behavior of the machine throughout the sequence. There exists sequences which, although they cannot determine the initial state, can decide the state of the machine at the end of the experiment.

## Definition 2.8

A <u>homing sequence</u> (HS) is an input sequence  $(\bar{x}_{HS})$ , such that the final state of the machine can be determined uniquely from the machine's response to  $\bar{x}_{HS}$  regardless of the initial state.

### Definition 2.9

A synchronizing sequence (SS) is an input sequence  $(\bar{x}_{SS})$  which has

$$\eta(s_i, \bar{x}_{SS}) = s_k,$$

where sk is the same for all i.

Hence, by observing the response of the machine to a homing sequence, it is assured that its final state is known. However, no predictions about the state of the machine during the experiment can be made. It has been shown that every machine which does not contain equivalent states has a homing sequence (17). Every synchronizing or distinguishing sequence is a homing sequence. Not every machine has a synchronizing sequence. These sequences are useful for maneuvering the machine into a desired state.

# Example 2.1

The following machine,  $M_0$ , displays the four types of sequences which have been defined.

The shortest identification sequence for state D is

$$IS_D = e/y$$

.

No other state can produce a response of y to the input e.

The application of the input sequence efef to  $M_{O}$  will leave the machine in state B regardless of its initial state. Thus, efef constitutes a synchronizing sequence.

A distinguishing sequence for this machine is ff.

The following shows the states and their responses to the distinguishing sequence.

Any distinguishing sequence is also a homing sequence and this one is too. Another homing sequence for this

machine is ef. The following shows the possible responses to ef and the final states which these responses define.

| initial | ef         | final |

|---------|------------|-------|

| A       | ww         | В     |

| B       | <b>W</b> W | В     |

| C       | wy         | D     |

| D       | УУ         | В     |

A complete IS set for  $M_0$  is the following where only the shortest state identification sequences are given.

# 2.3 Properties Regarding State Identification Sequences

This section concerns properties of sequential machines related to state identification sequences. These properties have a major bearing on the development of this work. Given in Theorem 2.2 is a condition which ensures a complete IS set for a sequential machine.

# Definition 2.10

A sequential machine is <u>reduced</u> if no two states are equivalent.

#### Lemma 2.2:

A complete IS set does not exist for any machine which is not reduced.

#### Proof:

Since the machine is not reduced, it has states which are equivalent. If two states are equivalent, then they respond identically for every input sequence and hence, neither has an identification sequence.

Using the results of Lemma 2.2 we now determine a specific condition for a machine flow table such that given this condition a machine is assured of having a complete IS set.

#### Theorem 2.2:

For an n-state reduced sequential machine, if

$$(\eta(\mathbf{s_i},\ \mathbf{x_l}),\,\rho(\mathbf{s_i},\ \mathbf{x_l})) \neq (\eta(\mathbf{s_j},\ \mathbf{x_l}),\,\rho(\mathbf{s_j},\ \mathbf{x_l}))$$

for all i,  $j \neq i$ , and all  $x_1 \in I$ , then the machine has a complete IS set.

#### Proof:

We shall assume the negation of the consequent of the theorem and show that this contradicts the premise. Assume that there exists a state, say  $s_i$ , in a machine satisfying

the conditions of this theorem which responds the same as at least one other state, sp (which depends on input sequence), for all input sequences. Then the machine does not have a complete IS set because s, does not produce a unique response for any of all input sequences. Suppose further that n copies of the machine are available each one in a different state than the rest. Then m; (the machine originally in s;) will respond the same as at least one other machine for every input string. Now apply an input such that some machines are distinguished from the others. This is possible, for if it were not, all states would be equivalent and the machine was reduced to begin with. Now m, is contained in a proper subset of the original n machines which were not distinguished from m<sub>i</sub>. All machines in this subset are in different states because if any were in the same state, some input must have caused these states to merge into the same state and give the same output which is contrary to premise. Now apply an input sequence to distinguish between m, and some other machine. This is possible because in a reduced machine all states are pair-wise distinguishable. Delete the machines so distinguished from m<sub>i</sub>. Continue this process until only two machines remain, m, and some other machine, which have not been distinguished between by all previous input strings. These two machines are in different states due to previous arguments. Now apply the input sequence which distinguishes the two states and m, has been found which is a contradiction to the assumption.

On the other hand, there exists a situation which prevents a state from possessing a state identification sequence. This is evident in Theorem 2.3.

# Theorem 2.3:

If state  $s_i$  in an n-state sequential machine has for each member of its input alphabet,  $x_1$ ,

$$\eta(s_1, x_1), \rho(s_1, x_1) = \eta(s_1, x_1), \rho(s_1, x_1)$$

for some  $j \neq i$ ,  $s_i$  does not have an identification sequence.

## Proof:

For every possible input symbol  $s_i$  is  $(\bar{x}_m)_k$ -prefix equivalent to another state. Therefore, no concatenation of input symbols exists which distinguishes  $s_i$  from any other state.

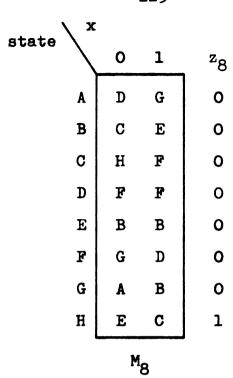

To illustrate the situation presented in Theorem 2.3, consider the following machine  $M_{\uparrow}$ .

State B of  $M_1$  responds the same as A and goes to the same next state as A for any input sequence having the initial input "O". State B also responds the same as C and goes to the same next state as C for all input sequences having the initial input "l". Thus, B responds the same as some other state of  $M_1$  for all input sequences.

Thus, there exists two situations concerning a machine's logical description which provide insight for design criterion. One situation to avoid (Theorem 2.3) and one to strive for (Theorem 2.2).

Since state identification sequences are to be used in verification of a machine's flow table, a procedure will be given for determining these sequences. It is therefore necessary to determine how far this procedure must be carried out in its search. Theorem 2.5 gives the bounds and Theorem 2.4 whose proof has been given by Gill (17) is useful. This same result (Theorem 2.4) has also been given by Salomaa (45) where he shows that the result of Theorem 2.4 is the best upper bound.

## Theorem 2.4:

Two states in an n-state machine are equivalent if they are (n-1)-equivalent and distinguishable if they are (n-1)-distinguishable.

## Theorem 2.5:

Given that a state of an n-state sequential machine

has an identification sequence, the length of the sequence need not be longer than k, where

$$k = (n-1)^2.$$

#### Proof:

Assume n copies of the n-state machine are available each in a different state and the machine in state s<sub>i</sub> is denoted m<sub>i</sub>. Since s<sub>i</sub> has an identification sequence, there exists some input sequence for which m<sub>i</sub> will respond uniquely. Theorem 2.4 assures that there exists an input sequence of length n-1 such that m<sub>i</sub> is distinguished, pair-wise, from at least one other machine. Lemma 2.1 assures that once m<sub>i</sub> is distinguished from another machine by some sequence, any inputs concatenated with this sequence will always distinguish the two machines.

Assume that no sequence of length n-1 distinguishes  $m_i$  from more than one other machine. Now  $m_i$  is contained in a set of n-1 machines and must be distinguished from the other members. Since  $s_i$  possesses an identification sequence, the first n-1 symbols of the identification sequence must leave  $m_i$  in a different state than the other members of the n-1 member indistinguished set. If not,  $m_i$  would be  $(\bar{x}_k)_j$ -prefix equivalent to another machine and hence, the sequence being constructed could not be an identification sequence.

Now considering all possible input sequences of

length n-l concatenated with the previous portion of the identification sequence, m<sub>i</sub> must be distinguished from at least one member of the indistinguished set. After application of the j<sup>th</sup> correct sequence, m<sub>i</sub> has been distinguished from at least j machines.

Continuing this process n-1 times will result in  $m_i$  being completely distinguished from all other machines. Therefore, the construction process has, under worst conditions, yielded an identification sequence for  $s_i$ , such that the maximum length of the sequence is

$$k = \sum_{i=1}^{n-1} (n-1) = (n-1)^2$$

.

The bound determined here does not imply that no sequence of length greater than  $(n-1)^2$  is an identification sequence. It shows that if an identification sequence exists, one exists within the bound derived here.

# 2.4 Design Provisions to Ensure a Complete IS Set

Because a machine's output function,  $\rho$ , is directly observable, we investigate this function for design possibilities. A machine which does not have a complete IS set can be made to have one by providing additional outputs. The existence of such a design procedure follows from Theorem 2.6.

#### Theorem 2.6:

Any sequential machine having v internal r-ary variables can be designed to possess a complete IS set, by providing m additional output variables, where m < v.

#### Proof:

Given v internal variables and r possible values for each variable, there are r possible combinations of these variables. Hence, there are r possible distinct states for the machine and using v output variables, each state can be assigned a different combination of output components. Therefore, each state has an identification sequence.

The possibility of adding inputs in ensuring a complete IS set is evident in Theorem 2.7.

## Theorem 2.7:

Any sequential machine can be made to have a complete IS set by the addition of only one member to its input alphabet

## Proof:

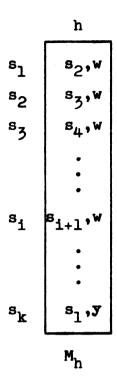

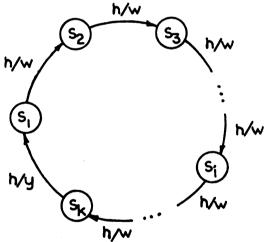

Consider the following machine,  $M_h$ , which has only one input, h.

M<sub>h</sub> State Diagram

Suppose  $M_h$  is initialized to  $s_i$ . After k-i inputs, k > i, the machine is in  $s_k$  and the response is k-i w's. The next input will produce a y response. Hence, initially in  $s_i$ , the machine will produce a y response on

the k-i+l input. The following results are observed for an input sequence of k-l h's.

|                |     |       | k-l                    |       |     |

|----------------|-----|-------|------------------------|-------|-----|

| State          | hhh | •••   | hhh                    | •••   | hhh |

| s <sub>1</sub> | www | • • • | www                    | • • • | www |

| s <sub>2</sub> | WWW | • • • | www                    | •••   | wwy |

| s <sub>3</sub> | WWW | •••   | www                    | •••   | wyw |

| •              |     |       |                        |       |     |

| s <sub>i</sub> | WWW | •••   | wyw                    | •••   | www |

| •              |     |       |                        |       |     |

| s <sub>k</sub> | yww |       | www<br> <br> <br> k-i+ |       | www |

It is certainly evident that each state of this machine has an identification sequence. The state identification sequence for state s; is

IS<sub>s,j</sub> =

$$hh \dots hh/ww \dots wy$$

,

where  $j \neq 1$ . The state identification sequence for  $s_1$  is

IS<sub>s<sub>1</sub></sub> =

$$hh \dots hh/ww \dots ww$$

.

It is also noted that the input string of k-l h's is a distinguishing sequence. Thus, adding h as one additional member to the input alphabet and assigning it the entries contained in M<sub>h</sub> yields a complete IS set for any sequential machine.

## 2.5 Concerning Inaccessible States

For every n-state sequential machine having v r-ary state variables where

$$r^{v-1} < n < r^v$$

.

there are r<sup>V</sup>-n inaccessible states. Inaccessible states do not appear as next states in the n-state machine. Therefore, occurence of faults can produce paths to previously inaccessible states and consequently checking experiments should be able to detect these faults. It would be advantageous to assign to inaccessible states, next states and responses suitable for detecting entry into them.

If faults create paths to inaccessible states, any checking experiment which relies on verification of the flow table requires alteration of the machine structure to provide entry to the inaccessible states. Because faults in inaccessible states are possible also, there exists the possibility or certainty for each fault which causes entry to an inaccessible state, a fault in that inaccessible state which masks the fault causing entry.

Suppose that in the checking experiment, a fault causes  $\mathcal{N}(s_i, a)$  to become  $s_m$  ( $s_m$  inaccessible) instead of  $s_j$ . Now  $\mathcal{N}(s_m, b)$  is  $s_j$  and  $\rho(s_m, b)$  is  $g_s$ . Since  $\mathcal{N}(s_j, b)$  is  $s_j$  and  $\rho(s_j, b)$  is  $f_s$ , the fault causing entry into  $s_m$  would be detected by an input of  $g_s$ . If  $\rho(s_m, b)$  is faulty and becomes  $f_s$ , the machine will be in the correct state and no fault is detected. If the checking experiment subjects state  $s_i$  to an a input only once, the fault is not detected by the checking experiment. It is necessary to verify the transitions in the inaccessible states as well. This can only be done if access, in some form, to the inaccessible states is available.

One way to solve this access problem would be to provide an additional member to the input alphabet which is used only during testing. This then would allow the previously inaccessible states to be entered as long as it was not faulty.

In assigning entries to the r<sup>V</sup>-n states, a primary goal is that each state have an identification sequence to ensure a complete IS set. From Theorem 2.2, it is necessary to assign unique entries under every input for the inaccessible states. The next state entries for these states are states contained in the original n. The reasoning will become evident in ensuing arguments.

## Theorem 2.8:

For an n-state, p-input, q-output sequential machine

which has v internal r-ary state variables, there are  $r^{V}$ -n possible distinct entries in the flow table available for each input symbol when n >  $r^{V}/2$ , using only the original n states.

#### Proof:

There are a maximum of nq possible distinct entries for each input symbol using the original n states. Since a maximum of n are used for an input, n(q-1) remain. Hence, n(q-1) must be greater than or equal to  $r^{V}$ -n in order to supply the unique entries which will satisfy Theorem 2.2. Thus,

$$n(q-1) \ge r^{V}-n$$

or

$$q \ge r^{V}/n$$

.

For nontrivial sequential machines,

$$q \ge 2 > r^{V}/n$$

.

Theorem 2.8 guarantees that sufficient distinct entries are available. It remains to find and assign these entries. The procedure which will accomplish the desired assignments is given in Chapter 3.

#### 2.6 Initializing the Machine

Given a sequential machine for testing, there may be no way of knowing its present state. Since only terminal experiments are allowed here, it is necessary to force the machine into a known state by terminal experiments. Maneuvering the machine into a known state is referred to as initialization. Once initialized, the future behavior of the machine can be predicted. Synchronizing sequences and adaptive homing techniques are useful for initialization and their derivation is given in Gill (17).

#### 2.7 Chapter Summary

The necessity of experimentally observing the transition function has resulted in a study of sequential machine state behavior. The primary concern in this chapter was to define and detect particular state behavior which could identify either the initial or final state of a machine with respect to the application of an input sequence.

The means by which states could be identified has stemmed from the notions of state equivalence and distinguishability. These notions have been formally developed and used extensively in the derivation of algorithms (Section 3.1.1) which generate the desired input sequences that identify states through output observations.

This chapter presents particular machine characteristics which are useful in machine design as applied to

fault detection. A discussion of unused or inaccessible states is also given in Section 2.5.

#### CHAPTER 3

## HOW TO MAKE A MACHINE MORE EASILY TESTABLE BY DESIGN

Not all sequential machines possess a complete state identification sequence set or a distinguishing sequence. Consequently one must rely on testing techniques introduced by Hennie (23), which result in checking experiments of great length, unless the machine can be designed to yield additional information about its states and transition function. This chapter will consider the design of machines which are more readily testable. In particular, faults which increase the number of accessible states can be made testable by design. The design criteria presented in this chapter can be used in conjunction with usual design practices resulting in a single design phase.

## 3.1 Determining State Identification Sequences

Although state identification sequences are discussed in the literature, efficient means for computing them are not, although there may be proprietary programs to do this. One way to solve the problem of finding state

identification sequences for a finite state sequential machine would be to determine if the machine, as an encoder, encodes (state, input) information into output sequences which are uniquely decodable (Abramson (2)). Thus,

$$(s_i, \bar{x}_{IS_{s_i}}) + \bar{\rho}(s_i, \bar{x}_{IS_{s_i}})$$

would represent an encoding which is uniquely decodable.

In this dissertation we present a means of determining state identification sequences for any sequential machine by using the successor tree. Gill (17) explains the successor tree and how he uses it to find distinguishing and homing sequences.

The successor tree is, in itself, infinite and of no practical use. To make the successor tree useful in the derivation of machine experiments, termination rules must be established such that branches in the tree are terminated when determinated useless or the tree growth itself is to be halted for some specified reason.

In the process of determining possible state identification sequences, particular input sequences may be

found which will not assist in finding an IS for a state

not having one already. Once found, these input sequences

(tree paths) are omitted from further use. An input

sequence which is retained offers potential value in

determining the desired identification sequences and is referred to as a potential input sequence.

The procedure to be developed here does not use the tree structure in the graphical sense but, uses a compressed representation of the tree to facilitate the tree searching. This representation consists of an array (G) acting as successor tree levels. Each row of G corresponds to a different state in the machine. The columns of G correspond to input sequences (tree paths to the particular tree level G represents). Given that the machine's state set is

$$s = \{s_i, s_2, \ldots, s_n\},$$

assign  $s_i$  to the i<sup>th</sup> row and  $(\bar{x}_m)_j$  to the j<sup>th</sup> column. Now the entries (tree nodes for the level) in G are

$$(g, h)_{ij} = g_{ij}, h_{ij} = \eta(s_i, (\bar{x}_m)_j), \bar{\rho}(s_i, (\bar{x}_m)_j).$$

The array at each successive tree level is referred to as a generation. The zeroth-generation is simply the original flow table. The input sequences for the next generation are determined by concatenating all members of the input alphabet with the prior generation's potential input sequences. For the prior generation input  $(\bar{\mathbf{x}}_m)_{\mathbf{j}}$ , the new generation input is  $(\bar{\mathbf{x}}_m)_{\mathbf{j}} \mathbf{x}_k$ ,  $\mathbf{x}_k \in I$ . Let

$$(\bar{x}_m)_j x_k = (\bar{x}_{m+1})_p$$

for some p, then

$$g_{ip} = \eta(g_{ij}, x_k)$$

$$h_{ip} = h_{ij} \rho(g_{ij}, x_k)$$

and each generation is computed using only  $\eta$ ,  $\rho$  and the most recent generation.

## 3.1.1 State Identification Sequence Algorithm

A partition on the machine's state set is a grouping of all states into disjoint subsets called blocks. A partition in which two states s<sub>i</sub> and s<sub>j</sub> are in the same block, if and only if

$$\bar{\rho}(s_i, (\bar{x}_m)_k) = \bar{\rho}(s_i, (\bar{x}_m)_k)$$

i.e.,

$$h_{ik} = h_{ik}$$

is said to be the <u>partition induced</u> by  $(\bar{x}_m)_k$  and denoted  $\pi((\bar{x}_m)_k)$ . A partition in which two states  $s_i$  and  $s_j$  are in the same block, if and only if

$$\eta(s_i, (\bar{x}_m)_k), \bar{\rho}(s_i, (\bar{x}_m)_k) = \eta(s_i, (\bar{x}_m)_k), \bar{\rho}(s_i, (\bar{x}_m)_k)$$

i.e.,

$$(g, h)_{ik} = (g, h)_{jk}$$

is denoted  $\omega((\bar{x}_m)_k)$ . The state identification sequence algorithm follows.

- 1. The machine flow table is the zeroth-generation. Set k equal to zero.

- 2. For each  $(\bar{x}_m)_j$  of the present generation, determine  $\pi((\bar{x}_m)_j)$  and  $\omega((\bar{x}_m)_j)$ . Increment k by 1.

- 3. If any  $\pi((\bar{\mathbf{x}}_m)_j)$  contains a singleton block, then that state  $(\mathbf{s}_i)$  in the block has a state identification sequence which is  $(\bar{\mathbf{x}}_m)_j/\bar{\rho}(\mathbf{s}_i,(\bar{\mathbf{x}}_m)_j)$ . Indicate that  $\mathbf{s}_i$  has a state identification sequence by a \$ and also the sequence.

- 4. If all states have been found to have state identification sequences, terminate with success; otherwise continue.

- 5. If all states which do not have state identification sequences are contained in nonsingleton blocks of  $\omega(\bar{x}_m)_j$ , then place a star over column  $(\bar{x}_m)_j$  indicating that it is of no further use.

- 6. If all inputs (columns) have been marked with a star, terminate without a complete IS set or no state

identification sequences at all; otherwise continue.

- 7. If  $k = (n-1)^2$ , terminate without a complete IS set; otherwise continue.

- 8. Construct the next generation i.e.,

$$g_{ip} = \eta(g_{ij}, x_k)$$

$$h_{ip} = h_{ij} \rho(g_{ij}, x_k),$$

for all  $x_k \in I$  and potential  $(\bar{x}_m)_j$  of the previous generation and go to step 2.

## Example 3.1

D A,01 D,00

This example illustrates the algorithm using machine  $\rm M_2$  which is defined by  $\rm G_0$

|             |            | 1    |

|-------------|------------|------|

| A           | A,0        | В,О  |

| В           | A,0        | c,o  |

| C           | A,O        | D,O  |

| <b>\$</b> D | <u>A,1</u> | D,O  |

|             | •          |      |

|             | 10         | 11   |

| A           | A,00       | C,00 |

| В           | A,00       | D,00 |

| C           | A . OT     | D,00 |

|     | ıio          | ıiı   | $G_2$ |

|-----|--------------|-------|-------|

| \$A | <u>A,000</u> | D,000 | _     |

| В   | A,001        | D,000 |       |

| C   | A,001        | D,000 |       |

| D   | A,001        | D,000 |       |

Since all remaining inputs have stars, the algorithm terminates with a partial IS set.

$$IS_A = 110/000$$

$IS_D = 0/1$

There are several aspects of this algorithm which are of interest to checking experiment theory.

## Theorem 3.1:

The state identification sequence algorithm will determine a state identification sequence for each state of a sequential machine for which a state identification sequence exists.

## Proof:

If a state does possess an identification sequence, then an input sequence exists for this state which will produce a unique response. Since an input's use is never terminated until it is known that all states without an identification sequence are  $(\bar{x}_m)_{,i}$ -prefix equivalent to at

least one other state for each input (step 6), then the existence of such an input sequence ceases once the algorithm terminates.

#### Theorem 3.2:

If an identification sequence exists for a state of a sequential machine, the state identification sequence algorithm will determine the shortest such sequence.

#### Proof:

Prior to the construction of a new generation, the present generation is checked for all possible state identification sequences. Hence, prior to increasing an input's length, all possible state identification sequences are determined and noted.

#### Theorem 3.3:

The state identification sequence algorithm will terminate for any finite state machine.

## Proof:

If the algorithm has not found an identification sequence within  $(n-1)^2$  generations, none exist by Theorem 2.5 and the algorithm terminates in step 7.

## 3.2 Algorithm For Additional Outputs

The notion of adding outputs to machines to render more efficient fault detection has been considered e.g., Kohavi and Lavellee (33), Sheppard and Vranesic (47). This additional output assignment problem is considered in this dissertation and expanded such that when applied to sequential machines, complete IS sets are the result. The existence of such a design procedure follows from Theorem 2.6.

The process of providing additional outputs is, in effect, that of embedding the original machine in a new machine which provides additional state information. Let

$$(z_{01}, ..., z_{0i}) = \rho_0(s_i, x_i)$$

denote the original output vector and

$$z_m = \rho_m(s_i, x_i)$$

denote the m<sup>th</sup> additional output. Then the output for the machine is a vector represented as

$$z = (z_{01}, ..., z_{0j}, z_1, z_2, ..., z_m).$$

In order to simplify the notation, base 10 values of these vectors are used. Hence,

$$R = z_{01}b^{m+j-1} + \cdots + z_{0j}b^{m} + z_{1}b^{m-1} + \cdots + z_{m}$$

where b is the base of the number system for the internal variables written in base 10. Consider the following in base 2.

$$Z = (1, 0, 1)$$

$$R = 5$$

Now R is used as the output and the flow table entry is

$$s_{i}$$

,(1, 0, 1) =  $s_{i}$ ,5.

Theorems 2.2 and 2.3 suggest a design procedure for adding outputs to ensure that a complete IS set exists. An algorithm for this design process first considers whether or not the machine does have a complete IS set. In the event that it doesn't, an additional output is created to attempt completion of the IS set. The new output is specified such that it will make states previously  $(\bar{\mathbf{x}}_{\mathbf{m}})_{\mathbf{j}}$ -prefix equivalent no longer equivalent. Therefore, identical  $\mathcal{N}(\mathbf{s}_{\mathbf{i}}, \mathbf{x}_{\mathbf{l}})$ ,  $\rho(\mathbf{s}_{\mathbf{i}}, \mathbf{x}_{\mathbf{l}})$  entries in the flow table for some input are made different by assigning the added output to make them different. Thus, these states become distinguishable at the earliest possible time.

The addition of outputs to the machine doesn't alter state identification sequences which existed prior to the addition. Existing output vector components are never changed. Thus, these components partition the machine's state set into blocks as they previously did. The added components simply break up nonsingleton blocks of  $\omega((\bar{x}_m)_j)$ into smaller blocks. Additional outputs for states which possess identification sequences are free and may be used as don't care conditions (dc). In many cases, identification sequences for states which previously exhibited them become shorter. The added outputs create state information and Theorem 2.6 shows that if carried far enough, all states would have a state identification sequence of length one for every  $x_1 \in I$ . In example 3.2, state A results with a state identification sequence whose length is one less than without the output.

This algorithm makes use of  $\omega((\bar{\mathbf{x}}_m)_j)$  as defined in Section 3.1.1. Breaking up the blocks of  $\omega((\bar{\mathbf{x}}_m)_j)$ , through additional outputs, results in state identification sequences for states which do not have them. The algorithm follows.

- 1. Initially set the index m to zero.

- 2. Apply the state identification sequence algorithm and increment m by 1.

- 3. Partition the states of the machine into two blocks  $\nu_1$  and  $\nu_2$  such that  $s_i$  is in  $\nu_1$ , iff it has an IS.

- 4. If  $V_2$  is empty, stop; otherwise continue.

- 5. For each  $x_1 \in I$ , determine  $\omega(x_1)$ .

- 6. Construct an array (A), one row for each state in  $\nu_2$  and one column for each  $x_1 \in I$ . The entries for A are

$$a_{i,j} = \left\{ s_j : s_j \neq s_i \text{ and } s_j \text{ is contained in the same block of } \omega(x_j) \text{ as } s_i \right\}.$$

7. For each  $s_i$ , assign  $z_m$  for all  $x_l \in I$  which has not had  $z_m$  assigned, as follows.

7a If

$$s_i \in V_1$$

,  $\rho_m(s_i, x_1) = dc$ .

7b If

$$s_i \in V_2$$

,  $\rho_m(s_i, x_l) \neq \rho_m(s_j, x_l)$ , for all  $s_j \in a_{il}$ .

8. Go to step 2.

The don't care situation allows the freedom of using this design procedure with any other state assignment criterion.

## Example 3.2

Using M<sub>2</sub> from Example 3.1, steps 1, 2 and 3 have been completed previously with states B and C found not to have state identification sequences. Application of steps 4 and 5 result in the following.

Steps 6 and 7 give rise to the new flow table M2.

In the simplified form this appears as the following.

Application of the state identification sequence algorithm yields the following complete IS set.

$IS_{A} = 10/10$

$IS_R = 0/0$

$IS_C = 1/0$

$IS_D = 0/3$

## 3.3 Additional Input Algorithm

To facilitate fault detection, an additional input has been considered by Kane and Yan (28), Murakami and Kinoshita (4). This notion of an additional input is expanded in this dissertation resulting in the capability of completing a machine's IS set. The state identification sequences generated are as short as possible. The possibility of an additional input in finding a means of making a machine more readily tested is evident in Theorem 2.7.

A primary goal in the derivation of checking experiments is to make the experiment as concise as possible. If a machine has a complete IS set, it is needless to add the additional input. If a machine has a partial IS set, then by a prescribed assignment of its state set to the state set of machine  $\mathbf{M}_h$  (Section 2.4), a shorter set of identification sequences can be constructed for the machine. This is accomplished by choosing one of the states not having an identification sequence to be  $\mathbf{s}_k$ . The next state without an identification sequence is assigned  $\mathbf{s}_k$  as its next state, etc.. The procedure of adding one input to complete the IS set for a machine is the following.

- 1. Apply the state identification sequence algorithm to the machine.

- 2. If the machine has a complete IS set, terminate; otherwise continue.

- 3. If the machine has a partial IS set, continue; otherwise go to step 5.

- 4. For the states which do not have an identification sequence, arrange them such that they are  $s_k$ ,  $s_{k-1}$ ,  $s_{k-2}$ , etc. until all such states are covered. Now the states with identification sequences can be arranged in the remainder of  $M_h$  in any manner.

- 5. Append the input h to the original machine and assign the entries for this input using the cyclic pattern indicated in  $M_h$ .

The design of a machine using this procedure and the added input h will make any machine have a complete IS set. This is true even if the original machine is non-reduced or not strongly connected.

## 3.4 Inaccessible State Assignment Algorithm

Prior to the introduction of the material in this section, no state assignment procedures have been given in the literature which have attempted to design inaccessible states such that faults causing entry to these states can be detected. The inaccessible state assignment algorithm follows.

- 1. For a sequential machine with p input and q output symbols, construct an array (B) having pq rows and 2 columns. Each row corresponds to a different possible  $x_1/r_j$  combination where  $x_1 \in I$  and  $r_j \in O$ .

- 2. The entries in B are:

$$b_{(x_1/r_j)1} = \{s_p: \text{ for all } s_i, \eta(s_i, x_1) = s_p \text{ when } \\ \rho(s_i, x_1) = r_j\}$$

$$b_{(x_1/r_j)^2} = \{ s_p : s_p \in S \text{ and } s_p \notin b_{(x_1/r_j)^1} \}.$$

3. For each inaccessible state  $(s_m)$ , assign a unique  $\eta(s_m, x_i)$ ,  $\rho(s_m, x_i)$  for all  $x_i \in I$ , such that

$$(s_m, x_i) \in b_{(x_i/r_j)2}$$

and

$$\rho(s_m, x_i) = r_i$$

When more than one choice is available in  $b_{(x_1/r_j)2}$ , any will suffice. However, certain design criteria may make one choice more desirable than another.

## Theorem 3.4:

If the original n states of an n-state sequential machine have identification sequences, assignment of entries to the r<sup>V</sup>-n inaccessible states using the inaccessible state assignment algorithm results in a complete IS set for the machine.

#### Proof:

Either by Theorem 2.3 or the inaccessible state assignment algorithm every state  $s_i$  of the machine has some input symbol such that for all  $i \neq j$ ,

$$\eta(s_i, x_m), \rho(s_i, x_m) \neq \eta(s_i, x_m), \rho(s_i, x_m).$$

Apply the particular  $\mathbf{x}_{m}$  for  $\mathbf{s}_{i}$  for which this is true. Now if the response is the same as some other state response, the next state must be different, and if the next state is the same, the response must be different which causes  $\mathbf{x}_{m}$  to distinguish  $\mathbf{s}_{i}$  from all  $\mathbf{s}_{j}$  which have the same next state as  $\mathbf{s}_{i}$  under  $\mathbf{x}_{m}$ .

Since every state has as next states one of the original n and each of the original n has an input sequence which distinguishes it from the n-1 other accessible states, application of  $x_m$  concatenated with  $IS_{n}(s_i, x_m)$  will distinguish  $s_i$  from all states. Hence, each of the  $r^{\mathbf{v}}$  states has an identification sequence.

The only item remaining in designing a machine to ensure that it is capable of being tested for faults that cause paths to inaccessible states, is creating access to

the inaccessible states. In Section 2.4 the cyclic, single input, machine  $\mathbf{M}_{h}$  was investigated and will serve as a model for creating the desired access.

## Example 3.3

The following example illustrates this algorithm by using  $M_3$ .

Steps 1 and 2 result in the following table.

Step 3 yields the following machine.

Appending the single input h and its cyclic entries gives the following.

Application of the state identification sequence algorithm returns the complete IS set.

No criteria has been given for choosing the unique entries for inaccessible states. The question of which decision is best and how decisions affect the length of state identification sequences is left to future work.

## 3.5 Chapter Summary

The purpose of this chapter was to investigate how to make a machine more easily testable by design. It has been shown that machines can be designed using additional outputs or an additional input to generate a machine of higher dimensionality which has a complete IS set and a distinguishing sequence. The question of whether it is better to add one additional input or additional outputs must be answered by the designer. Adding one input requires checking n more transitions in an n-state machine. Additional outputs may require more than one terminal being added to the machine. The additional implementation which must be added in either case may also be a deciding factor.

The greatest depth that must be completed for the successor tree in the state identification sequence algorithm is  $(n-1)^2$ . The maximum depth required for other sequences discussed in this dissertation according to Gill (17), Ginsburg (18), Hibbard (25) and Kohavi (32) are:

SS:  $(n-1)^2 n/2$ ;

HS: n(n-1)/2;

DS:  $(n-1)n^n$ .

In comparison to the distinguishing sequence, computation of a state identification sequence is shorter and requires less memory.

Since a state identification sequence is the shortest sequence which can be used to identify the state of a machine, the use of such sequences in checking experiments will result in checking experiments of shorter length than experiments using other sequences to identify states.

#### CHAPTER 4

# AN ALGORITHM FOR DETECTING FAULTS IN SEQUENTIAL MACHINES

It has been shown that the present state of a machine can be verified if the machine has a complete IS set.

Means of modifing machines which do not possess a complete IS set have been shown. The ability to verify the state of a machine is the basic tool used in an algorithm developed in this chapter. The machines to be considered in this fault detection algorithm must be completely specified, finite state and deterministic. This chapter also presents methods by which two classes of machines (non-strongly connected and nonreduced) can also be tested.

To make checking experiments produced by this algorithm efficient, a notational representation for the Mealy type sequential machine is introduced. This notation assists in eliminating redundancies in the checking experiment. Examples demonstrate the algorithm.

To establish apriori information regarding the length of checking experiments, bounds on experiment length are established.

## 4.1 Strongly Connected and Reduced Machines

In any fault detecting experiment which verifies the flow table transitions and associated responses, the experiment must be capable of maneuvering the machine into each state.

## Definition 4.1

If for every pair of states  $s_i$ ,  $s_j$  of a machine M there exists an input sequence which takes M from  $s_i$  to  $s_j$ , then M is said to be strongly connected.

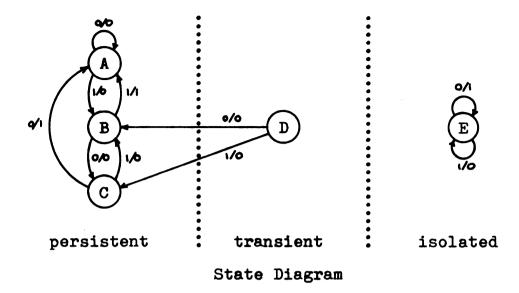

Thus, non-strongly connected machines contain states which cannot be entered from other states. Non-strongly connected machines are those which have persistent, isolated or transient submachines. The following machine,  $M_{\mu}$ , exhibits these submachines most readily by means of a state diagram.

M4

Because this machine has inaccessible states, the arguments used for faults which increase the number of accessible states are applicable.

Machines which are not reduced (Definition 2.10) can be represented by machines having fewer states. Suppose a fault in a non-reduced sequential machine causes state  $\eta(s_i, x_m)$  to be equivalent to the correct state. Then a fault exists and the machine performance is unchanged. We express this point in the following lemma which will not be proved.

#### Lemma 4.1:

In a non-reduced machine, a fault causing a transition to a different member of an equivalent set of states is in effect not a fault in that it does not change the behavior.

To derive a checking experiment for a non-reduced machine, reduce the machine flow table. Then use the state identification sequence found for all states, representing an equivalent set of states, as the identification sequence for each state of the set of states in which these representatives are contained.

## 4.2 Working Form Notation

A flow table representation called the "working form notation" is defined below. This notation is advantageous in fault detecting experiments because information about the machine is displayed in the experiment. The standard flow table notation, where columns represent inputs and rows represent states of the machine, uses

$$\eta(s_i, x_i), \rho(s_i, x_i)$$

as the row  $s_j$  column  $x_l$  entry. In working form notation

$$\eta(s_j, x_1), \rho(s_j, x_1)$$

is replaced by  $W_i^z$ , where W is  $\eta(s_j, x_1)$ , z is  $\rho(s_j, x_1)$ , and i is a unique pointer to each entry. An algorithm for going from flow table to working form notation is given in the following steps.

## 4.2.1 Working Form Algorithm

1. For each state of the machine, determine  $W_i^z$  for all  $x_1$  in I, where:

$$W = \gamma(s_j, x_1);$$

$$z = \rho(s_j, x_1);$$

- i = c-l+(r-l)m+l, where r and c are row and

column number and m is the maximum number

of columns (inputs). The index i is unique

for each entry.

- 2. Replace each  $\eta(s_j, x_1), \rho(s_j, x_1)$  by its corresponding  $w_i^z$ .

## Example 4.1

To illustrate this algorithm, consider machine  $M_2$  and its working form representation.

Morking Form

From the following arbitrary experiment conducted on  $M_2$ , initially in state A, it is evident that the working

form representation of the experiment indicates at each step the input, the output, and the next state for the machine.

110111011110110110101 input 000000100001000000000 output

$B_{2}^{0}C_{4}^{0}A_{5}^{0}B_{2}^{0}C_{4}^{0}D_{6}^{0}A_{7}^{1}B_{2}^{0}C_{4}^{0}D_{6}^{0}D_{8}^{0}A_{7}^{1}B_{2}^{0}C_{4}^{0}A_{5}^{0}B_{2}^{0}C_{4}^{0}A_{5}^{0}B_{2}^{0}A_{3}^{0}B_{2}^{0} \qquad \text{Working Form}$

This notation is particulary useful for concatenating sub-experiments and determining when they overlap.

#### 4.3 Transfer Sequences

In conducting machine experiments, the situation often arises where the machine is in one state and it is necessary to maneuver it into a different state. For small machines the transfer sequence is usually directly deducible from the flow table. However, for large machines, some necessary sequence or shortest sequence is not as easily found. Since conciseness is a goal in checking experiments, it will be necessary to have a procedure to find the shortest transfer sequence for a machine. The transition matrix is a useful tool for this purpose.

The <u>transition matrix</u>  $T = [t_{ij}]$  for an n-state sequential machine is an n x n matrix. Given that the machine's state set is

$$s = \{s_1, s_2, ..., s_n\},\$$

assignment of the j<sup>th</sup> state (s<sub>j</sub>) to the j<sup>th</sup> row and column will make book-keeping an easier task. Entries in T are

$$t_{ij} = \left\{ x_m : x_m \in I \text{ and } \eta(s_i, x_m) = s_j \right\}.$$

For the machine  $M_1$  of Section 2.2, the following transition matrix is obtained where  $\emptyset$  is the null set.

The <u>transfer sequence matrix</u> is now constructed from the transition matrix. A transfer sequence is transitive. That is, if  $T(s_i, s_j)$  and  $T(s_j, s_m)$  exist, then  $T(s_i, s_m)$  does also. The existence of  $T(s_i, s_j)$  does not imply that of  $T(s_j, s_i)$  and hence, a transfer sequence is not symmetric. The transfer sequence matrix is constructed by taking the transitive closure of the transition matrix using the following algorithm.

## 4.3.1 Transfer Sequence Matrix Algorithm

Prior to presenting the steps of the algorithm, some notation is considered. The transfer sequence matrix row i column j entry is referred to as t<sub>ij</sub>. The length of a sequence is

$$L(\bar{x}_k) = k,$$

where k is the number of symbols in the sequence and

$$L(\emptyset) = \infty.$$

Since all members of t<sub>ij</sub> are initially the same length and concatenations performed during the process do not cause any entries to have members of different lengths,

$$L(t_{ij}) = L((\bar{x}_m)_1 \in t_{ij}).$$

- 1. Construct the transition matrix for the machine and assign i the value O.

- 2. Increment i by 1.

- 3. If i = n (number of states in machine), terminate;

otherwise continue.

- 4. Assign j the value 0.

- 5. Increment j by 1 and assign m the value 1.

- 6. If j > n, go to step 2; otherwise continue.

- 7. If j = i or  $t_{ji} = \emptyset$ , go to step 5; otherwise continue.

- 8. If m > n, go to step 5; otherwise continue.

- 9. Left concatenate  $t_{ji}$  with  $t_{im}$  and assign  $t_{jm}$  as follows.

$$\mathbf{t}_{jm} = \begin{cases} \mathbf{t}_{jm}, & \text{if } L(\mathbf{t}_{ji}\mathbf{t}_{im}) < L(\mathbf{t}_{jm}) \\ (\mathbf{t}_{jm} \ \mathbf{U} \ \mathbf{t}_{ji}\mathbf{t}_{im}), & \text{if } L(\mathbf{t}_{ji}\mathbf{t}_{im}) = L(\mathbf{t}_{jm}) \\ \mathbf{t}_{ji}\mathbf{t}_{im}, & \text{if } L(\mathbf{t}_{ji}\mathbf{t}_{im}) > L(\mathbf{t}_{jm}). \end{cases}$$

10. Increment m by 1 and go to step 8.

The transfer sequence matrix algorithm is a result of applying the notion of Warshall's algorithm (50) to the sequential machine. The time complexity of transitive closure in the transfer sequence matrix algorithm for an n-state machine is no greater than n<sup>3</sup>. Since only the shortest transfer sequences are retained during an iteration of the algorithm, the resulting matrix contains the shortest possible transfer sequences.

## Example 4.2

Using this algorithm on  $M_1$  yields the following results.

|   |                   | _ A         | В       | C     | D _   |             |

|---|-------------------|-------------|---------|-------|-------|-------------|

|   | A Ø               |             | Ø       | 0     | ı     |             |

|   | В                 | ø<br>ø<br>ø | Ø       | 0     | 1     |             |

|   | C                 | ø           | 0       | Ø     | 1     |             |

|   | D                 | 0,1         | Ø       | 00,10 | 01,11 | i=l         |

|   |                   | _           |         |       | _     |             |

|   |                   | A           | В       | C     | D     |             |

|   | A                 | Ø           | Ø       | 0     | ı     |             |

|   |                   | ø           | Ø       | 0     | 1     |             |

|   | A Ø B Ø C Ø D O,1 |             | 0       | 00    | 1     |             |

|   | D 0,1             |             | Ø       | 00,10 | 01,11 | <b>i</b> =2 |

|   |                   | _           |         |       | -     |             |

|   |                   | A           | В       | C     | D     |             |

| A |                   | Ø           | 00      | 0     | 1     | 7           |

| В |                   | ø<br>ø      | 00      | 0     | 1     |             |

| C | ø                 |             | 0       | 00    | 1     |             |

| D | 0,1               |             | 000,100 | 00,10 | 01,   | 11 i=3      |

|   | _                 |             |         |       |       | _           |

|   |                   | A           | В       | C     | D     |             |

| A | \[ \] 10          | ,11         | 00      | 0     | 1     | 7           |

| В | 10                | ,11         | 00      | 0     | 1     |             |

| C | 10                | ,11         | 0       | 00    | 1     |             |

| D | c                 | ),1         | 000,100 | 00,10 | 01,   | ll   i=4    |

Thus, the transfer sequence matrix algorithm reveals

the shortest sequence of input symbols required to take the machine from one state to another. For machine M<sub>1</sub>, the transfer sequence from state C to state A is either 10 or 11 and represents the shortest path. The process of finding the transfer sequence matrix is equivalent to that of finding the shortest path between any two nodes in a graph.

#### 4.4 Sub-experiment Overlapping and Concatenation

The algorithm which will be presented in the next section is dependent on a "checking table", defined below. The checking table consists of 4 columns and np rows for an n-state, p-input sequential machine. Column 1 contains the indices for the working form representation in numerical order. The column labelled  $\mathbf{s_i}$ ,  $\mathbf{s_j}$  has in row m the present state and the next state for the m<sup>th</sup> index in the working form representation. The column labelled  $\mathcal{T}(\mathbf{s_i}, \mathbf{s_j})$  has in row m the working form representation having the index m. The final column in the table is the working form representation of the identification sequences for the left entries in column  $\mathbf{s_i}$ ,  $\mathbf{s_j}$ . The following illustrates the checking table.

| index | s <sub>i</sub> ,s <sub>j</sub> | (s <sub>i</sub> , s <sub>j</sub> ) | IS <sub>s</sub> j                               |

|-------|--------------------------------|------------------------------------|-------------------------------------------------|

| 1     | A,B                            | B <sub>1</sub> 0                   | A <sup>O</sup> D <sup>O</sup> D <sup>1</sup> 7  |

| 2     | A,D                            | D <sub>0</sub>                     | $C_{8}^{0}A_{6}^{0}B_{1}^{0}B_{4}^{0}A_{3}^{0}$ |

| 3     | В,А                            | A <sup>0</sup> <sub>3</sub>        | $B_{1}^{0}B_{4}^{0}A_{3}^{0}$                   |

| 4     | В,В                            | B <sub>4</sub> <sup>0</sup>        | A <sup>0</sup> D <sup>0</sup> D <sup>1</sup> 7  |

| 5     | C,D                            | D <sub>5</sub>                     | $C_{8}^{0}A_{6}^{0}B_{1}^{0}B_{4}^{0}A_{3}^{0}$ |

| 6     | C,A                            | A <sub>6</sub>                     | $B_{1}^{O}B_{4}^{O}A_{3}^{O}$                   |

| 7     | D,D                            | D <sub>7</sub> 1                   | $C_{8}^{0}A_{6}^{0}B_{1}^{0}B_{4}^{0}A_{3}^{0}$ |

| 8     | D,C                            | c <sub>8</sub> 0                   | A6B1B4A3                                        |

Checking Table for  $M_5$

Using the checking table, each  $T(s_i, s_j)$  concatenated with IS<sub>sj</sub> constitutes a sub-experiment. Overlapping is commenced by assuming an initial index. The sub-experiment corresponding to this index begins the CE. The next

candidate for the CE is the sub-experiment whose index is the subscript of the second member in the CE. If all of the candidate's members coincide with the CE's members, when positioned over the CE member whose subscript nominated the candidate, the two overlap and any members of the candidates extending beyond the CE are retained. The next rightmost subscript is attempted to find a candidate and if its members do not coincide, the next rightmost subscript is attempted until no next right subscript exists. Any index which has been used previously is never reused. This process is illustrated in the following assuming the initial index 2.

| index         | $\tau(s_i, s_j)Is_{s_j}$                                              |  |  |  |

|---------------|-----------------------------------------------------------------------|--|--|--|

| 2             | D2C8A6B1B4A3                                                          |  |  |  |

| 8             | $C_{8}^{O}A_{6}^{O}B_{1}^{O}B_{4}^{O}A_{3}^{O}$                       |  |  |  |

| 6             | $A_{6}^{O}B_{1}^{O}B_{4}^{O}A_{3}^{O}$                                |  |  |  |

| 4             | BOAODOD1                                                              |  |  |  |

| 7             | $D_{7}^{1}C_{8}^{0}A_{6}^{0}B_{1}^{0}B_{4}^{0}A_{3}^{0}$              |  |  |  |

| 2, 8, 6, 4, 7 | ${\tt D_2^OC_8^OA_6^OB_1^OB_4^OA_3^OD_2^OD_7^C8A_6^OB_1^OB_4^OA_3^O}$ |  |  |  |

Each experiment generated through overlapping is now a new sub-experiment. Suppose the overlapping and merging of the previous sub-experiment resulted in the following list of sub-experiments.

2, 8, 6, 4, 7

$$D_{2}^{0}C_{8}^{0}A_{6}^{0}B_{1}^{0}B_{4}^{0}A_{3}^{0}D_{2}^{0}D_{7}^{1}C_{8}^{0}A_{6}^{0}B_{1}^{0}B_{4}^{0}A_{3}^{0}$$

5, 3  $D_{5}^{1}C_{8}^{0}A_{6}^{0}B_{1}^{0}B_{4}^{0}A_{3}^{0}B_{1}^{0}B_{4}^{0}A_{3}^{0}$

1  $B_{1}^{0}A_{3}^{0}D_{2}^{0}D_{7}^{1}$

Since each new sub-experiment indicates which state the machine will be in after its completion, any further concatenation of them requires that the next sub-experiment begins from that state for the sake of continuity. In this example, sequence "2, 8, 6, 4, 7" ends in state A and since sequence "1" begins with a transition from state A, the two sequences can be concatenated. In the event that a sequence does not begin with a transition from the final state of the previous sequence, a transfer sequence must be found such that the two sequences are properly connected. Hence, the transfer sequence matrix becomes useful. To concatenate "1" with "5, 3", the transfer sequence  $\mathcal{T}(D, C)$  is required.

$M_5$  Transfer Sequence Matrix

Thus,  $C_8^0$  is the correct transfer sequence which will perform the concatenation and would appear as "1"  $C_8^0$  "5, 3". The final sequence is