# LIBRARY Michigan State University

This is to certify that the

dissertation entitled

A Generic Framework for Formalizing Object Oriented Modeling Notations for Embedded Systems Development

presented by

William Eugene McUmber

has been accepted towards fulfillment of the requirements for

Ph.D. degree in Computer Science and Engineering

Betty H. Cherry Major professor

Date 8/21/00

MSU is an Affirmative Action/Equal Opportunity Institution

0-12771

## PLACE IN RETURN BOX to remove this checkout from your record. TO AVOID FINES return on or before date due. MAY BE RECALLED with earlier due date if requested.

| DATE DUE | DATE DUE | DATE DUE |

|----------|----------|----------|

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

|          |          |          |

11/00 c:/CIRC/DateDue.p65-p.14

A G Mor

## A GENERIC FRAMEWORK FOR FORMALIZING OBJECT-ORIENTED MODELING NOTATIONS FOR EMBEDDED SYSTEMS DEVELOPMENT

$\mathbf{B}\mathbf{y}$

William Eugene McUmber

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

Department of Computer Science and Engineeering

August 8, 2000

in order

#### ABSTRACT

A GENERIC FRAMEWORK FOR FORMALIZING OBJECT-ORIENTED MODELING

NOTATIONS FOR EMBEDDED SYSTEMS DEVELOPMENT

Bv

#### William Eugene McUmber

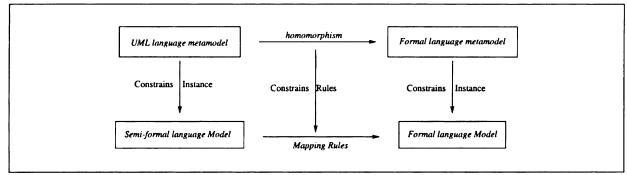

Embedded systems are 10 to 100 times more numerous than traditional systems with displays and keyboards But even though the object-oriented paradigm has been used to develop many traditional systems, it has not been widely applied to embedded systems. Application of the object-oriented paradigm in industry is encouraged and reinforced by graphical methods such as the Object Modeling Technique (OMT) and the Universal Modeling Language (UML), but the semantics of the diagrams are not rigorous. This research provides formal semantics for UML models in order to build embedded systems. This formalization enables the automated analysis of diagrams, such as simulation and model checking, which are particularly critical for the development of embedded systems, given the demand for specifying temporal and concurrency properties. This research constructs homomorphisms between metamodels of the source semi-formal language and the target formal language, so that consistency of formalization rules can be mechanically established in order to provide precise semantics to the semi-formal notation.

To my v

.

| To my wife, Cheryl, and my sons   | , Robbie and Weston,    | who have supported me |

|-----------------------------------|-------------------------|-----------------------|

| throughout while enduring my long | hours and lack of avail | lability              |

|                                   |                         |                       |

|                                   |                         |                       |

|                                   |                         |                       |

|                                   |                         |                       |

iv

I have kn

excellent

would not

student a

asked the

It was

and I trie

homomor

I wis!

formalit i

So ma

I wish to

Stirewalt

$F_{inal}$

through

the sacrif

#### ACKNOWLEDGMENTS

I have known Dr. Betty H. C. Cheng for quite some time because working, caring for family, and earning a Ph.D. all at once, takes a long time. Without her extreme patience, excellent advice, frequent encouragement, and expert editing capabilities, this dissertation would not have occurred. I'll bet she'll be careful about taking a "non-traditional" Ph.D. student again.

It was during my friend Enoch Wang's dissertation defense, that Dr. Anthony Wojcik asked the critical question that became central to this dissertation. It was a good question and I tried to build on Enoch's work to answer that question.

I wish also to thank Dr. Kurt Stirewalt for our many discussions about many things from homomorphic mappings, to semantics. Dr. Stirewalt was extremely helpful formulating the formalities and meanings of the homomorphisms.

So many others provided help along the way it is impossible to list them all in this space.

I wish to thank my committee members: Dr. Betty H. C. Cheng (chairperson), Dr. Kurt

Stirewalt, Dr. Anthony Wojcik, and Dr. Jacob Plotkin.

Finally, my wife, Cheryl, and my sons Rob and Weston, shared, and at times suffered, through this long process. I couldn't have done it without them and I deeply appreciate the sacrifices they made because I didn't have time for this or that. I do now.

#### LIST OF

- 1 Introd 1.1 Proble 1.2 Resea 1.3 Thesis 1.4 Organ

- 2 Backgr 21 UML 22 VHD 22.1 Str 22.2 Sig 22.3 Sig 22.4 Dat 23 Prom 23.1 Str 23.2 Ch 23.3 Dif 24 Mode 24.1 CT 24.2 SP 25 Form

- 3 Metar 31 Class 31.1 Foot 31.2 En 31.3 Mt 31.4 Ex 32 Mapp 32.1 Inf 32.2 Ho 32.3 Ha 32.4 Ta 33 Unifi

#### TABLE OF CONTENTS

| LIST OF FIGURES                                    | Х  |

|----------------------------------------------------|----|

| 1 Introduction                                     | 1  |

| 1.1 Problem Description                            | 3  |

| 1.2 Research Program                               | 4  |

| 1.3 Thesis Statement                               | 5  |

| 1.4 Organization of Dissertation                   | 6  |

| 2 Background                                       | 8  |

| 2.1 UML Overview                                   | 8  |

| 2.2 VHDL Overview                                  | 15 |

| 2.2.1 Structure and Statements                     | 16 |

| 2.2.2 Signals and Communications                   | 19 |

| 2.2.3 Signal Busses - Multiple Signal Drivers      | 20 |

|                                                    | 20 |

| · · ·                                              | 21 |

|                                                    | 21 |

| 2.3.2 Channels and Communications                  | 23 |

| 2.3.3 Differences From Other Guarded Languages     | 25 |

|                                                    | 25 |

| <del>-</del>                                       | 27 |

| 2.4.2 SPIN                                         | 28 |

| 2.5 Formal and Informal models                     | 29 |

|                                                    |    |

| 3 Metamodels and Mapping Framework                 | 32 |

| 3.1 Class Model Formalization                      | 32 |

|                                                    | 33 |

| 3.1.2 Enhanced Class Formalization                 | 34 |

| 3.1.3 Multiplicity Constraints, Revisited          | 37 |

| 3.1.4 Example of a Class Formalization             | 40 |

| 3.2 Mapping Framework                              | 42 |

| 3.2.1 Informal Discussion of the Mapping Framework | 43 |

| 3.2.2 Homomorphic Mappings on Metamodels           | 46 |

| 3.2.3 Handling Structurally Different Metamodels   | 47 |

| 3.2.4 Target Metamodel Templates                   | 48 |

| 3.3 Unified UML Class and Dynamic Metamodel        | 50 |

- 4 Design

41 Design

411 Use

412 Use

413 Clas

414 Clas

415 Sequ

416 Dyn

417 Sim

42 Choos

43 Feedb

44 Relati

#### 5 UML t

- 51 UML

- 5.1.1 Hon 5.2 UML 5.2.1 Clas 5.2.2 Dyr 5.2.3 Join 5.3 Exam

- 5.3.1 VH

- 5.3.2 Beh 5.3.3 Disc

## 6 UML 1

- 91 LMT

- 61.1 Hor 6.2 UML

- 621 Glo

- 6.2.2 Cla 6.2.3 Dyr

- 7 Relate

7.1 Ember

7.1.1 Ad

7.1.2 Str

7.1.3 RT

7.1.4 RO

7.1.5 Res

7.2 Grap

7.2.1 DF

- 721 DF 722 Flo 723 Fin 724 Ext 725 Sta 726 Spe 727 Pet

|                                                                                                                                                                      | esign Process                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>53</b>                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 4.1                                                                                                                                                                  | Design Process Data Flow                                                                                                                                                                                                                                                                                                                                                                                                         | 53                                                                                                                  |

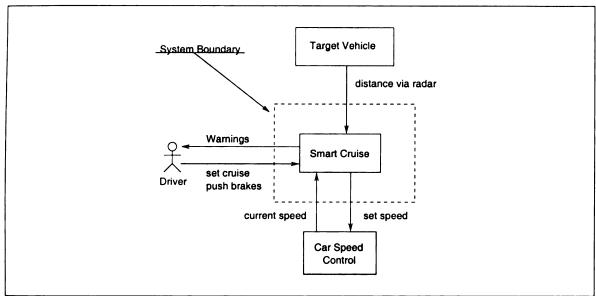

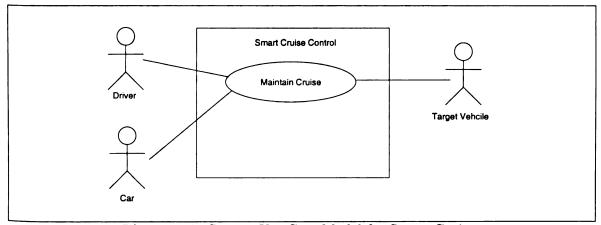

| 4.1.1                                                                                                                                                                | Use Case and Context Model                                                                                                                                                                                                                                                                                                                                                                                                       | 54                                                                                                                  |

| 4.1.2                                                                                                                                                                | Use Case Scenarios                                                                                                                                                                                                                                                                                                                                                                                                               | 57                                                                                                                  |

| 4.1.3                                                                                                                                                                | Class Model                                                                                                                                                                                                                                                                                                                                                                                                                      | 57                                                                                                                  |

| 4.1.4                                                                                                                                                                | Class Responsibility List                                                                                                                                                                                                                                                                                                                                                                                                        | 58                                                                                                                  |

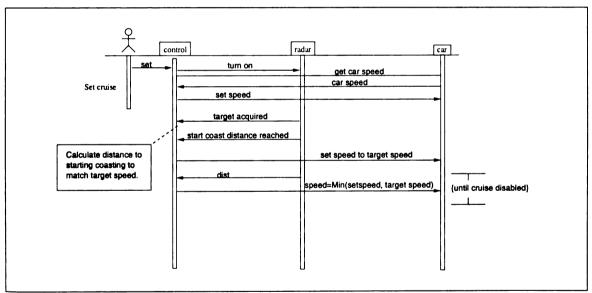

| 4.1.5                                                                                                                                                                | Sequence Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                | 58                                                                                                                  |

| 4.1.6                                                                                                                                                                | Dynamic Model                                                                                                                                                                                                                                                                                                                                                                                                                    | 60                                                                                                                  |

| 4.1.7                                                                                                                                                                | Simulation and Model Checking                                                                                                                                                                                                                                                                                                                                                                                                    | 60                                                                                                                  |

| 4.2                                                                                                                                                                  | Choosing Semantics                                                                                                                                                                                                                                                                                                                                                                                                               | 61                                                                                                                  |

| 4.3                                                                                                                                                                  | Feedback Loops                                                                                                                                                                                                                                                                                                                                                                                                                   | 62                                                                                                                  |

|                                                                                                                                                                      | Relation of the methodology to Formalization Integration                                                                                                                                                                                                                                                                                                                                                                         | 63                                                                                                                  |

|                                                                                                                                                                      | <del>-</del>                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |

|                                                                                                                                                                      | ML to VHDL Mapping Rules                                                                                                                                                                                                                                                                                                                                                                                                         | 64                                                                                                                  |

|                                                                                                                                                                      | UML to VHDL Diagram Homomorphisms                                                                                                                                                                                                                                                                                                                                                                                                | 64                                                                                                                  |

| 5.1.1                                                                                                                                                                | Homomorphic Mapping                                                                                                                                                                                                                                                                                                                                                                                                              | 67                                                                                                                  |

|                                                                                                                                                                      | UML to VHDL Mapping Rules                                                                                                                                                                                                                                                                                                                                                                                                        | 70                                                                                                                  |

| 5.2.1                                                                                                                                                                | Class Diagram Formalizations                                                                                                                                                                                                                                                                                                                                                                                                     | 70                                                                                                                  |

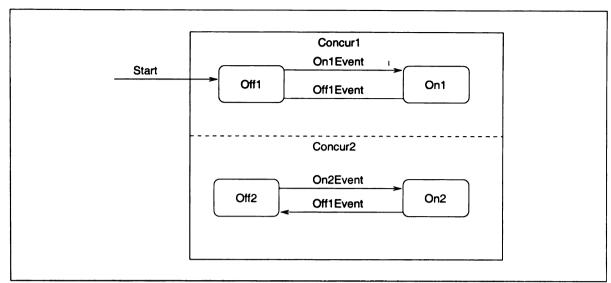

| 5.2.2                                                                                                                                                                | Dynamic Model Formalizations                                                                                                                                                                                                                                                                                                                                                                                                     | 77                                                                                                                  |

| 5.2.3                                                                                                                                                                | Joining Concurrent Threads                                                                                                                                                                                                                                                                                                                                                                                                       | 88                                                                                                                  |

| 5.3                                                                                                                                                                  | Example                                                                                                                                                                                                                                                                                                                                                                                                                          | 92                                                                                                                  |

| 5.3.1                                                                                                                                                                | VHDL Specifications                                                                                                                                                                                                                                                                                                                                                                                                              | 94                                                                                                                  |

| $\boldsymbol{5.3.2}$                                                                                                                                                 | Behavior Validation                                                                                                                                                                                                                                                                                                                                                                                                              | 94                                                                                                                  |

| <b>5.3.3</b>                                                                                                                                                         | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                       | 98                                                                                                                  |

|                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

| 0 TI                                                                                                                                                                 | MT 40 December /CDINI Manusium Dulan                                                                                                                                                                                                                                                                                                                                                                                             | ^^                                                                                                                  |

|                                                                                                                                                                      | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                          | 00                                                                                                                  |

| 6.1                                                                                                                                                                  | UML to Promela Diagram Homomorphisms                                                                                                                                                                                                                                                                                                                                                                                             | 100                                                                                                                 |

| 6.1<br>6.1.1                                                                                                                                                         | UML to Promela Diagram Homomorphisms                                                                                                                                                                                                                                                                                                                                                                                             | 100<br>101                                                                                                          |

| 6.1<br>6.1.1<br>6.2                                                                                                                                                  | UML to Promela Diagram Homomorphisms                                                                                                                                                                                                                                                                                                                                                                                             | 100<br>101<br>104                                                                                                   |

| 6.1<br>6.1.1<br>6.2<br>6.2.1                                                                                                                                         | UML to Promela Diagram Homomorphisms                                                                                                                                                                                                                                                                                                                                                                                             | 100<br>101<br>104<br>106                                                                                            |

| 6.1<br>6.1.1<br>6.2<br>6.2.1<br>6.2.2                                                                                                                                | UML to Promela Diagram Homomorphisms                                                                                                                                                                                                                                                                                                                                                                                             | 100<br>101<br>104<br>106<br>107                                                                                     |

| 6.1<br>6.1.1<br>6.2<br>6.2.1                                                                                                                                         | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations                                                                                                                                                                                                                                                                                       | 100<br>101<br>104<br>106                                                                                            |

| 6.1<br>6.1.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3                                                                                                                       | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations                                                                                                                                                                                                                                                         | 100<br>101<br>104<br>106<br>107<br>114                                                                              |

| 6.1<br>6.1.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3                                                                                                                       | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations                                                                                                                                                                                                                                                         | 100<br>101<br>104<br>106<br>107<br>114                                                                              |

| 6.1<br>6.1.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>7 R                                                                                                                | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations  elated Work  Embedded Systems Methodologies                                                                                                                                                                                                            | 100<br>101<br>104<br>106<br>107<br>114                                                                              |

| 6.1<br>6.1.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br><b>7</b> R<br>7.1                                                                                                  | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations  elated Work  Embedded Systems Methodologies  Ad Hoc                                                                                                                                                                                                    | 100<br>101<br>104<br>106<br>107<br>114<br>.40<br>141                                                                |

| 6.1<br>6.1.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br><b>7</b> R<br>7.1<br>7.1.1                                                                                         | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations  elated Work  Embedded Systems Methodologies  Ad Hoc  Structured Methods                                                                                                                                                                                | 100<br>101<br>104<br>106<br>107<br>114<br>.40<br>141<br>141                                                         |

| 6.1<br>6.2.1<br>6.2.2<br>6.2.3<br>7 R<br>7.1<br>7.1.1<br>7.1.2                                                                                                       | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations  elated Work  Embedded Systems Methodologies  Ad Hoc  Structured Methods  RTOOSA                                                                                                                                                                        | 100<br>101<br>104<br>106<br>107<br>114<br>.40<br>141<br>141<br>142                                                  |

| 6.1<br>6.2.1<br>6.2.2<br>6.2.3<br>7 R<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3                                                                                              | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations  elated Work  Embedded Systems Methodologies  Ad Hoc  Structured Methods  RTOOSA  ROOM                                                                                                                                                                  | 100<br>101<br>104<br>106<br>107<br>114<br>.40<br>141<br>141<br>142<br>144                                           |

| 6.1<br>6.1.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br><b>7</b> R<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5                                                     | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations  elated Work  Embedded Systems Methodologies  Ad Hoc  Structured Methods  RTOOSA  ROOM  Real-Time UML                                                                                                                                                   | 100<br>101<br>104<br>106<br>107<br>114<br>.40<br>141<br>142<br>144<br>146<br>149                                    |

| 6.1<br>6.2.1<br>6.2.2<br>6.2.3<br><b>7</b> R<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5                                                                            | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations  elated Work  Embedded Systems Methodologies  Ad Hoc  Structured Methods  RTOOSA  ROOM  Real-Time UML  Graphical Languages for Embedded Systems                                                                                                         | 100<br>101<br>104<br>106<br>107<br>114<br>.40<br>141<br>142<br>144<br>146<br>149                                    |

| 6.1<br>6.2.1<br>6.2.2<br>6.2.3<br>7 R<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.2<br>7.2.1                                                            | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations  elated Work  Embedded Systems Methodologies  Ad Hoc  Structured Methods  RTOOSA  ROOM  Real-Time UML  Graphical Languages for Embedded Systems                                                                                                         | 100<br>101<br>104<br>106<br>107<br>114<br>.40<br>141<br>142<br>144<br>146<br>149<br>151                             |

| 6.1<br>6.1.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br><b>7</b> R<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.2                                              | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations  elated Work  Embedded Systems Methodologies  Ad Hoc  Structured Methods  RTOOSA  ROOM  Real-Time UML  Graphical Languages for Embedded Systems  DFD-CFD  Flowcharts                                                                                    | 100<br>101<br>104<br>106<br>107<br>114<br>.40<br>141<br>142<br>144<br>149<br>151<br>151                             |

| 6.1<br>6.2.1<br>6.2.2<br>6.2.3<br>7 R<br>7.1.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.2<br>7.2.1<br>7.2.2                                                 | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations  elated Work  Embedded Systems Methodologies  Ad Hoc  Structured Methods  RTOOSA  ROOM  Real-Time UML  Graphical Languages for Embedded Systems  DFD-CFD  Flowcharts  Finite State Machines FSA                                                         | 100<br>101<br>104<br>106<br>107<br>114<br>.40<br>141<br>142<br>144<br>146<br>149<br>151<br>151<br>151               |

| 6.1<br>6.2.1<br>6.2.2<br>6.2.3<br>7 R<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4                                 | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations  elated Work  Embedded Systems Methodologies  Ad Hoc  Structured Methods  RTOOSA  ROOM  Real-Time UML  Graphical Languages for Embedded Systems  DFD-CFD  Flowcharts  Finite State Machines FSA  Extended Finite State Machine                          | 100<br>101<br>104<br>106<br>107<br>114<br>.40<br>141<br>141<br>142<br>144<br>146<br>149<br>151<br>151<br>151<br>152 |

| 6.1<br>6.1.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br><b>7</b> R<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5 | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations  elated Work  Embedded Systems Methodologies  Ad Hoc  Structured Methods  RTOOSA  ROOM  Real-Time UML  Graphical Languages for Embedded Systems  DFD-CFD  Flowcharts  Finite State Machines FSA  Extended Finite State Machine  Statecharts             | 100<br>101<br>104<br>106<br>107<br>114<br>.40<br>141<br>142<br>144<br>146<br>149<br>151<br>151<br>151<br>152        |

| 6.1<br>6.2.1<br>6.2.2<br>6.2.3<br>7 R<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4                                 | UML to Promela Diagram Homomorphisms  Homomorphic Mapping  UML to Promela Mapping Rules  Global Requirements  Class Diagram Formalizations  Dynamic Model Formalizations  elated Work  Embedded Systems Methodologies  Ad Hoc  Structured Methods  RTOOSA  ROOM  Real-Time UML  Graphical Languages for Embedded Systems  DFD-CFD  Flowcharts  Finite State Machines FSA  Extended Finite State Machine  Statecharts  Speccharts | 100<br>101<br>104<br>106<br>107<br>114<br>.40<br>141<br>141<br>142<br>144<br>146<br>149<br>151<br>151<br>151<br>152 |

7.3 Fort 7.3.1 O 7.4 Fort 7.4.1 Ft 7.4.2 T 7.4.3 Fc 7.4.4 E 8 Tool 81 Ove 82 Hyo 83 Hyo 84 Lar 841 C 842 R 843 T 9. Indu 9.1 Des 9.1.1 R 9.1.2 S 9.1.3 S 9.2 Initial 9.4 Cla 9.4.1 S 9.5.1 O 9.5.1 O 9.5.4 O 9.5.5 V 9.5.6 S 9.6.1 F 9.7.1 S 9.7.1 S 9.7.1 S 9.7.2 O 9.7.3 S 9.7.4 S 9.7.4 S 9.7.5 P 9.7.6 N 9.7.7 A 9.8 Dis 9.8.1 B

| 7.3   | Formalization of UML                       | 158 |

|-------|--------------------------------------------|-----|

| 7.3.1 | OCL                                        | 160 |

| 7.4   | Formalization of OO and Other Notations    | 162 |

| 7.4.1 |                                            | 162 |

| 7.4.2 |                                            | 164 |

| 7.4.3 |                                            | 166 |

| 7.4.4 |                                            | 169 |

|       | Extended Incidential I mile State Machines | 103 |

| 8 T   | ool Development                            | 171 |

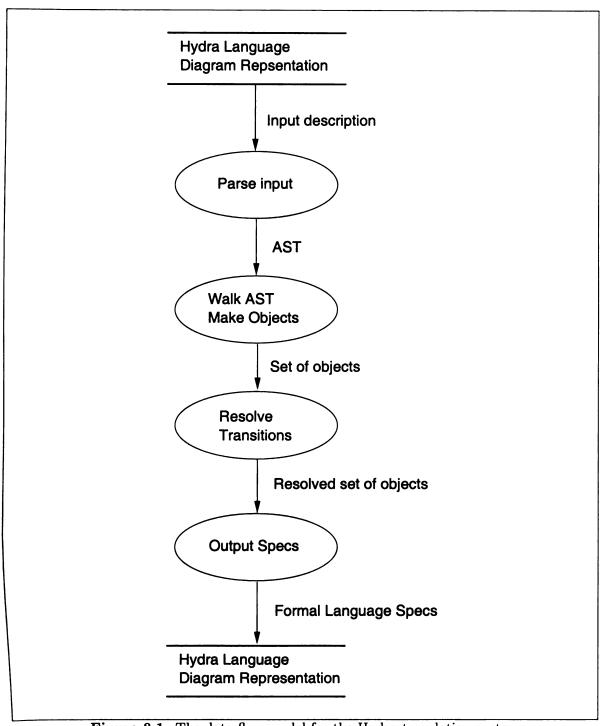

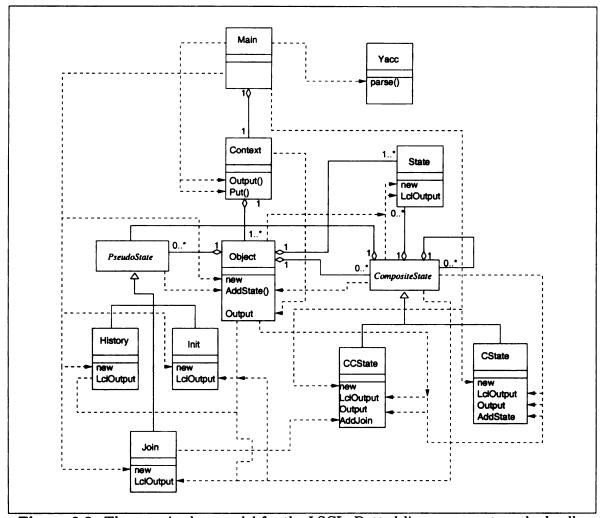

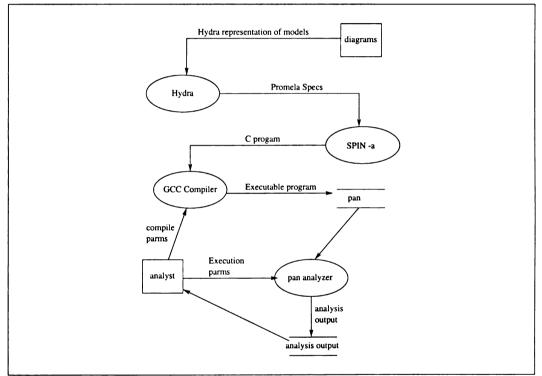

| 8.1   | Overview of Hydra                          | 171 |

|       |                                            | 172 |

|       |                                            | 179 |

|       | •                                          | 180 |

| 8.4.1 | • • •                                      | 184 |

| 8.4.2 |                                            | 184 |

| 8.4.3 | <u> </u>                                   | 187 |

| 0.4.0 | raiget specification defleration           | 101 |

| 9 Ir  | ndustrial Case Study                       | 189 |

|       | •                                          | 190 |

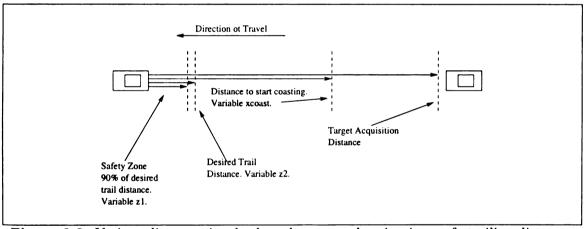

| 9.1.1 | •                                          | 191 |

| 9.1.2 | -                                          | 191 |

| 9.1.3 | ·                                          | 194 |

|       | •                                          | 194 |

|       | • 0                                        |     |

| 9.2.1 |                                            | 196 |

|       | 8                                          | 197 |

|       | •                                          | 199 |

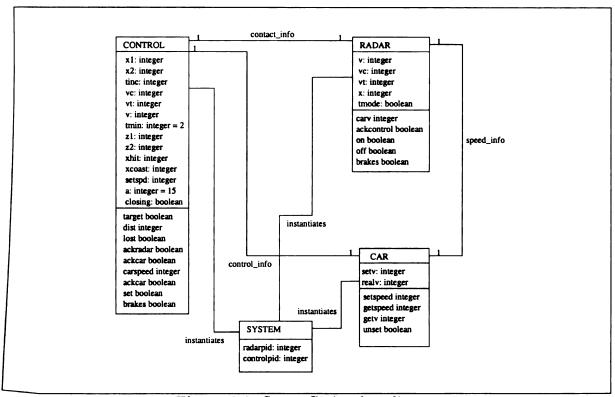

| 9.4.1 | 1 0                                        | 202 |

|       | •                                          | 203 |

| 9.5.1 | 0                                          | 204 |

| 9.5.2 |                                            | 205 |

| 9.5.3 | • · · · · · · · · · · · · · · · · · · ·    | 205 |

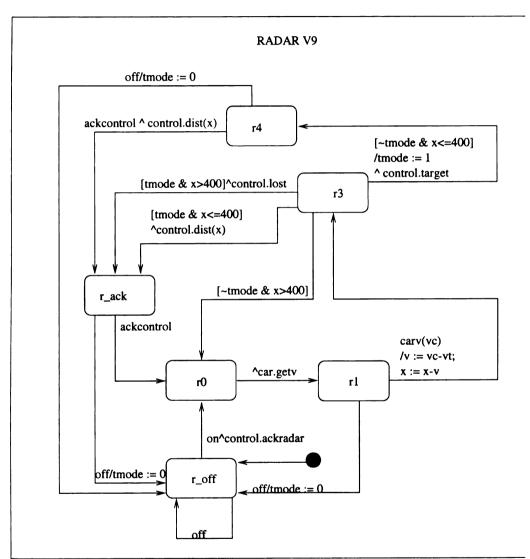

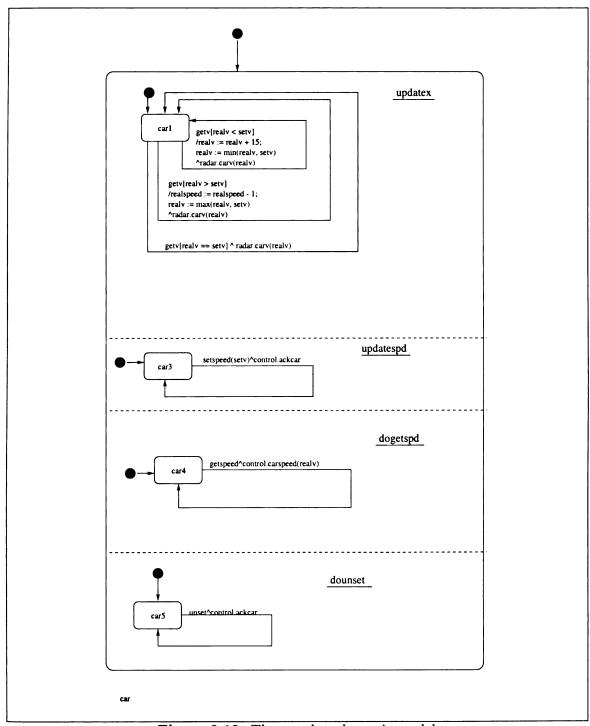

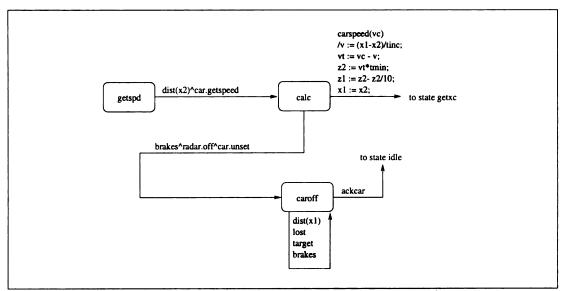

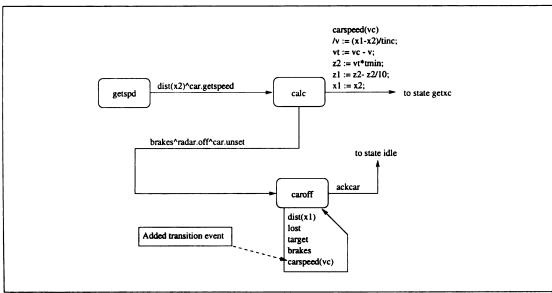

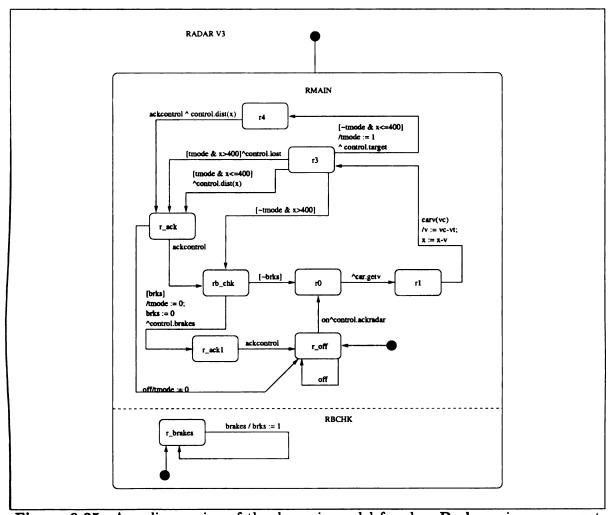

| 9.5.4 | Class Car Dynamic Model                    | 206 |

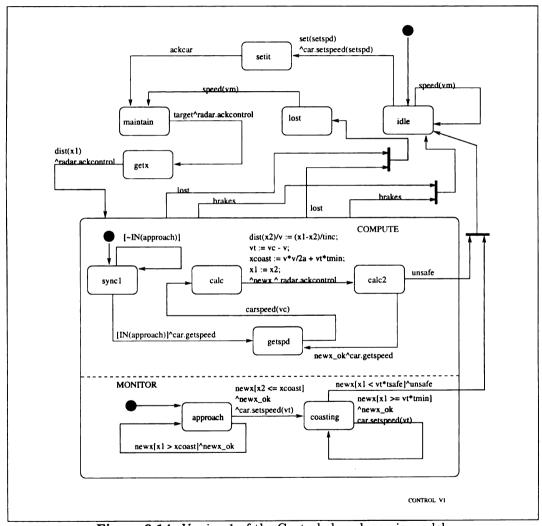

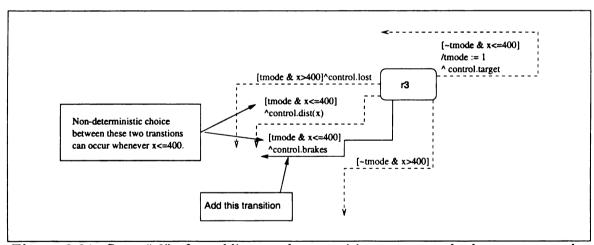

| 9.5.5 | Version 1 Class Control Dynamic Model      | 208 |

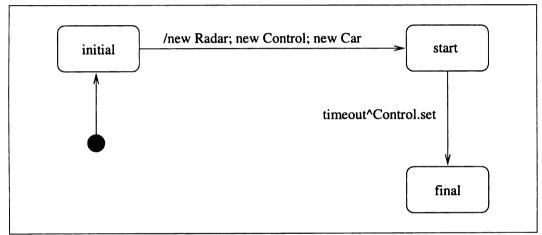

| 9.5.6 | SYSTEM Class                               | 211 |

| 9.6   | Initial Simulation Testing                 | 212 |

| 9.6.1 |                                            | 214 |

| 9.6.2 | ·                                          | 217 |

|       | •                                          | 218 |

| 9.7.1 |                                            | 218 |

| 9.7.2 | •                                          | 220 |

| 9.7.3 |                                            | 221 |

| 9.7.4 |                                            | 224 |

| 9.7.5 | ·                                          |     |

|       | •                                          | 225 |

| 9.7.6 |                                            | 228 |

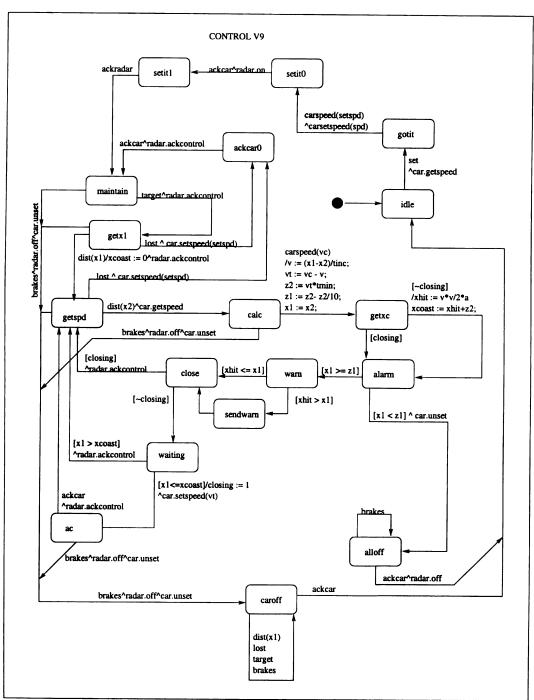

| 9.7.7 | <b>4 V</b>                                 | 232 |

| 9.7.8 | · ·                                        | 235 |

|       | •                                          | 239 |

| 9.8.1 | Bugs                                       | 239 |

9.8.2 Ch 9.8.3 Lac 9.8.4 Ne

10 Concl 10.1 Sum 10.2 Futu

A VHD

B Hydr

C Prom

D Yacc

E UML

F UML

G VHD

H SPIN

| 9.8.2 Challenges                                       | 240 |

|--------------------------------------------------------|-----|

| 9.8.3 Lack of Fairness                                 |     |

| 9.8.4 Never Claims                                     |     |

| 10 Conclusions and Future Investigations               | 244 |

| 10.1 Summary of Contributions                          |     |

| 10.2 Future Research                                   |     |

|                                                        |     |

| A VHDL for Furnace Example                             | 257 |

| B Hydra Language Input for the Smart Cruise Case Study | 265 |

| C Promela Specifications for Smart Cruise              | 270 |

| D Yacc Grammar for the Hydra Language                  | 279 |

| E UML to VHDL Mapping Rules                            | 282 |

| F UML to Promela Mapping Rules                         | 293 |

| G VHDL LCS Files                                       | 307 |

| H SPIN LCS Files                                       | 331 |

.]

2.1 Stat 2.2 An -2.3 Met 2.4 A V

2.5 VH 2.6 Pro 2.7 Fras

3.1 Bou3.2 Met3.3 The

3.4 Exa 3.5 A s 3.6 Exa 3.7 Exa 3.8 The

3.9 Agg 3.10 UM 3.11 The

4.1 Des 4.2 San 4.3 Sys 4.4 San

5.1 Uni 5.2 The

5.3 The

5.4 Met 5.5 The

5.6 The

5.7 The

#### LIST OF FIGURES

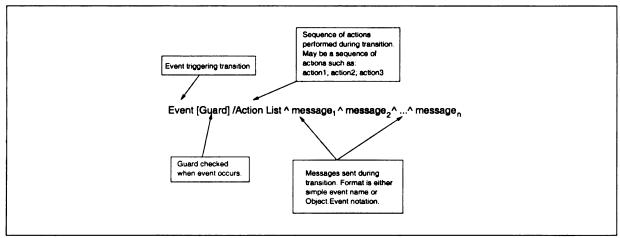

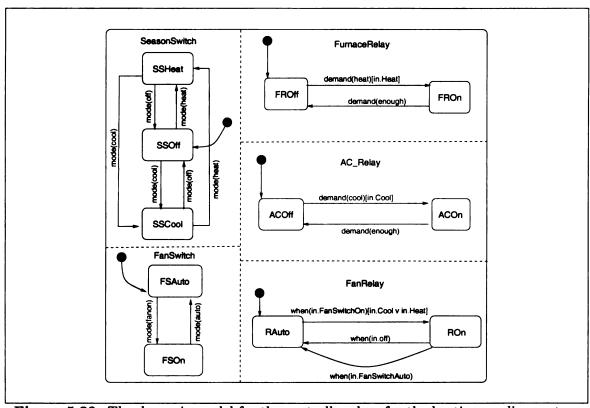

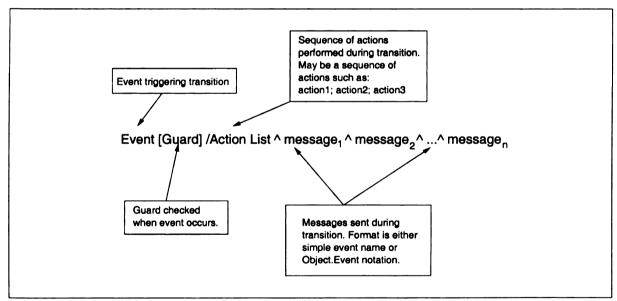

| 2.1         | State transition event syntax conventions                                                             | 11 |

|-------------|-------------------------------------------------------------------------------------------------------|----|

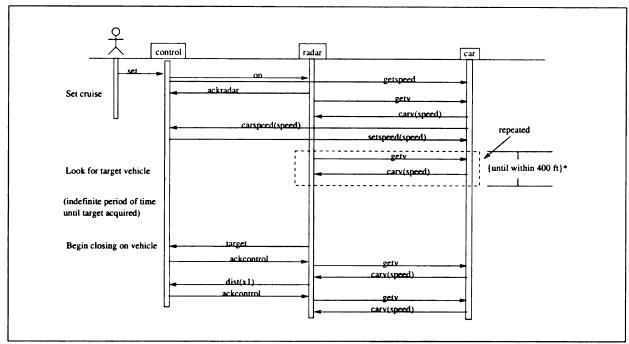

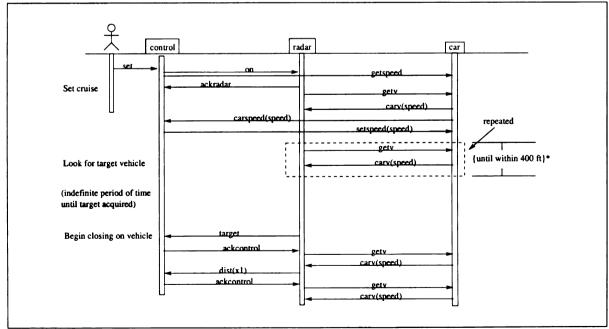

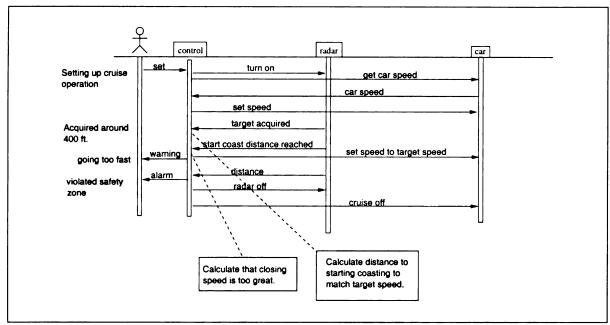

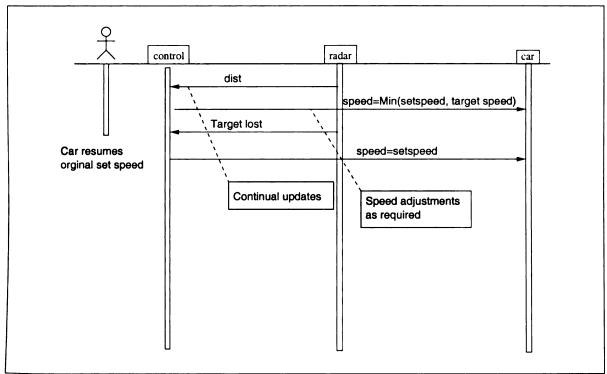

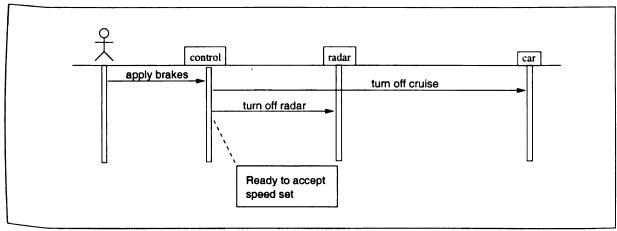

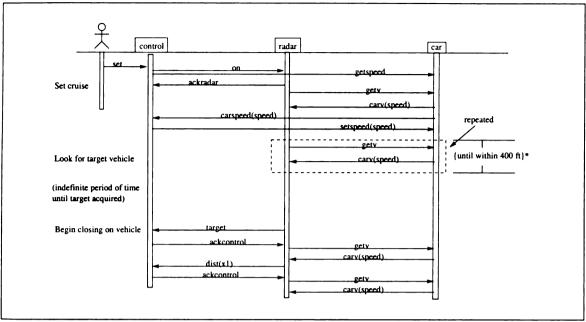

| 2.2         | An example of a sequence diagram                                                                      | 12 |

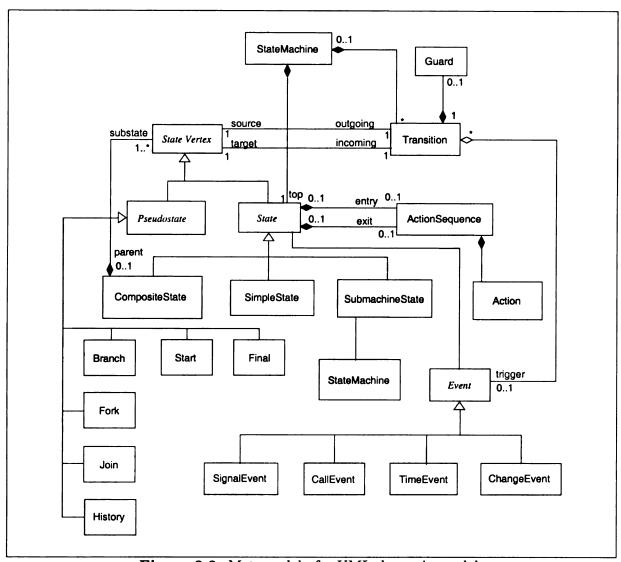

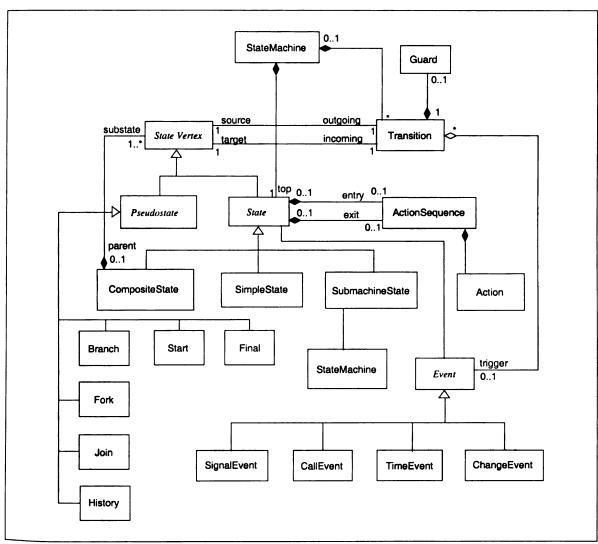

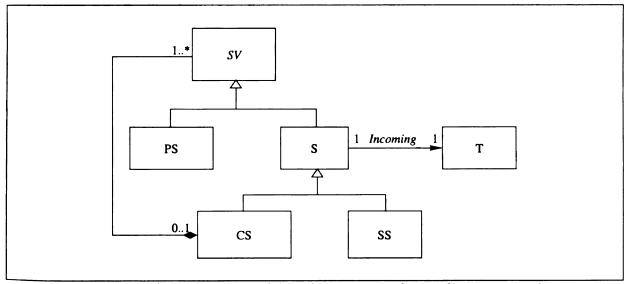

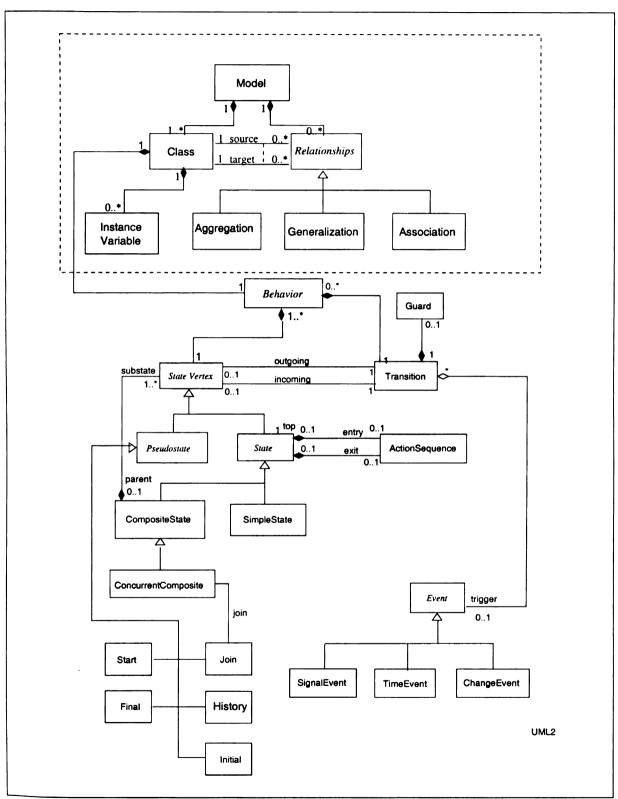

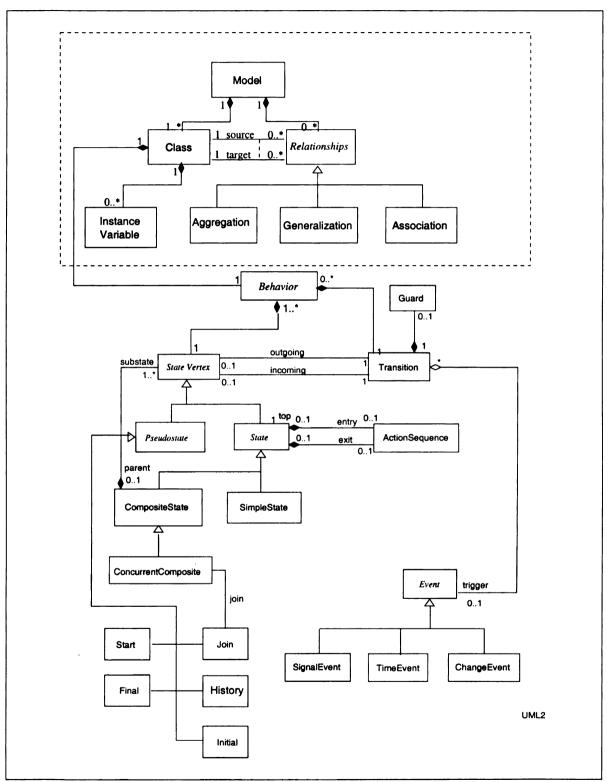

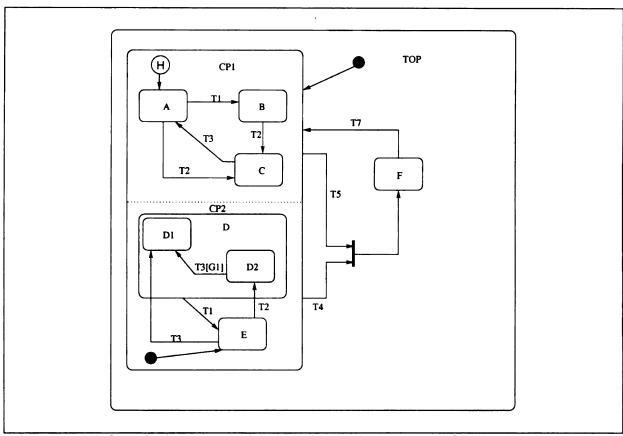

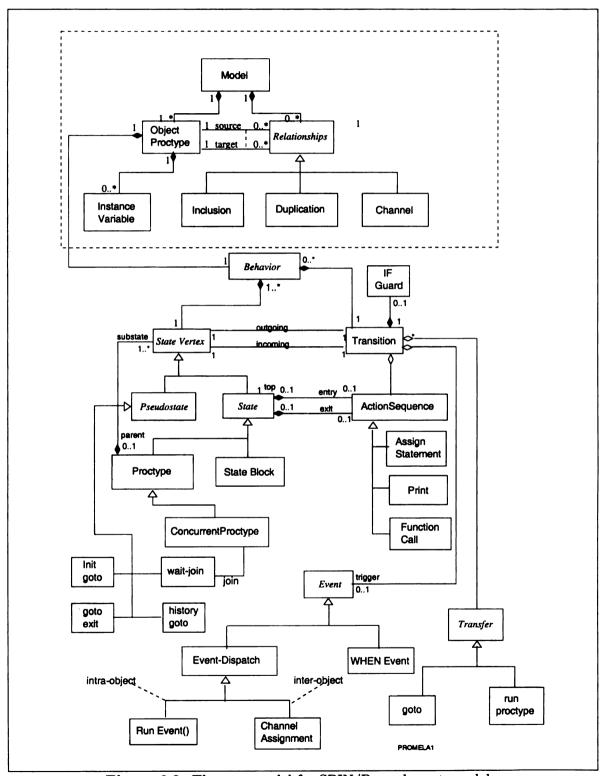

| 2.3         | Metamodel of a UML dynamic model                                                                      | 13 |

| 2.4         | A VHDL entity specification for a simple state machine implementation of por-                         |    |

|             | tion of a CD player                                                                                   | 16 |

| 2.5         | VHDL specification for a simple state machine implementing a CD Player                                | 17 |

| 2.6         | Promela model for a simple client-server system                                                       | 24 |

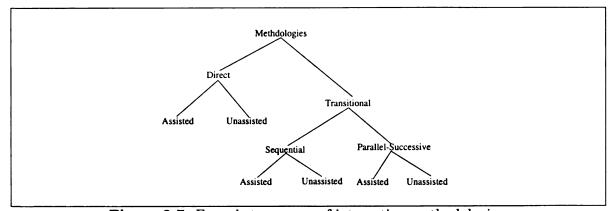

| 2.7         | Fraser's taxonomy of integration methodologies                                                        | 31 |

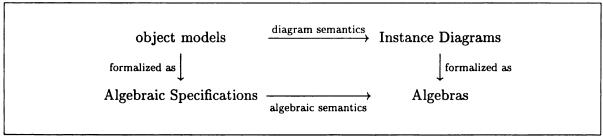

| 3.1         | Bourdeau and Cheng's basic approach to formalization.                                                 | 33 |

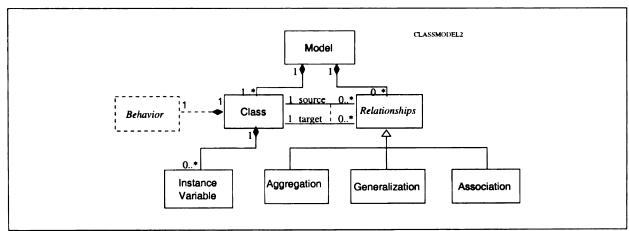

| 3.2         | Metamodel of a UML dynamic model                                                                      | 36 |

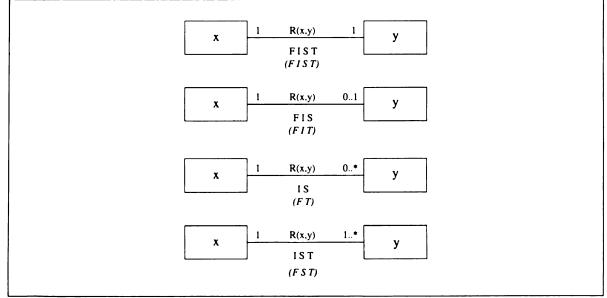

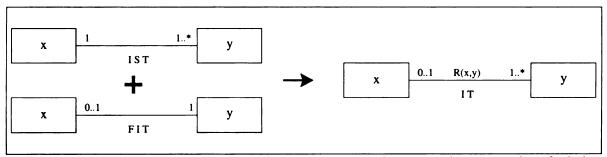

| 3.3         | The four basis relations from which all other association relationships can be formed.                | 38 |

| 3.4         | Example showing how multiplicities 01 and 1* are decomposed to find the set                           | JC |

| J.4         | of constraints for an association                                                                     | 39 |

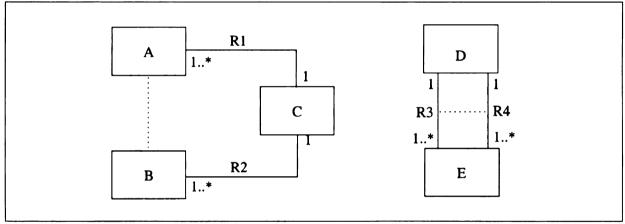

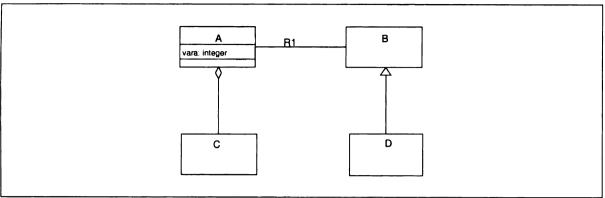

| 3.5         | A small metamodel to demonstrate the predicate constraints                                            | 40 |

| 3.6         | Example of dependencies between classes and associations.                                             | 42 |

| 3.7         | Example of an ambiguous section of a UML diagram                                                      | 44 |

| 3.8         | The relationship between the semi-formal source language, the formal target                           |    |

| <b>U</b> .U | language, the homomorphic binding and the instance-specific mapping rules.                            | 46 |

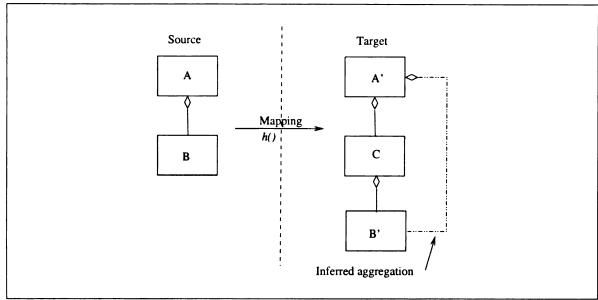

| 3.9         | Aggregations between $A'$ and $B'$ are inferred                                                       | 49 |

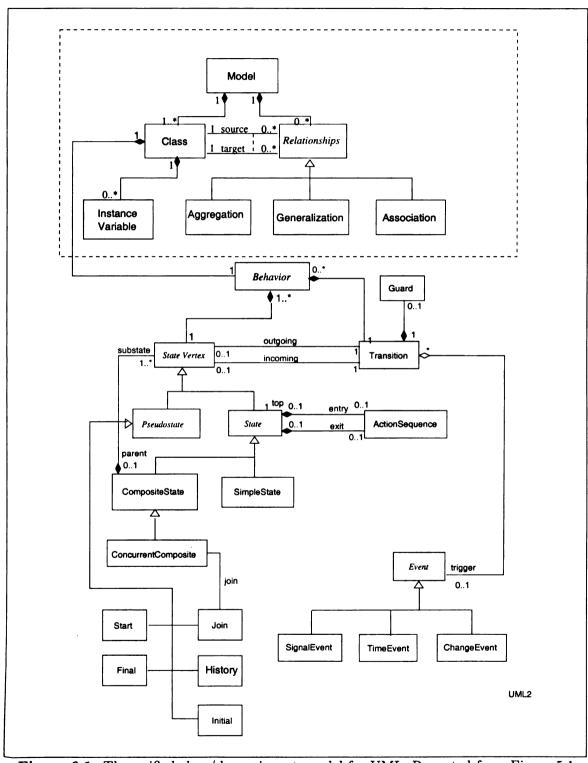

| 3.10        |                                                                                                       | 51 |

| 3.11        | The unified class/dynamic UML metamodel                                                               | 52 |

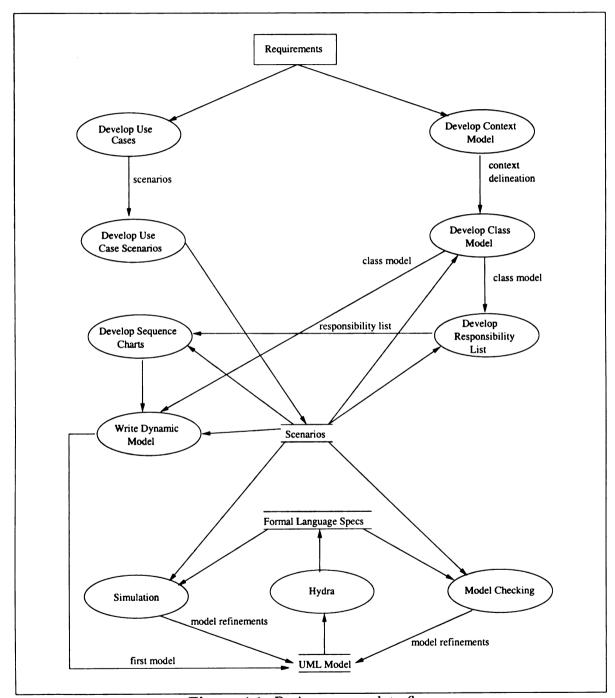

| 4.1         | Design process data flow                                                                              | 55 |

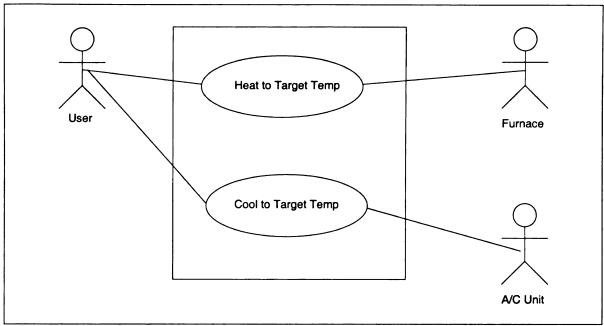

| 4.2         | Sample use case for a heating and cooling system.                                                     | 56 |

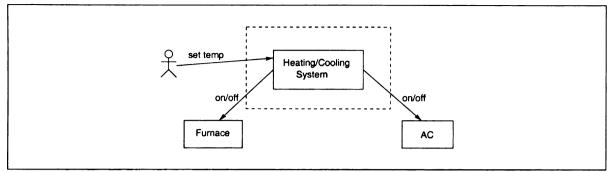

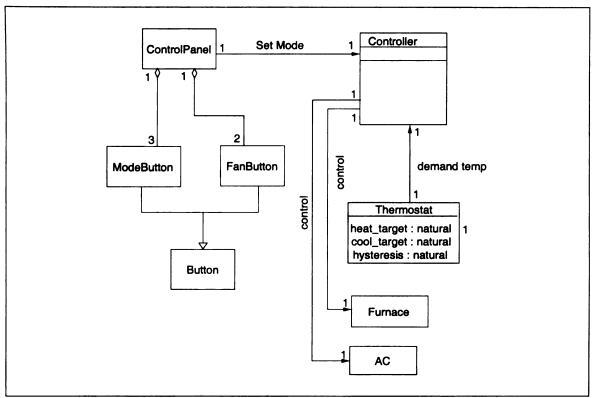

| 4.3         | System Context Model for a hypothetical heating/cooling system                                        | 57 |

| 4.4         | Sample sequence diagram                                                                               | 59 |

| 5.1         | Unified UML class/dynamic diagram metamodel                                                           | 65 |

| 5.2         | The list of non-aggregate and non-generalization relationship predicates from                         |    |

|             | the formalized representation of the UML metamodel                                                    | 66 |

| 5.3         | The list aggregation relationships predicates from the formalized representation of the UML metamodel | 67 |

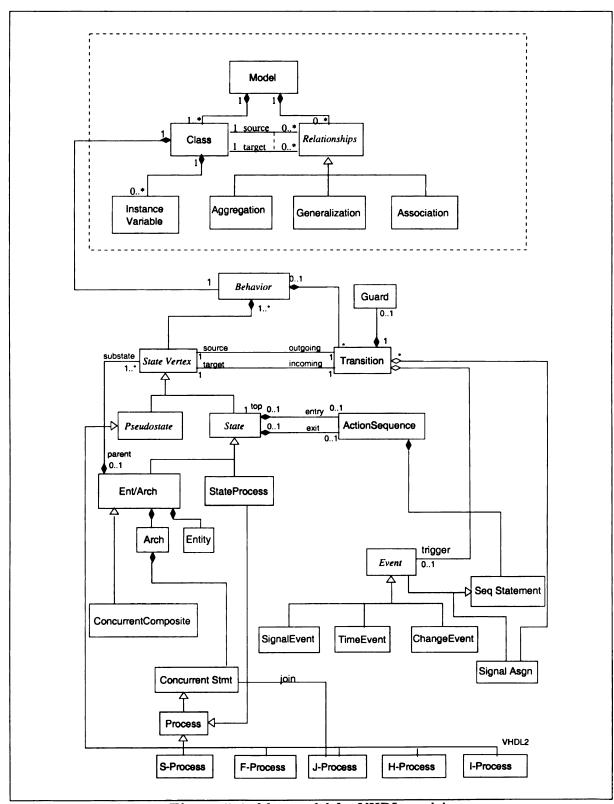

| 5.4         | Metamodel for VHDL models                                                                             | 68 |

| 5.5         | The definition of the homomorphic mapping of classes from the UML metamodel to the VHDL metamodel     | 69 |

| 5.6         | The definition of the homomorphic mapping of relationship predicates from the                         | US |

| J. <b>U</b> | UML metamodel to the VHDL metamodel                                                                   | 69 |

| 5.7         | The preserved hasComp and hasPart relationship predicates                                             | 70 |

5.8 Sa 5.9 Th 5.10 Er 5.11 VI 5.12 Sa 5.13 Ex 5.14 Ex 5.15 Th

5.16 T

5.17 E: 5.18 E:

5.19 T 5.20 T 5.21 T

5.22 T

5.23 O 5.24 E

5.25 S

6.1 T 6.2 T 6.3 T

6.4 T

6.5 T

6.6 Т

6.7 T 6.8 S 6.9 P 6.10 A 6.11 T

6.12 F

6.13 P

6.14 P

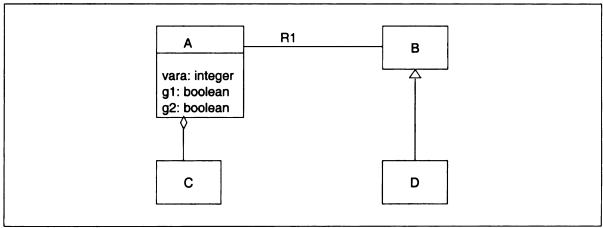

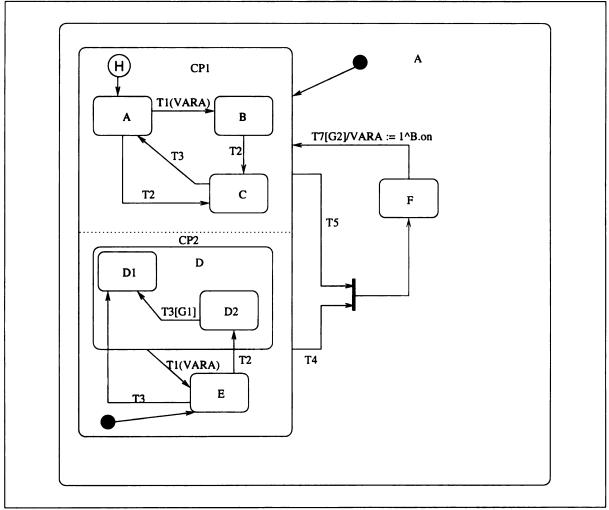

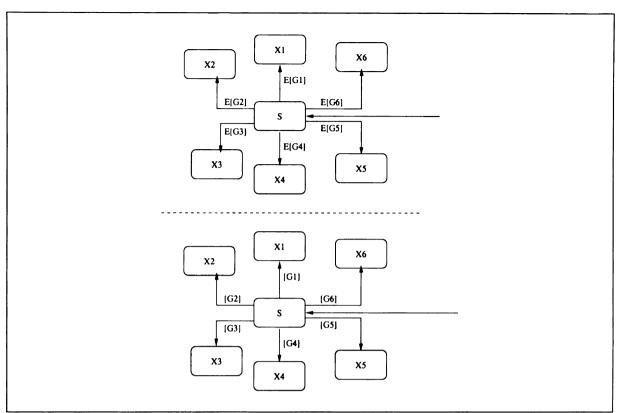

| Sample class model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The VHDL package statements generated for each class                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

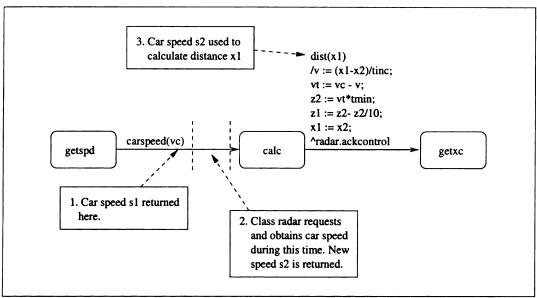

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |