# HARDWARE ALGORITHMS FOR HIGH-SPEED PACKET PROCESSING

By

Eric Norige

#### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

Computer Science — Doctor of Philosophy

2017

#### ABSTRACT

#### HARDWARE ALGORITHMS FOR HIGH-SPEED PACKET PROCESSING

By

#### Eric Norige

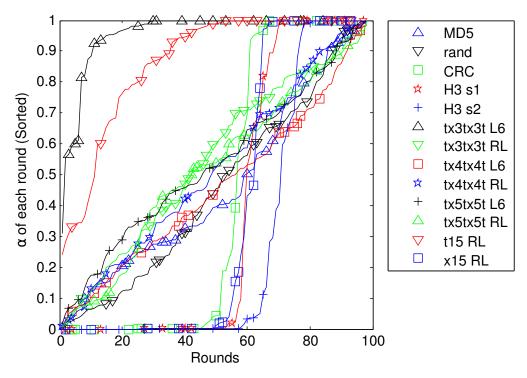

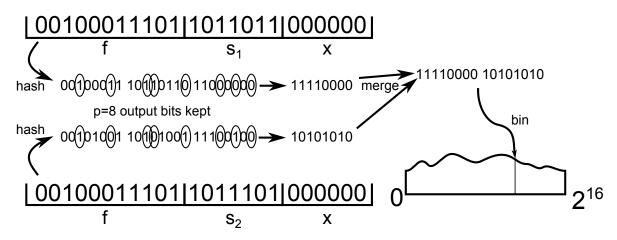

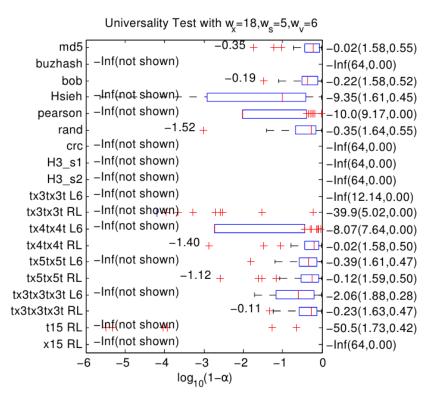

The networking industry is facing enormous challenges of scaling devices to support the exponential growth of internet traffic as well as increasing number of features being implemented inside the network. Algorithmic hardware improvements to networking components have largely been neglected due to the ease of leveraging increased clock frequency and compute power and the risks of implementing complex hardware designs. As clock frequency slows its growth, algorithmic solutions become important to fill the gap between current generation capability and next generation requirements. This paper presents algorithmic solutions to networking problems in three domains: Deep Packet Inspection (DPI), firewall ruleset compression and non-cryptographic hashing. The improvements in DPI are twopronged: first in the area of application-level protocol field extraction, which allows security devices to precisely identify packet fields for targeted validity checks. By using counting automata, we achieve precise parsing of non-regular protocols with small, constant per-flow memory requirements, extracting at rates of up to 30 Gbps on real traffic in software while using only 112 bytes of state per flow. The second DPI improvement is on the long standing regular expression matching problem, where we complete the HFA solution to the DFA state explosion problem with efficient construction algorithms and optimized memory layout for hardware or software implementation. These methods construct automata too complex to be constructed by previous methods in seconds, while being capable of 29 Gbps throughput with an ASIC implementation. Firewall ruleset compression enables more firewall entries to be stored in a fixed capacity pattern matching engine, and can also be used to reorganize a firewall specification for higher performance software matching. A novel recursive structure called TUF is given to unify the best known solutions to this problem and suggest future avenues of attack. These algorithms, with little tuning, achieve a 13.7% improvement in compression on large, real-life classifiers, and can achieve the same results as existing algorithms while running 20 times faster. Finally, non-cryptographic hash functions can be used for anything from hash tables to track network flows to packet sampling for traffic characterization. We give a novel approach to generating hardware hash functions in between the extremes of expensive cryptographic hash functions and low quality linear hash functions. To evaluate these mid-range hash functions properly, we develop new evaluation methods to better distinguish non-cryptographic hash function quality. The hash functions described in this paper achieve low-latency, wide hashing with good avalanche and universality properties at a much lower cost than existing solutions.

#### ACKNOWLEDGMENTS

I would like to thank Chad Meiners and Sailesh Kumar for providing strong shoulders to stand upon.

This work is partially supported by the National Science Foundation under Grant Numbers CNS-0916044, CNS-0845513, CNS-1017588, CCF-1347953, CNS-1318563 and CNS-1017598, and the National Natural Science Foundation of China under Grant Numbers 61272546 and 61370226, and by a research gift from Cisco Systems, Inc..

## TABLE OF CONTENTS

| LIST OF TABLES ix |                      |                                                                                                                             |  |  |  |  |  |

|-------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| LIST C            | F FI                 | ${f GURES}$                                                                                                                 |  |  |  |  |  |

| $\mathbf{Chapte}$ | r 1                  | Introduction                                                                                                                |  |  |  |  |  |

| Chapte            | r 2                  | Protocol Parsing                                                                                                            |  |  |  |  |  |

| 2.1               | Intro                | $duction \dots \dots$ |  |  |  |  |  |

|                   | 2.1.1                | Motivation                                                                                                                  |  |  |  |  |  |

|                   | 2.1.2                | Problem Statement                                                                                                           |  |  |  |  |  |

|                   | 2.1.3                | Limitations of Prior Art                                                                                                    |  |  |  |  |  |

|                   | 2.1.4                | Proposed Approach                                                                                                           |  |  |  |  |  |

|                   | 2.1.5                | Key Contributions                                                                                                           |  |  |  |  |  |

| 2.2               | Relat                | ed Work                                                                                                                     |  |  |  |  |  |

| 2.3               | Proto                | col and Extraction Specifications                                                                                           |  |  |  |  |  |

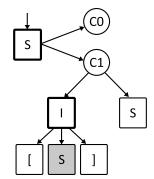

|                   | 2.3.1                | Counting Context Free Grammar                                                                                               |  |  |  |  |  |

|                   | 2.3.2                | Protocol Specification in CCFG                                                                                              |  |  |  |  |  |

|                   | 2.3.3                | Extraction Specification in CCFG                                                                                            |  |  |  |  |  |

| 2.4               | Grammar Optimization |                                                                                                                             |  |  |  |  |  |

|                   | 2.4.1                | Counting Regular Grammar                                                                                                    |  |  |  |  |  |

|                   | 2.4.2                | Normal Nonterminal Identification                                                                                           |  |  |  |  |  |

|                   | 2.4.3                | Normal Nonterminal Regularization                                                                                           |  |  |  |  |  |

|                   | 2.4.4                | Counting Approximation                                                                                                      |  |  |  |  |  |

|                   | 2.4.5                | Idle Rule Elimination                                                                                                       |  |  |  |  |  |

| 2.5               | Auto                 | mated Counting Automaton Generation                                                                                         |  |  |  |  |  |

|                   | 2.5.1                | Counting Automata                                                                                                           |  |  |  |  |  |

|                   | 2.5.2                | LPDFA                                                                                                                       |  |  |  |  |  |

|                   | 2.5.3                | CA Specific Optimizations                                                                                                   |  |  |  |  |  |

| 2.6               | Coun                 | ting Automaton Implementation                                                                                               |  |  |  |  |  |

|                   | 2.6.1                | Incremental Packet Processing                                                                                               |  |  |  |  |  |

|                   | 2.6.2                | Simulated CA                                                                                                                |  |  |  |  |  |

|                   | 2.6.3                | Compiled CA                                                                                                                 |  |  |  |  |  |

| 2.7               | Extra                | ction Generator                                                                                                             |  |  |  |  |  |

| 2.8               |                      | rimental Results                                                                                                            |  |  |  |  |  |

|                   | 2.8.1                | Methods                                                                                                                     |  |  |  |  |  |

|                   |                      | 2.8.1.1 Traces                                                                                                              |  |  |  |  |  |

|                   |                      | 2.8.1.2 Field Extractors                                                                                                    |  |  |  |  |  |

|                   |                      | 2.8.1.3 Metrics                                                                                                             |  |  |  |  |  |

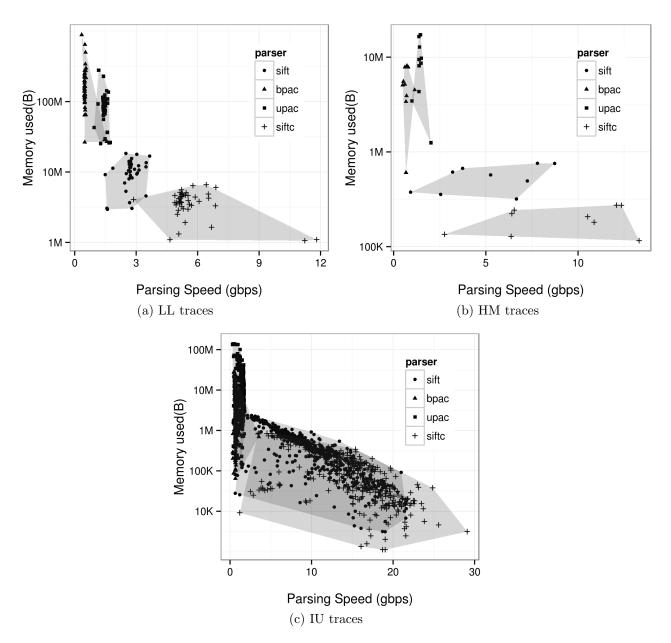

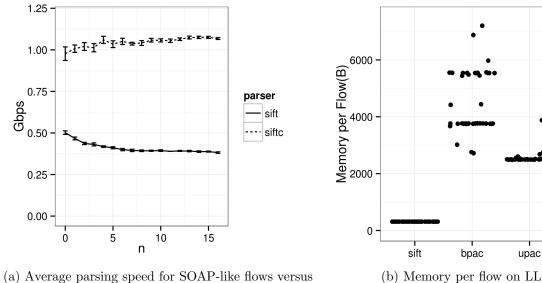

|                   | 2.8.2                | Experimental Results                                                                                                        |  |  |  |  |  |

|                   | J · <b>-</b>         | 2.8.2.1 Parsing Speed                                                                                                       |  |  |  |  |  |

|                   |                      | 2.8.2.2 Memory Use                                                                                                          |  |  |  |  |  |

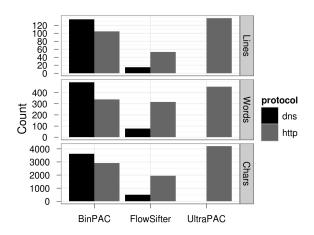

|        |        | 2.8.2.3 Parser Definition Complexity |

|--------|--------|--------------------------------------|

| 2.9    | Conclu | asions                               |

| Chapte | er 3   | Regex Matching                       |

| 3.1    |        | uction                               |

|        | 3.1.1  | Motivation                           |

|        | 3.1.2  | Limitations of Prior Art             |

|        | 3.1.3  | Proposed Approach                    |

|        | 3.1.4  | Challenges and Proposed Solutions    |

|        | 3.1.5  | Key Novelty and Contributions        |

| 3.2    |        | ed Work                              |

| 3.3    |        | natic HFA Construction               |

| 0.0    | 3.3.1  | Basic Construction Method            |

|        | 3.3.2  | Bit State Selection                  |

|        | 3.3.3  | HFA Construction without DFA         |

|        | 3.3.4  | Transition Table Optimization        |

| 3.4    |        | IFA Construction                     |

|        | 3.4.1  | Observation and Basic Ideas          |

|        | 3.4.2  | Bit State Pruning                    |

|        | 3.4.3  | Mixin Table Generation               |

|        | 3.4.4  | HFA Transition Table Generation      |

|        | 3.4.5  | Correctness of Fast HFA Construction |

| 3.5    | Fast P | Packet Processing                    |

|        | 3.5.1  | Design Considerations                |

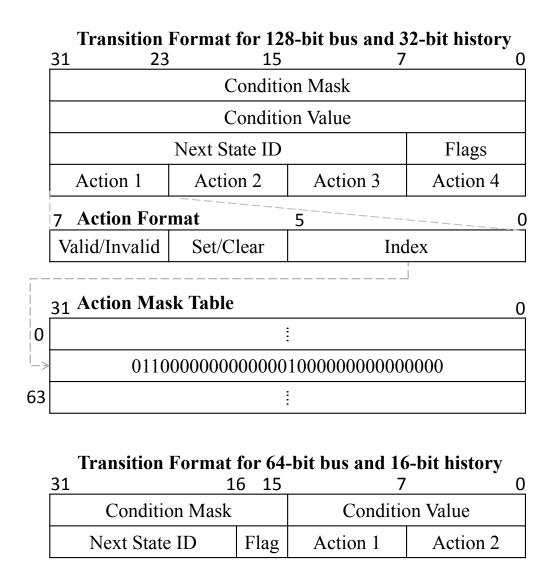

|        | 3.5.2  | Transition Format                    |

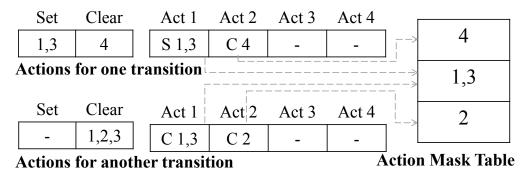

|        | 3.5.3  | Action Compression Algorithm         |

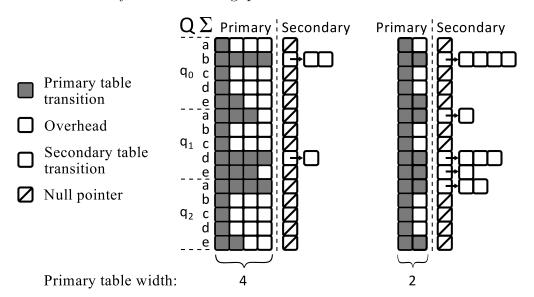

|        | 3.5.4  | Transition Table Image Construction  |

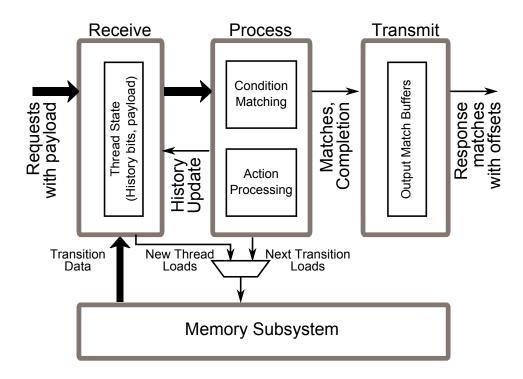

| 3.6    | Hardw  | vare Design                          |

| 3.7    | Exper  | imental Results                      |

|        | 3.7.1  | Data Set                             |

|        | 3.7.2  | Metrics & Experimental Setup         |

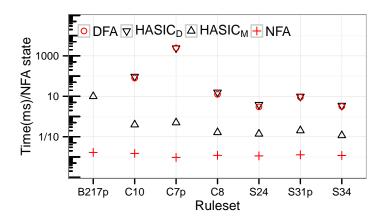

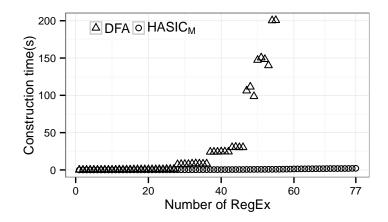

|        | 3.7.3  | Automaton Construction: Time & Size  |

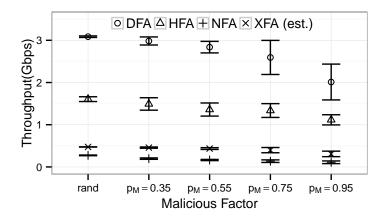

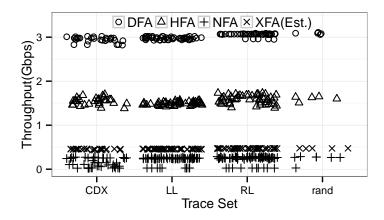

|        | 3.7.4  | Packet Processing Throughput         |

| 3.8    | Conclu | asions                               |

| Chapte | er 4   | Firewall Compression                 |

| 4.1    |        | uction                               |

|        | 4.1.1  | Background and Motivation            |

|        | 4.1.2  | Problem Statement                    |

|        | 4.1.3  | Limitations of Prior Art             |

|        | 4.1.4  | Proposed Approach                    |

|        | 4.1.5  | Key Contributions                    |

| 4.2    |        | ed Work                              |

| 4.3    |        | Framework                            |

|        | 431    | TIIF Outline 106                     |

| ΡI  | TTTT        | PENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1 <i>7</i> 6 |  |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|

|     | 5.6         | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 173          |  |

|     | 5.5         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 173          |  |

|     | 5 5         | y .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |  |

|     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 169          |  |

|     |             | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 161          |  |

|     |             | <u>*</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 161          |  |

|     | 0.4         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 160          |  |

|     | 5.4         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 150<br>159   |  |

|     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 150          |  |

|     |             | O Company of the comp | 154 $156$    |  |

|     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 153<br>154   |  |

|     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $150 \\ 153$ |  |

|     | 0.0         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 150          |  |

|     | 5.3         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 150          |  |

|     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 148          |  |

|     |             | 71.01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 140 $147$    |  |

|     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 146          |  |

|     | J.∠         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 140<br>146   |  |

|     | 5.2         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 143<br>146   |  |

|     | 0.1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 142          |  |

| UI. | apte<br>5.1 | G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 142          |  |

| CI  | anta        | or 5 Hashing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 142          |  |

|     | 4.11        | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 141          |  |

|     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 138          |  |

|     | 1.10        | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 136          |  |

|     |             | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 135          |  |

|     |             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 132          |  |

|     |             | v 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 132          |  |

|     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 130          |  |

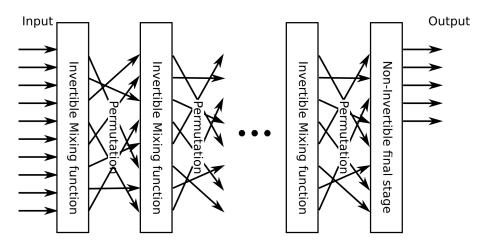

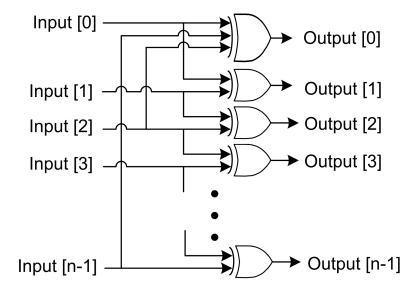

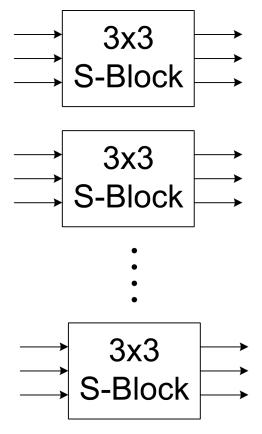

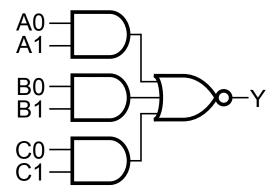

|     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 128          |  |