## MULTI-BAND RECONFIGURABLE RFICS IN SI-BASED TECHNOLOGIES FOR A COMPACT AND ADAPTIVE RF FRONT-END

By

Asad Ali Nawaz

## A DISSERTATION

Submitted to Michigan State University in partial fulfillment of the requirements for the degree of

Electrical Engineering — Doctor of Philosophy

2020

## ABSTRACT

## MULTI-BAND RECONFIGURABLE RFICS IN SI-BASED TECHNOLOGIES FOR A COMPACT AND ADAPTIVE RF FRONT-END

#### By

#### Asad Ali Nawaz

Recent advances in the wireless communication market have led to the coexistence of several networks such as cellular network, personal area network (PAN), wireless local area network (WLAN), etc. along with several different air interfaces (802.11a, 802.11g, Bluetooth, wireless code division multiple access (WCDMA), etc.). Thus, all the wireless devices need to be compatible with the different communication standards while still keeping similar performance, smaller die area and lower power consumption. The need to enable the "global roaming" capability between a wide variety of networks operating at different frequencies calls for the development of reconfigurable radio-frequency integrated circuits (RFICs) which can achieve maximum hardware sharing between different standards and across various functions. The objective of this dissertation is to present novel topologies for RF components and blocks that can yield a Si-based frequency-agile RF front-end. The targeted applications for this work are 5G multi-band wireless communication and reconfigurable short/long range phased arrays for automobile radars. However, the concept of the proposed reconfigurable RF elements is generic in nature and can be applied to all emerging applications which require on-chip reconfigurability at microwave and mm-wave frequencies.

To demonstrate the concept of a reconfigurable RF front end, a Ka/V band-switchable TRX amplifier is developed in 0.13um BiCMOS SiGe process and a 18-50 GHz receiver is developed in 45nm SOI CMOS process. Unlike the traditional approach for a multi-band radio – where the dedicated single band transceivers composed of fixed RF components are designed and

multiplexed with the help of switches – the proposed idea utilizes the switches inside each RF block; thus, adding the reconfigurability inside each block and eliminating the need for separate front-ends. However, the catch in the latter approach is to maintain the RF performance while still being able to save the real-estate and power consumption. The proposed Ka/V band-switchable TRX amplifier consists of a band-switchable LNA, a band-switchable PA, and integrated T/R switches which saves a lot of area. The band-switch functionality is realized using thin-film microstrip based shunt stubs with reverse saturated SiGe switches. Design techniques for switch loss reduction and size miniaturizations are presented. This work illustrates that with the optimization of switch loss, appropriate selection of each block between wideband or bandswitching topology and co-design of RF blocks, a highly integrated multi-band transceiver can be designed with the minimal degradation to the RF performance compared to state-of-the-art dedicated single band transceivers. To further explore reconfigurable transceivers, a direct quadrature down-conversion mixer first receiver with active channel select filters has been designed. The receiver supports 200MHz instantaneous RF bandwidth and can be reconfigured to receive any 200 MHz channel within 18-50 GHz frequency range. With the ever-evolving wireless standards like 4G/5G/6G, equipment manufacturers are required to add more functionality into the chips while still maintaining the backward compatibility with previous standards or fallback option to lower frequency bands. A low power, highly integrated, multi-band and multi-standard chipset has thus become a requisite in commercial products. The proposed concept of in-block reconfigurability and the presented design techniques to realize mm-wave frequency reconfigurable transceivers have a huge potential in this regard.

## ACKNOWLEDGEMENTS

I am most indebted to my parents, Samina and Nawaz, who not only just supported me throughout this intellectual journey but also instilled in me a sense of rightness, a sense of purpose, and a sense of greater good. This would never have been possible without their prayers and blessings of Almighty Allah.

I am thankful to my undergrad advisor, Dr. Inam Elahi Rana, for introducing me to the microwave circuit design and inspiring me to pursue this path. I am extremely thankful to my advisor, Dr. Ahmet Cagri Ulusoy. If I know anything about IC design today, I owe it to him. He took me in his group despite my rudimentary knowledge of circuits and absolutely no experience in IC design. He would come to lab, sit down with me and allow me to ask anything about the subject no matter how basic or foolish questions I had. We did a lot of tape-outs and some did not work as expected. He was never harsh on me and always encouraged me to look at the bright side and to learn from my mistakes. He made me capable of carrying out research independently. I would also like to thank Dr. John Albrecht. Had he not been there, my admission to MSU would not have been possible. When all the doors at MSU closed at me, he opened one. He put me in contact with Dr. Ulusoy and arranged everything for me. He has also been a great support to me after Dr. Ulusoy left MSU. I found him as a person who would go an extra mile to help. I would also like to thank my committee members (Dr. Sangmin Yoo, Dr. Yuying Xie and Dr. John Papapolymerou) for guiding me throughout my PhD.

I am also grateful to my friends at MSU. I am fortunate to have met with wonderful colleagues: Siwook, Ibrahim, Shih-Chang, Jubaid, Xenophon and Adamantia. There have been times when I was happy and there have been times when I was sad. Siwook and Ibrahim always

stood by me. We have shared countless discussions over the cup of coffee and made gigabytes of cherish-able memories. I have also learnt a lot about IC design from Siwook and he has helped me many times in debugging a circuit. I am also thankful to my Pakistani friends at MSU. They saved me from getting bored when I was not busy at work. They helped me in getting adjusted at MSU and were always there when needed.

Last but not the least, I am extremely grateful to my wife, Sidra. I have spent innumerable weekends and pulled a couple all-nighters at lab. She has been very patient and given me all the time I needed to finish this thesis. She has been with me through thick and thin and inspired me in many ways. I would not be where I am today if it was not for your support, Sidra.

# **TABLE OF CONTENTS**

| LIST OF TABLES                                                   | viii          |

|------------------------------------------------------------------|---------------|

| LIST OF FIGURES                                                  | ix            |

| KEY TO ABBREVIATIONS                                             | xiii          |

| 1 INTRODUCTION                                                   |               |

| 1.1 Wireless Communication and Frequency Bands                   |               |

| 1.2 Motivation for Multi-Band Radio                              |               |

| 1.3 Challenges in Milli-meter Wave Multi-Band Radio              |               |

| 1.4 Existing Techniques for Multi-Band Radios                    |               |

| 1.5 Objective and Organization of the Dissertation               |               |

| 2 HARMONIC TUNING OF STACKED POWER AMPLIFIERS                    | 9             |

| 2.1 Introduction                                                 | 9             |

| 2.2 Theory                                                       | 10            |

| 2.2.1 When the base is shorted                                   | 10            |

| 2.2.2 When the base is open                                      |               |

| 2.3 Design of Power Amplifiers Core                              | 14            |

| 2.4 Measurements                                                 | 14            |

| 2.5 Conclusion                                                   | 15            |

| 3 A KA-BAND POWER AMPLIFIER WITH RECONFIGUR-A                    | BLE IMPEDANCE |

| MATCHING NETWORK                                                 |               |

| 3.1 Scan Impedance Variation in Phased Arrays                    | 17            |

| 3.2 Reconfigurable Impedance Matching Network for Phased Arrays  |               |

| 3.3 Design of Ka-Band PA                                         | 19            |

| 3.4 Design of Reconfigurable Impedance Matching Network          |               |

| 3.4.1 Switch Loss Optimization                                   | 20            |

| 3.4.2 Shunt Stub Loss Reduction Technique (Theoretical Analysis) | )22           |

| 3.4.3 Shunt Stub Loss Reduction Technique (Intuitive Analysis)   | 25            |

| 3.5 Complete Schematic                                           | 26            |

| 3.6 Measured Results                                             | 27            |

| 3.7 Summary                                                      |               |

| 4 A COMPACT KA/V BAND-SWITCHABLE TRX AMPLIFIER WITH              |               |

| SWITCHES                                                         |               |

| 4.1 Ka/V Band-Switchable PA                                      |               |

| 4.1.1 Amplifier Design                                           |               |

| 4.1.2 Matching Network Design                                    |               |

| 4.1.3 Switch Design                                              |               |

| 4.1.4 Measured Results                                           |               |

| 4.1.5      | Summary                                                 | 37       |

|------------|---------------------------------------------------------|----------|

| 4.2 Ka/V   | / Band-Switchable LNA                                   | 39       |

| 4.2.1      | Amplifier Design                                        | 39       |

| 4.2.2      | Matching Network Design                                 |          |

| 4.2.3      | Switch Design                                           | 41       |

| 4.2.4      | Measured Results                                        | 42       |

| 4.2.5      | Summary                                                 | 46       |

| 4.3 Ban    | d-Switchable TRX Amplifier with Integrated Switches     | 46       |

| 4.3.1      | T/R Switch                                              | 47       |

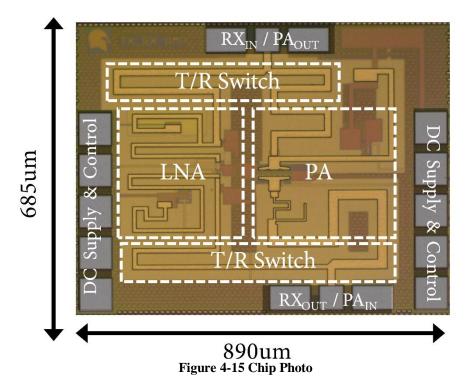

| 4.3.2      | Chip Photo                                              | 49       |

| 4.3.3      | Measurements                                            | 49       |

| 4.4 Con    | clusion                                                 | 55       |

|            |                                                         |          |

| 5 A 18-50  | GHZ RECONFIGURABLE MIXER-FIRST RECEIVE RF FRONT-END     | 56       |

| 5.1 Syst   | em Specifications                                       | 56       |

| 5.2 Syst   | em Design                                               | 57       |

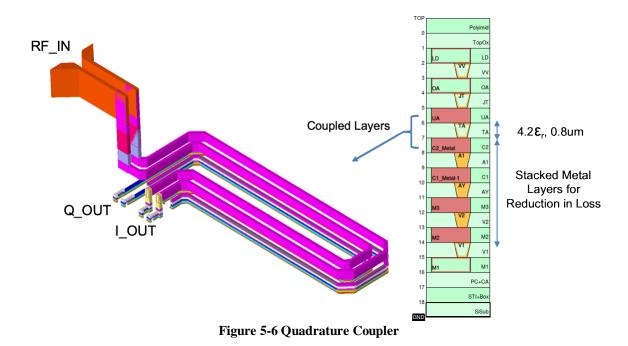

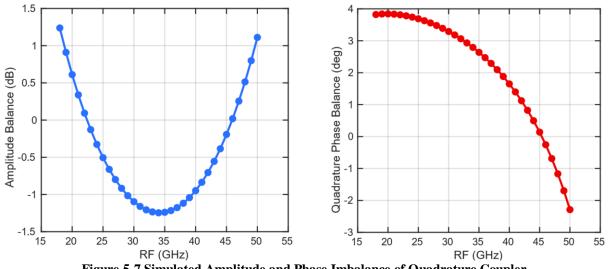

| 5.3 Diff   | erential Quadrature Coupler                             | 62       |

| 5.4 Pass   | ive Mixer                                               | 64       |

| 5.5 LO     | Driver                                                  | 69       |

| 5.6 Base   | band LNA and Filter                                     | 71       |

| 5.6.1      | Flicker Noise Optimization                              | 72       |

| 5.6.2      | Thermal Noise Optimization                              |          |

| 5.6.3      | Positive Feedback Filter                                | 73       |

| 5.6.3.     | 1 Test Case: When $C_F = 0$                             | 75       |

| 5.6.3.     | 2 Test Case: When $C_F \neq 0$ and feedback is negative | 76       |

| 5.6.3.     | Test Case: When $C_F \neq 0$ and feedback is positive   | 76       |

| 5.6.3.     | 4 Digital Control                                       | 77       |

| 5.7 Layo   | out                                                     | 79       |

| 5.8 Sim    | ulated Results                                          | 80       |

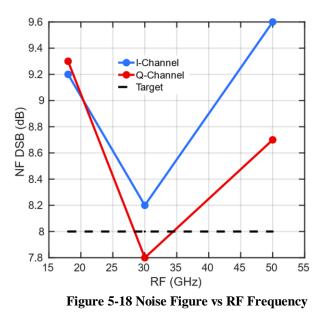

| 5.8.1      | Noise Figure                                            | 80       |

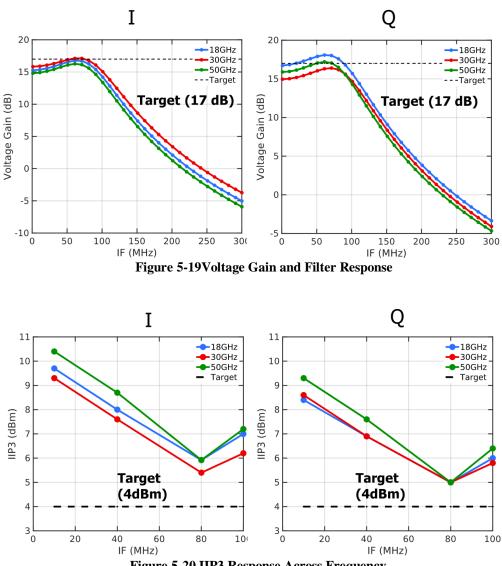

| 5.8.2      | Gain and Filter Response                                | 80       |

| 5.8.3      | IIP3                                                    | 81       |

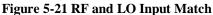

| 5.8.4      | DC Power                                                | 82       |

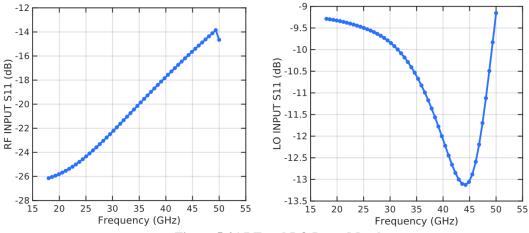

| 5.8.5      | RF and LO Input Return Loss                             | 82       |

| 5.9 Sum    | mary                                                    | 83       |

|            |                                                         | <u> </u> |

| 6 CONCL    | USION                                                   | 84       |

| BIBLIOGR A | РНҮ                                                     | 86       |

|            |                                                         |          |

# LIST OF TABLES

| Table 2-1 Comparison of PAE and Pout by Harmonic Tuning              |    |

|----------------------------------------------------------------------|----|

| Table 4-1 State-of-the-art Single Band, Multi-Band and Wideband PAs  | 38 |

| Table 4-2 State-of-the-art Single Band, Multi-Band and Wideband LNAs | 45 |

| Table 4-3 Performance Summary and State of the Art                   | 54 |

| Table 5-1 Specifications of Required 18-50 GHz RX                    | 56 |

# **LIST OF FIGURES**

| Figure 1-1 Wireless Technologies and Applications in Operation                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2 Emerging Wireless Application Requiring RF Hardware Reconfigurability3                                                                                           |

| Figure 1-3 Frequency Bands Required by A Multi-band Cellphone to be Compatible with all the Generations of Cellular Network (1G-5G)                                         |

| Figure 2-1 Y-parameter analysis of transistor with base and collector termination10                                                                                         |

| Figure 2-2 Designed X-Band power amplifiers: a) Cascode, b) Tri-stacked, c) Quad-stacked, d) Fabricated chip                                                                |

| Figure 2-3 Variation of $Z_{in1}$ , $Z_{in2}$ , and $Z_{in3}$ when $Z_L$ is varied from short to open13                                                                     |

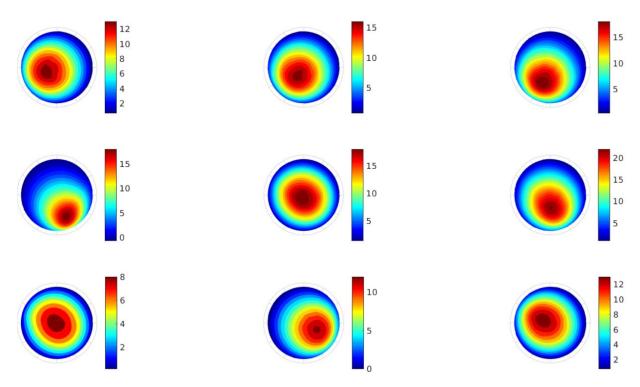

| Figure 2-4 Measured PAE (%) contours for 2nd harmonic (top) and 3rd harmonic (bottom) impedance sweep: a) Cascode, b) Tri-stacked, c) Quad-stacked16                        |

| Figure 2-5 Measured fundamental output power (dBm) contours for 2nd harmonic (top) and 3rd harmonic (bottom) impedance sweep: a) Cascode, b) Tri-stacked, c) Quad-stacked16 |

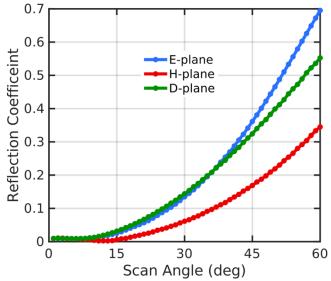

| Figure 3-1 Variation in Reflection Co-efficient wrt Scan Angle in Dipole Array at 28 GHz18                                                                                  |

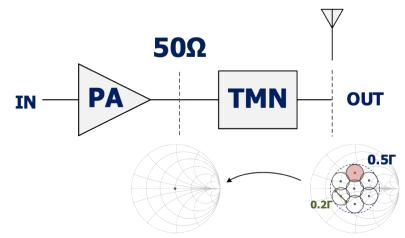

| Figure 3-2 Block Diagram of the Proposed System18                                                                                                                           |

| Figure 3-3 Schematic of the K-Band PA19                                                                                                                                     |

| Figure 3-4 Double Stub Reconfigurable Matching Network                                                                                                                      |

| Figure 3-5 (a) Switch Loss against Switch size (Width), (b) P1dB of the Switch in OFF State against Reverse Bias Voltage                                                    |

| Figure 3-6 Quality factor of shunt stub: (a) against electrical length of lossless stubError! Bookmark not defined.                                                         |

| Figure 3-7 Explanation of Shunt Stub Characteristic Impedance Effect on Matching with and Without Lossy Termination                                                         |

| Figure 3-8 Stub Characteristic Impedance Showing Different Sweet Spots for Different Switch Widths (or Resistances)                                                         |

| Figure 3-9 Complete Schematic                                                                                        |

|----------------------------------------------------------------------------------------------------------------------|

| Figure 3-10 Chip Photo                                                                                               |

| Figure 3-11 Measured and Simulated TMN Impedance Points for All Switch States27                                      |

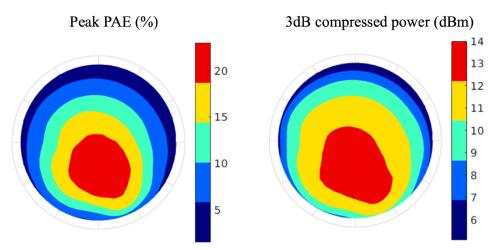

| Figure 3-12 Measured 3dB Compressed Power (dBm) Contours for All Switch States                                       |

| Figure 3-13 Measured Peak PAE (%) Contours for All Switch States                                                     |

| Figure 3-14 Combined Contours of Peak PAE and 3dB Compressed Output Power from Each<br>Switch State                  |

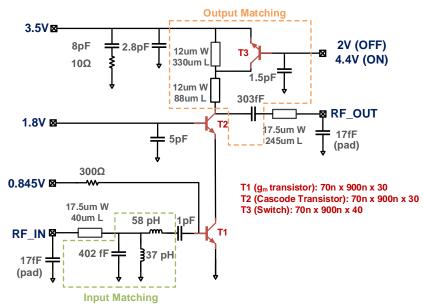

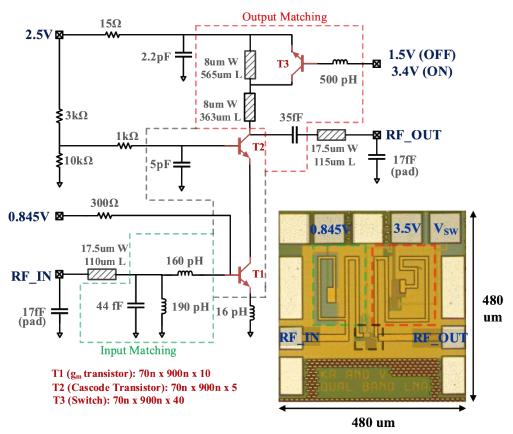

| Figure 4-1 Schematic of Ka/V Band-Switchable PA32                                                                    |

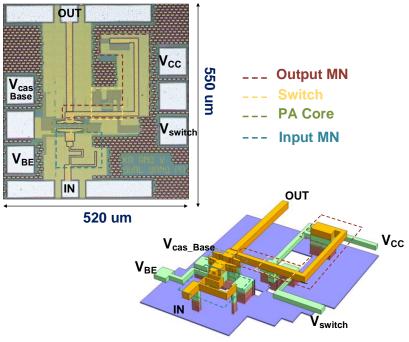

| Figure 4-2 Chip Photo and EM Simulation Model                                                                        |

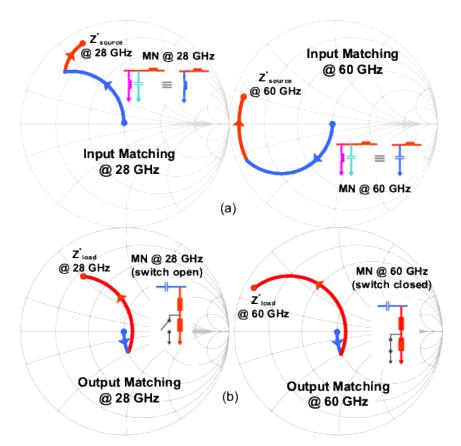

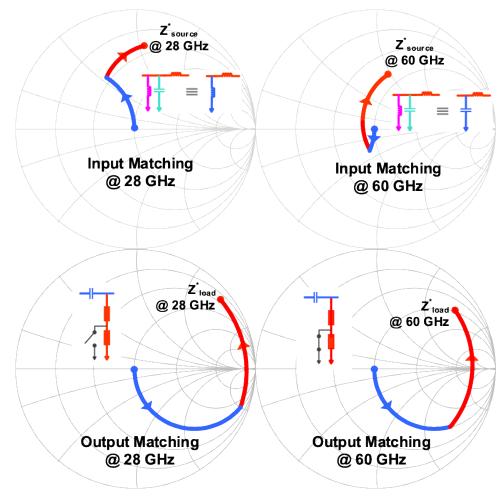

| Figure 4-3 Illustration of Input Output Dual-Band Matching (a) at 28GHz, (b) at 60 GHz34                             |

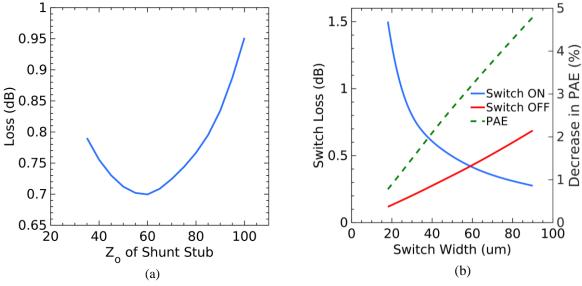

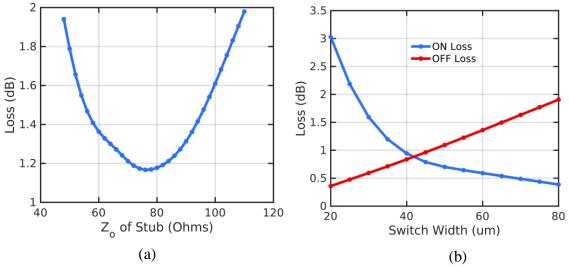

| Figure 4-4 (a) Stub Loss vs Characteristic Impedance of Stub, (b) Switch Loss vs Switch Size .35                     |

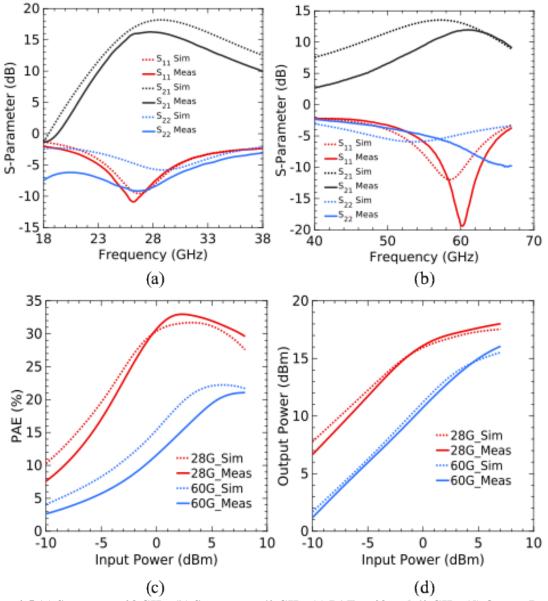

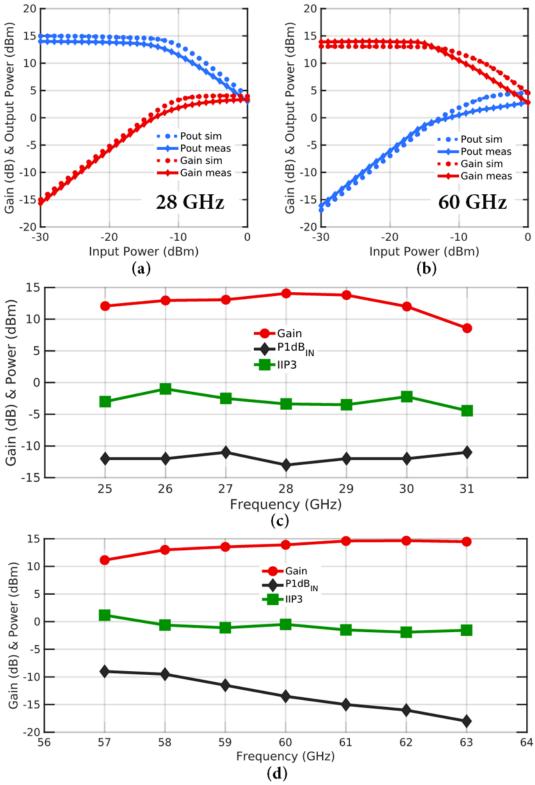

| Figure 4-5 (a) S-param at 28 GHz, (b) S-param at 60 GHz, (c) PAE at 28 and 60 GHz, (d) Output Power at 28 and 60 GHz |

| Figure 4-6 Schematic of Ka/V Band-Switchable LNA                                                                     |

| Figure 4-7 Illustration of Input Output Matching at 28 and 60 GHz40                                                  |

| Figure 4-8 (a) Stub Loss vs $Z_0$ of Stub, (b) Switch Loss vs Switch Size41                                          |

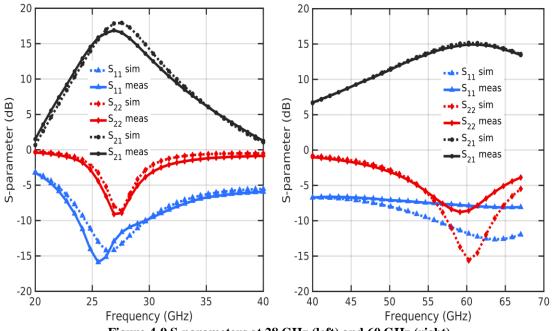

| Figure 4-9 S-parameters at 28 GHz (left) and 60 GHz (right)42                                                        |

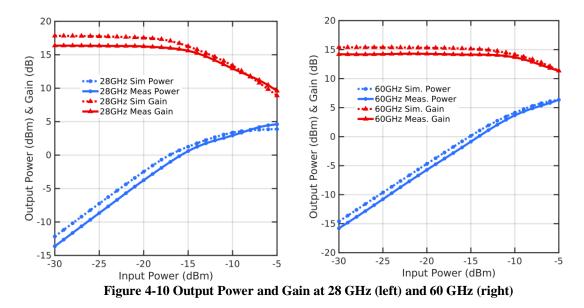

| Figure 4-10 Output Power and Gain at 28 GHz (left) and 60 GHz (right)43                                              |

| Figure 4-11 Noise Figure Measurement Setup at 60 GHz                                                                 |

| Figure 4-12 Noise Figure Plots at Ka-Band (left) and V-Band (right)44                                                |

| Figure 4-13 Conceptual schematic of the proposed amplifier                                                           |

| Figure 4-14 Schematic of the T/R switch incorporated into LNA and PA design                                          |

| Figure 4-15 Chip Photo                                                                                               |

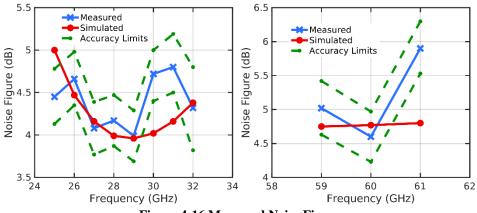

| Figure 4-16 Measured Noise Figure                                                                                    |

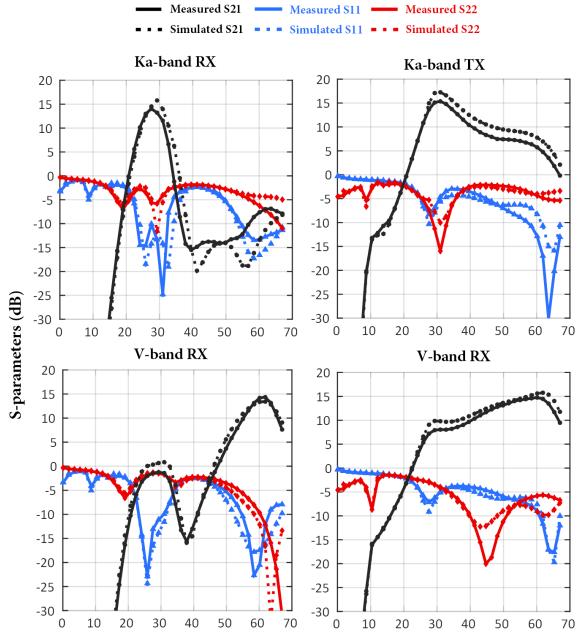

| Figure 4-17 Measured s-parameters                                                      |

|----------------------------------------------------------------------------------------|

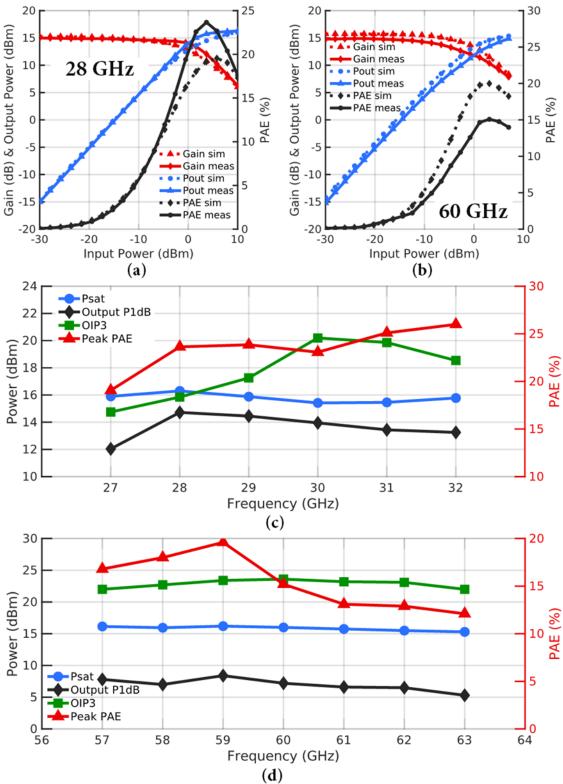

| Figure 4-18 Large Signal Transmit PerformanceError! Bookmark not defined.              |

| Figure 4-19 Large Signal Receive Performance53                                         |

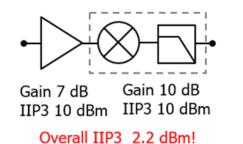

| Figure 5-1 IIP3 Degradation by the Gain of LNA Error! Bookmark not defined.            |

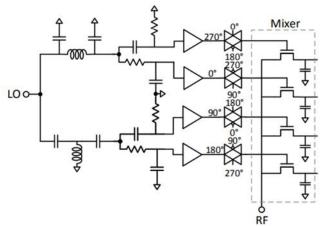

| Figure 5-2 A 0.05-2.4 GHz 4-Phase Mixer-First Receiver [35]58                          |

| Figure 5-3 A 20-30 GHz 4-Phase Mixer-First Receiver [36]60                             |

| Figure 5-4 A 20-30 GHz 4-Phase CLK Generation Circuit [36]Error! Bookmark not defined. |

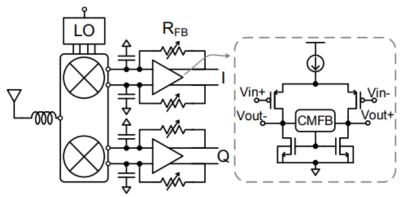

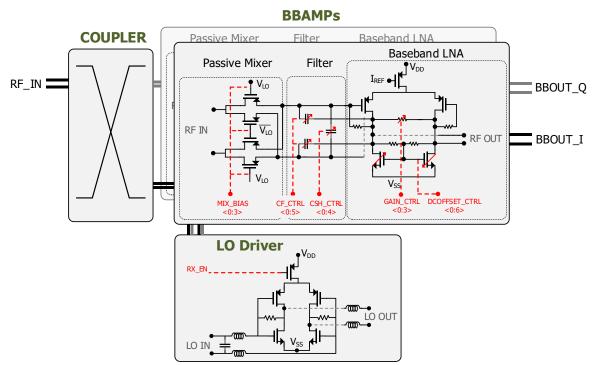

| Figure 5-5 Block Diagram of Designed 18-50 GHz Receiver                                |

| Figure 5-6 Quadrature Coupler                                                          |

| Figure 5-7 Simulated Amplitude and Phase Imbalance of Quadrature Coupler63             |

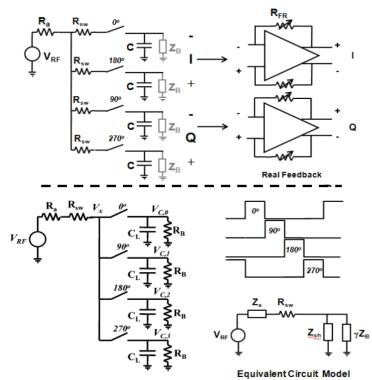

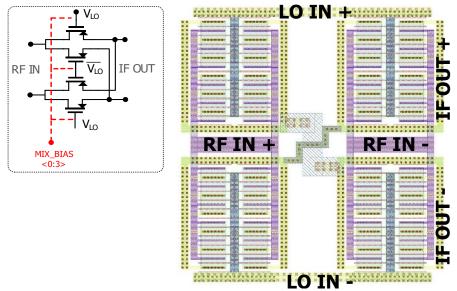

| Figure 5-8 Passive Mixer Schematic and Layout65                                        |

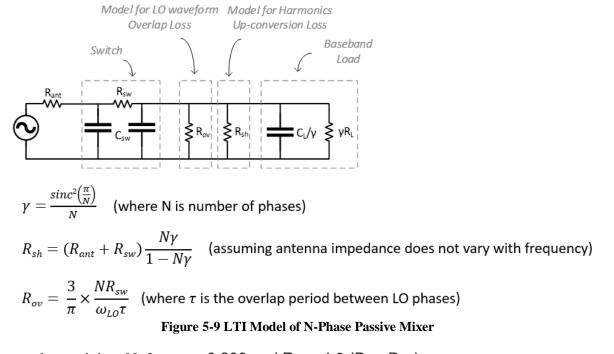

| Figure 5-9 LTI Model of N-Phase Passive Mixer65                                        |

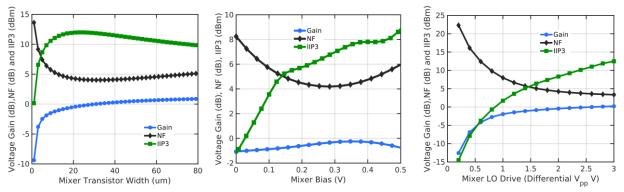

| Figure 5-10 Mixer Gain, NF and IIP3 against Different Design Parameters                |

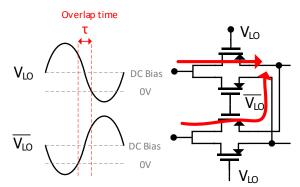

| Figure 5-11 Effects of Adding DC Bias to Sinusoidal LO Drive                           |

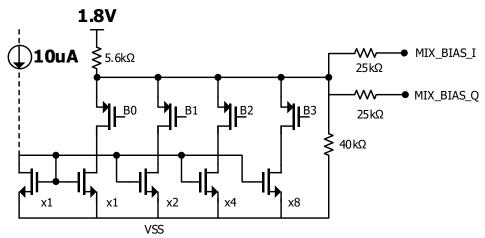

| Figure 5-12 Current DAC for Mixer's Bias Adjustment                                    |

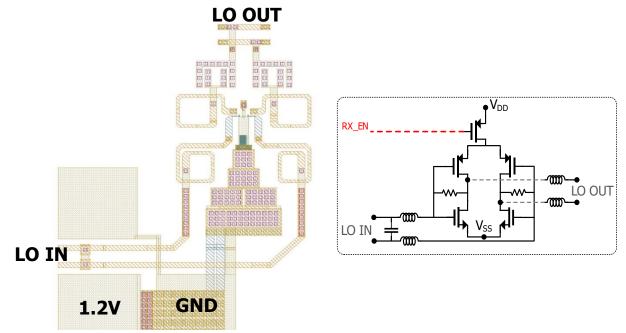

| Figure 5-13 LO Driver Layout and Schematic                                             |

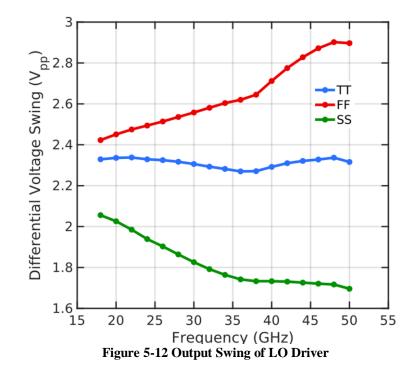

| Figure 5-14 Output Swing of LO Driver70                                                |

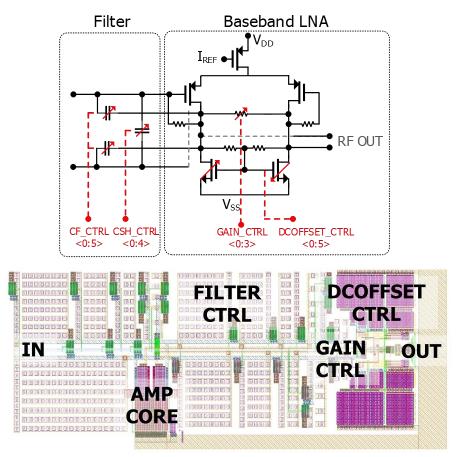

| Figure 5-15 Baseband LNA with Integrated Sallen-Key Low Pass Filter72                  |

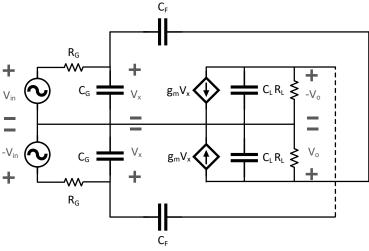

| Figure 5-16 Small Signal Model with Positive Feedback Capacitor75                      |

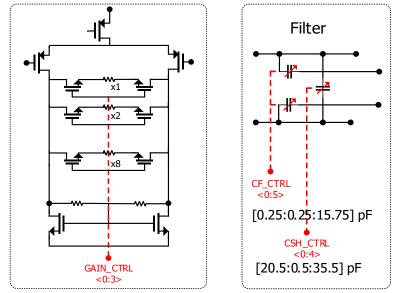

| Figure 5-17 Gain and Filter Control Banks77                                            |

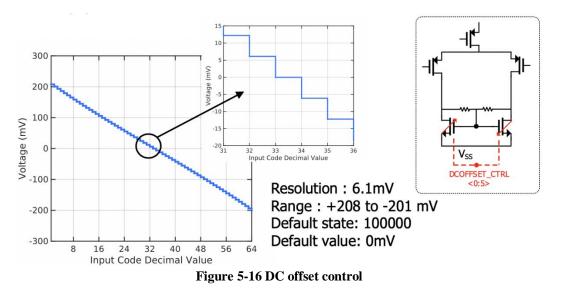

| Figure 5-18 DC offset control                                                          |

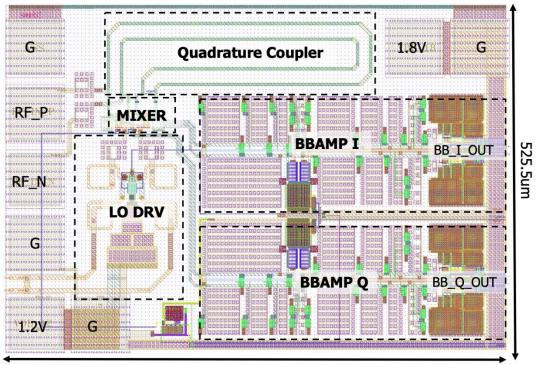

| Figure 5-19 Chip Layout79                                                              |

| Figure 5-20 Noise Figure vs RF Frequency    | 80 |

|---------------------------------------------|----|

| Figure 5-21Voltage Gain and Filter Response | 81 |

| Figure 5-22 IIP3 Response Across Frequency  | 81 |

| Figure 5-23 RF and LO Input Match           | 82 |

## **KEY TO ABBREVIATIONS**

| PA                 | Power Amplifier                                             |

|--------------------|-------------------------------------------------------------|

| TMN                | Tunable Matching Network                                    |

| LNA                | Low Noise Amplifier                                         |

| SiGe               | Silicon-Germanium                                           |

| CMOS               | Complementary Metal-Oxide Semiconductor                     |

| GSG                | Ground-Signal-Ground                                        |

| GSSG               | Ground-Signal-Signal-Ground                                 |

| IC                 | Integrated Circuit                                          |

| NMOS               | N-Channel Metal Oxide Semiconductor Field Effect Transistor |

| PMOS               | P-Channel Metal Oxide Semiconductor Field Effect Transistor |

| Q-factor           | Quality Factor                                              |

| RF                 | Radio Frequency                                             |

| λ                  | Wavelength [m]                                              |

| $\mathbf{f}_{max}$ | Maximum Oscillation Frequency                               |

| $f_{\tau}$         | Transit Frequency                                           |

| RX                 | Receiver                                                    |

| TX                 | Transmitter                                                 |

| TRX                | Transceiver                                                 |

| DSB                | Double sideband                                             |

| in  | Input     |  |

|-----|-----------|--|

| out | Output    |  |

| max | Maximum   |  |

| Th  | Threshold |  |

| L   | Load      |  |

| min | Minimum   |  |

## **1 INTRODUCTION**

## 1.1 Wireless Communication and Frequency Bands

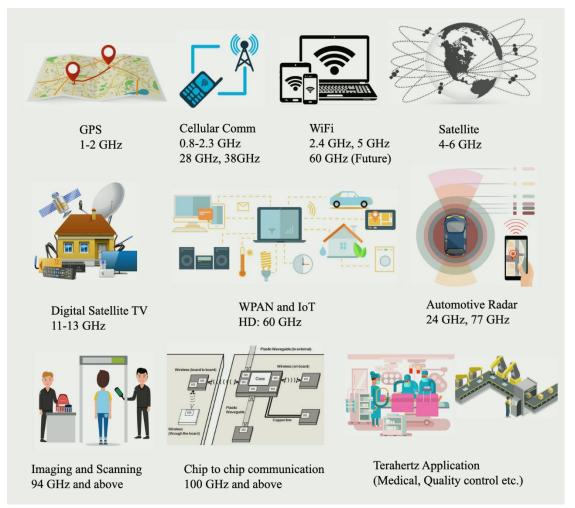

Although clearly worlds apart from today's technologies, the true definition of wireless communications can reach all the way back to the times past when humans used smoke signals and carrier pigeons to communicate wirelessly. In today's world, wireless communication is defined as transmission of information between two or more points using radio waves. The very first use of radio transmitted coded information was a result of the works of Maxwell and Hertz with their pioneering experiments using electromagnetic waves and the term "radio" was incepted after Marconi demonstrated long-range communication over the air without needing any wires. Radio technologies continued development for over a hundred years as people began to unravel the intricacies of wireless communications. This resulted in highly categorized frequency bands and respective applications. Some of the applications include AM and FM radio transmission (153 kHz to 108 MHz), radio frequency identification (RFID) (120 to 150 kHz 13.56 MHz, 433 MHz, 3.1 to 10 GHz), global positioning system (GPS 1-2 GHz), cellular communication (800 MHz, 2.4 GHz), 5G cellular communication (28 and 38 GHz), Wi-Fi (2.4 GHz, 5 GHz, 60 GHz in future), satellite communication (4-6 GHz), military radar systems (8-12 GHz), digital satellite television (11-13 GHz), WPAN (60 GHz), automobile collision avoidance radars (24 GHz, 77 GHz), microwave back haul communication (6, 11, 18, 23 38 GHz, 71 to 77 GHz, 81 to 86 GHz), mmwave body scanning and imaging (94 GHz), chip-to-chip communication (80 GHz and above), high resolution medical imaging (122 GHz, 140 GHz and above), radio astronomy(ALMA project), short-distance high speed communication (300 GHz and above) and terahertz medical applications [1]. Some of the above-mentioned wireless systems have matured over the years and have been

commercialized, but some systems, especially mm-wave systems, are still in the research domain. A snapshot of some of the wireless technologies in operation is shown in Figure 1-1.

## **1.2 Motivation for Multi-Band Radio**

Recent advances in the wireless communication market have led to the coexistence of several networks such as cellular network, personal area network (PAN), wireless local area network (WLAN), etc. along with several different air interfaces (802.11a, 802.11g, Bluetooth, wireless code division multiple access (WCDMA), etc.). Thus, the wireless devices need to be compatible with the different communication standards while still keeping similar performance, smaller die area and lower power consumption. The technology of the wireless devices also needs to allow for

Figure 1-1 Wireless Technologies and Applications in Operation

a smooth migration to future generations of communication standards with higher data rates. The need to enable the "global roaming" capability between a wide variety of networks operating at different frequencies calls for the development of compact and reconfigurable radio-frequency integrated circuits (RFICs) which can achieve maximum hardware sharing between different standards and across various functions. Such a compact RF front-end would require reconfigurable RF blocks rather than switched radio architectures [2].

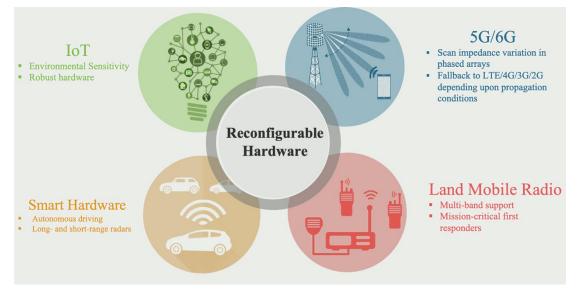

Most of the emerging wireless applications today, be it IoT (internet of things) devices, the 5G/6G communication system, the self-driving autonomous cars or land mobile communication in general, they all benefit from having a reconfigurable hardware integrated into them. Figure 1-2 shows some of the trending wireless applications which require some sort of RF hardware reconfigurability.

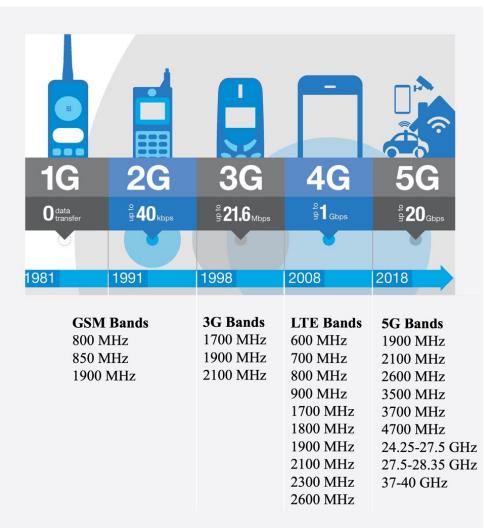

To emphasize the importance of reconfigurable RF hardware, a cellular phone example can be taken. The first (1G) and second generations (2G) of cellular network use GSM signals which are operated over 800/1900 MHz in Asia, Africa and Europe whereas 850/1900 MHz frequencies are used in Americas. The third generation (3G) employs UTMS system which require 1900/2100

Figure 1-2 Emerging Wireless Application Requiring RF Hardware Reconfigurability

MHz band along with 600/700/1700 MHz bands in some countries. With the introduction fourth generation (4G) in cellular network, more than 80 LTE bands were added which supported frequencies starting from 400MHz-6000MHz range. The fifth generation (5G) now adds millimeter wave bands extending from 24-40 GHz to the cellular network. Therefore, today's cellphone would at least require 6 frequency bands (800 MHz, 1900 MHz, 2100 MHz, 3500 MHz, 28 GHz, 39 GHz) in order to be compatible with all the generations of cellular network, at least in one part of the world. Figure 1-3 illustrates the most popular frequencies bands deployed in the world for different cellular generations [3].

Figure 1-3 Frequency Bands Required by A Multi-band Cellphone to be Compatible with all the Generations of Cellular Network (1G-5G)

## 1.3 Challenges in Milli-meter Wave Multi-Band Radio

The specifications placed on the reconfigurable RF element depends upon the RF block being designed. However, some common factors are:

- 1. Frequency tuning range and selectivity

- 2. Signal loss and DC power dissipation associated with tuning mechanism

- 3. Noise and Linearity degradation

An ideal reconfigurable element should be able to reconfigure to any frequency, provide zero loss and should not affect the linearity of the circuit. However, the available tunable components (e.g., varactor diodes) from the PDK have small tuning ratio, low-Q and large signal capacitance variation. Since these parameters are process dependents, therefore the achievable frequency tuning ratio and other metrics vary from process to process.

## **1.4 Existing Techniques for Multi-Band Radios**

Some of the popular techniques for reconfigurable or multi-band RFICs are as follows:

- 1. Switched-radio using SPDT switches [4]

- 2. Tunable inductors or varactors [5]

- 3. Resonant LC tanks [6]

- 4. MEMS based switches in matching network [7]

- 5. Variable delay transmission lines [8]

- 6. Switched feedback and output load [9]

- 7. Tunable stubs using transistor switches [10]

Switched-radio approach uses individual transceivers with dedicated frequency bands and a wideband SPNT switch at input and output to shift between different frequencies. This increases

the IC area N times and becomes unacceptable method for mm-wave phased arrays which require tight element spacing. Therefore, it is not extensively employed. Tunable inductors or capacitors suffer from low tuning range and low-Q; these techniques are used when narrowband tuning is required. Resonant LC-tank is the popular approach for dual/tri band transceiver designs. However, this approach is sensitive to the LC product and variation in resonance frequency is observed from sample to sample. Also, after certain point, it becomes impractical to have more than two or three LC tanks connected at the same node in the layout. Therefore, this approach is used for dual or tri-band applications only. Using switches in the matching network is another common approach for multi-band operation. There are many ways switches can be used. For example, switches can be used to turn connect/disconnect capacitors or inductors in the matching networks; switches can be used to make tunable transmission lines by controlling the current return path; switches can be used to make tunable shorted stubs. The major drawback with using the switches is the ON loss of the switch, which is technology dependent and varies from process to process. For example, a CMOS switch is usually less lossy than SiGe switch. Another drawback associated with the switch is the granularity. While varactors or tunable inductors may achieve continuous tuning range, a switch-based approach only achieves discrete resolution depending upon the number of switches used.

## **1.5** Objective and Organization of the Dissertation

The objective of this dissertation is to design the reconfigurable RF components and blocks operating at mm-wave frequencies which can yield a Si-based frequency-agile and adaptive RF front-end. The targeted applications for this work are 5G multi-band wireless communication and reconfigurable short/long range phased arrays for automobile radars. However, the concept of the

proposed reconfigurable RF elements is generic in nature and can be applied to all emerging applications which require on-chip reconfigurability at microwave and mm-wave frequencies.

Chapter 2 presents an analysis on harmonic tuning of stacked power amplifiers. It is concluded that stacked power amplifiers do not benefit from harmonic tuning as much as traditional cascode amplifiers owing to the fact that voltage swing is shared across all the transistors in stacked amplifier. Thus, each transistor needs to be harmonic tuned. Presented analysis shows only tuning the output transistor is not enough.

Chapter 3 presents the design of a reconfigurable impedance matching network at 28 GHz. The matching network is designed to cover half-gamma space in Smith chart. The performance of matching network integrated with PA has been measured and shows the feasibility of this approach. The proposed system is useful in phased array where the scan impedance variation is observed with respect to scan angle.

Chapter 4 builds on the similar concept and used the reconfigurable matching network for frequency band switching. Band-switchable LNA and PA have been designed and measured. Moreover, the designed LNA and PA are put together with the integrated T/R switches to form a bi-directional band-switchable amplifier. The amplifier takes very small die area and shows state-of-the-art performance.

Chapter 5 presents a reconfigurable 18-50 GHz direct down conversion receiver. The receiver is based on mixer-first topology to achieve high linearity. It is designed in 45nm SOI process and consists of a differential quadrature coupler, two-phase double balanced mixer, antialiasing positive feedback low pass filter and baseband low noise amplifier. Digital control for gain, filter response and offset calibration has been added. Chapter 6 summarizes the theme and contribution of this thesis.

## 2 HARMONIC TUNING OF STACKED POWER AMPLIFIERS

## 2.1 Introduction

The continuous scaling in modern semiconductor technologies for higher transit frequency  $(f_r)$  leads to a monotonic decrease in the breakdown voltages of the devices, especially for siliconbased device technologies. Therefore, the achievable output power using conventional power amplifier (PA) architectures, where a single device provides the output voltage swing, also decreases more and more. To overcome the low breakdown voltage limitation, it is possible to stack several devices in series. Series stacking of transistors makes it theoretically possible to obtain a higher output voltage swing by dividing the voltage equally among the stacked transistors. For an unchanged output current swing, the output power and the optimal load impedance are higher, allowing a high output power, as well as low impedance transformation ratio for matching networks. On the other hand, power added efficiency (PAE) is often degraded due to parasitic capacitances of intermediate nodes and non-constructive addition of voltage swings because of phase variations. In order to boost PAE, waveform engineering is commonly applied to PAs by harmonic tuning. The harmonic terminations at the output are typically optimized using load pull measurements, resulting in lower power dissipation and PAE enhancement.

In this chapter, we study the applicability of harmonic tuning techniques to stacked amplifiers. We conduct basic circuit analysis to show that the impact of harmonic tuning done at the topmost transistor significantly depends on the number of stacked transistors and the base termination impedance. Therefore, enhancement in efficiency turns out to be quite low as lower transistors continue dissipating more power. As a proof of concept, different X-band PA cores (cascode, tristacked and quad-stacked) have been designed and characterized using an active load-pull system with harmonic tuning capability. PAE contours are acquired for each case, and the measurements confirm the dependence of efficiency enhancement by harmonic tuning on the number of stacked transistors.

## 2.2 Theory

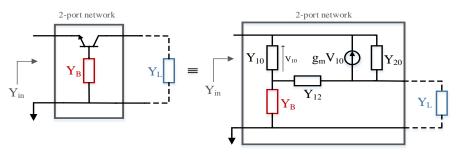

In a stacked PA, where the output transistor is terminated with a certain load impedance (at fundamental or harmonics), each transistor in the stack will see this impedance differently, mainly depending upon the base terminations. To clarify how the base termination affects the impedance seen by lower transistors, we analyze a generalized case as shown in Figure 2-1.

Figure 2-1 Y-parameter analysis of transistor with base and collector termination

Consider a transistor whose base is terminated with an admittance, YB, and the collector is terminated with a load admittance, YL. Using the small signal  $\pi$ -model as shown in Fig. 1, a Y-matrix can be derived. The input admittance of the two-port network can be written as:

$$Y_{in} = y_{11} - \frac{y_{12}y_{21}}{Y_L + y_{22}} \tag{1}$$

To clarify the impact of base termination, we will consider two limit cases:

## 2.2.1 When the base is shorted

Using  $Y_B = \infty$ , corresponding to a common-base topology, we get:

$$Y_{in} = g_m + Y_{10} - \frac{Y_{20}(g_m + Y_{20})}{Y_L + Y_{20} + Y_{12}}$$

(2)

Since a transistor's small signal ro is high and collector to emitter capacitance is small,  $Y_{20}$  becomes very small and we can neglect it. Therefore,

$$Y_{in} \approx g_m + Y_{10} \tag{3}$$

This shows that for the shorted base,  $Y_{in}$  becomes almost independent of load termination at output.

#### 2.2.2 When the base is open

This can be further divided into two cases for simplification:

a) When the load is shorted, that is  $Y_L=\infty$ , (1) gives:

$$Y_{in,SL} = \frac{Y_{12}}{Y_{12} + Y_{10}} [g_m + Y_{10}]$$

(4)

b) When the load is open, that is  $Y_L=0$ , (1) gives:

$$Y_{in,OL} = Y_{in,SL} - \frac{y_{12}y_{21}}{y_{22}}$$

(5)

This shows that  $Y_{in,OL}$  is smaller than  $Y_{in,SL}$  by  $\frac{y_{12}y_{21}}{y_{22}}$ . This means that  $Y_{in}$  has not only become dependent upon  $Y_L$ , but also follows the same trend as  $Y_L$ ; that is, when load is short, Zin becomes low and when load is open, Zin becomes high.

The above analysis draws an important conclusion that if the base of a transistor is terminated with high impedance, its input impedance (seen from the emitter) follows the load impedance (at collector); and if base is shorted (common base), the input impedance becomes independent of

load impedance. Since in stacked PAs, each lower transistor sees the load impedance through the emitter of the transistor above, this means that if the base termination of upper transistor is high, lower transistors can also see load harmonic impedances to a certain extent. However, as the number of stacked transistors increases, the load impedance seen by the lower transistors also reduces, eventually reaching a point where the impedance seen by lower transistors become independent of load impedance. This can be better understood with the help of examining a quad-stacked device as shown in Figure 2-2.

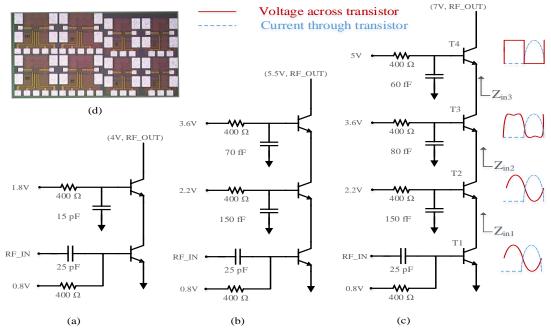

Figure 2-2 Designed X-Band power amplifiers: a) Cascode, b) Tri-stacked, c) Quad-stacked, d) Fabricated chip

Assume T4, the topmost transistor, is harmonically tuned for class-F operation where the second harmonic is shorted, and the third harmonic is presented with open circuit. This results in rectangular voltage waveform across T4. Transistor T3 sees the harmonic terminations through the emitter of T4. Considering that in a stacked design, the base termination impedance is high, the short and open are translated to some low and high impedances, as determined by (4) and (5), so voltage waveform across T3 also gets partially optimized for class F operation. However, T2 does

not benefit as it sees the open load through T3, which translates the open load impedance to a value which is not sufficiently high. Similarly, conditions for T1 tends to be even worse.

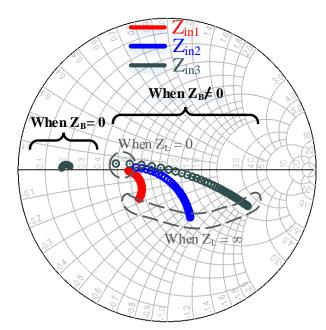

A simulation is also performed for the quad-stacked case to see how the impedance seen by each stacked transistor varies as a function of load impedance at the output node. Figure 2-3 shows a Smith chart plot of  $Z_{in1}$ ,  $Z_{in2}$  and  $Z_{in3}$  while  $Z_L$  is varied from short to open. It can be observed that  $Z_{in3}$  follows the trend of  $Z_L$ ; that is, when  $Z_L$  is short,  $Z_{in3}$  is also small and when  $Z_L$  is open,  $Z_{in3}$  is also high.  $Z_{in2}$  also follows the trend of  $Z_L$  but with smaller variation, whereas for  $Z_{in1}$  the variation is very small. This variation in  $Z_{in}$  keeps getting smaller as we increase the number of stacked transistors, and eventually converges to (4). Figure 2-3 also includes the case when the base of T4 is grounded and  $Z_{in3}$  becomes constant and independent of  $Z_L$  variation as expected from (3). These simulations confirm the theoretical analysis presented.

Figure 2-3 Variation of Zin1, Zin2, and Zin3 when ZL is varied from short to open

## 2.3 Design of Power Amplifiers Core

Cascode, tri-stacked, and quad-stacked PA cores have been designed at X-band using IHP SG25H4 0.25  $\mu$ m SiGe HBTs with a specified f<sub>r</sub>/f<sub>max</sub> of 180/220 GHz.

Figure 2-3 shows the designed cascode topology where the upper base is terminated with ample capacitance to have AC ground at X-band frequencies. Also shown are the tri-stacked and quad-stacked topologies where the upper bases are not AC grounded; instead, they are terminated with specific capacitances, based on the guidelines provided here. The values of base capacitors and bias voltages have been optimized through simulations to allow equal voltage swings across each transistor. The 400  $\Omega$  resistors are included in bias paths and serve the purpose of RF blocking.

## 2.4 Measurements

The MT2000 (Maury Microwave) mixed-signal active load pull system is used to perform fundamental and harmonic load pull measurements. All the PAs have been measured with continuous wave (CW) operating conditions at 10 GHz. Source pull is performed for fundamental only, whereas load pull is performed up to three harmonics. On-wafer small signal calibration is done using SOLT standards, and an absolute large signal power calibration is performed using manufacturer supplied SOL standards.

All designed device topologies are biased in class B operation. First, input power and fundamental impedances are swept to find the optimum load and source impedance for maximum PAE, while 2nd and 3rd harmonics are terminated by 50  $\Omega$ . Having the fundamental impedance terminated at the desired point, the 2nd harmonic impedance is swept (keeping the 3rd harmonic terminated at 50  $\Omega$ ), and PAE contours have been measured. After terminating fundamental and

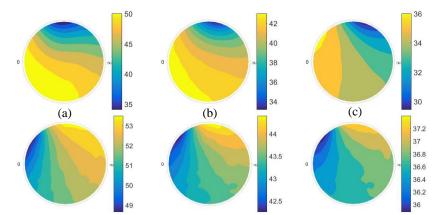

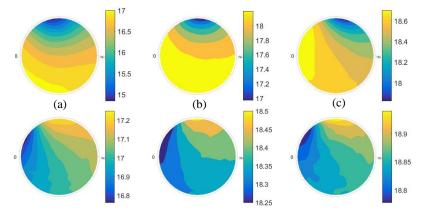

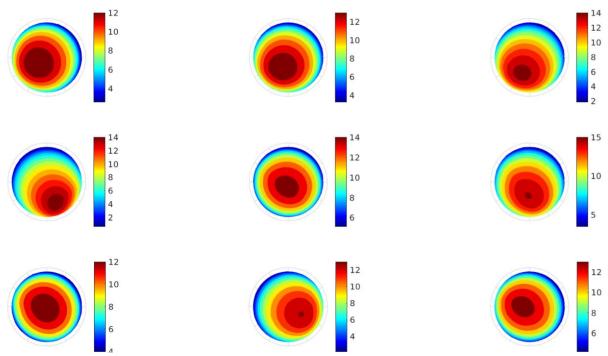

2nd harmonic load impedances at the highest PAE point, 3rd harmonic impedances are swept and PAE contours have been measured. Figure 2-4 shows measured PAE contours, and Figure 2-5 shows measured fundamental output power contours at 2 dB gain compression point.

Table 2-1 lists the PAE and output power (Pout) enhancement by harmonic tuning, where enhancement means the difference between PAE or Pout when a harmonic is terminated at the best possible and the worst possible location. The cascode device shows the highest PAE improvement of 18% for the 2nd harmonic and 5% for 3rd harmonic tuning. The tri-stacked device shows a PAE improvement of 10% for 2nd harmonic, and 2% for 3rd harmonic tuning. The quad-stacked device shows 7% improvement for 2nd harmonic tuning and 1% for the 3rd harmonic. These results are in parallel with the expectations and the analysis provided here.

While recent work suggests individual tuning of harmonic impedance for each stacked transistor, the effectiveness of this technique will potentially be limited, because the suggested additional harmonic termination appears in parallel to the emitter impedance of the next transistor. Our analysis shows that this impedance approaches the value derived in Eq. (4) as the number of the stacked transistors increases, which as a result dominates the impedance at these intermediate nodes.

## 2.5 Conclusion

Stacked transistor PAs where only the output transistor is loaded with a harmonic termination network does not result in significant overall PAE enhancement. This chapter shows that the more the number of stacked transistors, the lesser the improvement in PAE. This, in part, has to do with the fact that voltage swing is shared between each transistor in a stacked power amplifier; but also due to the reduction of impedance presented by the emitters moving downward

in the stack. Our analysis furthermore shows importance of correct base termination that can lead to a higher impedance at the emitter.

Figure 2-4 Measured PAE (%) contours for 2nd harmonic (top) and 3rd harmonic (bottom) impedance sweep: a) Cascode, b) Tri-stacked, c) Quad-stacked

Figure 2-5 Measured fundamental output power (dBm) contours for 2nd harmonic (top) and 3rd harmonic (bottom) impedance sweep: a) Cascode, b) Tri-stacked, c) Quad-stacked

Table 2-1 Comparison of PAE and Pout by Harmonic Tuning

| Topology     | Enhancement by 2 <sup>nd</sup> Harmonic Tuning |            | Enhancement by 3 <sup>rd</sup> Harmonic Tuning |            |

|--------------|------------------------------------------------|------------|------------------------------------------------|------------|

|              | PAE (%)                                        | Pout (dBm) | PAE (%)                                        | Pout (dBm) |

| Cascode      | 18                                             | 2.1        | 5                                              | 0.44       |

| Tri-stacked  | 10                                             | 1.4        | 2.3                                            | 0.26       |

| Quad-stacked | 7                                              | 0.9        | 1.6                                            | 0.18       |

# 3 A KA-BAND POWER AMPLIFIER WITH RECONFIGUR-ABLE IMPEDANCE MATCHING NETWORK

This chapter focuses on the design of a tunable impedance matching network (TMN) at Kaband. The TMN draws its motivation from the phased arrays where the antenna impedance changes with respect to the scan angle and hence output power and efficiency of the system is degraded due to the mismatch between antenna and the power amplifier. As a proof of concept, a Ka-band power amplifier (PA) is also designed and integrated with the TMN. The output power of the PA is observed as the function of load impedance. The sections below provide details on the analysis and design of PA and TMN.

## **3.1 Scan Impedance Variation in Phased Arrays**

A phased array is an array of antennas where each antenna is excited with different phase to modify the overall radiation pattern and form a beam. Since the antenna elements are normally close to each other ( $\lambda/2$  apart) and excited with different phase, there is mutual coupling between adjacent elements which induces stray current in antennas, hence changing the V/I ratio or the impedance of the antenna. The change in impedance depends on the phase difference between the antenna elements which is governed by the scan angle of the beam. Figure 3-1 shows the theoretical variation in reflection coefficient of an antenna element with respect to scan angle for half-wave infinite dipole array at 28 GHz.

## 3.2 Reconfigurable Impedance Matching Network for Phased Arrays

An analysis on infinite patch array suggests that the magnitude of reflection coefficient varies from 0 to 0.5 (on average) for scan angles up to 60° in E, H or D-plane [11]. Therefore, the design goal is set to match any load within half-gamma around center of the Smith chart. To realize

Figure 3-1 Variation in Reflection Co-efficient wrt Scan Angle in Dipole Array at 28 GHz

a more practical circuit, only 7 impedance points (3 inductive, 3 capacitive and one nominal 50  $\Omega$ ) are chosen which would be able to provide magnitude mismatch of less than 0.2 (i.e.,  $|\Gamma| < 0.2$ ) for all the loads in half-gamma circle. The mismatch can further be improved by having more impedance points, but it leads to increase in the size and the loss of TMN. Therefore, the loss in the TMN becomes higher than the performance gained by preventing the mismatch. The 0.2 gamma mismatch has been chosen as it provides acceptable performance degradation. This concept is illustrated in Figure 3-2.

Figure 3-2 Block Diagram of the Proposed System

## **3.3 Design of Ka-Band PA**

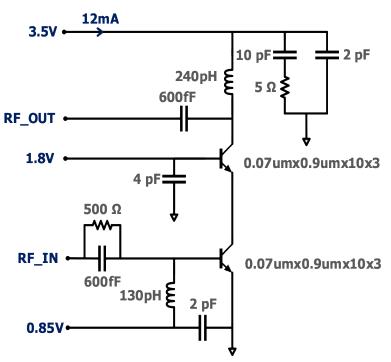

The power amplifier has been designed using IHP SG13G2 0.13  $\mu$ m SiGe HBTs with specified f<sub>r</sub>/f<sub>max</sub> of 300/500 GHz. The amplifier uses cascode topology and operates common-base transistor in weak-avalanche region. Input has been matched to 50  $\Omega$  for small signal conditions whereas output has been matched to 50  $\Omega$  for large signal conditions determined through load-pull analysis. Input series capacitor and output shunt capacitors are made low Q to make PA unconditionally stable. Large signal stability has been ensured by sweeping the input bias voltage and maintaining the k-factor greater than one. Figure 3-3 shows the schematic of the PA.

Figure 3-3 Schematic of the K-Band PA

## **3.4 Design of Reconfigurable Impedance Matching Network**

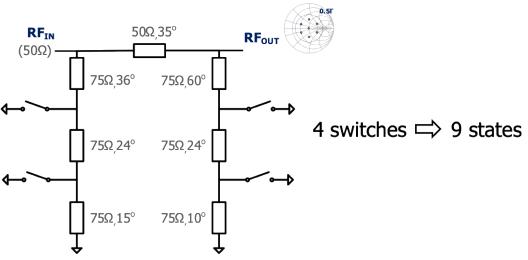

To design a tunable matching network, transmission line based stubs have been preferred over varactors as the available varactors provided very limited tuning range with very low Q. Double shunt stub topology (Figure 3-4) has been chosen as it provides greater flexibility to move around in half-gamma circle and low loss compared to a L sections where the series tunable element would appear in main signal path and incur more loss. To tune the stubs, transistor switches are used to short out the stub at various points, thus, controlling the effective length of the stub. The number of switches is dictated by the impedance points that are required to match. Since we are targeting 7 impedance points, we need at least 4 switches. However, with 4 switches, we can have 9 different ON/OFF configurations and generate 9 impedance points.

Figure 3-4 Double Stub Reconfigurable Matching Network

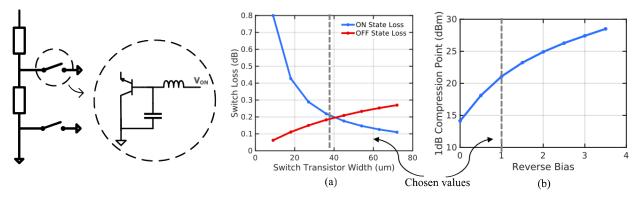

## 3.4.1 Switch Loss Optimization

To tune the stubs, transistor switches are used to short out the stub at various points, thus, controlling the effective length of the stub. The transistor switches are operated in reverse saturated mode where the collector is grounded, and the emitter is connected to RF signal path. This improves the insertion loss of the switch as the emitter is physically well isolated from the conductive silicon, therefore providing better isolation [12]. One concern of using transistors as switches at mm-wave frequencies is the tradeoff between the on resistance and off capacitance. However, since the transmission line itself is a distributed reactive element, it can be modeled as a series of inductors and capacitors, the capacitance of transistors in their off state can be absorbed into the transmission line model, allowing for much larger transistors to be used, which reduces

the on resistance. On the other hand, a too large transistor would have a large off state capacitance which, in turn, would reduce the required length of transmission line to such a point that the physical separation between two switches may not be enough. Also, after a certain size, the decrease in insertion loss (due to decrease in on resistance) is not significant. Therefore, an optimum size is determined by running simulations with different sizes (as shown in Figure 3-5 (a)). The collector of the transistor is DC blocked to avoid any static current while the switch is ON.

An additional concern is the linearity of the switch. This is critical in the OFF state, as the AC voltage present at the emitter leaks to the base of the switch and develops a base-emitter differential, which may self-actuate the switch. This can be alleviated by applying a reverse bias on the switch. Figure 3-5 (b) plots 1-dB compression point of the switch against reverse bias applied to it. The reverse emitter-base breakdown limit for HBT in this process is -1.6V, therefore we use a VBE of -1.5V, which gives 22 dBm compression point which is far higher than the PA 1dB output compression point of 15.5 dBm. Therefore, the linearity of the PA is not affected, and switch is not operated beyond its breakdown limit

Figure 3-5 (a) Switch Loss against Switch size (Width), (b) P1dB of the Switch in OFF State against Reverse Bias Voltage

## 3.4.2 Shunt Stub Loss Reduction Technique (Theoretical Analysis)

Consider a transmission line stub of characteristic impedance  $Z_o$ , electrical length  $\theta$ , and terminated by ON impedance of the switch R<sub>ON</sub>. The impedance looking into the stub,  $Z_{in}$ , is given as:

$$Z_{in} = Z_o \frac{R_{ON} + jZ_o tan(\theta)}{Z_o + jR_{ON} tan(\theta)}$$

. . .

Rationalizing the denominator to separate real and imaginary parts:

$$Z_{in} = Z_o \left[ \frac{Z_o R_{ON} (1 + tan^2 \theta)}{Z_o^2 + R_{ON}^2 tan^2 \theta} + j \frac{Z_o^2 tan \theta - R_{ON}^2 tan \theta}{Z_o^2 + R_{ON}^2 tan^2 \theta} \right]$$

The quality factor of impedance Zin can be defined as:

$$Q = \frac{X_{in}}{R_{in}} = \frac{\tan\theta(Z_o^2 - R_{ON}^2)}{Z_o R_{ON}(1 + \tan^2\theta)}$$

using trigonometric identities, it can be simplified to following:

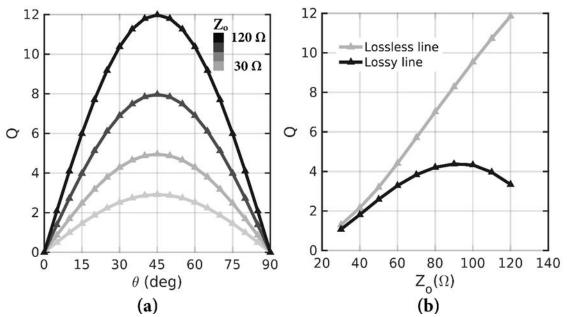

$$Q = \left[\frac{Z_o^2 - R_{ON}^2}{Z_o R_{ON}}\right] \left[\frac{\sin 2\theta}{2}\right]$$

Assuming  $R_{ON}$ = 5  $\Omega$ , Figure 3-6 (a) plots Q for different Z<sub>o</sub> of the stub against  $\theta$ . There are two important observations:

- 1. the quality factor of the  $Z_{in}$  increases as the characteristic impedance of the stub increases

- 2. the quality factor peaks at an electrical length of  $45^{\circ}$

This means to have the highest quality factor (to reduce loss), the design procedure should be as follows:

- start with the stub length of 45° and the highest characteristic impedance allowed by the process

- 2. optimize the characteristic impedance to meet the desired impedance for matching

Please note that the highest characteristic impedance of the stub is limited by the process design rules like width and spacing of the conductors. For example, the process used is this chapter requires minimum top metal width of 2 um which limits the characteristic impedance to 105  $\Omega$  if the stub is realized using a microstrip transmission line.

While the above analysis is valid for near lossless transmission lines, a lossy transmission line needs special treatment. The quality factor of lossy transmission line terminate with  $R_{ON}$  can be derived using the similar method as in previous subsection:

$$Q = \left[\frac{Z_o^2 - R_{ON}^2}{Z_o R_{ON}}\right] \left[\frac{tanh(\gamma l)}{1 + tanh^2(\gamma l)}\right]$$

where

$$\gamma = \alpha + j\beta$$

Here,  $\alpha$  is the attenuation constant and  $\beta$  is the phase constant. The attenuation constant,  $\alpha$ , is dependent on the physical width of the conductor used to realize the transmission line. For example, the attenuation constant for microstrip transmission line can be given as:

$$\alpha = \frac{R_s}{Z_o W}$$

where Rs and W are resistivity and width of the conductor, respectively. Above expression shows that attenuation constant is inversely related to the width of the conductor. Therefore, a stub of higher characteristic impedance (i.e., lower conductor width) has higher attenuation constant. This means that we cannot use the highest characteristic impedance available from a given process as then the loss is then dominated by the physical conductor width. On the other hand, a small characteristic impedance stub also has poor quality factor as described in the previous subsection. This suggests there should exist an optimal characteristic impedance for which the loss reaches minima. Figure 3-6 (b) compares the quality factor of a lossless and a lossy stub against the characteristic impedance. It can be seen that while the Q-factor of the lossless line increases linearly with the characteristic impedance, the lossy line has peak Q-factor around 90 W characteristic impedance. This observation leads to the following design procedure:

- 1. sweep the characteristic impedance of the stub (while adjusting the electrical length to maintain a fixed impedance looking into the stub) to find optimal condition for peak Q

- 2. optimize the stub length to meet the desired impedance for matching

Figure 3-6 Quality factor of shunt stub: (a) against electrical length of lossless stub

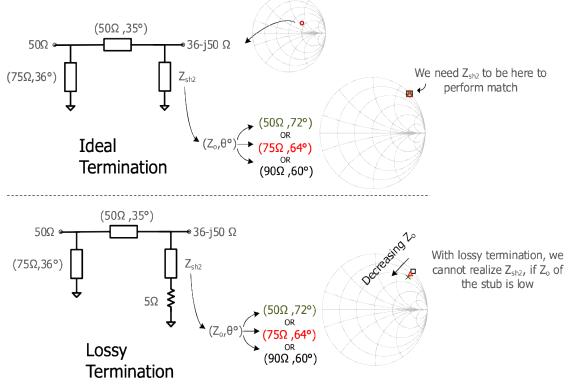

#### 3.4.3 Shunt Stub Loss Reduction Technique (Intuitive Analysis)

Consider two cases as shown in Figure 3-7. Let's say we want to match the impedance 36j50  $\Omega$  as shown by the red dot in Smith chart. Say, we have designed first shunt stub and the series stub, and we need to design the second stub is supposed to provide Z<sub>sh2</sub> impedance. Now, there are different (Z<sub>o</sub>, $\theta$ ) pairs that can be used in order to realize Z<sub>sh2</sub> impedance. The choice of pair does not affect the stub loss. However, if the stub is terminated with switch impedance (say 5  $\Omega$ ), the different (Z<sub>o</sub>, $\theta$ ) pairs are not able to generate the same Z<sub>sh2</sub> impedance. It appears that the higher characteristic impedance, the closer the stub impedance gets to Z<sub>sh2</sub> as shown in Figure 3-6. Therefore, a very high characteristic impedance is desired. However, as the characteristic impedance increases, the width of the transmission line becomes smaller which increases the metallic loss of the conductor. On the other hand, if characteristic impedance is reduced, we may

Figure 3-7 Explanation of Shunt Stub Characteristic Impedance Effect on Matching with and Without Lossy Termination

Sweet spot for 36um switch width

Figure 3-8 Stub Characteristic Impedance Showing Different Sweet Spots for Different Switch Widths (or Resistances) not be able to generate Z<sub>sh2</sub> impedance. Therefore, there exists is a sweet spot for characteristic

impedance of the stub which depends on the switch resistance and the place where the stub is connected in the matching network. Figure 3-8 shows the variation of loss against the characteristic impedance of the stub.

# 3.5 Complete Schematic

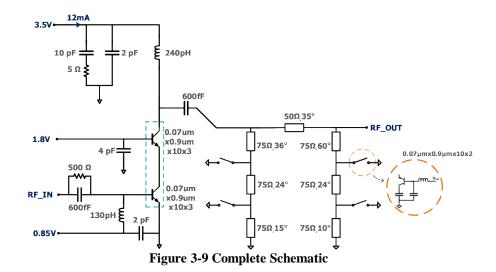

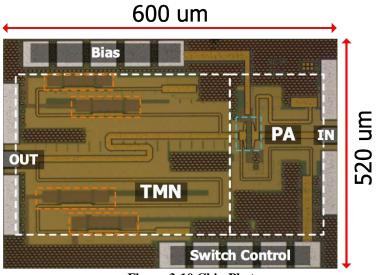

Figure 3-9 shows complete schematic of TMN+PA and Figure 3-10 shows the chip photo.

#### Figure 3-10 Chip Photo

# 3.6 Measured Results

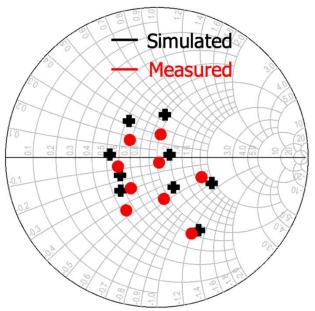

Two sets of measurements have been performed. First, tunable matching network has been characterized by measuring small signal parameters using Agilent N5227A PNA. Figure 3-11 shows the simulated and measured Smith chart coverage at 26.5 GHz for various switch settings. The measured impedances are slightly off from the simulated impedances due to imperfections in

Figure 3-11 Measured and Simulated TMN Impedance Points for All Switch States

the layout. Second, large signal measurements of the PA integrated with TMN have been

performed at 26.8 GHz using MT2000 (Maury Microwave) active load pull system. Figure 3-12 shows 3 dB compressed output power contours and Figure 3-13 shows peak PAE contours for nine different switch states. The power contours shift to different impedance points depending upon the switch states, thereby covering more than half of the Smith chart. Figure 3-14 shows combined peak PAE and 3dB compression power contours which have been plotted by taking out the maximum of PAE and power from individual contours for each switch state. The contours are plotted with 5% PAE steps and 2 dBm Pout steps. The max PAE contour (20%) is very wide (compared to a typical non-tunable PA where max PAE happens only at a narrow region) which means the PA can match to different impedances within that contour and provide constant efficiency. Next, second PAE contour (15%) covers more than half of the Smith chart, and similarly power contours are very wide, indicating the ability of the PA+TMN to match different load impedances and provide constant performance throughout the half-gamma region.

## 3.7 Summary

This chapter shows a tunable matching network integrated with the PA at Ka-band for eliminating mismatch between PA and antenna due to scan impedance variation in a phased array system. The matching network uses double shunt stub topology with tunable stubs and covers halfgamma area in the Smith chart. Guidelines to optimize switch and stub loss has been presented. The measured results confirm the feasibility of this approach by showing wide and expanded PAE and Pout contours. The proposed integrated impedance matching networks can also be used to tune the center frequency of the PA or compensate for variations in the active device parameters due to temperature drift, fabrication tolerances or on-chip load pull purposes.

Figure 3-13 Measured 3dB Compressed Power (dBm) Contours for All Switch States

Figure 3-12 Measured Peak PAE (%) Contours for All Switch States

Figure 3-14 Combined Contours of Peak PAE and 3dB Compressed Output Power from Each Switch State

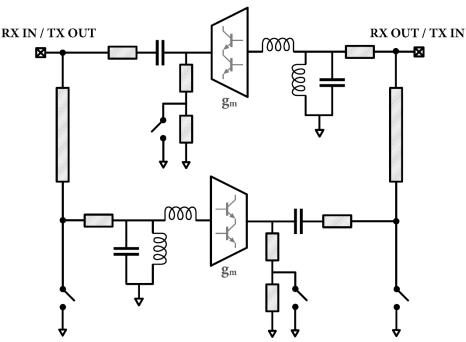

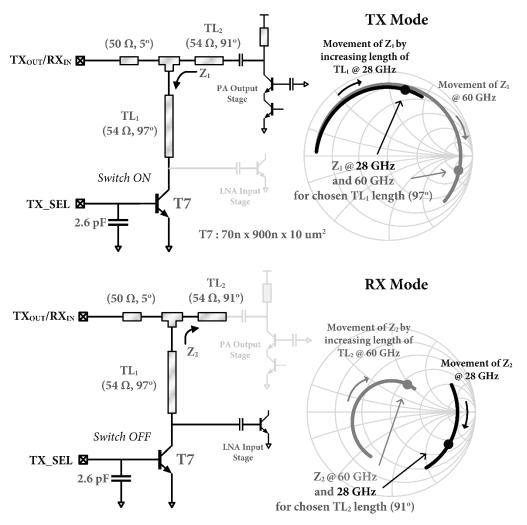

# 4 A COMPACT KA/V BAND-SWITCHABLE TRX AMPLIFIER WITH INTEGRATED T/R SWITCHES

This chapter builds on the previous chapter and uses the reconfigurable matching network to change the frequency band of operation. To demonstrate the effectiveness of this approach, a highly integrated 28/60 GHz band-switchable transmit-receive (TRX) amplifier is designed which consists of 28/60 GHz LNA, 28/60 GHz PA and integrated transmit-receive (T/R) switch. A dual-band transceiver operating at Ka/V band is of special interest for both radar and wireless communication purposes. The vast unlicensed bandwidth (7 GHz) at V-band can provide multi-Gbps data rate for communications or very high resolution for radar at V-band, whereas the low atmospheric and free-space propagation loss at Ka-band can provide long distance communication or higher range for radar. Furthermore, due to the varying propagation characteristics and capacities among different potential 5G bands, a reconfigurable or multi-band RF transceiver unit is proposed, which can use appropriate frequency band as required by the environment, country or application. The designed 28/60 GHz TRX amplifier achieves state of the art performance by co-designing the amplifiers with T/R switch, thereby occupying a very small real estate. Sections below discuss design of individual blocks and integration.

### 4.1 Ka/V Band-Switchable PA

The PA is designed in IHP SG13G2 BiCMOS process. The technology features high performance 130 nm HBTs with a specified  $f_T/f_{max}$  of 300/450 GHz. The collector-emitter breakdown voltage, BVCEO, equals 1.7 V and collector-base breakdown voltage, BVCBO, equals 4.8 V.

#### 4.1.1 Amplifier Design

Figure 4-1 shows the circuit diagram of the designed PA. T1 (gm transistor) and T2 (cascode transistor) have been biased in class AB mode. T2 operates in weak avalanche region with its base terminated with a very low impedance (AC ground). SiGe HBT cascode PAs designed in this fashion with low upper base resistance allow large-signal collector voltage excursions beyond BV<sub>CEO</sub> without occurrence of catastrophic damage and without impact to long-term hot-carrier reliability [13]. Device sizes and bias current are optimized through load pull simulations to achieve output power around 17 to 18 dBm. The base node of cascode transistor (T2), which is AC grounded, is very prone to oscillation at mm-wave frequencies. Therefore, large AC ground capacitors have been laid out as close to the base as possible, and EM simulations have been performed to ensure stability. Also, the low-frequency oscillations arising due to RF chokes in the bias paths have been suppressed by shunting the bias paths with proper low-Q capacitors. Figure 4-2 shows chip photo and EM simulation model.

#### 4.1.2 Matching Network Design

The input of the PA has been dual-band matched at 28/60 GHz by employing a parallel LC tank and a series inductor. This tank resonates around 36 GHz, thereby providing positive reactance below 36 GHz and a negative reactance above 36 GHz. Therefore, the LC tank behaves as an inductor at 28 GHz and as a capacitor at 60 GHz. In essence, it's an L-type matching network with a L<sub>shunt</sub>-L<sub>series</sub> topology at 28 GHz and a C<sub>shunt</sub>-L<sub>series</sub> topology at 60 GHz, as shown in Figure 4-3 (a). The output of the PA has been dual-band matched at 28/60 GHz by using a shunt stub and series capacitor. The shunt stub is a thin film microstrip line (TFML) with an HBT switch used to tune its length. When the switch is turned OFF, the RF signal sees a longer stub length and PA switches to the 28 GHz mode. When the switch is turned ON, it shorts a part of the stub to the ground, effectively reducing the length of the TFML, as shown in Figure 4-3 (b). Therefore, RF signal sees a shorter stub length and the PA switches to the 60 GHz mode.

Figure 4-2 Chip Photo and EM Simulation Model

Figure 4-3 Illustration of Input Output Dual-Band Matching (a) at 28GHz, (b) at 60 GHz

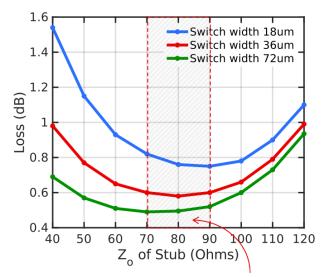

#### 4.1.3 Switch Design

The loss incurred by the switch in the TFML can be minimized by reducing the product  $I^2Z$  product as described in section 3.4.1 and 3.4.2. Figure 4-4 (a) shows dependence of the switch loss on the characteristic impedance of the stub. As we move to low characteristic impedances, input impedance of the shunt stub decreases, which increases the switch loss, whereas for high characteristic impedances metallic loss through conductor dominates (as physical width of the conductor decreases). Therefore, there exists an optimum where the loss is minimum. Figure 4-4 (a) shows this is Z0=60  $\Omega$  in this case. Therefore, while designing the shunt stub a 60  $\Omega$  characteristic impedance is chosen, and the length is then determined according to the matching network requirement. As for the switch ON resistance,  $R_{sw}$ , it can be minimized by increasing the

switch size. However, there is a trade-off between the ON resistance, OFF resistance and OFF capacitance. Since the transmission line itself is a distributed element, the capacitance of the switch in the OFF state can be absorbed into the transmission line, allowing for much larger transistors to be used with lower ON resistance. After a certain size, the reduction in insertion loss in ON state (due to decrease in ON resistance) becomes insignificant whereas the increase in insertion loss in OFF state (due to proportional decrease in OFF resistance) becomes significant. Also, at large switch size, there is additional drop to PAE due to the switch bias current. Figure 4-4 (b) captures these tradeoffs. Based on these tradeoffs, switch size of 0.09 x 36 mm<sup>2</sup> is chosen which results in 0.7dB loss in ON state, 0.3dB loss in OFF state and 2% additional decrease in PAE due to switch bias current. Switch is turned OFF by applying reverse bias which helps in improving the linearity as described in section 2.4.1.

Figure 4-4 (a) Stub Loss vs Characteristic Impedance of Stub, (b) Switch Loss vs Switch Size

#### 4.1.4 Measured Results

Small signal measurements have been performed using Keysight N5227A PNA network analyzer which is calibrated using SOLT standards from 0.1MHz to 67 GHz range. Figure 4-5 (a) and (b) shows measured and simulated s-parameters at 28 GHz and 60 GHz respectively. Measured gain at 28/60 GHz is 16.2/11.8 dB and measured input return loss is -8/-19 dB. To measure the output power, input of the PA is excited using a Keysight E8257D analog signal generator and the output is measured using Keysight N9010B EXA signal analyzer. Figure 4-5 (c) shows measured and simulated PAE at 28/60 GHz and Figure 4-5 (d) shows measured and simulated output power at 28/60 GHz. Due to the measurement setup, there is measurement uncertainty of  $\pm$  0.2 dB in the output power which also adds uncertainty of  $\pm$  1.5 % to the peak PAE. The PA shows simulated

Figure 4-5 (a) S-param at 28 GHz, (b) S-param at 60 GHz, (c) PAE at 28 and 60 GHz, (d) Output Power at 28 and 60 GHz

$P_{sat}$  of 18/16.5 dBm and simulated peak PAE of 32/22 % at 28/60 GHz whereas the measured Psat is 18.4/17.2 dBm and measured peak PAE is 33/21 % at 28/60 GHz. Table 4-1 compares this PA with the most recent single-band and wideband PAs around 28/60 GHz frequencies.

#### 4.1.5 Summary

A band-switchable PA operating in 28 GHz and 60 GHz mode is presented. The PA employs cascode topology, LC tank at input matching network and tunable stub at the output matching network to shift the frequency of operation between 28 GHz and 60 GHz. Performances in each band are comparable to single band state of the art PAs. The designed PA is suitable for 5G transceivers or dual-band phased array radars.

|                    |                 | Tashralasr  | Torraloor                      | Frequency | D (JD-11)              | Peak PAE | Gain | Core Area                  |

|--------------------|-----------------|-------------|--------------------------------|-----------|------------------------|----------|------|----------------------------|

| ľ                  | Reference       | Technology  | Topology                       | (GHz)     | P <sub>sat</sub> (dBm) | (%)      | (dB) | ( <b>mm</b> <sup>2</sup> ) |

| Dual-band          |                 | 120 510     |                                | 28        | 18.4                   | 33       | 16.2 | 0.1                        |

| РА                 | This Work       | 130 nm SiGe | Class AB Cascode               | 60        | 17.2                   | 21       | 11.8 | 0.1                        |

|                    | 2017 ISSCC [14] | 45 nm SOI   | Cascode                        | 60        | 16.7                   | 28.3     | 24   | 0.067                      |

|                    | 2018 MWCL [15]  | 45 nm SOI   | Cascode                        | 60        | 18.5                   | 25.5     | 15   | 0.12                       |

|                    | 2016 ISSCC [16] | 130 nm SiGe | Cascode                        | 60        | 23.6                   | 27.7     | 24   | 0.55*                      |

| Dedicated          | 2015 ISSCC [17] | 28 nm CMOS  | Doherty                        | 60        | 18.2                   | 21       | 15.2 | 0.16                       |

| Single Band<br>PAs | 2017 TMTT [18]  | 130 nm SiGe | Class AB<br>Harmonically Tuned | 28        | 18.8                   | 35.3     | 15.5 | 0.27                       |

| #                  | 2018 MWCL [19]  | 45 nm SOI   | Doherty                        | 28        | 22.4                   | 40       | 10   | 0.25*                      |

|                    | 2018 RFIC [20]  | 45 nm SOI   | Hybrid Class F/F <sup>-1</sup> | 28        | 18.6                   | 45.7     | 11.4 | 0.14                       |

|                    | 2018 RFIC [21]  | 90 nm CMOS  | Cascode                        | 28        | 26                     | 34       | 16.3 | 0.4                        |

|                    | 2016 JSSCC [22] | 28 nm CMOS  | CS w/ Source Degen.            | 28        | 14                     | 35.5     | 15.7 | 0.155                      |

|                    | 2011 TMTT [23]  | 130 nm SiGe | Distributed                    | DC-77     | 17.5                   | 13       | 10   | 2.2#                       |

| Wideband           | 2018 PAWR [24]  | 130 nm SiGe | Distributed                    | 12-40     | 21.5                   | 20.1     | 14   | 1.2#                       |

| PAs                | 2016 JSSC [25]  | 90 nm SiGe  | Distributed                    | 14-105    | 15 <sup>&amp;</sup>    | 9.7      | 12   | 1.51#                      |

|                    | 2017 MWCL [26]  | 180 nm CMOS | Distributed                    | 2-22      | 14.5 <sup>&amp;</sup>  | 10       | 11.9 | 1.7#                       |

Table 4-1 State-of-the-art Single Band, Multi-Band and Wideband PAs

### 4.2 Ka/V Band-Switchable LNA

The LNA is also designed in the same SG13G2 BiCMOS process. The design procedure of Ka/V band switching is almost the same as described in the section 4.1 for the PA. However, some details are presented here again.

#### 4.2.1 Amplifier Design

Figure 4-6 shows the circuit diagram of the designed LNA.  $T_1$  (g<sub>m</sub> transistor) and  $T_2$  (cascode transistor) have been biased in class AB mode. Device sizes and bias current are optimized through s-parameter simulations for minimum noise figure. Emitter degeneration inductor and base inductor at the input have been added to bring  $\Gamma_s$  and  $\Gamma_{opt}$  closer for simultaneous noise and input matching. The base node of cascode transistor (T<sub>2</sub>), which is AC grounded, is very

Figure 4-6 Schematic of Ka/V Band-Switchable LNA

prone to oscillation at mm-wave frequencies. Therefore, large AC ground capacitors have been

laid out as close to the base as possible, and EM simulations have been performed to ensure stability. A series resistor of  $15\Omega$  has been added in VCC path to suppress low-frequency oscillations arising due to RF choke.

#### 4.2.2 Matching Network Design

The input of the LNA has been dual-band matched at 28/60 GHz by employing a parallel LC tank and a series inductor. This tank resonates around 54 GHz, thereby providing positive reactance below 54 GHz and a negative reactance above 54 GHz. Therefore, the LC tank behaves as an inductor at 28 GHz and as a capacitor at 60 GHz. In essence, it's an L-type matching network with a L<sub>shunt</sub>-L<sub>series</sub> topology at 28 GHz and a Cshunt-Lseries topology at 60 GHz, as shown in

Figure 4-7 Illustration of Input Output Matching at 28 and 60 GHz

Figure 4-7. The output of the LNA has been dual-band matched at 28/60 GHz by using a shunt stub and series capacitor. The shunt stub is a thin film microstrip line (TFML) with an HBT switch used to tune its length. When the switch is turned OFF, the RF signal sees a longer stub length and LNA switches to the 28 GHz mode. When the switch is turned ON, it shorts a part of the stub to the ground, effectively reducing the length of the TFML. Therefore, RF signal sees a shorter stub length and the LNA switches to the 60 GHz mode.

#### 4.2.3 Switch Design

The switch and stub loss have been optimized using the same guidelines as presented in section 4.1.3 for the power amplifier case. As mentioned in this section, the loss of the stub is dependent on the characteristic impedance of the stub, and there exists a sweet spot where the stub of the loss is minimum. This is shown in Figure 4-8 (a). The loss of the stub is minimum around 75  $\Omega$ , therefore we chose 75  $\Omega$  characteristic impedance for all the stub design. The switch loss depends on the switch size. However, after a certain size the reduction in loss is not appreciable, therefore through simulations a size has been chosen (as shown in Figure 4-8 (b) where ON loss

Figure 4-8 (a) Stub Loss vs Z<sub>0</sub> of Stub, (b) Switch Loss vs Switch Size

is not so high and OFF loss is also small. More details on design has already been presented in section 4.1.3.

#### 4.2.4 Measured Results

Small signal measurements have been performed using Keysight N5227A PNA network analyzer which is calibrated using SOLT standards from 0.1MHz to 67 GHz range. Figure 4-9 shows measured and simulated s-parameters at 28 GHz and 60 GHz respectively. Measured gain at 28/60 GHz is 16.2/15 dB, input return loss is -10/-6 dB and the output return loss is -7/-8 dB. To measure the compression point, input of the PA is excited using a Keysight E8257D analog signal generator and the output is measured using Keysight N9010B EXA signal analyzer. The measured P1dB input compression point is -12/-7 dBm at 28/60 GHz whereas the simulated compression point is -11/-7 dBm at 28/60 GHz. Figure 4-10 shows gain and output power plots at 28 GHz and 60 GHz respectively.

Figure 4-9 S-parameters at 28 GHz (left) and 60 GHz (right)

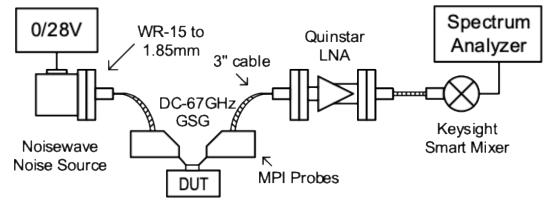

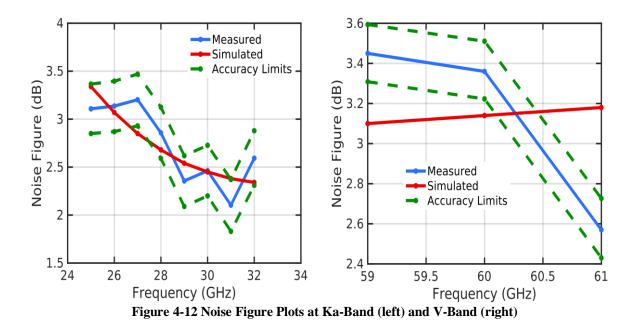

The noise figure measurement setup at 60 GHz has been shown in Figure 4-12. A noise source with ENR around 17dB at 60 GHz has been used. Quinstar LNA with gain around 35dB and noise figure 4dB has been used to suppress the mixer and spectrum analyzer noise figure. Keysight smart mixer has been used to downconvert 60 GHz signal to IF which is within spectrum analyzer measurement range. The noise floor of spectrum analyzer itself has been mathematically subtracted by spectrum analyzer by using the "Noise Floor Extension" option in the spectrum analyzer. The losses of the cables and connectors have been measured using the Keysight E8257D signal generator. The signal generator has output power accuracy of ±1dB at 60 GHz (according to the manual). Therefore, there is 1dB uncertainty to the noise figure from signal generator. The writer is not sure about how to solve this problem and it is being ignore for this report. Spectrum analyzer resolution bandwidth has been set to 10 Hz with 512 samples average and an average detector. The noise output power measured by the spectrum analyzer fluctuates within  $\pm 0.2$ dB which also adds uncertainty of around ±0.2dB (exact amount can be calculated from Y-factor formula). The noise figure has been measured by using the Y-factor method and the noise associated with measurement setup has been de-embedded using the Friis formula. Figure 4-11