# IMPROVING THE PERFORMANCE OF PASSIVE COMPONENTS OF THE POWER ELECTRONICS AT HIGH SWITCHING FREQUENCY

By

Abdulrhman Alshaabani

### A DISSERTATION

Submitted to

Michigan State University

in partial fulfillment of the requirements

for the degree of

Electrical Engineering – Doctor of Philosophy

2021

#### **ABSTRACT**

# IMPROVING THE PERFORMANCE OF PASSIVE COMPONENTS OF THE POWER ELECTRONICS AT HIGH SWITCHING FREQUENCY

By

#### Abdulrhman Alshaabani

Power converters have an important role in modern electric and electronic systems due to different voltage and power level requirements. Magnetic components are considered to be essential elements of the power converters. Storing the energy, filtering the signal, and transferring the energy are the main tasks of the magnetic components in the power converters. With developing the technology of power switches, the power converter can be operated at high frequencies. However, the magnetic components are suffering from their parasitic capacitance at high frequencies. Modeling the parasitic capacitance of the magnetic components is crucial to design power converters at high frequency. To date, the researches that have been conducted to modeling the parasitic capacitance have mainly targeted the low power applications with very high frequencies and high power with multi-layer transformers. Consequently, there remains a blank in the body of knowledge regarding modeling the parasitic capacitance of a single-layer inductor with a magnetic core at medium power. The relation between the number of turns and the parasitic capacitance of the single-layer inductors with the magnetic core should be considered. Moreover, improving the magnetic components by reducing the parasitic capacitance is essential. By using the technique of reducing the parasitic capacitance, the resonant frequency of the magnetic components can be shifted to a higher frequency besides improving the impedance of the inductor. Therefore, this dissertation contributes in four main parts: (1) Modeling the parasitic capacitance of a single-layer inductor with a magnetic core. (2) Reducing the parasitic capacitance using the technique of magnetic coupling. (3) Selecting the appropriate range of high operating frequency for power converter applications. (4) Estimating the parasitic capacitance of interleaved coupled two-phase inductors.

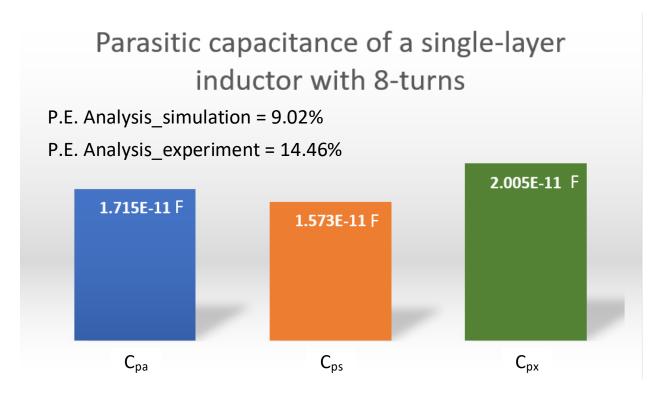

For the first part, a new approach to determining the total parasitic capacitance of a singlelayer inductor with the magnetic core at a medium frequency range that is below the first resonant frequency is presented in this research. The proposed analytical approach can obtain the parasitic capacitance between the winding and core based on the physical structure of the inductor. The analytical approach depends on approximating the rod wire shape to a square shape. The total equivalent parasitic capacitance is derived. The results are verified by finite element analysis and experimental measurements using impedance network analyzer.

The second part of this research presents a technique for improving the performance of an inductor at high frequencies through mitigating effects caused by the parasitic capacitance. This technique adds a small capacitor to the coupled windings of the inductor to reduce the parasitic capacitance of the inductor. The relationship between the parasitic capacitance, magnetic coupling coefficient, and the small capacitor is introduced. The method to size the reduction capacitor is detailed in this research. The results of applying this technique show an improvement in the inductance impedance by 40 dB and shifting the resonant frequency to a higher frequency when k = 0.97. The experimental results validated the effectiveness of the proposed technique.

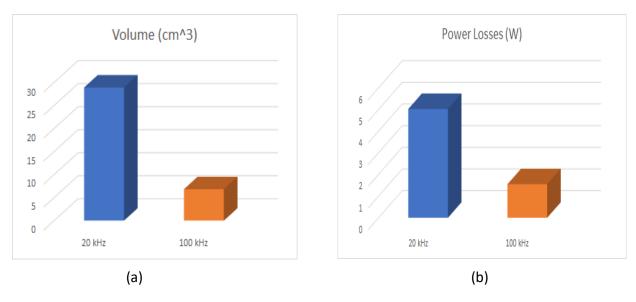

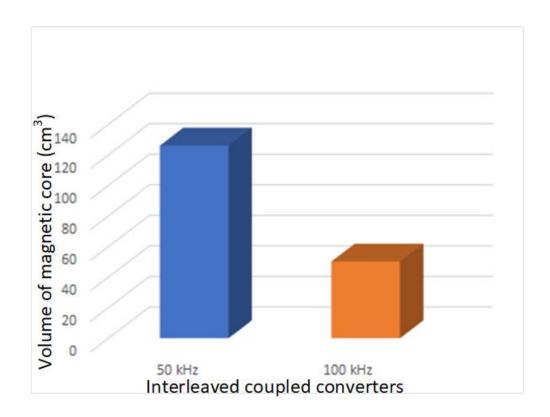

Moreover, a new methodology to properly select the highest operating frequency for the magnetic components in power electronics devices is presented in this research. Several parameters of the magnetic components such as the resonant frequency and the losses of the magnetic core are taken under consideration. The results of this methodology prove the maintaining the efficiency with reducing the volume of the magnetic core by 70%.

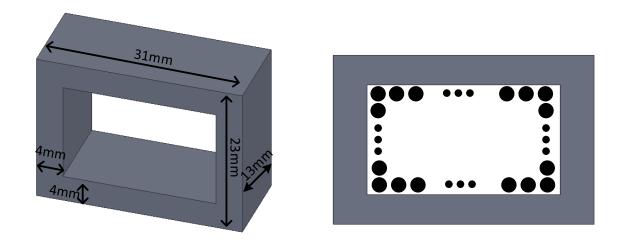

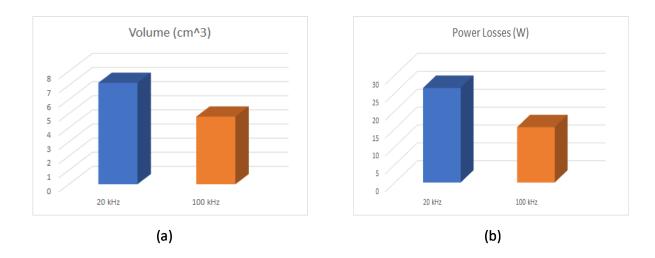

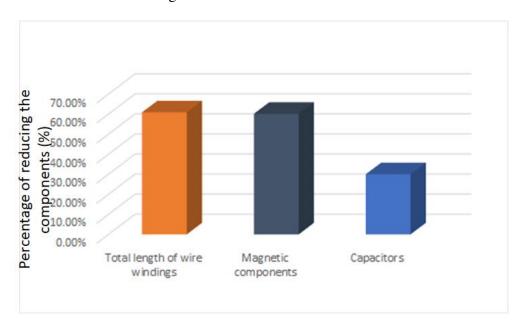

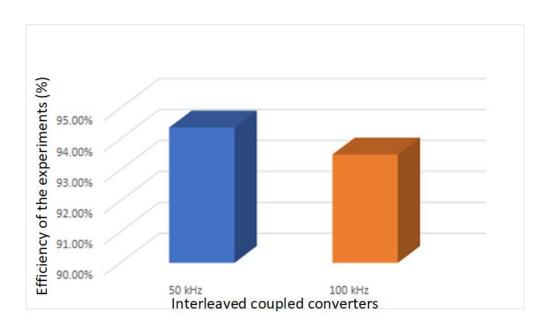

Finally, the parasitic capacitance of the interleaved two-phase coupled-inductors is introduced in this research. Besides estimating the parasitic capacitance, the method of determining the size of the interleaved two-phase coupled inductors of boost converter is explained. The result shows the reduction of the size of the two-phase coupled inductors by using the proposed selecting suitable high operating frequency methodology. Moreover, the efficiency of the interleaved coupled inductors boost converter is maintained with reducing the volume by 60% and increasing the operating frequency by doubling the frequency.

Copyright by ABDULRHMAN ALSHAABANI 2021

| This dissertation is dedicated to my beloved father, Lafi Faheem Alshaabani, my beloved mother, |

|-------------------------------------------------------------------------------------------------|

| Fatima Salem Alrashidi, and my beloved brothers and sisters.                                    |

|                                                                                                 |

|                                                                                                 |

#### ACKNOWLEDGEMENTS

I would like to take this opportunity to express my sincerest and deepest appreciation to my advisor, Prof. Bingsen Wang. I am greatly indebted to my advisor, Prof. Wang, for his continuous support, help, and encouragement throughout the past few years. I genuinely appreciate his thoughtfulness, patience, and continued guidance to make my Ph.D. experience productive.

I would also like to thank Prof. Elias Strangas, Prof. Joydeep Mitra, and Prof. Guoming Zhu for being the members of my committee. I am deeply grateful to them for their inspiring and helpful courses, and valuable comments.

A special thanks go to my colleagues in the Electrical Machines and Power Electronics Research Laboratory for their kind support and valuable friendship.

I am greatly thankful to my parents, my brothers and sisters, and my friends for their genuine care, encouragement, and understanding. Thank you all for making my dream come true.

### TABLE OF CONTENTS

| LIST OF TABLES                                                                                                                                              | X                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| LIST OF FIGURES                                                                                                                                             | хi                         |

| CHAPTER 1 INTRODUCTION  1.1 Motivation and Challenge  1.2 Problem Statement  1.3 Objective  1.4 Research Scope and Contributions  1.5 Research Organization | 1<br>1<br>6<br>6<br>7<br>8 |

|                                                                                                                                                             | 9<br>9<br>11<br>11         |

| CHAPTER 3 EXISTING METHODS OF DETERMINING THE PARASITIC                                                                                                     | 10                         |

| 3.1 Basic cells method to determining the parasitic capacitance                                                                                             | 13<br>13<br>16<br>17       |

| 3.2.1 Advantages and Disadvantages                                                                                                                          | 22<br>23                   |

| 3.3.1 Advantages and Disadvantages                                                                                                                          | 25                         |

| 4.2 Methodology of Modeling Inductors                                                                                                                       | 27<br>30<br>30<br>34       |

| 1                                                                                                                                                           | 39<br>46                   |

| CHAPTER 5 INVESTIGATING THE OVERALL PARAMETERS AFFECTING THE PARASITIC CAPACITANCE OF THE MAGNETIC COMPONENTS                                               | 48                         |

| 5.1 Introduction                                                                                                                                            | 48<br>49<br>49<br>49       |

|       | 5.2.4 Number of layers of the winding                                                                    | 51    |

|-------|----------------------------------------------------------------------------------------------------------|-------|

| 5.3   | Minor Parameters of the Parasitic Capacitance of the Magnetic Components                                 | 52    |

|       | 5.3.1 Effects of the bobbin material                                                                     | 53    |

|       | 5.3.1.1 Frequency Effects on the Bobbin                                                                  | 54    |

|       | 5.3.1.2 Temperature Effects on the Bobbin                                                                | 57    |

|       | 5.3.1.3 Thickness of the Bobbin                                                                          | 58    |

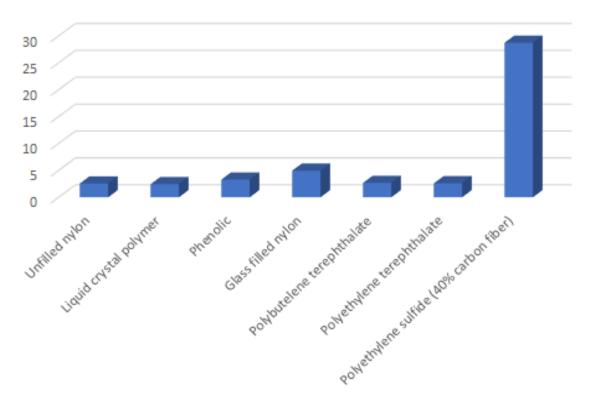

|       | 5.3.2 Effects of the Wire                                                                                | 59    |

| 5.4   | Results                                                                                                  | 60    |

| 5.5   | Conclusion                                                                                               | 62    |

| СНАРТ | TER 6 EXISTING TECHNIQUES OF REDUCTION THE PARASITIC                                                     |       |

|       | CAPACITANCE FOR INDUCTORS                                                                                | 64    |

| 6.1   | Using Mutual Capacitance Concept to Reducing the Parasitic Capacitance                                   | 64    |

| 6.2   | Using the Mutual Inductance Concept for Reducing the Parasitic Capacitance                               | 68    |

| СНАРТ | TER 7 PARASITIC CAPACITANCE REDUCTION TECHNIQUE BY USING                                                 |       |

|       |                                                                                                          | 72    |

| 7.1   |                                                                                                          | 72    |

| 7.2   | Reduction Technique using mutual inductance and magnetic coupling                                        | 74    |

| 7.3   | Experimental Results                                                                                     | 80    |

| 7.4   | Conclusion                                                                                               | 82    |

| СНАРТ |                                                                                                          |       |

|       | COMPONENTS FOR DC-DC CONVERTER                                                                           |       |

| 8.1   | Introduction                                                                                             |       |

| 8.2   | Methodology                                                                                              |       |

|       | 8.2.1 Resonant Frequency                                                                                 | 88    |

|       | 8.2.2 Magnetic core frequency range                                                                      | 91    |

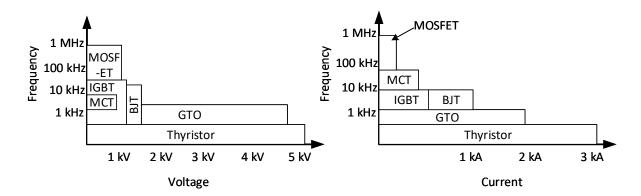

|       | 8.2.3 The frequency limitation of the electronic switch                                                  | 92    |

| 8.3   | Selecting the magnetic core size and number of turns                                                     | 93    |

| 8.4   | Experiment and Result                                                                                    |       |

| 8.5   | Conclusion                                                                                               | 102   |

| СНАРТ |                                                                                                          |       |

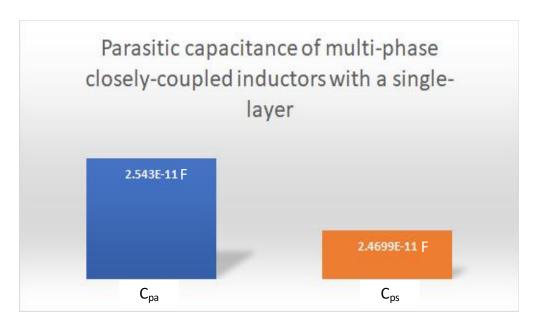

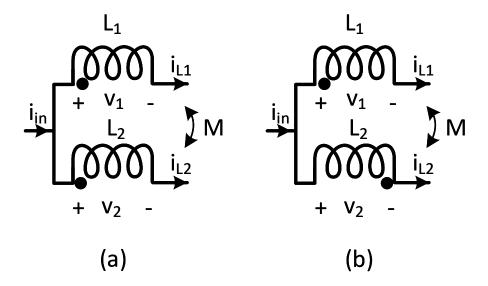

| 9.1   | Estimating the Parasitic Capacitance of Two-Phase Inductors                                              | 103   |

|       | 9.1.1 Estimating the Parasitic Capacitance of the Loosely-Coupled Inductors with a Single-Layer Windings | 105   |

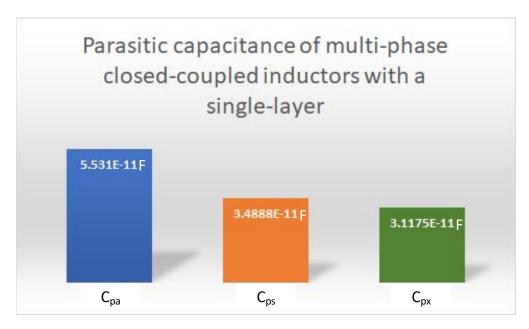

|       | 9.1.2 Estimating the Parasitic Capacitance of the Closed-Coupled Inductors                               | . 0 . |

|       | with a Single-Layer Windings                                                                             |       |

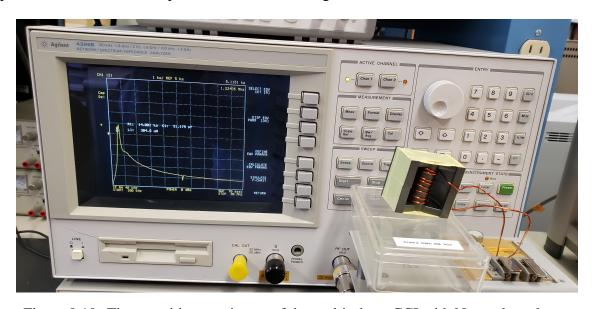

|       | 9.1.3 Experiments and Results                                                                            | 110   |

| 9.2   | Design Interleaved Boost Converter with Two-Phase Coupled Inductors                                      | 113   |

|       | 9.2.1 Determining the Inductance value of the Interleaved Loosely-Coupled                                |       |

|       | Inductors Boost Converter                                                                                |       |

|       | 9.2.2 Experiment and Results                                                                             | 117   |

| CHAPTER 10 | CONC    | LU | SIO | NS | A) | NE | F | ľU′ | ΓU | RI | E <b>\</b> | W( | )R | K |  |  |  |  |  |   |      |  | . 1 | 29 |

|------------|---------|----|-----|----|----|----|---|-----|----|----|------------|----|----|---|--|--|--|--|--|---|------|--|-----|----|

| 10.1 Conc. | lusions |    |     |    |    |    |   |     |    |    |            |    |    |   |  |  |  |  |  |   |      |  | . 1 | 29 |

| 10.2 Futur | e Work  |    |     |    |    |    |   |     |    |    |            |    |    |   |  |  |  |  |  |   |      |  | . 1 | 30 |

| BIBLIOGRAP | ΉΥ      |    |     |    | •  |    |   | •   |    |    | •          |    |    | • |  |  |  |  |  | • | <br> |  | . 1 | 32 |

### LIST OF TABLES

| Table 5.1: | The PET permittivity of the bobbin versus temperature                                      |

|------------|--------------------------------------------------------------------------------------------|

| Table 7.1: | Results of the inductor impedances                                                         |

| Table 8.1: | Parameters of the Boost converter                                                          |

| Table 9.1: | Interleaved two-phase loosely-coupled inductors boost converter parameters with $50 \ kHz$ |

| Table 9.2: | Interleaved two-phase loosely-coupled inductors boost converter parameters 100 kHz         |

### LIST OF FIGURES

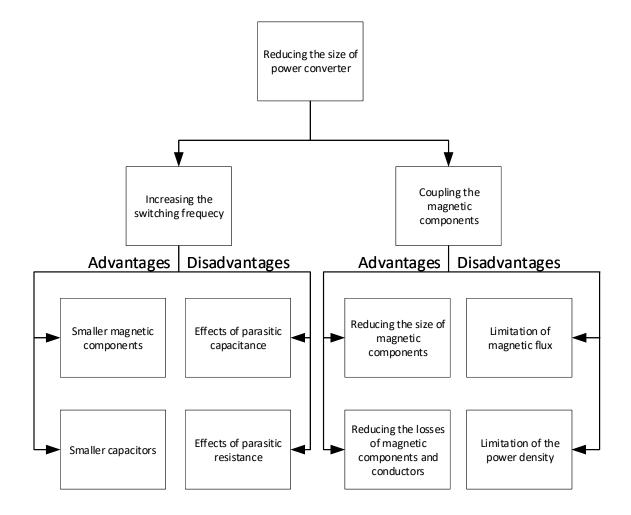

| Figure 1.1: | A flowchart of methods to reduce the size of magnetic components                          | 3  |

|-------------|-------------------------------------------------------------------------------------------|----|

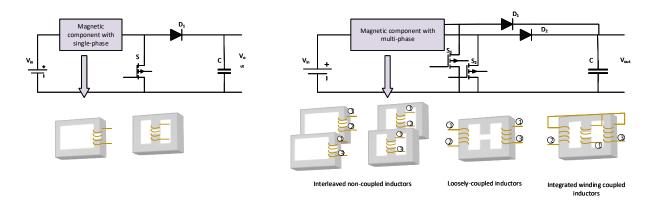

| Figure 1.2: | Different topologies of DC-DC boost converter                                             | 6  |

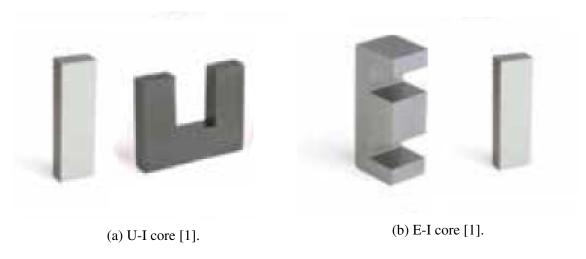

| Figure 2.1: | Several designs of magnetic core                                                          | 10 |

| Figure 2.2: | Toroid core [1]                                                                           | 11 |

| Figure 2.3: | Two-different shapes of magnetic core                                                     | 12 |

| Figure 3.1: | The basic cells method                                                                    | 14 |

| Figure 3.2: | The electric field line between two turns                                                 | 15 |

| Figure 3.3: | The electric filed lines between turns                                                    | 18 |

| Figure 3.4: | The cross section of the core geometry                                                    | 19 |

| Figure 3.5: | The electric field lines of lateral region                                                | 20 |

| Figure 3.6: | The electric field lines between turn and core.                                           | 21 |

| Figure 3.7: | The lamped capacitance network                                                            | 23 |

| Figure 4.1: | Models of an inductor                                                                     | 28 |

| Figure 4.2: | Characteristic impedance of an inductor with parasitic capacitance included in the model. | 28 |

| Figure 4.3: | Approximation shape of rod conductor                                                      | 31 |

| Figure 4.4: | U-I core with approximation shape of rod conductor                                        | 32 |

| Figure 4.5: | High frequency circuit of an inductor with magnetic core.                                 | 32 |

| Figure 4.6: | Simplified high frequency circuit of an inductor with magnetic core                       | 33 |

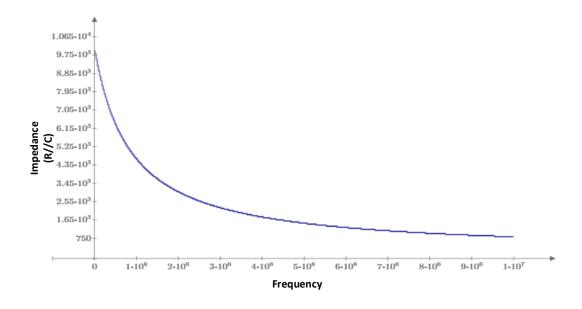

| Figure 4.7: | Curve of impedance versus frequency.                                                      | 33 |

| Figure 4.8: | The parasitic capacitance model of U-I core                                               | 34 |

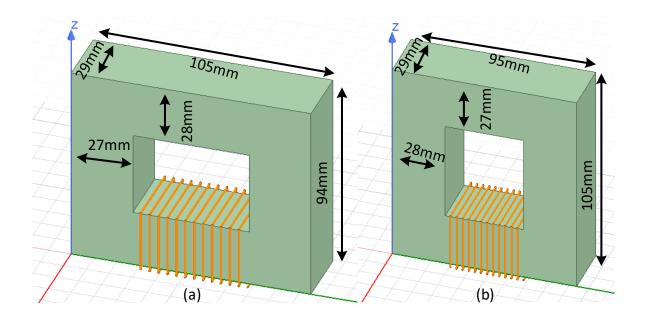

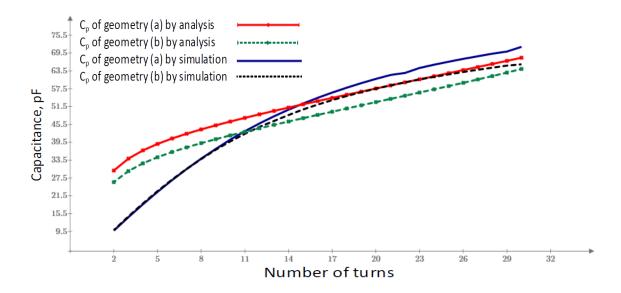

| Figure 4.9:  | Dimension of two geometries                                                                                                                   | 39 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

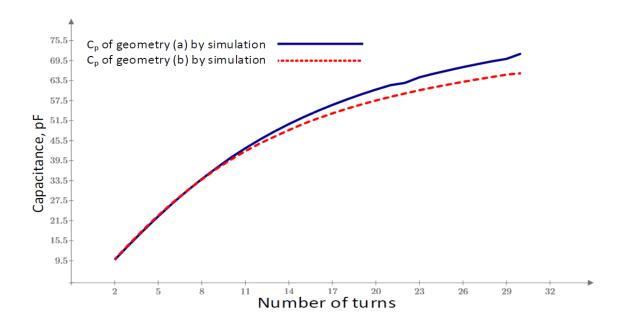

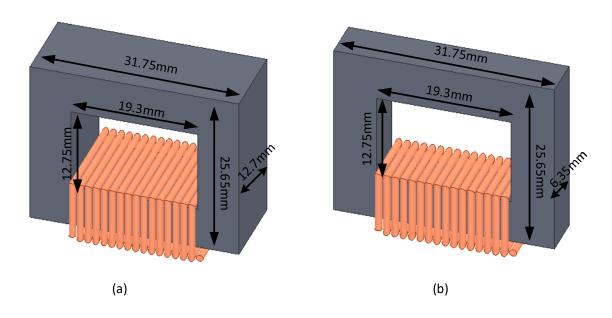

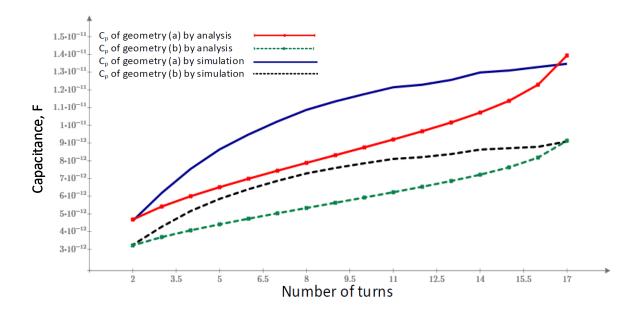

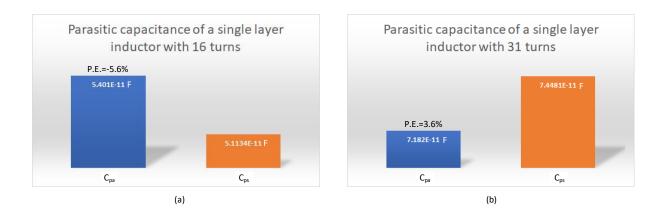

| Figure 4.10: | Parasitic capacitance versus number of turns by Electrostatic simulation                                                                      | 40 |

| Figure 4.11: | Parasitic capacitance versus number of turns by electrostatic simulation and analytical model                                                 | 41 |

| Figure 4.12: | Percentage of error of two geometries                                                                                                         | 41 |

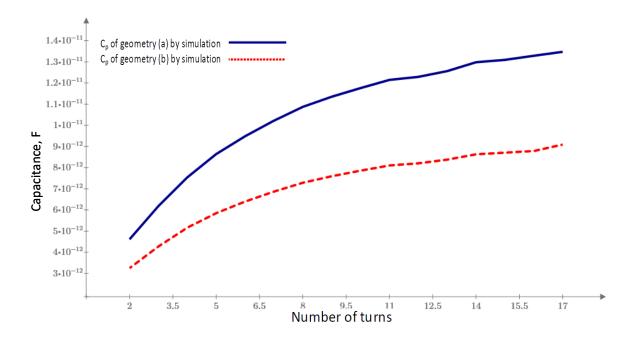

| Figure 4.13: | Dimension of two different inductors with same size but different volume                                                                      | 42 |

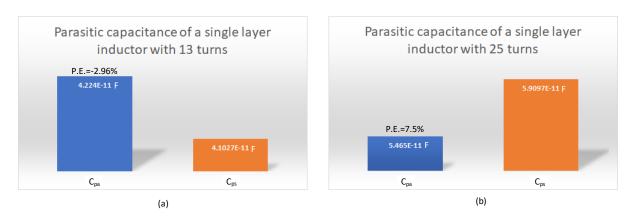

| Figure 4.14: | Parasitic capacitance versus number of turns by Electrostatic simulation                                                                      | 42 |

| Figure 4.15: | Parasitic capacitance versus number of turns by electrostatic simulation and analytical model                                                 | 43 |

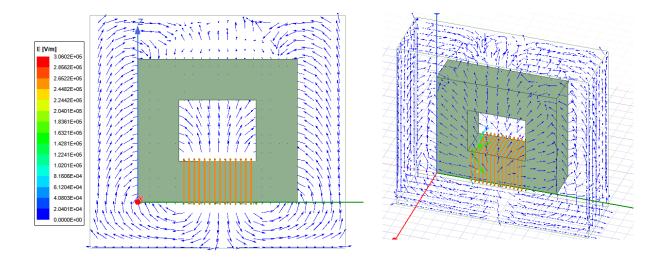

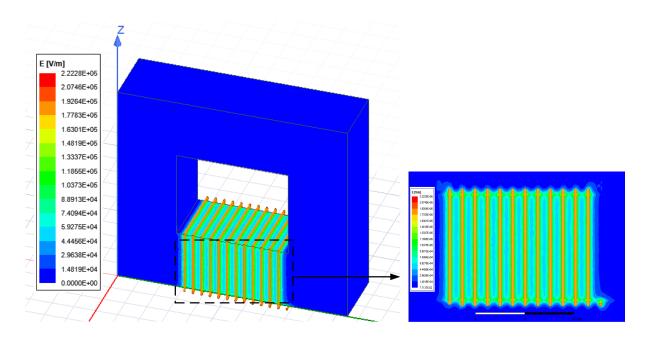

| Figure 4.16: | Electric field and fringing effects in ANSYS maxwell software                                                                                 | 43 |

| Figure 4.17: | Electric field of a single layer inductor with magnetic core                                                                                  | 45 |

| Figure 4.18: | Comparison of geometry with long central limb.                                                                                                | 45 |

| Figure 4.19: | Comparison of geometry with short central limb.                                                                                               | 46 |

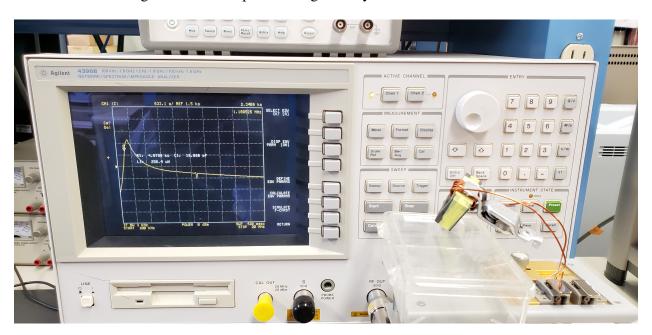

| Figure 4.20: | Impedance Network Analyzer device.                                                                                                            | 46 |

| Figure 4.21: | Comparison of geometry with long central limb between experiment, simulation, and analytical results.                                         | 47 |

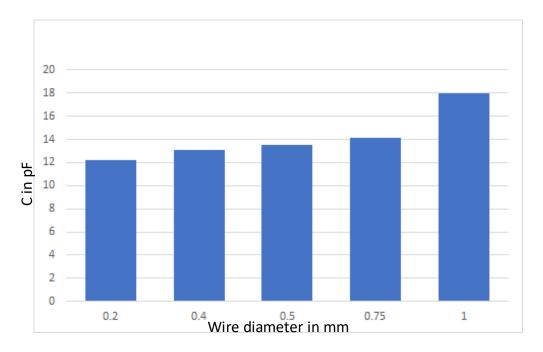

| Figure 5.1:  | The parasitic capacitance of the 20 turn inductor with different wire diameter. The wire with $1mm$ diameter is wounded close to the core     | 50 |

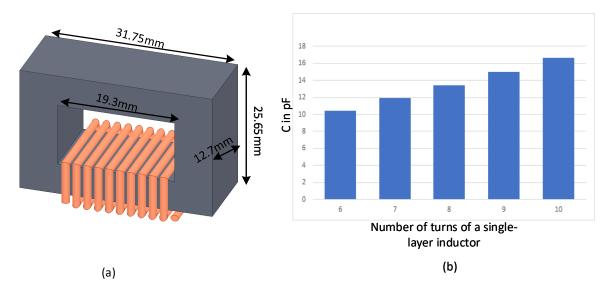

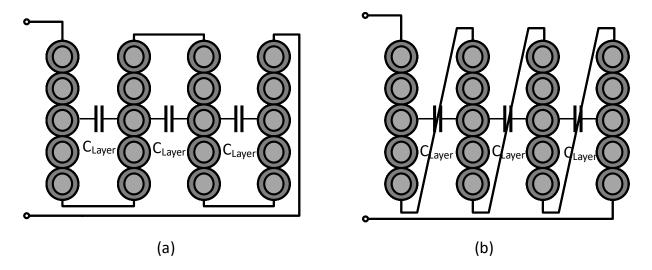

| Figure 5.2:  | (a) The single-layer inductor with 10 turns. (b) The parasitic capacitance of the single-layer inductor in (a) with different number of turns | 51 |

| Figure 5.3:  | (a) Multi-layer Standard winding. (b) Multi-layer fly back winding                                                                            | 52 |

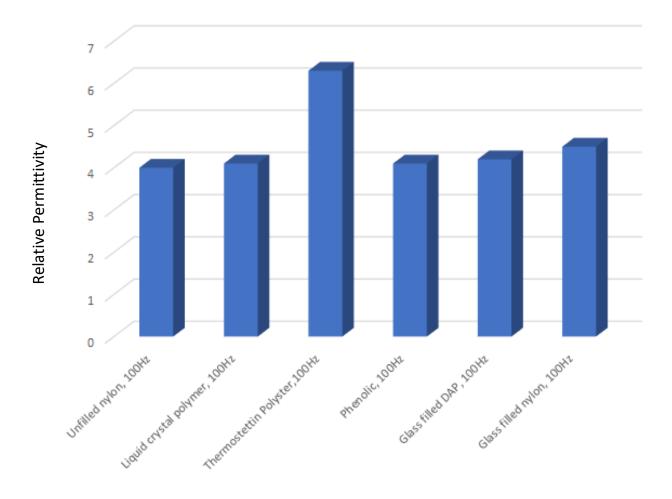

| Figure 5.4:  | The relative permittivity of different bobbins                                                                                                | 53 |

| Figure 5.5:  | The parasitic capacitance of an inductor with different bobbins                                                                               | 55 |

| Figure 5.6:  | The single turn inductor with magnetic core and PET bobbin material                                                                           | 56 |

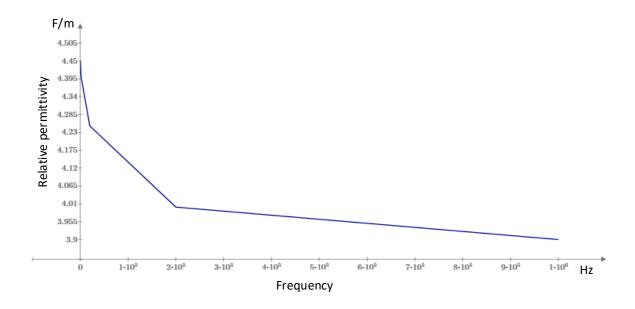

| Figure 5.7:  | The relation between the frequency and the relative permittivity of the PET bobbin material                                                   | 56 |

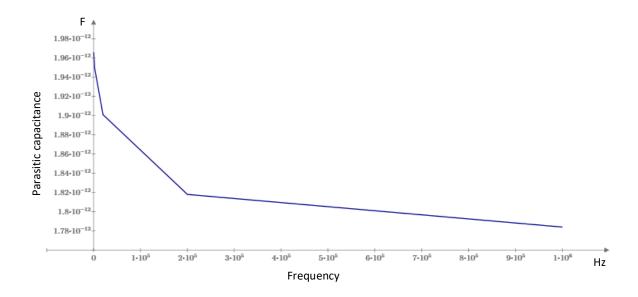

| Figure 5.8:  | bobbin versus frequency                                                                                                                                                          | 57 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

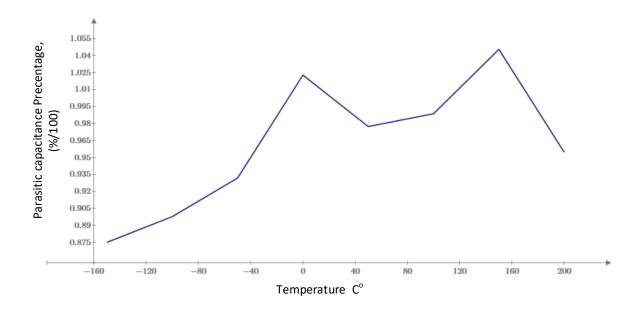

| Figure 5.9:  | The parasitic capacitance percentage of the single turn inductor with PET bobbin versus the temperature                                                                          | 58 |

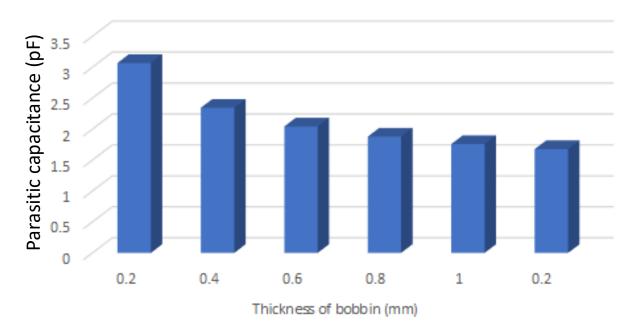

| Figure 5.10: | Thicknesses of the bobbin versus the parasitic capacitance                                                                                                                       | 59 |

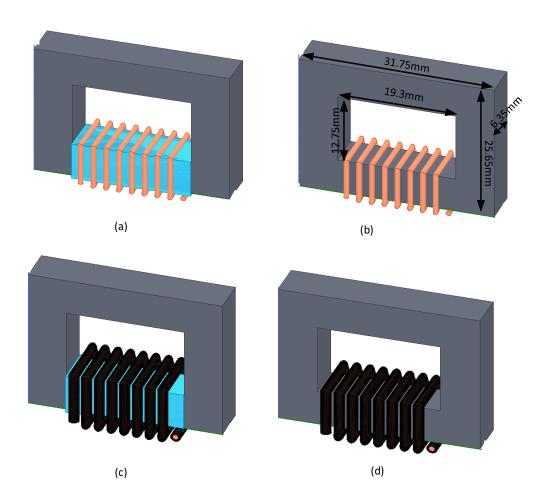

| Figure 5.11: | (a) the inductor with magnet wire and PET bobbin, (b) the inductor with magnet wire, (c) the inductor with insulated wire and PET bobbin, (d) the inductor with insulated wire   | 61 |

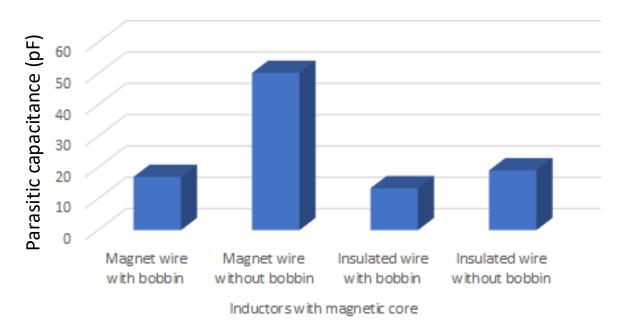

| Figure 5.12: | The parasitic capacitances of the four inductors with different wires and with/without bobbins                                                                                   | 62 |

| Figure 6.1:  | A flowchart of methods to reduce the size of magnetic components                                                                                                                 | 65 |

| Figure 6.2:  | A flowchart of methods to reduce the size of magnetic components                                                                                                                 | 66 |

| Figure 6.3:  | A flowchart of methods to reduce the size of magnetic components                                                                                                                 | 67 |

| Figure 6.4:  | A flowchart of methods to reduce the size of magnetic components                                                                                                                 | 68 |

| Figure 6.5:  | A flowchart of methods to reduce the size of magnetic components                                                                                                                 | 69 |

| Figure 6.6:  | A flowchart of methods to reduce the size of magnetic components                                                                                                                 | 69 |

| Figure 6.7:  | A flowchart of methods to reduce the size of magnetic components                                                                                                                 | 70 |

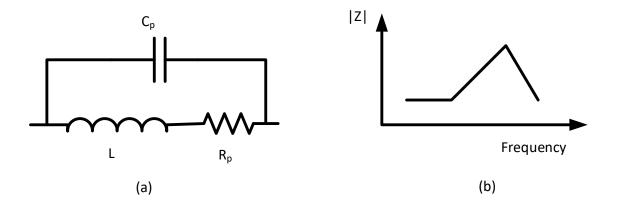

| Figure 7.1:  | (a) Inductor model of parasitics (b) The impedance curve of an inductor versus frequency.                                                                                        | 74 |

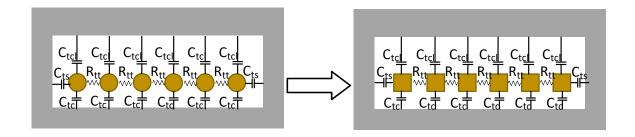

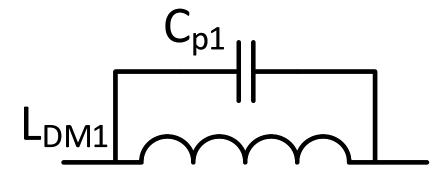

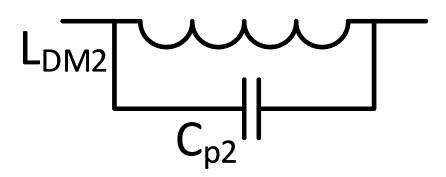

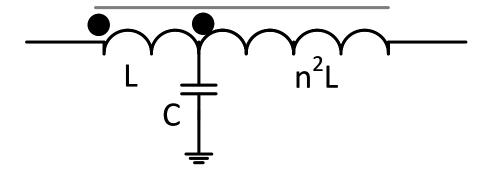

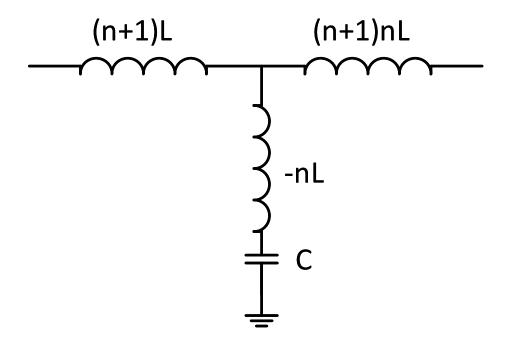

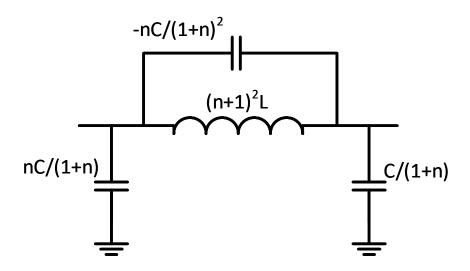

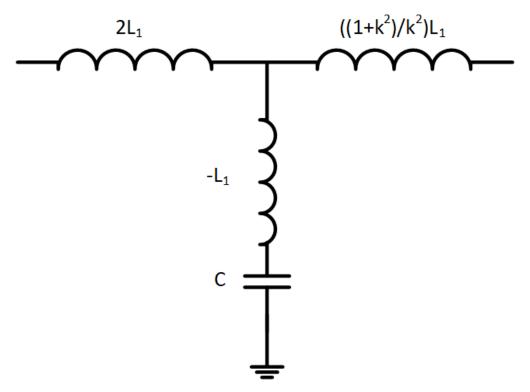

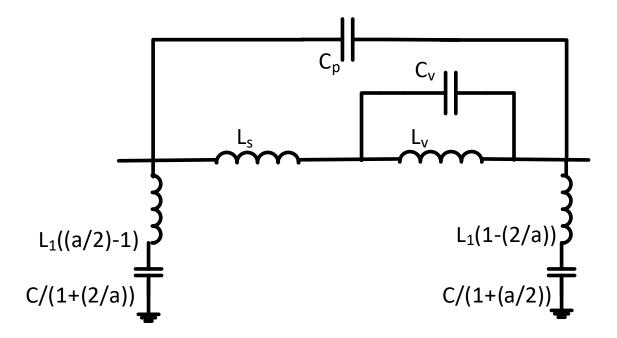

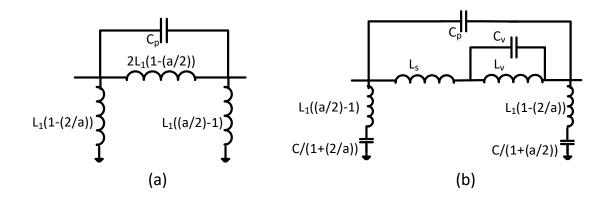

| Figure 7.2:  | The direct coupled windings with adding small capacitor                                                                                                                          | 75 |

| Figure 7.3:  | The decoupled mutual inductance with magnetic coupling coefficient                                                                                                               | 75 |

| Figure 7.4:  | The $\pi$ model of decoupled mutual inductance with $k$ and the addition small capacitor                                                                                         | 76 |

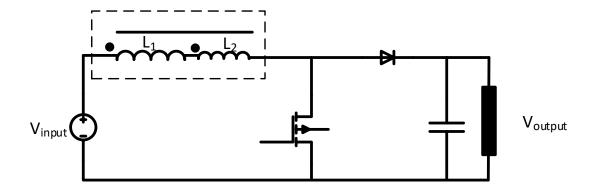

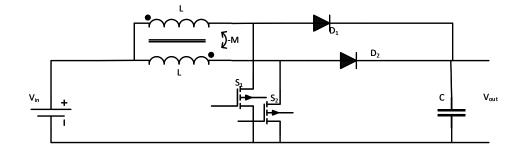

| Figure 7.5:  | The boost converter with mutual inductance                                                                                                                                       | 79 |

| Figure 7.6:  | (a) The mutual inductance and magnetic coupling coefficient without additional capacitor. (b) The mutual inductance and magnetic coupling coefficient with additional capacitor. | 79 |

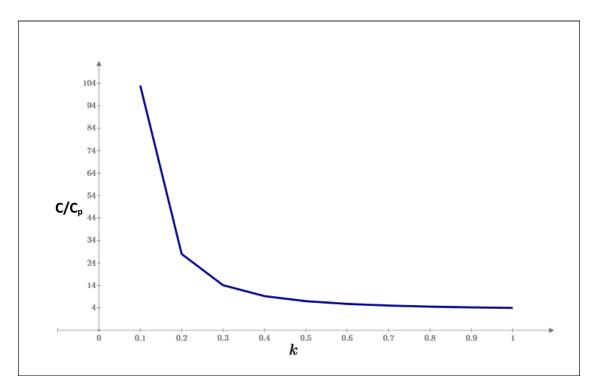

| Figure 7.7:  | coupling coefficient                                                                                                                                                                                           | 80 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

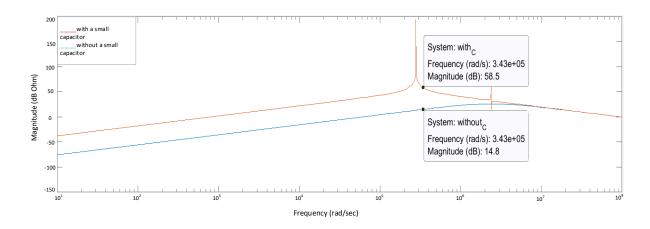

| Figure 7.8:  | The bode diagram of comparison between with and without additional capacitor when $k = 0.97 \dots \dots$ | 83 |

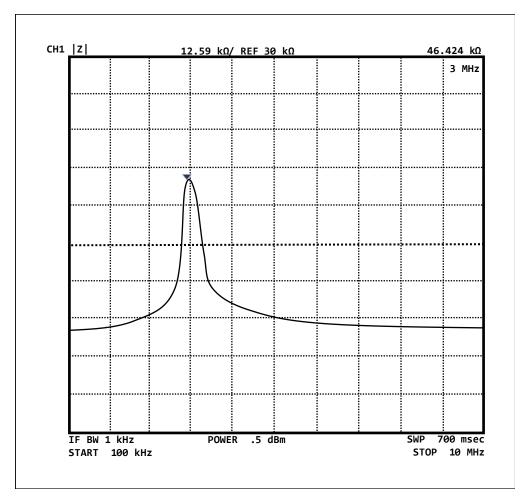

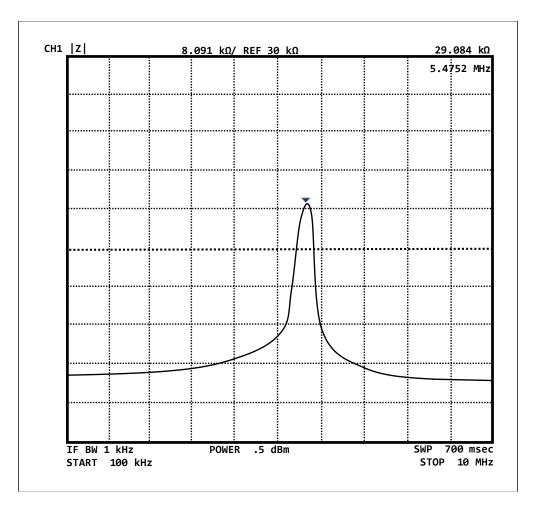

| Figure 7.9:  | The Network Analyzer results of the coupled inductor without applying the parasitic capacitance cancellation                                                                                                   | 83 |

| Figure 7.10: | The Network Analyzer results of the coupled inductor with applying the parasitic capacitance cancellation                                                                                                      | 84 |

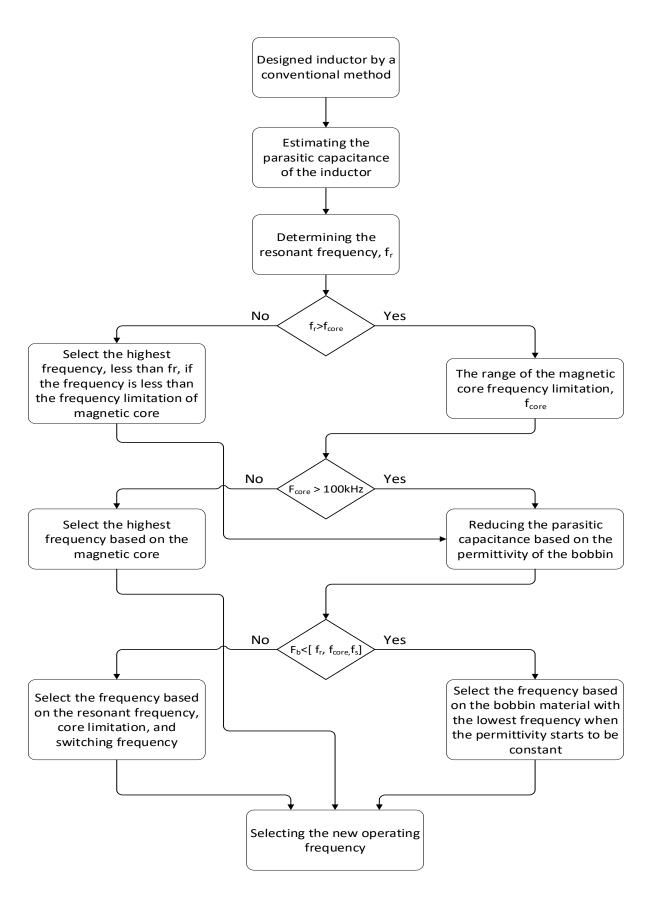

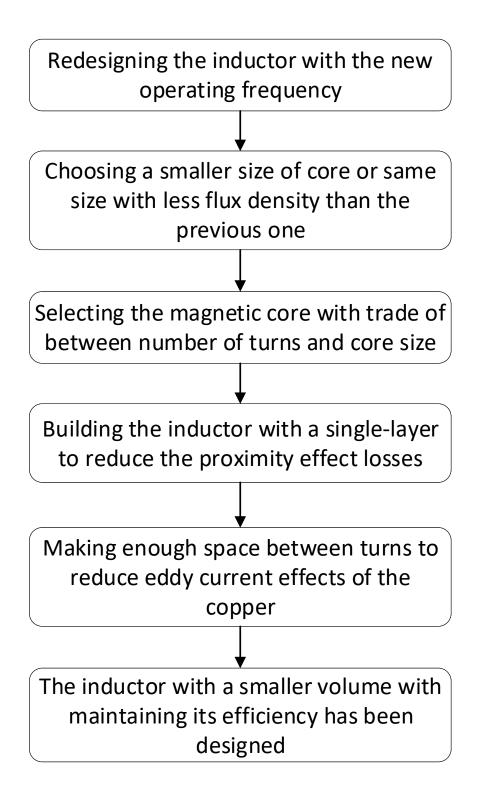

| Figure 8.1:  | The flowchart process of selecting the operating frequency range                                                                                                                                               | 89 |

| Figure 8.2:  | The inductor behavior with increasing the operating                                                                                                                                                            | 90 |

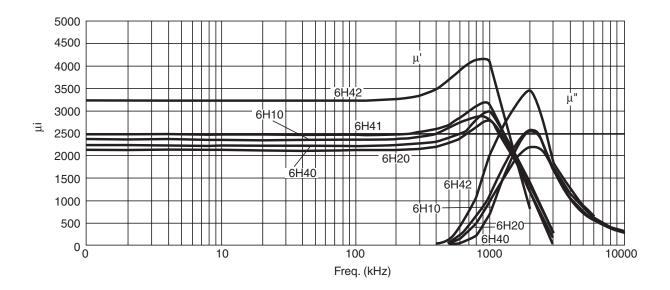

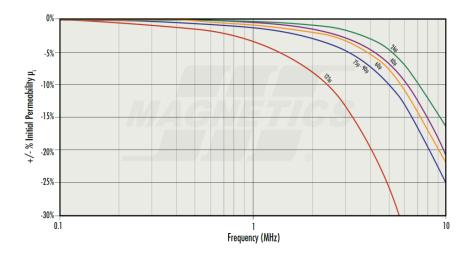

| Figure 8.3:  | The permeability curves of different magnetic core materials versus frequency 9                                                                                                                                | 91 |

| Figure 8.4:  | The voltage and current versus frequency for different switches                                                                                                                                                | 93 |

| Figure 8.5:  | The flowchart process for selecting the appropriate number of turns and the volume of the new inductor                                                                                                         | 96 |

| Figure 8.6:  | The Kool Mu powder core permeability versus the frequency [2]                                                                                                                                                  | 97 |

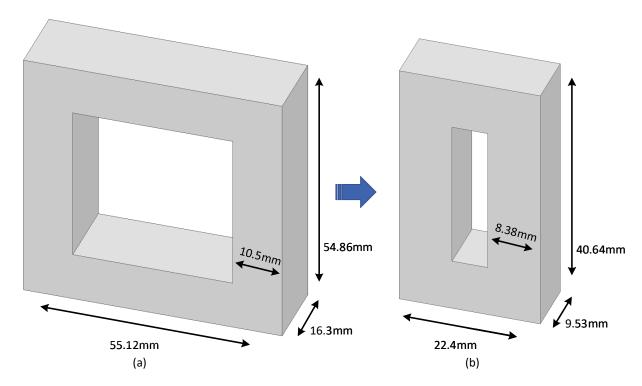

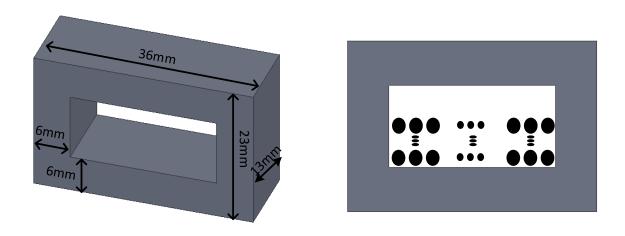

| Figure 8.7:  | (a) The magnetic core dimensions of the conventional inductor, (b) The magnetic core dimensions of the new inductor                                                                                            | 98 |

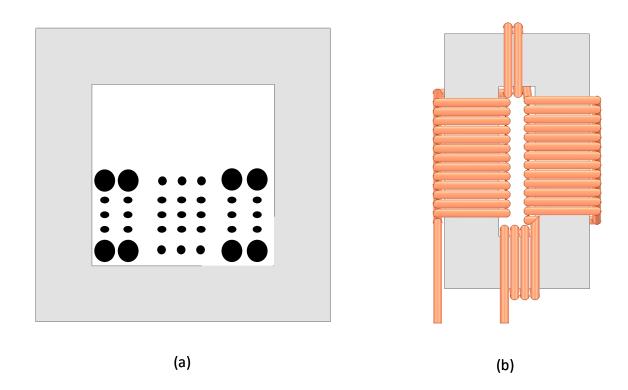

| Figure 8.8:  | • • • •                                                                                                                                                                                                        | 99 |

| Figure 8.9:  | (a) The volume comparison between the conventional inductor and the new inductor. (b) The power losses of both the conventional inductor and the new inductor                                                  | 00 |

| Figure 8.10: | The conventional inductor with milt-layer and N49 Ferrite core                                                                                                                                                 | 00 |

| Figure 8.11: | The new inductor with a single-layer and N49 Ferrite core                                                                                                                                                      | )1 |

| Figure 8.12: | (a) The volume comparison between the conventional inductor and the new inductor. (b) The power losses of both the conventional inductor and the new inductor                                                  | 01 |

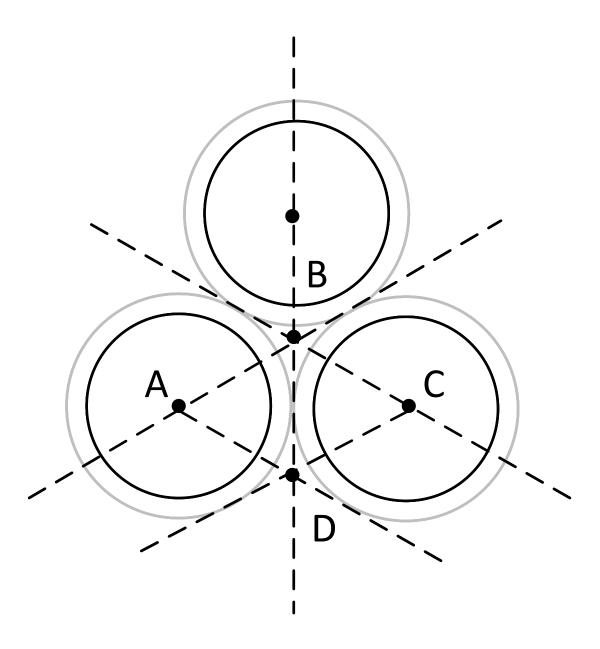

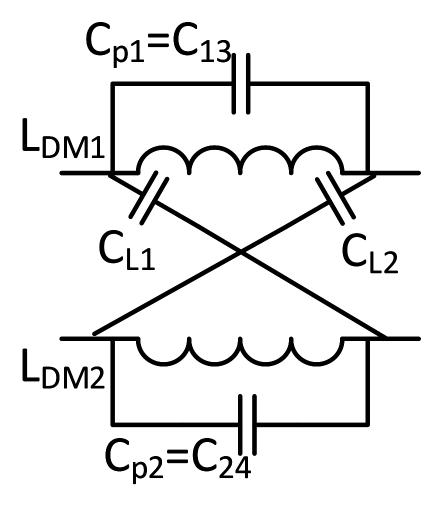

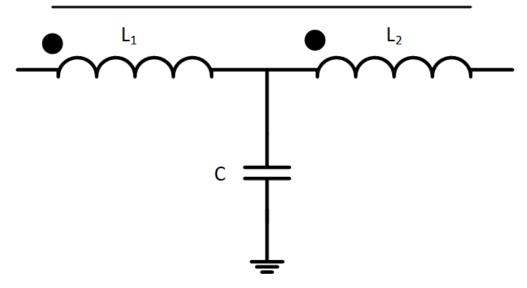

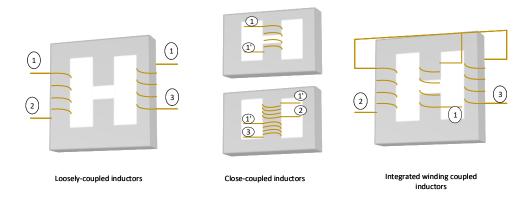

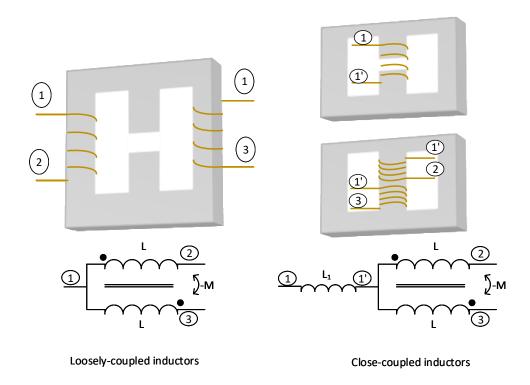

| Figure 9.1.  | Different types of two-phase coupled inductors                                                                                                                                                                 | 74 |

| Figure 9.2:  | is on the right                                                                                                                                           |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 9.3:  | The single-layer loosely-coupled inductors with the parasitic capacitance network                                                                         |

| Figure 9.4:  | The single-layer closed-coupled inductors with the parasitic capacitance network                                                                          |

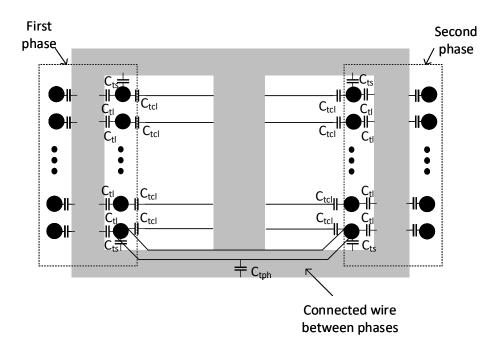

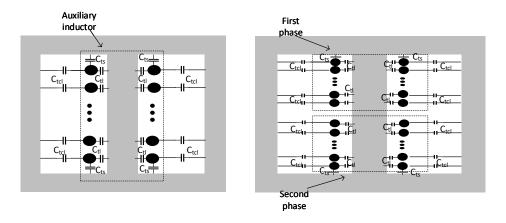

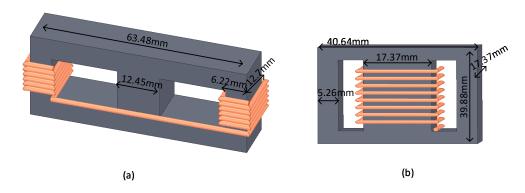

| Figure 9.5:  | (a) The geometry of the multi-phase loosely-coupled inductors. (b) The geometry of the multi-phase closed-coupled inductors without an auxiliary inductor |

| Figure 9.6:  | The comparison results of the multi-phase LCI between the modeling approach and the electrostatic model with FEA                                          |

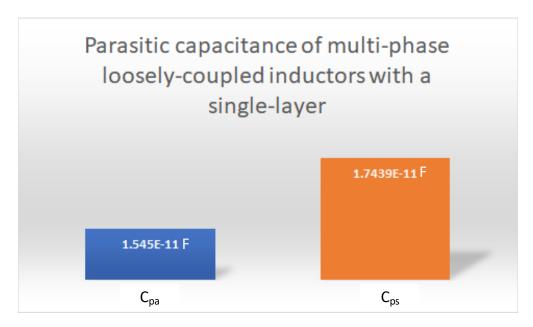

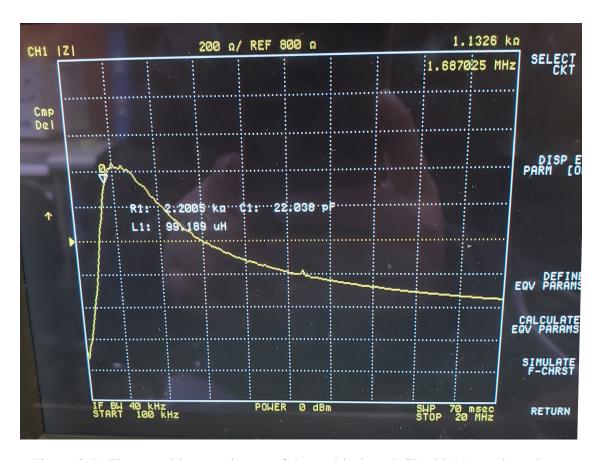

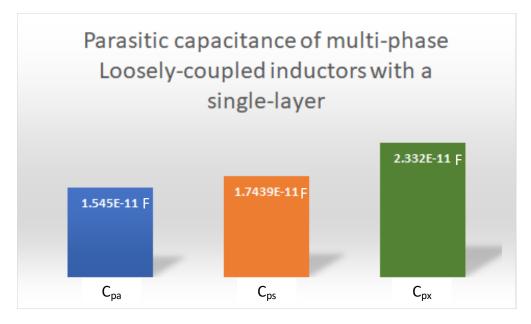

| Figure 9.7:  | The parasitic capacitance of the multi-phase LCI with Network analyzer 112                                                                                |

| Figure 9.8:  | The comparison results of the multi-phase LCI between the modeling approach and the electrostatic model with FEA                                          |

| Figure 9.9:  | The comparison results of the multi-phase CCI between the modeling approach and the electrostatic model with FEA                                          |

| Figure 9.10: | The parasitic capacitance of the multi-phase CCI with Network analyzer 113                                                                                |

| Figure 9.11: | The comparison results of the multi-phase CCI between the modeling approach and the electrostatic model with FEA                                          |

| Figure 9.12: | (a) The direct coupled inductors. (b) The inverse coupled inductors                                                                                       |

| Figure 9.13: | The interleaved boost converter with two-phase coupled inductors                                                                                          |

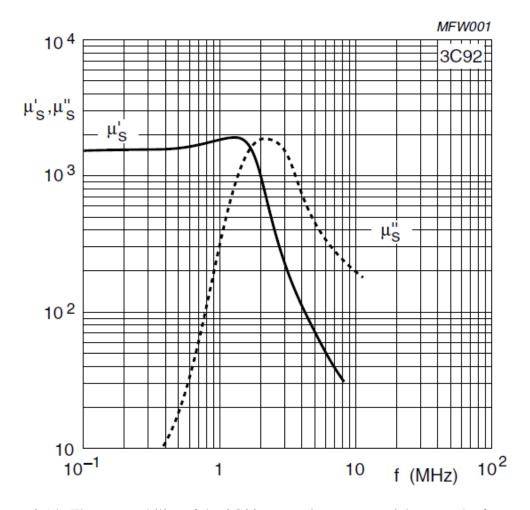

| Figure 9.14: | The permeability of the 3C92 magnetic core material versus the frequency 119                                                                              |

| Figure 9.15: | The volume comparison between the conventional LCI inductor and the new LCI inductor designed                                                             |

| Figure 9.16: | The conventional LCI inductor with 50 $kHz$ is on the left while the new inductor designed with 100 $kHz$ is on the right                                 |

| Figure 9.17: | The percentage of reducing each component of the interleaved coupled boost converter compared with the conventional converter                             |

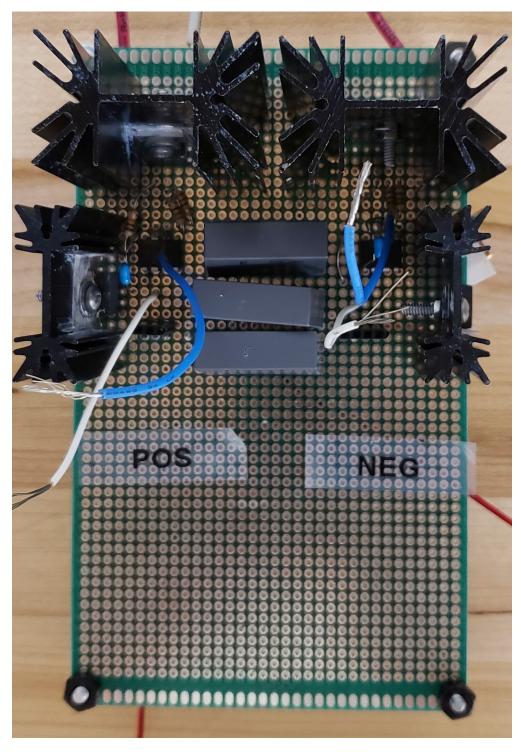

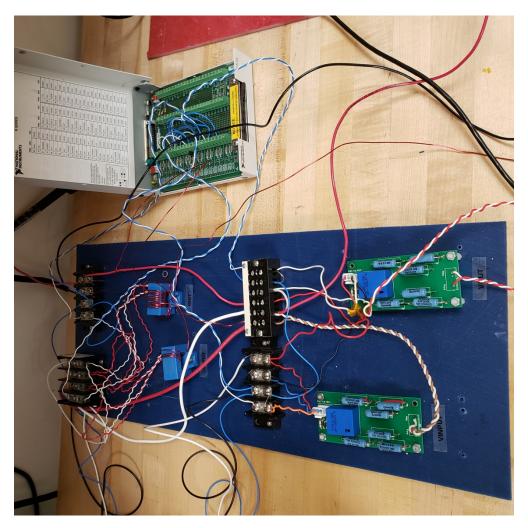

| Figure 9.18: | The circuit components of the interleaved boost converter                                                                                                 |

| Figure 9.19: | The measurement setup of the experiment                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------|

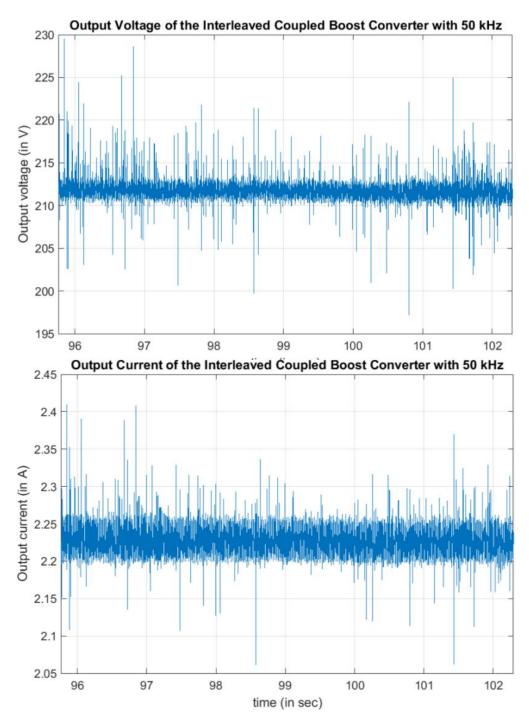

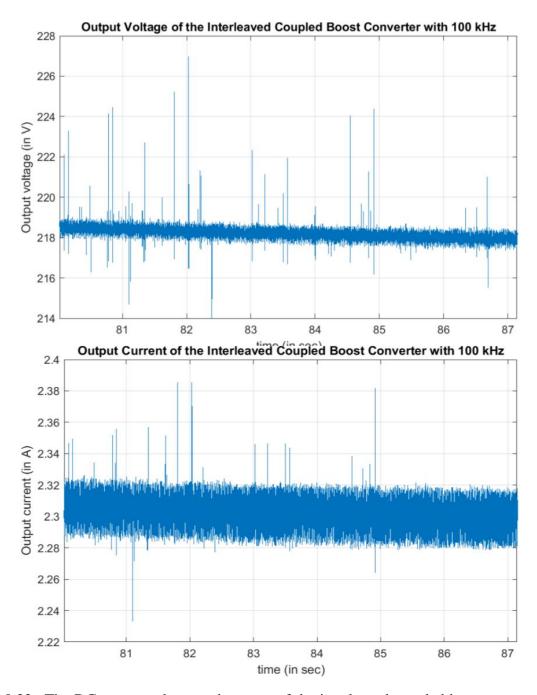

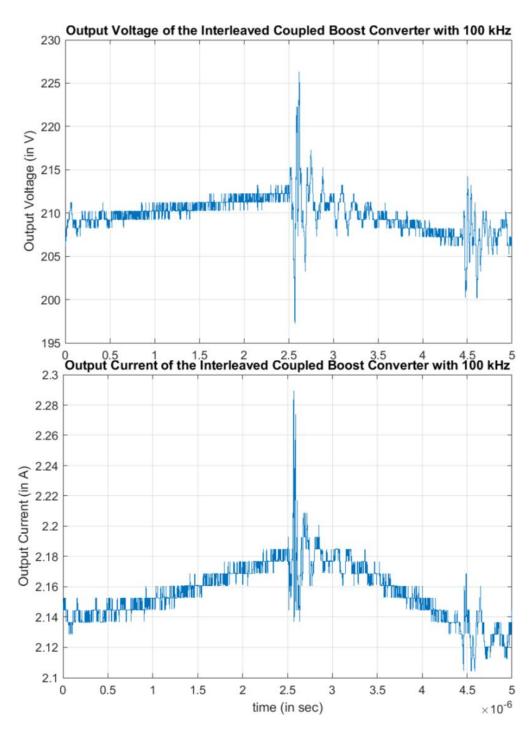

| Figure 9.20: | The DC output voltage and current of the interleaved coupled boost converter with $50 \ kHz$             |

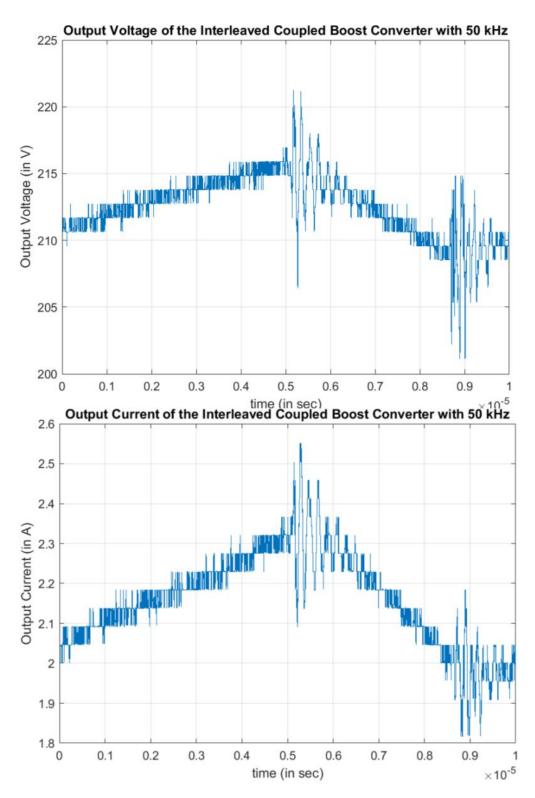

| Figure 9.21: | The cycle outputs of the voltage and current of the interleaved coupled boost converter with $50 \ kHz$  |

| Figure 9.22: | The DC output voltage and current of the interleaved coupled boost converter with $100 \ kHz$            |

| Figure 9.23: | The cycle outputs of the voltage and current of the interleaved coupled boost converter with $100 \ kHz$ |

| Figure 9.24: | The efficiency of both The interleaved coupled converters                                                |

#### CHAPTER 1

#### INTRODUCTION

In this chapter, the main aspects of improving the magnetic components are presented. For power electronic systems, different methods can be applied to improve efficiency [3–10]. Besides improving the efficiency of magnetic components, an overview of downsizing techniques of the size of the magnetic components is introduced. The research scope and summary of contributions are presented.

### 1.1 Motivation and Challenge

The main objectives of power converters are to have high efficiency and to also reduce the size of converters. Reducing the size of the converter can be achieved by coupling the magnetic components and/or increasing the switching frequency [3,5,8–10]. By coupling the magnetic components, the losses of conductors and magnetic materials are decreased, besides reducing the size of converters [4,8–10]. The switching frequency of power converters is the main aspect of reducing the size of magnetic components and devices of the converters [3,5,8]. However, by reducing the volume of power converters at high frequencies, the efficiency and performance of power electronic systems are reduced [11–17]. One of the main reasons for reducing the efficiency of power converters at high frequency is the effects of parasites of magnetic components [11, 12, 14, 15, 17–22].

Magnetic components of power converters such as inductors, choke inductors, interleaved coupled inductors, and transformers have parasitic elements that appear at high frequency [14, 17, 18]. There are two types of parasites of magnetic components, they are parasitic capacitance and parasitic resistance. Conductor and magnetic losses, eddy and proximity currents cause the parasitic resistance. The parasitic capacitance can be caused by capacitances between turn-to-turn, layer-to-layer, and winding-to-core [14, 17, 18, 21, 22]. Because of the parasitic capacitance of magnetic components, the efficiency of the power converter is reduced at high frequency. Also, it is the reason why the magnetic components have a resonant frequency, which will cause

electromagnetic interference [18]. Therefore, this research aims to model the parasitic capacitance of magnetic components in order to avoid operating and designing the power converters at the resonant frequency and also around it.

The modeling of the parasitic capacitance of magnetic components has been a major and challenging research area for decades, and is considered in the following classification [12, 14, 15, 17–22]:

- Single-layer inductors with conductive core for applications of very high frequencies such as EMI filters.

- Single-layer inductors with air-core at high frequency.

- Multi-layers inductors with high frequency.

- High frequency transformer applications.

To improve the modeling and calculations of the parasitic capacitance of magnetic components, the operating frequency of power converters should be divided in specific categories. There are three ranges of frequency that can be applied to power converters, they are: low frequency range (the parasitic capacitance does not affect the inductor behavior), medium frequency range (the characteristic of an inductor starts to get affected until the frequency reaches the first resonant frequency), and high frequency range (frequencies above the first resonant frequency such as radio frequency and EMI filter applications). The existing methods of modeling the parasitic capacitance for the single-layer inductors with magnetic core have some issues that do not work properly for the power converter with medium power range and medium frequency range. Some issues of existing methods of modeling the parasitic capacitance for single-layer inductors with magnetic core are the methods have no relationship between the number of turns and the parasitic capacitance while the experiment and simulation results show a relationship between them. Another issue of the existing methods of parasitic capacitance is the distance between turns and the core are not included. Because of the quick developments of switching frequency technology for medium and high power

converters, this research focuses on medium frequency range with medium power range to model the parasitic capacitance. The modeling of parasitic capacitance of this research concentrates on the single-layer inductors with magnetic core.

Figure 1.1: A flowchart of methods to reduce the size of magnetic components.

Figure 1.1 shows the flowchart of the methods for reducing the size and volume of power electronic systems. The flowchart presents the main advantages and disadvantages of each method of reducing the size of power converters.

Another objective of power converters in high frequency is improving the efficiency of power converters. It is essential to improve the efficiency of the magnetic components in the power converter. There are two ways to improve the performance of magnetic components. The magnetic components can be improved by reducing the losses of their material [3, 12, 23–25]. Another

method to improve the efficiency is by reducing the parasitic capacitance of magnetic components [11,26–31].

Reducing the parasitic capacitance of magnetic components has been a challenging area for decades [11, 26–31]. The techniques of reducing the parasitic capacitance are applied based on the applications [28]. Improving the method of reducing the parasitic capacitance is essential for power converter applications.

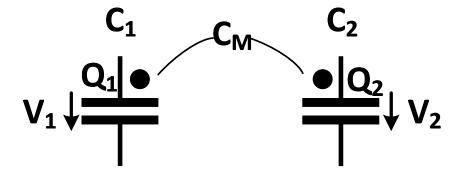

There are two main methods of reducing the parasitic capacitance. Using the mutual capacitance between two inductors can be applied to reduce the parasitic capacitance of inductors [27, 28]. Another method of reducing the parasitic capacitance is by utilizing the mutual inductance. Using the mutual inductance with adding a small capacitor can generate a negative capacitance [26, 28, 30–33]. The negative capacitance can reduce the parasitic capacitance of the coupled inductors. Estimating the appropriate value of the small capacitor is an essential topic to reduce the parasitic capacitance. This research focuses on estimating the value of the small capacitor when the coupled inductors are not perfectly coupled  $k \neq 1$  to reduce the parasitic capacitance by generating the negative capacitance.

The estimating of the parasitic capacitance for the magnetic components can lead to the design of the power converter with reducing the total size of the converter. By selecting the appropriate speed of the switching frequency based on estimating the parasitic capacitance value with considering the resonant frequency of the magnetic components, The capacitor value and the number of turns of the magnetic components of the power converter can be reduced with increasing the switching frequency. The losses of the magnetic components are reduced through decreasing the number of turns of the magnetic components which yields to improve the efficiency of the power converter. As a result of improving the magnetic components of power converters at high frequency, the power converter should be designed to achieve a smaller size with maintaining the efficiency. To maintain the performance with reducing the size of the power converter for medium power applications, the two methods of reducing the size of the converter can be applied.

Recently, many researches focused on the applications of electric vehicles to improve the

efficiency and to reduce the size of the power converters [4, 7–10, 34–37]. One of the major issues in the electric vehicle is the volume of the electric power-train [4,7,38,39]. The effective technique to reduce the volume and size of the electric power-train is downsizing the DC-DC converter that is located between the storage unit and motor inverter [4,7,38–40]. The DC-DC boost converter can be applied in different topologies as shown in Figure 1.2. The effective topology that can reduce the total size of the DC-DC converter is the multi-phase boost converter with interleaved coupled inductors [4]. However, reducing the size of the multi-phase boost converter by coupling the inductors can be downsized more by considering the estimating value of the parasitic capacitance to operate it at a specific frequency. It is essential to estimate the parasitic capacitance based on the proposed method of determining the parasitic capacitance for medium power and medium frequency range, which concentrates on the single-layer inductors with a magnetic core, while all the existing methods of determining the parasitic capacitance for single-layer inductors with a magnetic core focus on low power application with high frequency. Moreover, the existing methods of determining the parasitic capacitance for single-layer inductors with a magnetic core have the main disadvantage that is there is no relationship between the parasitic capacitance and the number of turns, even if the experiment and simulation results show the relationship between the number of turns and the parasitic capacitance as presented in [12, 41, 42]. Also, the relationship between the parasitic capacitance and the distance between turns and a core is not included in the existing methods of determining the parasitic capacitance of the single-layer inductors with the magnetic core while the proposed method has a relation between the parasitic capacitance and the distance between turns and the core. For these reasons, estimating the parasitic capacitance of multi-phase inductors is essential and considered in this research by using the proposed method of determining the parasitic capacitance for single-layer inductors with a magnetic core.

As a result, the DC-DC interleaved boost converter will be designed based on the proposed estimating of the parasitic capacitance of the inductors with increasing the switching frequency. By increasing the switching frequency, the size of other components of the power converter will be reduced such as output capacitors, footprint of the printed circuit board which leads to saving the

board space, and the magnetic components.

Figure 1.2: Different topologies of DC-DC boost converter.

### 1.2 Problem Statement

As the technology of power switches develops, the power converter can operate at higher frequencies. These high frequencies create the likelihood of unwanted parasites such as parasitic capacitance in the magnetic components. It is imperative to model the parasitic capacitance to improve performance. For example, the parasitic capacitance can be reduced by using the proposed methods which leads to enhanced performance.

To reduce the size along with improving the performance of the power converter at high frequencies, a new methodology of selecting a proper high operating frequency is required. By properly selecting the suitable high operating frequency, the total volume of the power converter can be downsized while maintaining the efficiency. It is important to model and design the power converter and magnetic components in the early stages of designing to prevent cataclysmic ramifications in the converter.

# 1.3 Objective

The objective of this research is to minimize the losses of the magnetic components of the DC-DC power converter and to downsize the magnetic components by estimating and reducing the parasitic capacitance. Moreover, the DC-DC power converter can have a smaller size with

maintaining efficiency by selecting a suitable high operating frequency.

## 1.4 Research Scope and Contributions

The purpose of this research is to present a new approach of modeling the parasitic capacitance of magnetic components, the technique of reducing the parasitic capacitance of magnetic components, the new methodology of properly selecting a high operating frequency, and reducing the size of the interleaved boost converter with two-phase coupled inductors based on the modeling of the parasitic capacitance. The outcome of this work is to improve the performance of the power converter with reducing its total size. Improving the performance of the power converter can be done by selecting the proper high operating frequency which yields to reducing the number of turns, a magnetic core size of the magnetic components, the DC link input capacitor and output capacitor, and saving the board space. Then the losses of the magnetic components are reduced. Moreover, reducing the size of the total power converter can be done by reducing the magnetic core volume and the output capacitor value. The power converter should be designed based on estimating the value of the parasitic capacitance to select the appropriate switching frequency speed. The contributions of this research can be summarized in the following:

- Generalizing the frequency response of magnetic components based on the impedance of parasitic capacitance.

- Proposing a novel method to estimate the parasitic capacitance of power converters. To the

best knowledge of the author, this is the first approach of modeling the parasitic capacitance

of single-layer inductors for medium power.

- Generalizing the overall parameters affecting the parasitic capacitance of the magnetic components.

- Proposing a new technique of reducing the parasitic capacitance to estimate the generated negative capacitance based on the magnetic coupling coefficient.

- Proposing a new methodology of properly selecting a high operating frequency for the power converter which can offer reducing the magnetic components volume with maintaining the performance. To the best knowledge of the author, this is the first methodology of selecting the suitable high operating frequency with maintaining the efficiency.

- Estimating the parasitic capacitance of multi-phase inductors to design the power converter with coupling the magnetic components at high frequency.

### 1.5 Research Organization

The rest of this research is organized as follows. In chapter 2, overview of the magnetic components is presented. The existing methods of determining the parasitic capacitance for single-layer inductor with magnetic core is shown in chapter 3. The new modeling of the parasitic capacitance for single-layer inductor with magnetic core is introduced in chapter 4. The investigating of the overall parameters affecting the parasitic capacitance of magnetic components is introduced in chapter 5. In chapter 6, the techniques of reducing the parasitic capacitance are presented. The new technique of reducing the parasitic capacitance by using the mutual inductance is shown in chapter 7. In chapter 8, the new methodology of properly selecting the operating frequency of magnetic components for power converter is presented. The interleaved two-phase coupled-inductors boost converter with estimating the parasitic capacitance is shown in chapter 9. Finally, the conclusion and the future work are presented in chapter 10.

#### **CHAPTER 2**

#### MAGNETIC COMPONENTS IN POWER CONVERTER

In this chapter, The overall magnetic core materials for power electronic systems is presented. Different shapes of magnetic core with their applications are introduced.

### 2.1 Overview about the Magnetic Components

Magnetic components in power electronics have different shapes and materials based on the desired application. The magnetic components contain two parts, are the coil of winding and the magnetic core or air-core. The magnetic core is a piece of magnetic material that has magnetic permeability. The magnetic permeability is an important feature to select the appropriate core type [3,5,25]. The magnetic core can be made from two main material types, are ferromagnetic metal and ferrimagnetic compounds. Each type of magnetic material and shape has advantages and disadvantages which can be applied for certain applications with specific frequencies and watts.

Based on the desired application, the magnetic core shape is selected. The magnetic core has several shapes, is designed based on the reduced losses of eddy currents and hysteresis besides the magnetic permeability, usage of power, and frequency limit [1,25]. Figure 2.1 shows several different designs of magnetic core [1,25]. Some magnetic core designs can work with most power electronics applications such as toroid, E-I, and U-I cores.

### 2.1.1 Toroid Core

Toroid core or choke inductor is used widely in electric and electronic systems. In the power electronic systems, the inductor and transformer with toroid core are essential parts.

Toroid magnetic core is mainly applied for broadband transformers, common mode chokes, converter and inverter transformers, noise filters, pulse transformers. However, the power used for toroid should be at a low power and it can work with high frequency. Figure 2.2 shows inductor and transformer with toroid magnetic core.

Figure 2.1: Several designs of magnetic core

Figure 2.2: Toroid core [1].

#### 2.1.2 U-I Core & E-I Core

The other important magnetic core designs are E-I and U-I cores. The two types of the magnetic core are used widely in electrical, electronics, and power electronic systems. The main advantage of these magnetic core shapes is having a high saturation level besides low losses [2]. The main applications for E-I magnetic core are the interleaved converter for an electric vehicle, differential mode, power and telecoms inductors, as well as the power converter and inverter transformer. The power transformer applications are ideally using U-I magnetic core. Also, the U-I core is applied for high-frequency transformer applications in power electronics such as dc-dc converter with high frequency [2]. Figure ?? depicts two types of magnetic cores which are E-I core and U-I core.

### 2.1.3 Magnetic Core Selected

The main focus of this research is to improve the magnetic component efficiency in power converters. For this reason, three types of magnetic components are studied. Toroid core is chosen for canceling the parasitic capacitance to improve the converter with single-phase and high frequency. Other types of the magnetic core, which are E-I core and U-I core, are selected to study and model the parasitic capacitance for a single-layer inductor. The reason for modeling this type of magnetic core

Figure 2.3: Two-different shapes of magnetic core.

is because no paper has been modeled for this type of magnetic component, besides the increasing use of magnetic geometry with wide-bandgap technology.

#### **CHAPTER 3**

# EXISTING METHODS OF DETERMINING THE PARASITIC CAPACITANCE FOR SINGLE LAYER INDUCTORS

Inductors with a single layer are widely used in many applications. They can be used at any level of frequency range. However, the frequency response of inductors with magnetic core are different from the response of inductors with air core at high frequency. [13, 15, 17, 19, 22, 43]. The inductors with air core are mainly applied with high frequency applications while the inductors with magnetic core are preferred to be applied in low and medium frequency [13, 16, 18, 19, 21]. There are many researches on modeling the parasitic capacitance of single layer inductors with air-core [13, 19, 22, 43]. However, There exists a few models that consider modeling the parasitic capacitance of single layer inductors with magnetic core [15, 17, 22, 43, 44].

The parasitic capacitance of single layer inductors with a magnetic core are modeled for applications with high frequency (HF) and low power such as EMI filter, RF filter, and common-mode choke filter. It is important to study the techniques of modeling the parasitic capacitance for single layer inductors with a magnetic core at HF in order to determine a new approach of modeling the parasitic capacitance in medium frequency and medium power range.

The existing techniques of estimating the parasitic capacitance of single layer inductors with magnetic core focus on the parasitic capacitance between turns and the parasitic capacitance between turns and a core [15, 17, 22, 43, 44]. Most of these techniques are using toroid core to determine the parasitic capacitance. The distinguished methods of determining the parasitic capacitance of single layer inductors with magnetic core are presented in the following.

## 3.1 Basic cells method to determining the parasitic capacitance

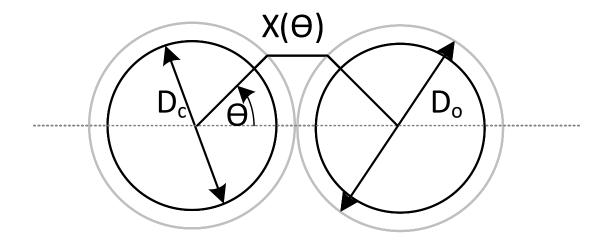

Massarini and Marian, the authors of "Self-Capacitance of Inductors", are the first scientists who made a method to predict the parasitic capacitance of inductors [17,43]. This method depends on the direction of the electric field lines. By applying the basic cells method as shown in Figure

3.1, the parasitic capacitance can be determined by a function of a few parameters.

Figure 3.1: The basic cells method.

This paper provides an approximated model to determine the parasitic capacitance. This model depends on the angle of electric field lines between adjacent turns. The turn-to-turn capacitance is

represented by  $C_{tt}$ .  $C_{tt}$  can be determined as following.

$$C_{tt} = \epsilon_o l_t \int_0^{\frac{\pi}{6}} \frac{1}{1 + \frac{1}{\epsilon_r} \ln \frac{D_o}{D_c} - \cos \theta}$$

$$2\epsilon_r \arctan \left[ \frac{\left( -1 + \sqrt{3} \right) \left( 2\epsilon_r + \ln \frac{D_o}{D_c} \right)}{\left( 1 + \sqrt{3} \right) \sqrt{\ln \frac{D_o}{D_c} \left( 2\epsilon_r + \ln \frac{D_o}{D_c} \right)}} \right]$$

$$= \epsilon_o l_t \frac{\sqrt{2\epsilon_r \ln \frac{D_o}{D_c} + \left( \ln \frac{D_o}{D_c} \right)^2}}{\sqrt{2\epsilon_r \ln \frac{D_o}{D_c} + \left( \ln \frac{D_o}{D_c} \right)^2}}$$

(3.1)

where the diameter of the conductor with and without the coating are represented by  $D_o$  and  $D_c$ , respectively. The length of a turn is  $l_t$ . The angle between two adjacent turns, which is represented by  $\theta$ , is shown in figure 3.2. Since the path lengths of the lines of the electric field between the turn and a core in the air gap are one half of the path lengths between two adjacent turns in the air gap, the parasitic capacitance between a turn and core can be approximated. The parasitic capacitance between a turn and core is denoted as  $C_{tc}$ .

$$C_{tc} = 2C_{tt} \tag{3.2}$$

Figure 3.2: The electric field line between two turns.

For a single-layer coil with a conductive core, the total parasitic capacitance can be approximated

based on the number of turns. If the number of turns are even and less than 10 turns, the parasitic capacitance can be determined as follows

$$C_s(n_{even}) = \frac{C_{tt}C_s(n_{even} - 2)}{2C_s(n_{even} - 2) + C_{tt}} + C_{tt}$$

(3.3)

where  $C_s$  is the total parasitic capacitance. The even number of turns can be represented by  $n_{even}$  while the odd number of turns is  $n_{odd}$ . The total parasitic capacitance of an inductor with odd number of turns that is less than 10 turns is expressed as follows.

$$C_s(n_{odd}) = \frac{C_{tt}C_s(n_{odd} - 2)}{2C_s(n_{odd} - 2) + C_{tt}} + C_{tt}$$

(3.4)

The total parasitic capacitance of any number of turns can be calculated. The following equation is to calculate the total parasitic capacitance.

$$C_s(n) = \frac{C_t t}{2 + \frac{C_{tt}}{C_s(n-2)}} + C_{tt}$$

(3.5)

The equation of calculating the total parasitic capacitance, which is represented in (3.5), becomes a convergent value after 10 turns. Therefore, the total parasitic capacitance can be as a constant value of inductors with more than 10 turns. The parasitic capacitance can be approximated as following.

$$C_s \cong 1.366C_{tt}, \ for \ n \ge 10$$

(3.6)

### 3.1.1 Advantages and Disadvantages

The new method of determining the parasitic capacitance of single-layer inductors with a magnetic core has several advantages as well as disadvantages. The following points represent the advantages of this method.

• This paper is considered to be the first analytical method that focuses on determining the parasitic capacitance.

- The analytical method is applied to applications with high frequency.

- A few parameters can determine the parasitic capacitance.

- The accuracy of this method's result is good compared with the experimental's.

While there are advantages in this method, there are disadvantages as well. The following points summarize the drawbacks of this method.

- This method can not estimate the parasitic capacitance of applications with frequencies lower than the first resonant frequency.

- The space between turns can not be increased in this method.

- There is no distance included between turns and core.

- The parasitic capacitance of any inductors is constant when the number of turns goes over 10 turns.

- There is no relationship between the number of turns and the parasitic capacitance.

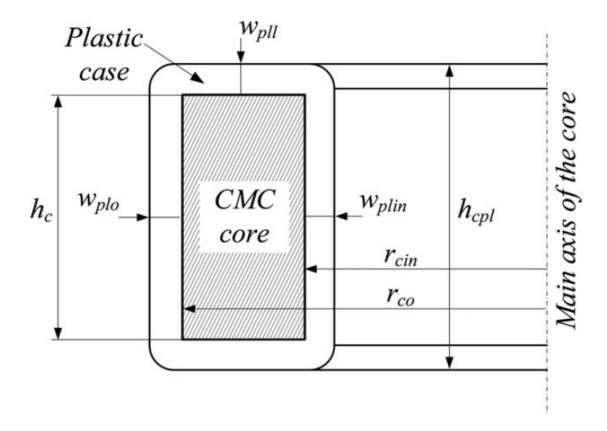

## 3.2 Modeling the Parasitic Capacitance of Common-Mode Choke

The paper for modeling the parasitic capacitance of common-mode choke is proposed in [15]. This model is an extension to the method of estimating the parasitic capacitance with high frequency applications in [17,43]. The contribution of this model is to calculate the parasitic capacitance of common-mode choke when there is distance between turns and between a turn to core.

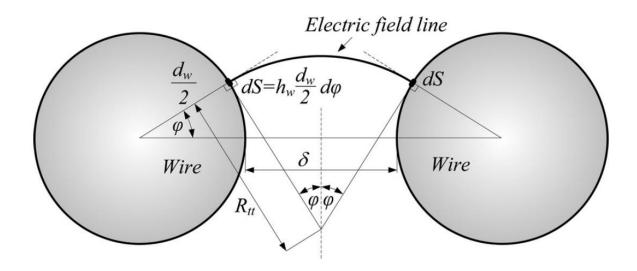

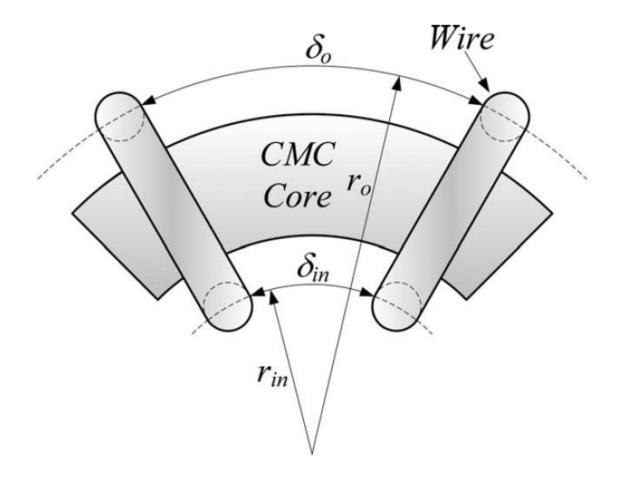

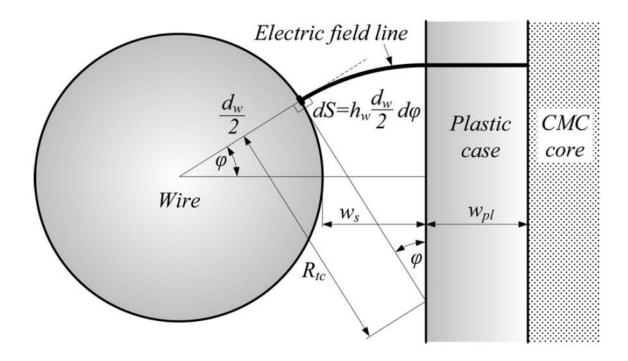

The proposed model is based on determining the electric field lines between turns as well as between a turn and core. Figure 3.3 shows the electric filed lines between turns. The electric filed lines can be approximated as a circular arc, where the end of the circular arc is perpendicular to the surface of a conductor. In order to calculate the capacitance between turns and between a turn to core, three different regions are analyzed that are known as the inner, outer, and lateral regions. The inner and outer regions have different arc lengths between turns that are  $\delta_{in}$  and  $\delta_{o}$ , respectively.

Figure 3.3: The electric filed lines between turns.

The radius of the inner and outer arc of the electric field lines are  $R_{ttin}$  and  $R_{ttout}$ .  $R_{ttin}$  can be determined as following.

$$R_{ttin} = \left[ \frac{\delta_i n}{2} + \frac{d_w}{2} (1 - \cos \theta) \right] \frac{1}{\sin \theta}$$

(3.7)

where the bare conductor diameter is denoted by  $d_w$ .  $\theta$  is the angle of the electric field line. The radius formula can be expressed as a function of  $\theta$ . Therefore, the turn-to-turn capacitance of the inner region  $C_{ttin}$  can be expressed as shown.

$$C_{ttin} = \epsilon_0 h_w \frac{d_w}{2} \int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} \frac{\sin \theta d\theta}{\theta \left[\delta_{in} + d_w (1 - \cos \theta)\right]}$$

(3.8)

where

$$h_w = h_{cpl} + 2w_s + d_w (3.9)$$

The conductor length in either inner or outer region of the core is represented by  $h_w$  where  $h_{cpl}$  is the core height with plastic case. The distance between the conductor surface and the core plastic is  $w_s$  as shown in figure 3.4. The turn-to-turn capacitance of the outer region  $C_{tto}$  is following the same procedure of the capacitance between turns of the inner region.

$$C_{tto} = \epsilon_o h_w \frac{d_w}{2} \int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} \frac{\sin \theta d\theta}{\theta \left[\delta_o + d_w (1 - \cos \theta)\right]}$$

(3.10)

Figure 3.4: The cross section of the core geometry.

The last region of turn-to-turn capacitance is the lateral region. The capacitance in the lateral region is denoted as  $C_{ttl}$ . It can be determined as followed.

$$C_{ttl} = \epsilon_o \frac{d_w}{2}$$

$$\int_{r_{in}}^{r_o} \int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} \frac{\sin\theta d\theta dr}{\theta \left[\frac{\delta_o - \delta_{in}}{r_o - r_{in}} (r - r_{in}) + \delta_{in} + d_w (1 - \cos\theta)\right]}$$

(3.11)

where the definitions of  $\delta_o$ ,  $\delta_{in}$ ,  $r_o$ , and  $r_{in}$  are shown in figure 3.5. The total parasitic capacitance of turn to turn can be determined as followed.

$$C_{tt} = C_{ttin} + C_{tto} + 2C_{ttl} \tag{3.12}$$

The capacitance between a turn and core has a similar way of calculating the capacitance between turns. Figure 3.6 shows the electric filed line between a turn and core. The capacitance

Figure 3.5: The electric field lines of lateral region.

between a turn and core of the inner region is represented by  $C_{tcin}$ .  $C_{tcin}$  can be determined as following.

$$C_{tcin} = \epsilon_{o} h_{w} \frac{d_{w}}{2}$$

$$\int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} \frac{d\theta}{\left(\theta \left[\delta_{c} + \left(\frac{d_{w}}{2}\right) (1 - \cos \theta)\right] / \sin \theta\right) + \frac{w_{plin}}{\epsilon_{rpl}}}$$

(3.13)

where the width of the core plastic case for the inner region is  $w_{plin}$ . The relative permittivity of the plastic case is  $\epsilon_{rpln}$ . Similarly, the capacitance between a turn and core for the outer region can be determined as followed.

Figure 3.6: The electric field lines between turn and core.

$$C_{tco} = \epsilon_0 h_w \frac{d_w}{2}$$

$$\int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} \frac{d\theta}{\left(\theta \left[w_s + \left(\frac{d_w}{2}\right) (1 - \cos\theta)\right] / \sin\theta\right) + \frac{w_{plo}}{\epsilon_{rpl}}}$$

(3.14)

where the width of the core plastic case for the outer region is  $w_{plo}$ . For the lateral region, the capacitance between a turn and core can be determined as followed.

$$C_{tcl} = \epsilon_o (r_o - r_{in}) \frac{d_w}{2}$$

$$\int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} \frac{d\theta}{\left(\theta \left[w_s + \left(\frac{d_w}{2}\right) (1 - \cos\theta)\right] / \sin\theta\right) + \frac{w_{pll}}{\epsilon_{rpl}}}$$

(3.15)

where the length of conductor  $h_w$  can be represented as the expression for the difference between  $r_o$  and  $r_{in}$ . The width of the core plastic case for the lateral region is  $w_{pll}$ . The total capacitance between a turn and core can be found as a sum of the turn to core capacitances in all regions.

$$C_{tc} = C_{tcin} + C_{tco} + 2C_{tcl} \tag{3.16}$$

### 3.2.1 Advantages and Disadvantages

Modeling the parasitic capacitance of common-mode choke of single-layer inductors with a magnetic core has several advantages as well as disadvantages. The following points represent the advantages of this method.

- This paper focuses on determining the parasitic capacitance of common-mode choke.

- The analytical method is applied for applications with high frequency.

- The model includes three different regions to calculate the capacitance between turns and between a turn and a core.

- The model depends on the electric filed lines in order to calculate the capacitance.

- The distance between turns and between a turn and a core can be applied in this model.

While there are advantages in this method, there are disadvantages as well. The following points summarize the drawbacks of this method.

- This method can not estimate the parasitic capacitance of applications with frequencies lower than the first resonant frequency.

- The complexity of this model is high.

- This model does not include the total capacitance of the winding.

- There is no relationship between the number of turns and the parasitic capacitance.

### 3.3 Modeling the Parasitic Capacitance by Using the Finite Element Method

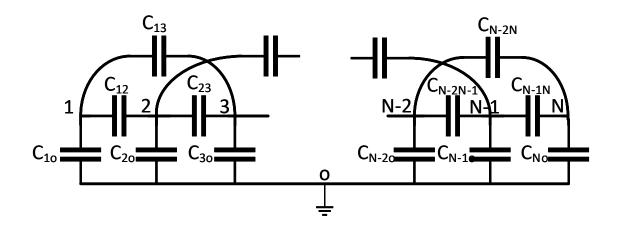

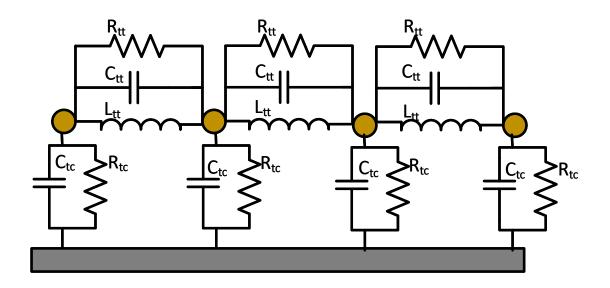

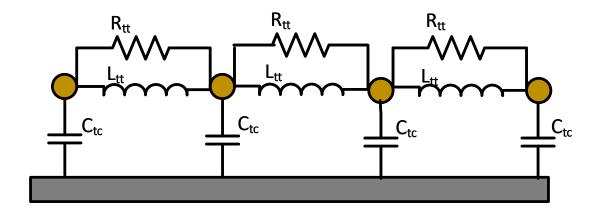

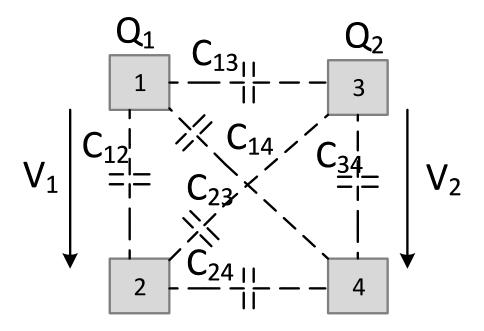

A new model of the parasitic capacitance of inductors with high frequency applications is proposed in [22]. The purpose of this method is to calculate the capacitance between adjacent turns and nonadjacent turns. Figure 3.7 shows the lamped capacitance network of high frequency applications.

Figure 3.7: The lamped capacitance network.

The distributed capacitance of an inductor, which is shown in figure 3.7, presents node-to-node capacitance elements. Each node of the capacitance network represents a turn. The capacitance  $C_{ij}$  is the capacitance between the turns i and j, each are different than the other. The capacitance between the turn and the ground can be denoted by  $C_{io}$ . Each node has a voltage and a current. The node voltages, node currents, and node-to-node capacitance have a relationship. The relationship can be represented by a square admittance matrix, as shown next.

$$\begin{pmatrix}

I_1 \\

I_2 \\

\vdots \\

I_N

\end{pmatrix} = \begin{pmatrix}

Y_{11} & Y_{12} & \dots & Y_{1N} \\

Y_{21} & Y_{22} & \dots & Y_{2N} \\

\vdots & \dots & \dots & \vdots \\

Y_{N1} & Y_{N2} & \dots & Y_{NN}

\end{pmatrix} * \begin{pmatrix}

V_1 \\

V_2 \\

\vdots \\

V_N

\end{pmatrix}$$

(3.17)

where the current, voltage, and admittance can be represented by  $I_i$ ,  $V_j$ , and  $Y_{ij}$ , respectively. (3.17) shows a general expression about the capacitive couplings among conductors. The parasitic

capacitance of an inductor can be determined by eliminating all intermediate nodes between its two terminals. The matrix in equation (3.17) is reduced to vectors and matrices as shown next.

$$\begin{pmatrix} V_x \end{pmatrix} = \begin{pmatrix} V_1 \\ V_x \end{pmatrix} \\

\begin{pmatrix} V_y \end{pmatrix} = \begin{pmatrix} V_2 \\ \vdots \\ V_{N-1} \end{pmatrix}$$

(3.18)

where the node voltages can be divided to two vectors  $V_x$  and  $V_y$ . The node current, which are  $I_x$  and  $I_y$ , is represented by two vectors.

$$\begin{pmatrix} I_x \end{pmatrix} = \begin{pmatrix} I_1 \\ I_x \end{pmatrix} \\

\begin{pmatrix} I_y \end{pmatrix} = \begin{pmatrix} I_2 \\ \vdots \\ I_{N-1} \end{pmatrix} \tag{3.19}$$

The admittance matrix is reduced to four different matrices. The reduction is based on the node place at the inductor.

$$(Y_{xx}) = \begin{pmatrix} Y_{11} & Y_{1N} \\ Y_{N1} & Y_{NN} \end{pmatrix}$$

$$(Y_{xy}) = \begin{pmatrix} Y_{12} & \dots & Y_{1N-1} \\ Y_{N2} & \dots & Y_{NN-1} \end{pmatrix}$$

$$(Y_{yx}) = \begin{pmatrix} Y_{21} & Y_{2N} \\ \vdots & \vdots \\ Y_{N-11} & Y_{N-1N} \end{pmatrix}$$

$$(Y_{yy}) = \begin{pmatrix} Y_{22} & \dots & Y_{2N-1} \\ \vdots & \vdots & \vdots \\ Y_{N-12} & \dots & Y_{N-1N-1} \end{pmatrix}$$

$$(3.20)$$

The nondiagonal admittance in the  $Y_x$  that is presented in (3.21) is equal to  $-j\omega C_{1N}$ .

$$Y_x = Y_{xx} - Y_{xy}Y_{yy}^{-1}Y_{yx} (3.21)$$

Therefore, by assuming  $I_y = 0$ , the voltage vectors can be determined. Hence, the lumped parasitic capacitance of the inductor can be estimated easily.

### 3.3.1 Advantages and Disadvantages

The new model of determining the parasitic capacitance of single-layer inductors with a magnetic core has several advantages as well as disadvantages. The following points represent the advantages of this method.

- This paper focuses on determining the parasitic capacitance of inductors with radio frequency circuit.

- The analytical method is applied for applications with high frequency.

- The model is verified by a 2D electrostatic model with finite element method.

• The model includes adjacent and nonadjacent turns capacitance.

While there are advantages in this method, there are disadvantages as well. The following points summarize the drawbacks of this method.

- This method can not estimate the parasitic capacitance of applications with frequencies lower than first resonant frequency.

- The method of using this model is complex.

- There is no relationship between the number of turns and the parasitic capacitance.

### **CHAPTER 4**

### MODELING THE PARASITIC CAPACITANCE OF MAGNETIC COMPONENTS

### 4.1 Introduction

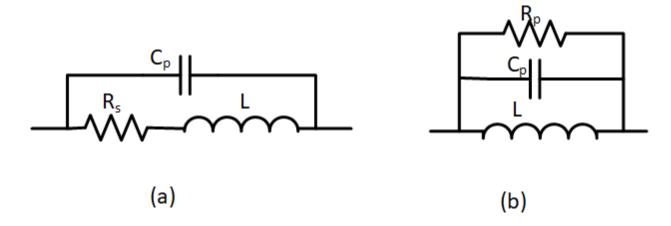

Magnetic components such as inductors, interleave coupled inductors, and transformers are important parts of electric and electronic systems [20]. Magnetic components have inherent parasitics that affect their performance when frequency increases. In fact, the parasitic elements of magnetic components can play a significant role on the modern electrical system. The magnetic components have two types of parasitics which are resistance and capacitance parasitics. The winding resistance and core losses constitute the parasitic resistance while the parasitic capacitance is caused by the inter-turn, inter-layer, and winding-to-core capacitances. [11, 17, 26, 43]. The parasitic elements of an inductor can be represented by the models as shown in figure 4.1. The commonly adopted model in figure 4.1(a) consists of the parasitic resistance  $R_s$  is in series with inductance while the parasitic capacitance  $C_p$  is in parallel with the series connected  $R_s$  and L. Figure 4.1(b) represents an inductor model with parallel parasitic resistance  $R_p$  and parallel parasitic capacitance [12, 27, 32, 43, 45].

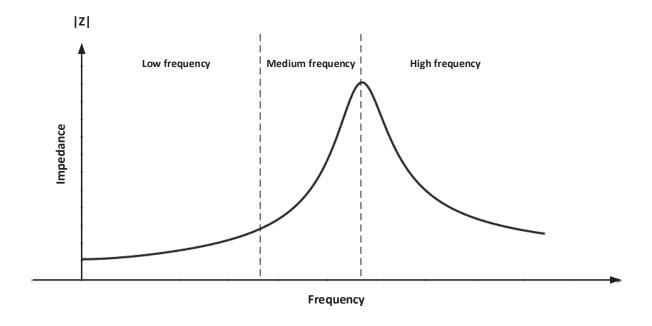

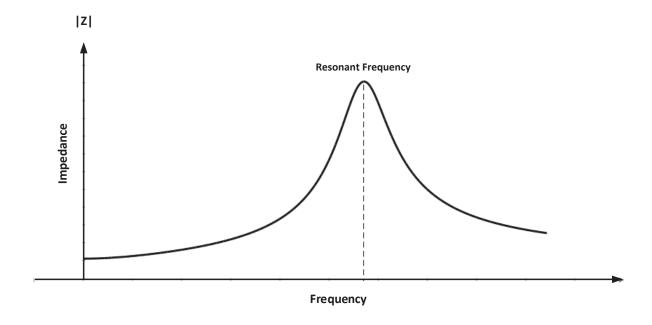

The impedance of an inductor increases when the frequency increases. Because of the recent development of switching frequency, the efficiency of power electronics applications can be affected and reduced based on the range of frequency [16, 43]. Figure 4.2 shows the characteristic of the inductor impedance when the frequency increases. The frequencies range of an inductor in power electronics applications can be divided into three categories: low frequency range in which the parasitic capacitance does not affect the inductor behavior, medium frequency range when the characteristic of an inductor start to be affected by frequency which appears below first resonant frequency, and high frequency range which is the range of frequencies above the first resonant frequency such as radio frequency and EMI filter applications.

The parasitic capacitance over medium frequency range is different than the parasitic capacitance

Figure 4.1: Models of an inductor.

Figure 4.2: Characteristic impedance of an inductor with parasitic capacitance included in the model.

over high frequency range [13,43]. Most of the parasitic capacitance models over medium frequency range are developed for high frequency transformer applications [18]. However, there is no model of calculating the single layer inductor in medium range frequency for power electronic converters.

For single-layer inductor, there are a couple of models to calculate the parasitic capacitance for high frequency applications [12, 29, 43]. Most of these models are applied with air-core inductor in order to use them with frequencies above 1MHz [13, 19, 43, 45] such as EMI filter, EMC filter, and radio frequency applications.

It is essential to have accurate and simple analytical method to calculate the total parasitic capacitance for medium frequency range that can be applied to magnetic components such as inductors. Inductors can be applied as filter or energy storage for converters like a boost converter in medium frequency range.

This paper introduces a new approach to estimating the total parasitic capacitance of an inductor of a single-layer with a magnetic core in medium frequency range. This model can determine the parasitic capacitance based on the geometry of an inductor core and the approximated shape of the conductor.

In order to verify the analytical method of calculating the parasitic capacitance, two different techniques have been applied. The first technique is to test the inductor with various frequencies speed such as using network analyzer [18,21]. The other technique is to apply the finite element analysis (FEA), which is considered to be of higher accuracy than analytical models [18,21,22].

The FEA simulation have two models with different accuracy that can determine the parasitic capacitance. The models of FEA simulation are two-dimensional (2-D) model which considers to be lower accuracy than three-dimensional (3-D) model of simulation [21,22]. For more complex geometry and multiple layers, the analytical model is proved to be time efficient and more convenient for the model-based design [21].

The rest of the chapter is divided as follows. The approximation model of conductor is presented in subsection 4.2.1. In subsection 4.2.2, the analytical method of modeling the parasitic capacitance of single-layer inductor with a magnetic core is explained. The results and discussion are introduced

in section 4.3. Finally, the conclusion of the new approach of modeling the parasitic capacitance is shown in section 4.4.

### 4.2 Methodology of Modeling Inductors

Magnetic components contain two main parts that are magnetic core and winding conductor. For modeling the parasitic capacitance of magnetic components, the geometry of magnetic core, conductor, and the distance between them should be considered. For the trade-off between accuracy and simplicity, the conductor can be modeled in approximated shape as explained it in the subsequent text.

The magnetic core material should be chosen based on frequency and losses in the material. The magnetic core has many different shape that can be selected based on the power and magnetic flux needed. For instance, E-I & U-I shapes are used for interleaved coupled inductors, transformers, and single-phase and multi-phase inductors [4, 6, 16, 34].

### 4.2.1 Modeling the conductor

Modeling the parasitic capacitance of magnetic components has been one of the technically challenging topics for decades. Significant research effort has been invested in modeling the parasitic capacitance for different magnetic components geometries [16, 21, 43]. Most of the previous work on modeling the parasitic capacitance of inductors are aimed for applications with very high frequencies. Some of these models are only applicable for air-core inductors [13, 19]. There exist very few models that consider the magnetic core for calculating the parasitic capacitance of single-layer inductors. The existing models work only in very high frequencies such as EMI, and EMC filters [13, 17, 43]. Another model type of parasitic capacitance for magnetic components is aimed for transformers [18, 46]. This type of model is focused on the frequencies below first resonant frequency [16, 18]. However, most of these models are less accurate compared with 3-D electrostatic model simulations and still complex to calculate the parasitic capacitance.

In order to achieve a model that strikes a balance between accuracy and complexity in esti-

Figure 4.3: Approximation shape of rod conductor.

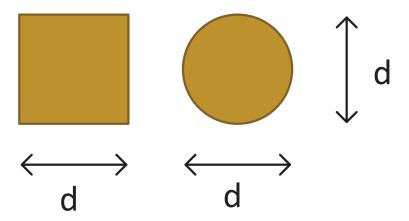

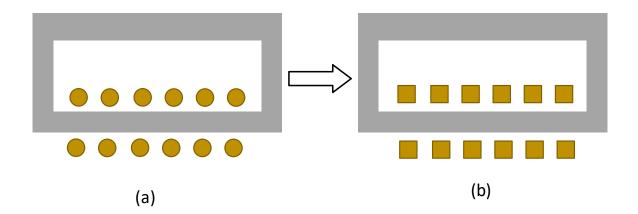

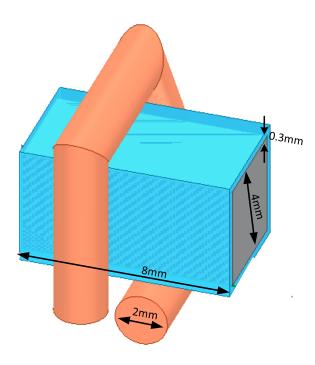

mating the parasitic capacitance, the approximation of conductor shape is proposed. The close approximation of rod wire conductor with a square shape can simplify the analytical calculation of parasitic capacitance. Figure 4.3 shows the approximation of rod conductor with a square shape. This approximation is applied to model and calculate the parasitic capacitance of inductors with a single-layer for power converters. Without loss of generality, the magnetic U-I core is selected in this study. Figure 4.4 shows the approximation model of single-layer inductor with magnetic U core.

The results based on this approximation method show improved accuracy as compared with other models of single-layer inductor with magnetic core such as in [43]. The percentage of error between FEA simulations such as 3D electrostatic and Q3D extractor models and the proposed analytical model is less than 8%. Moreover, the proposed model has many advantages over the model in [17,43] such as including the distance between turn to turn, turn to core, and turn to side limb of magnetic core.

The process of calculating the parasitic capacitance for a single-layer inductor with magnetic core is presented in the following section.

Figure 4.4: U-I core with approximation shape of rod conductor.

Figure 4.5: High frequency circuit of an inductor with magnetic core.

Figure 4.6: Simplified high frequency circuit of an inductor with magnetic core.

Figure 4.7: Curve of impedance versus frequency.

Figure 4.8: The parasitic capacitance model of U-I core.

### 4.2.2 Modeling inductors with single-layer