#### OPTIMIZATION OF LARGE SCALE ITERATIVE EIGENSOLVERS

By

Md Afibuzzaman

#### A DISSERTATION

Submitted to Michigan State University in partial fulfillment of the requirements for the degree of

Computer Science - Doctor of Philosophy

2021

#### ABSTRACT

#### OPTIMIZATION OF LARGE SCALE ITERATIVE EIGENSOLVERS

#### $\mathbf{B}\mathbf{y}$

#### Md Afibuzzaman

Sparse matrix computations, in the form of solvers for systems of linear equations, eigenvalue problem or matrix factorizations constitute the main kernel in problems from fields as diverse as computational fluid dynamics, quantum many body problems, machine learning and graph analytics. Iterative eigensolvers have been preferred over the regular method because the regular method not being feasible with industrial sized matrices. Although dense linear algebra libraries like BLAS, LAPACK, SCALAPACK are well established and some vendor optimized implementation like mkl from Intel or Cray Libsci exist, it is not the same case for sparse linear algebra which is lagging far behind. The main reason behind slow progress in the standardization of sparse linear algebra or library development is the different forms and properties depending on the application area. It is worsened for deep memory hierarchies of modern architectures due to low arithmetic intensities and memory bound computations. Minimization of data movement and fast access to the matrix are critical in this case. Since the current technology is driven by deep memory architectures where we get the increased capacity at the expense of increased latency and decreased bandwidth when we go further from the processors. The key to achieve high performance in sparse matrix computations in deep memory hierarchy is to minimize data movement across layers of the memory and overlap data movement with computations. My thesis work contributes towards addressing the algorithmic challenges and developing a computational infrastructure to achieve high performance in scientific applications for both shared memory and distributed memory architectures. For this purpose, I started working on optimizing a blocked eigensolver and optimized specific computational kernels which uses a new storage format. Using this optimization as a building block, we introduce a shared memory task parallel framework focusing on optimizing the entire solvers rather than a specific kernel. Before extending this shared memory implementation to a distributed memory architecture, I simulated the communication pattern and overheads of a large scale distributed memory application and then I introduce the communication tasks in the framework to overlap communication and computation. Additionally, I also tried to find a custom scheduler for the tasks using a graph partitioner. To get acquainted with high performance computing and parallel libraries, I started my PhD journey with optimizing a DFT code named Sky3D where I used dense matrix libraries. Despite there might not be any single solution for this problem, I tried to find an optimized solution. Though the large distributed memory application MFDn is kind of the driver project of the thesis, but the framework we developed is not confined to MFDn only, rather it can be used for other scientific applications too. The output of this thesis is the task parallel HPC infrastructure that we envisioned for both shared and distributed memory architectures.

Copyright by MD AFIBUZZAMAN 2021

| I would like to dedicate this thesis wife Mayeesha Farzana and my S |  |  |

|---------------------------------------------------------------------|--|--|

|                                                                     |  |  |

|                                                                     |  |  |

#### ACKNOWLEDGMENTS

I would like to thank my advisor Dr. Hasan Metin Aktulga who has supported me throughout my PhD career with research grants and enriched my knowledge with innovative ideas. From the very beginning he has taught me the fundamentals of research. He made constructive criticisms throughout my PhD journey and also motivated me to keep going when things were not going as I expected. I would also like to thank my friends in Michigan State University who made my time enjoyable and did not let me fall victim to research related fatigue. I sincerely thank my group mates for their ideas and support. My parents and brother Md Ahiduzzaman always encouraged me and supported me living in a different country. My son Taaif who was born in the final year of my PhD motivated me to push my work with his amazing smile. And most importantly my wife Mayeesha deserves the most credit with her constant support and presence in my life.

## TABLE OF CONTENTS

| LIST (     | F TABLES                                                                  | xi   |

|------------|---------------------------------------------------------------------------|------|

| LIST (     | F FIGURES                                                                 | xiii |

| LIST (     | F ALGORITHMS                                                              | xx   |

| Chapte     | r 1 INTRODUCTION AND MOTIVATION                                           | 1    |

| 1.1        | Background And Related Work                                               | 1    |

| 1.2        | Emergence Of Deep Memory Hierarchies                                      | 3    |

| 1.3        | Optimizing Sky3D                                                          | 6    |

| 1.4        | Optimization Of Blocked Eigensolver For Sparse Matrix                     | 9    |

| 1.5        | Inrtroducing the DeepSparse Framework                                     | 13   |

| 1.6        | Exploring Custom Schedule For Tasks Using Graph Partition                 | 15   |

| 1.7        | Simulating Communication Behavior Of A Real World Distributed Application | n 18 |

| 1.8        | Introducing Communication for DeepSparse                                  | 19   |

| Chapte     | r 2 OPTIMIZATION IN LARGE SCALE DISTRIBUTED DENSE                         |      |

| Chapt      | MATRICES                                                                  | 22   |

| 2.1        | Nuclear Density Functional Theory With Skyrme Interaction                 | 22   |

| 2.2        | Sky3D Software                                                            | 25   |

| 2.3        | Distributed Memory Parallelization With MPI                               | 26   |

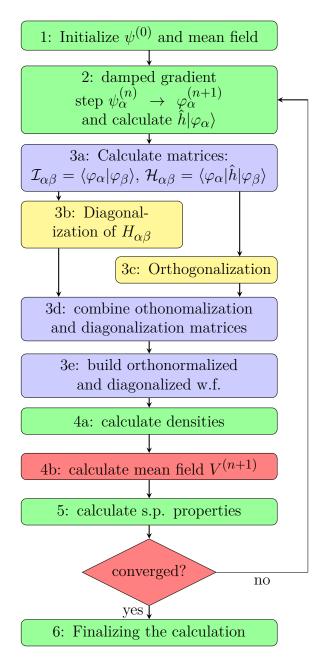

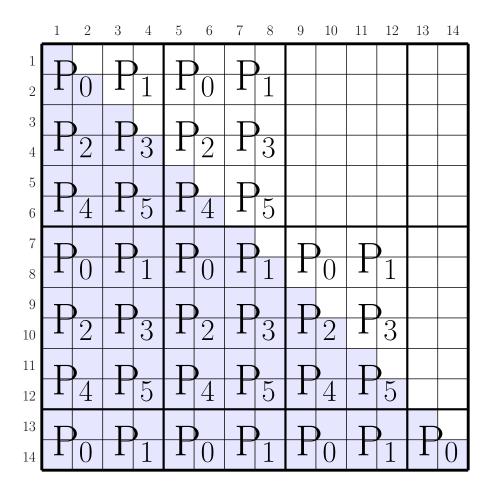

|            | 2.3.1 The 1D and 2D partitionings                                         | 28   |

|            | 2.3.2 Parallelization across Neutron and Proton groups                    | 30   |

|            | 2.3.3 Calculations with 2D distributions                                  | 32   |

|            | 2.3.3.1 Matrix construction (step 3a)                                     | 33   |

|            | 2.3.3.2 Diagonalization and Orthonormalization (steps 3b & c)             | 34   |

|            | 2.3.3.3 Post-processing (steps 3d & e)                                    | 36   |

|            | 2.3.4 Calculations with a 1D distribution                                 | 37   |

|            | 2.3.5 Switching between different data distributions                      | 38   |

|            | 2.3.6 Memory considerations                                               | 38   |

| 2.4        | Shared Memory Parallelization with OpenMP                                 | 40   |

| 2.5        | Performance Evaluation                                                    | 41   |

|            | 2.5.1 Experimental setup                                                  | 41   |

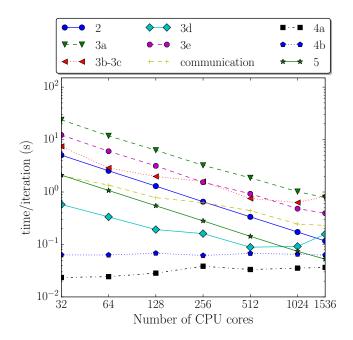

|            | 2.5.2 Scalability                                                         | 42   |

|            | 2.5.3 Comparison between MPI-only and MPI/OpenMP hybrid parallelization   | n 46 |

|            | 2.5.4 Load balancing                                                      | 51   |

|            | 2.5.5 Conclusion of this work                                             | 55   |

| <b>~</b> 1 |                                                                           | _    |

| Chapte     |                                                                           |      |

|            | MATRICES                                                                  | 57   |

| 3.1          | Eigenvalue Problem in CI Calculations                            | 57                |

|--------------|------------------------------------------------------------------|-------------------|

| 3.2          | Motivation and CI Implementation                                 | 58                |

| 3.3          | Multiplication of the Sparse Matrix with Multiple Vectors (SpMM) | 61                |

| 3.4          | Matrix Storage Formats                                           | 62                |

| 3.5          | Methodology and Optimization                                     | 64                |

| 3.6          | An Extended Roofline Model for CSB                               | 67                |

| 3.7          | Kernels with Tall and Skinny Matrices                            | 70                |

| 3.8          | Performance Evaluation                                           | 72                |

| 3.0          | 3.8.1 Experimental setup                                         | 73                |

|              | 3.8.2 Performance of SpMM and SpMM $^T$                          | 77                |

|              | 3.8.3 Improvement with using CSB                                 | 78                |

|              | 3.8.4 Tuning for the Optimal Value of $\beta$                    | 79                |

|              | 3.8.5 Combined $SpMM/SpMM^T$ performance                         | 79                |

|              | 3.8.6 Performance analysis                                       | 80                |

|              | 3.8.7 Performance of tall-skinny matrix operations               | 81                |

|              | 3.8.8 Performance summary                                        | 83                |

| 3.9          | Evaluation on Xeon Phi Knights Corner (KNC)                      | 89                |

| 0.5          | 3.9.1 Conclusions of this work                                   | 92                |

|              | 9.9.1 Conclusions of this work                                   | 52                |

| Chapte       | er 4 ON NODE TASK PARALLEL OPTIMIZATION                          | 93                |

| 4.1          | DeepSparse Overview                                              | 95                |

| 1.1          | 4.1.1 Primitive Conversion Unit (PCU)                            | 97                |

|              | 4.1.1.1 Task Identifier (TI)                                     | 97                |

|              | 4.1.1.2 Task Dependency Graph Generator (TDGG)                   | 98                |

|              | 4.1.2 Task Executor                                              | 96                |

|              |                                                                  | 101               |

|              | r ·                                                              | 104               |

| 4.2          |                                                                  | 105               |

| 7.2          | ••                                                               | 105               |

|              |                                                                  | 106               |

| 4.3          |                                                                  | 107               |

| 4.0          |                                                                  | 107               |

|              | 1                                                                | 109               |

|              |                                                                  | 111               |

|              |                                                                  | 113               |

|              | r r r r r                                                        | 113               |

|              | 4.5.5 Conclusions of this work                                   | 110               |

| Chapte       | er 5 SCHEDULING TASKS WITH A GRAPH PARTITIONER . :               | 115               |

| 5.1          |                                                                  | 116               |

| 5.1          |                                                                  | 119               |

| 5.3          |                                                                  | 122               |

| 5.3          | -,                                                               | $\frac{122}{124}$ |

| $5.4 \\ 5.5$ |                                                                  | 130               |

| 5.6          | · · · · · · · · · · · · · · · · · · ·                            | 133               |

| 5.0          |                                                                  | 133               |

|              | 5.6.1 Upperboounds                                               | TOC               |

|        | 5.6.2 Refinement                                          |

|--------|-----------------------------------------------------------|

|        | 5.6.3 Graph structure                                     |

|        | 5.6.4 Edgecut                                             |

| 5.7    | PowerLaw Graph Partitioning Attempts                      |

|        | 5.7.1 Lowest Common Ancestor                              |

|        | 5.7.2 Hierarchical partitioning attempts                  |

| 5.8    | Memory Bound Implementation                               |

| 5.9    | Experimental Results                                      |

|        | 5.9.1 Experiment setup                                    |

|        | 5.9.2 Performance of the partitioner                      |

| 5.10   | Future work on the partitioner                            |

| Chapte | er 6 SIMULATING THE COMMUNICATION PATTERNS IN A           |

|        | LARGE SCALE DISTRIBUTED APPLICATION 15                    |

| 6.1    | MFDn Communication Motif                                  |

| 6.2    | Simulation of a Distributed communication                 |

| 6.3    | Simulation Framework and Implementation                   |

|        | 6.3.1 Ember                                               |

|        | 6.3.2 FireFly                                             |

|        | 6.3.3 Merlin                                              |

| 6.4    | Implementation                                            |

|        | 6.4.1 Random Distribution of Processes                    |

| 6.5    | Evaluation and Results                                    |

|        | 6.5.1 Hardware and Software                               |

|        | 6.5.2 Benchmark problems                                  |

|        | 6.5.3 SST parameters for Cori-KNL simulations             |

|        | 6.5.4 Simulation results in Cori-KNL                      |

| 6.6    | Simulation for A Future Network                           |

|        | 6.6.1 Conclusions of this work                            |

| Chapte | er 7 OPTIMIZING A DISTRIBUTED MEMORY APPLICATION          |

|        | USING DEEPSPARSE                                          |

| 7.1    | Motivation                                                |

|        | 7.1.1 Introducing communication tasks                     |

|        | 7.1.2 Better pipelining of matrix and vector operations   |

| 7.2    | Methodology                                               |

|        | 7.2.1 Issue with blocking MPI calls                       |

|        | 7.2.2 Issue with absence of TAG fields in MPI collectives |

|        | 7.2.3 Distributed SpMM                                    |

|        | 7.2.4 Blocked communication                               |

|        | 7.2.5 Custom reduction                                    |

| 7.3    | Experiments and Results                                   |

|        | 7.3.1 Experimental setup                                  |

|        | 7.3.2 Impact of blocked communications                    |

|        | 7.3.3 Improvement with custom reduction                   |

| 7.3.4     | Breakdown of individual kernel performance                    | 197 |

|-----------|---------------------------------------------------------------|-----|

| 7.3.5     | Expensive matrix multiplication compared to vector operations | 199 |

| 7.3.6     | Conclusions of this work                                      | 201 |

| Chapter 8 | CONCLUSION AND FUTURE WORK                                    | 203 |

| BIBLIOGRA | APHY                                                          | 206 |

## LIST OF TABLES

| Table 2.1: | Hardware specifications for a single socket on Cori, a Cray XC40 super-<br>computer at NERSC. Each node consists of two sockets                                                                                                                     | 42  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2: | Scalability of MPI-only version of Sky3D for the $L=32\mathrm{fm}$ grid. Time is given in seconds, and efficiency (eff) is given in percentages.                                                                                                    | 44  |

| Table 2.3: | Scalability of MPI-only version of Sky3D for the $L=48\mathrm{fm}$ grid. Time is given in seconds, and efficiency (eff) is given in percentages.                                                                                                    | 46  |

| Table 2.4: | Scalability of MPI/OpenMP parallel version of Sky3D for the $L=32\mathrm{fm}$ grid. Time is given in seconds, and efficiency (eff) is given in percentages                                                                                          | 48  |

| Table 2.5: | Scalability of MPI/OpenMP parallel version of Sky3D for the $L=48\mathrm{fm}$ grid. Time is given in seconds, and efficiency (eff) is given in percentages                                                                                          | 50  |

| Table 2.6: | Scalability of MPI-only version of Sky3D for the 5000 neutrons and 1000 protons system using the $L=48\mathrm{fm}$ grid. Time is given in seconds, and efficiency (eff) is given in percentages                                                     | 54  |

| Table 3.1: | MFDn matrices (per-process sub-matrix) used in our evaluations. For the statistics in this table, all matrices were cache blocked using $\beta = 6000.$                                                                                             | 74  |

| Table 3.2: | Overview of Evaluated Platforms. <sup>1</sup> With hyper threading, but only 12 threads were used in our computations. <sup>2</sup> Based on the saxpy1 benchmark in [1]. <sup>3</sup> Memory bandwidth is measured using the STREAM copy benchmark | 76  |

| Table 3.3: | Statistics for the full MFDn matrices used in distributed memory parallel Lanczos/FO and LOBPCG executions.                                                                                                                                         | 87  |

| Table 4.1: | Major data structures after parsing third line                                                                                                                                                                                                      | 104 |

| Table 4.2: | Matrices used in our evaluation                                                                                                                                                                                                                     | 109 |

| Table 6.1: | Matrices used in this study, the dimensions and number of nonzero matrix elements of each matrix                                                                                                                                                    | 166 |

| Table 6.2: | Router and NIC Parameters used for Simulating Cori-KNL                                                                                                                                                                                              | 169 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 6.3: | MPI ranks, number of diagonals, number of ranks per custom communicators, Message Size during Broadcast and Reduce and Message Size during Allgather and Reduce_Scatter.                                                                            | 170 |

| Table 6.4: | Router and NIC Parameter used for simulating Perlmutter's predicted network                                                                                                                                                                         | 175 |

| Table 7.1: | Overview of Evaluated Platforms. <sup>1</sup> With hyper threading, but only 12 threads were used in our computations. <sup>2</sup> Based on the saxpy1 benchmark in [1]. <sup>3</sup> Memory bandwidth is measured using the STREAM copy benchmark | 193 |

| Table 7.2: | Matrices used in this experiment. Number of MPI ranks, dimensions and number of nonzeroes per rank                                                                                                                                                  | 194 |

## LIST OF FIGURES

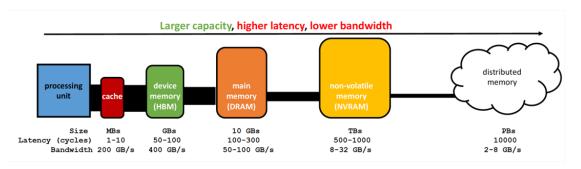

| Figure 1.1: | Memory hierarchy in deep memory architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1: | Flowchart of the parallelized Sky3D code. Parts in the 1d distribution are marked in green, parts in full 2d distribution are marked in blue, parts in divided 2d distribution are marked in yellow and collective non-parallelized parts are marked in red. $\psi_{\alpha}^{(n)}$ denotes the orthonormal and diagonal wave function at step n with index $\alpha$ , $ \varphi_{\alpha}\rangle = \varphi_{\alpha}^{(n+1)}$ denotes the non-diagonal and non-orthonormal wave function at step n+1. $\hat{h}$ is the one-body Hamiltonian | 27 |

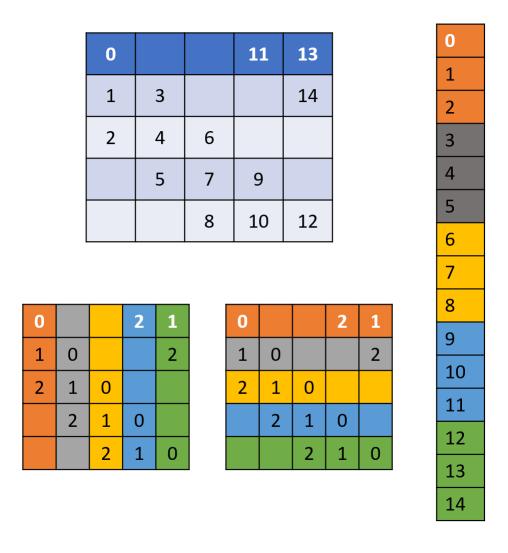

| Figure 2.2: | 2D block cyclic partitioning example with 14 wave functions using a $3\times2$ processor topology. Row and column block sizes are set as $NB=MB=2$ . The blue shaded area marks the lower triangular part.                                                                                                                                                                                                                                                                                                                                | 30 |

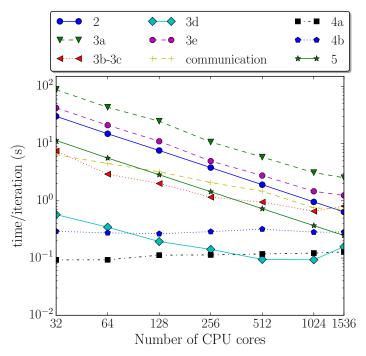

| Figure 2.3: | Scalability of MPI-only version of Sky3D for the 3000 neutron and 3000 proton system using the $L=32\mathrm{fm}$ grid                                                                                                                                                                                                                                                                                                                                                                                                                     | 43 |

| Figure 2.4: | Scalability of MPI-only version of Sky3D for the 3000 neutron and 3000 proton system using the $L=48\mathrm{fm}$ grid                                                                                                                                                                                                                                                                                                                                                                                                                     | 45 |

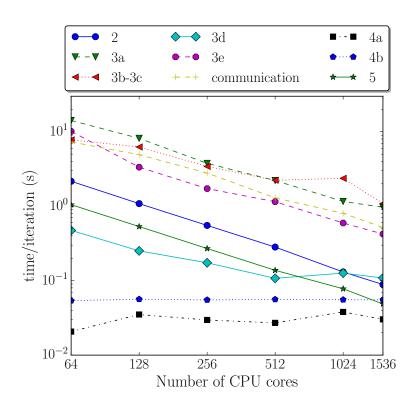

| Figure 2.5: | Scalability of MPI/OpenMP parallel version of Sky3D for the 3000 neutron and 3000 proton system using the $L=32\mathrm{fm}$ grid                                                                                                                                                                                                                                                                                                                                                                                                          | 47 |

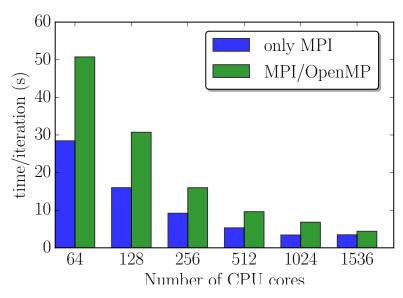

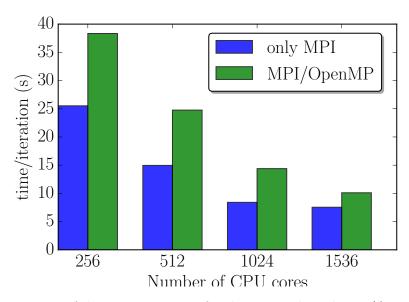

| Figure 2.6: | Comparison of the execution times for the MPI-only and MPI/OpenMP parallel versions of Sky3D for the 3000 neutron and 3000 proton system using the $L=32\mathrm{fm}$ grid                                                                                                                                                                                                                                                                                                                                                                 | 49 |

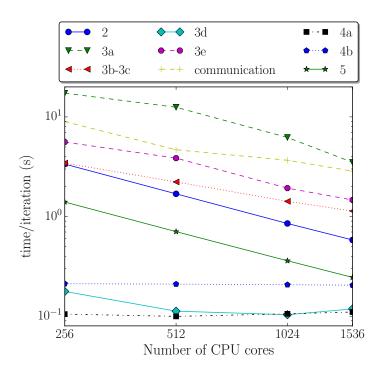

| Figure 2.7: | Scalability of MPI/OpenMP parallel version of Sky3D for the 3000 neutron and 3000 proton system using the $L=48\mathrm{fm}$ grid                                                                                                                                                                                                                                                                                                                                                                                                          | 50 |

| Figure 2.8: | Comparison of the execution times for the MPI-only and MPI/OpenMP parallel versions of Sky3D for the 3000 neutron and 3000 proton system using the $L=32\mathrm{fm}$ grid                                                                                                                                                                                                                                                                                                                                                                 | 51 |

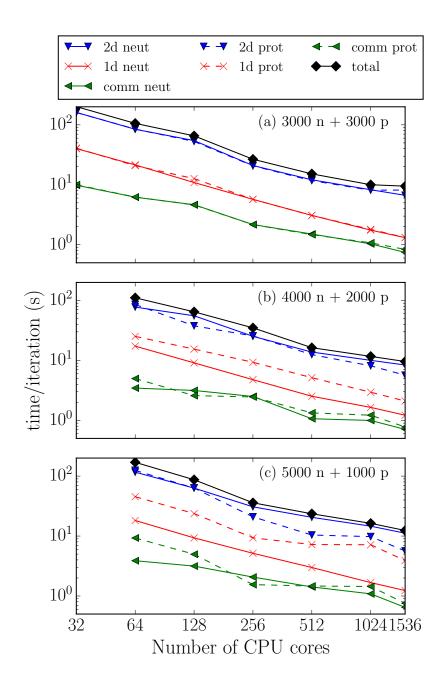

| Figure 2.9: | Times per iteration for neutron and proton processor groups, illustrating the load balance for the 3000 neutrons and 3000 protons (a), 4000 neutrons and 2000 protons (b), and 5000 neutrons and 1000 protons (c) systems using the $L=48$ fm grid. Due to memory constraints the latter two cases cannot be calculated using 32 CPII                                                                                                                                                                                                     | 59 |

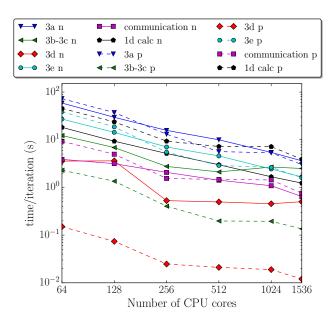

| Figure 2.10: | A detailed breakdown of per iteration times for neutron and proton processor groups, illustrating the load balance for the 5000 neutrons and 1000 protons system                                                                                                                    | 54 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

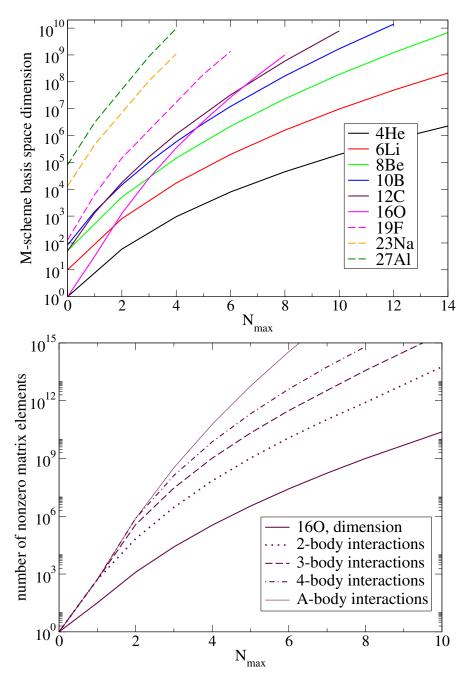

| Figure 3.1:  | The dimension and the number of non-zero matrix elements of the various nuclear Hamiltonian matrices as a function of the truncation parameter $N_{\text{max}}$ . While the bottom panel is specific to $^{16}\text{O}$ , it is also representative of a wider set of nuclei [2, 3] | 59 |

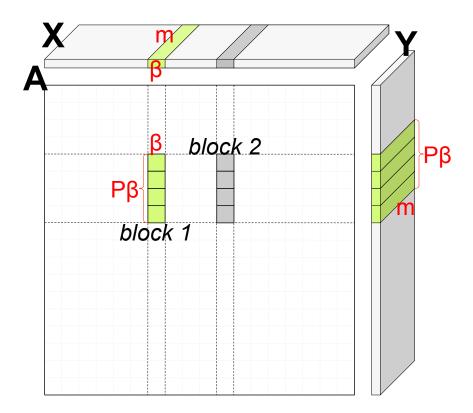

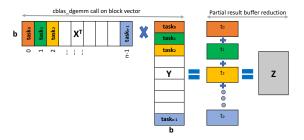

| Figure 3.2:  | Overview of the SpMM operation with $P=4$ threads. The operation proceeds by performing all $P\beta \times \beta$ local SpMM operations Y=AX+Y one blocked row at a time. The operation $A^TX$ is realized by permuting the blocking $(\beta \times P\beta \text{ blocks})$         | 65 |

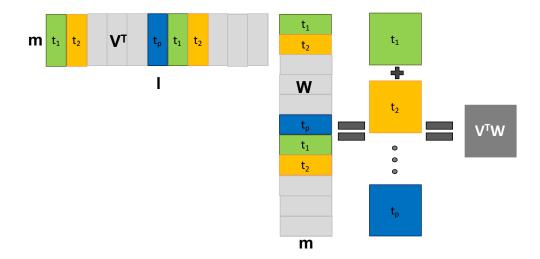

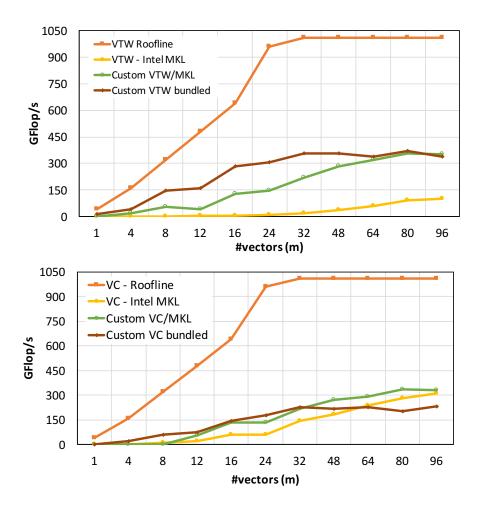

| Figure 3.3:  | Performance in GFlop/s for vector block inner product, $V^TW$ , and vector block scaling, $VX$ kernels using Intel MKL and Cray libsci libraries on a Cray XC30 system (Edison @ NERSC)                                                                                             | 72 |

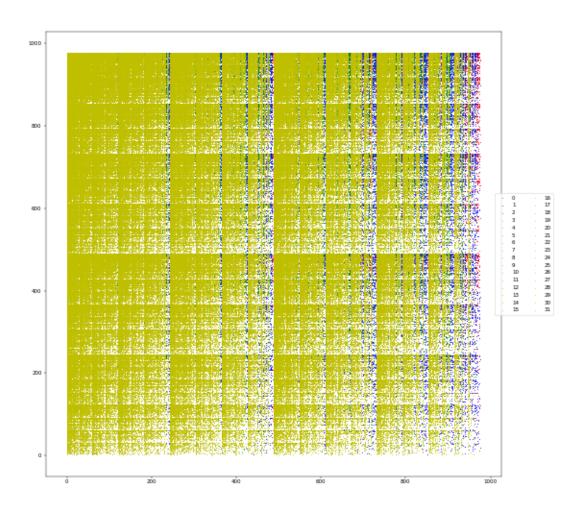

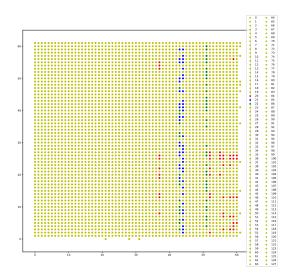

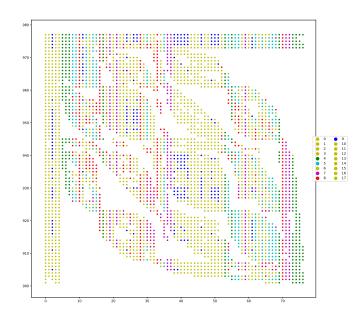

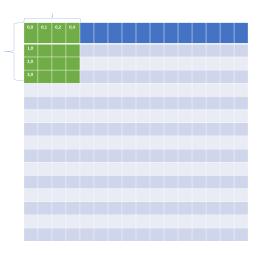

| Figure 3.4:  | Sparsity structure of the local Nm6 matrix at process 1 in an MFDn run with 15 processes. A block size of $\beta=6000$ is used. Each dot corresponds to a block with nonzero matrix elements in it. Darker colors indicate denser nonzero blocks                                    | 74 |

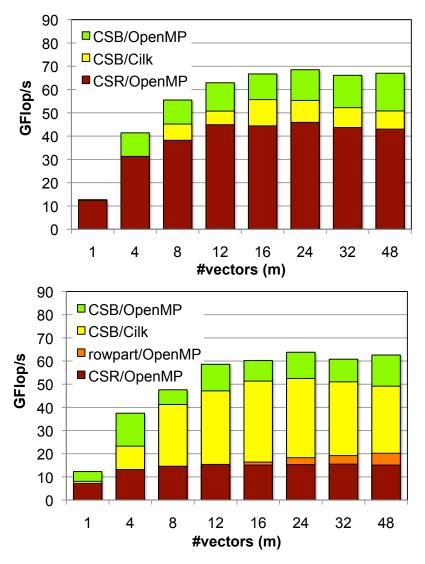

| Figure 3.5:  | Optimization benefits on Edison using the Nm6 matrix for SpMM (top) and SpMM <sup><math>T</math></sup> (bottom) as a function of $m$ (the number of vectors).                                                                                                                       | 77 |

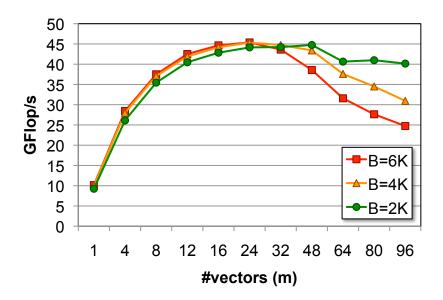

| Figure 3.6:  | Performance benefit on the combined SpMM and SpMM <sup><math>T</math></sup> operation from tuning the value of $\beta$ for the Nm8 matrix                                                                                                                                           | 80 |

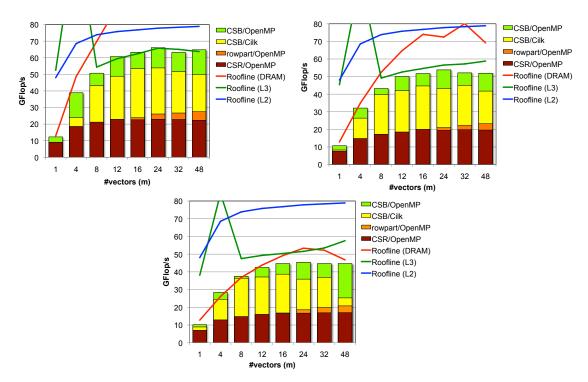

| Figure 3.7:  | SpMM and SpMM <sup><math>T</math></sup> combined performance results on Edison using the Nm6, Nm7 and Nm8 matrices (from top to bottom) as a function of $m$ (the number of vectors). We identify 3 Rooflines (one per level of memory) as per our extended roofline model for CSB  | 82 |

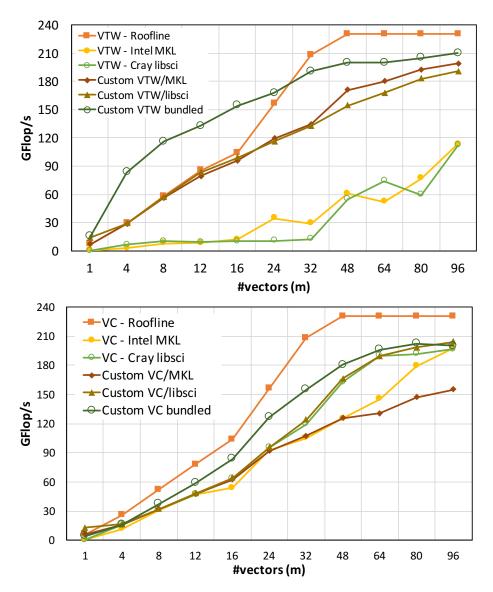

| Figure 3.8:  | Performance in GFlop/s for inner product $V^TW$ (top), and linear combination $VC$ (bottom) operations, using Intel MKL and Cray $LibSci$ libraries, as well as our custom implementations on Edison. Tall-skinny matrix sizes are $l \times m$ , where $l = 1 \mathrm{M.}$         | 84 |

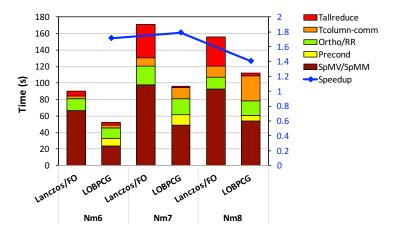

| Figure 3.9:  | Comparison and detailed breakdown of the time-to-solution using the new LOBPCG implementation vs. the existing Lanczos/FO solver. Nm6, Nm7 and Nm8 testcases executed on 15, 66, and 231 MPI ranks (6 OpenMP threads per rank), respectively, on Edison                             | 87 |

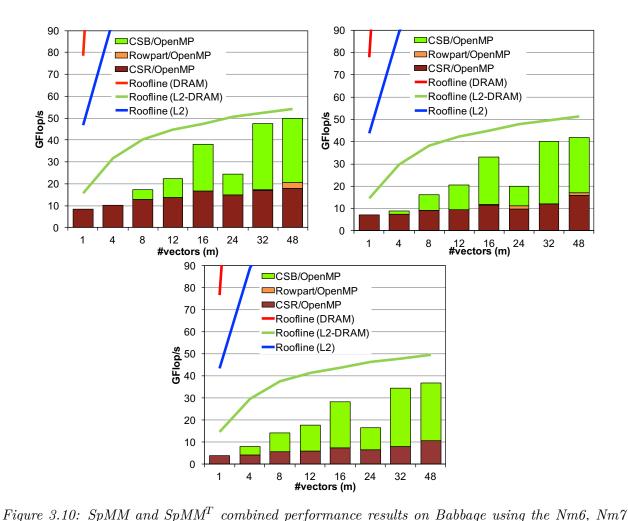

| Figure 3.10: | SpMM and SpMM <sup><math>I</math></sup> combined performance results on Babbage using the Nm6, Nm7 and Nm8 matrices (from top to bottom) as a function of $m$ (the number of vectors)                                           | 90  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.11: | Performance of $V^TW$ (top) and $VC$ (bottom) kernels, using the MKL library, as well as our custom implementations on an Intel Xeon Phi processor. Local vector blocks are $l \times m$ , where $l = 1  \text{M.} \dots \dots$ | 91  |

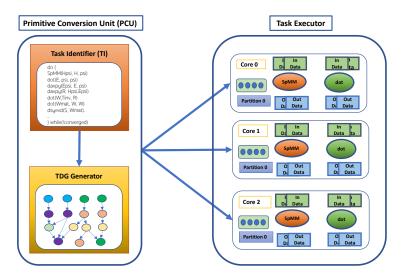

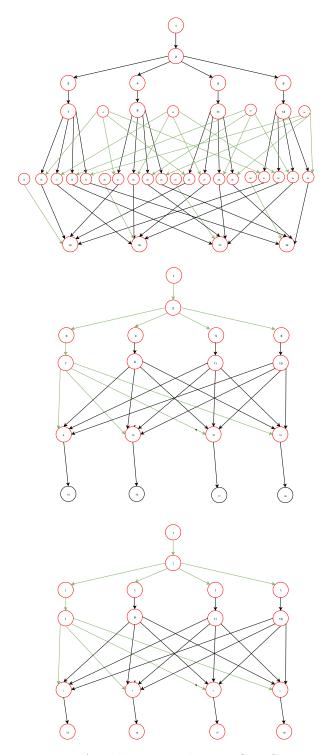

| Figure 4.1:  | Schematic overview of DeepSparse                                                                                                                                                                                                | 96  |

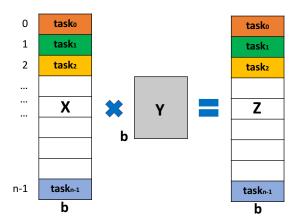

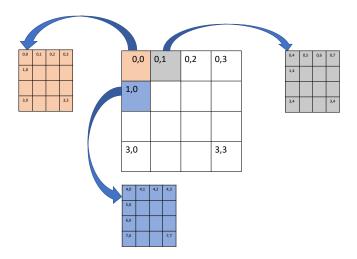

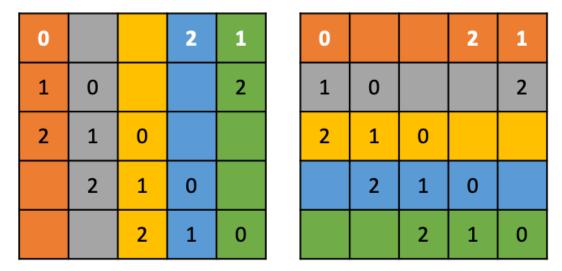

| Figure 4.2:  | Overview of input output matrices partitioning of task-based matrix multiplication kernel                                                                                                                                       | 102 |

| Figure 4.3:  | Overview of matrices partitioning of task-based SpMM kernel                                                                                                                                                                     | 102 |

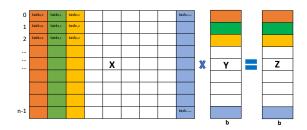

| Figure 4.4:  | Overview of matrices partitioning of task-based inner product kernel.                                                                                                                                                           | 103 |

| Figure 4.5:  | Task graph for the psudocode in listing 4.2                                                                                                                                                                                     | 103 |

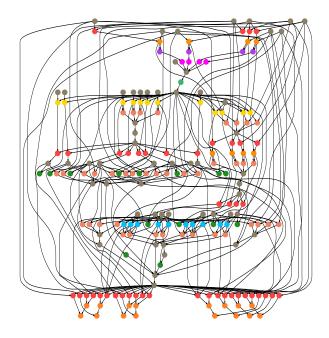

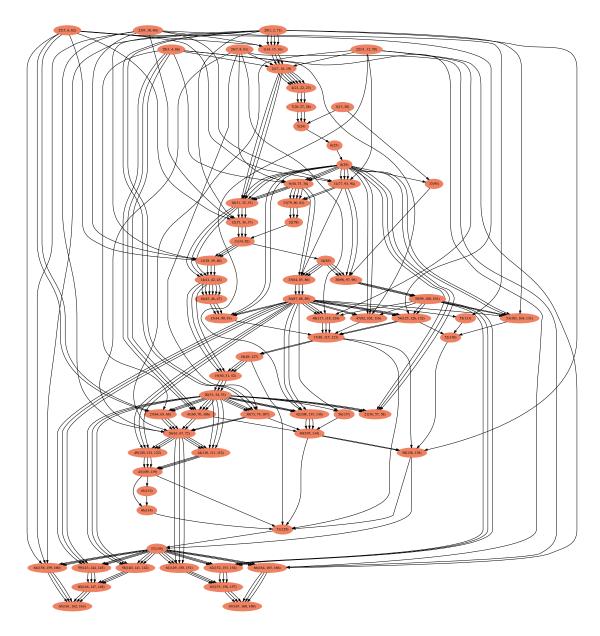

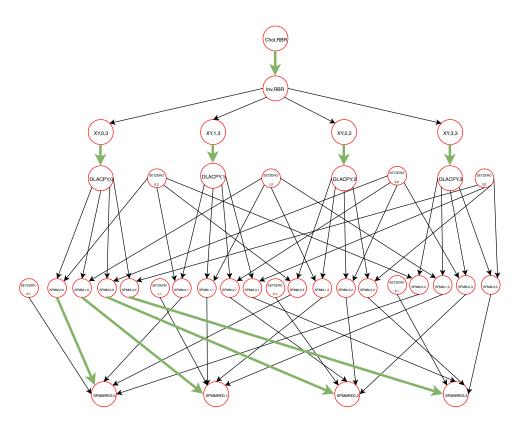

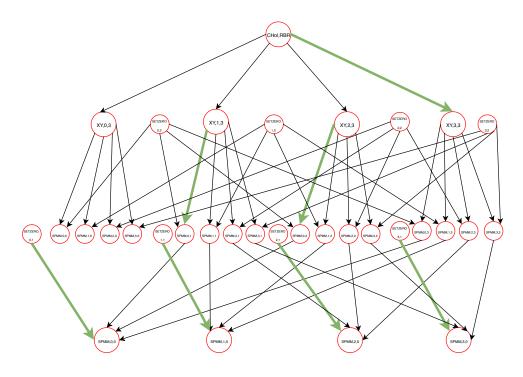

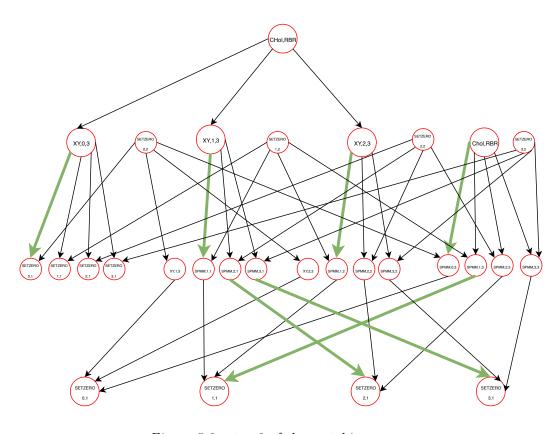

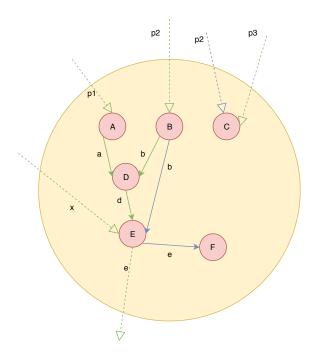

| Figure 4.6:  | A sample task graph for the LOBPCG algorithm using a small sparse matrix                                                                                                                                                        | 107 |

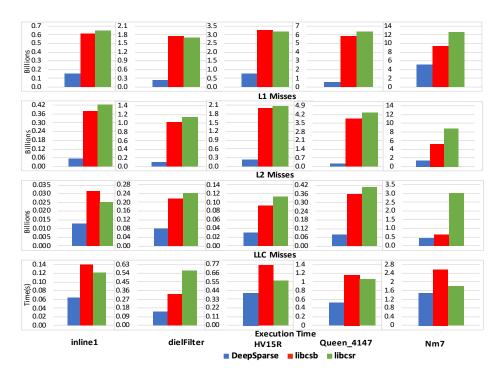

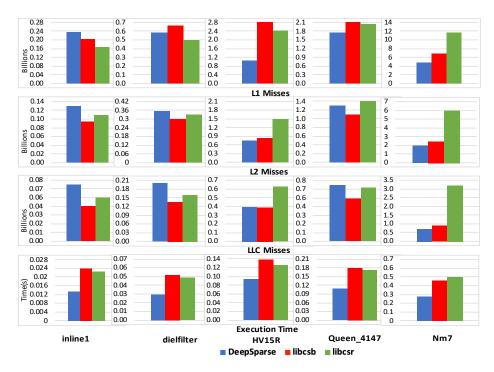

| Figure 4.7:  | Comparison of L1, L2, LLC misses and execution times between Deepsparse, libcsb and libcsr for the LOBPCG solver                                                                                                                | 110 |

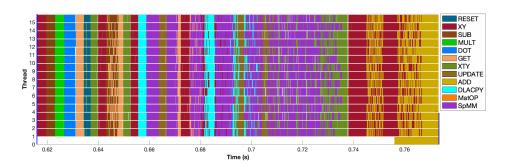

| Figure 4.8:  | LOBPCG single iteration execution flow graph of diel<br>Filter<br>V3real. $$ .                                                                                                                                                  | 110 |

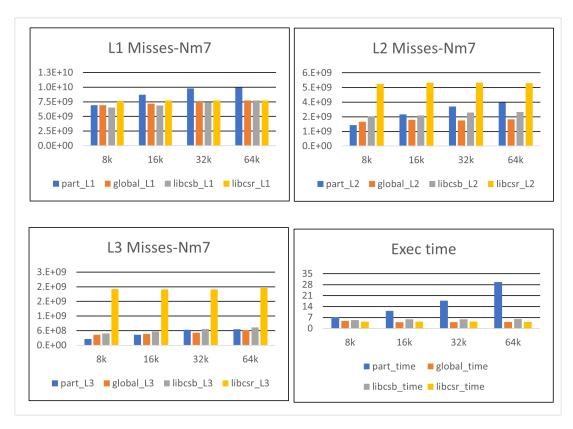

| Figure 4.9:  | Comparison of L1, L2, LLC misses and execution times between Deepsparse, libcsb and libcsr for the Lanczos solver                                                                                                               | 111 |

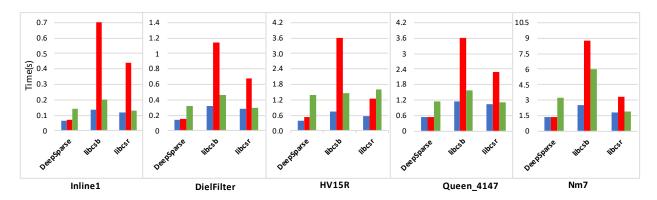

| Figure 4.10: | Comparison of execution time for different compilers between Deepspars                                                                                                                                                          | se, |

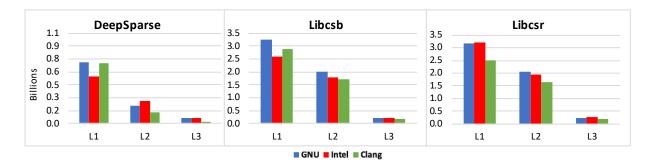

|              | libcsb and libcsr for Lanczos Algorithm. (Blue/Left: GNU, Red/Middle: Intel, Green/Right: Clang compiler.)                                                                                                                      | 112 |

| Figure 4.11: | Cache Miss comparison between compilers for HV15R                                                                                                                                                                               | 112 |

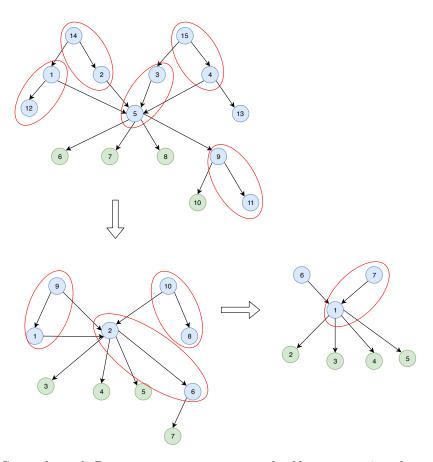

| Figure 5.1:  | Matching example                                                                                                                                                                                                                | 117 |

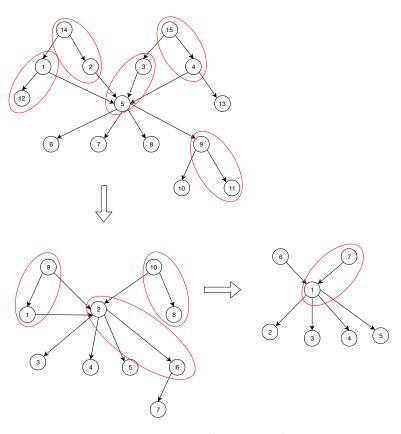

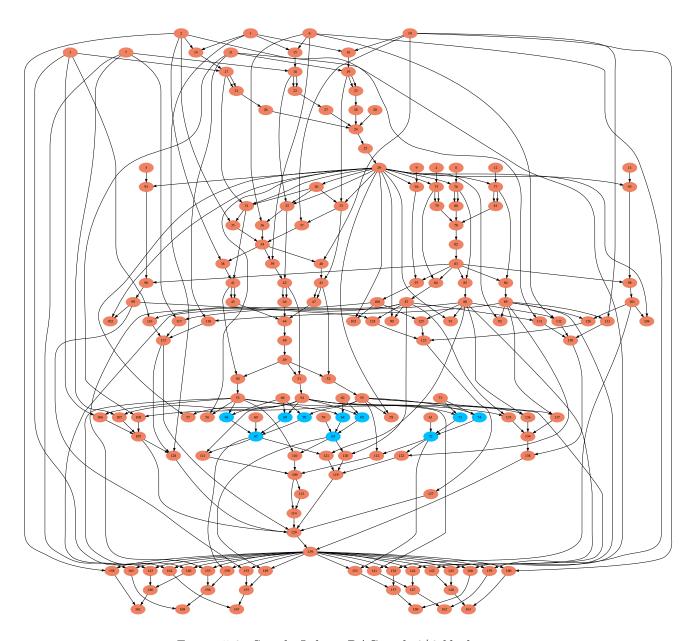

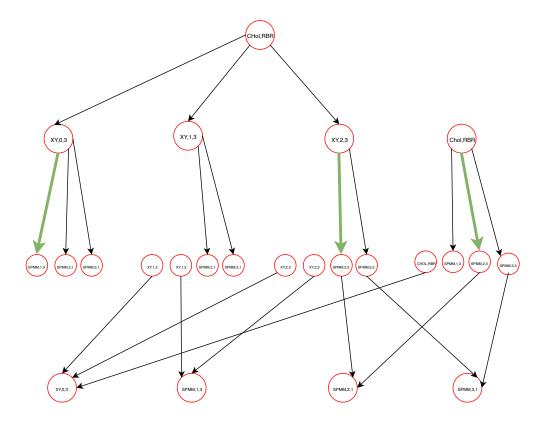

| Figure 5.2:  | Simple Lobpcg DAG with 3*3 blocks                                                                                                                                                                                               | 120 |

| Figure 5.3:  | Lobpcg graph after pre-processing with every 3 nodes in the same topological level are coarsened into one single node and the edges are kept intact                                                                             | 121 |

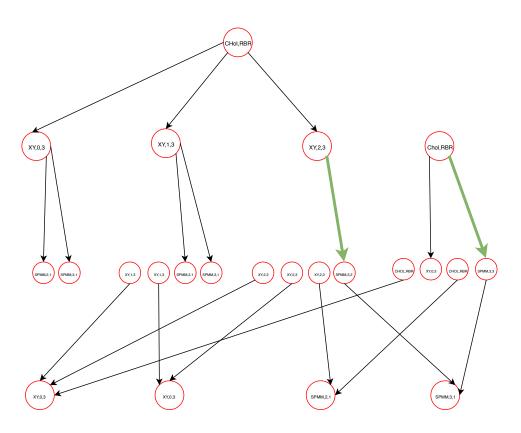

| Figure 5.4:  | Coarsed graph Partition assignment example, blue is part 0 and green is part 1                                                                           | 123       |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Figure 5.5:  | Sparse matrix block access patterns in different parts with matching                                                                                     | 126       |

| Figure 5.6:  | Sparse matrix block access patterns in different parts with pre-processing before matching                                                               | ıg<br>127 |

| Figure 5.7:  | A Small part of the Original DAG that is generated. The matched edges are shown in green color                                                           | 127       |

| Figure 5.8:  | step 2 of the matching                                                                                                                                   | 129       |

| Figure 5.9:  | step 3 of the matching                                                                                                                                   | 129       |

| Figure 5.10: | step 4 of the matching                                                                                                                                   | 130       |

| Figure 5.11: | step 5 of the matching                                                                                                                                   | 131       |

| Figure 5.12: | blocking of csb blocks to coarse multiple nodes into one node $\ .\ .\ .$                                                                                | 132       |

| Figure 5.13: | Sparse matrix block access patterns in different parts                                                                                                   | 134       |

| Figure 5.14: | Sparse matrix block access patterns in different parts                                                                                                   | 135       |

| Figure 5.15: | A cycle is created using GRLG approach                                                                                                                   | 139       |

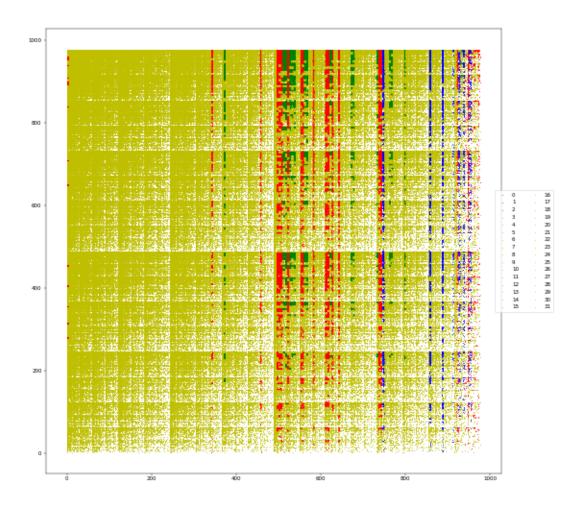

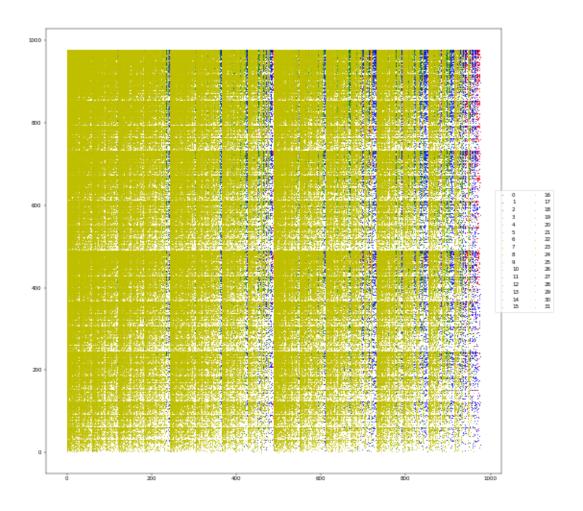

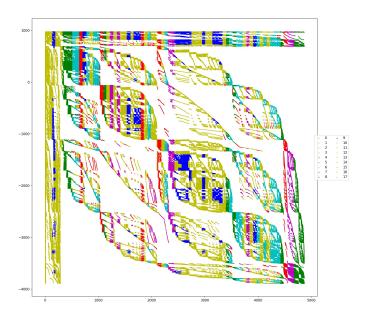

| Figure 5.16: | Partitioning of Z5 matrix with 64K block size                                                                                                            | 142       |

| Figure 5.17: | Hierarchical blocking scheme                                                                                                                             | 143       |

| Figure 5.18: | Partitioning of Z5 matrix with 1K block size                                                                                                             | 144       |

| Figure 5.19: | Memory Management in partitions                                                                                                                          | 146       |

| Figure 5.20: | Performance comparisons between different cache levels and execution time of Nm7 matrix in Haswell nodes                                                 | 148       |

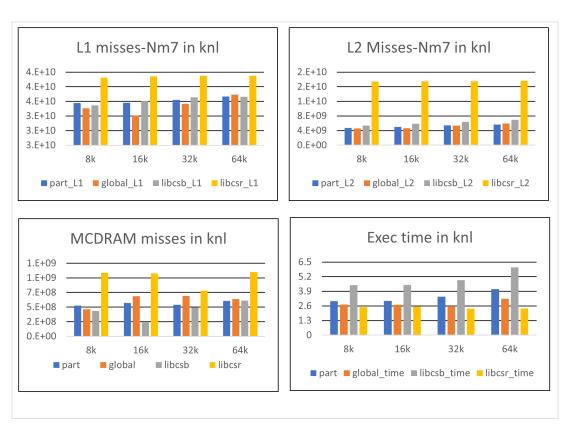

| Figure 5.21: | Performance comparisons between different cache levels and execution time of Nm7 matrix in knl nodes                                                     | 149       |

| Figure 6.1:  | Processor topology with 15 processors numbered from 0-15. Distributed in an efficient manner where each row and column has the same number of processors | 155       |

| Figure 6.2: | Processor distribution in MFDn: MPI_COMM_WORLD (top) and custom column (left) and row (right) communicator groups                                                                                                                                                                                                                                                                                                                                                    | 156                 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

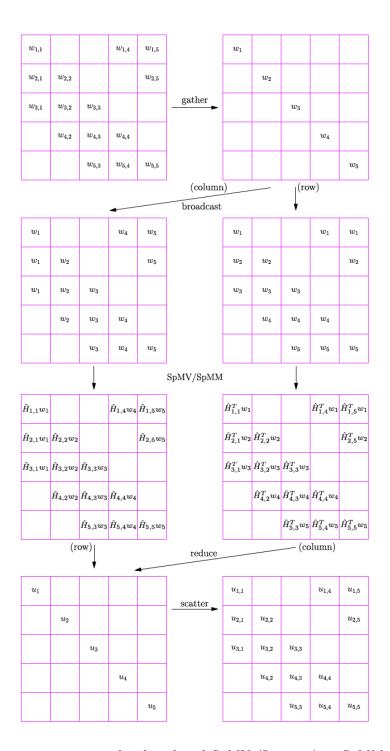

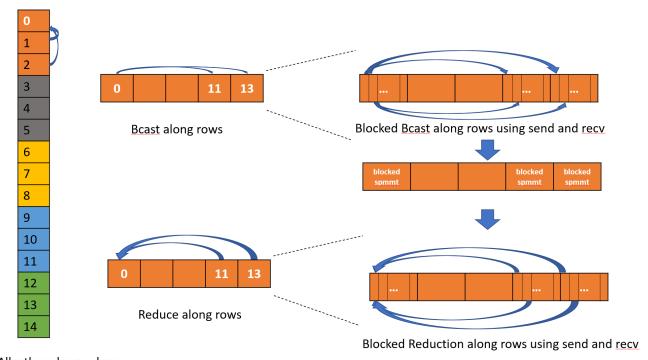

| Figure 6.3: | Communication pattern for distributed SpMV (Lanczos) or SpMM (LOBPCG) during iterative solver. In our actual implementation, we have replaced the initial Gather + Broadcast along the columns by a single call to AllGatherV, and similarly, the final Reduce + Scatter along the columns by a single call to ReduceScatter. Also, the Broadcast and Reduce along the rows is overlapping with the local SpMV and SpMV <sup>T</sup> . (Figure adapted from Ref. [4] | 157                 |

| Figure 6.4: | Random selection of the ranks                                                                                                                                                                                                                                                                                                                                                                                                                                        | 164                 |

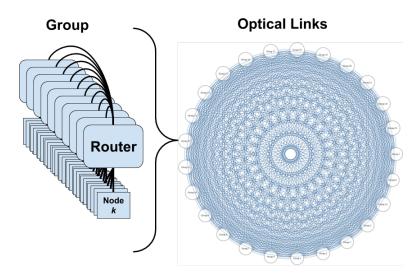

| Figure 6.5: | Illustration of a general Dragonfly topology with a single group shown on the left and the optical all-to-all connections of each group in a system shown on the right. Per the original definition of a dragonfly [5], the design within a group is not strictly specified                                                                                                                                                                                          | 167                 |

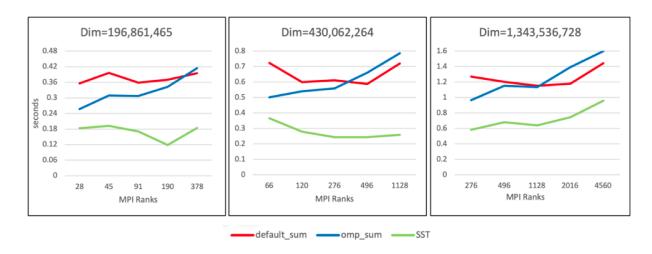

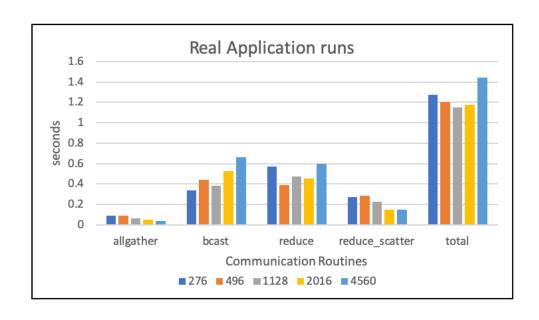

| Figure 6.6: | Total Execution time per iteration in Cori-KNL for real application using default MPI_SUM, custom OMP_SUM and SST Simulation                                                                                                                                                                                                                                                                                                                                         | 171                 |

| Figure 6.7: | Ratio of different MPI communication routines between SST simulation and communication skeleton runs with MPI_SUM. i.e. $\frac{SST\_tim}{Real\_run\_t}$                                                                                                                                                                                                                                                                                                              | $\frac{e}{ime}$ 171 |

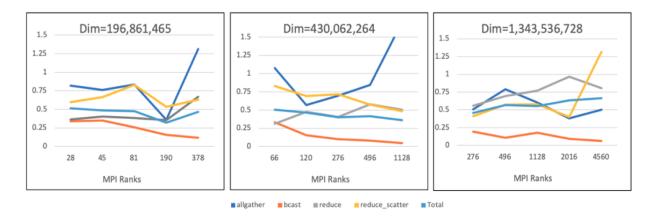

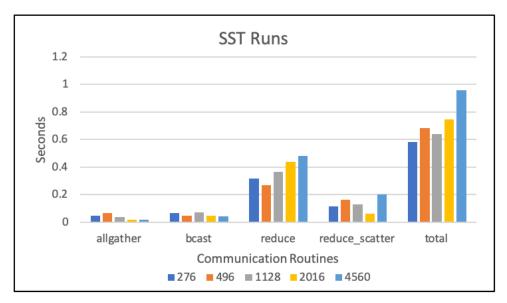

| Figure 6.8: | Communication time breakdown for a real run and SST simulation for dimension = $1,343,536,728$                                                                                                                                                                                                                                                                                                                                                                       | 174                 |

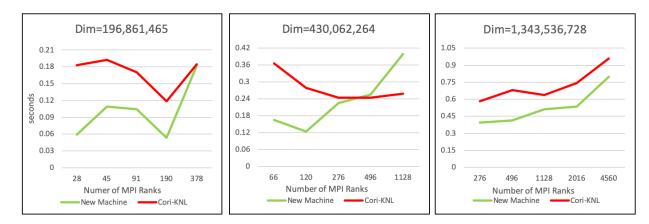

| Figure 6.9: | Timing comparison of the simulation of MFDn motif in Cori-KNL and the soon-to-be-installed Perlmutter machine with our predicted parameters                                                                                                                                                                                                                                                                                                                          | 175                 |

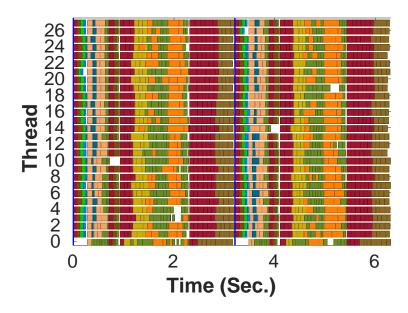

| Figure 7.1: | LOBPCG two iteration execution flow graph of nlpkkt240 matrix. SpMM is represented using orange color, XY operation is Maroon and XTY is using green color palette                                                                                                                                                                                                                                                                                                   | 180                 |

| Figure 7.2: | Example code for a blocking mpi call as an OpenMP task                                                                                                                                                                                                                                                                                                                                                                                                               | 183                 |

| Figure 7.3: | Example code for a non blocking mpi call                                                                                                                                                                                                                                                                                                                                                                                                                             | 183                 |

| Figure 7.4: | Matrix and Vector distribution in MPI ranks and efficient processor topology                                                                                                                                                                                                                                                                                                                                                                                         | 186                 |

| Figure 7.5: | Blocked Communication along the processes in the same row com-                                                                                                                                                                                                                                                                                                                                                                                                       | 188                 |

| Figure 7.6:  | Hierarchical blocked communication                                                                                                                 | 188   |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 7.7:  | Blocked broadcast code                                                                                                                             | 189   |

| Figure 7.8:  | Blocked SpMM code                                                                                                                                  | 190   |

| Figure 7.9:  | Blocked Reduction code                                                                                                                             | 191   |

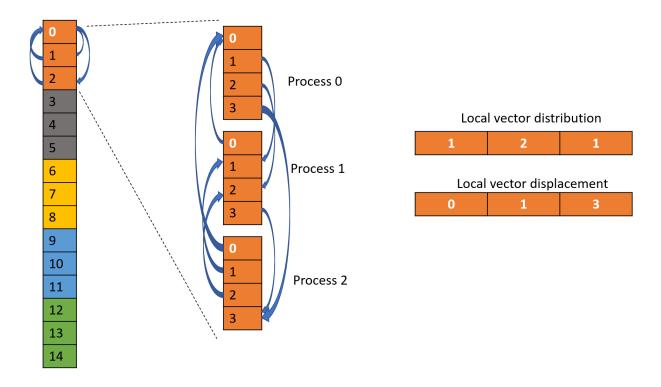

| Figure 7.10: | Custom Reduction depending on the local vector distribution                                                                                        | 192   |

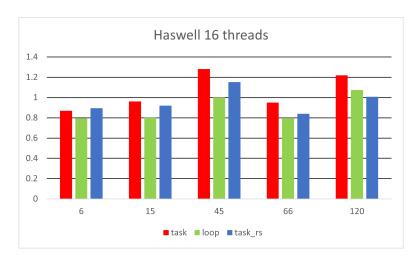

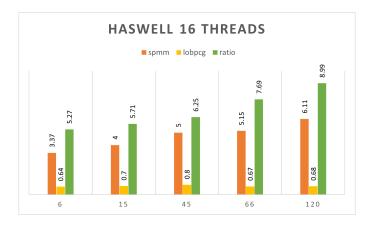

| Figure 7.11: | Comparison of execution time per iteration in Haswell 16 threads between loop parallel, task parallel and task parallel with custom reduce-scatter | 195   |

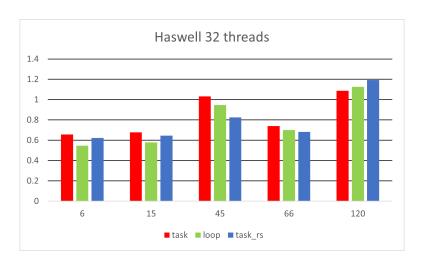

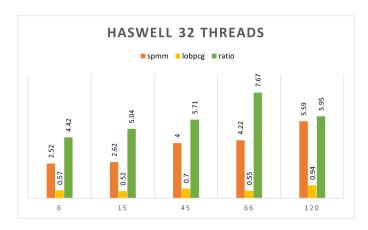

| Figure 7.12: | Comparison of execution time per iteration in Haswell 32 threads between loop parallel, task parallel and task parallel with custom reduce-scatter | 196   |

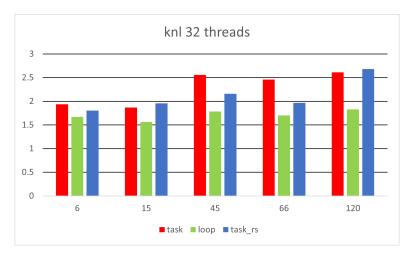

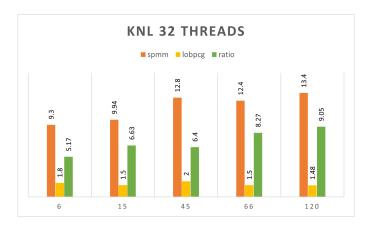

| Figure 7.13: | Comparison of execution time per iteration in knl 32 threads between loop parallel, task parallel and task parallel with custom reduce-scatter     | r 196 |

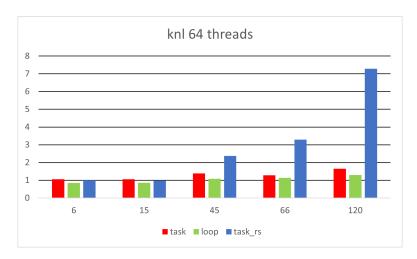

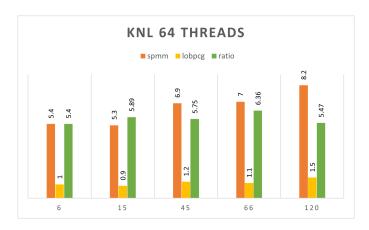

| Figure 7.14: | Comparison of execution time per iteration in knl 64 threads between loop parallel, task parallel and task parallel with custom reduce-scatter     | r 197 |

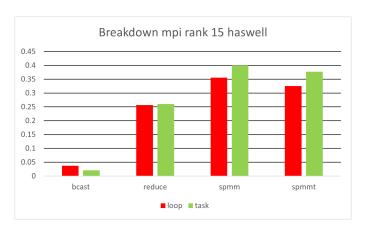

| Figure 7.15: | Breakdown of communication and computation operations with 6 mpi ranks in Haswell nodes                                                            | 198   |

| Figure 7.16: | Breakdown of communication and computation operations with 6 mpi ranks in KNL nodes                                                                | 198   |

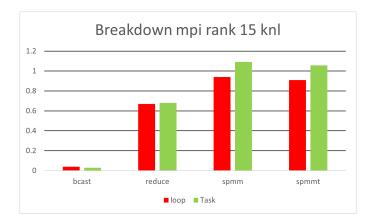

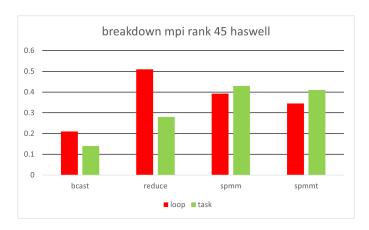

| Figure 7.17: | Breakdown of communication and computation operations with 45 mpi ranks in haswell nodes                                                           | 199   |

| Figure 7.18: | Breakdown of communication and computation operations with 45 mpi ranks in knl nodes                                                               | 199   |

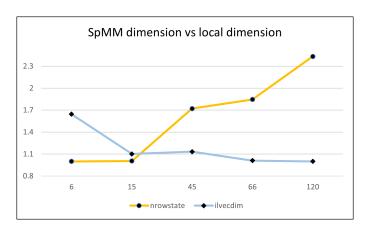

| Figure 7.19: | Change in SpMM dimension and local dimensions with the increase of mpi ranks                                                                       | 200   |

| Figure 7.20: | Ratio of LOBPCG compared to SpMM in Haswell nodes with 16 threads                                                                                  | 200   |

| Figure 7.21: | Ratio of LOBPCG compared to SpMM in Haswell nodes with 32 threads                                                                                  | 201   |

Figure 7.22: Ratio of LOBPCG compared to SpMM in knl nodes with 32 threads 201

Figure 7.23: Ratio of LOBPCG compared to SpMM in knl nodes with 64 threads 202

#### LIST OF ALGORITHMS

| Algorithm 1: | SpMM kernel                                                    | 1          |

|--------------|----------------------------------------------------------------|------------|

| Algorithm 2: | Lanczos Algorithm in Exact Arithmetic                          | 16         |

| Algorithm 3: | LOBPCG Algorithm (for simplicity, without a preconditioner) 10 | 18         |

| Algorithm 4: | Ember pseudocode for the MFDn communication motif              | <b>j</b> 4 |

# Chapter 1

# INTRODUCTION AND

# **MOTIVATION**

# 1.1 Background And Related Work

Eigenvalue calculation is one of the most important parts in application of numerical linear algebra. Almost all kinds of scientific research whether it is nuclear astrophysics or molecular dynamics, whether this is applied machine learning or life science, calculating eigenvalues often becomes one of the primary requirements theoretically. Also with the emerging of Artificial Intelligence and Machine learning in the current computing world, eigenvalue calculations plays a big part. The naive way to find the eigenvalues of a matrix is to find all the roots of the characteristic polynomial of the matrix. But in large scale analysis where the matrix dimensions are in thousands or millions, this is fairly impractical to find the eigenvalues in such a way. Hence a number of iterative algorithms have been developed over the years. These methods work by repeatedly refining approximations to the eigenvectors or eigenvalues, and can be terminated whenever the approximations reach a suitable degree of accuracy. Iterative methods form the basis of much of modern day eigenvalue computation.

Since a graph represented in an adjacency matrix format is essentially a sparse matrix, graph algorithms can also be expressed in the language of sparse linear algebra. In fact, recent studies have shown that graph algorithms expressed in this way achieve significantly better

performance than alternative abstractions [6]. To simplify the presentation, we use a unified nomenclature for both, and use the term sparse matrix to also refer to the network structure in a graph. The term nonzeros will refer to the nonzero matrix elements in sparse matrices or edge meta-data (e.g., weights) in graphs. Finally, we overload the term vector in sparse matrix computations to also refer to the array of vertex properties in graph computations. Most fundamental operation in sparse linear algebra is thought to be the multiplication of a sparse matrix with a vector (SpMV), as it forms the main computational kernel for several applications (e.g., the solution of partial differential equations (PDE) [7] and the Schrödinger Equation [8] in scientific computing, spectral clustering [9] and dimensionality reduction [10] in machine learning, and the Page Rank algorithm [11] in graph analytics). The Roofine model by Williams et al. [12] suggests that the performance of SpMV kernel is ultimately bounded by the memory bandwidth. Consequently, performance optimizations to increase cache utilization and reduce data access latencies for SpMV has drawn significant interest [13, 14, 15, 16, 17, 18, 19, 20, 21], which is a rather incomplete list of related work on this topic.

A closely related kernel is the multiplication of a sparse matrix with multiple vectors (SpMM) which constitutes the main operation in block solvers, e.g., the block Krylov subspace methods and block Jacobi-Davidson method. SpMM has much higher arithmetic intensity than SpMV and can effciently leverage wide vector execution units. As a result, SpMM-based solvers has recently drawn significant interest in scientific computing [22, 23, 24, 25, 26]. SpMM also finds applications naturally in machine learning where several features (or eigenvectors) of sparse matrices are needed [10, 9]. Although SpMM has a significantly higher arithmetic intensity than SpMM, the extended Roofline model that we recently proposed suggests that cache bandwidth, rather than the memory bandwidth, can

still be an important performance limiting factor for SpMM [22]. Multiplication of sparse matrices (SpGEMM) and sparse matrix times sparse vector (SpMSV) operation also find applications in important problems. SpGEMM is the main kernel in the algebraic multi-grid method [27], and the Markov Clustering algorithm, while SpMSV is the main building block for breadth-first search, bipartite graph matching, and maximal independent set algorithms.

## 1.2 Emergence Of Deep Memory Hierarchies

Given the widening gap between memory system and processor performance [28], irregular data access patterns and low arithmetic intensities of sparse matrix computations have effectively made them "memory-bound" computations. Furthermore, the downward trend in memory space and bandwidth per core in high performance computing (HPC) systems [29] has paved the way for a deepening memory hierarchy. For example, many-core processors (i.e., GPUs and Xeon Phis) have their own high-bandwidth (but limted size) device memories (HBM). NVRAM storages have recently emerged to alleviate issues (such as cost, capacity, energy consumption and resiliency) associated with the DRAM technology. Consequently, ash memory and 3D-XPoint memory have already found wide adoption as a storage-class cache between DRAM and disk systems, and they are being adopted as memory-class storages complementing DRAM in modern HPC systems.

In Fig. 1.1, we give an abstract view of the assumed underlying memory hierarchy, along with some hardware specifications based on current technology. Our target architectures are many-core processors such as GPUs and Xeon Phis, which are essentially the cornerstones of big data analytics and scientific computing. While exact specifications and number of layers change as architectures evolves, the underlying principle of memory hierarachy stays

Figure 1.1: Memory hierarchy in deep memory architectures

the same: Going further away from the processor, memory capacity increases at the expense of increased latency and reduced bandwidth. Thus, minimizing data movement across layers of the memory and overlapping data movement with computations are keys to achieving high performance in sparse matrix computations. While we mainly focus on parallelism and performance on a single node, developed techniques and software will be complementary to those aimed at enabling distributed memory parallelism for sparse matrix computations and graphs (such as Par-METIS, Xtra- PuLP, etc.), or manual partitionings specified by a user. Hence, the footprint of applications that can benefit from this project will be significant.

In data analytics and scientific computing, total available memory is often a limiting factor. Hence, data management is an important due to both the size of the data involved and the complexity of the program ow. As an example, in Fig. 3, we give the pseudocode for the locally optimal block preconditioned conjugate gradient algorithm (LOBPCG), a widely used block eigensolver [30]. SpMM of the sparse matrix H and block vector, despite being an expensive step, is only one part of the computation in line 4. In terms of memory, while the H matrix takes up considerable space, when a large number of eigenpairs are needed (e.g. dimensionality reduction, spectral clustering or quantum many-body problems), memory needed for block vector can be comparable to or even greater than that of H. In addition, other block vectors (residual R, preconditioned residual W, previous direction P), block

vectors from the previous iteration and the preconditioning matrix T (if available) must be stored, and accessed at each iteration. Clearly, orchestrating the data movement in a deep memory hierarchy to attain an efficient implementation can become a daunting task for a domain scientist.

In fact, considering the complete range of solvers that sparse matrix computations arise in, LOBPCG algorithm is a relatively simple case. For instance, when performing Singular Value Decompositions (SVD), each node would need to perform operations pertaining also to the transpose MT (or complex conjugate M) matrix of the sparse partition that they own [38], which must be applied on the result of the application of M over the source vector. The interior eigenvalue problem is another example illustrating complexities in a real application. An effective way to accelerate convergence to eigenpairs in a desired range is to build polynomial filters [65] (e.g., [a3M3 + a2M2 + a1M]x is a 3rd order matrix polynomial), which require several applications of a sparse matrix over the source vector in each iteration. Finally, an SpGEMM kernel or sparse LU factorization represent significantly more complex computations, as computations associated with nonzeros form a complex dependency graph in these cases. We propose a comprehensive framework that can effciently handle complex and irregular (due to sparsity) task depedencies arising in a wide variety of applications. In addition to conventional applications involving static sparse matrices, we envision our framework to be generic enough to support incremental algorithms used to to tackle streaming (or online) problems [34, 69, 93]. Such applications are common in data analytics, e.g., to analyze dynamic web graphs or social networks, or incrementally incorporate user feedback.

For our work first we target an application called Sky3d which works on a dense matrix. Then we shift our interest to sparse matrix iterative eigensolvers. We start with the Sky3d application which is a density functional theory approach to study different kinds of nuclear shapes. After a successful exploration of dense matrix linear algebra libraries we worked on a sparse matrix iterative eigensolver code named MFDn. In that project we optimized the sparse matrix multiple vector kernels using a new storage format for sparse matrices. Taking that experience, we developed a shared memory framework for iterative eigensolvers using task parallelism. At first we used a default scheduler from OpenMP libraries but we also wanted to have our own schedule for tasks. We studied some graph partitioners and created custom partitions and task orders for execution. We wanted to extend the framework for a distributed solver like MFDn. Hence we first studied the communication behavior of MFDn using a simulator called SST. Looking at the observations, we introduced communication tasks in our framework which overlaps the communication and computations. Now I will present some motivations, background studies for all the projects.

## 1.3 Optimizing Sky3D

Compact objects in space such as neutron stars are great test laboratories for nuclear physics as they contain all kinds of exotic nuclear matter which are not accessible in experiments on earth [31, 32]. Among interesting kinds of astromaterial is the so called nuclear "pasta" phase [33, 34] which consists of neutrons and protons embedded in an electron gas. The naming arises from the shapes, e.g. rods and slabs, which resemble the shapes of the Italian pasta (spaghetti and lasagna).

Nuclear pasta is expected in the inner crust of neutron stars in a layer of about 100 m at a radius of about 10 km, at sub-nuclear densities. Since the typical length scale of a neutron or a proton is on the order of 1 fm, it is impossible to simulate the entire system. The usual

strategy is to simulate a small part of the system in a finite box with periodic boundary conditions. While it is feasible to perform large simulations with semi-classical methods such as Molecular Dynamics (MD) [35, 36, 37, 38, 39, 40, 41] involving 50,000 or even more particles or the Thomas-Fermi approximation [42, 43, 44, 45], quantum mechanical (QM) methods which can yield high fidelity results have been limited to about 1000 nucleons due to their immense computational costs [46, 47, 48, 49, 50, 51, 52, 53].

The side effects of using small boxes in QM methods are twofold: First, the finite size of the box causes finite-volume effects, which have an observable influence on the results of a calculation. Those effects have been studied and can be suppressed by introducing the twist-averaged boundary conditions [51]. More importantly though, finite boxes limit the possible resulting shapes of the nuclear pasta because the unit cell of certain shapes might be larger than the maximum box size. For instance, in MD simulations [54], slabs with certain defects have been discovered. Those have not been observed in QM simulations because they only manifest themselves in large boxes. To observe such defects, we estimate that it is necessary to increase the number of simulated particles (and the corresponding simulation box volume) by about an order of magnitude.

In this work, we focus on the microscopic nuclear density functional theory (DFT) approach to study nuclear pasta formations. The nuclear DFT approach is a particularly good choice for nuclear pasta. The most attractive property is the reliability of its answers over the whole nuclear chart [55, 56], and yet it is computationally feasible for applications involving the heaviest nuclei and even nuclear pasta matter, because the interaction is expressed through one-body densities and the explicit n-body interactions do not have to be evaluated.

In contrast to finite nuclei that are usually calculated employing a harmonic oscillator finite-range basis [57, 58] using mostly complete diagonalization of the basis functions to solve

the self-consistent equations, nuclear pasta matter calculations have to be performed in a suitable basis with an infinite range. We use the DFT code Sky3D [59], which represents all functions on an equidistant grid and employs the damped gradient iteration steps, where fast Fourier transforms (FFTs) are used for derivatives, to reach a self-consistent solution. This code is relatively fast compared to its alternatives and incorporates all features necessary to perform DFT calculations with modern functionals, such as the Skyrme functionals (as used here). Since Sky3D can be used to study static and time-dependent systems in 3d without any symmetry restrictions, it can be applied to a wide range of problems. In the static domain it has been used to describe a highly excited torus configuration of <sup>40</sup>Ca [60] and also finite nuclei in a strong magnetic field as present in neutron stars [61]. In the time-dependent context, it was used for calculations on nuclear giant resonances [62, 63], and on the spin excitation in nuclear reactions [64]. The Wigner function, a 6 dimensional distribution function, and numerical conservation properties in the time-dependent domain have also been studied using Sky3D [65, 66].

For the case of time-dependent problems, the Sky3D code has already been parallelized using MPI. The time-dependent iterations are simpler to parallelize, because the treatment of the single particles are independent of each other and can be distributed among the nodes. Only the mean field has to be communicated among the computational nodes. On the other hand, accurate computation of nuclear ground states, which we are interested in, requires a careful problem decomposition strategy and organization of the communication and computation operations as discussed below. However, only a shared memory parallel version of Sky3D (using OpenMP) exists to this date. In this work, we present algorithms and techniques to achieve scalable distributed memory parallelism in Sky3D using MPI.

# 1.4 Optimization Of Blocked Eigensolver For Sparse Matrix

We found out that for dense matrices there are some very optimized numerical libraries for distributed memory. Being a relatively well studied area, these libraries have been serving the scientific community for quite a while. In our work we observed strong scaling using the highly optimized ScLAPACK library. But we also noticed that for sparse matrices there are a lot of room for improvement. The choice of numerical algorithms and how efficiently they can be implemented on high performance computer (HPC) systems critically affect the time-to-solution for large-scale scientific applications. Several new numerical techniques or adaptations of existing ones that can better leverage the massive parallelism available on modern systems have been developed over the years. Although these algorithms may have slower convergence rates, their high degree of parallelism may lead to better time-to-solution on modern hardware [24]. In the next work, we consider the solution of the quantum many-body problem using the configuration interaction (CI) formulation. We present algorithms and techniques to significantly speed up eigenvalue computations in CI by using a block eigensolver and optimizing the key computational kernels involved.

The quantum many-body problem transcends several areas of physics and chemistry. The CI method enables computing the wave functions associated with discrete energy levels of these many-body systems with high accuracy. Since only a small number of low energy states are typically needed to compute the physical observables of interest, a partial diagonalization of the large CI many-body Hamiltonian is sufficient.

More formally, we are interested in finding a small number of extreme eigenpairs of a

large, sparse, symmetric matrix:

$$x_i = \lambda x_i, \quad i = 1, \dots, m, \quad m \ll N.$$

(1.1)

Iterative methods such as the Lanczos and Jacobi–Davidson [67] algorithms, as well as their variants [68, 69, 70], can be used for this purpose. The key kernels for these methods can be crudely summarized as (repeated) sparse matrix–vector multiplications (SpMV) and orthonormalization of vectors (level-1 BLAS). As alternatives, block versions of these algorithms have been developed [71, 72, 73] which improves the arithmetic intensity of computations at the cost of a reduced convergence rate and increased total number of matrix–vector operations [74]. In block methods, SpMV becomes a sparse matrix multiple vector multiplication (SpMM) and vector operations become level-3 BLAS operations.

Performance of SpMV is ultimately bounded by memory bandwidth [75]. The widening gap between processor performance and memory bandwidth significantly limits the achievable performance in several important applications. On the other hand, in SpMM, one can make use of the increased data locality in the vector block and attain much higher FLOP rates on modern architectures. Gropp et al. was the first to exploit this idea by using multiple right hand sides for SpMV in a computational fluid dynamics application [23]. SpMM is one of the core operations supported by the auto-tuned sequential sparse matrix library OSKI [20]. OSKI's shared memory parallel successor, pOSKI, currently does not support SpMM [76]. More recently, Liu et al. [24] investigated strategies to improve the performance of SpMM <sup>1</sup> using SIMD (AVX/SSE) instructions on modern multicore CPUs. Their driv-

<sup>&</sup>lt;sup>1</sup>Liu et al. actually uses the name GSpMV for "generalized" SpMV. We refrain from doing so because the same name has been used in conflicting contexts such as SpMV for graph algorithms where the scalar operations can be arbitrarily overloaded.

ing application is the motion simulation of biological macromolecules in solvent using the Stokesian dynamics method. Röhrig-Zöllner et al. [25] discuss performance optimization techniques for the block Jacobi–Davidson method to compute a few eigenpairs of large-scale sparse matrices, and report reduced time-to-solution using block methods instead of single vector counterparts, particularly for problems in quantum mechanics and PDEs.

Our work differs from previous efforts substantially, in part due to the immense size of the sparse matrices involved. We exploit symmetry to reduce the overall memory footprint, and offer an efficient solution to perform SpMM on a sparse matrix and its transpose (SpMM<sup>T</sup>) with roughly the same performance [22]. This is achieved through a novel thread parallel SpMM implementation, CSB/OpenMP, which is based on the compressed sparse block (CSB) framework [77] (Sect. 3.3). We demonstrate the efficiency of CSB/OpenMP on a series of CI matrices where we obtain  $3-4\times$  speedup over the commonly used compressed sparse row (CSR) format. To estimate the performance characteristics and better understand the bottlenecks of the SpMM kernel, we propose an extended Roofline model to account for eache bandwidth limitations (Sect. 3.3).

In this work, we extend a previous work (presented in [22]) by considering an end-toend optimization of a block eigensolver implementation. As will be discussed in Sect. 3.7,

the performance of the tall-skinny matrix operations in block eigensolvers is critical for an

excellent overall performance. We observe that the implementations of these level-3 BLAS

operations in optimized math libraries perform significantly below expectations for typical

matrix sizes encountered in block eigensolvers. We propose a highly efficient thread parallel

implementation for inner product and linear combination operations that involve tall-skinny

matrices and analyze the resulting performance.

To demonstrate the merits of the proposed techniques, we incorporate the CSB/OpenMP

implementation of SpMM and optimized tall-skinny matrix kernels into a LOBPCG [73] based solver in MFDn, an advanced nuclear CI code [2, 78, 3]. We demonstrate through experiments with real-world problems that the resulting block eigensolver can outperform the widely used Lanczos algorithm (based on single vector iterations) with modern multicore architectures (Sect. 3.8.8). We also analyze the performance of our techniques on an Intel Xeon Phi Knights Corner (KNC) processor to assess the feasibility of our implementations for future architectures.

While we focus on nuclear CI computations, the impact of optimizing the performance of key kernels in block iterative solvers is broader. For example, spectral clustering, one of the most promising clustering techniques, uses eigenvectors associated with the smallest eigenvalues of the Laplacian of the data similarity matrix to cluster vertices in large symmetric graphs [79, 80]. Due to the size of the graphs, it is desirable to exploit the symmetry, and for a k-way clustering problem, k eigenvectors are needed, where typically  $10 \le k \le 100$ , an ideal range for block eigensolvers. Block methods are also used in solving large-scale sparse singular value decomposition (SVD) problems [81], with most popular methods being the subspace iteration and block Lanzcos. SVDs are critical for dimensionality reduction in applications like latent semantic indexing [82]. In SVD, singular values are obtained by solving the associated symmetric eigenproblem that requires subsequent SpMM and SpMM $^T$  computations in each iteration [83]. Thus, our techniques are expected to have a positive impact on the adoption of block solvers in closely related applications.

# 1.5 Inrtroducing the DeepSparse Framework

Sparse matrix computations, in the form of solvers for systems of equations, eigenvalue problems or matrix factorizations, constitute the main kernel in fields as diverse as computational fluid dynamics (CFD), quantum many-body problems, machine learning and graph analytics. The scale of problems in these scientific applications typically necessitates execution on massively parallel architectures. Moreover, sparse matrices come in very different forms and properties depending on application area. However, due to the irregular data access patterns and low arithmetic intensities of sparse matrix computations, achieving high performance and scalability is very difficult. These challenges are further exacerbated by the increasingly complex deep memory hierarchies of the modern architectures as they typically integrate several layers of memory storage. While exact specifications and number of layers change as architectures evolve, the underlying principle of memory hierarchy stays the same: Going farther away from the processor, memory capacity increases at the expense of increased latency and reduced bandwidth. As such, minimizing data movement across layers of the memory and overlapping data movement with computations are keys to achieving high performance in sparse matrix computations.

Unlike its dense matrix analogue, the state of the art for sparse matrix computations is lagging far behind. The widening gap between the memory system and processor performance, irregular data access patterns and low arithmetic intensities of sparse matrix computations have effectively made them "memory-bound" computations. Furthermore, the downward trend in memory space and bandwidth per core in high performance computing (HPC) systems [29] has paved the way for a deepening memory hierarchy. Thus, there is a dire need for new approaches both at the algorithmic and runtime system levels for sparse

matrix computations.

In this work, we propose a novel sparse linear algebra framework, named *DeepSparse*, which aims to accelerate sparse solver codes on modern architectures with deep memory hierarchies. Our proposed framework differs from existing work in two ways. First, we propose a holistic approach that targets all computational steps in a sparse solver rather than narrowing the problem into a single kernel, e.g., sparse matrix vector multiplication (SpMV) or sparse matrix multiple vector multiplication (SpMM). Second, we adopt a fully integrated task-parallel approach while utilizing commonly used sparse matrix storage schemes.

In a nutshell, DeepSparse provides a GraphBLAS plus BLAS/LAPACK-like frontend for domain scientists to express their algorithms without having to worry about the architectural details (e.g., memory hierarchy) and parallelization considerations (i.e., determining the individual tasks and their scheduling) [84, 85, 86]. DeepSparse automatically generates and expresses the entire computation as a task dependency graph (TDG) where each node corresponds to a specific part of a computational kernel and edges denote control and data dependencies between computational tasks. We chose to build DeepSparse on top of OpenMP [87] because OpenMP is the most commonly used shared memory programming model, but more importantly it supports task-based data-flow programming abstraction. As such, DeepSparse relies on OpenMP for parallel execution of the TDG.

We anticipate two main advantages of DeepSparse over a conventional bulk synchronous parallel (BSP) approach where each kernel relies on loop parallelization and is optimized independently. First, DeepSparse would be able to expose better parallelism as it creates a global task graph for the entire sparse solver code. Second, since the OpenMP runtime system has explicit knowledge about the TDG, it may be possible to leverage a pipelined execution of tasks that have data dependencies, thereby leading to better utilization of the

hardware cache.

# 1.6 Exploring Custom Schedule For Tasks Using Graph Partition

In the DeepSparse framework we generate a global task graph. In our executor we use appropriate OpenMP task dependencies with proper memory offsets and sizes to make the task parallel implementation coherent across the entire iteration. OpenMP looks at the in-out dependencies and generates a direct acyclic graph underneath after solving those dependencies. In case of a dependency of a task gets resolved, that task is(or can be) pulled from the task pool by OpenMP engine.

Although we saw that OpenMP does a great job with memory utilization over all level of memories, it is still beyond our control. OpenMP is generating the DAG itself and resolving themselves. Whenever the data dependencies of a task is resolved and it is not dependent on any other task for its execution, it can be immediately pulled and executed. But this might not be optimal scenario if we think from memory usage perspective. A task which does not have any relation with the tasks that are active at the moment can be immediately executed once a thread gets free regardless of its memory input and outputs. Hence there is a possibility of a task which would improve the memory usage with the input already being in the lower level of the memory and having cache hits reduces. The probability of cache misses increases with this kind of scheduling.