### MODULARIZED MULTILEVEL AND Z-SOURCE POWER CONVERTER AS RENEWABLE ENERGY INTERFACE FOR VEHICLE AND GRID-CONNECTED APPLICATIONS

By

Dong Cao

### A DISSERTATION

Submitted to Michigan State University in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

**Electrical Engineering**

2012

#### ABSTRACT

### MODULARIZED MULTILEVEL AND Z-SOURCE POWER CONVERTER AS RENEWABLE ENERGY INTERFACE FOR VEHICLE AND GRID-CONNECTED APPLICATIONS

#### By

#### Dong Cao

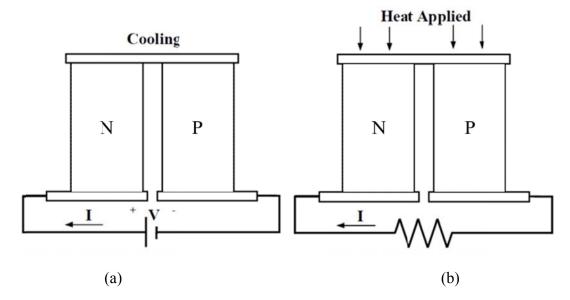

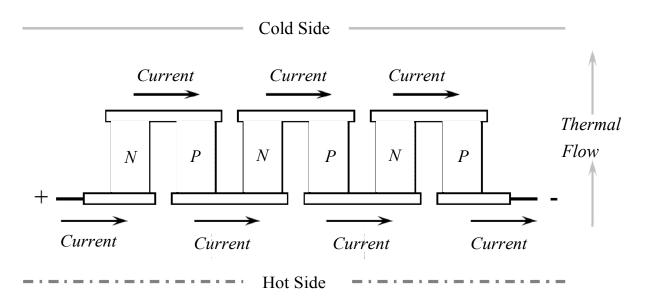

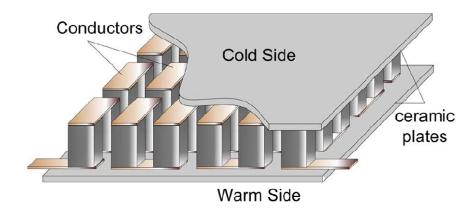

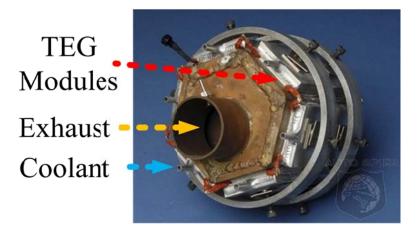

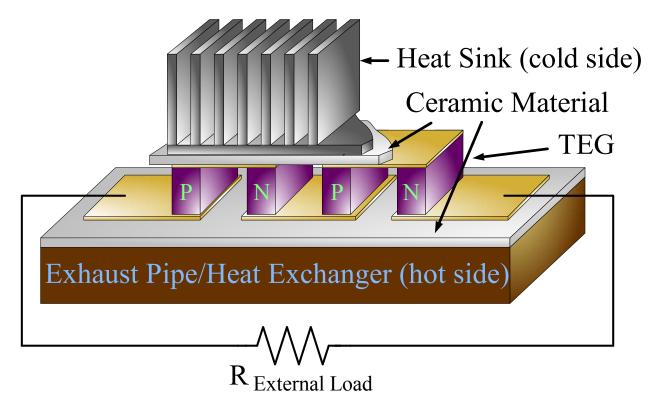

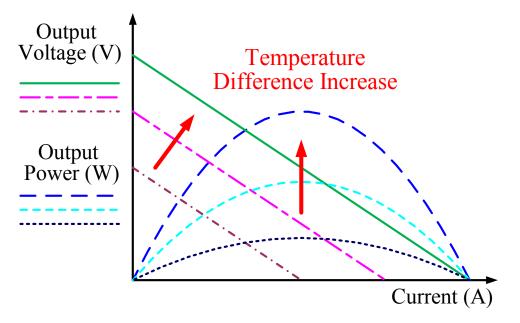

Due the energy crisis and increased oil price, renewable energy sources such as photovoltaic panel, wind turbine, or thermoelectric generation module, are used more and more widely for vehicle and grid-connected applications. However, the output of these renewable energy sources varies according to different solar radiation, wind speed, or temperature difference, a power converter interface is required for the vehicle or grid-connected applications.

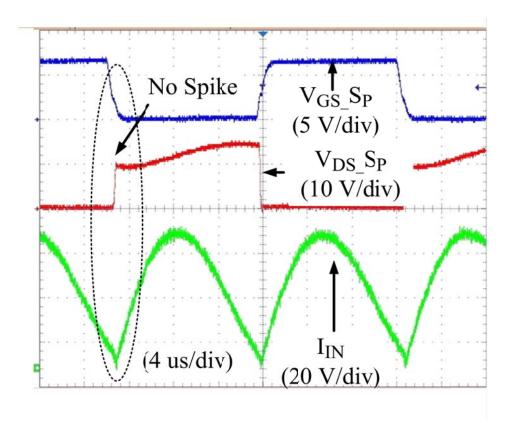

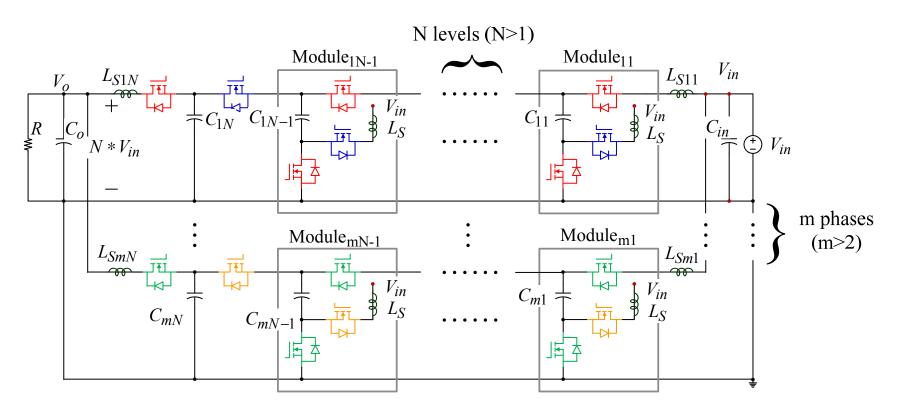

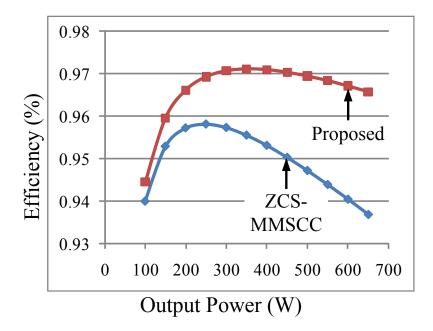

Thermoelectric generation (TEG) module as a renewable energy source for automotive industry is becoming very popular recently. Because of the inherent characteristics of TEG modules, a low input voltage, high input current and high voltage gain dc-dc converters are needed for the automotive load. Traditional high voltage gain dc-dc converters are not suitable for automotive application in terms of size and high temperature operation. Switched-capacitor dc-dc converters have to be used for this application. However, high voltage spike and EMI problems exist in traditional switched-capacitor dc-dc converters. Huge capacitor banks have to be utilized to reduce the voltage ripple and achieve high efficiency. A series of zero current switching (ZCS) or zero voltage switching switched-capacitor dc-dc converters have been proposed to overcome the aforementioned problems of the traditional switched-capacitor dc-dc converters. By using the proposed soft-switching strategy, high voltage spike is reduced, high EMI noise is restricted, and the huge capacitor bank is eliminated. High efficiency, high power density and high temperature switched-capacitor dc-dc converters could be made for the TEG

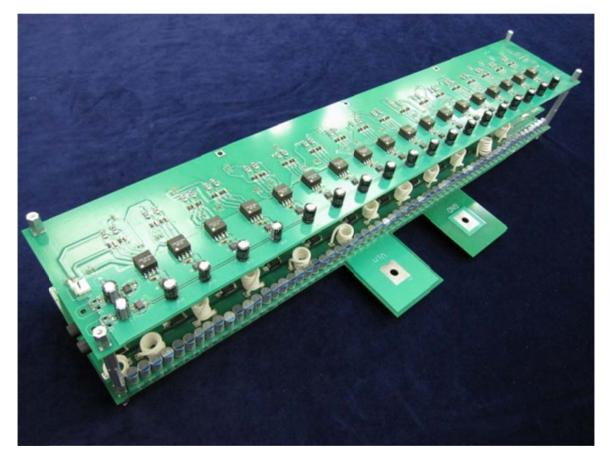

interface in vehicle applications. Several prototypes have been made to validate the proposed circuit and confirm the circuit operation.

In order to apply PV panel for grid-connected application, a low cost dc-ac inverter interface is required. From the use of transformer and safety concern, two different solutions can be implemented, non-isolated or isolated PV inverter. For the non-isolated transformer-less solution, a semi-Z-source inverter for single phase photovoltaic systems has been proposed. The proposed semi-Z-source inverter utilizes only two switching devices with doubly grounded feature. The total cost have been reduced, the safety and EMI issues caused by the high frequency ground current are solved. For the transformer isolated solution, a boost half-bridge dc-ac micro-inverter has been proposed. The proposed boost half-bridge dc-dc converter utilizes only two switching devices with zero voltage switching features which is able to reduce the total system cost and power loss. Dedicated to: my wife, Ying Ding and our unborn baby

## ACKNOWLEDGEMENTS

First of all, I would like to thank my advisor Prof. Fang Z. Peng for his insightful comments, strict requirements, and continuous support during my graduate studies. There is a Chinese proverb: "Good pupils are to be brought up by strict teachers". Thanks to his high standard requirements, I have the chance to reinvestigate the familiar circuits and propose all these new circuits.

I would like to express my appreciation to my committee members, Dr. Joydeep Mitra, Dr. Bingsen Wang, and Dr. Guoming Zhu for their enlightening class, valuable suggestions and serving on my PH.D committee.

I would also like to thank Dr. Zhaoming Qian, my first mentor in power electronics. His guidance and encouragement are always so valuable in the past and in the future. And I also thank so much to my colleagues working at Dr. Qian's lab in Zhejiang University in China, Fan Zhang, Xinping Ding, Xinke Wu, Liqing Tong, Shuitao Yang Chen Zhao, Huijie Zhao, Naixin Kuang, Lingxiao Xue, for their valuable discussions and helps in both study and life.

I thank so much all the PELab colleagues, especially to Dr. Lihua Chen for his help on understanding IGBT gate drive, Dr. Honnyong Cha, Dr. Yi Huang, Dr. Baoming Ge, Dr. Dan Wang, Dr. Yuan Li, Wei Qian, Xi Lu, Qingsong Tang, for their valuable discussions and priceless help in both study and life.

Finally I would like to especially appreciate my wife Ying Ding with our unborn baby for her unconditional love and support, my parents and grandparents for their care and support. There is no word can express my appreciation to them.

# TABLE OF CONTENTS

| LIST OF TABLES                                                           | X                     |

|--------------------------------------------------------------------------|-----------------------|

| LIST OF FIGURES                                                          | xi                    |

| CHAPTER 1 Introduction and Motivation                                    | 1                     |

| 1.1 Background                                                           |                       |

| 1.1.1 TEG Modules Basic Structures and Potential Automotive Applications |                       |

| 1.1.2 TEG Modules Electrical Characteristics                             |                       |

| 1.2 Power Electronic Challenges for TEG                                  |                       |

| 1.3 Summary of Previous Works                                            |                       |

| 1.3.1 Traditional Step-up DC-DC Converter                                | 13                    |

| 1.3.2 Switched-Capacitor DC-DC Converter                                 |                       |

| 1.4 Outline of Dissertation                                              |                       |

| CHAPTER 2 Zero Current Switching Multilevel Modular Switched-Capacitor   | DC-DC                 |

| Converter                                                                |                       |

| 2.1 Introduction                                                         |                       |

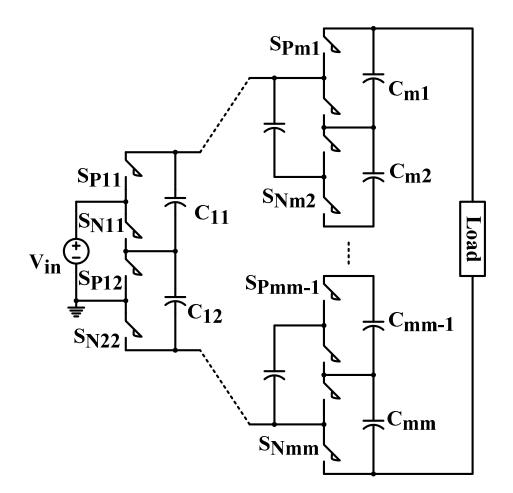

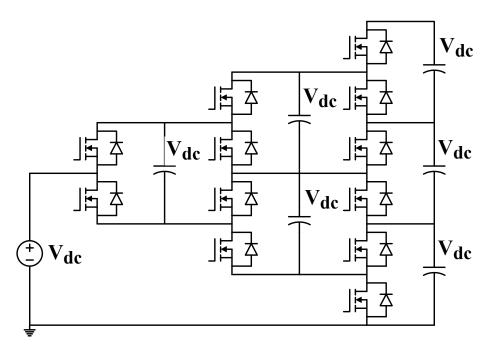

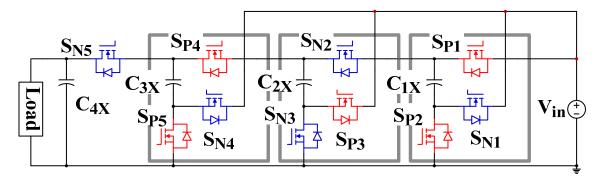

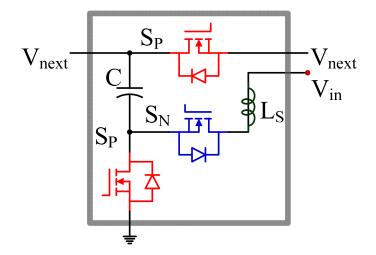

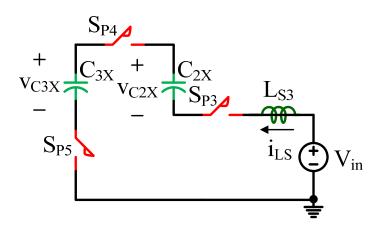

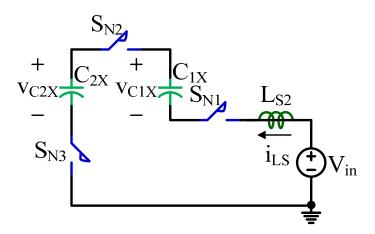

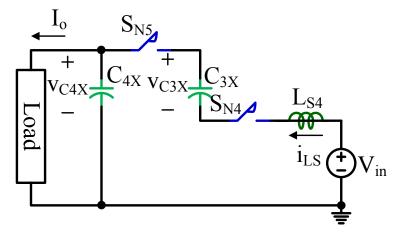

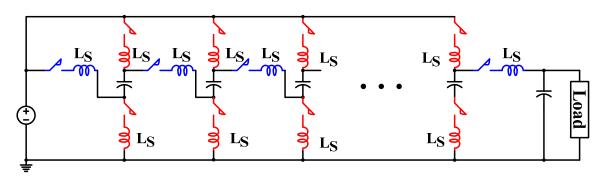

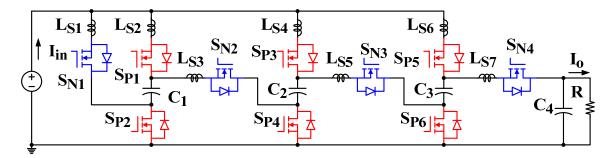

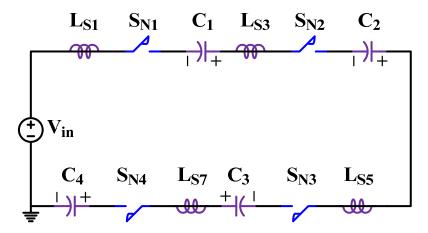

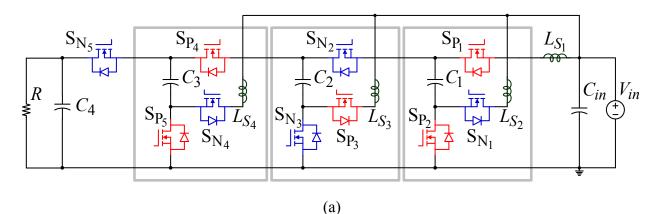

| 2.2 Proposed Circuit Topology                                            |                       |

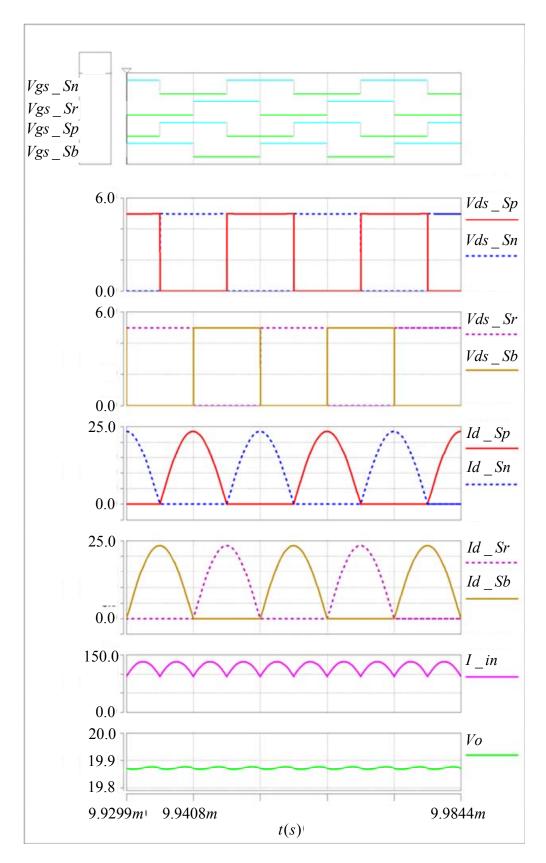

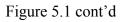

| 2.3 Operation Principle                                                  |                       |

| 2.3.1 State I                                                            | 50                    |

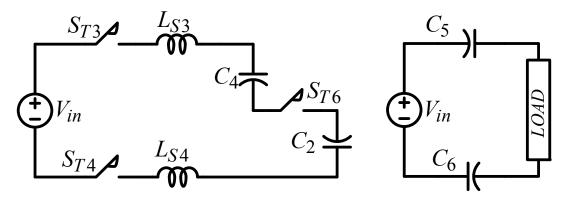

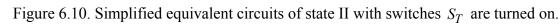

| 2.3.2 State II                                                           | 53                    |

| 2.4 Design Guidelines                                                    |                       |

| 2.4.1 Capacitance                                                        |                       |

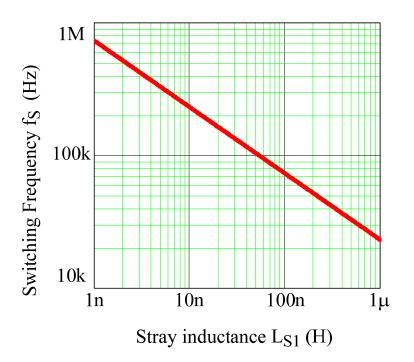

| 2.4.2 Stray inductance                                                   |                       |

| 2.4.3 Switching frequency                                                | 59                    |

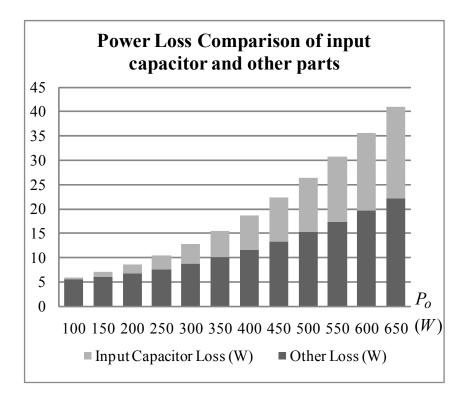

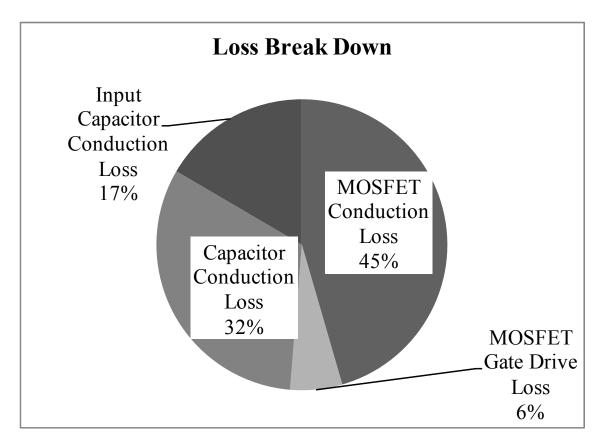

| 2.5 Power Loss Analysis                                                  | 59                    |

| 2.5.1 Power device loss                                                  | 59                    |

| 2.5.2 Capacitor conduction loss                                          | 60                    |

| 2.5.3 Total power loss                                                   | 61                    |

| 2.6 Simulation and Experiment Results                                    |                       |

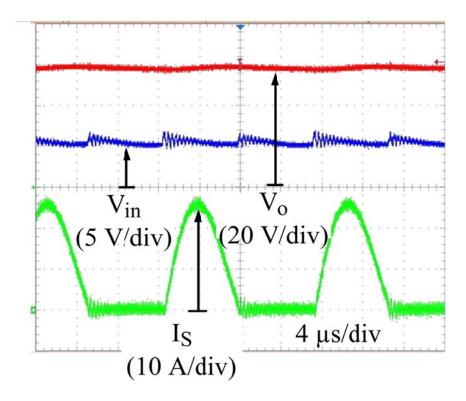

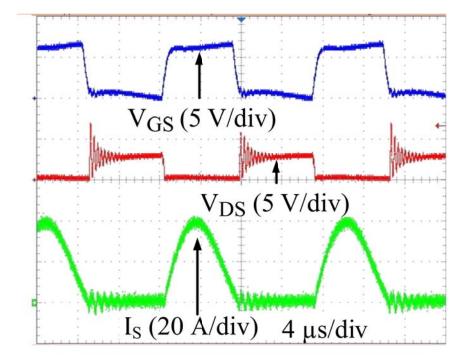

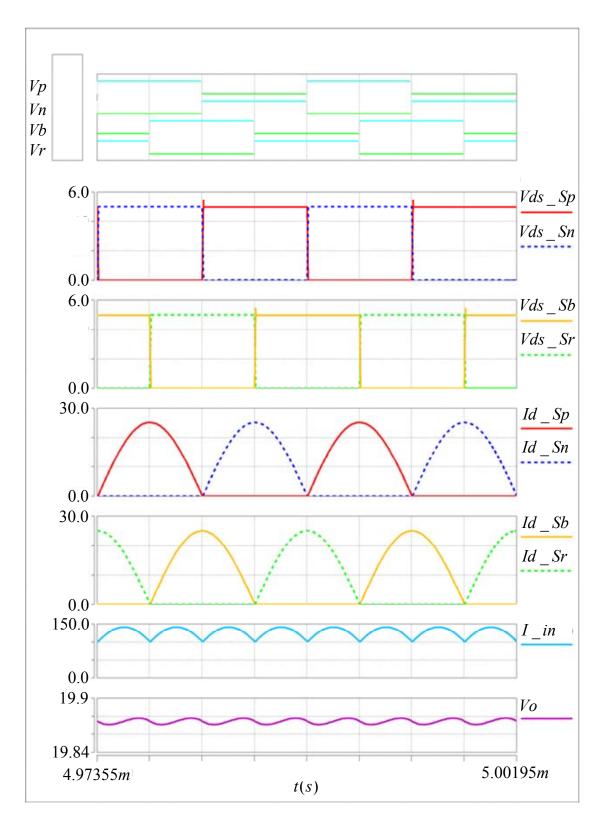

| 2.6.1 A 150 W four-level ZCS-MMSCC prototype                             |                       |

| 2.7 Conclusion                                                           |                       |

| CHAPTER 3 A Family of ZCS Switched-Capacitor DC-DC Converters            | 68                    |

| 3.1 Introduction                                                         |                       |

| 3.2 Proposed ZCS Switched-Capacitor DC-DC Converter Family               |                       |

| <ul><li>3.3 Operation Principle</li></ul>                                |                       |

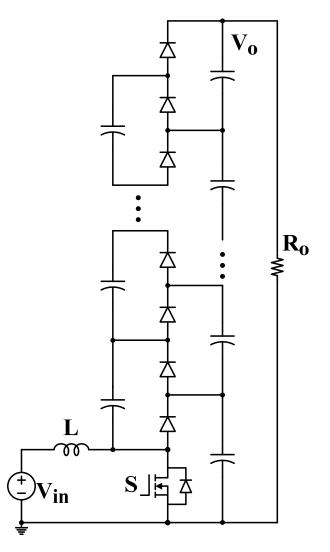

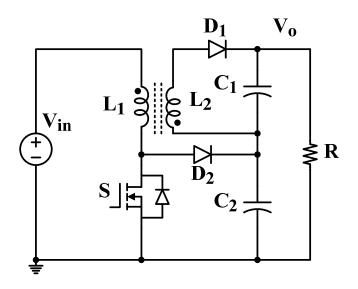

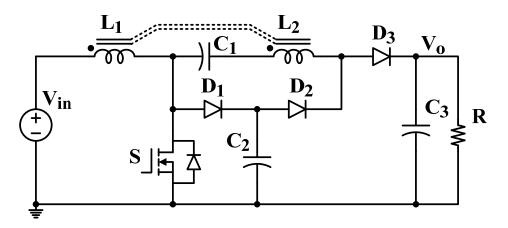

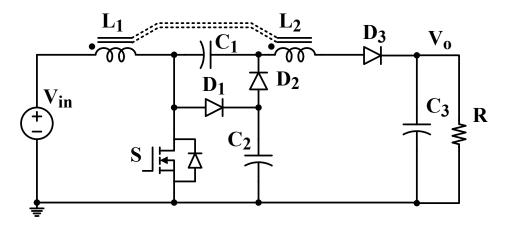

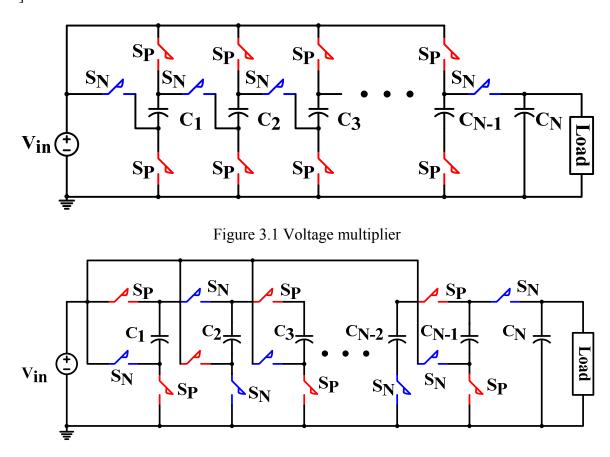

| 3.3.1 ZCS voltage multiplier                                             |                       |

| 3.3.2 ZCS voltage doubler                                                |                       |

| 3.4 Design Considerations                                                |                       |

| 3.4.1 ZCS voltage multiplier                                             |                       |

| 3.4.2 ZCS voltage doubler                                                |                       |

| 3.5 Simulation and Experiment Results                                    |                       |

| 3.5.1 ZCS voltage multiplier                                             |                       |

|                                                                          | · · · · · · · · · · - |

| 3.5.2 ZCS voltage doubler                                                   |     |

|-----------------------------------------------------------------------------|-----|

| 3.6 Conclusion                                                              |     |

|                                                                             |     |

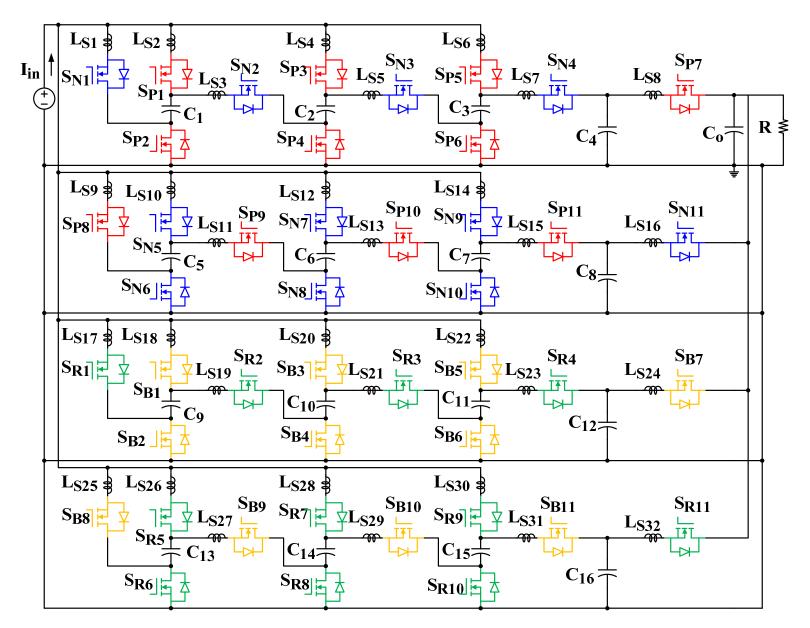

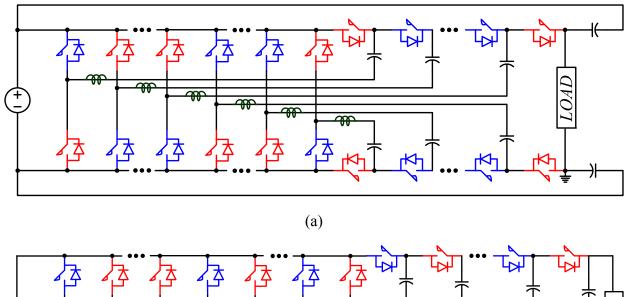

| CHAPTER 4 Multiphase Multilevel Modular DC-DC Converter for High Curr       |     |

| Gain TEG Application                                                        |     |

| 4.1 Background                                                              |     |

| 4.2 Introduction                                                            |     |

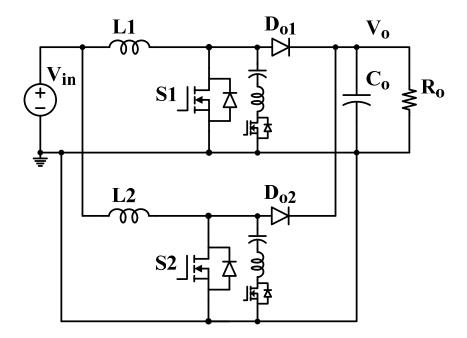

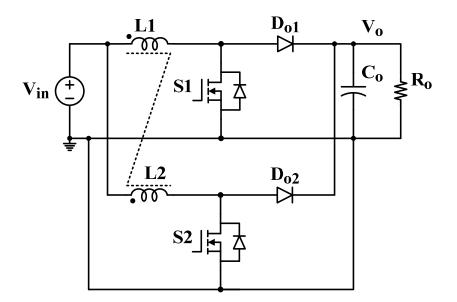

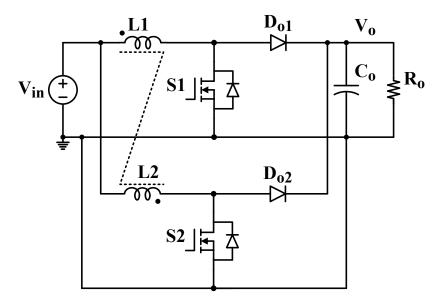

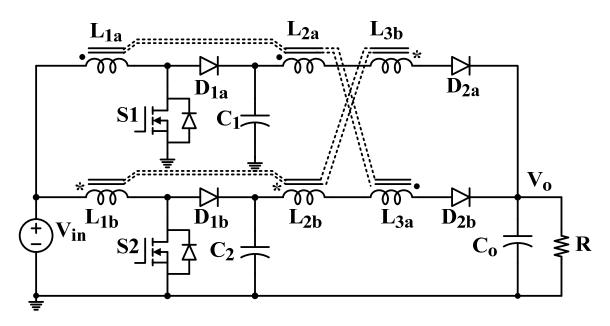

| 4.3 Proposed Circuit and Operation Principles                               |     |

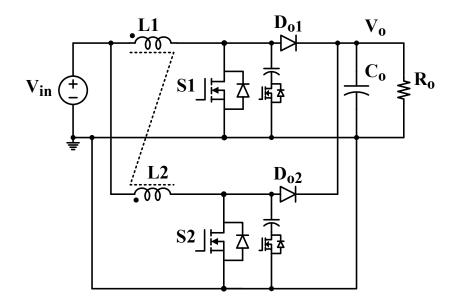

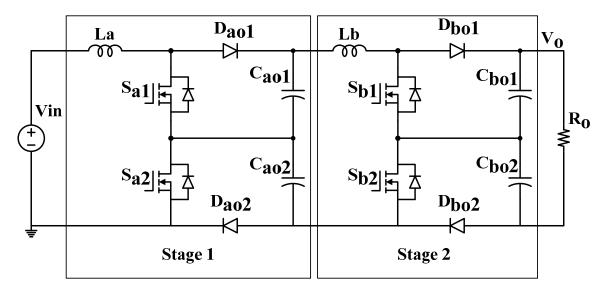

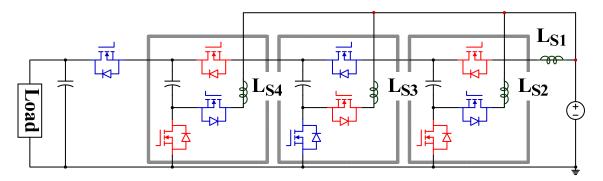

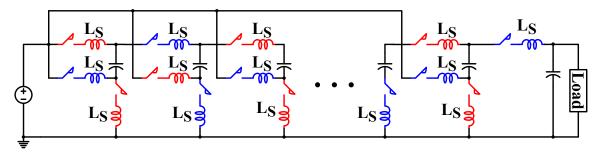

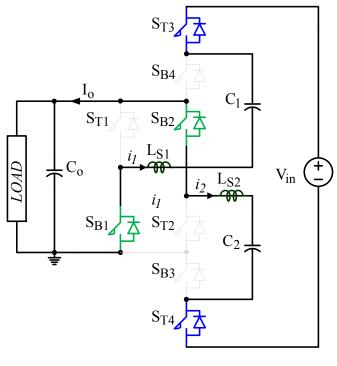

| 4.3.1 Multiphase ZCS-MMSCC with continuous input current                    |     |

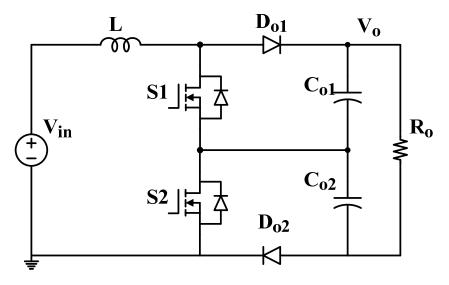

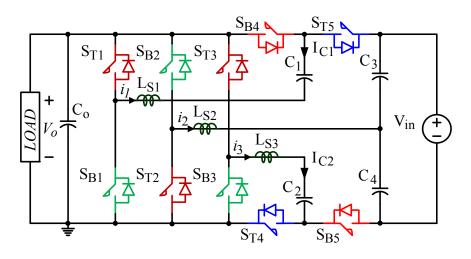

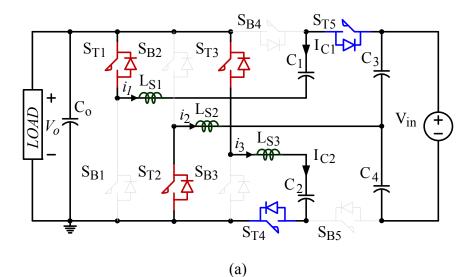

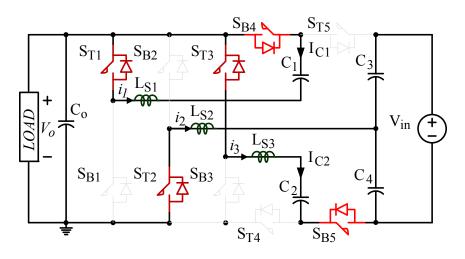

| 4.3.2 Multiphase ZCS voltage multiplier with continuous input current       |     |

| 4.4 Operation Principles                                                    |     |

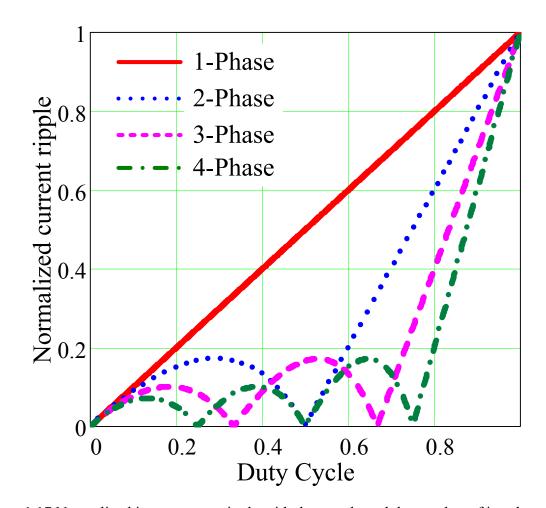

| 4.5 Current Ripple Comparison and Power Loss Analysis                       |     |

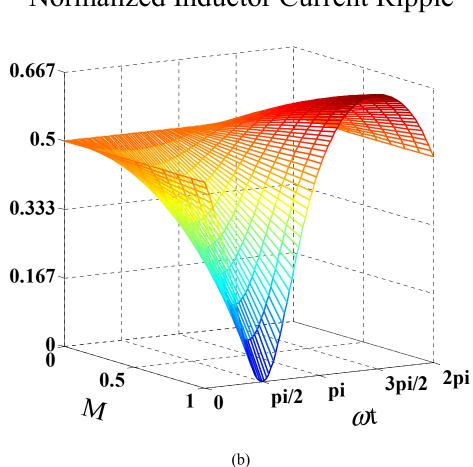

| 4.5.1 Multiphase ZCS-MMSCC                                                  |     |

| 4.5.2 ZCS voltage multiplier type                                           |     |

| 4.6 Zero Current Switching Realization Discussion in Different Load and Ter |     |

| Situation                                                                   |     |

| 4.7 Simulation and Experiment Results                                       |     |

| 4.7.1 Improved ZCS-MMSCC with continuous input current                      |     |

| 4.7.2 Improved ZCS voltage multiplier with continuous input current         |     |

| 4.8 Conclusion                                                              | 12/ |

| CHAPTER 5 Optimal Design Considerations of Multilevel Modular Switched-     |     |

| Capacitor DC-DC Converter                                                   | 129 |

| 5.1 Introduction                                                            |     |

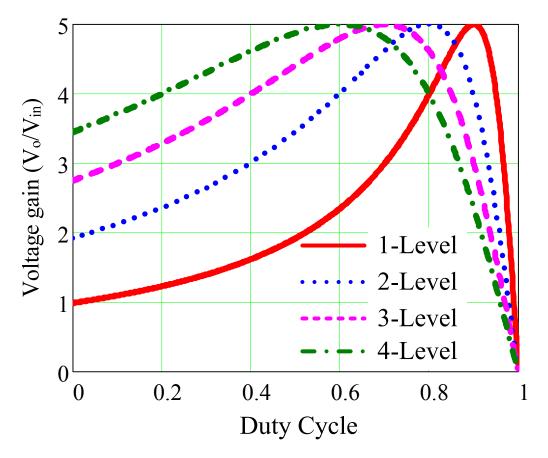

| 5.2 MMSCC Operation Principle and Power Loss Analysis                       |     |

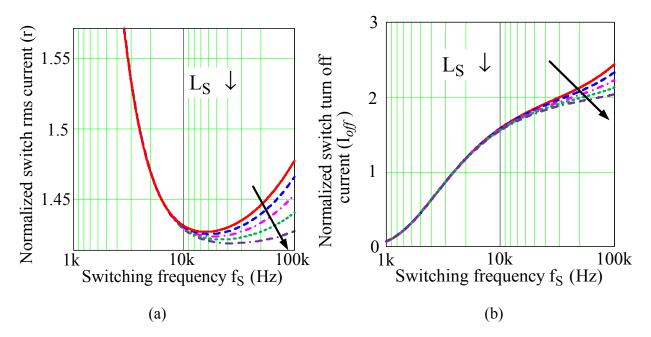

| 5.2.1 Switching Device Power Loss                                           |     |

| 5.2.2 Capacitor Power Loss                                                  |     |

| 5.2.3 Total Power Loss                                                      |     |

| 5.3 Optimal Design Considerations                                           |     |

| 5.3.1 Over-damped Case                                                      |     |

| 5.3.2 Under-damped Case                                                     |     |

| 5.4 Design Example and Experimental Results                                 |     |

| 5.5 Conclusion                                                              |     |

|                                                                             |     |

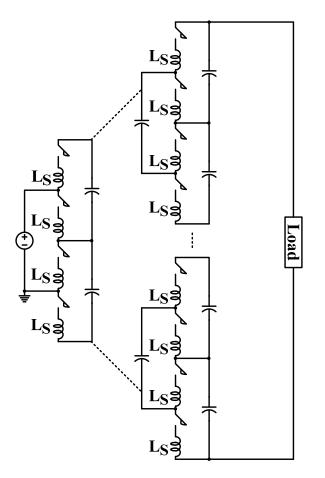

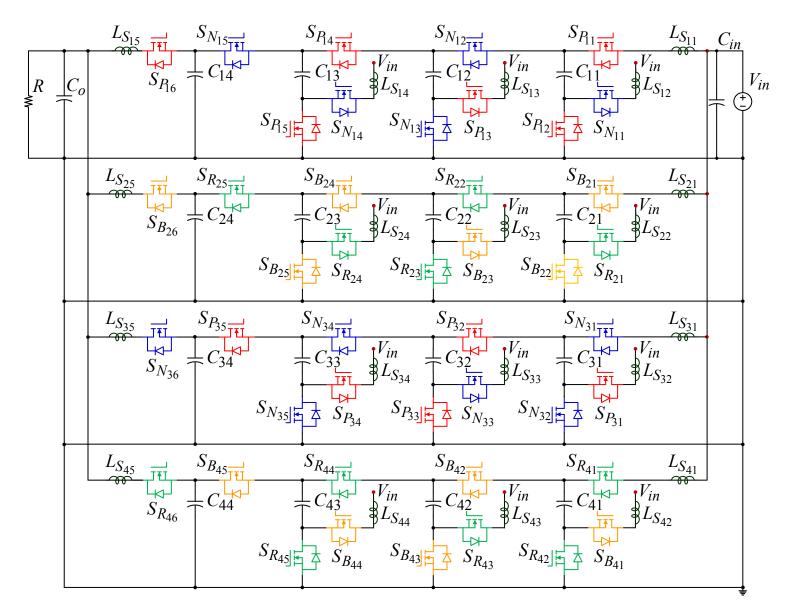

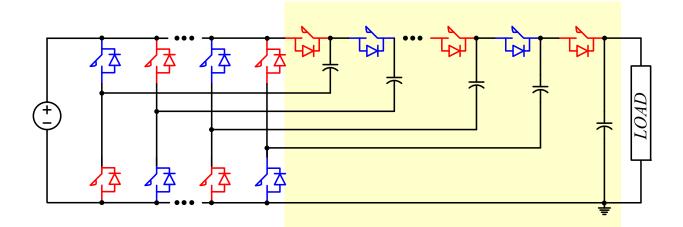

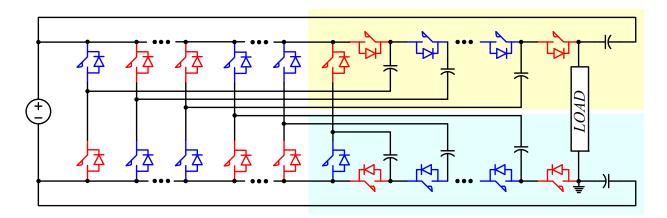

| CHAPTER 6 A Double-Wing Multilevel Modular Capacitor-Clamped DC-DC          |     |

| Converter with Reduced Capacitor Voltage Stress                             | 154 |

| 6.1 Introduction                                                            |     |

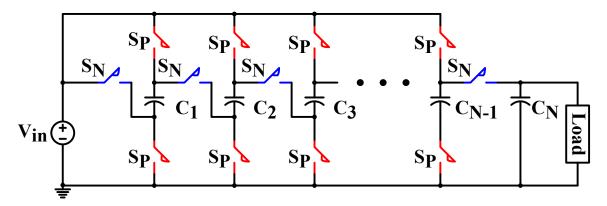

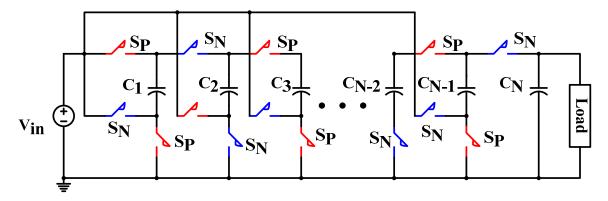

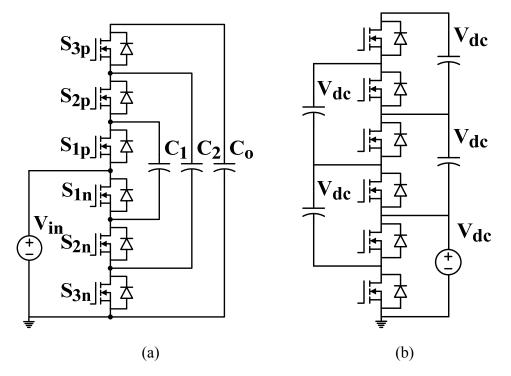

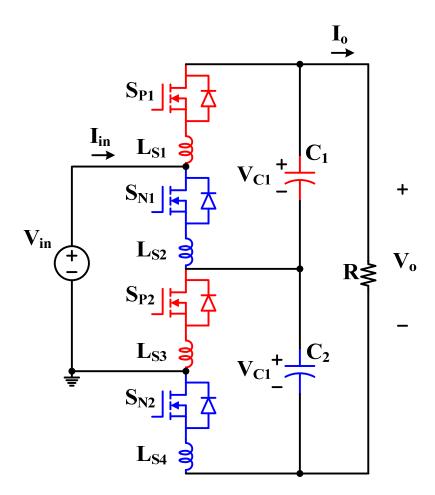

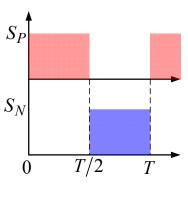

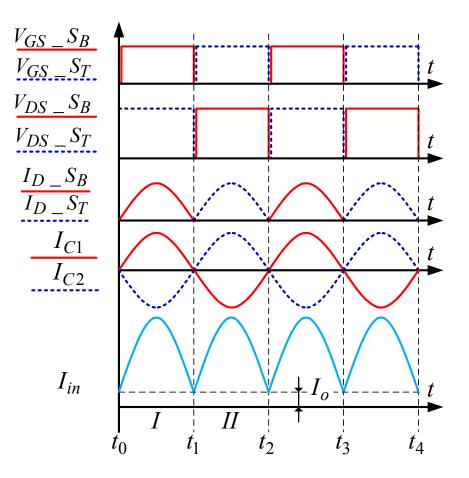

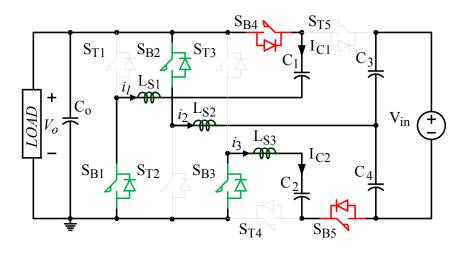

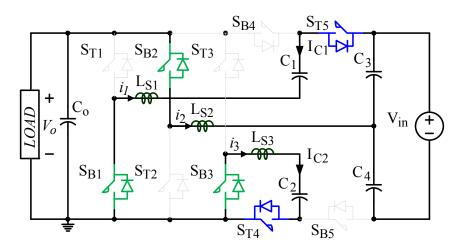

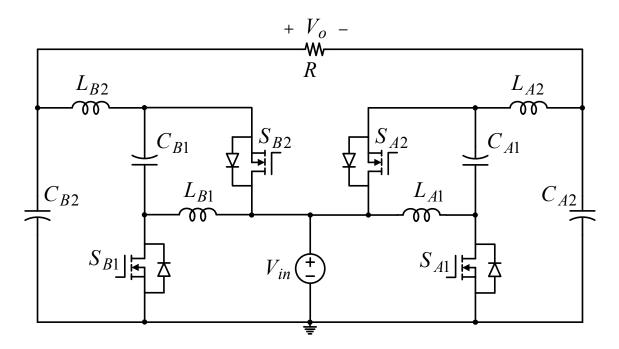

| 6.2 Proposed Circuit Topology                                               | 157 |

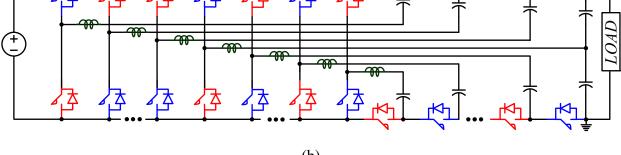

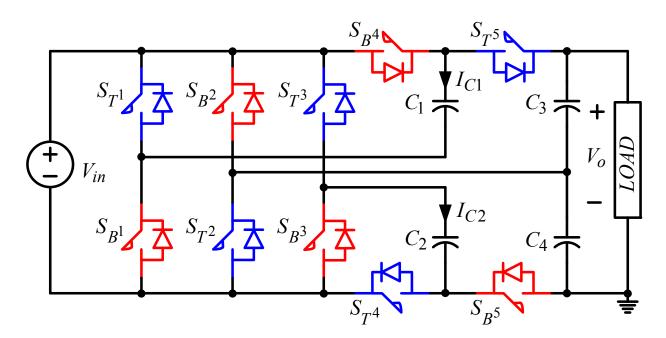

| 6.2.1 NX DW-MMCCC                                                           |     |

| 6.2.2 NX ZCS-DW-MMCCC                                                       | 160 |

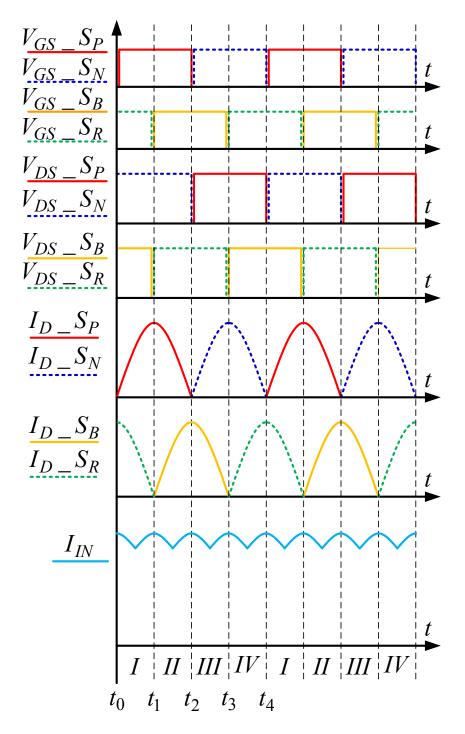

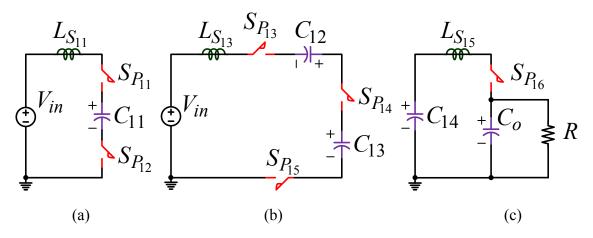

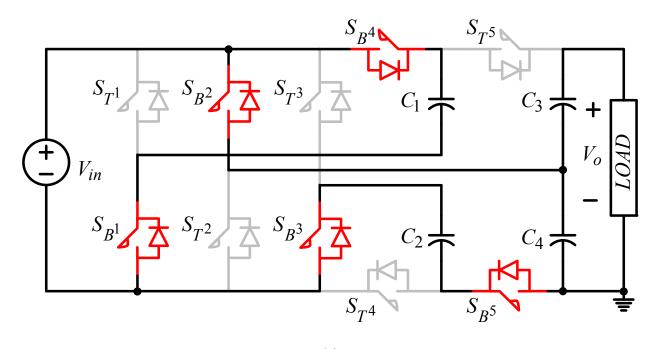

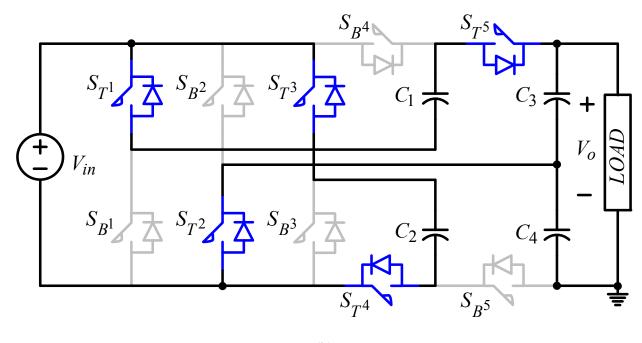

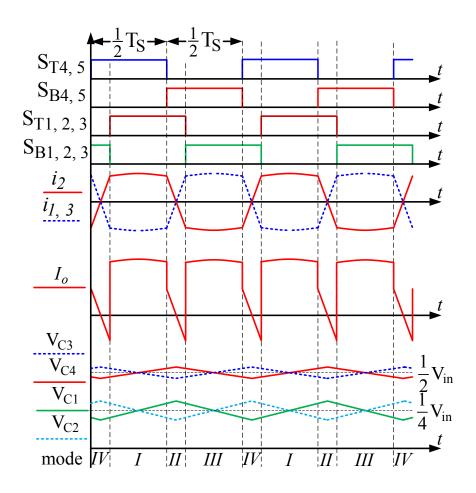

| 6.3 Operation Principles                                                    | 161 |

| 6.3.1 4X-DW-MMCCC                                                           |     |

| 6.3.2 5X-ZCS-DW-MMCCC                                                       |     |

| 6.4 Multiphase DW-MMCCC                                                     |     |

| 6.5 Design Considerations                                                   | 173 |

| 6.6 Simulation and Experiment Results                                       | 174 |

| 6.7 Conclusion                                                              |     |

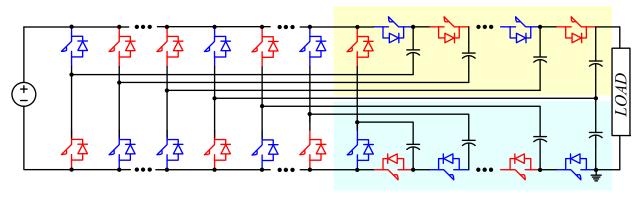

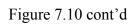

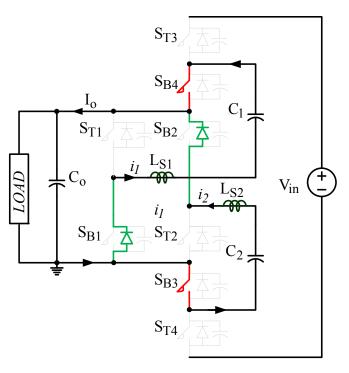

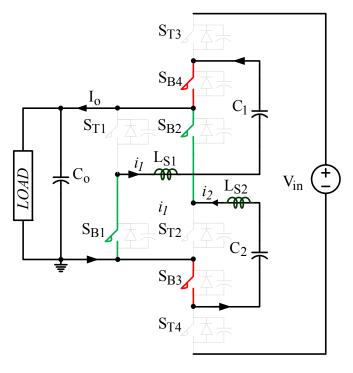

| Capacitor DC-DC Converter with Voltage Regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CHAP   | <b>TER 7</b> Zero Voltage Switching Double-Wing Multilevel Modular Switched | -    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------|------|

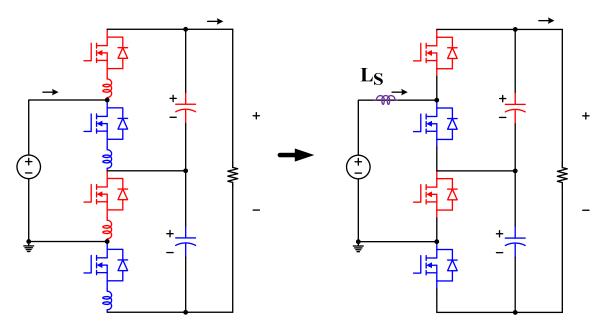

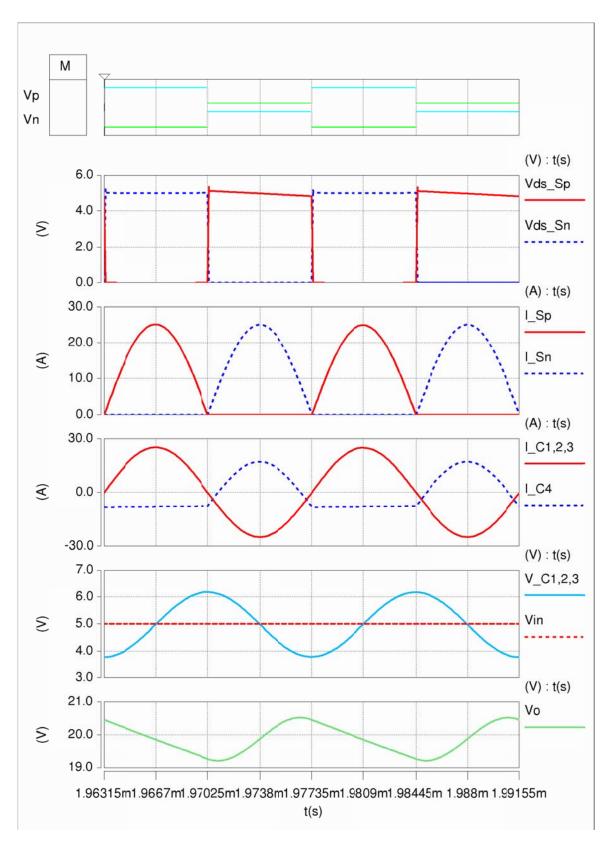

| 7.2       Proposed Circuit Description and Basic Operation Principles.       181         7.3       Soft-switching Operation Principles of the DC-DC Converter Module       189         7.4       Control Strategy       195         7.5       Simulation Results.       195         7.6       Conclusion       200         CHAPTER 8       Z-source and Quasi-Z-source DC-DC Converters for DC Motor Drive<br>and Zero Voltage Electronic Load Applications.       202         8.1       Introduction       202         8.2       Topology Derivation and Proposed Circuits.       203         8.3       The DC Operation Modes Analysis       211         8.3.1       Buck Mode with Positive Output(0 <d=0.5).< td="">       213         8.3.2       Buck-boost Mode with Negative Output (0.5<d<1).< td="">       216         8.3.3       Zero Output Voltage Gain Analysis       222         8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress.       226         8.5.2       Passive Components Design Considerations.       231         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive.       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       235         8.8</d<1).<></d=0.5).<>                                                                   |        |                                                                             |      |

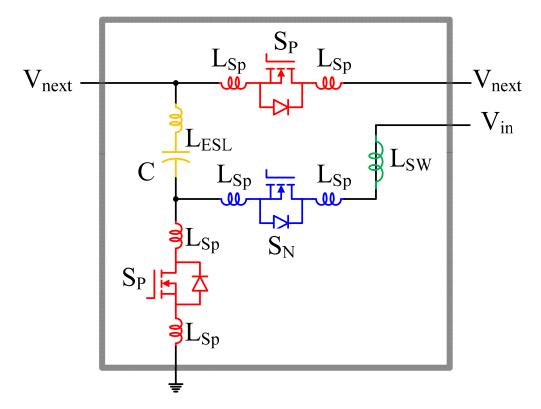

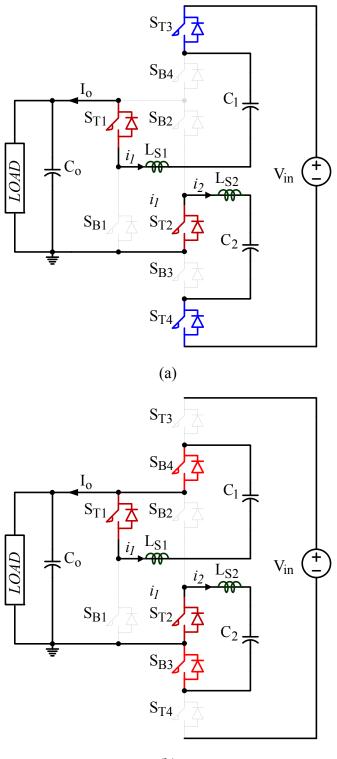

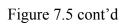

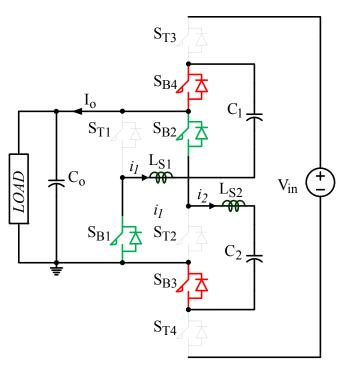

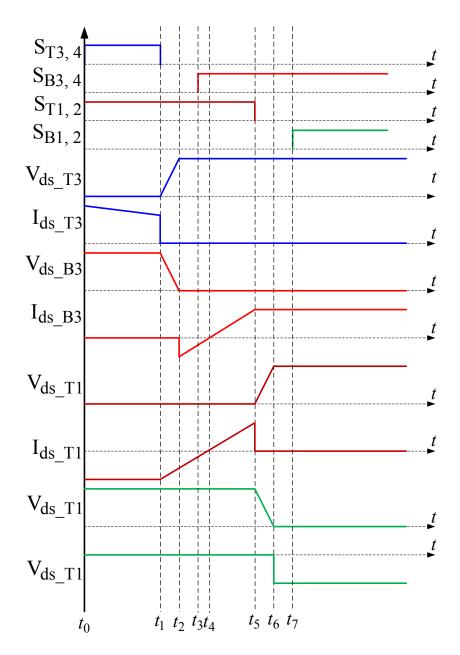

| 7.3       Soft-switching Operation Principles of the DC-DC Converter Module       188         7.4       Control Strategy       195         7.5       Simulation Results       195         7.6       Conclusion       200         CHAPTER 8 Z-source and Quasi-Z-source DC-DC Converters for DC Motor Drive and Zero Voltage Electronic Load Applications       202         8.1       Introduction       202         8.2       Topology Derivation and Proposed Circuits       203         8.3       The DC Operation Modes Analysis       212         8.3.1       Buck Mode with Positive Output(0 <d=0.5)< td="">       213         8.3.2       Buck-boost Mode with Negative Output (0.5<d<1)< td="">       216         8.3.3       Zero Output Voltage Mode (D=0.5)       219         8.4       Converter Voltage Gain Analysis       222         8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress       226         8.5.2       Passive Components Design Considerations       231         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       235         8.8       Conclusion       244</d<1)<></d=0.5)<>                                                                                         | -      |                                                                             |      |

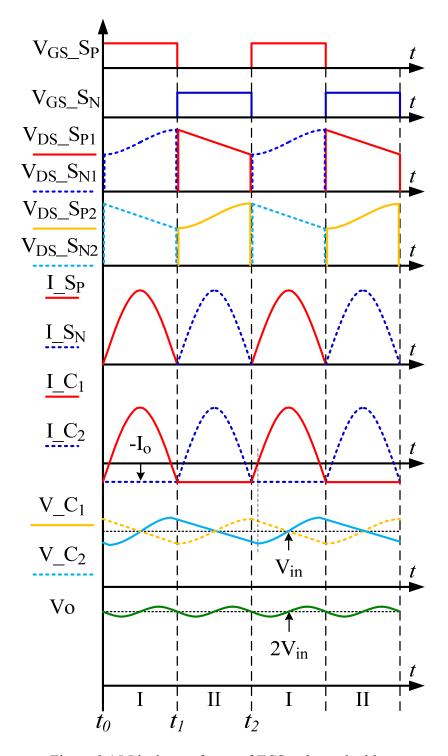

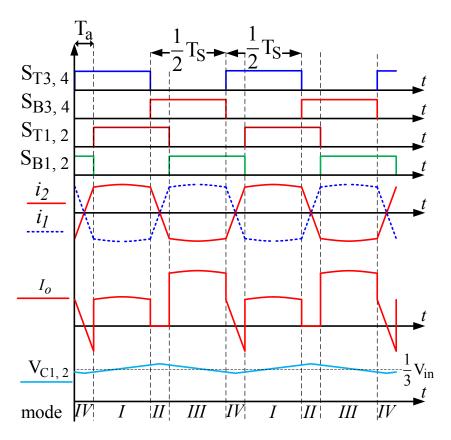

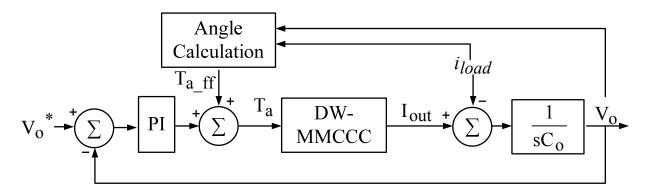

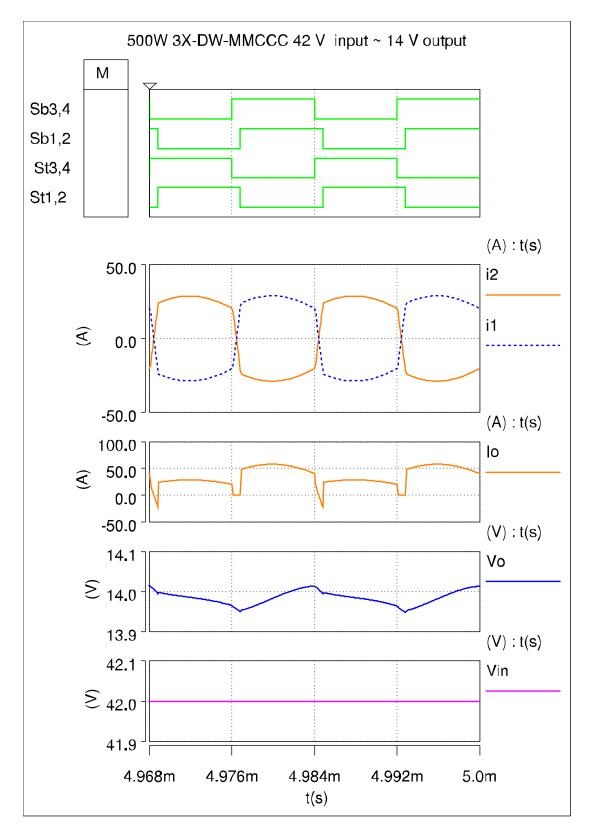

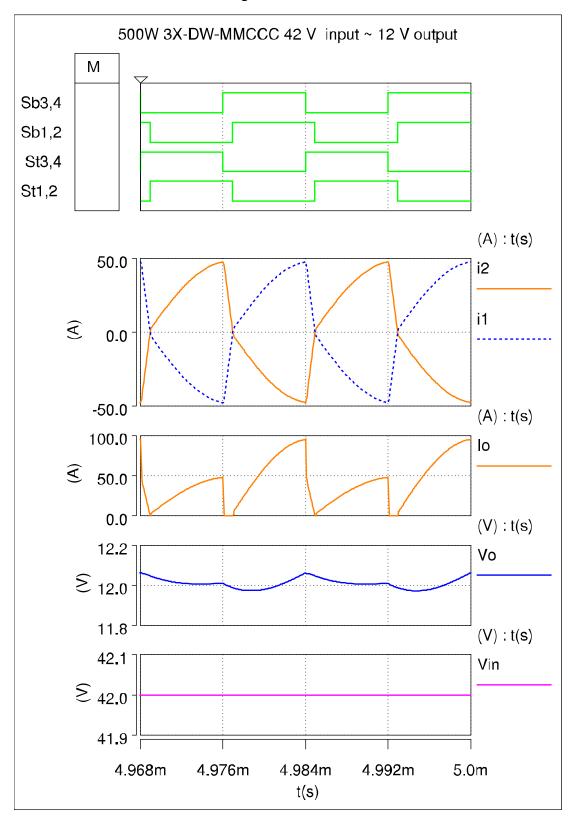

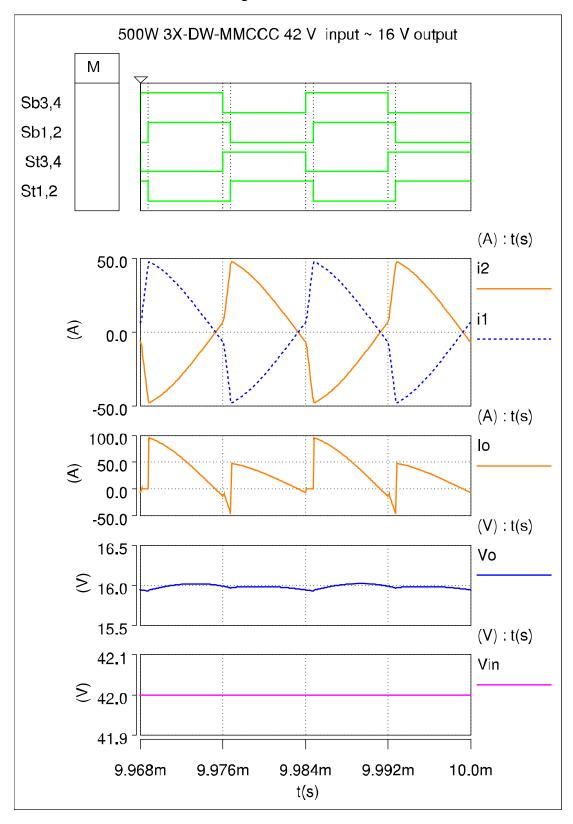

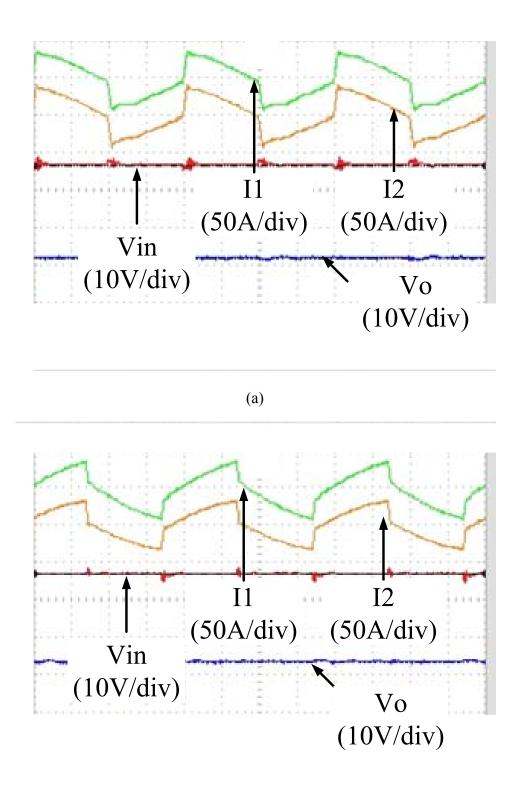

| 7.4       Control Strategy       199         7.5       Simulation Results.       195         7.6       Conclusion       200         CHAPTER 8       Z-source and Quasi-Z-source DC-DC Converters for DC Motor Drive<br>and Zero Voltage Electronic Load Applications       202         8.1       Introduction       202       203         8.2       Topology Derivation and Proposed Circuits       203         8.3       The DC Operation Modes Analysis       213         8.3.1       Buck Mode with Positive Output(0 <d-0.5)< td="">       213         8.3.2       Buck-boost Mode with Negative Output (0.5<d<1)< td="">       216         8.3.3       Zero Output Voltage Mode (D=0.5)       219         8.4       Converter Voltage Gain Analysis       222         8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress.       226         8.5.2       Passive Components Design Considerations       233         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive.       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       239         8.8       Conclusion       244         9.1       Introduction       244         <td< td=""><td>7.2</td><td>Proposed Circuit Description and Basic Operation Principles</td><td> 181</td></td<></d<1)<></d-0.5)<> | 7.2    | Proposed Circuit Description and Basic Operation Principles                 | 181  |

| 7.4       Control Strategy       199         7.5       Simulation Results.       195         7.6       Conclusion       200         CHAPTER 8       Z-source and Quasi-Z-source DC-DC Converters for DC Motor Drive<br>and Zero Voltage Electronic Load Applications       202         8.1       Introduction       202       203         8.2       Topology Derivation and Proposed Circuits       203         8.3       The DC Operation Modes Analysis       213         8.3.1       Buck Mode with Positive Output(0 <d-0.5)< td="">       213         8.3.2       Buck-boost Mode with Negative Output (0.5<d<1)< td="">       216         8.3.3       Zero Output Voltage Mode (D=0.5)       219         8.4       Converter Voltage Gain Analysis       222         8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress.       226         8.5.2       Passive Components Design Considerations       233         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive.       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       239         8.8       Conclusion       244         9.1       Introduction       244         <td< td=""><td>7.3</td><td>· · · · ·</td><td></td></td<></d<1)<></d-0.5)<>                                                       | 7.3    | · · · · ·                                                                   |      |

| 7.6       Conclusion       200         CHAPTER 8       Z-source and Quasi-Z-source DC-DC Converters for DC Motor Drive         and Zero Voltage Electronic Load Applications       202         8.1       Introduction       202         8.2       Topology Derivation and Proposed Circuits       202         8.3       The DC Operation Modes Analysis       213         8.3.1       Buck Mode with Positive Output (0.5 <d< td="">       213         8.3.2       Buck-boost Mode with Negative Output (0.5<d< td="">       216         8.3.3       Zero Output Voltage Mode (D=0.5)       216         8.4       Converter Voltage Gain Analysis       222         8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress.       226         8.5.2       Passive Components Design Considerations       231         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       235         8.8       Conclusion       244         9.1       Introduction       244         9.2       Proposed Semi-Z-source Inverters for Single-Phase Photovoltaic Systems.       253         9.4       Modulation of Semi-Z</d<></d<>                                                                                             | 7.4    |                                                                             |      |

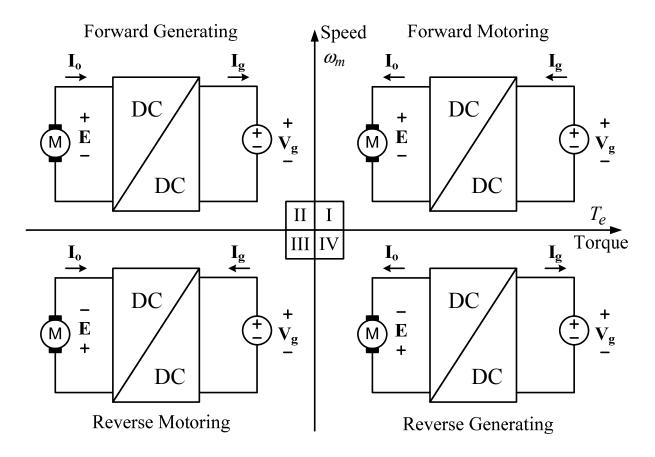

| CHAPTER 8       Z-source and Quasi-Z-source DC-DC Converters for DC Motor Drive         and Zero Voltage Electronic Load Applications       202         8.1       Introduction       202         8.2       Topology Derivation and Proposed Circuits       205         8.3       The DC Operation Modes Analysis       212         8.3.1       Buck Mode with Positive Output(0 <d<0.5)< td="">       213         8.3.2       Buck-boost Mode with Negative Output (0.5<d<1)< td="">       216         8.3.3       Zero Output Voltage Gain Analysis       222         8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress.       226         8.5.2       Passive Components Design Considerations       231         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive       234         8.7       Quasi-Z-source Inverter for Single-Phase Photovoltaic Systems.       244         9.1       Introduction       244         9.2       Proposed Semi-Z-source Inverters and Topology Derivations       248         9.3       Operating Principle of Semi-Z-source Inverters       256         9.4       Modulation of Semi-Z-source Inverters       256         9.5       Device Stress Analysis and Passive Component</d<1)<></d<0.5)<>                                          | 7.5    |                                                                             |      |

| and Zero Voltage Electronic Load Applications       202         8.1       Introduction       202         8.2       Topology Derivation and Proposed Circuits       205         8.3       The DC Operation Modes Analysis       212         8.3.1       Buck Mode with Positive Output(0 <d<0.5)< td="">       213         8.3.2       Buck-boost Mode with Negative Output (0.5<d<1)< td="">       216         8.3.3       Zero Output Voltage Mode (D=0.5)       219         8.4       Converter Voltage Gain Analysis       222         8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress       226         8.5.2       Pasive Components Design Considerations       231         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       239         8.8       Conclusion       244         9.1       Introduction       244         9.2       Proposed Semi-Z-source Inverter for Single-Phase Photovoltaic Systems       244         9.3       Operating Principle of Semi-Z-source Inverters.       253         9.4       Modulation of Semi-Z-source Inverters.       253         9.5</d<1)<></d<0.5)<>                                                                                               |        |                                                                             |      |

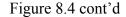

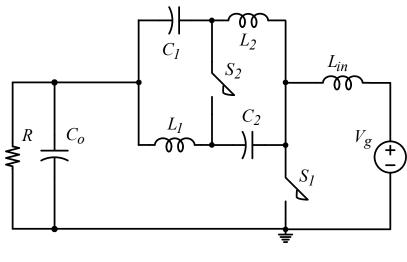

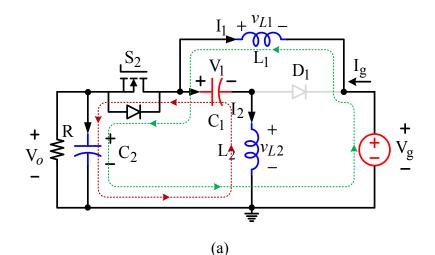

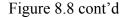

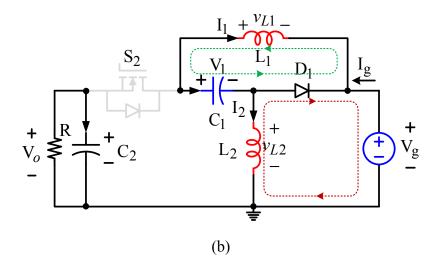

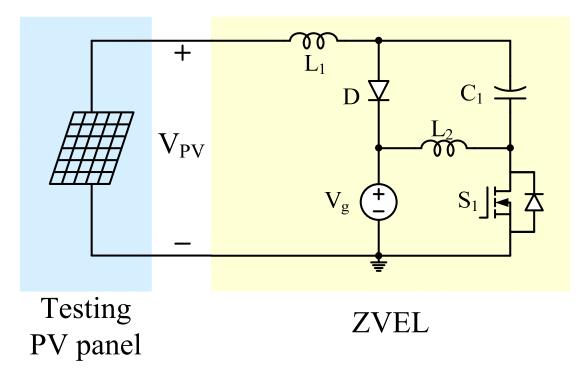

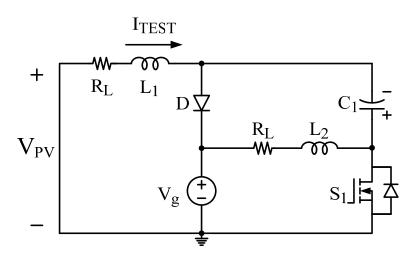

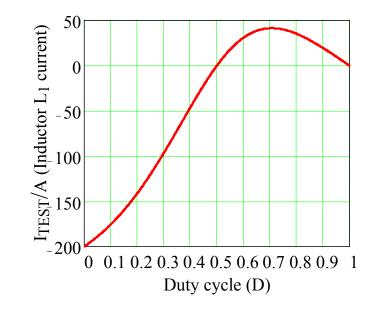

| 8.1       Introduction       202         8.2       Topology Derivation and Proposed Circuits       205         8.3       The DC Operation Modes Analysis       211         8.3.1       Buck Mode with Positive Output(0 <d<0.5)< td="">       213         8.3.2       Buck-boost Mode with Negative Output (0.5<d<1)< td="">       216         8.3.3       Zero Output Voltage Mode (D=0.5)       219         8.4       Converter Voltage Gain Analysis       222         8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress       226         8.5.2       Passive Components Design Considerations       231         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       239         8.8       Conclusion       244         9.1       Introduction       244         9.2       Proposed Semi-Z-source Inverter for Single-Phase Photovoltaic Systems.       242         9.4       Modulation of Semi-Z-source Inverters       250         9.5       Device Stress Analysis and Passive Component Design       256         9.4       Modulation of Semi-Z-source Inverters       250         &lt;</d<1)<></d<0.5)<>                                                                                       | CHAP   | <b>TER 8</b> Z-source and Quasi-Z-source DC-DC Converters for DC Motor Dri  | ive  |

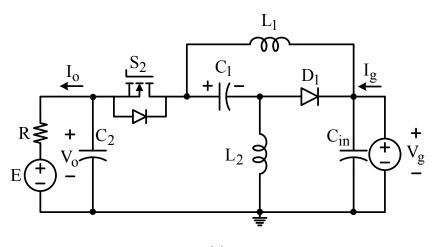

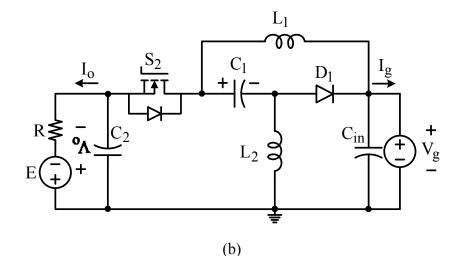

| 8.2       Topology Derivation and Proposed Circuits       205         8.3       The DC Operation Modes Analysis       212         8.3.1       Buck Mode with Positive Output (0 <d<0.5)< td="">       213         8.3.2       Buck-boost Mode with Negative Output (0.5<d<1)< td="">       216         8.3.3       Zero Output Voltage Mode (D=0.5)       219         8.4       Converter Voltage Gain Analysis       222         8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress       226         8.5.2       Passive Components Design Considerations       231         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       239         8.8       Conclusion       244         CHAPTER 9       Low Cost Semi-Z-source Inverter for Single-Phase Photovoltaic Systems.         244         9.1       Introduction       244         9.2       Proposed Semi-Z-source Inverters and Topology Derivations       248         9.3       Operating Principle of Semi-Z-source Inverters       250         9.4       Modulation of Semi-Z-source Inverters       253         9.5       <t< td=""><td>and Ze</td><td>ro Voltage Electronic Load Applications</td><td> 202</td></t<></d<1)<></d<0.5)<>       | and Ze | ro Voltage Electronic Load Applications                                     | 202  |

| 8.3       The DC Operation Modes Analysis       212         8.3.1       Buck Mode with Positive Output(0 <d<0.5)< td="">       213         8.3.2       Buck-boost Mode with Negative Output (0.5<d<1)< td="">       216         8.3.3       Zero Output Voltage Gain Analysis       222         8.4       Converter Voltage Gain Analysis       222         8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress       226         8.5.2       Passive Components Design Considerations       233         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       239         8.8       Conclusion       244         9.1       Introduction       244         9.2       Proposed Semi-Z-source Inverter for Single-Phase Photovoltaic Systems.       244         9.1       Introduction       244         9.2       Proposed Semi-Z-source Inverters and Topology Derivations       248         9.3       Operating Principle of Semi-Z-source Inverters       253         9.4       Modulation of Semi-Z-source Inverters       253         9.5       Device Stress Analysis and Passive Component Design       256</d<1)<></d<0.5)<>                                                                          | 8.1    |                                                                             |      |

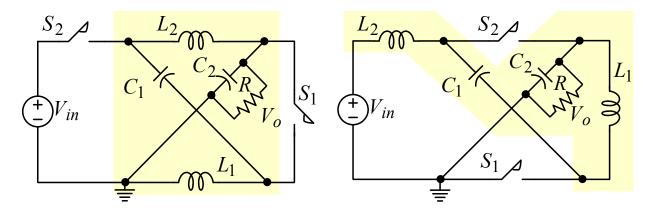

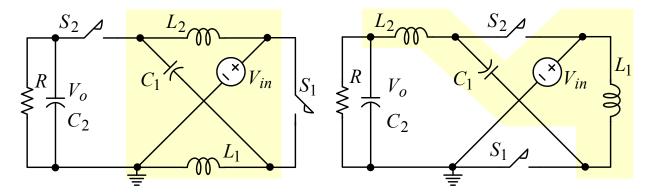

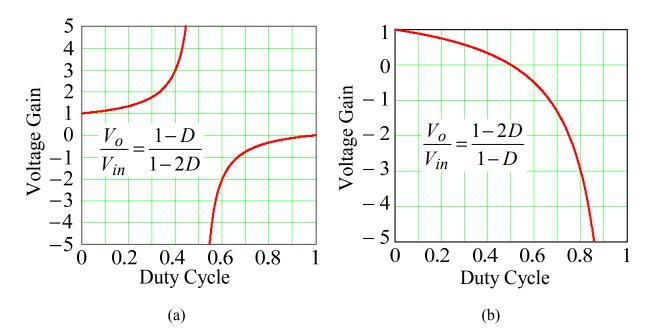

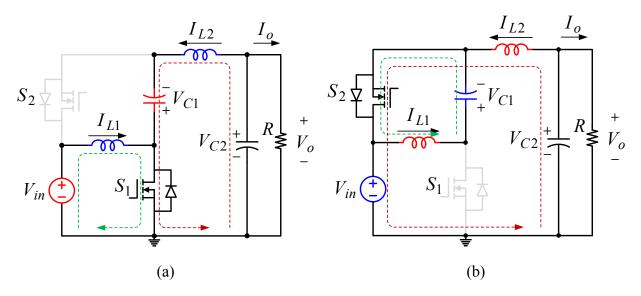

| 8.3.1       Buck Mode with Positive Output(0 <d<0.5)< td=""><td>8.2</td><td>Topology Derivation and Proposed Circuits</td><td> 205</td></d<0.5)<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8.2    | Topology Derivation and Proposed Circuits                                   | 205  |

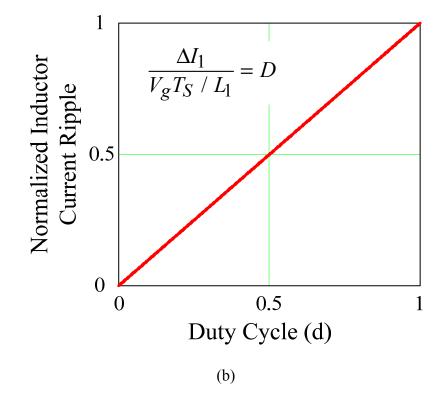

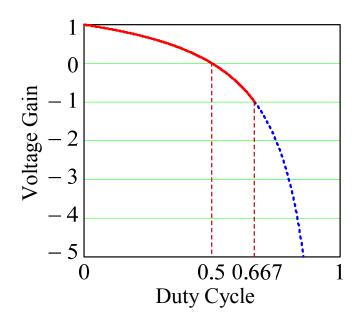

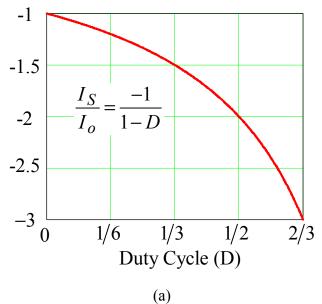

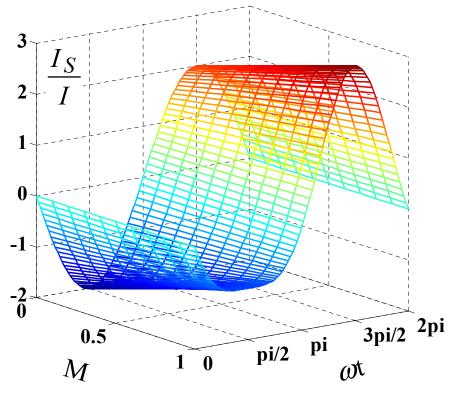

| 8.3.2       Buck-boost Mode with Negative Output (0.5 <d<1)< td="">       216         8.3.3       Zero Output Voltage Mode (D=0.5)       219         8.4       Converter Voltage Gain Analysis       222         8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress.       226         8.5.2       Passive Components Design Considerations       231         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive.       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       235         8.8       Conclusion       242         CHAPTER 9       Low Cost Semi-Z-source Inverter for Single-Phase Photovoltaic Systems         244         9.1       Introduction       244         9.2       Proposed Semi-Z-source/-quasi Z-source Inverters and Topology Derivations       248         9.3       Operating Principle of Semi-Z-source Inverters       253         9.5       Device Stress Analysis and Passive Component Design       256         9.4       Modulation of Semi-Z-source Inverters       253         9.5       Device Stress Analysis and Passive Component Design       256         9.6       Topology Expansion and Discussion       264     <!--</td--><td>8.3</td><td>The DC Operation Modes Analysis</td><td> 212</td></d<1)<>                | 8.3    | The DC Operation Modes Analysis                                             | 212  |

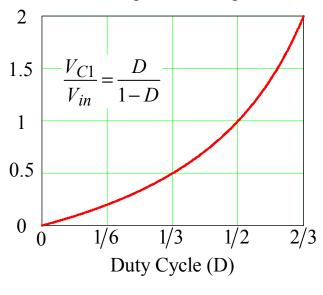

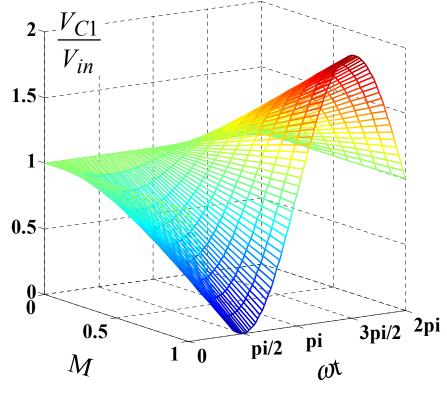

| 8.3.3       Zero Output Voltage Mode (D=0.5)       219         8.4       Converter Voltage Gain Analysis       222         8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress       226         8.5.2       Passive Components Design Considerations       231         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       239         8.8       Conclusion       242         CHAPTER 9       Low Cost Semi-Z-source Inverter for Single-Phase Photovoltaic Systems.         244         9.1       Introduction       244         9.2       Proposed Semi-Z-source/-quasi Z-source Inverters and Topology Derivations       248         9.3       Operating Principle of Semi-Z-source Inverters       250         9.4       Modulation of Semi-Z-source Inverters       250         9.5       Device Stress Analysis and Passive Component Design       256         9.6       Topology Expansion and Discussion       266         9.7       Experiment Results       267         9.8       Conclusion       276         9.9       Conclusion       276 <td>8.3</td> <td>.1 Buck Mode with Positive Output(0<d<0.5)< td=""><td> 213</td></d<0.5)<></td>                                                   | 8.3    | .1 Buck Mode with Positive Output(0 <d<0.5)< td=""><td> 213</td></d<0.5)<>  | 213  |

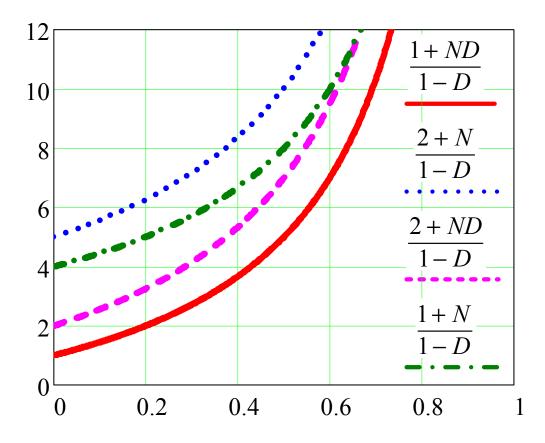

| 8.4       Converter Voltage Gain Analysis       222         8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress       226         8.5.2       Passive Components Design Considerations       231         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       239         8.8       Conclusion       242         CHAPTER 9       Low Cost Semi-Z-source Inverter for Single-Phase Photovoltaic Systems         244         9.1       Introduction       244         9.2       Proposed Semi-Z-source/-quasi Z-source Inverters and Topology Derivations       248         9.3       Operating Principle of Semi-Z-source Inverters       250         9.4       Modulation of Semi-Z-source Inverters       253         9.5       Device Stress Analysis and Passive Component Design       256         9.6       Topology Expansion and Discussion       266         9.7       Experiment Results       267         9.8       Conclusion       276         9.8       Conclusion       276         9.4       Modulation of Semi-Z-source Inverters       25                                                                                                                                                  | 8.3    |                                                                             |      |

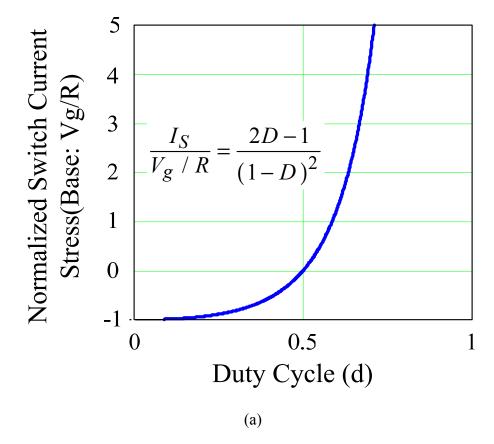

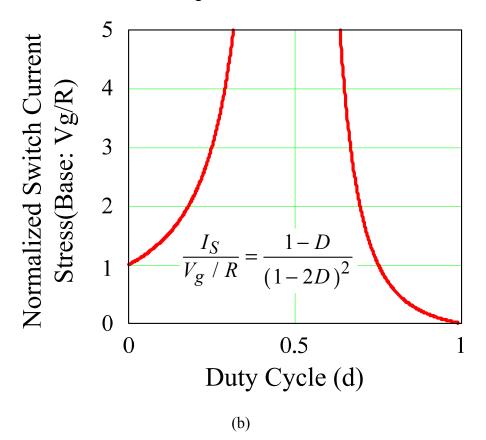

| 8.5       Device Stress Analysis and Passive Components Design Guidelines       226         8.5.1       Switching Device Voltage and Current Stress       226         8.5.2       Passive Components Design Considerations       231         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       239         8.8       Conclusion       242         CHAPTER 9       Low Cost Semi-Z-source Inverter for Single-Phase Photovoltaic Systems         244         9.1       Introduction       244         9.2       Proposed Semi-Z-source/-quasi Z-source Inverters and Topology Derivations       248         9.3       Operating Principle of Semi-Z-source Inverters.       253         9.4       Modulation of Semi-Z-source Inverters.       253         9.5       Device Stress Analysis and Passive Component Design       256         9.6       Topology Expansion and Discussion       264         9.7       Experiment Results       267         9.8       Conclusion       276         10.1       Introduction       276         10.2       Proposed Circuit Description and Operating Principle       279         10.3       Soft-switching Operation Pr                                                                                                                                         | 8.3    |                                                                             |      |

| 8.5.1       Switching Device Voltage and Current Stress       226         8.5.2       Passive Components Design Considerations       231         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       239         8.8       Conclusion       242         CHAPTER 9       Low Cost Semi-Z-source Inverter for Single-Phase Photovoltaic Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                                                                             |      |

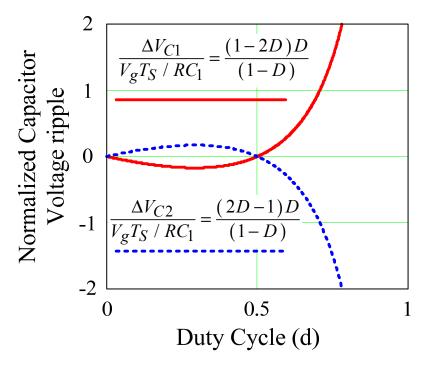

| 8.5.2       Passive Components Design Considerations       231         8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL       239         8.8       Conclusion       242         CHAPTER 9       Low Cost Semi-Z-source Inverter for Single-Phase Photovoltaic Systems.         244         9.1       Introduction       244         9.2       Proposed Semi-Z-source/-quasi Z-source Inverters and Topology Derivations       248         9.3       Operating Principle of Semi-Z-source Inverters       250         9.4       Modulation of Semi-Z-source Inverters       253         9.5       Device Stress Analysis and Passive Component Design       256         9.6       Topology Expansion and Discussion       264         9.7       Experiment Results       267         9.8       Conclusion       276         10.1       Introduction       276         10.2       Proposed Circuit Description and Operating Principle       279         10.3       Soft-switching Operation Principles of the DC-DC Converter Module       290         10.4       Conclusion       308         CHAPTER 11       Conclusion and Future works       309                                                                                                                                                         | 8.5    |                                                                             |      |

| 8.6       Proposed Converter Four-quadrant Operation for DC Motor Drive.       234         8.7       Quasi-Z-source DC-DC Converter as ZVEL.       239         8.8       Conclusion.       242         CHAPTER 9       Low Cost Semi-Z-source Inverter for Single-Phase Photovoltaic Systems         244         9.1       Introduction       244         9.2       Proposed Semi-Z-source/-quasi Z-source Inverters and Topology Derivations       248         9.3       Operating Principle of Semi-Z-source Inverters       250         9.4       Modulation of Semi-Z-source Inverters       253         9.5       Device Stress Analysis and Passive Component Design       256         9.6       Topology Expansion and Discussion       264         9.7       Experiment Results       267         9.8       Conclusion       276         9.8       Conclusion       276         10.1       Introduction       276         10.2       Proposed Circuit Description and Operating Principle       279         10.3       Soft-switching Operation Principles of the DC-DC Converter Module       290         10.4       Control Strategy       296       296         10.5       Prototype and Experimental Results       296                                                                                                                                                                      |        |                                                                             |      |

| 8.7       Quasi-Z-source DC-DC Converter as ZVEL       239         8.8       Conclusion       242         CHAPTER 9       Low Cost Semi-Z-source Inverter for Single-Phase Photovoltaic Systems         244         9.1       Introduction       244         9.2       Proposed Semi-Z-source/-quasi Z-source Inverters and Topology Derivations       248         9.3       Operating Principle of Semi-Z-source Inverters       250         9.4       Modulation of Semi-Z-source Inverters       253         9.5       Device Stress Analysis and Passive Component Design       256         9.6       Topology Expansion and Discussion       264         9.7       Experiment Results       267         9.8       Conclusion       274         CHAPTER 10       Low Cost Transformer Isolated Boost Half-bridge Micro-inverter for         Single-phase Grid-connected Photovoltaic System       276         10.1       Introduction       276         10.2       Proposed Circuit Description and Operating Principle       279         10.3       Soft-switching Operation Principles of the DC-DC Converter Module       290         10.4       Control Strategy       296       296         10.5       Prototype and Experimental Resul                                                                                                                                                        |        | 1 0                                                                         |      |

| 8.8       Conclusion       242         CHAPTER 9       Low Cost Semi-Z-source Inverter for Single-Phase Photovoltaic Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |                                                                             |      |

| CHAPTER 9       Low Cost Semi-Z-source Inverter for Single-Phase Photovoltaic Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |                                                                             |      |

| 2449.1Introduction2449.2Proposed Semi-Z-source/-quasi Z-source Inverters and Topology Derivations2489.3Operating Principle of Semi-Z-source Inverters2509.4Modulation of Semi-Z-source Inverters2539.5Device Stress Analysis and Passive Component Design2569.6Topology Expansion and Discussion2649.7Experiment Results2679.8Conclusion274CHAPTER 10Low Cost Transformer Isolated Boost Half-bridge Micro-inverter forSingle-phase Grid-connected Photovoltaic System27610.1Introduction27610.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11Conclusion and Future works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8.8    | Conclusion                                                                  | 242  |

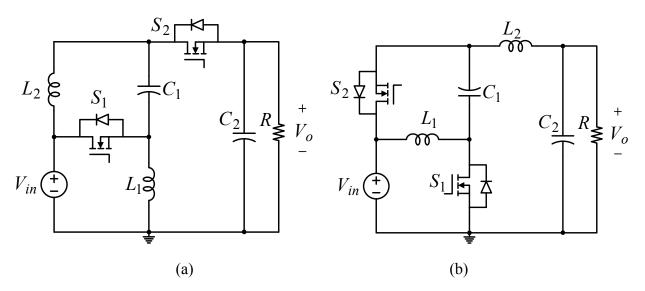

| 2449.1Introduction2449.2Proposed Semi-Z-source/-quasi Z-source Inverters and Topology Derivations2489.3Operating Principle of Semi-Z-source Inverters2509.4Modulation of Semi-Z-source Inverters2539.5Device Stress Analysis and Passive Component Design2569.6Topology Expansion and Discussion2649.7Experiment Results2679.8Conclusion274CHAPTER 10Low Cost Transformer Isolated Boost Half-bridge Micro-inverter forSingle-phase Grid-connected Photovoltaic System27610.1Introduction27610.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11Conclusion and Future works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CILAD  | FED 0 Low Cost Sami Z source Inventor for Single Dhase Dhotoveltais Sus     | toma |

| 9.1Introduction2449.2Proposed Semi-Z-source/-quasi Z-source Inverters and Topology Derivations2489.3Operating Principle of Semi-Z-source Inverters2509.4Modulation of Semi-Z-source Inverters2539.5Device Stress Analysis and Passive Component Design2569.6Topology Expansion and Discussion2649.7Experiment Results2679.8Conclusion274CHAPTER 10Low Cost Transformer Isolated Boost Half-bridge Micro-inverter forSingle-phase Grid-connected Photovoltaic System27610.1Introduction27610.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11Conclusion and Future works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CHAP   |                                                                             |      |

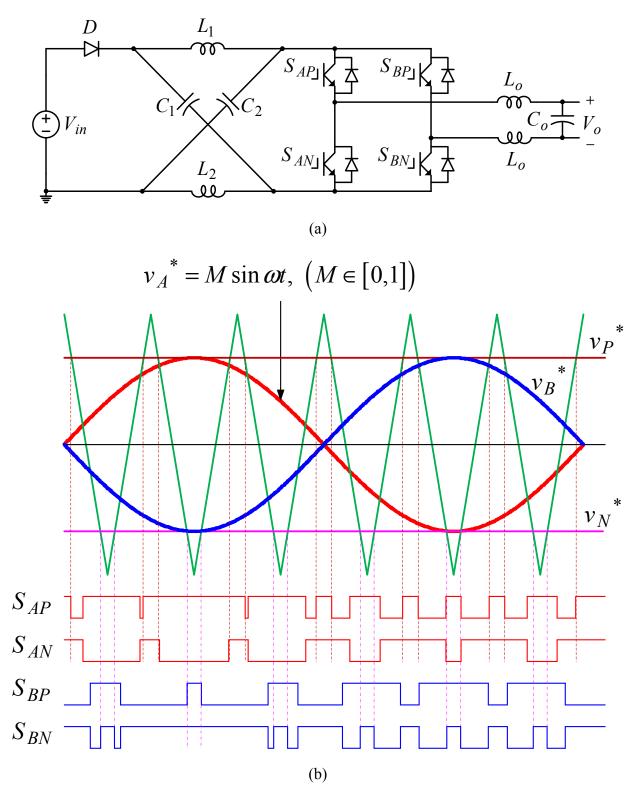

| 9.2Proposed Semi-Z-source/-quasi Z-source Inverters and Topology Derivations2489.3Operating Principle of Semi-Z-source Inverters2509.4Modulation of Semi-Z-source Inverters2539.5Device Stress Analysis and Passive Component Design2569.6Topology Expansion and Discussion2649.7Experiment Results2679.8Conclusion274CHAPTER 10 Low Cost Transformer Isolated Boost Half-bridge Micro-inverter forSingle-phase Grid-connected Photovoltaic System27610.1Introduction27610.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11Conclusion and Future works309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 91     |                                                                             |      |

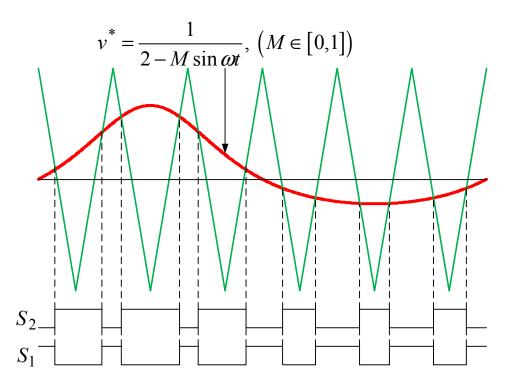

| 9.3Operating Principle of Semi-Z-source Inverters2509.4Modulation of Semi-Z-source Inverters2539.5Device Stress Analysis and Passive Component Design2569.6Topology Expansion and Discussion2649.7Experiment Results2679.8Conclusion274CHAPTER 10Low Cost Transformer Isolated Boost Half-bridge Micro-inverter forSingle-phase Grid-connected Photovoltaic System0.1Introduction27610.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11Conclusion and Future works309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                                                             |      |

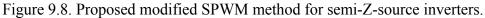

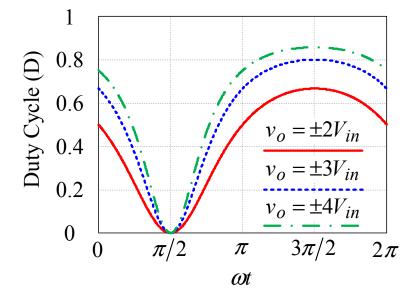

| 9.4Modulation of Semi-Z-source Inverters2539.5Device Stress Analysis and Passive Component Design2569.6Topology Expansion and Discussion2649.7Experiment Results2679.8Conclusion274CHAPTER 10 Low Cost Transformer Isolated Boost Half-bridge Micro-inverter forSingle-phase Grid-connected Photovoltaic System10.1Introduction27610.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11 Conclusion and Future works309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |                                                                             |      |

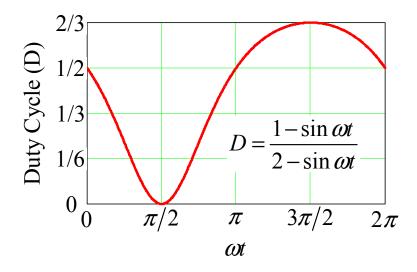

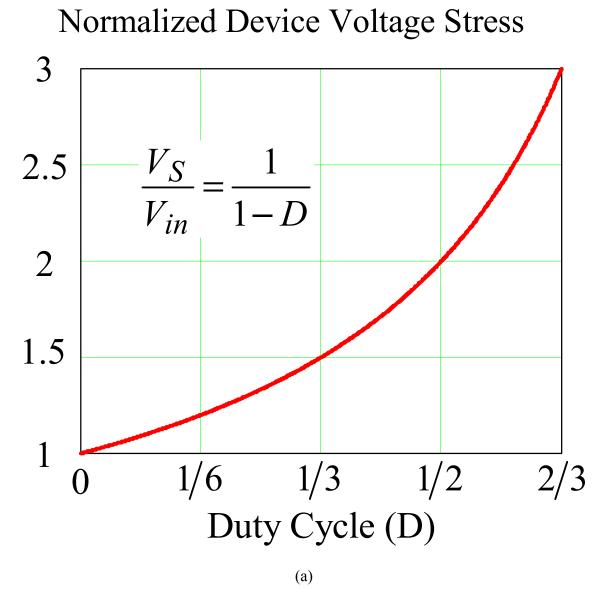

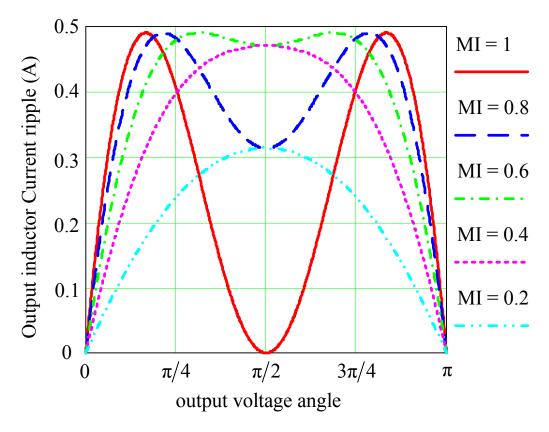

| 9.5Device Stress Analysis and Passive Component Design2569.6Topology Expansion and Discussion2649.7Experiment Results2679.8Conclusion274CHAPTER 10Low Cost Transformer Isolated Boost Half-bridge Micro-inverter forSingle-phase Grid-connected Photovoltaic System10.1Introduction27610.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11Conclusion and Future works309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |                                                                             |      |

| 9.6Topology Expansion and Discussion2649.7Experiment Results2679.8Conclusion274CHAPTER 10 Low Cost Transformer Isolated Boost Half-bridge Micro-inverter forSingle-phase Grid-connected Photovoltaic System10.1Introduction27610.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11Conclusion and Future works309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                                                                             |      |

| 9.7Experiment Results2679.8Conclusion274CHAPTER 10 Low Cost Transformer Isolated Boost Half-bridge Micro-inverter forSingle-phase Grid-connected Photovoltaic System27610.1Introduction27610.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11Conclusion and Future works309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |                                                                             |      |

| 9.8Conclusion.274CHAPTER 10 Low Cost Transformer Isolated Boost Half-bridge Micro-inverter for<br>Single-phase Grid-connected Photovoltaic System.27610.1Introduction27610.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11 Conclusion and Future works309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |                                                                             |      |

| CHAPTER 10Low Cost Transformer Isolated Boost Half-bridge Micro-inverter forSingle-phase Grid-connected Photovoltaic System27610.1Introduction27610.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11Conclusion and Future works309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        | 1                                                                           |      |

| Single-phase Grid-connected Photovoltaic System27610.1Introduction27610.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11Conclusion and Future works309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7.0    | Conclusion                                                                  | 274  |

| 10.1Introduction27610.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11Conclusion and Future works309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 8                                                                           |      |

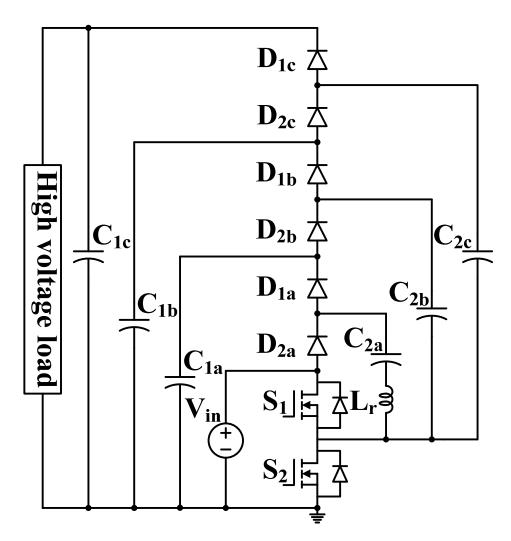

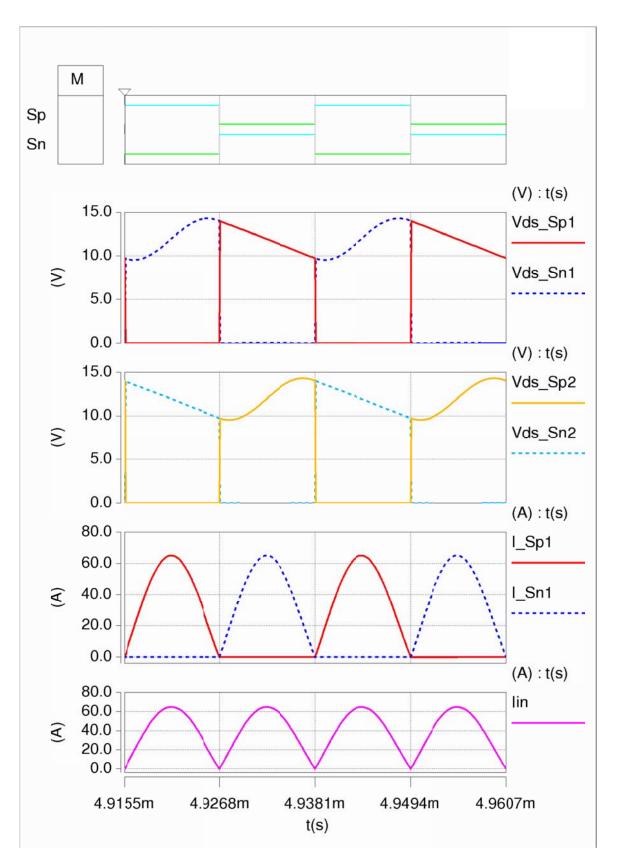

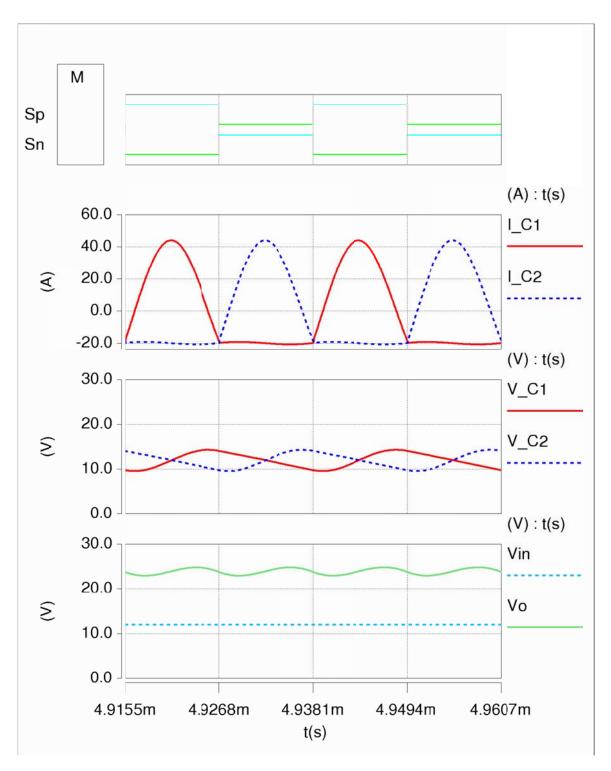

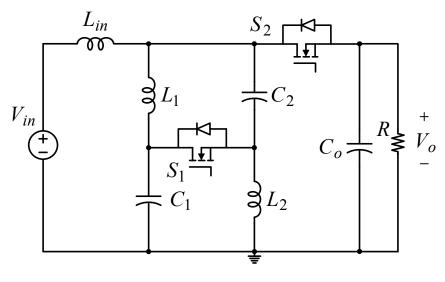

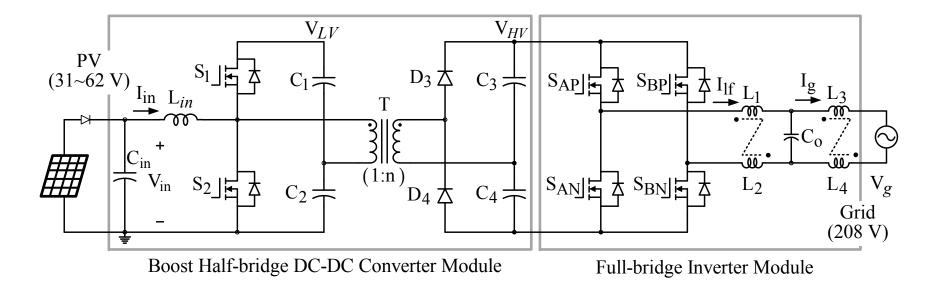

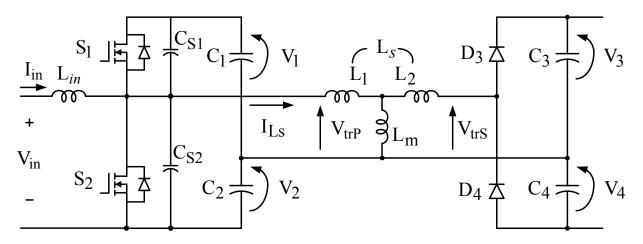

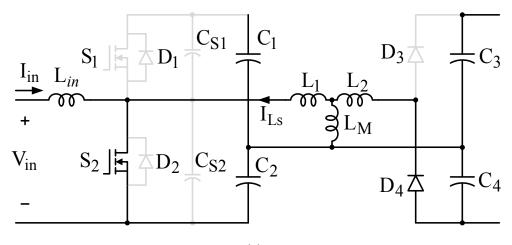

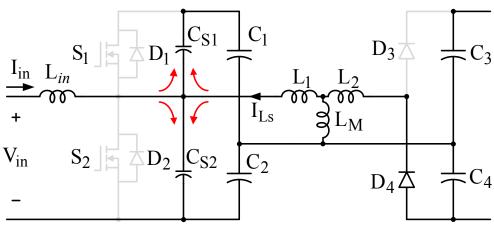

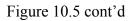

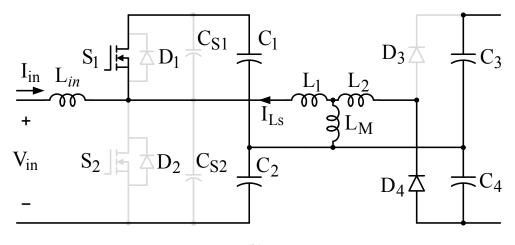

| 10.2Proposed Circuit Description and Operating Principle27910.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11Conclusion and Future works309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | •                                                                           |      |

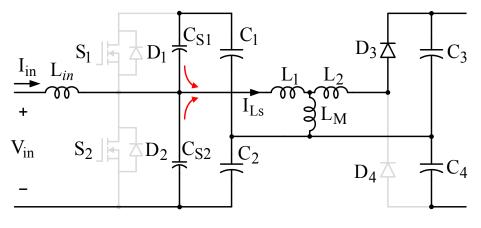

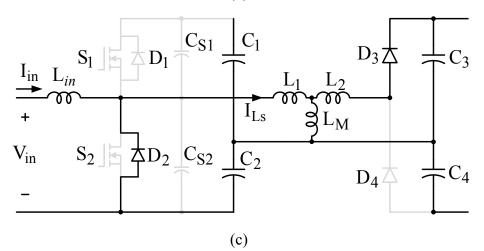

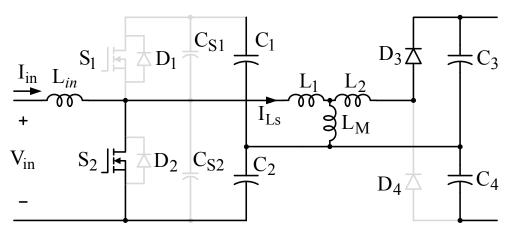

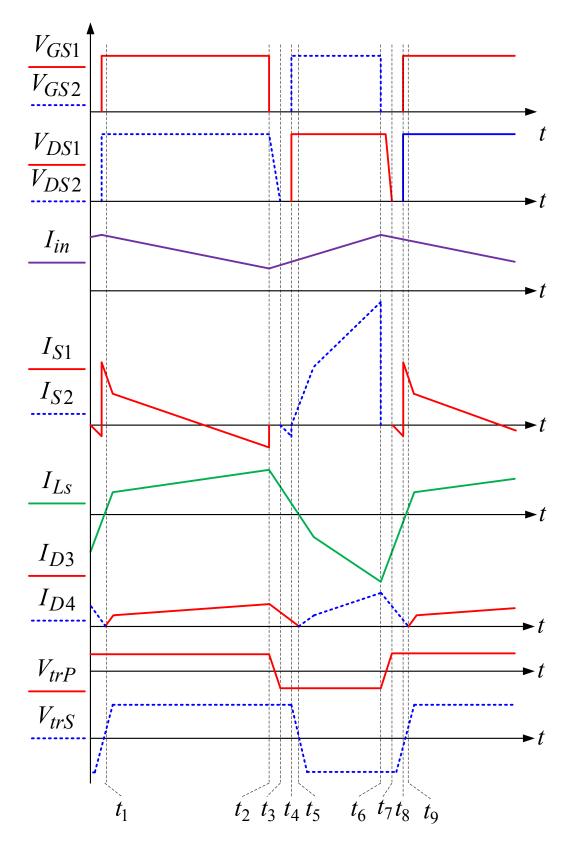

| 10.3Soft-switching Operation Principles of the DC-DC Converter Module29010.4Control Strategy29610.5Prototype and Experimental Results29610.6Conclusion308CHAPTER 11Conclusion and Future works309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |                                                                             |      |

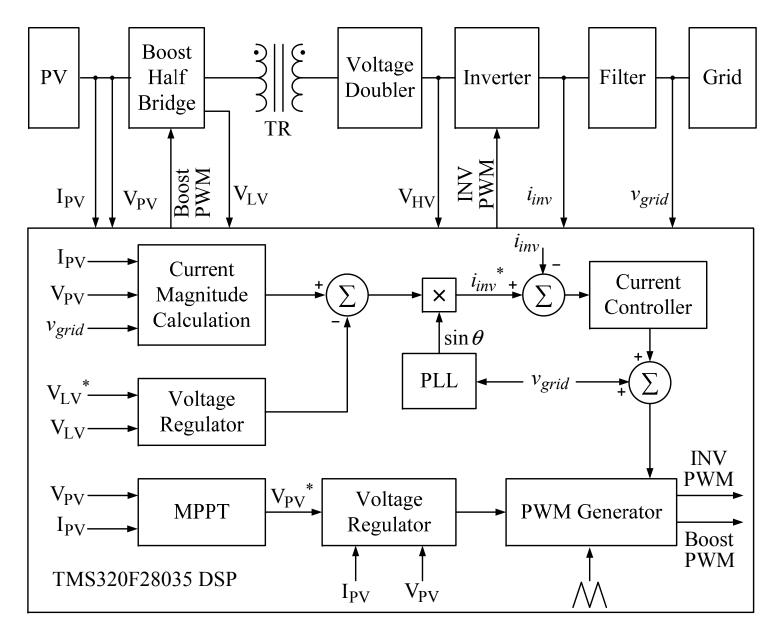

| 10.4 Control Strategy29610.5 Prototype and Experimental Results29610.6 Conclusion308CHAPTER 11 Conclusion and Future works309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |                                                                             |      |

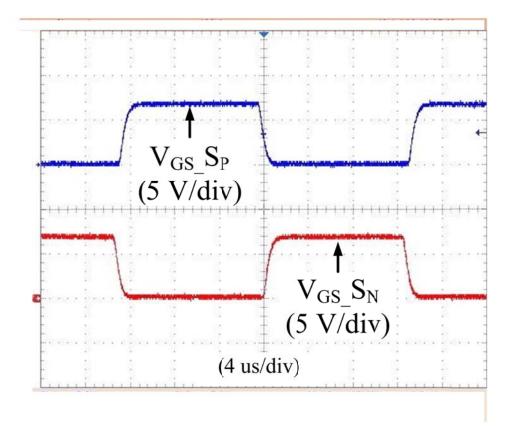

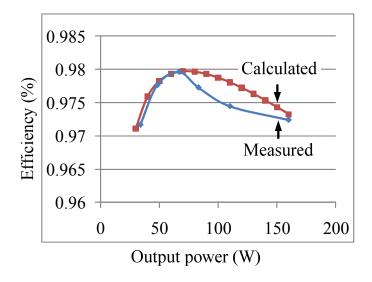

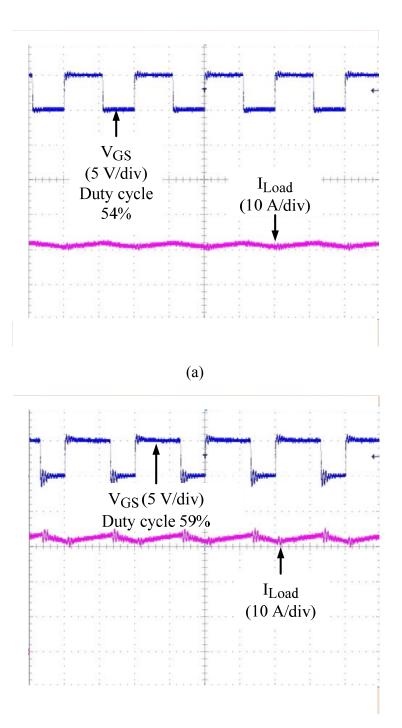

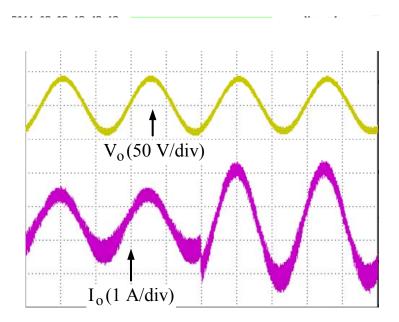

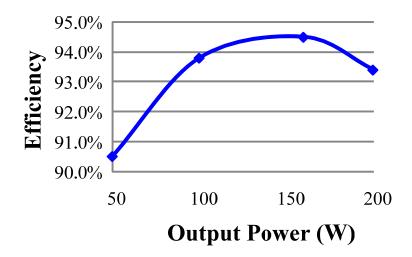

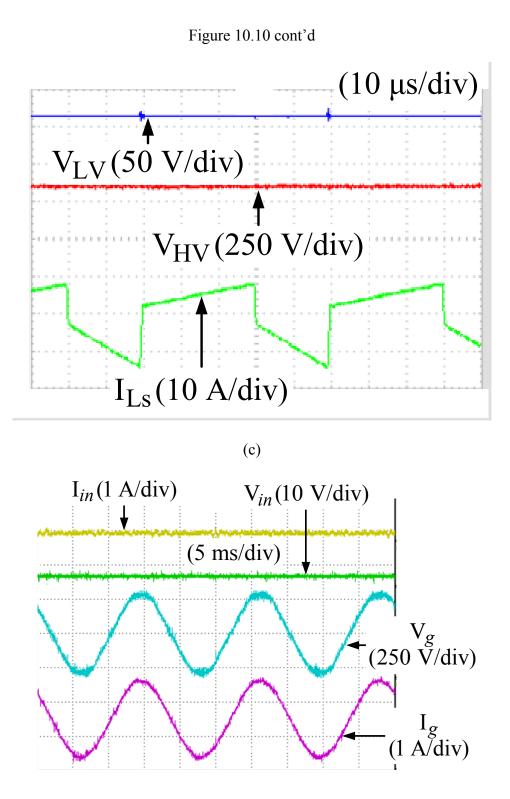

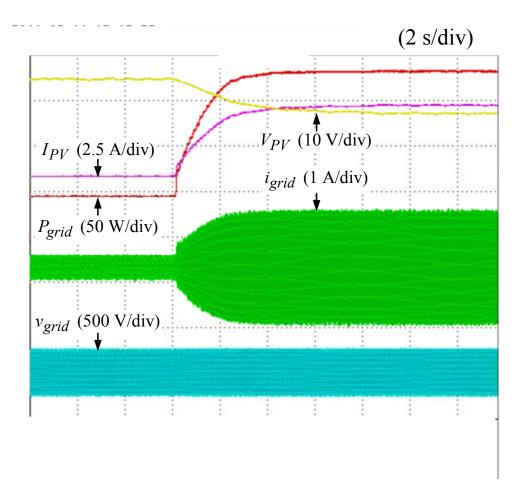

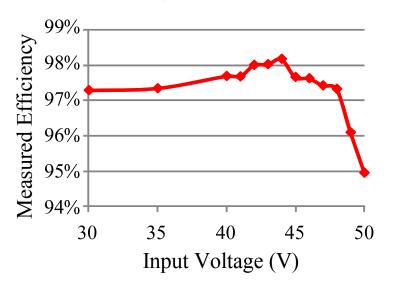

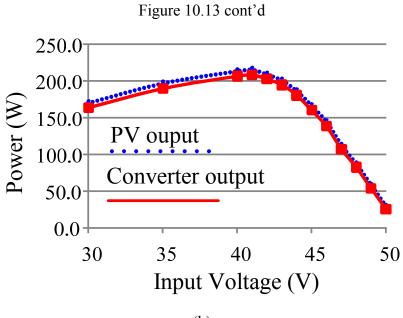

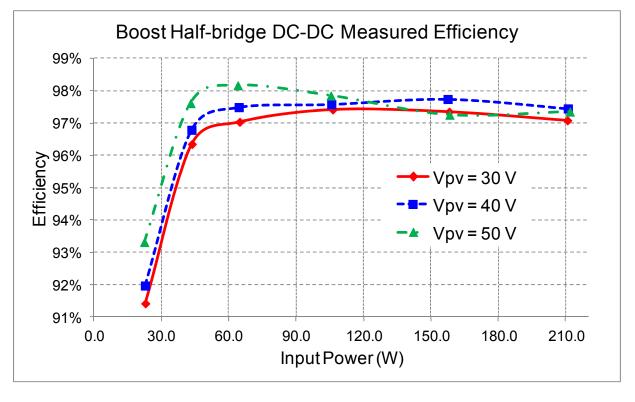

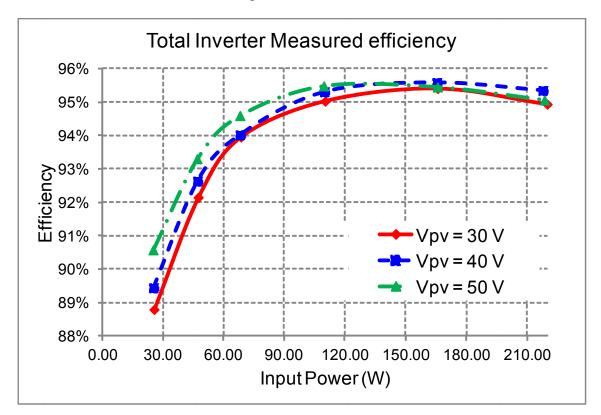

| 10.5       Prototype and Experimental Results       296         10.6       Conclusion       308         CHAPTER 11       Conclusion and Future works         309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                                                             |      |

| 10.6 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | Control Strategy                                                            | 296  |

| CHAPTER 11 Conclusion and Future works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |                                                                             |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10.6   | Conclusion                                                                  | 308  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | СНАРТ  | FER 11 Conclusion and Future works                                          | 309  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11.1   |                                                                             |      |

| 11.2   | Recommendations for Future Works | 311 |

|--------|----------------------------------|-----|

| BIBLIC | OGRAPHY                          | 313 |

# LIST OF TABLES

| Table 2.1 Required stray inductance according to switching frequency | 58  |

|----------------------------------------------------------------------|-----|

| Table 5.1 Circuit parameter examples for power loss analysis.        | 143 |

| Table 6.1 Comparison of SW-MMCCC and DW-MMCCC                        | 160 |

| Table 6.2 Switching Schemes (Steady State) of DW-MMCCC.              | 164 |

| Table 6.3 Switching Schemes (Steady State) of ZCS DW-MMCCC.          | 169 |

| Table 10.1 System specification                                      | 297 |

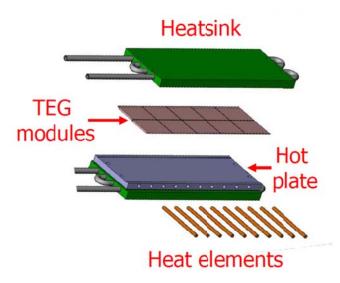

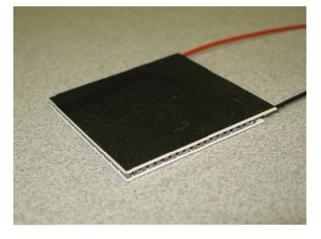

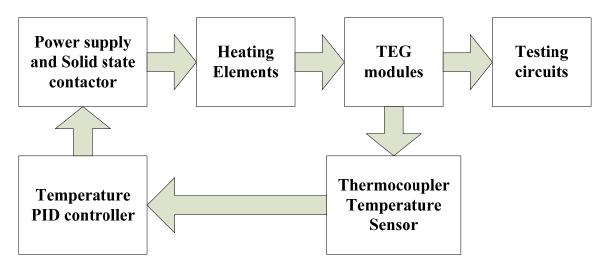

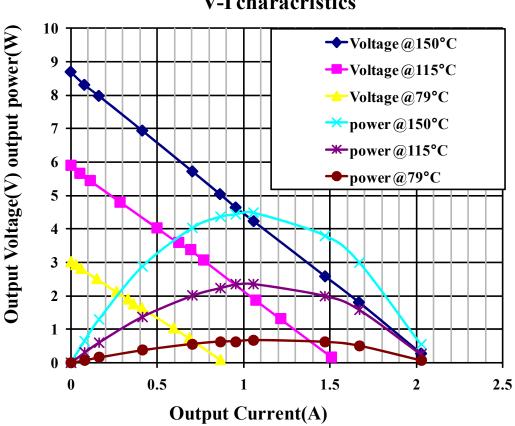

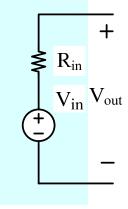

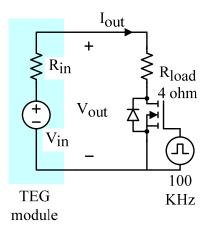

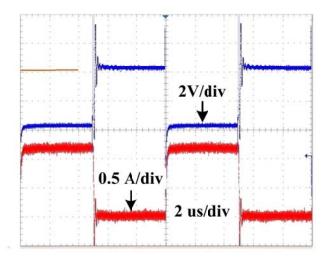

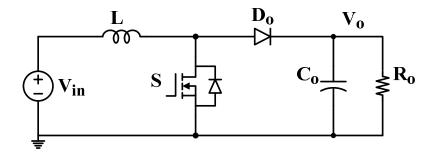

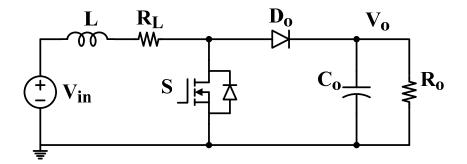

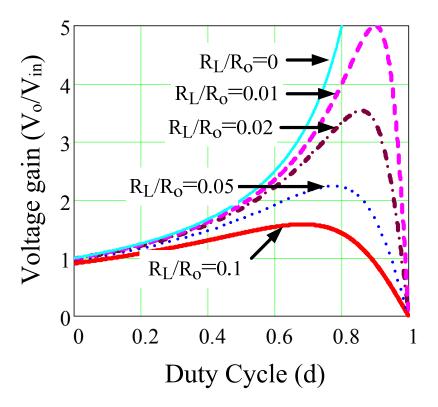

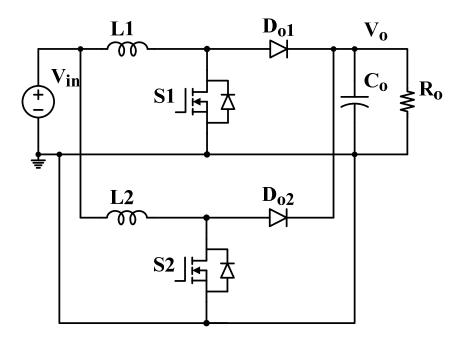

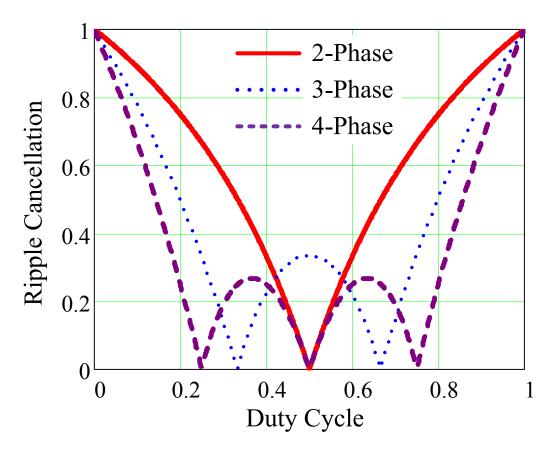

# **LIST OF FIGURES**